# A Novel Analog Front-End For ECG Acquisition

Øyvind Bjørkøy Theie

Master of Science in ElectronicsSubmission date:October 2012Supervisor:Trond Ytterdal, IETCo-supervisor:Bang Sup-Song, UCSD

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# A Novel Analog Front-End For ECG Acquisition

by

Øyvind Theie

Supervisors: Bang Sup Song Trond Ytterdal

Norwegian University of Science and Technology

Faculty of Information Technology Mathematics and Electrical Engineering

Department of Electronics and Telecommunications

Department of Electrical and Computer Engineering

# A Novel Analog Front-End For ECG Acquisition

# Abstract

This paper presents a novel, low-power analog front-end aimed for electrocardiogram (ECG) data acquisition. A typical ECG acquisition circuit is composed of a preamplifier, a filter and an analog-to-digital converter (ADC). The proposed solution takes all the analog front-end (AFE) components and integrates them into the loop filter of a 10-bit continuous-time  $\Delta\Sigma$ -ADC.

The  $\Delta\Sigma$ -ADC has a 100Hz bandwidth, achieves an ENOB<sup>1</sup> of 9.8 bits and a DR<sup>2</sup> of 85dB at a power consumption of  $3.6\mu W$ , which is comparable with current state-of-the-art. Through dynamic programming of preamplifier gain, the ADC can maintain a high conversion performance for a wide input signal range.

The low power consumption and moderate resolution makes the AFE especially attractive for portable ECG acquisition systems that utilize wireless data transmission.

$<sup>^{1}\</sup>mathrm{Effective}$  Number Of Bits $^{2}\mathrm{Dynamic}$  Range

# Acknowledgements

This project was carried out spring/summer 2012 and submitted on September 24, 2012 to NTNU, Trondheim. I would like to thank Professor Bang Sup-Song for his guidance and encouragement. Without him this project would not have been possible.

I would also like to thank Professor Trond Ytterdal at NTNU for his supervision and support.

I would like to thank Erik Fossum Færevaag, Mattis Pettersen, and all the others at Energy Micro. Lastly, I would like to thank Johnny Bjørnsen from Analog Concepts.

San Diego, September 24, 2012 Øyvind Theie

# Abbreviations

- AAF Anti-Aliasing Filter

- ADC Analog-to-Digital-Converter

- AFE Analog Front-End

- BJT Bipolar Junction Transistor

- CMFB Common-Mode FeedBack

- CMRR Common-Mode-Rejection-Ratio

- CT Continuous-Time

- DAC Digital-to-Analog-Converter

- DT Discrete-Time

- ENOB Effective Number Of Bits

- FB FeedBack

- FFT Fast Fourier Transform

- $\bullet\,$  FS Full Scale

- LNA Low Noise Amplifier

- LSB Least Significant Bit

- MOS Metal-Oxide-Semiconductor

- NTF Noise Transfer Function

- OSR OverSampling Ratio

- PDK Process Design Kit

- PGA Programmable Gain Amplifier

- PM Phase Margin

- PSD Power Spectral Density

- PVT Process, Voltage and Temperature variations

- RMS Root-Mean-Square

- SAR Successful Approximation

- SFDR Spurious-Free Dynamic Range

- SNR Signal-to-Noise-Ratio

- SNDR Signal-to-Noise-and-Distortion-Ratio

- SQNR Signal-to-Quantization-Noise-Ratio

- STF Signal Transfer Function

- THD Total Harmonic Distortion

#### Model definitions

$U_T = kT/q$  Thermal voltage

$n_i$  Intrinsic carrier concentration of silicon

$\epsilon_S\,$  Absolute dielectric constant of silicon

q Elementary charge

$C_{ox}$  Gate capacitance per unit area,  $C_{ox} = \frac{\epsilon_{SiO_2}}{T_{ox}}$ ,  $T_{ox}$  is the oxide thickness

$N_B$  Impurity concentration in the channel

$\phi_F = U_T ln(N_B/n_i)$  Fermi potential in the substrate

$V_{th0}$  Gate threshold voltage at equilibrium

$\mu\,$  Electron mobility in the channel

$\gamma = \frac{\sqrt{2qN_B\epsilon_S}}{C_{ox}}~$  Substrate factor

$W\!,L\,$  Effective electrical width and length of channel

$Q_i$  Mobile induced charge per unit area in the channel

$V_{ch}$  Channel "potential"

$V_p~$  The pinch-off voltage, describes the channel voltage when  $Q_i\approx 0$

$V_{eff}\,$  The effective channel voltage,  $V_{GS}-V_{th}$

$r_o\,$  The resistance looking into the drain of a MOS transistor

# Contents

| 1        | Intr | roduction                                                            | 1  |

|----------|------|----------------------------------------------------------------------|----|

| <b>2</b> | The  | eory                                                                 | 2  |

|          | 2.1  | Electrocardiography and the cardiac cycle                            | 2  |

|          | 2.2  | ADC fundamentals                                                     | 3  |

|          |      | 2.2.1 Quantization noise                                             | 4  |

|          |      | 2.2.2 ADC performance metrics                                        | 4  |

|          | 2.3  | Portable ECG circuits                                                | 5  |

|          | 2.4  | $\Delta\Sigma$ -Modulator fundamentals                               | 7  |

|          |      | 2.4.1 Noise shaping and oversampling                                 | 8  |

|          |      | 2.4.2 The loop filter                                                | 12 |

|          |      | 2.4.3 Stability                                                      | 13 |

|          |      | 2.4.4 $1^{st}$ - and $2^{nd}$ -order $\Delta\Sigma$ -modulators      | 13 |

|          |      | 2.4.5 $$ Summary of architectural choices and design techniques $$ . | 14 |

|          |      | 2.4.6 Continuous-Time $\Delta\Sigma$ -modulators                     | 15 |

|          | 2.5  | MOSFET devices                                                       | 17 |

|          |      | 2.5.1 Gate leakage                                                   | 19 |

| 3        | Cire | cuit specification                                                   | 22 |

|          | 3.1  | Noise                                                                | 24 |

|          |      | 3.1.1 Quantization noise                                             | 24 |

|          |      | 3.1.2 Intrinsic noise                                                | 24 |

|          |      | 3.1.3 Extrinsic noise                                                | 25 |

|          |      | 3.1.4 Total noise floor                                              | 25 |

|          | 3.2  | Digital post-filtering                                               | 26 |

| 4        | Des  | ign                                                                  | 28 |

|          | 4.1  | Simulation tools and methodology                                     | 28 |

|          | 4.2  | Architecture and concept                                             | 28 |

|          | 4.3  | Loop filter                                                          | 29 |

|          |      | 4.3.1 OTA and AGC                                                    | 29 |

|      | 4.3.2 Integrator scaling                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.4  | Preamplifier                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.5  | Comparator                                                                                                                                                                                                                       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.6  | SR-latch                                                                                                                                                                                                                         | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.7  | Delay element                                                                                                                                                                                                                    | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.8  | DAC                                                                                                                                                                                                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.9  | Buffer OTA                                                                                                                                                                                                                       | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.10 | Bias circuit                                                                                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.10.1 Generating $V_{n-casc}$ and $V_{n-casc}$                                                                                                                                                                                  | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.10.2 $V_{ref}$ -generation by resistor string divider 4                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.10.3 Generating bias for the preamplifier $\ldots \ldots \ldots \ldots 4$                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

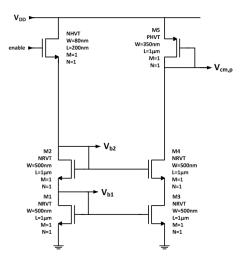

|      | 4.10.4 Generating $V_{b1}$ and $V_{b2}$                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.10.5 Logic gates                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Sim  | ulations 4                                                                                                                                                                                                                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.1  | Loop filter                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.1.1 Results summary                                                                                                                                                                                                            | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.1.2 Loop filter simulations                                                                                                                                                                                                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.1.3 Typical corner                                                                                                                                                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 5.1.4 Fully differential AGC input - Common-mode rejection . 5                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.2  | Preamplifier                                                                                                                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.3  | Comparator                                                                                                                                                                                                                       | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.4  | Summary                                                                                                                                                                                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.5  | Delay element                                                                                                                                                                                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.6  | Transient response of comparator and delay element 6                                                                                                                                                                             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.7  | DAC                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.8  | PVT                                                                                                                                                                                                                              | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.9  | $\Delta\Sigma$ -ADC                                                                                                                                                                                                              | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.10 | Power consumption                                                                                                                                                                                                                | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

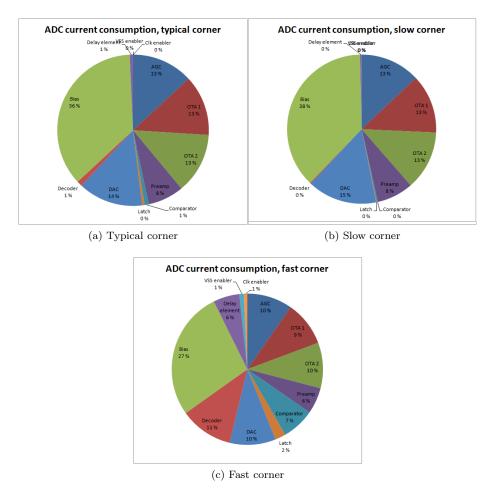

|      | 5.10.1 Submodule current consumption distribution against cor-<br>ners                                                                                                                                                           | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.11 |                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | <ul> <li>4.5</li> <li>4.6</li> <li>4.7</li> <li>4.8</li> <li>4.9</li> <li>4.10</li> </ul> Simulation 5.1 5.2 <ul> <li>5.3</li> <li>5.4</li> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>5.10</li> </ul> | 4.4       Preamplifier       3         4.5       Comparator       3         4.6       SR-latch       3         4.7       Delay element       3         4.8       DAC       3         4.9       Buffer OTA       3         4.10       Bias circuit       3         4.10       Generating $V_{n-casc}$ and $V_{n-casc}$ 3         4.10.1       Generating bias for the preamplifier       4         4.10.3       Generating $V_{b1}$ and $V_{b2}$ 4         4.10.4       Generating $V_{b1}$ and $V_{b2}$ 4         4.10.5       Logic gates       4         5.1       Loop filter       4         5.1.1       Results summary       4         5.1.2       Loop filter simulations       4         5.1.3       Typical corner       4         5.1.4       Fully differential AGC input - Common-mode rejection       5         5.2       Preamplifier       5         5.3       Comparator       5         5.4       Summary       6         5.5       Delay element       6         5.6       Transient response of comparator and delay element       6         5.7< |

|   |      | 5.11.1  | Capacitor area                                                                                                           | 80  |

|---|------|---------|--------------------------------------------------------------------------------------------------------------------------|-----|

|   |      | 5.11.2  | Resistor area                                                                                                            | 81  |

|   |      | 5.11.3  | MOSFET area                                                                                                              | 81  |

|   |      | 5.11.4  | Estimated area consumption including routing $\ldots \ldots$                                                             | 82  |

|   | 5.12 | Input   | referred noise                                                                                                           | 82  |

|   | 5.13 | ADC (   | Conversion performance                                                                                                   | 83  |

| 6 | Disc | ussion  | ı                                                                                                                        | 90  |

|   | 6.1  | Input   | structure                                                                                                                | 91  |

|   | 6.2  | Area    |                                                                                                                          | 91  |

|   | 6.3  | Linear  | ity - Telescopic OTA                                                                                                     | 92  |

|   | 6.4  | AGC .   |                                                                                                                          | 93  |

|   | 6.5  | Gate l  | eakage                                                                                                                   | 93  |

|   | 6.6  | Power   |                                                                                                                          | 93  |

|   | 6.7  | Noise . |                                                                                                                          | 94  |

| 7 | Con  | clusio  | n                                                                                                                        | 95  |

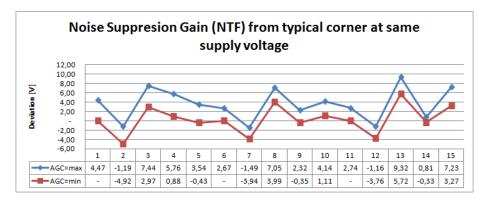

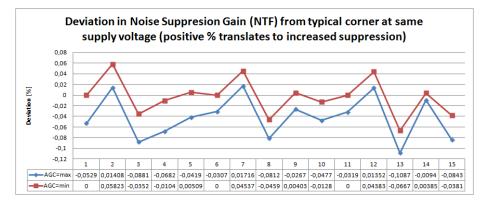

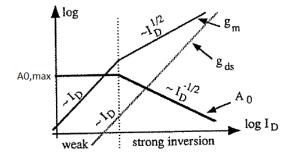

| 8 | The  | effect  | of AGC gain variation on NTF gain                                                                                        | 99  |

|   |      | 8.0.1   | Analysis of the effect of varying AGC gain in the loop filter of the classical source-degenerated OTA                    | 99  |

|   |      | 8.0.2   | Small-signal analysis of classical source-degenerated OTA                                                                | 100 |

|   |      | 8.0.3   | Small signal analysis of first integrator node using classical source-degenerated OTAs with variable degeneration in AGC | 100 |

|   |      | 8.0.4   | Measured results of the effect of varying AGC gain in the loop filter of the classical source-degenerated OTA $\ldots$ . | 102 |

|   |      | 8.0.5   | Small signal analysis of telescopic OTA                                                                                  | 105 |

| 9 | Nois | e in E  | OSM                                                                                                                      | 108 |

|   | 9.1  | Noise   | contribution from cascodes                                                                                               | 108 |

|   | 9.2  | Noise   | contribution from active load                                                                                            | 108 |

|   | 9.3  | Noise   | contribution from source degenerating resistor, $R_S$                                                                    | 109 |

|   | 9.4  | Noise   | contribution from differential pair tail current mirror $\ldots$                                                         | 109 |

|   | 9.5  | Input   | referred noise of telescopic OTA                                                                                         | 110 |

|              | 9.6  | Input referred noise of loop filter                         | 110 |

|--------------|------|-------------------------------------------------------------|-----|

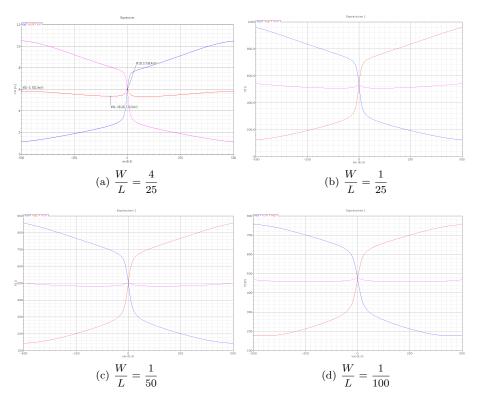

| 10           | Des  | ign considerations                                          | 112 |

|              |      | 10.0.1 OTA scaling considerations                           | 112 |

|              | 10.1 | Derivations for bias circuitry of telescopic OTA's cascodes | 113 |

| 11           | Add  | litional simulation results                                 | 117 |

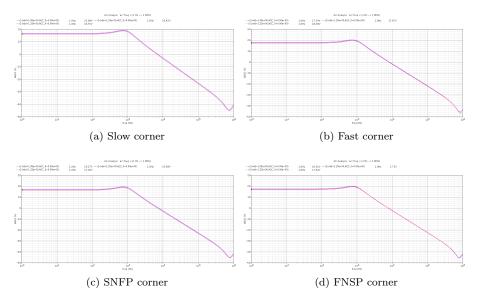

|              | 11.1 | Loop filter                                                 | 117 |

|              | 11.2 | Preamplifier                                                | 126 |

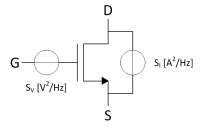

| A            | мо   | SFET                                                        | 128 |

|              |      | A.0.1 Noise in MOS transistors                              | 130 |

| в            | Idle | -tones in $1^{st}$ -order $\Delta\Sigma$ -modulators        | 132 |

| $\mathbf{C}$ | The  | cardiac cycle                                               | 133 |

| D            | MA   | TLAB script for plotting and sizing of transistors          | 135 |

| $\mathbf{E}$ | Test | bench for $V_{DS}$ sweeps for $g_m/I_D$ -methodology        | 147 |

# List of Figures

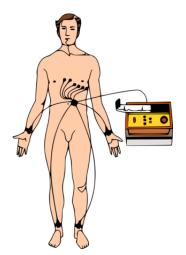

| 1  | A patient connected to an ECG.                                                                                        | 2  |

|----|-----------------------------------------------------------------------------------------------------------------------|----|

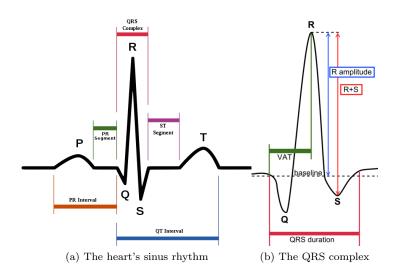

| 2  | Schematic representation of ECG.                                                                                      | 3  |

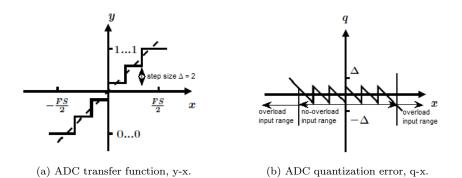

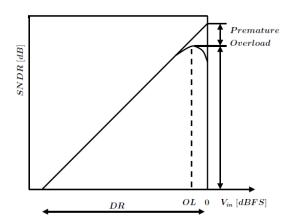

| 3  | ADC SNDR versus input amplitude                                                                                       | 5  |

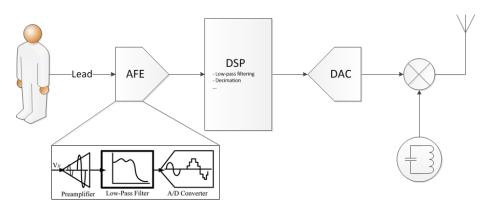

| 4  | A typical portable ECG block diagram.                                                                                 | 6  |

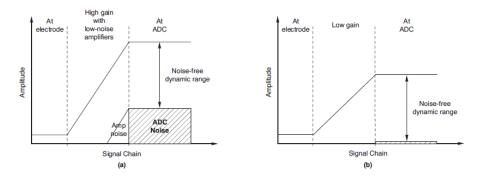

| 5  | System approach based on ADC resolution                                                                               | 6  |

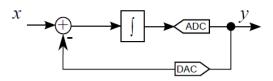

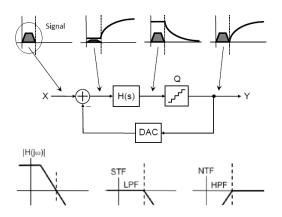

| 6  | $\Delta\Sigma$ -ADC block                                                                                             | 7  |

| 7  | Voltage-to-frequency conversion using a 1-bit quantizer. Colored pulses represent 1's, white pulses represent 0's.    | 8  |

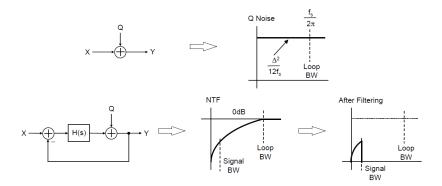

| 8  | Noise shaping and digital filtering                                                                                   | 9  |

| 9  | Spectrum shaping in $\Delta\Sigma$ -modulator                                                                         | 9  |

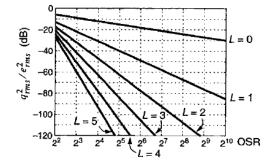

| 10 | Theoretical in-band noise power for $\mathcal{L}^{th}\text{-}\mathrm{order}\ \Delta\Sigma\text{-}\mathrm{modulator.}$ | 11 |

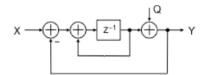

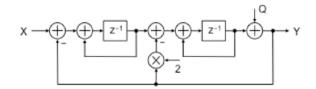

| 11 | $1^{st}$ -order $\Delta\Sigma$ -modulator                                                                             | 13 |

| 12 | $2^{nd}$ -order $\Delta\Sigma$ -modulator.                                                         | 13 |

|----|----------------------------------------------------------------------------------------------------|----|

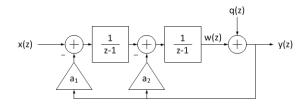

| 13 | $2^{nd}$ -order loop filter coefficient scaling                                                    | 14 |

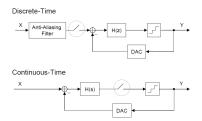

| 14 | Discrete-Time versus Continuous-Time modulator                                                     | 15 |

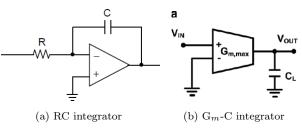

| 15 | CT integrators.                                                                                    | 16 |

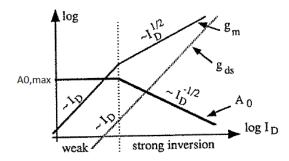

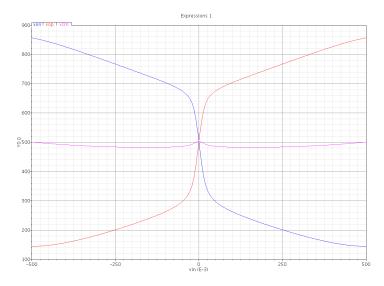

| 16 | Change of gain, $g_m$ , $g_{ds}$ and inversion with respect to $I_D$ , not accounting for DIBL.    | 19 |

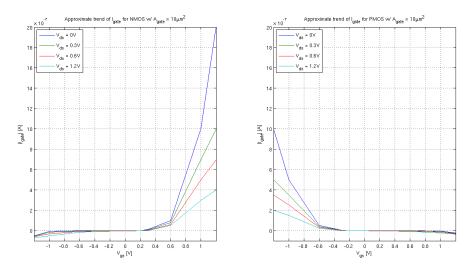

| 17 | $I_{gate}$ for $V_{ds}$ versus $V_{gs}$                                                            | 20 |

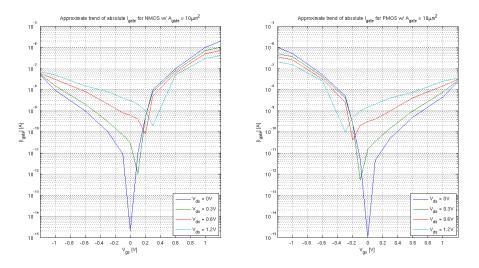

| 18 | Absolute $I_{gate}$ for $V_{ds}$ versus $V_{gs}$                                                   | 20 |

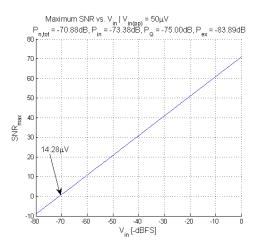

| 19 | Ideal SNR with $50\mu V_{ni(pp)}$                                                                  | 26 |

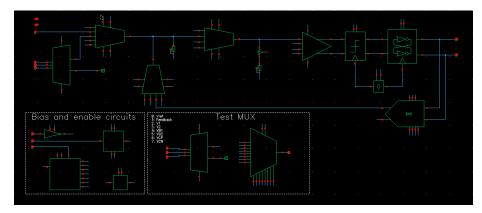

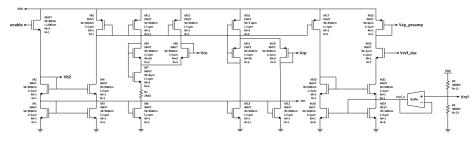

| 20 | Schematic of the ADC in its entirety including a test MUX                                          | 29 |

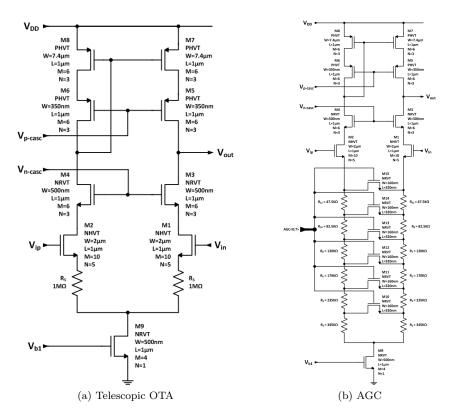

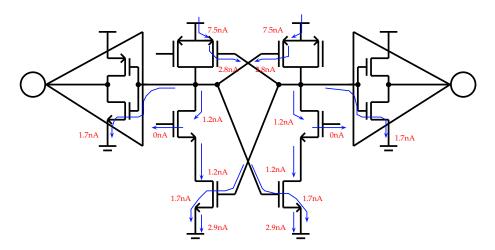

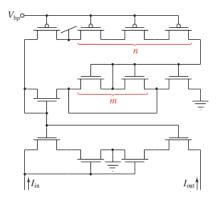

| 21 | Schematic of OTAs                                                                                  | 30 |

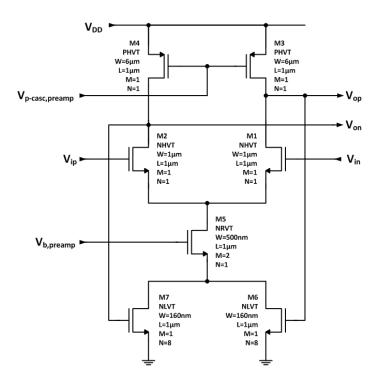

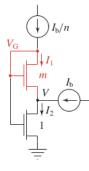

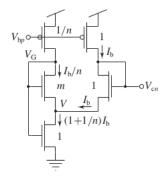

| 22 | Schematic of fully differential preamplifier                                                       | 32 |

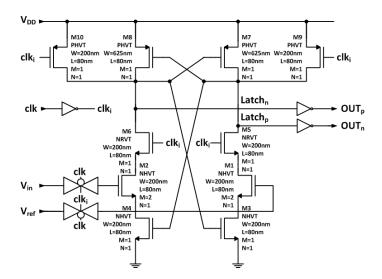

| 23 | Schematic of comparator.                                                                           | 33 |

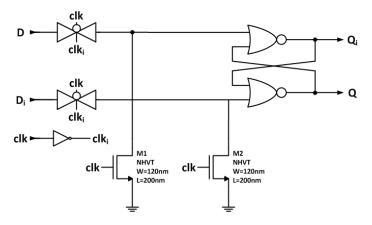

| 24 | Schematic of SR-latch.                                                                             | 34 |

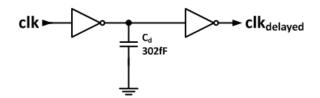

| 25 | Schematic of delay element.                                                                        | 35 |

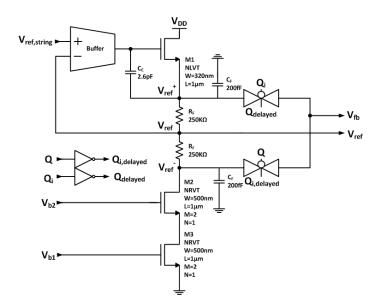

| 26 | Schematic of DAC.                                                                                  | 36 |

| 27 | Schematic of buffer OTA                                                                            | 37 |

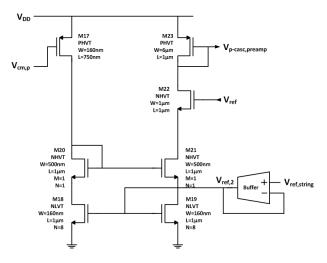

| 28 | Full schematic view of bias circuit.                                                               | 38 |

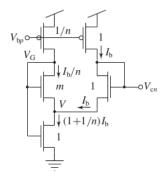

| 29 | Low-voltage cascode bias.                                                                          | 38 |

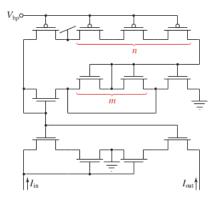

| 30 | Layout driven design.                                                                              | 39 |

| 31 | Resistor string for generation of $V_{ref}$                                                        | 40 |

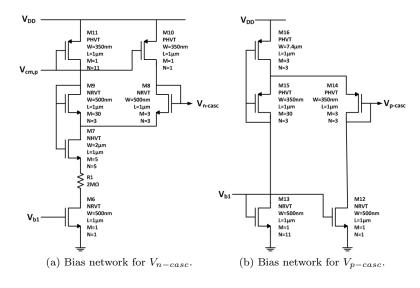

| 32 | Bias network for preamplifier                                                                      | 40 |

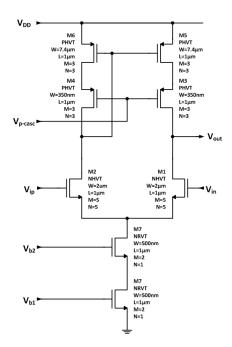

| 33 | Zoom in of bias network for $V_{b1}$ and $V_{b2}$                                                  | 41 |

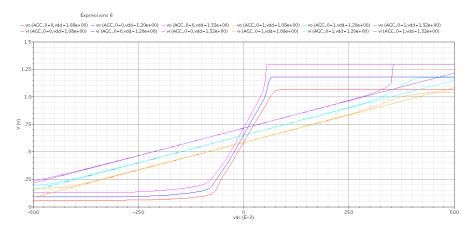

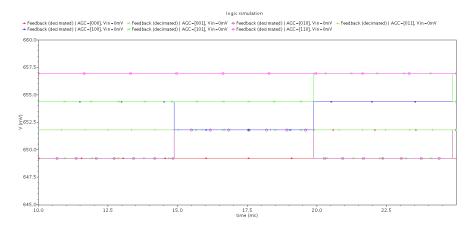

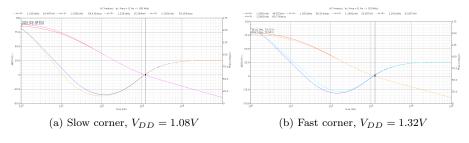

| 34 | DC response for AGC=[000,110] versus supply voltage                                                | 45 |

| 35 | Closed loop DC response of filter for $AGC = [000, 110]$                                           | 45 |

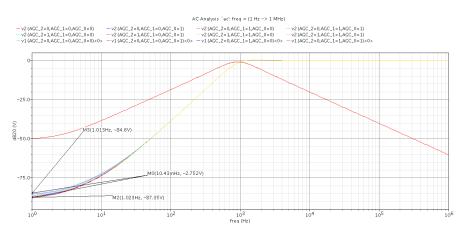

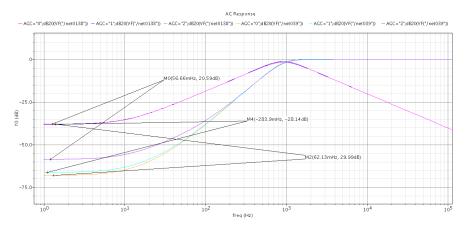

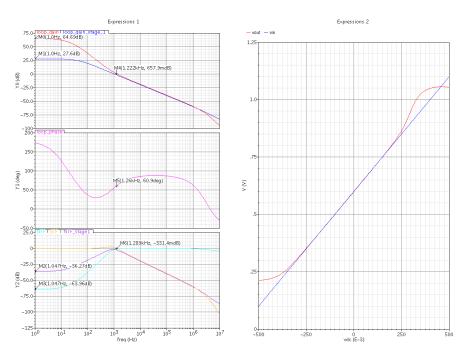

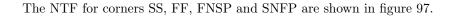

| 36 | NTF for $AGC = [000 \rightarrow 110]$                                                              | 46 |

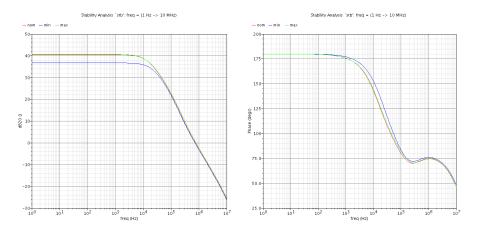

| 37 | Open loop frequency response in nominal corner                                                     | 46 |

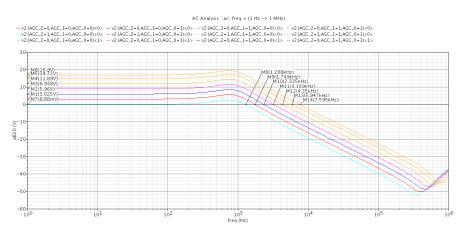

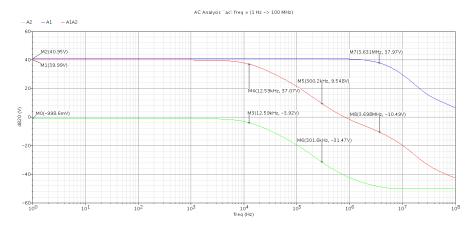

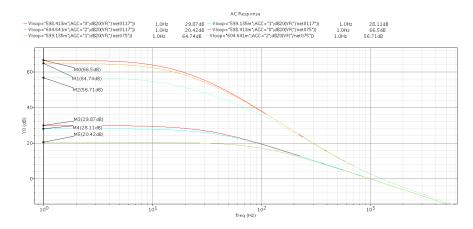

| 38 | STF for $AGC = [000 \rightarrow 110]$ in nominal corner                                            | 47 |

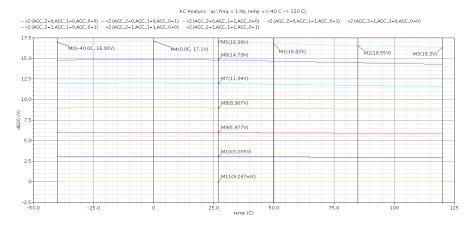

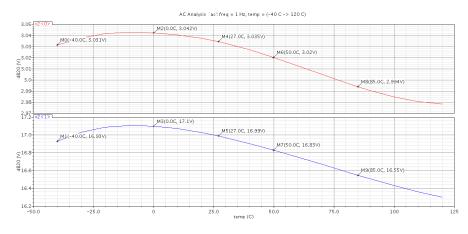

| 39 | $A_{v_{STF}}$ for $AGC = [000 \rightarrow 110]$ versus temperature, $V_{DD} = 1.2V$ .              | 47 |

| 40 | $A_{v_{STF}}$ for $AGC = [001, 110]$ versus temperature, $V_{DD} = 1.2V.$                          | 48 |

| 41 | $A_{v_{STF}}$ for $AGC = [110]$ versus temperature, for minimum, nom-<br>inal and maximum corners. | 48 |

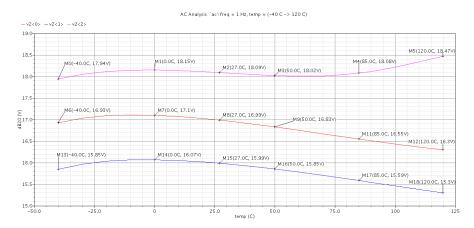

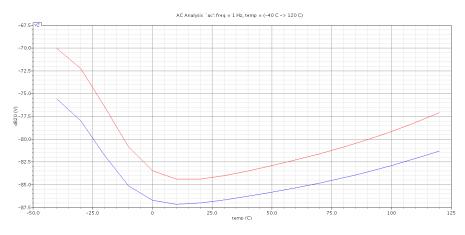

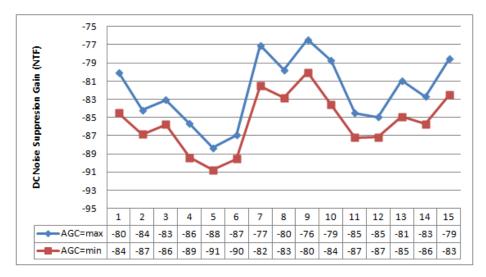

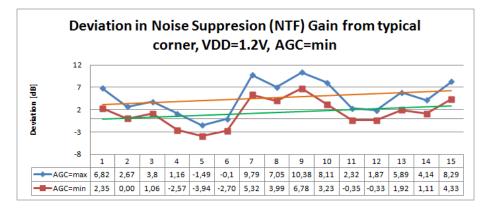

| 42 | $A_{v_{NTF}}$ for $AGC = [001, 110]$ versus temperature, $V_{DD} = 1.2V$ .                                                                                                                                                                                                                                                                          | 49 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

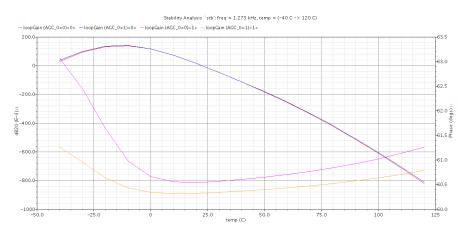

| 43 | Open loop gain and phase seen at 1273Hz versus temperature for $AGC = [000, 110]$ .                                                                                                                                                                                                                                                                 | 49 |

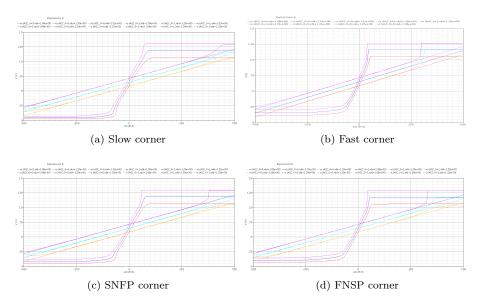

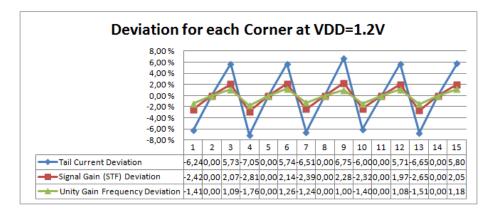

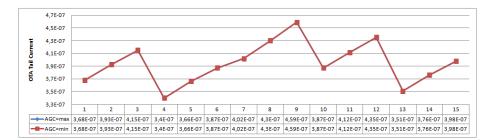

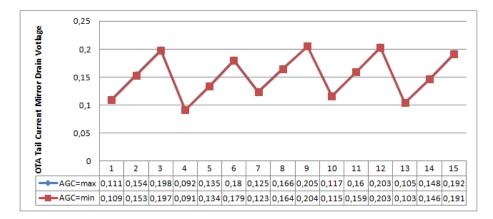

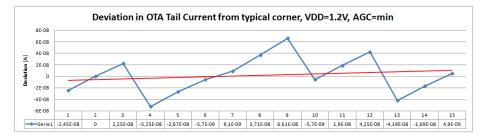

| 44 | $A_{v_{STF}} _{AGC=[000]}$ , OTA tail current and $f_{ug}$ vs. process and supply. $V_{DD}$ swept for each process and related to typical supply voltage (1.2V) for each process ( $\#_1$ -notation)                                                                                                                                                | 52 |

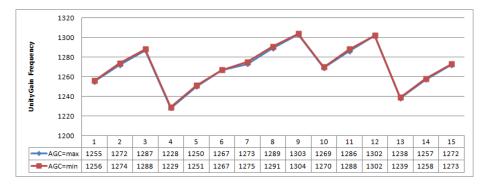

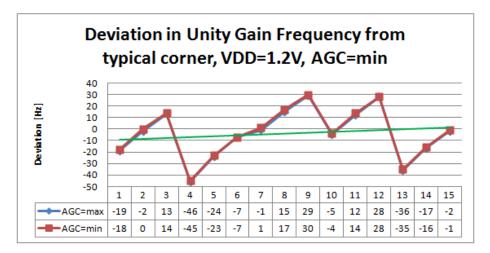

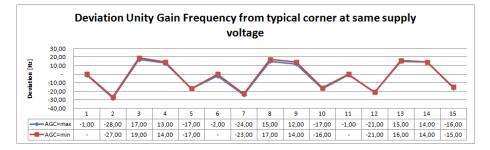

| 45 | Unity gain frequency [Hz], $f_{ug}$ , vs. process and supply (#1-notation)                                                                                                                                                                                                                                                                          | 52 |

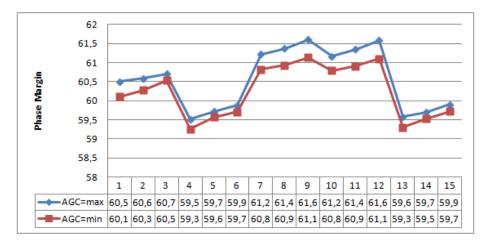

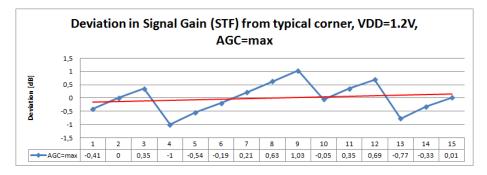

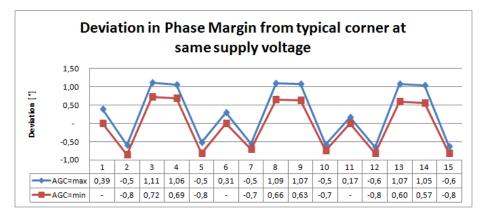

| 46 | Phase margin [°] vs. process and supply ( $\#_1$ -notation)                                                                                                                                                                                                                                                                                         | 53 |

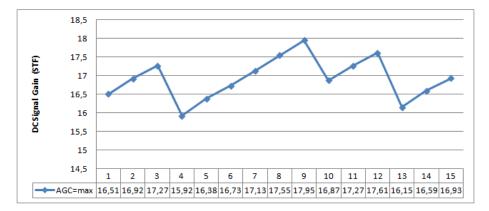

| 47 | $A_{v_{STF}}$ for $AGC = [000, 110]$ vs. process and supply (#1-notation).                                                                                                                                                                                                                                                                          | 53 |

| 48 | $A_{v_{NTF}}$ for $AGC = [000, 110]$ vs. process and supply (#1-notation).                                                                                                                                                                                                                                                                          | 54 |

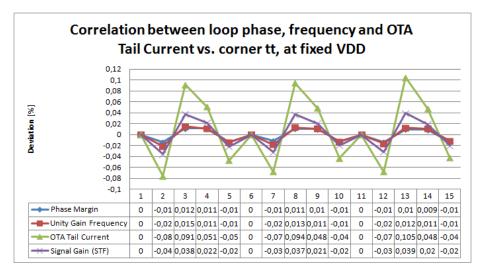

| 49 | Correlation between phase margin, $f_{ug}$ , OTA tail current and $\Delta A_{v_{STF}}$ , vs. process and supply (#2-notation). Process has been swept for a fixed $V_{DD} = [1.08, 1.2, 1.32]V$ , and related to process tt in percentages.                                                                                                         | 54 |

| 50 | Differential and common-mode outputs between $\pm 500 mV$ differential input in typical corner.                                                                                                                                                                                                                                                     | 56 |

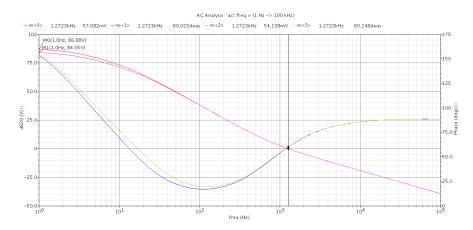

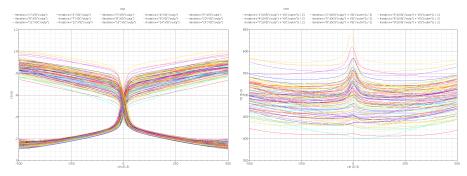

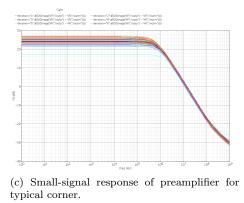

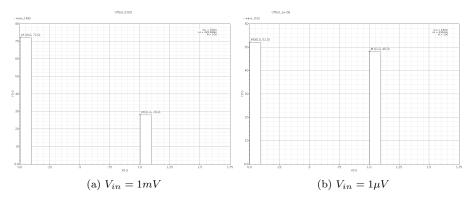

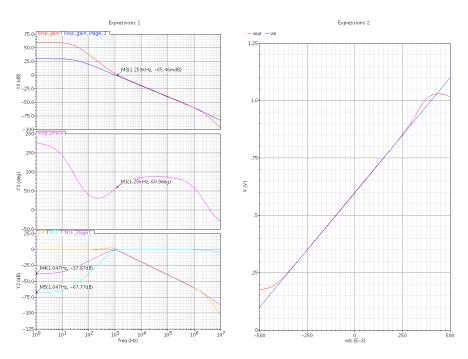

| 51 | Small-signal and DC response of preamp in typical corner                                                                                                                                                                                                                                                                                            | 56 |

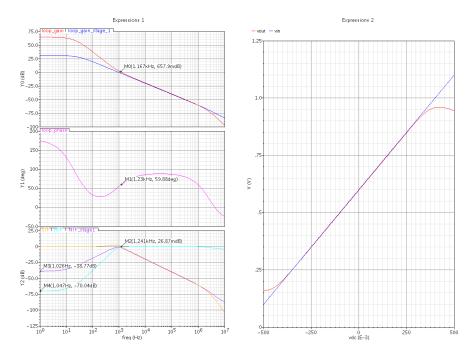

| 52 | Small-signal and DC response of preamp from Monte Carlo analysis.                                                                                                                                                                                                                                                                                   | 57 |

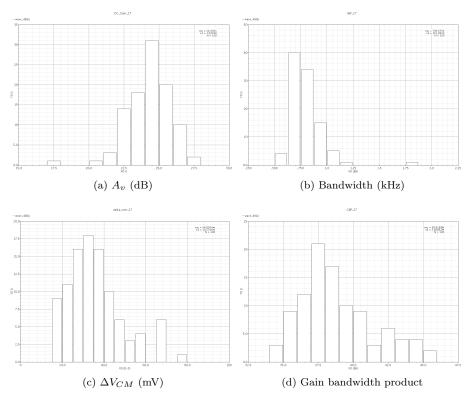

| 53 | Monte Carlo distribution of key characteristics of preamplifier                                                                                                                                                                                                                                                                                     | 58 |

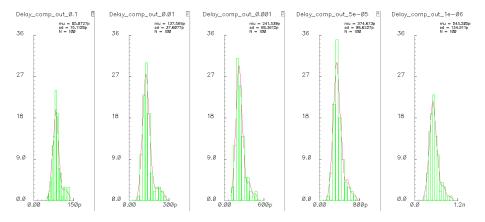

| 54 | Time delay for the latch output (pre-buffer) to reach 90% of $V_{DD}$ ,<br>$V_{in} = [1u, 50u, 1m, 10m, 100m]V$                                                                                                                                                                                                                                     | 59 |

| 55 | Time delay for the comparator output (post-buffer) to reach 90% of $V_{DD}$ , $V_{in} = [1u, 50u, 1m, 10m, 100m]V$                                                                                                                                                                                                                                  | 59 |

| 56 | Monte Carlo results of offset rate                                                                                                                                                                                                                                                                                                                  | 60 |

| 57 | Leakage estimates of comparator in typical corner. $\ldots$                                                                                                                                                                                                                                                                                         | 62 |

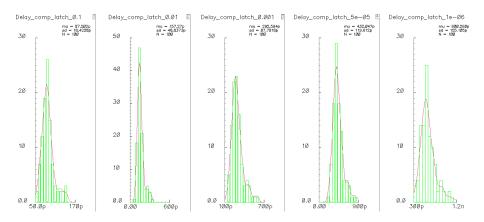

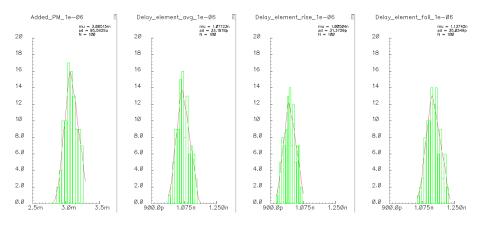

| 58 | Monte Carlo simulation for delay element                                                                                                                                                                                                                                                                                                            | 62 |

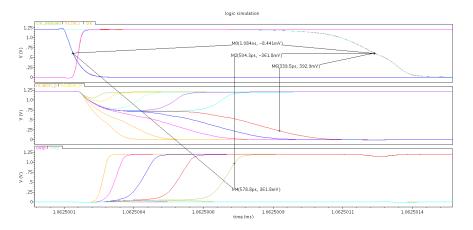

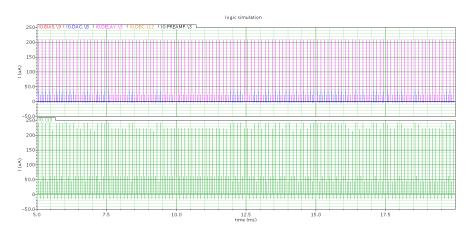

| 59 | Transient response of the comparator's latch output and the com-<br>parator's buffer output for $V_{in} = [1\mu, 50\mu, 1m, 10m, 100m]V$ . The<br>upper plot depicts the clock signals, the middle plot shows the<br>output nodes of the latches in the comparator, while the lower<br>plot depicts the outputs of the comparator after the buffers | 63 |

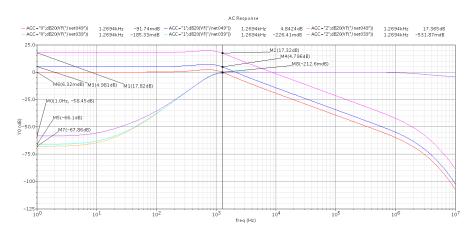

| 60 | Frequency response of voltage buffer in negative feedback config-<br>uration for typical, slow and fast corner.                                                                                                                                                                                                                                     | 64 |

| 61 | Open loop response of first stage (blue), second stage (source follower) (green) and the two-stage buffer (blue).                                                                                                                                                                                                                                   | 65 |

| 62 | Transient response of DAC for $V_{DD} = [1.08, 1.2, 1.32]V.$                                                                                                                                                                                                                                                                                        | 65 |

| 63 | Transition between high and low feedback, seen at nodes $V_{ref}^+$ , $V_{ref}$ , $V_{and}$ fb with $C_C = 2pF$ and no $C_F$ to reduce glitches                                                                                                                                                                                                                                                                       | 7–<br>ref<br>66 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 64 | Settling of $V_{fb}$ and $V_{ref}$ with $C_C = 2pF$ and no $C_F$ to reduce glitches.                                                                                                                                                                                                                                                                                                                                  | 66              |

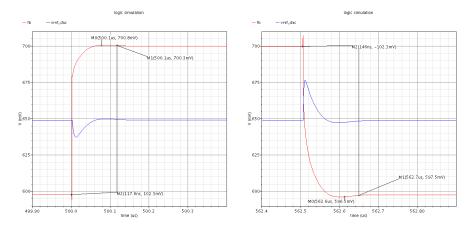

| 65 | Transient response of nodes $V_{fb}, V_{ref}^+, V_{ref}$ and $V_{ref}^-$ when switching states.                                                                                                                                                                                                                                                                                                                       | 67              |

| 66 | Rising and falling edge of $V_{fb}$ . The settling times are consistent with what we expect.                                                                                                                                                                                                                                                                                                                          | 68              |

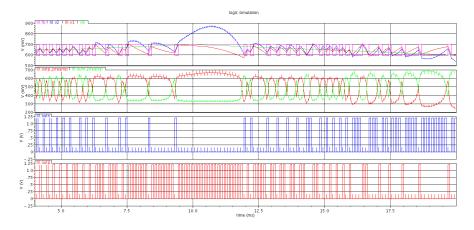

| 67 | Transient response of nodes $V_{in}$ (green), $V_1$ (red), $V_2$ (blue), $V_{fb}$ (pink) above, $V_{out,preamp}^+$ (red) and $V_{out,preamp}^-$ (green) in the middle, and $V_{out,comparator}^-$ (blue) and $V_{out,comparator}^+$ (red) in the two bottom plots. $V_1$ and $V_2$ are the first and second integrating node of the loop filter, while $V_{fb}$ is the negative feedback voltage provided by the DAC. | 69              |

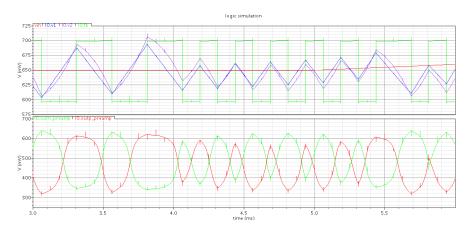

| 68 | Zoom in of transient response                                                                                                                                                                                                                                                                                                                                                                                         | 70              |

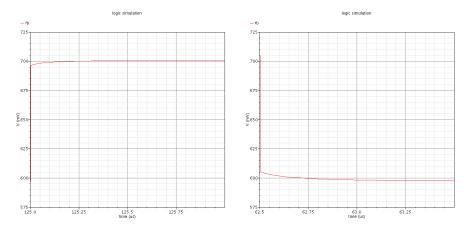

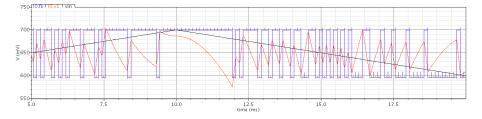

| 69 | Transient response of $V_1$ (red), $V_{fb}$ (blue) and $V_{in}$ (black)                                                                                                                                                                                                                                                                                                                                               | 71              |

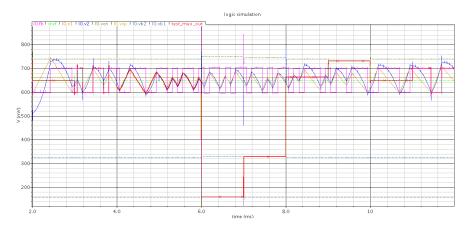

| 70 | Transient simulation when sweeping test-MUX setting                                                                                                                                                                                                                                                                                                                                                                   | 71              |

| 71 | Non-post-filtered decimated offset when $V_{in} = 0V$                                                                                                                                                                                                                                                                                                                                                                 | 72              |

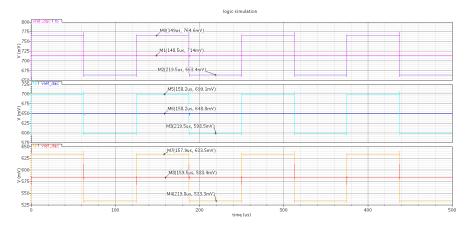

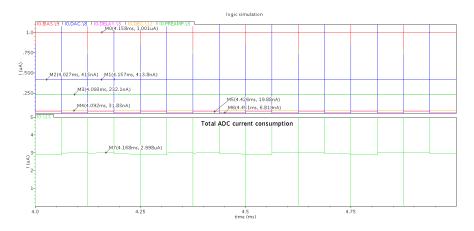

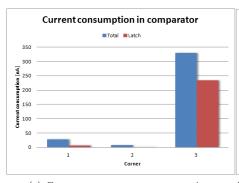

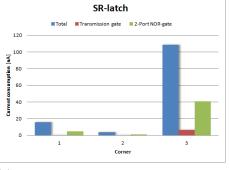

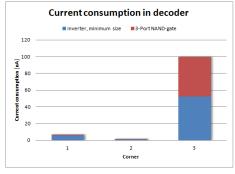

| 72 | The upper plot displays the current consumption of the following blocks for typical corner: Bias (red), DAC (blue), delay (pink), decoder (yellow), preamplifier (green). The lower plot displays the total current consumption of the whole ADC                                                                                                                                                                      | 73              |

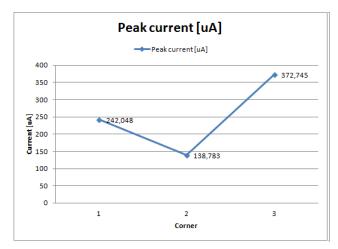

| 73 | Peak current consumption, same notation as figure above (except<br>for the color of the preamp has been changed from green to black).                                                                                                                                                                                                                                                                                 | 74              |

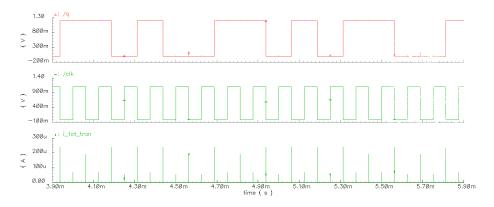

| 74 | Peak current consumption versus clock- and latched signal signal.                                                                                                                                                                                                                                                                                                                                                     | 74              |

| 75 | Peak current consumption versus nominal, minimum and maxi-<br>mum corner                                                                                                                                                                                                                                                                                                                                              | 75              |

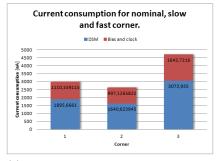

| 76 | Total current consumption                                                                                                                                                                                                                                                                                                                                                                                             | 77              |

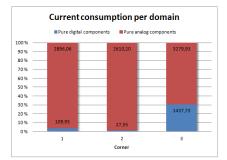

| 77 | Total current consumption ratio of submodules in minimum, nom-<br>inal and maximum corners.                                                                                                                                                                                                                                                                                                                           | 78              |

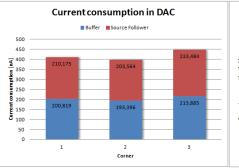

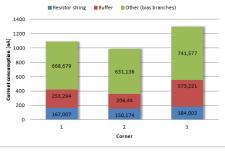

| 78 | Submodule current consumption in minimum, nominal and max-<br>imum corner.                                                                                                                                                                                                                                                                                                                                            | 79              |

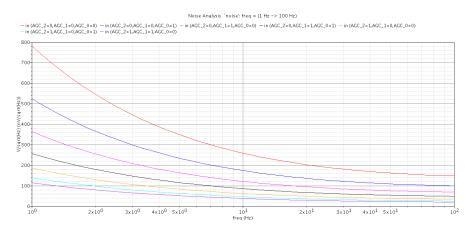

| 79 | Equivalent input referred noise for $AGC = [000 \rightarrow 110]$ within the bandwidth.                                                                                                                                                                                                                                                                                                                               | 82              |

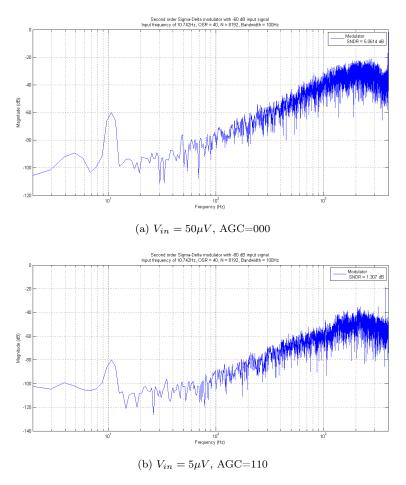

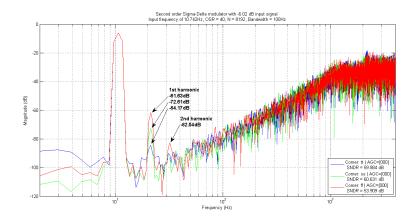

| 80 | FFT for $AGC = [000, 110]$ , with $V_{in}$ close to the dynamic range of each AGC setting                                                                                                                                                                                                                                                                                                                             | 84              |

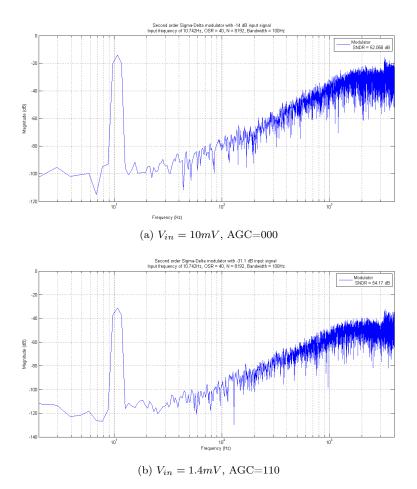

| 81  | FFT of $V_{in} = [1.4, 10]mV$ for AGC=[000,110]. The signal gain<br>of AGC=[110] amplifies the 1.4mV signal up to a 10mV level,<br>resulting in the two settings producing the same output signal,<br>with approximately the same SNDR values |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

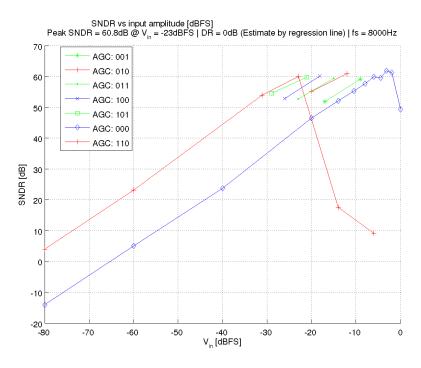

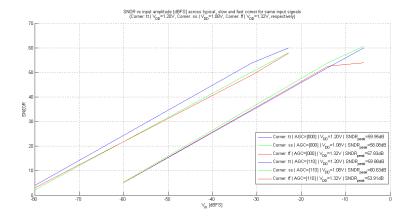

| 82  | SNDR (input referred noise excluded) for all AGC gain settings<br>and $V_{in}$ swept                                                                                                                                                          |

| 83  | $V_{in}$ sweep for AGC=[000,110] versus nominal, minimum and max-<br>imum corner                                                                                                                                                              |

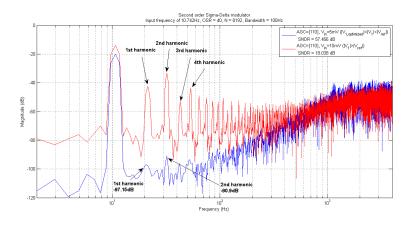

| 84  | FFT for a 25mV input signal, AGC=[000] against nominal, min-<br>imum and maximum corners                                                                                                                                                      |

| 85  |                                                                                                                                                                                                                                               |

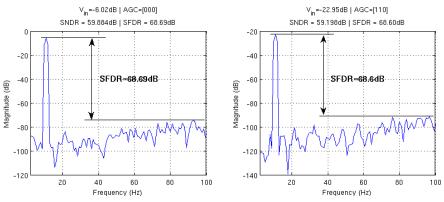

| 86  | SFDR within 100Hz bandwidth                                                                                                                                                                                                                   |

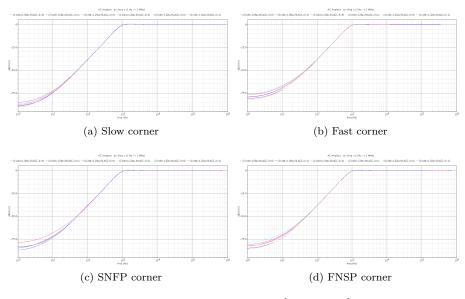

| 87  | STF and NTF of the three AGC cases                                                                                                                                                                                                            |

| 88  | NTF of the three AGC cases                                                                                                                                                                                                                    |

| 89  | Loop gain of the three AGC cases                                                                                                                                                                                                              |

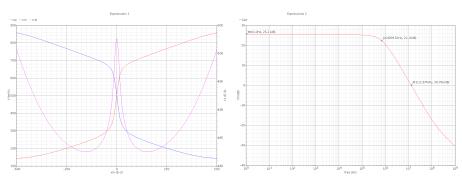

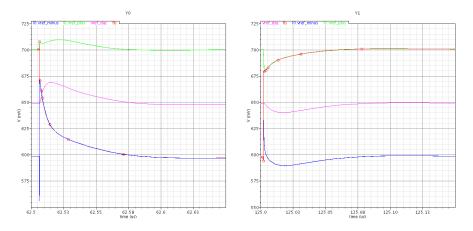

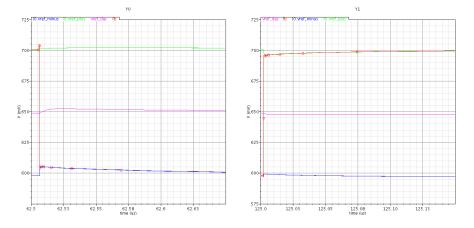

| 90  | AC and DC loop response using classic OTA. Corner: TT $\ . \ . \ . \ 104$                                                                                                                                                                     |

| 91  | AC and DC loop response using classic OTA. Corner: SS $\ldots$ 104                                                                                                                                                                            |

| 92  | AC and DC loop response using classic OTA. Corner: FF $\ . \ . \ . \ 105$                                                                                                                                                                     |

| 93  |                                                                                                                                                                                                                                               |

| 94  | Low-voltage cascode bias                                                                                                                                                                                                                      |

| 95  | Layout driven design                                                                                                                                                                                                                          |

| 96  | NTF of filter for $PGA = [000, 110]$                                                                                                                                                                                                          |