# Automated Self-Test of an Analog Delta-Sigma Modulator

Trond Jarle Pedersen

Master of Science in Electronics

Submission date: June 2007

Supervisor: Trond Sæther, IET

Co-supervisor: Are Hellandsvik, Atmel Norway

Norwegian University of Science and Technology Department of Electronics and Telecommunications

#### **Problem Description**

#### Background:

Time spent in semiconductor factories on testing manufactured integrated circuits is a large part of the total cost of production. The AVR Microcontroller contains an increasing amount of analog circuitry that pose a great challenge in design for test, both in terms of time spent on testing and the accuracy of test equipment.

Delta-Sigma Modulators are popular in ADCs due to the high accuracy obtainable in low-cost standard CMOS technology. DS-ADCs are however difficult to test efficiently, especially in low-bandwidth, high-oversampling implementations.

#### Description:

We want to investigate the possibility of implementing a Built In Self-Test of an analog delta-sigma modulator using circuit components available on the AVR Microcontroller. The project objective is to investigate the state-of-the-art in Automated Built-In Self Test, ABIST, for DS ADCs and implementing one on the AVR Microcontroller.

The following topics are of special interest:

- Implementation cost (area, circuit complexity, speed of test)

- Test coverage

- Test equipment requirements

Analysis and detection of output, accuracy of the characterization

Assignment given: 18. January 2007 Supervisor: Trond Sæther, IET

# **Preface**

This thesis is the result from work done as part of a master's degree from Department of Electronics and Telecommunications (IET), The Norwegian University of Science and Technology.

The project title is "Automated Self-Test of an Analog Delta-Sigma Modulator" and was proposed by Are Hellandsvik at Atmel Norway. The objective was to investigate different self-test schemes for a  $\Delta\Sigma$ -modulator and suggest a feasible test for integration on Atmel's AVR <sup>®</sup> 8-bit microcontrollers.

The work was carried out during the spring 2007 at Atmel Norway AS and the Department of Electronics and Telecommunications (IET), The Norwegian University of Science and Technology.

I would like to thank my supervisor Are Hellandsvik at Atmel Norway for his invaluable contribution and continuous guidance throughout the project.

Trondheim 12 June 2007

Trond Jarle Pedersen

\_

<sup>&</sup>lt;sup>®</sup> Atmel and AVR are registered trademarks of Atmel Corporation.

# **Abstract**

This project investigates the feasibility of automating the test of  $\Delta\Sigma$ -modulators using circuit components available on 8-bit microcontrollers, and by doing so reducing test costs.

A Built-In-Self-Test (BIST) scheme, using a binary stream as stimuli and two different solutions for signal analysis is suggested and simulated in SPICE to investigate its suitability.

The test can not lead to a large area increase, increasing area leads to an increase in production cost. The test has to reduce testing time. The extra area occupied by the test architecture has to be paid in shorter testing time and therefore a lower unit price. The test has to remove or lower the requirements of the off-chip tester, and by doing so reducing cost.

The proposed BIST requires a very small area and is capable of calculating offset, gain and Signal to Noise Ratio with a high degree of accuracy. The proposed solution enables on-chip testing without the need for expensive external stimuli and signal analyzers, making testing on wafer possible thus improving production yield.

The proposed test will not reduce test time by itself, however by integrating the test on-chip and allowing this to run in the background while other on-chip modules are tested total test time can be reduced to the time required to shift the stimuli into the chip

.

# **Table of contents**

| 1 | Introduct            | ion                                               | 1  |

|---|----------------------|---------------------------------------------------|----|

| 2 | Backgrou             | ınd Theory                                        | 2  |

|   | 2.1 Anti             | -aliasing Filter                                  | 2  |

|   | 2.2 Sam              | ple and Hold                                      | 3  |

|   |                      | Modulator                                         |    |

|   | 2.3.1                | $\Delta$ Σ-Modulator with Delaying Integrators    | 4  |

|   | 2.3.2                | Quantization Noise and the White Noise Assumption |    |

|   | 2.3.3                | The Oversampling Advantage                        |    |

|   | 2.3.4                | Noise Shaping                                     |    |

|   | 2.4 Deci             | imation Filter                                    |    |

|   | 2.4.1                | Hybrid Decimation Filter                          |    |

| 3 | $\Delta\Sigma$ -Modu | ulator Limitations and Non-Idealities             |    |

|   |                      | k Jitter                                          |    |

|   |                      | grator Noise and Non-Idealities                   |    |

|   | 3.2.1                | Switching Thermal Noise                           |    |

|   | 3.2.2                | Op-amp Thermal Noise                              |    |

|   | 3.2.3                | Flicker Noise                                     |    |

|   | 3.2.4                | Gain and Pole-error                               |    |

|   | 3.2.5                | Slew Rate and Finite Settling Time.               |    |

|   | 3.2.6                | Saturation and Integrator Clipping                |    |

|   | 3.3 Com              | nparator Non-Idealities                           |    |

|   |                      | lback Non-Idealities                              |    |

| 4 |                      | Iodes in Physical Circuits                        |    |

|   |                      | ure Mechanisms in CMOS materials                  |    |

|   | 4.1.1                | Metal Failure modes                               |    |

|   | 4.1.2                | Gate Oxide Failures                               |    |

|   | 4.2 Brid             | ging defects                                      |    |

|   | 4.2.1                | Resistance in Bridges                             |    |

|   | 4.2.2                | Gate Oxide shorts                                 |    |

|   | 4.3 Open             | n Defects                                         | 20 |

|   | -                    | metric Failures                                   |    |

|   | 4.4.1                | Intrinsic Parametric Failures                     |    |

|   | 4.4.2                | Extrinsic Parametric Failures                     | 24 |

|   | 4.5 Capa             | acitor failure mechanisms                         | 25 |

| 5 | -                    | ecifications, Terminology and Testing             |    |

|   |                      | c Specifications and Testing                      |    |

|   | 5.1.1                | Offset and Gain                                   |    |

|   | 5.1.2                | Integrated nonlinearity error                     | 27 |

|   | 5.1.3                | Differential nonlinearity error                   |    |

|   | 5.1.4                | Histogram Testing                                 |    |

|   | 5.1.5                | Coherent Sampling                                 |    |

|   | 5.1.6                | Missing codes                                     |    |

|   | 5.2 Dyna             | amic specifications                               |    |

|   | 5.2.1                | Signal to Noise Ratio                             |    |

|   | 5.2.2                | Signal to Noise and Distortion Ratio.             |    |

|   | 5.2.3                | Sine-Wave Fitting                                 |    |

|   | 5.2.4                | Effective Number Of Bits                          |    |

| 6 | BIST Imr             | plementation Techniques                           |    |

|    | 6.1 Exis  | ting BIST Proposals                                | 34 |

|----|-----------|----------------------------------------------------|----|

|    | 6.1.1     | Integrator Created Ramp Stimulus                   |    |

|    | 6.1.2     | ΔΣ-DAC Created Stimulus                            |    |

|    | 6.1.3     | $\Delta$ Σ-Modulator As a Resonator                | 36 |

|    | 6.1.4     | Periodic Recorded Stimulus                         | 36 |

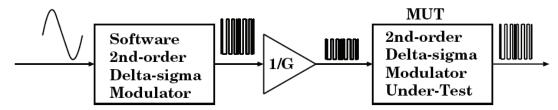

|    | 6.1.5     | Software $\Delta\Sigma$ -Modulator                 | 37 |

|    | 6.1.6     | Recorded Binary Stimulus                           |    |

| 7  | Binary Si | gnals as Stimuli                                   | 39 |

|    | 7.1 Test  | bench and Test Setup                               |    |

|    | 7.1.1     | Signal Generation                                  |    |

|    | 7.1.2     | Test bench                                         |    |

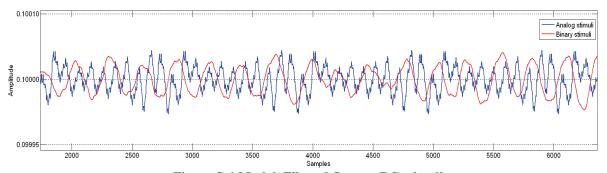

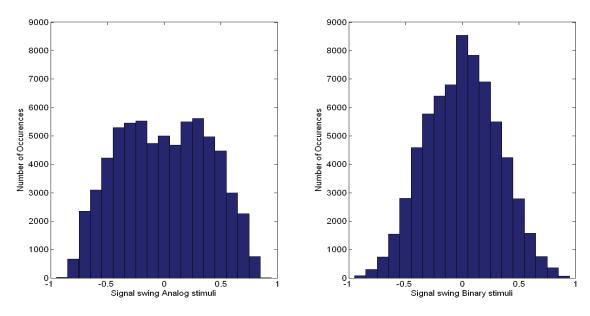

|    | 7.2 Resp  | oonse and Results                                  |    |

|    | 7.2.1     | Detectability in integrator 1                      |    |

|    | 7.2.2     | Detectability in Bias Circuit                      |    |

|    | 7.2.3     | Detectability in the Common Mode Voltage generator |    |

|    | 7.2.4     | Detectability in the Comparator                    |    |

|    |           | ımary                                              |    |

| 8  | BIST Pro  | posal                                              | 54 |

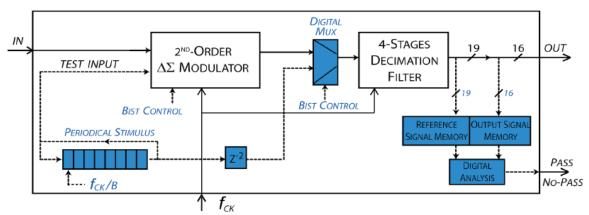

|    |           | Γ Structure                                        | 54 |

|    |           | Γ Signal Generation                                |    |

|    | 8.2.1     | Dynamic Signal Generation                          |    |

|    | 8.2.2     | Static Signal Generation                           |    |

|    | _         | al Quality                                         |    |

|    | _         | al Analysis                                        |    |

|    |           | T Performance                                      |    |

|    | 8.5.1     | Dynamic Testing                                    |    |

|    | 8.5.2     | Static Testing                                     |    |

| 9  |           | on                                                 |    |

|    |           | Γ coverage                                         |    |

|    |           | Γ Arithmetic Requirements                          |    |

|    |           | Γ Implementation Cost                              |    |

|    | 9.3.1     | BIST with External Signal Analysis                 |    |

|    |           | BIST with Internal Signal Analysis                 | 66 |

|    | 9.3.3     | Test time                                          |    |

|    | 9.3.4     | Implementation Summary                             |    |

|    |           | ernal Test Equipment Requirements                  |    |

| 10 |           | ısion                                              |    |

| 11 |           | work                                               |    |

| A  |           | es                                                 |    |

| В  |           | used in testing                                    |    |

|    |           | modulator schematics and VHDL-AMS mapping          |    |

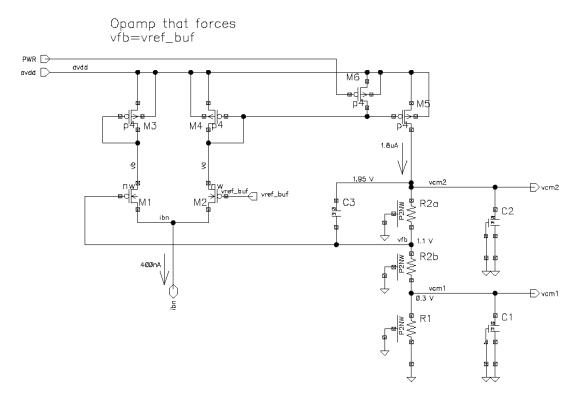

|    | B.1.1     | Op-amp 1                                           |    |

|    | B.1.2     | Integrator 1                                       |    |

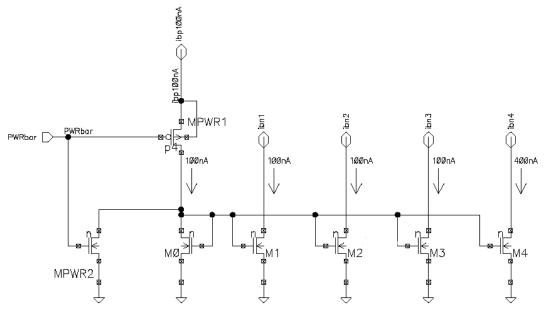

|    | B.1.3     | Bias Circuit                                       |    |

|    | B.1.4     | Common mode voltage generator                      |    |

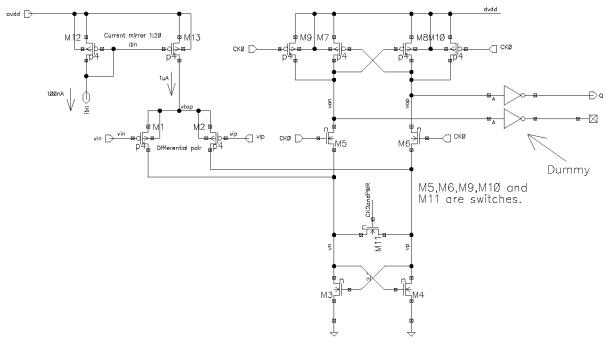

|    | B.1.5     | Comparator                                         |    |

| C  |           |                                                    |    |

|    | C.1.1     | Dynamic Testing                                    |    |

|    | C.1.2     | Static Testing                                     |    |

|    | C.1.3     | Integrator Signal Swing                            |    |

|    |           |                                                    |    |

| D TestBench                                                                                    | D-19   |

|------------------------------------------------------------------------------------------------|--------|

| D.1 Testbench Code                                                                             | D-20   |

| D.2 DAC Code                                                                                   | D-27   |

| D.3 Octave Scripts                                                                             | D-28   |

| D.3.1 Four Parameter Sine Wave Fitting                                                         | D-29   |

| D.3.2 BIST octave code                                                                         |        |

| E Arithmetic Calculations.                                                                     | E-35   |

| F Simulation results Binary signals as stimuli                                                 | F-37   |

| F.1 Simulation results Integrator 1                                                            |        |

| F.1.1 Simulation results Op-amp                                                                |        |

| F.1.2 Simulation results Integrator                                                            |        |

| F.2 Simulation Results Common Mode Voltage Generator                                           |        |

| F.3 Simulation Results Bias Circuit                                                            |        |

| F.4 Simulation Results Comparator                                                              |        |

| G BIST Proposal. Dynamic Simulation results                                                    |        |

| G.1 BIST Simulation results Integrator 1                                                       |        |

| G.1.1 BIST Simulation results Op-amp, Integrator 1                                             |        |

| G.1.2 BIST Simulation results Integrator                                                       |        |

| G.2 BIST Simulation results Common Mode Voltage Generator                                      |        |

| G.3 BIST Simulation results Bias circuit                                                       |        |

| G.4 BIST Simulation results Comparator                                                         |        |

| Figure 2-1 a $\Delta\Sigma$ -ADC prinsipal schematic                                           |        |

| Figure 2-3 Modified modulator structure                                                        |        |

| Figure 2-4 Input vs. output and quantizer error                                                |        |

| Figure 2-5 $\Delta\Sigma$ -modulator model                                                     | 3<br>7 |

| Figure 2-6 $\Delta\Sigma$ -modulator linear model                                              |        |

| Figure 3-1 Single-ended SC integrator.                                                         |        |

| Figure 3-2 Sampled Capacitor                                                                   |        |

| Figure 4-1 Bathtub Failure Rate Curve (Hawkins and Segura, 1999)                               |        |

| Figure 4-2 Void and Hillock due to electromigration (Lienig, 2006)                             |        |

| Figure 4-3 Metal Stress Void (Segura and Hawkins, 2004)                                        |        |

| Figure 4-4 Metal Sliver and Metal Blob (Segura and Hawkins, 2004)                              |        |

| Figure 4-5 pMOS and nMOS cross section                                                         |        |

| Figure 4-6 Electrical Models For Gate Oxide Shorts (Segura and Hawkins, 2004)                  |        |

| Figure 4-7 Resistive Open and missing Vias (Segura and Hawkins, 2004)                          |        |

| Figure 4-8 Mousebites.                                                                         |        |

| Figure 5-1 Offset and Gain errors (Johns and Martin, 1997)                                     |        |

| Figure 5-2 INL error (Johns and Martin, 1997)                                                  |        |

| Figure 5-3 Histogram testing (Hoeschele, 1994)                                                 |        |

| Figure 6-1 Traditional test                                                                    |        |

| Figure 6-2 Static test with ramp generation (Yun-Che and Kuen-Jong, 2000)                      |        |

| Figure 6-3 Static test with triangular signal generation (Wang et al., 2005)                   |        |

| Figure 6-4 $\Delta\Sigma$ -DAC stimulus generator (Wang et al., 2005)                          |        |

| Figure 6-5 $\Delta\Sigma$ -modulator as resonator (Kuen-Jong et al., 2003)                     |        |

| Figure 6-6 Stimulus generated from a periodic stream                                           | 36     |

| Figure 6-7 Stimulus generated by a software $\Delta\Sigma$ -modulator (Chee-Kian et al., 2004) | 37     |

| Figure 6-8 Stimulus generated by recorded binary stream (Rolindez et al., 2006)    | 38   |

|------------------------------------------------------------------------------------|------|

| Figure 7-1 Stimulus Spectrum                                                       |      |

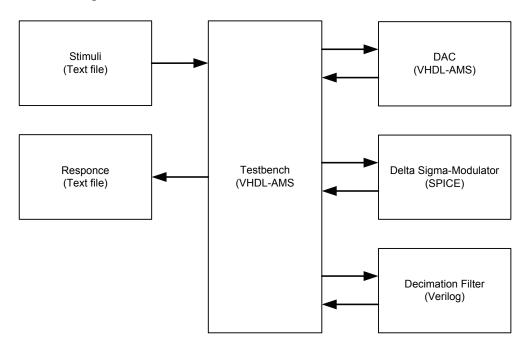

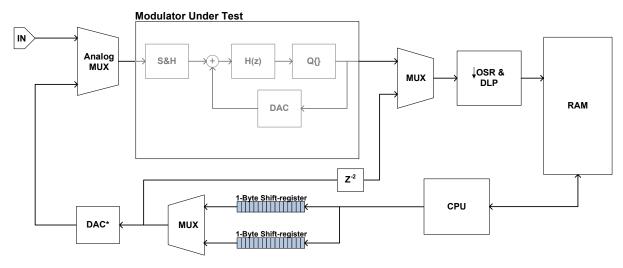

| Figure 7-2 Test Bench, Binary stimulus                                             | 42   |

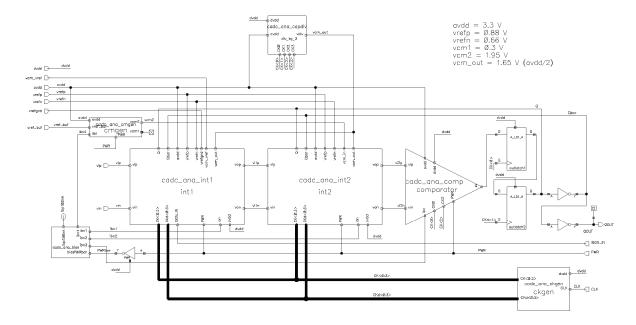

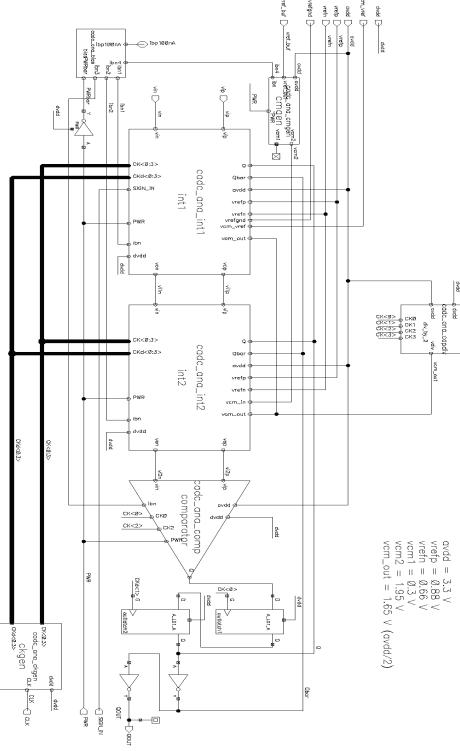

| Figure 7-3 Analog Top Level                                                        | 44   |

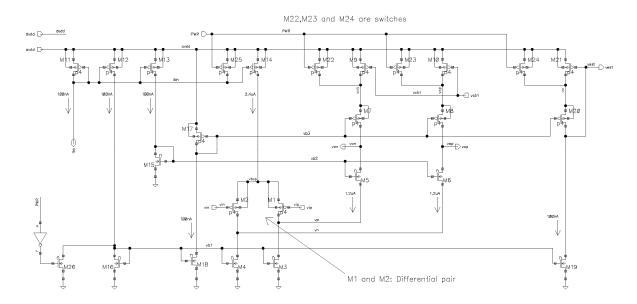

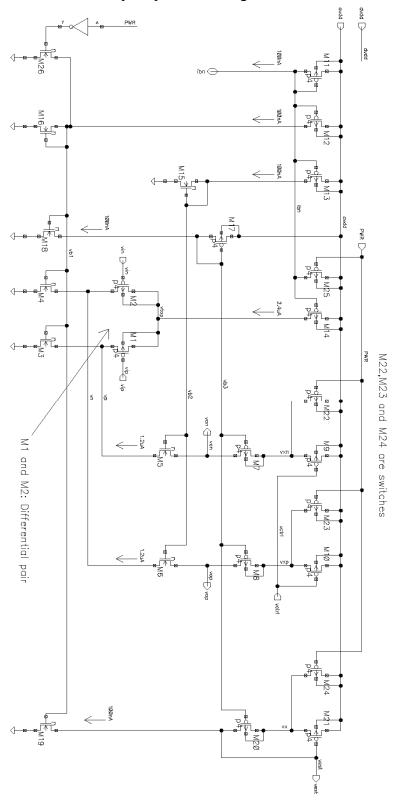

| Figure 7-4 Op-amp schematic                                                        | 45   |

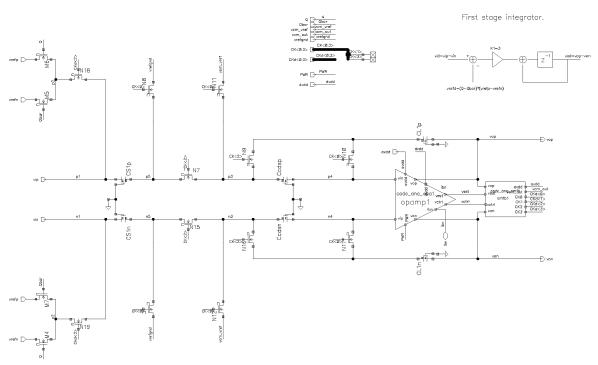

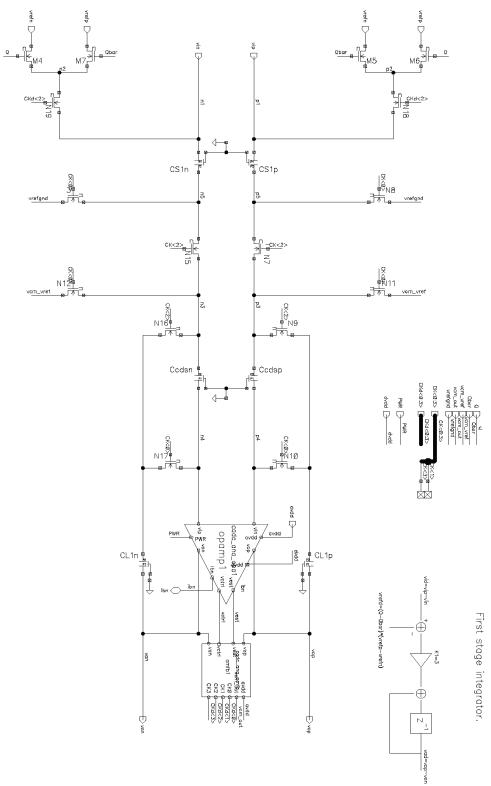

| Figure 7-5 Integrator 1 schematic                                                  | 47   |

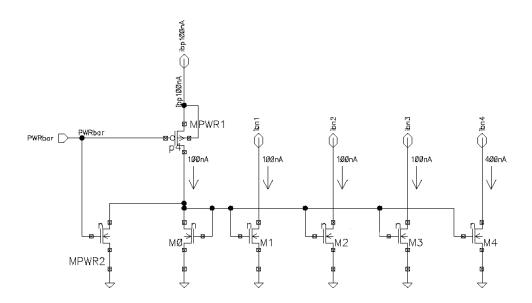

| Figure 7-6 Bias Circuit Schematic                                                  | 49   |

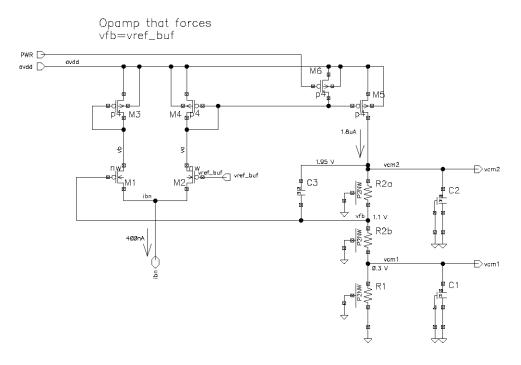

| Figure 7-7 Common voltage schematic                                                | 50   |

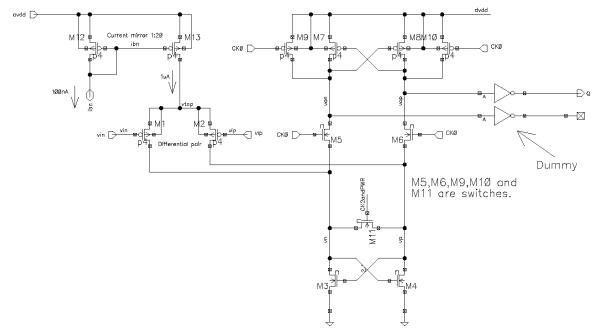

| Figure 7-8 Comparator schematic                                                    | 52   |

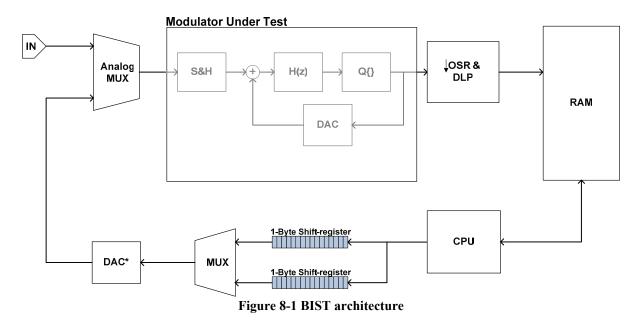

| Figure 8-1 BIST architecture                                                       | 54   |

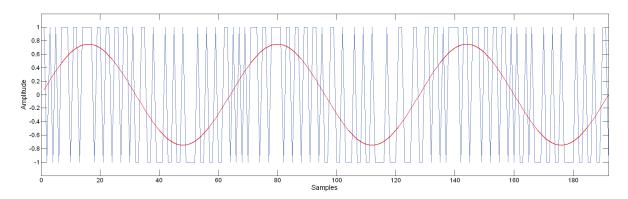

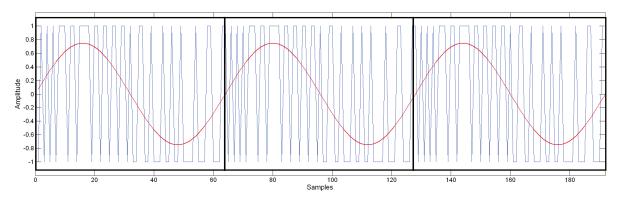

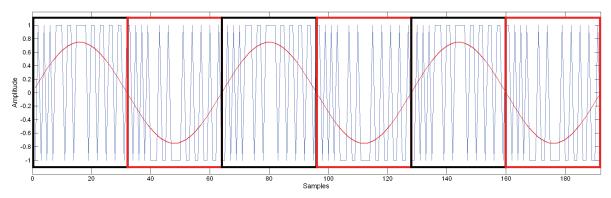

| Figure 8-2 Non-periodic $\Delta\Sigma$ -modulator output                           | 55   |

| Figure 8-3 Periodic $\Delta\Sigma$ -modulator output                               | 56   |

| Figure 8-4 Optimized $\Delta\Sigma$ -modulator output                              | 56   |

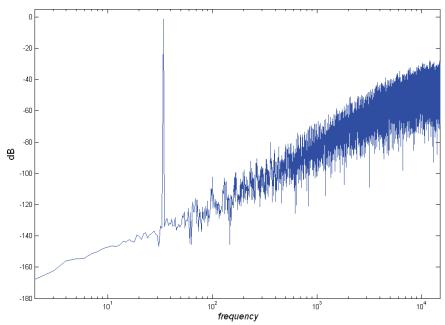

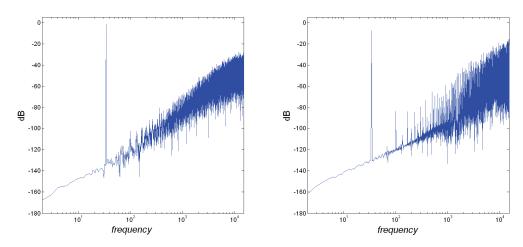

| Figure 8-5 Modulator output spectrum. High-resolution and Periodic binary stimulus | 57   |

| Figure 8-6 Modified BIST architecture                                              | 59   |

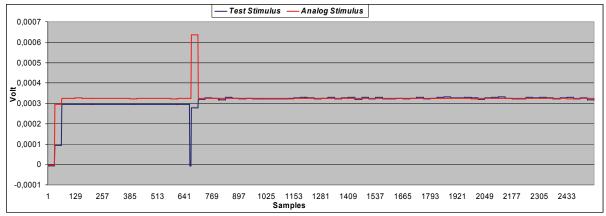

| Figure 8-7 Static vs Test Stimuli                                                  | 63   |

| Figure B-1 Boser-Wooley modulator                                                  | B-3  |

| Figure B-2 Modified modulator structure                                            | B-4  |

| Figure B-3 Analog Top Level                                                        | B-5  |

| Figure B-4 Op-amp 1 schematic                                                      | B-10 |

| Figure B-5 Integrator 1 schematic                                                  | B-11 |

| Figure B-6 Bias schematic                                                          | B-13 |

| Figure B-7 Common voltage schematic                                                | B-14 |

| Figure B-8 Comparator schematic                                                    | B-15 |

| Figure C-1 Matlab Filtered Output, DC-stimuli                                      | C-17 |

| Figure C-2 Integrator swing first integrator                                       | C-18 |

| Figure C-3 Integrator swing second integrator                                      | C-18 |

| Figure D-1 Test Bench, Binary stimulus                                             | D-19 |

# List of symbols and acronyms

| $arDelta \Sigma$ | Delta Sigma                   |

|------------------|-------------------------------|

| $\Delta f$       | Bandwidth                     |

| ADC              | Analog-to-Digital Converter   |

| AMS              | Analog Mixed Signal           |

| BIST             | Build-In-Self-Test            |

| DAC              | Digital-to-Analog Converter   |

| DLP              | Digital Low-Pass filter       |

| DNL              | Differential Non-Linear error |

| DSP              | Digital Signal Processor      |

| DUT              | Device Under Test             |

| e                | Noise/Error                   |

| $e_t$            | Thermal noise voltage         |

| $E_{o\!f\!f}$    | Offset error                  |

| $E_{gain}$       | Gain error                    |

| ENOB             | Effective Number Of Bit       |

| $f_0$            | Signal frequency              |

| $f_{l}$          | Unity gain frequency          |

| $f_s$            | Sampling frequency            |

|                  |                               |

$f_{sn}$  Nyquist frequency

FFT Fast Fourier Transformation

$g_m$  Transconductance INL Integral Non-linearity

G Gain

k Boltzmann's constant

$k_x$  Height of the quantization noise spectral density, see section 2.3.2

L Gate length

LSB Least Significant Bit

LPF Low-Pass Filter

M Sequence length

MUT Modulator Under Test

N Number of digitized bit

OSR Over-Sampling Rate

$P_e$  mean square quantization noise power  $P_s$  mean square quantization signal power

S&H Sample And hold SC Switched-capacitance

SINAD Signal-To-Noise-and-Distortion Ratio

SNR Signal-to-Noise Ratio SR Slew Rate in V/s

T Absolute Temperature in Kelvin

Vdd Supply Voltage W Gate width

## 1 Introduction

Time spent in semiconductor factories on testing manufactured integrated circuits is a large part of the total cost of production. Microcontrollers contains an increasing amount of analog circuitry, that pose a great challenge in design for test, both in terms of time spent on testing and the accuracy of test equipment.

$\Delta\Sigma$ -Modulators are popular in ADCs due to the high accuracy obtainable in low-cost standard CMOS technology.  $\Delta\Sigma$ -ADCs are however difficult to test efficiently due to their requirement for high-resolution test-stimulus. And due to their oversampling implementation they do not have a direct input to output relationship.

One possible solution to reduce test time and thereby reducing cost associated with testing is to embed an automated Built-In Self Test into the microcontroller. To justify the development and implementation of a BIST, increase in area must be very small and the time required to characterize the modulator can not be larger than the time a traditional test setup uses.

# 2 Background Theory

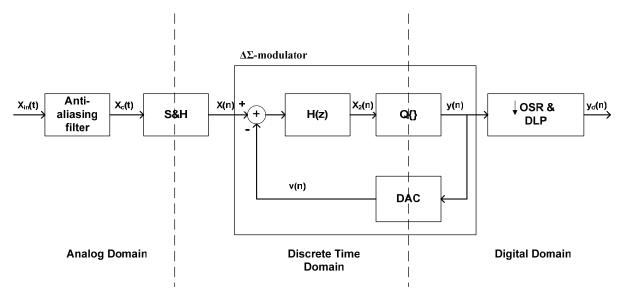

Before going into  $\Delta\Sigma$ -ADC non-linearity's and their impact on performance a brief introduction to the  $\Delta\Sigma$ -ADC is in place. An oversampling ADC works by trading resolution in time with resolution in amplitude, running at a sampling rate much higher than the Nyquist rate they are able to extract extra resolution out of a relatively low resolution ADC. By utilizing negative feedback and thereby shaping the quantization noise-spectrum it is possible to increase the resolution even further. Figure 2-1 shows a principal schematic of a  $\Delta\Sigma$ -ADC.

Figure 2-1 a  $\Delta\Sigma$ -ADC principal schematic

An analog filer is used as an anti-aliasing filter to remove out-of-band components and thereby preventing aliasing of the signal. The input signal is sampled in the sample and hold circuit at a much higher sampling-rate than the Nyquist-rate. The  $\Delta\Sigma$ -modulator acts as a low-pass filter for the input signal, and as a high-pass for the quantization noise provided a proper choice of H(z), this concept is further explained in section 2.3.4. And a quantizer that digitizes the sample, using a 1-bit quantizer is favorable due to its inherent linearity. By utilizing a single bit DAC as feedback source the signal spectrum is shaped and the noise is moved to higher frequencies where a digital low-pass filter can easily remove it at the same time as the signal is down-sampled to the wanted samplerate.(Johns and Martin, 1997)

# 2.1 Anti-aliasing Filter

This is a analog low pass filter that band-limits the input signal prior to sampling thus preventing aliasing the high-frequency components into the base band. Due to the oversampling nature of  $\Delta\Sigma$ -modulators the anti-aliasing filter requirements are not as strict as in a Nyquist rate ADC.

## 2.2 Sample and Hold

The Sample and hold circuit samples the input signal at a much higher rate than the Nyquist rate. The Nyquist rate  $f_{sn}$  is defined as twice the bandwidth of the continuous-time signal. (Proakis and Manolakis, 1996)

$$f_{sn} = 2f_0$$

(2-1)

It should be noted that the Sample and hold circuit is usually implemented in the first integrator of the  $\Delta\Sigma$ -modulator along with the feedback and not as a separate component.

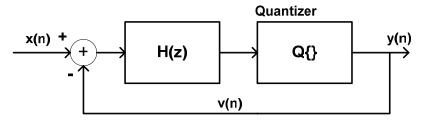

#### 2.3 ΔΣ-Modulator

The  $\Delta\Sigma$ -modulator consists of an filter H(z) and a coarse quantizer QTODO enclosed in a feedback loop. The feedback loop and filter, constitute a low-pass filter when seen from the signal input, but as a high pass filter as seen from the quantizer input, where the quantization noise is injected. Thus the over sampled system will leave the signal band unaltered while the quantization noise is pushed towards higher frequencies. Since the  $\Delta\Sigma$ -modulator samples the signal at a much higher rate than the Nyquist rate these high frequency noise components can be removed without affecting the wanted frequencies. The simplest  $\Delta\Sigma$ -modulators is a first order loop where the filter is realized using a single integrator, however the quantization noise from a first order modulator is highly correlated and the required oversampling rate needed to achieve a resolution over 12 bit is unreasonable large . Throughout this project a second order  $\Delta\Sigma$ -modulator with delaying integrators is used.

## 2.3.1 ΔΣ-Modulator with Delaying Integrators

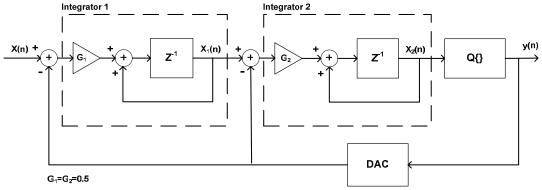

All testing and development in this thesis is performed on a second order  $\Delta\Sigma$ -modulator used to monitor charge and discharge current flowing through an external sense resistor (Atmel, 2005). The modulator is of a modified Boser-Wooley design utilizing delaying integrators. Using delaying integrators is favorable because it allows the op-amps to settle independently, leading to greater signal independency, thus reducing the speed requirements (Boser and Wooley, 1988).

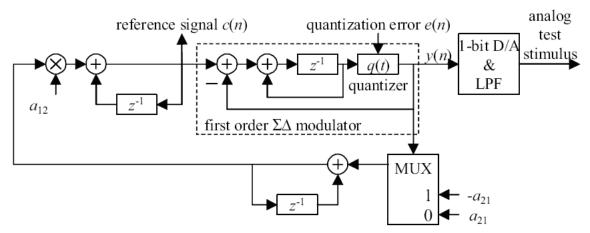

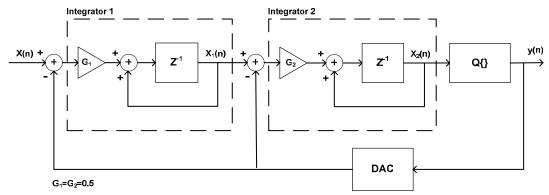

Figure 2-2 Boser-Wooley modulator

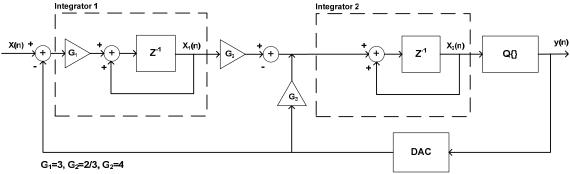

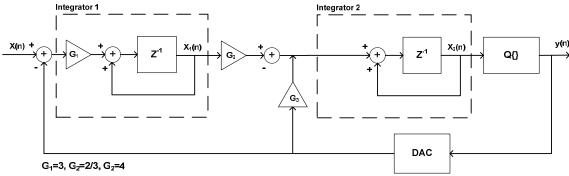

In the original design (Figure 2-2) an integrator attenuation of 0.5 was used, however given the maximum input swing of  $\pm 220$ mV specified such a modulator structure would require large sampling capacitors. (Atmel, 2006) The modulator was therefore redesigned with a larger first integrator gain resulting in the block diagram shown in Figure 2-3

Figure 2-3 Modified modulator structure

The modulator is thoroughly described in appendix B.

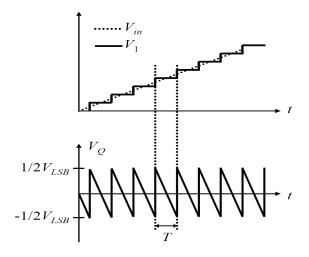

## 2.3.2 Quantization Noise and the White Noise Assumption

To convert a continuous analog signal into a digital one, the signal is sampled and then its amplitude is rounded into a finite value, this quantization is (usually) uniform so that two adjacent quantized values are spaced by a fixed spacing of  $\Delta$ . The size of  $\Delta$  is determined by the number of bits used to represent the signal. The deviation e from these fixed values to the real analog value is a nonlinear process that never will exceed:

$$-\frac{\Delta}{2} \le e \le \frac{\Delta}{2} \tag{2-2}$$

provided that the analog input is within the signal range.

Figure 2-4 Input vs. output and quantizer error

The quantization error e is completely defined by the input. If the input signal is very active, one may assume that e is uncorrelated from sample to sample. Under this assumption the quantization error can be viewed as a white noise source with samples uniformly distributed between  $\pm \Delta/2$ . The mean-square power of the quantization noise will then be given by: (Johns and Martin, 1997)

$$P_e = \int_{-f_s/2}^{f_s/2} S_e^2(f) df = \int_{-f_s/2}^{f_s/2} k_x^2 df = k_x^2 f_s = \frac{\Delta^2}{12}$$

(2-3)

where

$$k_x = \left(\frac{\Delta}{\sqrt{12}}\right) \sqrt{\frac{1}{f_s}}$$

(2-4)

Where  $S_e(f)$  is the spectral density of e(n), and  $k_x$  is the height of  $S_e(f)$

## 2.3.3 The Oversampling Advantage

Oversampling is the process of sampling a signal band-limited to  $f_0$  at a rate of  $f_s > f_{sn}$ , the oversampling rate OSR is defined as:

$$OSR = \frac{f_s}{2f_0} \tag{2-5}$$

When the sampled signal is filtered through a low-pass filter all frequency components higher than  $f_0$  is attenuated. This filtering leads to a reduction of the quantization noise power to:

$$P_{e} = \int_{-f_{s}/2}^{f_{s}/2} S_{e}^{2}(f) |H(f)| df = \int_{-f_{0}}^{f_{0}} k_{x}^{2} df = \frac{2f_{0}}{f_{s}} \frac{\Delta^{2}}{12} = \frac{\Delta^{2}}{12} \left(\frac{1}{OSR}\right)$$

(2-6)

From equation (2-6) one can se that a doubling of OSR decreases the quantization noise power by a factor of one half, or equivalent 3 dB.

If the input signal is a sinusoidal wave where the maximum peak amplitude without clipping is  $2^{N}(\Delta/2)$ , the signal power  $P_{s}$  will be:

$$P_{s} = \left(\frac{\Delta 2^{N}}{2\sqrt{2}}\right)^{2} = \frac{\Delta^{2} 2^{2N}}{8}$$

(2-7)

Where the term N is the quantizers number of bit. The maximum theoretic SNR defined as the ratio between the sinusoidal input signal and the quantization noise (in dB) can be found combining equations (2-6) and (2-7)

$$SNR_{\text{max}} = 10\log\left(\frac{P_s}{P_e}\right) = 10\log\left(\frac{3}{2}2^{2N}\right) + 10\log(OSR)$$

(2-8)

This translates to:

$$SNR_{\text{max}} = 6.02N + 1.76 + 10\log(OSR)$$

(2-9)

Where the term containing *OSR* represents the gain in SNR obtained from oversampling. As expected from equation (2-6) a doubling of the oversampling rate gives a SNR improvement of 3dB/octave (Johns and Martin, 1997).

## 2.3.4 Noise Shaping

By utilizing feedback a noise shaping effect can be obtained. When feedback is introduced into the modulator as seen in Figure 2-5 and the feedback signal v(n) is subtracted from the input signal, quantization noise can be suppressed in the signal band while the signal itself remains largely unaffected. The best way to illustrate this effect is to employ the  $\Delta\Sigma$ -modulators linear model.

Figure 2-5  $\Delta\Sigma$ -modulator model

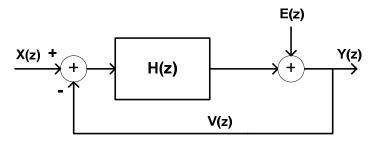

Figure 2-5 shows a  $\Delta\Sigma$ -modulator and by using the white noise assumption from chapter 2.3.2 the model can be transformed to Figure 2-6.

Figure 2-6  $\Delta\Sigma$ -modulator linear model

Treating the linear model as having two independent inputs, the signal transfer function  $S_{TF}(z)$  and a noise transfer function  $N_{TF}(z)$  can be derived.

$$S_{TF}(z) = \frac{Y(z)}{X(z)} = \frac{H(z)}{1 + H(z)}$$

(2-10)

$$N_{TF}(z) = \frac{Y(z)}{E(z)} = \frac{1}{1 + H(z)}$$

(2-11)

By writing the output Y(z) as a combination of the noise and signal inputs where each is filtered by its corresponding transfer function as shown in equation (2-12) and choosing the loop filter H(z) so that it has a high gain in the signal band, the in-band quantization noise can be attenuated while leaving the input signal intact. (Johns and Martin, 1997)

$$Y(z) = S_{TF}(z)X(z) + N_{TF}(z)E(z)$$

(2-12)

Chapter 14.2 in (Johns and Martin, 1997) shows that the theoretic maximum SNR for a second order modulator is

$$SNR_{MAX} = 6.02N + 1.76 - 12.9 + 50 \log(OSR)$$

(2-13)

where N represents the number of bits in the quantizer.

## 2.4 Decimation Filter

The high samplerate one-bit output from the  $\Delta\Sigma$ -modulator is filtered in a low pass digital filter before being down-sampled into a multi-bit low-samplerate output. This filter has to remove all frequency components above the Nyquist rate  $2f_0$ , or the remaining high frequency components can be aliased down into the signal band. This requirement is usually fulfilled if a filter with one higher order than the  $\Delta\Sigma$ -modulator is used (Norsworthy, 1997).

## 2.4.1 Hybrid Decimation Filter

Throughout this thesis a hybrid decimation filter consisting of a third order Sinc filter (Proakis and Manolakis, 1996) is cascaded with a first order Sinc filter. The third order Sinc filter decimates the signal and outputs a 13-bit sample every 128th clock sample. The following first order filter decimates the data with a programmable decimation-ratio of 32, 64, 128 or 256 and outputs an accumulated 18-bit signal. Internal registers are 22-bit long.

## 3 ΔΣ-Modulator Limitations and Non-Idealities

One of the main advantages of  $\Delta\Sigma$ -modulators their high tolerance for analog component mismatch and non-idealities but at the same time they call for increased digital complexity. The oversampling nature allows a low amplitude resolution to be traded for high resolution over time. However all circuits are subjected to non-idealities that affect performance by limiting speed and accuracy, and even though  $\Delta\Sigma$ -modulators have high insensitivity their performance is affected. This section will investigate important non-idealities, how they affect SC  $\Delta\Sigma$ -modulators and how the non-idealities can be detected.

## 3.1 Clock Jitter

When a signal is moved it from the analog to the discrete domain it is sampled at fixed intervals determined by the sampling frequency  $f_s$ , if this interval changes from sample to sample, clock jitter or sampling time uncertainty rises and causes distortion. Once the signal is sampled the system is a discrete time system thus variations in clock period have no direct effect on the circuit performance. Therefore the effect of clock jitter can be completely described by computing its effect on the input signal sampling. This also means that clock jitter degradation on  $\Delta\Sigma$ -modulators is independent of modulator structure and order.

The non-uniform sampling causes an increase in output noise power. The jitter error magnitude is a function of the jitters statistical properties and the modulators input signal. If the input is a sinusoidal signal x(t) with amplitude A and frequency  $f_{in}$  that is sampled with a deviation  $\delta$  from the ideal sampling spacing, (Malcovati et al., 2003) shows that the error introduced will be given by:

$$x(t+\delta)-x(t) \approx 2\pi f_0 \delta A \cos(2\pi f_0 t) = \delta \frac{d}{dt} x(t)$$

(3-1)

By assuming that the sampling time uncertainty  $\delta$  is a Gaussian random process with a standard deviation of  $\Delta \tau$ , the resultant error has uniform power-spectral density from  $\theta$  to  $f_s/2$  with a total power of:

$$e_{\delta}^{2} = \frac{1}{2} (2\pi f_{0} \Delta \tau A)^{2}$$

(3-2)

By using this assumption and equation ( 3-1 ) clock jitter can easily be simulated by taking the derivative of the continuous time-signal, multiplying it with  $\delta$  and adding the result to the acquired sample.

## 3.2 Integrator Noise and Non-Idealities

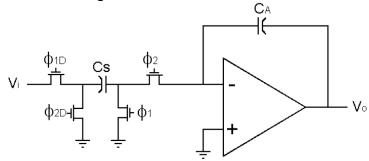

When isolating and analyzing noise sources in SC integrators it is convenient to analyze the single ended version shown in Figure 3-1

Figure 3-1 Single-ended SC integrator

Due to the noise shaping the input integrator is the one that affects overall performance most, since all subsequent noise contributions are divided by the integrator gain when referred back to the input. The easiest way to estimate the effect a particular non-ideality has on the modulator is to refer it back to the modulator input.

The integrators ideal transfer function is

$$H(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{3-3}$$

And the unity gain frequency  $f_l$  will then be:

$$\left| \frac{z^{-1}}{1 - z^{-1}} \right| = \left| \frac{e^{-j2\pi \frac{f_1}{f_s}}}{1 - e^{-j2\pi \frac{f_1}{f_s}}} \right| = 1 \Rightarrow \left| 1 - e^{-j2\pi \frac{f_1}{f_s}} \right| = 1 \Rightarrow f_1 = \frac{f_s}{6}$$

(3-4)

Referring the signal back to its input is the equivalent to dividing it by the transfer function of the integrator. Since  $\Delta\Sigma$ -modulators usually employ a large amount of oversampling causing

$$OSR = \frac{f_s}{2f_0} \Rightarrow f_s = 2f_0 OSR$$

(3-5)

$f_s$  to be large the integrator have considerable gain in the base band, causing noise and distortion due to circuit non-idealities to be greatly attenuated when they are referred back through the integrator. Noise and non-idealities in succeeding integrators will be further attenuated by being referred back through all the integrators. (Norsworthy, 1997)

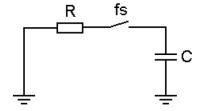

## 3.2.1 Switching Thermal Noise

Thermal noise is caused by thermal excitation of carriers in all conductors. (Johns and Martin, 1997) When the sampling transistors on the integrator input are turned on, their equivalent onresistance acts as a source for thermal noise, a white wideband noise that is proportional to temperature. The effect of thermal noise in SC circuits can be illustrated as shown in Figure 3-2 as a resistor  $R_{on}$  in series with an ideal switch that periodically opens, to sample a noise voltage onto the capacitor C.

Figure 3-2 Sampled Capacitor

To calculate the total noise power, the resistor can be modeled as a noise source in series with a power source equal to  $4kTR\Delta f$  where k is Boltzmann's constant, T absolute temperature and  $\Delta f$  is the signal bandwidth. (Norsworthy, 1997) The total noise power can then be found by evaluating the integral:

$$e_T^2 = \int_0^\infty \frac{4kTR_{on}}{1 + (2\pi f R_{on}C)^2} df = \frac{kT}{C}$$

(3-6)

An interesting property is that although it is the on-resistance that generates the thermal noise, the total noise power is only dependant of the capacitor C.

Assuming that the pole created by the RC time constant is at much higher a frequency than the sampling frequency, the noise power will be aliased down into the frequency band from  $\theta$  to  $f_s/2$  giving a white final spectrum with a spectral density:

$$S_T(f) = \frac{2kT}{f_s C} \tag{3-7}$$

However this is the noise spectral density when the thermal noise is sampled once every clock cycle, while most SC circuits samples twice every clock cycle. The noise spectral density will then be doubled, leading to:

$$S_T(f) = \frac{2kT}{f_s C} \tag{3-8}$$

An important note here is that integrators usually include more than one SC branch, leading to the general expression:

$$S_T(f) = \frac{2kT}{f_s} \sum_{i=1}^{i} \frac{1}{C_i}$$

(3-9)

Where  $C_i$  is the *i'th* input capacitor.

Superimposing the thermal noise voltage  $e_T$  (also called kT/C noise) to the input voltage x(t) the following equation gives a simulation model:

$$y(t) = [x(t) + e_{T}(t)]b$$

$$= \left[x(t) + \sqrt{\frac{kT}{C_{s}}}n(t)\right]b$$

$$= \left[x(t) + \sqrt{\frac{kT}{bC_{A}}}n(t)\right]b$$

(3-10)

Where n(t) is a Gaussian random process with unity standard deviation while  $b=C_s/C_A$  is the integrator coefficient for each SC branch. (Malcovati et al., 2003)

## 3.2.2 Op-amp Thermal Noise

As SC switches, op-amps excitate broadband thermal noise, the total noise power in op-amps depends on the transconductance of the selected op-amp structure. The noise can usually be represented as a source with power spectral density  $2kTR_{eq}$  at the input terminal where

$$R_{eq} = \frac{4}{3} \frac{1}{g_m} \left( 1 + \frac{\alpha}{g_m} \right)$$

(3-11)

represent the equivalent thermal noise resistance. The parameter  $\alpha$  will be dependant on the op-amp structure and the process used in fabrication. (Dias et al., 1992)

#### 3.2.3 Flicker Noise

Flicker noise, also called *1/f* noise, has a spectral density inversely proportional to frequency. The noise arises by variations in channel charge. In MOSFET devices flicker noise can be modeled as a voltage source in series with the gate. The source has a spectral power density given by:

$$S_{1/f}(f) = \frac{K}{WL} \frac{1}{f}$$

(3-12)

Where K is an empirical determined constant, W is gate-width and L is gate-length. Flicker noise can be substantially reduced by raising OSR, increasing gate area, correlated double sampling, chopper stabilization and employing auto zeroing integrators. (Norsworthy, 1997)

#### 3.2.4 Gain and Pole-error

The integrator transfer function H(z) given in section 3.2, and repeated her for convenience,

$$H(Z) = \frac{z^{-1}}{1 - z^{-1}}$$

(3-13)

show an ideal transfer function, Analog circuit implementations will deviate from this due to non-ideal effects. Both pole and gain errors influences the integrators transfer function. The consequence is that only a fraction of the previous output is added to the new input sample. In a single ended integrator such as the one shown in Figure 3-1 the gain and pole-error will lead to the following transfer function:

$$H(Z) = \frac{C_S}{C_A} \frac{(1-\alpha)z^{-1/2}}{1-(1-\beta)z^{-1}}$$

(3-14)

Where  $\alpha$  represents gain error and  $\beta$  represents pole-error. The dc gain of the integrator therefore becomes:

$$H_0 = H(1) = \frac{C_S}{C_A} \frac{1 - \alpha}{\beta}$$

(3-15)

However (Norsworthy, 1997) states that gain and pole error does not have a large effect in single-loop modulators. If integrators have a dc-gain equal to or larger than the OSR increase in base band noise will be less than 0.3 dB.

## 3.2.5 Slew Rate and Finite Settling Time

Speed constraints given by the RC-time constant in the op-amp limits maximum sampling frequency by introducing a finite settling time. The RC-time constant follows a slope that is called slew rate. Settling time can be described as the minimum time required for the output of the op-amp to reach its new value between each sample. Sampling at shorter intervals than the settling time or if the settling time is changed by circuit imperfections harmonics distortion is introduced into the circuit. This noise may be interpreted as a nonlinear gain and can be described by two separate cases.

Case one is when the sought change in output is able to settle in time, in this case the output reaches its target within one finite sample and no noise is introduced.

Case two appears when the change in output is higher than the op-amps slew rate, the integrator is not able to settle fully and the output v(n) will then be given by:

$$v(n) = v(n-1) + (\alpha V_{dd} - SRn) \left(1 - e^{-\frac{n_{\text{max}} - n}{\tau}}\right)$$

(3-16)

Where v(n-1) is the previous output,  $\alpha$  is op-amp gain, SR is slew rate in V/s,  $n_{max}$  is the sample time and  $\tau$  is the time constant.

## 3.2.6 Saturation and Integrator Clipping

Physical SC integrators have an upper and lower boundary that is determined by the output range of the op-amp. When the sought integrator output exceeds the op-amps maximum range the integrator will saturate. This indicates that even if the input rise the output will be fixed at the maximum output. This behavior is called clipping and introduces nonlinear noise into the modulator that degrades its performance. Integrator clipping can be simulated by setting a maximum signal swing.

## 3.3 Comparator Non-Idealities

The comparator or quantizer quantizes the signal in the modulator loop and by so doing it generates the modulator output. This output is also fed to the one-bit DAC where it is converted back to an analog signal to provide feedback. Since the quantizer is placed in the feedback loop after the loop gain blocks and before the output terminal distortion generated by this is noise-shaped and effectively attenuated in the base band.

## 3.4 Feedback Non-Idealities

The feedback loop consists of a DAC that reconvert the digital output back into the analog feedback signal. Due to its placement in the feedback loop it has to have high accuracy and linearity, using a one-bit DAC in the feedback guaranties differential linearity by having only one step. But the output is the product of the digital input and the analog voltage reference and inaccurate unstable or skewed references can cause distortions in the modulators transfer function and by doing so creating integral nonlinearity and harmonic distortions.

# 4 Failure Modes in Physical Circuits

Modern integrated circuits contains several million transistors, miles of metal interconnect lines and several millions vias and contact that all work together to form a high performing entity that contains both digital and analog circuits.

One common used fault classification in analog circuits is to divide the faults into two categories:

- Catastrophic Faults or Hard Faults

- Deviation Faults or Soft Faults.

Hard faults describe defects that cause shorts, open circuits or large deviations from the expected performance. Soft Faults represent parametric deviations from the nominal value that causes the circuit to perform outside its intended performance band.

Time

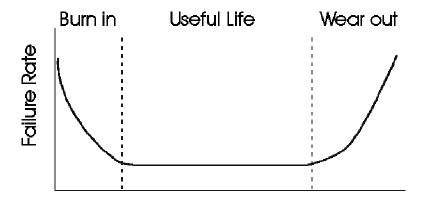

Figure 4-1 Bathtub Failure Rate Curve (Hawkins and Segura, 1999)

Figure 4-1 shows the bathtub curve expressing product failure rate as a function of product life. The early large failure rate is attributed to defective (extrinsic) material and is often referred to as the infant mortality phase. The lower, nearly constant failure rate is the stable useful life of the product that typically declines with time for modern ICs. The stable life period has a finite failure rate due to a low level of residual defects or due to electrical overstress/electrostatic discharge events. The final increase in failure rate occurs in intrinsic material and is due to wear out mechanisms.(Hawkins and Segura, 1999)

This chapter will try to highlight some of the failure mechanisms that exist in integrated circuits. It is deliberately placed at a high abstraction level, and does not deal with the underlying effects in detail.

## 4.1 Failure Mechanisms in CMOS materials

Metal and oxide materials failure modes have always been with us, but they are now more significant in the submicron technologies. This chapter tries to highlight the failure modes and effects that material defects might cause.

#### 4.1.1 Metal Failure modes

Metal structures, such as interconnect lines, pads and vias is essential to modern integrated circuits. Metal must be made without defects and must not fail over time.

#### 4.1.1.1 Electromigration

Electromigration is the movement of metal under the influence of electron flow and temperature. Any metal line will fail if sufficient current density and/or high temperature are applied. Electrons are believed to transfer a small but sufficient momentum to thermally active metal atoms forcing those atoms out of their lattice sites, and moving them in the same direction as the electrons.

To start the electromigration process an imperfection or a defect in the metal structure must exist. Unfortunately, all metals have, to some extent, flaws and defects that can initiate Electromigration. The non-uniform atomic flow rates, caused by these flaws, through different sections of the conductor result in mass depletion, and mass accumulation. (Lienig, 2006) (Segura and Hawkins, 2004)

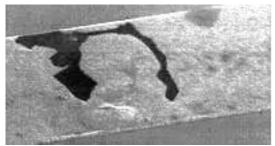

Figure 4-2 Void and Hillock due to electromigration (Lienig, 2006)

The mass depletion leads to resistive bridges and eventually opens in the circuits, while the mass accumulation can lead to shorts.

#### 4.1.1.2 Metal Stress Voiding

The effect when metal lines is pulled apart due to the difference in the thermal coefficient of expansion between the metal line and the pacification materials surrounding it is called stress voiding, (or stress induced voiding), it might cause open faults and/or fertile conditions for electromigration.

Figure 4-3 Metal Stress Void (Segura and Hawkins, 2004)

#### 4.1.2 Gate Oxide Failures

In MOS transistors the gate is separated from the channel by a thin dielectric silicone-dioxide (SiO<sub>2</sub>) layer. Gate oxide failure is the destruction of this dielectric layer. Gate oxide failure is also sometimes referred to as gate oxide rupture or gate oxide breakdown, and often manifests as a short or leakage path from the gate to the channel or substrate.

#### 4.1.2.1 Oxide Wearout

All gate oxides wear out and rupture if a charge is continuously injected. This effect has nothing to do with defects from fabrication. Each time a transistor has a voltage put across its gate oxide, a small amount of charge is injected into the oxide. This charge slowly generates defects within the oxide until a defect path links the gate terminal to the substrate. When this path is established a soft breakdown increases the gate current and noise. Eventually a hard breakdown appears where the gate current exponentially increases. (Hawkins et al., 1999)

### 4.1.2.2 Hot Carrier Injection

When the transistors electric field at the drain-to-channel depletion is too high an electron can gain sufficient kinetic energy to overcome the barrier that the oxide layer poses and degrades this, causing electron and hole traps to form and by so doing increase leakage current, shift in threshold voltage, and change in transconductance. It will eventually cause the transistor to fail.(Segura et al., 2002)

#### 4.1.2.3 Defect-induced Oxide Breakdown

Foreign particles or poor quality oxides can lead to premature breakdown of the oxide for lower voltages than those caused by Hot Carriers. These are called oxide short and are discussed in section 4.2.2

## 4.2 Bridging defects

A bridge or shorting failure is an unintentional connection between to or more circuit nodes. Bridges induce abnormal behavior depending on the resulting circuit topology. Bridging defects usually can be placed in the following categories: (Segura and Hawkins, 2004):

- Ohmic or nonlinear bridge defects

- Intragate-connections across transistors internal nodes.

- Connections across the I/O nodes of logic gates

- Power to ground rail bridges

- Combinational or sequence resulting circuits topology

- Interconnect material types metal, poly and diffusion region

- Critical resistance- transistor drive strength and W/L ratios

Ohmic bridge defects may be metal slivers that connect to interconnection lines, large amount of material shorting more than one interconnect or certain transistor gate oxide shorts as seen in Figure 4-4. (Segura and Hawkins, 2004)

Figure 4-4 Metal Sliver and Metal Blob (Segura and Hawkins, 2004)

## 4.2.1 Resistance in Bridges

If a circuit defect shorts two logic nodes the resulting resistance between these two nodes, called bridging resistance, may or may not cause the surrounding circuit to fail. Based on this, one can define a critical resistance, which is defined as the boundary resistance where the circuit will not functionally fail.

#### 4.2.2 Gate Oxide shorts

Gate oxide Shorts (GOS) describes defects caused by hard oxide breakdown from particles or oxide imperfections.

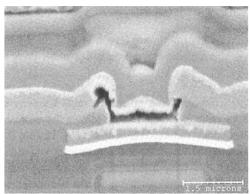

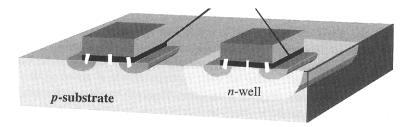

Figure 4-5 pMOS and nMOS cross section

Figure 4-5 show a cross section of pMOS and nMOS transistors in CMOS technology. Gate to drain/source oxide shorts have simple electrical models. There are six places where a gate short can acquire a distinct parasitic connection when the gate material merges with the substrate material. Since gate oxide shorts connect the gate polysilicon with the drain, source or bulk of the device, the electrical properties of the contact depend on the doping type of the terminals being shorted. If the gate and diffusion are of the same doping type, then the electrical model is a resistor between both terminals. If the shorted region has the opposite doping, the electrical model is a *pn* junction diode. (Segura and Hawkins, 2004). This leads to the simulation models shown in Figure 4-6

| <i>n</i> - type polysilicon |    |                                         | <i>p</i> -type polysilicon |    |    |

|-----------------------------|----|-----------------------------------------|----------------------------|----|----|

| GS                          | GB | GD                                      | GS                         | GB | GD |

| <u>F</u>                    |    | _====================================== |                            |    |    |

|                             |    |                                         | <u></u>                    |    |    |

Figure 4-6 Electrical Models For Gate Oxide Shorts (Segura and Hawkins, 2004)

## 4.3 Open Defects

Open circuit defects are unintentional electrical discontinuities. They cause behavior that may vary greatly and be difficult to predict. The defects include open contacts (missing metal or unopened oxide), metallization opens (patterning, improper etching, electromigration, or stress voiding), or opens in diffusion or polysilicon (mask or fabrication errors). (Hawkins et al., 1994)

Figure 4-7 Resistive Open and missing Vias (Segura and Hawkins, 2004)

As transistors decreases in size, behavior modeling of open defects becomes more and more complex. A modern IC contains form millions to several billions transistors, and a total metal length of several kilometers. As deep-submicron CMOS technology comes into use with metal line width of 130  $\mu$ m or less and via height-to-width ratios of more than 5:1 open defects are more or less inevitable. (Ohletz, 1996b)

The main effect of an open IC signal line is that one circuit node is no longer driven by any gate, but might be left in a floating or high impedance state. The floating node does not have a direct path to  $V_{dd}$  or ground and the voltage on the floating node depends on the properties and topology of the surrounding circuitry. The size of the crack or open determines if electrons can tunnel across the open, thereby controlling the amount of charge injected from the original driver toward the floating node, in addition the charge of the floating node depend on the capacitive coupling to the surrounding nodes and the charge at the gate and drain terminals of the connected transistors (Segura and Hawkins, 2004).

## 4.4 Parametric Failures

Parametric failures are failures due to variations in one or a set of circuit parameters so that the circuits' performance falls outside its specifications. Parametric failures have always been present in integrated circuits, but their impact on circuit performance grows spectacularly in deep-submicron technologies. Parametric failures shows in two general forms: one failure form is caused by defect-free (intrinsic) parameter shifts, the second failure form affects functionality through environmentally sensitive defects on the die (extrinsic). This failure class is called parametric as the intrinsic or extrinsic failures are either caused by variation of the IC process parameters, or due to sensitivity to environmental parameters such as power supply, temperature, clock frequency and/or radiation.

Table 4-1 Parametric Failure Sources and Effects (Segura and Hawkins, 2004)

|                        | Failure mechanism                            | Physical Effect                                                    |

|------------------------|----------------------------------------------|--------------------------------------------------------------------|

| Intrinsic              | Process Fabrication                          | Threshold Voltage Shift                                            |

|                        | Parameter Variation                          | ILD variation                                                      |

|                        |                                              | Interconnect Ω shift, metal width, spacing, thickness, granularity |

|                        |                                              | L <sub>eff</sub> shift                                             |

|                        |                                              | W <sub>eff</sub> shift                                             |

|                        |                                              | nMOS-to-pMOS length ratio shift                                    |

|                        |                                              | Diffusion resistance                                               |

| Extrinsic or intrinsic | Metal:                                       | Resistive metal                                                    |

|                        | Via-interconnect defect;<br>Electromigration |                                                                    |

|                        | Stress Void                                  |                                                                    |

|                        | Oxide:                                       | Gate oxide short                                                   |

|                        | Defects or wear out;                         | Hot Carrier injection                                              |

|                        | Hot Carriers                                 |                                                                    |

Table 4-1 lists some of the different forms of intrinsic and extrinsic parametric failure mechanisms and the physical effects that may significantly alter a circuit's performance. Parametric failures are typically insensitive to many test methods such as  $I_{DDQ}$ , stuck-at, delay and logic functional tests. Most parametric failures are speed, current and amplitude related and subsequently not conditions that causes DC parametric failures.

#### 4.4.1 Intrinsic Parametric Failures

Two factors cause intrinsic parameter variation, environmental and physical. Environmental factors include variation of the power supply levels within the die or on the board, or switching activity and temperature variations across the circuit. Physical variation comes from the inherent weakness in circuit manufacturing that allow transistor and interconnect structural variations. These deviations from the targeted values are limitations or imperfections in process and mask steps.

#### 4.4.1.1 Transistor Parameter Variation

Individual transistor parameters vary within a die, die-to-die, and lot-to-lot, making transistor speed and drive strength difficult to predict. The main parameters that determine the transistor drive properties are: (Segura and Hawkins, 2004)

- Channel length variation

- Channel width variation

- nMOS-to-pMOS length ratio variation

- Effective gate oxide thickness variation

- Doping variation- threshold voltage and diffusion resistance

These parameters directly modulate the drive and behavior of the device. Both drain current, threshold voltage and signal amplitude are interrelated and a function of these, and other, parameters.

Channel Length Variation: As seen equation (4-1) for a MOS in active region, channel length lies in the denominator and as  $L_{\rm eff}$  gets smaller, drain current raises, and by so doing alters the characteristics of the device, and the speed characteristics of the circuits. Channel length variations are due to a combination of photolithography, gate etching, ion-implant, spacer formation, and thermal processing effects. It has been showed that  $L_{\rm eff}$  variation has the greatest affect on IC performance compared to other process parameters (Segura and Hawkins, 2004).

$$I_{D} = \frac{\mu_{n} C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{tn})^{2} [1 + \lambda (V_{DS} - V_{EFF})]$$

(4-1)

Channel Width Variations: As with length variations, width variations affect the drain current, but another important effect is the narrow-channel which rises in minimum width devices. The main narrow-channel effect is that the transistor effective threshold voltage varies across the transistor width, changing from the nominal value at the center region to an altered value toward the device edge. The narrow-width effect is typical seen for channel widths less than  $0.4~\mu m$ . (Segura and Hawkins, 2004)

**nMOS** to **pMOS** length ratio variation: this variation is important in ICs that use ratioed logic styles. The width-to-length aspect ratio between *nMOS* and *pMOS* transistor determines the noise margin and the switching point of the logic gates. The channel length variations attributed to the two types of devices may come from implant dose, energy and diffusion tolerances of the dopants associated with the different MOSFET types.

Effective Gate Oxide Thickness Variation: oxide thickness has a first-order impact on device performance, directly affecting transconductance, threshold voltage, and device drive current. Gate oxide physical thickness variance is related to the tolerance of the thermal growing process. In modern processes this variation is kept below 0.5% of the effective oxide thickness. (Hawkins et al., 2003)

Random Doping Fluctuations: Doping variations may differ for devices in the same die and are due to variations in the implant dose, angle and energy. These change the junction dept and doping profiles impacting the effective channel length and threshold voltage. Another performance noise source that impacts the threshold voltage is related to the distributing of dopant atoms. A variation in doping density beneath the gate makes local threshold voltage uneven under the gate.

## Intrinsic variation impact on transistor properties

The parameters listed over cause fluctuations of drain saturation current, threshold voltage or both in devices from the same circuit. The transistor effective length and threshold voltages are the main parameters that determine current drive and therefore the circuits' maximum clock speed.

#### 4.4.2 Extrinsic Parametric Failures

There are five major extrinsic IC mechanisms associated with parametric failures:

- Weak interconnect opens

- Resistive vias and contacts

- Metal mousebites

- Metal slivers

- Gate oxide shorts

Weak opens and resistive vias are major defect-related parametric failure mechanisms. Mousebites occur when sections of metal are missing from an interconnect line. Slivers are common defects in which a metal particle lays between two metal conductors and barely contacts the signal lines. Gate shorts may show timing and power-supply-dependent failures. (Segura et al., 2002)

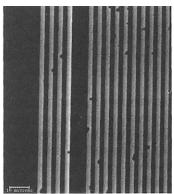

Figure 4-8 Mousebites

**Weak interconnects opens:** In section 4.3 open defects were discussed, weak opens are included here since they cause a relatively small increase in interconnect resistance, and does not prevent current through the line. Depending of the location and the resistance of the defect the impact will vary from none, through decreased speed/amplitude to a hard circuit defect.

**Resistive Vias and Contacts:** connecting the different metal layers, and physical parts of each transistor are contacts and vias. Several fabrication-related mechanisms can cause resistive failures, and although this is a different failure mechanisms that cause resistive failures the way they fail is similar to that of weak interconnect opens.

**Metal Mousebites:** missing regions of interconnect metal are called mousebites. These can be caused by particle defects, electromigration or stress voids. Mousebites have a minor electrical effect, but are a major reliability risk, and may cause electromigration, or local hotspots that cause interconnects to fail.

**Metal Slivers:** a small metal slivers that lie between two interconnect lines, barely or not even touching them, when the temperature rises, the metal expand, and the sliver will now touch the signal lines, causing bridges and circuit failures.

# 4.5 Capacitor failure mechanisms

Capacitors are much like transistors susceptible to faults such as bridges, shorts and opens. The large use of unit size capacitors reduce the effect of capacitance size deviations thus cause the most common fault in on-die capacitors to be oxide breakdown caused by a rupture in the thin oxide layer between the capacitors top and bottom plate. Oxide rupture causes a short and a represents itself as a short between the two input nodes, the fault simulation model will then be a resistor in parallel with the capacitor.

# 5 ADC Specifications, Terminology and Testing

Before studying different test architectures and how they are implemented on-chip it is important to have a clear perception of key specifications, the terminology used and how different tests reveals different non-idealities.

ADC testing can roughly be divided into two separate parts, static and dynamic testing. In static testing the converter under test is subjected to a series of dc voltage levels and the output values are monitored to determine the converters accuracy. One major limitation in static testing is that nonlinearities related to the input signal bandwidth may pass undetected. Dynamic testing is when the converter is stimulated by periodic waveforms instead of dc levels. This type of testing is usually better suited for production testing due to easier signal generation and less time consuming behavior. The signal bandwidth can be higher than in static testing and thereby resembling the actual applications signal. However one disadvantage is that dynamic tests are usually not deterministic in nature, the analog input is not compared to the resulting digital code, instead the converter transfer function is interpreted from the resulting out data. To ensure sufficient resolution under test the signal source needs a resolution at least 3-bit greater than device under test. (IEEE Std 1241, 2001)

The following sections are based on the IEEE standards (IEEE\_Std\_1057, 1994) and (IEEE\_Std\_1241, 2001)

# 5.1 Static Specifications and Testing

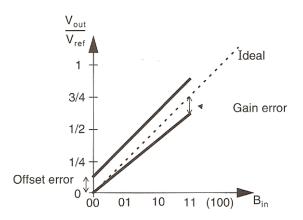

#### 5.1.1 Offset and Gain

Offset and gain are endpoint errors. They characterize the deviation from the ideal transition level for the first and last code.

Figure 5-1 Offset and Gain errors (Johns and Martin, 1997)

Offset error  $E_{off}$  is defined as the deviation from  $V_{0..01}$  from ½ LSB.

$$E_{off} = \frac{V_{0...01}}{V_{LSP}} - \frac{1}{2}LSB$$

(5-1)

Where  $V_{LSB}$  is the ideal width of a code bin, LSB is the step size and N is the number of digitized bits.

An effective method of estimation offset is to start at the lowest input voltage possible and raise the voltage slowly until the transition level has been found.

Gain error  $E_{gain}$  is defined as the deviation from  $V_{1...11}$  corrected for  $E_{off}$ .

$$E_{gain} = \left(\frac{V_{1...11}}{V_{LSR}} - \frac{V_{0...01}}{V_{LSR}}\right) - \left(2^{N} - 2\right)$$

(5-2)

An effective method of finding the transition level is to start at the highest input voltage possible and lower the voltage slowly until the transition level has been found.

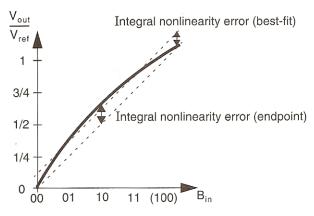

## 5.1.2 Integrated nonlinearity error

Integrated nonlinearity error is the difference between the ideal and the measured code transition levels after both gain and offset errors have been removed.

Figure 5-2 INL error (Johns and Martin, 1997)

INL can be expressed in either a percentage of full scale or in unit of LSB. If INL is given as a single number without code bin specification it specifies the maximum INL over the entire code range. INL can be calculated using:

$$INL(k) = \frac{T(k) - V_{LSB}(k-1) - T_{ideal}}{V_{LSB}2^{N}}$$

(5-3)

Where T(k) is the code transition level for the kth transition,  $V_{LSB}$  is the ideal width of a code bin,  $T_{ideal}$  is the ideal input value corresponding to the code transition level and N is the number of digitized bits.

## 5.1.3 Differential nonlinearity error

Differential Nonlinearity error is the difference between a specified code bin width and the ideal code bin width divided by the ideal code bin width e.g. the variation in analog step sizes away from 1 LSB. When this is given as a single number without code bin specification it is the maximum DNL of the entire range. DNL can be calculated using:

$$DNL(k) = \frac{W(k) - V_{LSB}}{V_{LSB}}$$

(5-4)

Where W(k) is the width of code bin k. Note that neither W(o) nor  $W(2^{N}-1)$  is defined.

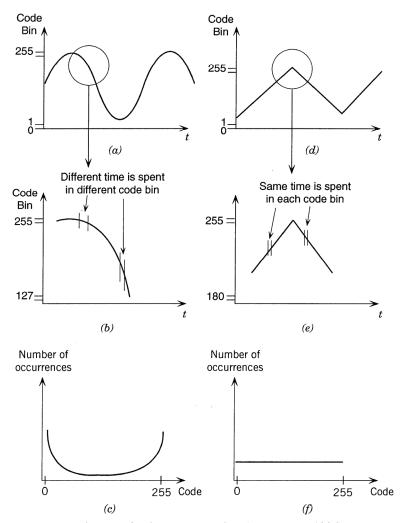

## **5.1.4 Histogram Testing**

Histogram testing is based on the fact that any periodic waveform has a predictable percentage of time in each code bin, after sampling a periodic signal a statistical large number of periods the occurrence of each code can be compared to the amount it should have if the ADC was ideal and the device non-linearity can be calculated.

Figure 5-3 Histogram testing (Hoeschele, 1994)

As shown in Figure 5-3 both sine- and triangular-waveforms can be used in histogram testing although using a sine-wave will cause a predictable skew in the number of occurrences due to the fact that a sine-wave changes value faster when it is at its midpoint than it does when it is close to its extreme values.

Two important consideration when using a histogram test is that an integer number of periods is not used the number of occurrences will be skewed, and the input amplitude has to be exactly controlled. If the input exceeds the converters range the zero and full scale occurrence will be excessively high and if the input range is to low the zero and full scale values will never appear.

## 5.1.5 Coherent Sampling

Coherent sampling is when an integer number of cycles of the test signal are sampled In other words coherent sampling occurs when the following equation is fulfilled:

$$f_s \cdot M_c = f_0 \cdot M \tag{5-5}$$

Where  $M_c$  is the integer number of cycles in the test signal, and M is the number of samples in the output.

### 5.1.6 Missing codes

An ADC is guarantied to have no missing codes if the maximum INL is less than 0.5 LSB or maximum DNL is less than 1 LSB.

# 5.2 Dynamic specifications

### 5.2.1 Signal to Noise Ratio

Signal to noise ratio is the ratio of the signal root-mean-square (*RMS*) value of the fundamental frequency to the *RMS* of all other frequencies excluding harmonics.

$$SNR = \frac{Signal_{RMS}}{Noise_{RMS}}$$

(5-6)

Note that depending of the context and application it is often used in different ways and therefore is ambiguous, as an example (IEEE\_Std\_1057, 1994) uses the same definition of SNR as (IEEE\_Std\_1241, 2001) does for SINAD,

### 5.2.2 Signal to Noise and Distortion Ratio

SINAD is the ratio of the *RMS* value of the signal to the *RMS* value of all other frequencies including harmonics. Section 4.5.1.1 in (IEEE\_Std\_1241, 2001) claims that SINAD test results are affected by almost all error sources, with the exception of dc offset and gain accuracy thus making SINAD testing well suited for production testing. SINAD is defined as:

$$SINAD = \frac{Signal_{RMS}}{Noise_{RMS} + Distortion_{RMS}}$$

(5-7)

A SINAD test can be executed in the time or frequency domain. In the frequency domain SINAD can be determined from conducting a FFT of the digital out signal. In the time domain it is possible to calculate SINAD by performing a sine wave fitting to calculate the noise *RMS* value.

## 5.2.3 Sine-Wave Fitting

Sine-wave fitting or curve fitting is finding a wave form which matches a series of data points, in this case the output from an ADC when a sine wave is introduced at the input. By calculating the phase, amplitude, DC-offset and frequency of the data points and using these it is possible to generate a reference sine-wave that minimizes the squared difference between the calculated sine-wave and that observed in the data points.

$$\Pi = d_1^2 + d_2^2 + \dots + d_n^2 = \sum_{i=1}^m d_i^2 = \sum_{i=1}^m \left[ y_i - f(x_i) \right]^2 = small$$

(5-8)

Equation (5-14) describes the general problem where  $\Pi$  is the square sum of difference (residue),  $d_i$  is the i'th coefficient used to minimize the difference,  $y_i$  is the i'th data point and  $f(x_i)$  is the i'th estimated data point. There is no exact solution to finding the least square difference  $\Pi$ , but algorithms such as the Gauss-Newton algorithm is developed to minimize the least square difference. In the special case where the output is a sine wave this problem can be expressed in the following form:

$$\Pi = \sum_{i=1}^{m} [y_i - A_0 \cos(\omega_0 t_i) - B_0 \sin(\omega_0 t_i) - C_0]^2$$

(5-9)

By calculating the coefficients  $A_0$ ,  $B_0$ ,  $C_0$  and  $\omega_0$  it is possible minimize the least sum of squared difference.

Performing a Sine-wave fit requires the estimation of four parameters (three if frequency is known) which can be found by performing complex matrix operations or large summating algorithms, this is complicated and time consuming to execute in a microcontroller. Chapter 4.1.4 in (IEEE\_Std\_1241, 2001) gives different algorithms for estimating the coefficients and is highly recommended as further studies in this topic.

When best fit coefficients have been found  $C_0$  represents DC-offset and the signal amplitude  $A_{signal}$  and phase  $\theta$  can be found:

$$A_{signal} = \sqrt{A_0^2 + B_0^2} \tag{5-10}$$

$$\theta = \tan^{-1} \left( -\frac{B_0}{A_0} \right) \qquad \text{if } A_0 \ge 0$$

$$\theta = \tan^{-1} \left( -\frac{B_0}{A_0} \right) + \pi \quad \text{if } A_0 < 0$$

(5-11)

The residuals  $r_i$  of the fit will be given by the following equation:

$$r_i = y_i - A_0 \cos(\omega_0 t_i) - B_0 \sin(\omega_0 t_i) - C_0$$

(5-12)

And the *RMS* error will be given by:

$$e_{RMS} = \sqrt{\frac{1}{M} \sum_{i=1}^{M} r_i^2}$$

(5-13)

When the total *RMS* error in the data point has been established it is easy to calculate SINAD:

$$SINAD = \frac{Signal_{RMS}}{Error_{PMS}} = \frac{\frac{A_{signal}}{\sqrt{2}}}{e_{PMS}} = \frac{\sqrt{2} \cdot A_{signal}}{2 \cdot e_{PMS}}$$

(5-14)

#### 5.2.3.1 Test Length, Amplitude and Frequency

When conducting a dynamic SINAD test a large input signal is required to ensure that the ADC is tested over its complete range without overloading the ADC. By choosing the signals amplitude to be at least 90% of the full-scale range this can be achieved.

By choosing an input frequency relatively prime to the sampling frequency the samples are spread in the sine-waves phase over 0 to  $2\pi$ .

In a dynamic test the number of cycles a test has to be performed will vary depending on the amount of noise present in the modulator. However section 4.1.3.5 in (IEEE\_Std\_1057, 1994) states that as a general rule of thumb a test length larger than five cycles has to be used to ensure a sufficient accuracy.

#### 5.2.4 Effective Number Of Bits

Given that the SNR of an ideal ADC without any noise except quantization noise was shown in section 2.3.4 to be:

$$SNR_{MAX} = 6.02N + 1.76$$

(5-15)

Where *N* is number of bit, it is possible to calculate ENOB directly out of this to:

$$ENOB = \frac{SNR - 1.76}{6.02}$$

(5-16)

# 6 BIST Implementation Techniques

Testing high resolution  $\Delta\Sigma$ -modulators is a costly task due to the high resolution and large number of samples required. To successfully test an N-bit ADC the stimuli need a resolution greater than N+2 bit (IEEE\_Std\_1241, 2001). Due to the  $\Delta\Sigma$ -modulators oversampling nature it does not have a direct input to output relationship, making characterization and testing even more challenging.

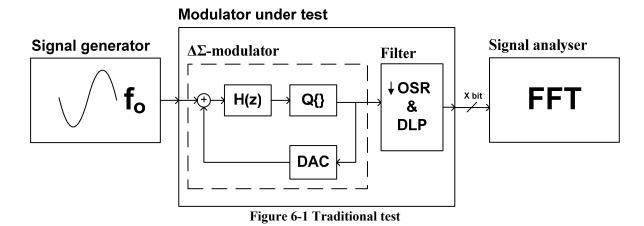

A traditional setup required for testing high resolution  $\Delta\Sigma$ -modulators consist of a high resolution external signal generator that stimulates the modulator under test.

As mentioned in section 5 the stimuli depend on the test performed. If the tester performs static testing, to find offset and linearity errors, input is usually a set of DC values or a saw tooth waveform. To estimate dynamic performance such as SNR or SINAD a sine waveform is used as stimulus. The digital response is loaded from the MUT and into a signal analyzer that evaluates performance.

Using this setup the chip/system is usually prevented from running any other testing in parallel since shifting data into the chip can contribute to noise on the ADC input pin. This leads to long and ineffective test time that could be better utilized.

By implementing an on-chip stimulus the likelihood for digital noise affecting the input signal will be reduced since the analog input pin can be removed. However other challenges then appear. On-chip signal generation is susceptible to supply voltage drift and substrate noise and the signal linearity and resolution can not be guarantied since production can alter or degrade the signal generator.

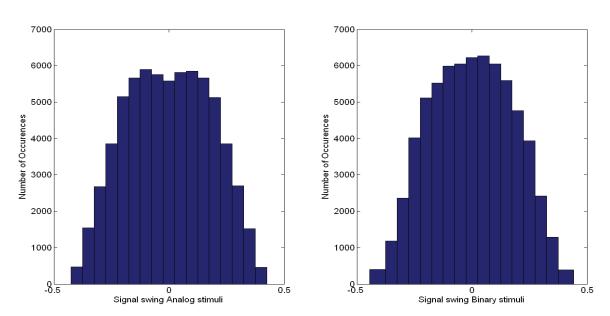

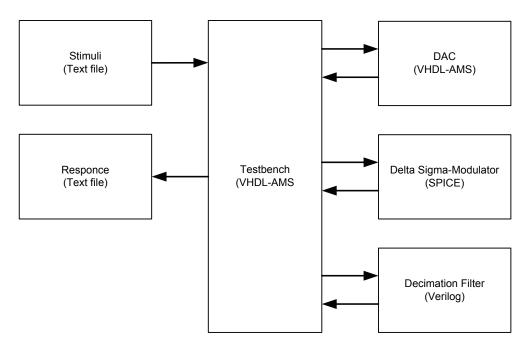

Generating stable high resolution signal generators on-chip is quite possible but usually this signal generation requires large area, and some sort of on-chip calibration to guaranty signal quality, thus leading to even greater area consumption.