# Network on Chip for FPGA

Development of a test system for Network on Chip

Magnus Krokum Namork

Master of Science in Electronics Submission date: June 2011 Supervisor: Kjetil Svarstad, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

This assignment is a continuation of the project-assignment of fall 2010, where it was looked into the development of reactive modules for application-test and profiling of the Network on Chip realization. It will especially be focused on the further development of:

- The programmability of the system by developing functionality for more advanced surveillance of the communication between modules and routers

- Framework that will be used to test and profile entire applications on the Network on Chip

The work will primarily be directed towards testing and running the system in a way that resembles a real system at run time. The work is to be compared with relevant research within similar work.

| Assignment given: | January 2011         |

|-------------------|----------------------|

| Supervisor:       | Kjetil Svarstad, IET |

#### Abstract

Testing and verification of digital systems is an essential part of product development. The Network on Chip (NoC), as a new paradigm within interconnections; has a specific need for testing. This is to determine how performance and properties of the NoC are compared to the requirements of different systems such as processors or media applications.

A NoC has been developed within the AHEAD project to form a basis for a reconfigurable platform used in the AHEAD system. This report gives an outline of the project to develop testing and benchmarking systems for a NoC. The specific work has been regarding the development of a generic module connected to the NoC and capability of testing the NoCs' properties. The test system was initiated by Ivar Ersland in 2009 and developed further by Andreas Hepsø, and Magnus Namork in the fall of 2010. The functionality and systems that are implemented are the following:

- Fully functional Hardware/Software interface which defines communication between NoC and the user

- Reactive system which responds to interaction based on package information

- MPEG example system that mimics an MPEG data stream

- Software reconfiguration of the traffic tables by sending specific packages to the system

- Cell processor example application to test simple computation and communicating modules on the network

The systems have been tested successfully, verified and implemented on a Xilinx Spartan FPGA. It has also been developed a software system written in C to read and interpret data from the Network in on-chip tests. In total these implementations have been the foundation of building a benchmarking platform for the NoC.

# Preface

This assignment is written at the Institute of Electronics and Telecommunications (IET), NTNU in the spring of 2011. It has been done under the guidance of Professor Kjetil Svarstad and as a continuation of the AHEAD Network on Chip project. The assignment was chosen based on its practical and experimental nature, which has also been the main challenge for this project. I wish to thank Kjetil Svarstad for supervision and help during the entire process.

# Contents

| 1        | The | e AHEAD project                                                                                               | 1  |

|----------|-----|---------------------------------------------------------------------------------------------------------------|----|

|          | 1.1 | Reconfigurable systems                                                                                        | 1  |

|          | 1.2 | Concept                                                                                                       | 2  |

|          | 1.3 | Areas of focus                                                                                                | 3  |

|          | 1.4 | Network on $Chip(NoC)$                                                                                        | 4  |

|          |     | 1.4.1 Basic concept $\ldots$ | 4  |

|          |     | 1.4.2 Network on Chip in reconfigurable systems                                                               | 5  |

|          |     | 1.4.3 Testing of digital circuits                                                                             | 5  |

|          |     | 1.4.4 Profiling of applications                                                                               | 6  |

|          | 1.5 | Testing the NoC                                                                                               | 6  |

|          |     | 1.5.1 Experimental working method                                                                             | 7  |

| <b>2</b> | The | eory and research                                                                                             | 9  |

|          | 2.1 | Design for test                                                                                               | 9  |

|          | 2.2 | Benchmarking                                                                                                  | 10 |

|          |     | 2.2.1 System properties                                                                                       | 11 |

|          |     | 2.2.2 Benchmarking protocol                                                                                   | 12 |

|          |     | 2.2.3 NoC benchmarking research                                                                               | 12 |

|          | 2.3 | Deadlocks                                                                                                     | 12 |

|          | 2.4 | Clustering                                                                                                    | 13 |

|          | 2.5 | System platforms                                                                                              | 14 |

| 3        | Pre | vious work                                                                                                    | L7 |

|          | 3.1 | Functionality                                                                                                 | 17 |

|          | 3.2 | Design of the AHEAD Network on Chip                                                                           | 19 |

|          |     | 3.2.1   | Test system                                        | 20 |

|----------|-----|---------|----------------------------------------------------|----|

|          |     | 3.2.2   | Reactive test modules                              | 21 |

|          | 3.3 | Initial | status of the system                               | 21 |

|          |     | 3.3.1   | System properties                                  | 22 |

|          | 3.4 | Test s  | ystem motivation                                   | 22 |

| 4        | Dev | elopm   | ent of the system                                  | 25 |

|          | 4.1 | Struct  | ural development                                   | 25 |

|          |     | 4.1.1   | Generic code development                           | 25 |

|          |     | 4.1.2   | Hardware software interfacing (HW/SW)              | 26 |

|          |     | 4.1.3   | Other structural changes                           | 27 |

|          | 4.2 | Functi  | ional development                                  | 28 |

|          |     | 4.2.1   | Specifications                                     | 28 |

|          | 4.3 | Applic  | cation example:MPEG decoder                        | 30 |

|          |     | 4.3.1   | Real time requirements                             | 31 |

|          | 4.4 | Applic  | cation example: PS3 ring bus system                | 31 |

|          | 4.5 | Other   | possible application examples                      | 33 |

|          |     | 4.5.1   | RSA encryption                                     | 33 |

| <b>5</b> | Req | uirem   | ents and design                                    | 35 |

|          | 5.1 | Desigr  | 1 goals                                            | 35 |

|          |     | 5.1.1   | Area                                               | 35 |

|          |     | 5.1.2   | Flexible Design                                    | 36 |

|          | 5.2 | Hardw   | vare/Software interface                            | 37 |

|          |     | 5.2.1   | Software accessible registers                      | 37 |

|          |     | 5.2.2   | Hardware interfacing                               | 39 |

|          | 5.3 | Traffic | generator                                          | 39 |

|          |     | 5.3.1   | Sending and receiving packages with traffic tables | 40 |

|          | 5.4 | Traffic | e pattern in the NoC                               | 40 |

|          |     | 5.4.1   | Motivation                                         | 40 |

|          |     | 5.4.2   | Sendback pattern                                   | 41 |

|          |     | 5.4.3   | MPEG pattern                                       | 42 |

|          |     | 5.4.4   | Internal Design                                    | 44 |

|   | 5.5  | Multit   | casking test generator; Cell application                                                                                           |

|---|------|----------|------------------------------------------------------------------------------------------------------------------------------------|

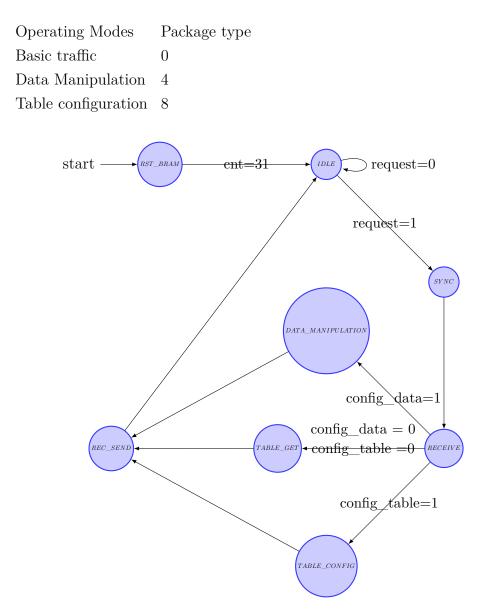

|   |      | 5.5.1    | Operating modes                                                                                                                    |

|   |      | 5.5.2    | Data Manipulation                                                                                                                  |

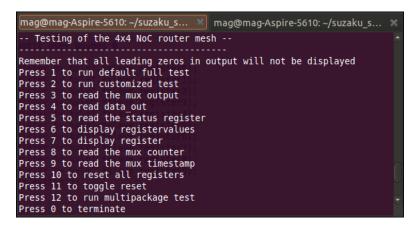

|   | 5.6  | Softwa   | are based test program $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 48$                                  |

|   |      | 5.6.1    | Redefining behaviour through software                                                                                              |

|   | 5.7  | Survei   | llance and monitoring of traffic $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 50$                        |

|   |      | 5.7.1    | Measuring throughput                                                                                                               |

| 6 | Ver  | ificatio | on and testing 53                                                                                                                  |

|   | 6.1  | Simula   | ation $\ldots \ldots 53$                |

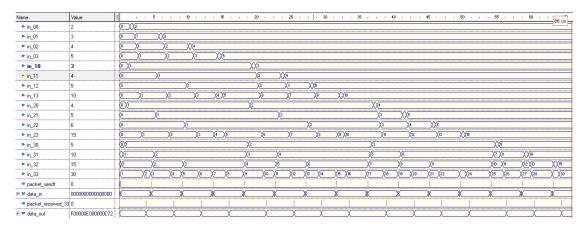

|   |      | 6.1.1    | Simulation of basic functionality                                                                                                  |

|   |      | 6.1.2    | Simple traffic pattern simulation                                                                                                  |

|   |      | 6.1.3    | Patterns with crossing traffic and deadlocks $\ldots \ldots \ldots \ldots 55$                                                      |

|   | 6.2  | Synth    | esis of the circuits $\ldots \ldots 56$                      |

|   |      | 6.2.1    | Synthesis challenges                                                                                                               |

|   |      | 6.2.2    | Synthesis of the circuit                                                                                                           |

|   | 6.3  | FPGA     | $ mplementation \dots \dots$ |

|   |      | 6.3.1    | Initial testing                                                                                                                    |

|   |      | 6.3.2    | Testing patterns, initial MPEG test                                                                                                |

|   |      | 6.3.3    | Higher packet rate                                                                                                                 |

|   | 6.4  | Cell p   | rocessor application $\ldots \ldots 60$               |

|   |      | 6.4.1    | Streaming test of the application                                                                                                  |

|   | 6.5  | Summ     | ary of testing $\ldots \ldots 67$       |

| 7 | Dise | cussior  | n 71                                                                                                                               |

|   | 7.1  | Evalua   | ation of the system $\ldots \ldots 71$                |

|   |      | 7.1.1    | MPEG example                                                                                                                       |

|   |      | 7.1.2    | Cell example                                                                                                                       |

|   |      | 7.1.3    | Interface as bottleneck                                                                                                            |

|   | 7.2  | Throu    | ghput results                                                                                                                      |

|   |      | 7.2.1    | MPEG                                                                                                                               |

|   |      | 7.2.2    | Cell application                                                                                                                   |

|   |      | 7.2.3    | Stream test                                                                                                                        |

|   | $7.3 \\ 7.4$   | Application module placementFurther use of the test system               |     |

|---|----------------|--------------------------------------------------------------------------|-----|

| 8 | Con            | clusion                                                                  | 81  |

| 9 | Furt           | ther work                                                                | 83  |

| Α | Illus          | strations of the systems                                                 | 89  |

| в | $\mathbf{Cod}$ | le                                                                       | 95  |

|   | B.1            | VHDL code                                                                | 95  |

|   | B.2            | C-code                                                                   | 114 |

| С |                |                                                                          | 127 |

|   | C.1            | Equipment list for this project                                          | 128 |

| D | Tute           | orial:How to implement the Network on Chip on the Suzaku-S               |     |

|   | plat           | form 1                                                                   | 129 |

|   | D.1            | Installing Xilinx in debian(Atmark Development environment(Atde3)        |     |

|   |                | or Ubuntu)                                                               | 129 |

|   | D.2            | VHDL code for the Suzaku Image<br>(Peripheral or IP) $\hdots$            | 130 |

|   |                | D.2.1 Using AHDL for development                                         | 130 |

|   |                | D.2.2 Setting up the project in Xilinx EDK                               | 130 |

|   |                | D.2.3 Synthesis                                                          | 132 |

|   |                | D.2.4 Exporting project from EDK to ISE                                  | 132 |

|   |                | D.2.5 Interfacing HW/SW                                                  | 134 |

|   | D.3            | Downloading the generated bit file to the suzaku board $\ . \ . \ . \ .$ | 134 |

|   |                | D.3.1 With serial interface                                              | 134 |

|   |                | D.3.2 With Ethernet                                                      | 135 |

|   | D.4            | Compiling and creating the uCLinux image                                 | 136 |

|   |                | D.4.1 Known errors and solutions                                         | 136 |

|   |                | D.4.2 NFS                                                                | 137 |

|   |                | D.4.3 Setting static IP                                                  | 137 |

|   | D.5            | Sources of error                                                         | 138 |

|   | D.6            | File list NoC                                                            | 138 |

# List of Abbreviations

| AHEAD | Ambient Hardware, Embedded Architectures on Demand, page 2 |

|-------|------------------------------------------------------------|

| ASIC  | Application Specific Integrated Circuit, page 1            |

| CLB   | Configurable Logic Block, page 14                          |

| EIB   | Element Interconnect Bus, page 31                          |

| FPGA  | Field Programmable Gate Array, page 1                      |

| FSM   | Finite State Machine, page 39                              |

| GPP   | General Purpose Processor, page 1                          |

| HW    | Hardware, page 1                                           |

| LUT   | Look up table, page 14                                     |

| MIC   | Memory Interface Controller, page 31                       |

| MISD  | Multiple Input Single Destination, page 48                 |

| NFS   | Network File System, page 27                               |

| NoC   | Network on Chip, page 4                                    |

| PE    | Processing Element, page 48                                |

| PPE   | Power Processing Element, page 31                          |

| SPE   | Synergistic Processing Element, page 31                    |

| SW    | Software, page 1                                           |

| TG    | Test Generator, page 19                                    |

| USB   | Universal Serial Bus, page 3                               |

## Router table

The routers are an essential part of the Network on Chip, but their names vary due to previous version implementation and practical use of signal names. Provided is a table of the equivalent names of the routers used in this assignment both in the text and the code:

| Router | Decimal | Binary | Hexadecimal |

|--------|---------|--------|-------------|

| 00     | 0       | 0000   | 0           |

| 01     | 1       | 0001   | 1           |

| 02     | 2       | 0010   | 2           |

| 03     | 3       | 0011   | 3           |

| 10     | 4       | 0100   | 4           |

| 11     | 5       | 0101   | 5           |

| 12     | 6       | 0110   | 6           |

| 13     | 7       | 0111   | 7           |

| 20     | 8       | 1000   | 8           |

| 21     | 9       | 1001   | 9           |

| 22     | 10      | 1010   | А           |

| 23     | 11      | 1011   | В           |

| 30     | 12      | 1100   | С           |

| 31     | 13      | 1101   | D           |

| 32     | 14      | 1110   | Е           |

| 33     | 15      | 1111   | F           |

# List of Figures

| 1.1 | AHEAD illustration                                                      | 2  |

|-----|-------------------------------------------------------------------------|----|

| 1.2 | AHEAD concept                                                           | 3  |

| 1.3 | Network on Chip                                                         | 4  |

| 1.4 | Design and working methodology                                          | 8  |

| 2.1 | Deadlock situation                                                      | 13 |

| 2.2 | Suzaku boards                                                           | 15 |

| 3.1 | Network on Chip structure                                               | 18 |

| 3.2 | Illustration of handshaking.                                            | 20 |

| 4.1 | HW/SW interface vector handling                                         | 28 |

| 4.2 | MPEG traffic pattern                                                    | 30 |

| 4.3 | Cell processor                                                          | 32 |

| 4.4 | Cell processor in NoC                                                   | 32 |

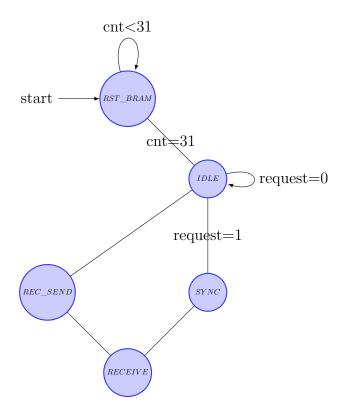

| 5.1 | Input state machine of the Traffic generator, MPEG configuration        | 43 |

| 5.2 | Input state machine of the Traffic generator, Cell example application. | 45 |

| 5.3 | Table reconfiguring through packages                                    | 47 |

| 5.4 | ALternatives FPGA test                                                  | 49 |

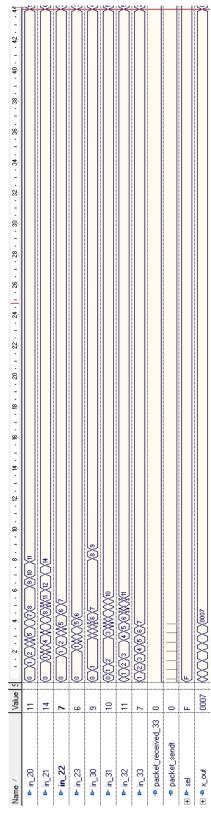

| 6.1 | Basic simulation                                                        | 54 |

| 6.2 | MPEG simulation                                                         | 55 |

| 6.3 | Structural test of the FPGA                                             | 59 |

| 6.4 | Structural test FPGA                                                    | 59 |

| 6.5 | Simple MPEG FPGA                                                        | 60 |

| 6.6 | MPEG 100 packages simulation                                            | 61 |

| 6.7  | Software program test MPEG pattern           |

|------|----------------------------------------------|

| 6.8  | Traffic Cell example, FPGA test              |

| 6.9  | Simulation table reconfiguration             |

| 6.10 | Simulation average, one package              |

| 6.11 | Calculation average FPGA Cell                |

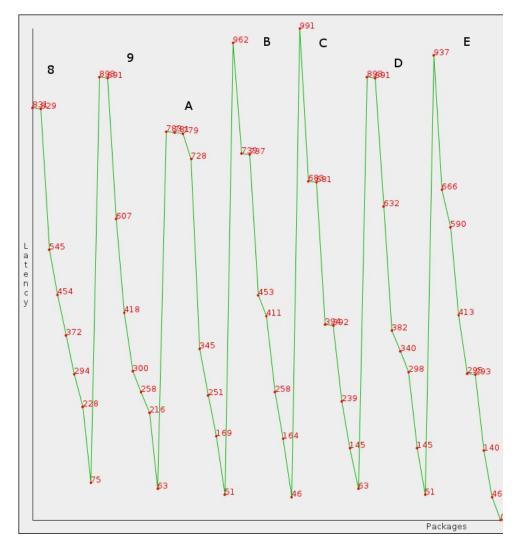

| 6.12 | Graph of latency 64                          |

| 6.13 | Graph of latency, second table configuration |

| 6.14 | Stream tests                                 |

| 7.1  | Two interface modules                        |

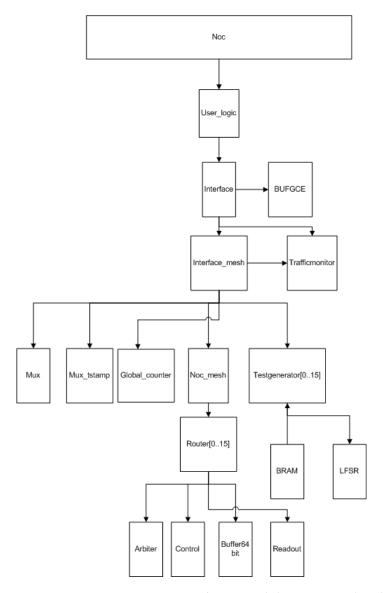

| A.1  | Modules presented in hierarchy               |

| A.2  | Test generator block                         |

| Δ3   |                                              |

| 11.0 | Floorplan NoC                                |

|      | Floorplan NoC92Floorplan NoC description93   |

| A.4  |                                              |

# List of Tables

| 2.1 | FPGA data 1                        | 4  |

|-----|------------------------------------|----|

| 4.1 | Properties Cell                    | 1  |

| 5.1 | Address listing                    | 8  |

| 5.2 | Register numbers and functionality | 8  |

| 5.3 | Traffic table                      | :1 |

| 5.4 | MPEG protocol                      | 2  |

| 5.5 | Multi functional protocol          | 6  |

| 5.6 | change_data                        | :7 |

| 5.7 | Average value input                | 8  |

| 5.8 | Cell application example table     | 9  |

| 6.1 | Synthesis MPEG system              | 7  |

| 6.2 | Synthesis TG Cell-example          | 8  |

| 6.3 | Test load                          | 6  |

| 6.4 | Cell application example table     | 6  |

# Chapter 1

## The AHEAD project

This chapter is an introduction to the AHEAD project and gives a description of some important terms associated with it. It also describes how this report is structured and how the work has been performed.

### 1.1 Reconfigurable systems

Development of electronic systems is in constant change and new and improved systems and algorithms are developed at a high rate. There are several ways of implementing these types of systems; one is the Application Specific Integrated Circuit (ASIC). ASICs are hard wired circuits that performs a given task, but with no or limited possibility to perform a different task after production. The second one is the general purpose processor (GPP) which performs software (SW) tasks by dividing it into predefined operations which are run on the processor. The first instance gives high speed and one efficient solution, the latter gives flexibility and the ability to do various different tasks.

Reconfigurable systems falls into the category that is between the two mentioned platforms. In these systems hardware descriptions are loaded into a platform i.e. an FPGA and the tasks are solved in hardware (HW). However; in contrast to the ASIC, Field Programmable Gate Array (FPGA) systems are completely reconfigurable,hence, it achieves flexibility not provided by any ASIC. In addition, it provides more speed to a system than what is the case with the processor. The FPGA is the foundation of the AHEAD project and adds the possibility of having extra computational power in order to serve any requirements of the system user.

### 1.2 Concept

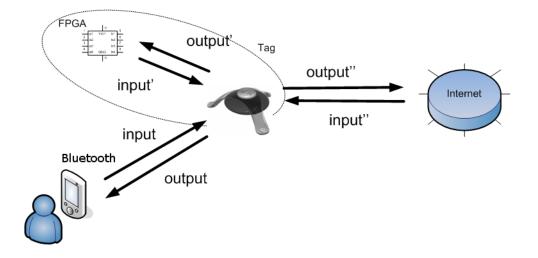

Ambient Hardware, Embedded Architectures on Demand (AHEAD) [9] is a project which was started in 2006 by Professor Kjetil Svarstad at NTNU, Department of Electronics and Telecommunications. It is based on Ambient Intelligence which is a concept describing an environment of devices which is sensitive to people. The idea is based on portable modules, i.e. PDAs or cell phones, and tags with extra computational power located within the environment of the modules [31]. This could, for instance, be an airport or a bus stop where a tag is located, as illustrated in Figure 1.1AHEAD illustrationfigure.caption.9, that detects and interacts with the portable device carried by the user when entering the environment of the tag.

Figure 1.1: General outline of the AHEAD concept; Tag and user with PDA [31].

This way of operation is intended to provide extra computational power for small mobile devices with limited standalone processing capabilities. It is achieved by having HW architecture descriptions located on the portable device. A wireless protocol like Bluetooth is used for communication between the portable device and

Figure 1.2: General outline of the AHEAD concept; Connection between user and tag, and tag and internet.

the tag on the wall. Then the portable device instantiates the architecture specific for the task on a reconfigurable co-processor, for instance an FPGA, within the tag as illustrated in Figure 1.2AHEAD conceptfigure.caption.10. The task is then run on the FPGA instead of the small processor of the user's mobile device.

## **1.3** Areas of focus

The AHEAD project has several different areas of focus. Initially external communication was investigated with assignments on USB, Bluetooth and serial communication. For the past two years there has been a focus on the Network on Chip and the self-reconfiguration and run time reconfiguration of the system. The Network on Chip provides a framework and platform for the reconfiguration and simplifies this operation while the reconfiguration provides an adaptive approach for the AHEAD system.

## 1.4 Network on Chip(NoC)

Interconnections in System on  $\text{Chip}(\text{SoC})^1$  systems have traditionally been bus based or point to point communication architectures. Some examples includes, cross bar buses and ring buses [28].However, a new paradigm within this topic is emerging and this is called Network on Chip [24]. NoC has as its goal to be a a scalable interconnection between modules, and separate the communication from computation in SoCs.

Figure 1.3: Network on Chip illustration [23]. Shows a system with IP cores, interface modules and processor connected with an NoC and its routers.

#### 1.4.1 Basic concept

Different definitions have been used to describe Networks on Chip. Predominantly, it is an interconnection system to handle communication between elements on a chip, with the usage of routers organized in i.e. a mesh topology. Its has a large resemblance to regular telecommunications systems. The concept is simply to use switching techniques to send digital packages between routers and connect modules to these routers [15]. This improves the scalability of the system and the possibility to use the system in reconfiguration because it is possible to change subparts of the system without having to change the entire system and its interconnection. This is especially interesting when partial reconfiguration is a highly demanded property.

<sup>&</sup>lt;sup>1</sup>All parts of a system integrated on one chip

#### 1.4.2 Network on Chip in reconfigurable systems

As mentioned, the self reconfigurable part of the AHEAD project and the Network on Chip might work together in the future. There has already been some research in the area regarding Network on Chip systems. For instance, Bobda et al. in [11], describes a system where modules are placed and connected to an NoC in different sized areas on an FPGA. Since the routers of the NoC already defines the communication between the modules it only has to adapt to the protocol used in the network to start operating. Hence, no new interconnection between the existing modules and the new module has to be added. This also provides a good platform for partial reconfiguration. If one has a method to locate a specific module connected to the network, and then in turn change only that module, the rest of the system can remain untouched. This is desirable for instance when optimizing a SoC or the new requirement of the SoC is only partially different from the previously implemented one.

#### **1.4.3** Testing of digital circuits

In production of modern electronic systems, testing is a vital part of the development process. The formal definition of testing i

A test is feasible if a known set of input vectors can be applied to a circuit in a known state resulting in a response that may be compared to an expected known response

Knowing that all the modules are in place and function as intended is critical when completing a design process. This is to verify that the system will exhibit desired behaviour. Several test-methodologies exists in order to obtain this goal.

For ASICs the verification of signals and registers by using physical tests and fault models are applied. To a post fabrication FPGA test, functional tests and structural tests are more relevant. The formal definition of functional test is;

Testing that the circuit is functioning correctly using functional vectors

and the definition of structural test is;

Testing that all the components and connections are present using special test vectors. [8]

These two test models give the relevant information when designing FPGA systems, namely is the system complete and will the output be as expected.

#### **1.4.4** Profiling of applications

A connected part to the testing of a system is the profiling of applications. If one wants to use a platform in a practical setting it is important to know what applications that are possible to implement on it. The ability to run a simple test that provides the information about how a more complex system will behave is then beneficial. Hence, profiling is merely concentrated around the possible placement of the application in for instance an NoC. This profiling could be done by mimicking its communication and use of the same resources within the system.

#### 1.5 Testing the NoC

For this project it has been a primary goal to develop a system that can be used to mimic, test and profile an NoC implemented system. It has been a main focus to develop examples that mimics a streaming application and a small processor. In addition the environment around with communication with the NoC and surveillance of package data has been emphasized. These elements assembled forms a platform for a benchmark that is capable of measuring the performance of the network. The system also provides information about efficient placement of an implemented system on the NoC.

The assignment is connected to the NoC system developed for the AHEAD project by several participants since 2006. In this paper there will first be a brief description of some background and theory behind NoC testing and benchmarking in Chapter 2Theory and researchchapter.2. In Chapter 3Previous workchapter.3 a brief description and outline of the system status before commencing is presented. Then it moves over to how the system development is performed in Chapter 4Development of the systemchapter.4. Further it describes how this is implemented

7

in general. And then what requirements are connected to the developed system in Chapter 5Requirements and designchapter.5. In Chapter 6Verification and testingchapter.6 the verification of the system is described along with details on simulation, synthesis and on-chip test-results. Finally the system and its results from testing are discussed, and important results are evaluated in Chapter 7Discussionchapter.7, before these discussions are concluded with in Chapter 8Conclusionchapter.8.

#### 1.5.1 Experimental working method

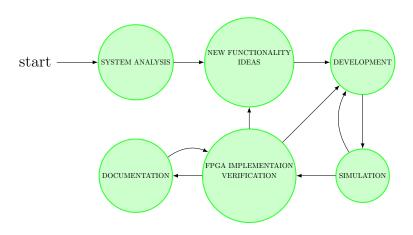

When developing an implementation of a system without any algorithms or specification, it is necessary with an experimental approach to complete the work. In this assignment, development has been conducted by brainstorming, experimentation followed by testing to verify how new elements have applied to the existing system. The system not has been out of the box to use, hence, adding new functionality has been followed both by extensive pre implementation simulation and testing. Both to develop new functionality, but also to understand how the system works. Adapting the contribution one step at a time in the implementation stage has been a critical factor.

The challenges and solutions have been separated into different parts: Analyzation of the system and its functionality. Under the analysis, detecting problem areas and the possibility of implementing new ideas and removing redundant functionality correct. Based on this analysis, new functionality and ideas for the system has been planned. Then testing and verification in simulation, and on chip, followed by documentation of the results has been performed. When one iteration has been run, the next iteration begins based on the previous one. In this way the previous iteration forms the platform for the next one and so forth. This methodology is depicted in Figure 1.4Design and working methodology.figure.caption.12

Figure 1.4: Design and working methodology.

## Chapter 2

# Theory and research

The Network on chip (NoC) is a rather new paradigm within the world of electronic systems. Hence little practical test-cases are commonly known, and those known to exist are mainly academic. The research done by manufacturing companies are to some extent confidential and thus not publicly available. In this chapter there will be a presentation of the theory used to compare the effect of the testing in our network on chip. Some important terms and their use for the AHEAD NoC are also included.

### 2.1 Design for test

The main theme of this project has initially been to create a design eligible for on-chip testing. Design For Test (DFT) is one well known method to complete this task. The basis is to create a test written in for instance VHDL or C and apply it to see if the system responds as expected. In the project mentioned this forms the basis for the structural testing of the system. It is applied to verify that the circuit is correctly assembled by controlling that it gives output, when applied a known input. The other form of testing is the functional testing which aims towards verification of the functionality of the implemented system. An example of a DFT applied to a NoC is described in depth in [32].

### 2.2 Benchmarking

The ability to measure the performance of a system is essential. Benchmarking of general purpose processors has been a well-known area for many years, and has also been introduced as a way of measuring the performance of NoCs. Benchmarks are models or programs of known input that resembles or simulates a real application behaviour and measures its performance [14]. The problem with NoC architectures is that they are not, compared to general purpose processors, fixed architectures. This implies that in order to test the network it is necessary not only to specify the program code to run on the platform, but also the platform itself in order to test the network. The benchmarking of NoCs is in that way a more complex operation than benchmarking a general purpose processor. There exists a research group which has this as its main focus. The NoC Benchmarking Work group with Grecu et al. has described the benchmarking of NoCs and some proposed parameters of this process. They lists some properties a NoC benchmark should test in an attempt to reach an open standard for Network on chip benchmarks [14, p.6].

- Network size (small, medium, large)

- IP core composition (amount of processing, memory cores, other)

- Topology(regular, irregular)

- Traffic characteristics(spatial and temporal)

- QoS requirements(best effort,guaranteed bandwidth,guaranteed latency)

These are properties that directly relates to the AHEAD NoC project. However, the main focus of the testing is related to the traffic characterization and Quality of Service requirements, as initiated by Ersland in [18]. Under this area, the latency of packages and actual throughput in testing are main areas since they in many cases are the most interesting metrics [14, p.5]. When only one or few of these properties are tested, the benchmark is called a micro-benchmark [14, p.2].

#### 2.2.1 System properties

There are some metrics that will be of particular importance, to get an impression of the performance. Following is a description and definition of some of the most important for the benchmarking of the AHEAD NoC.

**Latency** Latency is defined as the delay time from one point to another within a computer system. The end-to-end latency is the time it takes for a package to enter the NoC until an output arrives. In a typical microprocessing system like i.e. Cell [10, p.9], latency is defined as:

Latency = sending overhead+time of flight+transmission time+receiver overhead(2.1)

The latency could be given in either seconds or to measure it in number of clock cycles. The Cell microprocessor will be described in further detail in Chapter 4De-velopment of the systemchapter.4

**Throughput** Throughput is a metric used to define the amount of data passing through a communication channel such as a bus. The throughput is given in bits per second (bps). The definition of the throughput in [10] defines the throughput as the amount of information being transferred over a time interval. When relating this to a package based system, the throughput would be practical to define as the amount of packages being successfully transferred. This is the definition that will be used in this assignment. Throughput is highly frequency dependent as it is measured over a given timespan.

**Bandwidth** The bandwidth of a system is given as the amount of data transmitted over a given time through a system. It is very similar to the term throughput, but refers often to the maximum information-carrying capacity of a line or a network [21]. The bandwidth is also denoted by bits per second. The relation between the throughput and bandwidth is that bandwidth is the maximum and throughput is the actual speed of the transferred data [26]. In this aspect the bandwidth is generally the theoretically achievable bit per second transfer rate, while throughput is what is actually being transmitted. Bandwidth is, similar to the throughput, highly dependent of the frequency.

#### 2.2.2 Benchmarking protocol

Any benchmark or test system applied to the NoC must have a defined communication protocol. The word protocol means "codes of correct conduct" and this is what it is for the modules connected in the system. Each module has to comply with the protocol to perform its task of communicating with the other parts of the system. An example of a suitable protocol for NoCs is the Open Core Protocol [14, p.10]. This is an open source core-centric protocol applicable to the NoC and defines a set of functionality in point to point communication between modules in a system on chip. The advantage of this protocol is the open nature of it that enables high re-usability of intellectual property by having an open interface description available for designers [1].

#### 2.2.3 NoC benchmarking research

Several research groups have investigated NoCs and benchmarking of them. Salminen et al describes some of the requirements connected to benchmarking in [30]. In this paper it is a focus on the open nature of benchmarking to enable comparison between different types of NoCs. As previously mentioned, a group has been formed, NoC Benchmarking Workgroup, with special emphasis on this open nature of the benchmarking and has taken the ideas further. This work group and their milestones is presented in further details in [16].

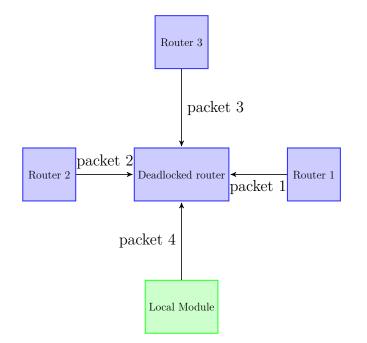

### 2.3 Deadlocks

One major problem with shared resource<sup>1</sup> systems such as the NoC is deadlocks [3, p.66]. This is a state where two or more applications wants to use the same resource and are unable to proceed because all awaits the others to move on. For the AHEAD-NoC this situation occurs when to packages arrive from three or four

<sup>&</sup>lt;sup>1</sup>Shared resources in this aspect are elements such as buses, memory or input/output pins

direction at specific router at the same time. The system stalls and has to be reset to function properly. Hence, to have a running system it is essential to avoid deadlocks or make the system able to solve this problem. The situation is depicted in Figure 2.1Deadlock situationfigure.caption.16 where the router is only able to hold two packages and route one through itself at the same time. When the third package from the local module arrives at the same time as the two others, the router is locked and unable to perform its routing operation. When this situation occurs for the AHEAD NoC is described in [25].

Figure 2.1: Deadlock situation with three routers and one local module sending package to the router at the same time.

### 2.4 Clustering

Clustering was introduced in the pre-project report [27] as a way of grouping elements with large communication needs together. In a system with the risk of deadlocks, to cluster objects with large communications need is essential. By using this methodology, the modules connected to the NoC avoids generating crossing traffic and the risk of deadlocks is reduced. With low crossing traffic and shorter distance for packages to travel, latency will also be reduced.

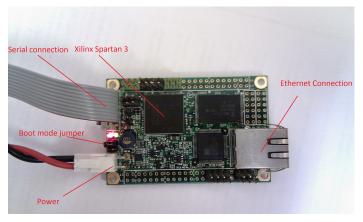

### 2.5 System platforms

The platform for this assignment has been the Suzaku-S platform. This platform includes a Spartan 3 XC3S1000 FPGA for the SZ030 version and a Spartan 3E XC3S1200 for the SZ130 version. The assignment started out with the 030 version, but changed to the 130 to have more resources in the development. The Spartan 3E is based on the Spartan 3 and is quite similar to it but has more Configurable Logic Blocks (CLB) available and more Digital Clock Managers (DCM).

CLBs are the basic building block in Xilinx Spartan FPGAs and contains four Slices that contains two Look Up Tables (LUT) and two flip flops. DCMs assist the clock distribution on the FPGA and provides control over clock frequency, clock skew and phase shifts. The main motivation to use the 130 instead of the 030 in this project is the higher number of available CLBs. More details about the Xilinx Spartan FPGAs and their content are given in their data sheets [4,5] and in the Xilinx dictionary [33]. List of other equipment used in this project is given in Appendix C.1Equipment list for this projectsection.C.1

| FPGA      | CLBs | Slices | LUTs  | Slice Flip Flops | Block RAM bits |

|-----------|------|--------|-------|------------------|----------------|

| XC3S1000  | 1920 | 7680   | 17280 | 17280            | 432K           |

| XC3S1200E | 2168 | 8672   | 19512 | 19512            | 504K           |

Table 2.1: Data for the two FPGAs used in the project.

(a) Suzaku-S 030

(b) Suzaku-S 130

Figure 2.2: The suzaku boards in operation [27].

# Chapter 3

## **Previous work**

The assignment is based on the work performed by Ivar Ersland (2009), Andreas Hepsø (2010) and the project by Magnus Namork in the fall of 2010. Ersland more or less finished the router design while Hepsø started the creation of an application test of the network. In the pre-project of this thesis this system was developed further and new table driven functionality was added. It is the foundation of the development of a full system test with reactive functionality. This chapter describes the previous work done with the NoC and the test system

#### **3.1** Functionality

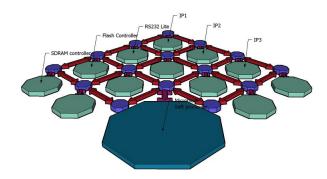

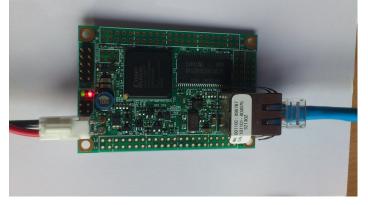

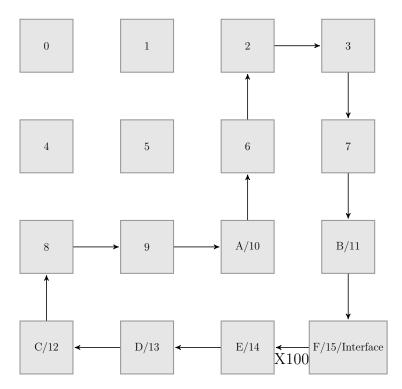

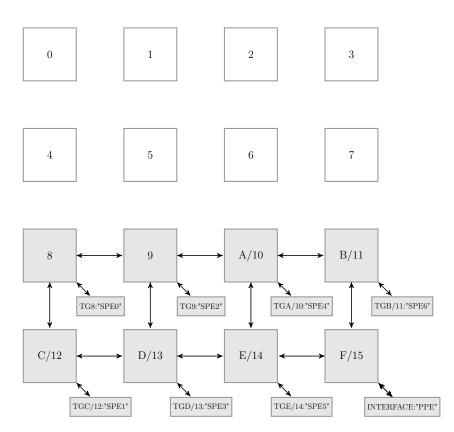

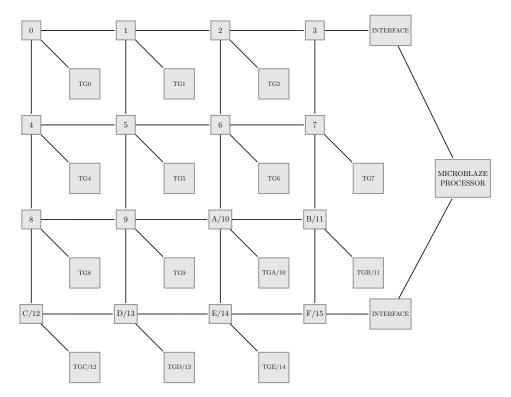

The system consists of 16 routers with a test generator connected, as depicted in Figure 3.1Network on Chip structurefigure.caption.19. It operates using the XY routing algorithm which is a simple algorithm that sends packages first in the correct horizontal (X) direction before it sends the package in vertical (Y) direction [17]. The NoC routers are connected through an interface module, via the on chip bus of the FPGA to a microprocessor called MicroBlaze. This microprocessor is a soft core processor implemented on the FPGA [34]. It runs the operating system uClinux which is a small variant of the Linux operating system. The uClinux adds the possibility of software communication with the network on the FPGA in run time. It is accomplished by cross compiling C programs with a specific compiler called mb-gcc which adapts the program to the MicroBlaze processor.

Figure 3.1: The Network on Chip in a basic mesh configuration with test generator connected to each router.

## 3.2 Design of the AHEAD Network on Chip

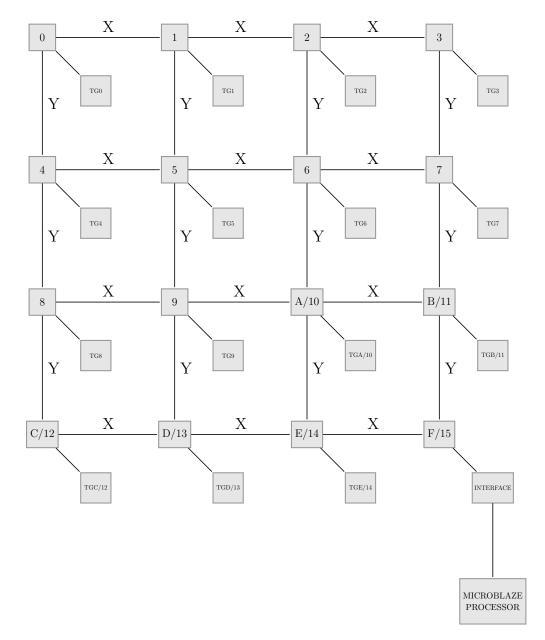

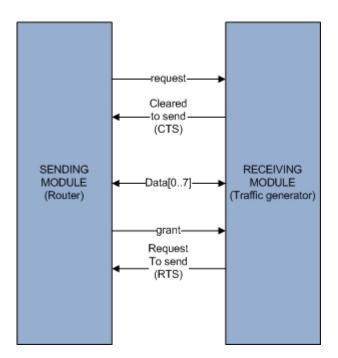

The system created by Ersland in [17] is the main foundation of the current system with some smaller adjustments. The system consists of a mesh of routers with buffers that routes packages based on information in the package. It uses packet-switching as transmission topology. The packages are 64 bit wide divided into eight flits<sup>1</sup> sent over an eight bit bus between each router. The routers and connected modules have a handshaking protocol that controls the sending and receiving of data between routers and from routers to modules. This protocol has the signals CTS (Cleared to send), RTS (request to send), request and grant. The latter signals are the signals on the senders side. This handshaking is used by the interface module and the test generators (TG) to be able to interact with their corresponding routers.

Sending of packages between TG and router is performed in the following operations:

- The router has a package it wants to send

- It sends its request signal to the TG

- The TG sends the CTS signal back and the transmission commences.

- After the TG is finished and ready to send back to the router the TG sets its RTS signal high

- The router sends a grant back in response

- Transmission from TG to router is completed

This operation is illustrated in Figure 3.2Illustration of handshaking.figure.caption.20. AHEAD NoC previously had a system to handle prioritization of packages, but this was later removed in [25] because the behaviour did not function as intended.

One thing worth mentioning is the static nature of the design. The modules in the NoC are all defined as single entities several times in the HDL code. They are

<sup>&</sup>lt;sup>1</sup>Flit is a part of the package transferred at the same time [18]

Figure 3.2: Illustration of handshaking.

not generic entities that could easily be added or removed by changing the system parameters. I.e. specifying in the top module that this system has eight TGs and eight routers instead of sixteen. This way of describing the NoC gives low degree of flexibility in modifying the system size and properties.

For more detailed information about the structure of the routing system and the routers, refer to Ersland [17].

## 3.2.1 Test system

The test-system work was initially started by Ersland, however he did not manage to complete the entire work of this system. Hepsø took this part further and introduced in [25] a more complete test system with a test generator and a system for monitoring traffic with traffic monitors. These monitors and a multiplexer module counted packages and stamped the packages with a global time based on clock cycles. In his work he also tested limitations within the system by testing different loads applied to the routers, including crossing traffic similar to Figure 2.1Deadlock situationfigure.caption.16.

#### 3.2.2 Reactive test modules

The project completed in the fall of 2010, Namork [27] developed reactive functionality within the test system developed by Hepsø. The difference between these modules and the ones from previous versions was the ability to generate specified traffic and give the modules an independent set of operations to perform based on input. Based on a table that defined the behaviour of the test generator, the test generator sent traffic out on the network. It is mainly this work which is developed further and tested in this assignment.

## 3.3 Initial status of the system

When looking at the system after the project performed in 2010 one could map some areas to be looked at in further development. In brevity these were the properties of the system prior to the work on this assignment began.

- The hardware/software interface defined in the user\_logic was not functional, the readout from the circuit was incorrect

- The previous C-code program developed for the system was not up to date with regards to the current version of the NoC system

- The area consumption was above 100% for the entire system of 16 test generators

- Reactive test generators exist, but not tested in a system

- The routing works as intended

- The routing is not deadlock free

These properties has been the foundation for detecting different areas where it is possible to achieve improvements. Especially the hardware/software interface was an area with great interest because a functional interface would mean onchip-testing of the network would be possible. This would also open the door for developing more complex programs that could use the network on the FPGA.

#### 3.3.1 System properties

The system bandwidth was determined by Ivar Ersland [18] as

$$8 \times 8 \text{bit} \frac{123 \text{MHz}}{12 \text{ Clock cycles}} \times 2 = 1312 \text{Mbit/s} = 1,3 \text{Gbit/s}$$

(3.1)

This is given a frequency of 123 MHz for the system without any loads i.e. test generators.In [27], a lower frequency of 50 MHz with was found to be more feasible. Due to the proportional relationship between frequency and bandwidth, this leads to the following bandwidth.

$$8 \times 8 \text{bit} \frac{50 \text{MHz}}{12 \text{ Clock cycles}} \times 2 = 533 \text{Mbit/s}$$

(3.2)

The number 12 comes from eight cycles to transfer a package four cycles in handshaking between routers and between routers and test generators. For this reason, 533 Mbit/s from Equation 3.2System properties equation.3.3.2 is the reference value used for the bandwidth in this assignment.

| ſ | Frequency           | Theoretical   | Bus Width       | Package Size |

|---|---------------------|---------------|-----------------|--------------|

|   |                     | Bandwidth     | flit size       |              |

|   |                     |               | router<->router |              |

|   | $123 \mathrm{~MHz}$ | 1,3 Gbps [18] | 8 bit           | 64  bit      |

|   | $50 \mathrm{~MHz}$  | 533 Mbps      | 8 bit           | 64  bit      |

# 3.4 Test system motivation

The initial status of the system gives the backdrop and motivation for the further development of the system. Since the system is not deadlock-free, the ability to use it for specific purposes and applications requires knowledge of how modules functionally could be placed in the network. To get this information it is essential to test the properties of the NoC and compare it with the applications' requirements. When knowledge of the the properties has been gained, limitations and possibilities with the NoC provides the information about what is feasible to implement in the AHEAD NoC system. In addition this provides information about what is necessary to do to extend functionality. Some interesting factors to investigate, is how large traffic of packages the system can handle, and how long time it will use to handle the traffic in the system. These factors corresponds to the avoidance of deadlocks and the latter to the throughput and latency of the system.

# Chapter 4

# Development of the system

The development of the system has been divided into two different areas. Since the system did not function properly from the beginning of the project, some effort had to be put into the development of a functioning system. The goal was then to run it on the FPGA in a proper manner and receive a response when testing. This is the structural development of the system. The second part considers the functionality of the test system and in particular the test generators in the system and their behaviour. This is defined as functional development. This chapter presents some of the main features connected to these to areas. Chapter 5Requirements and designchapter.5 will describe the features from this chapter in further detail.

# 4.1 Structural development

### 4.1.1 Generic code development

Having a system which is built for communication between modules proposes a challenge when it comes to how the design is organized. This is because everything has to be linked properly together and several instances of the same modules has to be added to the system. By having a focus on a generic design it is possible to both achieve flexibility in the system and improve the ability to alter the functionality and testability. The implementation of this concept is described in details in Chapter 5Requirements and designchapter.5 as a backdrop to the development of the test generator functionality.

## 4.1.2 Hardware software interfacing (HW/SW)

The HW/SW interface has been an issue in previous NoC projects, as described in the report of Ersland in [17]. It is a critical component to run proper tests of the NoC when implemented on the FPGA. This part describes the investigations made and the solutions implemented that makes the interface functional.

#### Interfacing from software

The user-interface to the circuit is described in software with an application written in C. The application, in this case the NoC, is assigned a memory space divided into registers when instantiating the peripheral in the Embedded Development Kit(EDK). In the current version of the system, nine registers are connected to the hardware, each of 32 bit . This requires a memory of  $32 \times 9 = 288$ bit = 0x120(hexadecimal) which entails a memory range of 512 bits and an address range from 000 to 1FF. To use these in a simple and easily understandable manor has been one of the main focus' of the development. The C coded program has, based on this motivation, been adapted to use the registers as variables to simplify read and write operations.

#### Memory organization

A step down in the hierarchy of the design is the hardware/software interface. This is the communications channel between the FPGA hardware implementation and the software executing on the MicroBlaze processor. When communicating between these two domains there are some considerations that has to be taken into account. An area with great impact is the memory space. Spartan FPGAs comes without a Memory Management Unit(MMU) and memory read-and-write has to be done in a direct manner. Hence, none of the default C methods for handling memory read and write works. The first problem to arise with the memory space was the location of the registers in the memory block of the FPGA. The initial memory area was defined between 0x81000000 and 0x810001FF. This was not functioning properly either due to defect memory (SDRAM) or proximity/overlap of other modules' assigned memory. The SDRAM controller of the Suzaku FPGA system is located just up to 0x80FFFFFF in Spartan 3 and 0x81FFFFFF for the

Spartan 3E and this might be the root of the problems with the mentioned memory space.

To remove these problems, the memory space designated for the Network on Chip was moved. The solution to this problem, was found using a simple adder module with simple output from [20]. The adder module was moved around to several memory ranges and tested before concluding with an area suitable for the AHEAD NoC. The NoC entity was placed in the area [0x84000000->0x8400001FF] and managed to run properly with this memory space. Hence providing a working solution for the NoC module. For further details about memory and how to organize the system, please refer to Appendix DTutorial:How to implement the Network on Chip on the Suzaku-S platformappendix.D and Figure D.2System Assembly EDKfigure.caption.81.

#### Interfacing from Hardware

When developing and implementing the HW/SW interface, another challenge surfaced. It was located a difference between the way the Microblaze processor writes to the memory registers and how the FPGA module reads from these registers. The cause was found in the Microblaze reference guide [34, p.21] that the registers are written 0:31 with the Least significant bit(LSB) at 31. However, the hardware interface and the NoC uses the common 31 downto 0 notation for VHDL, and this causes a SW input of hexadecimal x"ABCDEF00" would give an input x"00FEDCBA" to the NoC on the FPGA. This incorrect input gave no useful information to the circuit as described in [17].

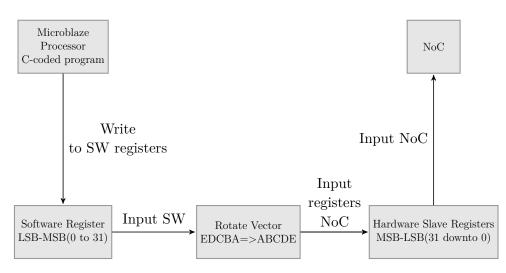

The solution was adding a function to reverse the incoming vectors. This enabled the use of the common "31 downto 0" notation without having to write the vectors inversely in the C coded program. The vectors added from the C-code are in this way directly compatible with the data entering the network through the interface module. This method is illustrated in Figure 4.1HW/SW interface vector handling.figure.caption.25.

Figure 4.1: HW/SW interface vector handling.

## 4.1.3 Other structural changes

There has also been done work improving the easiness of communicating with the NoC on FPGA. In general this is connected to using the Ethernet connection of the Suzaku-S together with tools such as Network File System(NFS) [12]. Having these parts in place simplifies the development of the system and the time from new functionality is developed to its FPGA implementation is reduced. The different ways of setting up and reconfiguring the NoC system on the FPGA is described in details in Appendix DTutorial:How to implement the Network on Chip on the Suzaku-S platformappendix.D.

## 4.2 Functional development

This part of the project development is based on desired properties to test on the AHEAD NoC. It gives an idea of the direction the test-system is developed.

### 4.2.1 Specifications

To create a more generic design and to full-fill the testing motivation of the project, a set of different design implementations was developed. The motivation for these features was to improve the benchmarking of the AHEAD Network on Chip. Func-

29

tionality introduced for the NoC test system included:

- 1. Completely reactive system which reacts to the information in the package

- 2. Use information in packages and tables to generate specific traffic patterns

- 3. Ability to change traffic tables from software

- 4. Manipulation of data in each packet

- 5. Calculate the bandwidth and latency of the system

- 6. Ability to run software programs and interact with the system when executing on the FPGA

#### What properties to measure

To get a precise measurement of the network it was necessary to have some properties to measure. The system already has functionality counting packages and stamping them with current number of clock cycles. It has been used further and connected to important metrics for the NoC. These metrics are useful to get an idea of the properties of the system, as introduced in Section 2.2.1System propertiessubsection.2.2.1:

- Throughput

- Latency

- Bandwidth

#### How to create the tests

To perform a test strategy that measures the given properties, it has been looked at the number of active components in the system and how they communicate. Secondly, the idea has been to develop a system with the ability to generate larger amount of data to get a test system that resembles the application one wants to evaluate. The focus was to get a good understanding of how the traffic behaves in the circuit, therefore the modules are deterministic<sup>1</sup> in their behaviour. This was in contrast to the previous version that included a pseudo random functionality.

The functionality of the test generators are Finite State Machines(FSM) all together. This provides a good platform for performing different tasks based on different information in packages. The development of the functionality is in that matter only a question of altering the states within the modules. In the development the concept was to have one module that could fill all the roles in a benchmark or test and therefore the generic structure of each module was essential. The specific functionality of the modules was based upon two different application examples. These are:

- An MPEG pattern simulated and run on the FPGA

- A Cell processor like system with computation and communication

## 4.3 Application example:MPEG decoder

Andreas Hepsø introduced in his Master thesis, an MPEG decoder and scaler as an application applicable to the NoC [25]. This system consists of 11 different modules performing the MPEG decoding and scaling of a movie stream. In a mobile application it will is desired to be able to downscale the video in real time without delays. The MPEG decoder is fixed in its structure in the way that one sends packages in the same direction through all the steps without sending packages backwards or to several different test generators.

#### 4.3.1 Real time requirements

If used as an on-the-fly scaler<sup>2</sup>, as described by Hepsø in [25], some system requirements will apply. The packet stream has to be continuous and little delay will be accepted as it will lead to a reduced quality of the movie for the user. This means that such a system has soft real time requirements<sup>3</sup>. Because the system has these

$<sup>^{1}</sup>$ Deterministic behaviour means that the behaviour is predictable

<sup>&</sup>lt;sup>2</sup>On the fly scaler means that the scaling is done in real time

$<sup>^{3}</sup>$ Soft real time requirements means that the output/result of the system has a deadline,but a missed deadline is not critical to the system

Figure 4.2: MPEG traffic pattern, X defines a (possible) generation of packages.

requirements it is necessary to have a high degree of determinism in the system and a highly controlled data and package flow.

# 4.4 Application example: PS3 ring bus system

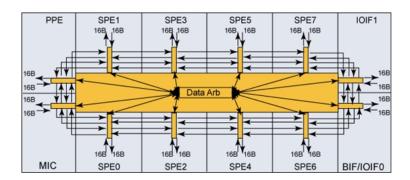

Another application example is the Cell processor of the Playstation 3 [10]. The system consists of eight so called synergistic processing elements(SPE), one Power processing element(PPE) and one memory interface controller(MIC). The PPE is in control of running the operating system and coordinating data flow through SPEs. The Cell processor has the Element Interconnect Bus(EIB) as its main interconnect between elements in the processor. This system has a ring bus topology with a centralized arbiter which decides which processing element has access to the bus. The system is then capable of routing packages to and from the processing element either in a clockwise or a counter-clockwise manor. This is illustrated in Figure 4.3Cell processorfigure.caption.30. The Cell system parameters are not the

Figure 4.3: Illustration of the Cell processor.

main focus of the use of this as a test example. It is not a goal to achieve the same performance from the AHEAD NoC, but to show one way of using the NoC and to visualize the essential parameters and properties that is measured by referring to a real application.

| Frequency | Theoretical | Effective Bandwidth | Bus Width | Package Size |

|-----------|-------------|---------------------|-----------|--------------|

|           | Bandwidth   |                     |           |              |

| 3.2 GHz   | 204.8  GB/s | 78GB/s - 197GB/s    | 16 bytes  | 256 bytes    |

Table 4.1: Properties of the Cell processor [13].

With this system as a test case example, a relevant question would be; what if the PS3 system was implemented on a Network on Chip? What would the properties of the system be and would the network handle the data communication between modules? These are questions that forms the foundation for the development of a similar system for the NoC. This system is not able to do as many operations as the cell processor, but the communication and way of operating is similar [13]. The concept is to replace the EIB with NoC and see how the behaviour of the system is like. It is in this case worth noticing that the Cell EIB uses centralized arbitration<sup>4</sup> as shown in Figure 4.3Cell processorfigure.caption.30 while the NoC uses distributed arbitration in each router [18]. The packages in Cell and in the NoC are similar with regards to dimension. The Cell EIB has a width of 16 bytes and a pacakge size of 128 bytes while the NoC has a data width out of each router of 8 bits and a package size of 64. This means that both

<sup>&</sup>lt;sup>4</sup>Arbiter is a component using certain criteria to determine which module allowed to access the resource i.e a bus [28, p.26]

Figure 4.4: Cell processor with NoC instead of ring bus, White is deactivated area.

needs 8 cycles in receiving and 8 cycles in sending data out on both networks. The implementation of this example is described further in the next chapter.

# 4.5 Other possible application examples

## 4.5.1 RSA encryption

A common example well-applicable to benchmarking and testing of processors and other systems is the RSA encryption algorithm [29]. This algorithm encrypts and decrypts a message of various size. This has been used as benchmark for several applications such as the already mentioned cell processor [19]. An RSA system from a previous project at NTNU, Realization and test of digital components, was synthesized and used 10% of the area of the Spartan 3E FPGA. The implementation has, however, not been developed further since the RSA circuit is quite complex and has to be modularized and distributed in a correct way on the Network on Chip to be used as a benchmarking and test system. This would take a lot of effort and not necessarily provides more information about the systems' properties than a simpler system such as the Cell example does. However, it is a possibility that would be interesting if one wants to develop a specific practical application for later use.

# Chapter 5

# **Requirements and design**

This chapter describes implementation details about the systems described in Chapter 4Development of the systemchapter.4. It describes the code behind the solution, from development of the hardware/software interface to the specifications of the traffic system on the network.

# 5.1 Design goals

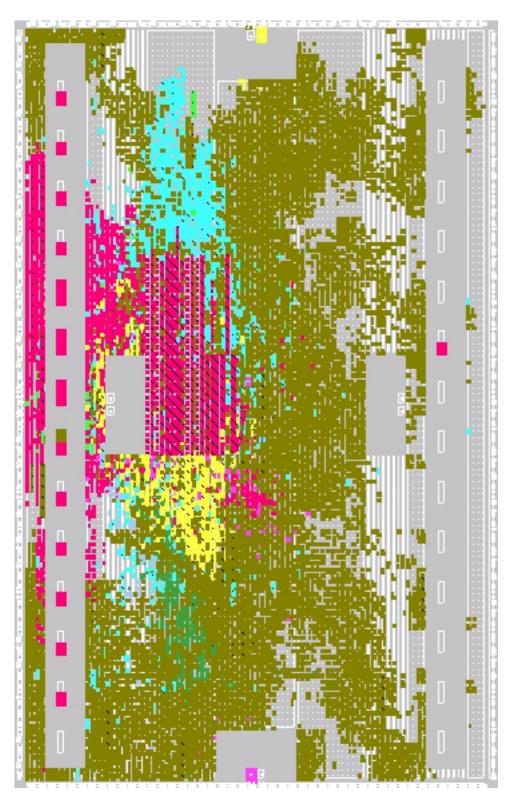

## 5.1.1 Area

The conclusions made in [25] [17] and [27] said that the circuit-area containing the test modules is close to 100%. Due to this, the design is primarily concentrated around optimization and reduction of the circuit area. Optimization of the frequency is outside the scope for the circuit. Mainly because the focus is to see how NoC routing behaves with a certain load of data packages, and not how fast it will perform. The original code has been inspected and some areas of improvements has been detected, to optimize the design for a minimum area of the circuit.

#### Area improvements attempts

1. Reducing the size of large global vectors including

Time-stamp-vector

Package counter vector

- 2. Changing the structure of the FSMs from variables to signals in next state control logic

- 3. Changing from asynchronous reset to synchronous reset

- 4. Removing pseudo-random test functionality

The only factor contributed towards reducing the area substantially was the removal of the pseudo-random functionality. This gave a reduction of the area for the test generator of approximately 10%. The rewrite of the test generators' FSM caused a timing problem in communication with the router, hence it was not developed further. Changing the reset from asynchronous to synchronous reset, as suggested by Xilinx in [22], gave some issues with the previous implemented functionality and was not investigated further. None of the other attempts proved to give a substantial contribution of available area. This is possibly due to the structure of the FPGA.

Succeeding with the other improvements, a more thorough investigation of the design, including floor planning, would be required and has not been pursued. A simpler approach has been chosen due to the efficient use of time. The way of testing and implementing added functionality is therefore primarily based upon creating a design that is easy to alter the size when testing different properties and versions of the system.

#### 5.1.2 Flexible Design

When changing the system functionality it is advantageous that minor changes of code may result in a substantial change in behaviour and size. The existing design lacked a good framework for maintainability and flexibility. It has therefore been made some improvements in the direction of creating a flexible design. This is beneficial since the area of the design is close to 100% of the FPGA, and to include more functionality in the test system requires this property. In addition, to develop it to fit different FPGA platforms might be a desired feature in future projects. For instance, it might be desired to use the NoC on a smaller platform and then it must be simple to include and exclude modules in the system.

In HW designs using VHDL this is solved by using generic mapping and generate

statements as displayed in the code in Listing 5.1Example of how the generate statement is used to make it easier to add and remove parts of the system; the generic variable:deactivated\_tm defines the number of modules deactivatedlstlisting.5.1. From before, in [27], a test- and type library was developed. These libraries include types, functions and signals to be added and withdrawn from the system based on the current requirements. In that way they provide a system to maintain, develop and optimize the NoC system in an easy way in both this project and further development.

One area that has been evaluated, but not improved, is the router design. As mentioned in Section 3.2Design of the AHEAD Network on Chipsection.3.2 it was designed in a very static way, and no easy way of changing the number of routers in the system exists. The possibility of changing this in the same way as with the test generators has been looked into, but this would require an entire rewrite of the system. For testing purposes it does not provide an improvement, and will require more time to do. Therefore, the possibility to remove and add test generators and traffic monitors is present, but not to remove the connected and then redundant router connected to it. However, in later optimization of the NoC this could be a beneficial improvement of the system. Supplied code of the test generator and interface is supplied in Appendix BCodeappendix.B.

```

NoC TM: for n in deactivated tm to number of routers-1 generate

TM: entity noc_v1_00_a.TM(behavioral)

2

generic map(tm_number=>n)--gives the correct index to the traffic monitor

3

4

port map(

5

clk

\Rightarrow ungated_clk,

6

\Rightarrow reset,

reset

7

CTS

=> packet_trigger(n),

readout_finished => readout_finished ,

8

9

packet_counter

=> packet_cnt(n)

10

);

11

end generate:

```

Listing 5.1: Example of how the generate statement is used to make it easier to add and remove parts of the system; the generic variable:deactivated\_tm defines the number of modules deactivated.

## 5.2 Hardware/Software interface

#### 5.2.1 Software accessible registers

The communication between hardware and software is done with registers in memory defined in the synthesis tool. There are in total nine HW/SW registers currently in use and they are organized like in Table 5.2Register numbers and functionality.table.caption.34.

A specifically important register is register 4. This register is the controlregister and it is used to determine transmission of the packages to the network. It also contains the reset functionality. This register and its bit values are depicted in Table 5.1Address listingtable.caption.33 In total there are 20 registers in the AHEAD NoC, but as mentioned only nine of them are connected to the it. The remaining ones are added to have registers available when extending functionality, i.e. with a second interface module. Another potential use of these registers is to use them as a platform for readout of the monitoring of data on the FPGA in real time. These ideas have not been developed further in this assignment due to the focus on the functionality of the test system and that it requires more time.

| Bit values    | 3128       | 27   | 26               | 258        | 7                   | 3     | 20         |

|---------------|------------|------|------------------|------------|---------------------|-------|------------|

| Signal names: | Mux_select | send | readout_finished | not in use | ${ m BRAM\_enable}$ | reset | not in use |

Table 5.1: List of different bit values and their use in the control register.

## 5.2.2 Hardware interfacing

The registers are all instantiated in the user logic file of the system which serves as a high level hardware part of the HW/SW interface. The interface module is in this case the low-level interface part which is connected directly to the NoC. The registers are all 32 bit wide. The read-and-write to these are controlled by

| Register | Info                     | Address range | Name         |

|----------|--------------------------|---------------|--------------|

| 0        | Data_in_33               | 0x84000000+0  | slv_reg0     |

| 1        | Data_in_33               | 0x84000000+4  | slv_reg1     |

| 2        | $Data_out_33$            | 0x84000000+8  | slv_reg2     |

| 3        | Data_out_33              | 0x84000000+C  | slv_reg3     |

| 4        | Status bits/Control bits | 0x84000000+10 | slv_reg4     |

| 5        | BRAM address register    | 0x84000000+14 | slv_reg5     |

| 6        | Feedback register        | 0x84000000+18 | slv_reg6     |

| 7        | Counter                  | 0x84000000+1C | $slv_reg7$   |

| 8        | Timer                    | 0x84000000+22 | slv_reg8     |

| 919      | Available                | 0x84000000    | $slv_reg919$ |

Table 5.2: Register numbers and functionality.

three different processes; read, write and a specific process to specify how these operations are connected to the NoC. By dividing these processes it is much easier to change a specific part of the NoC interface. The processes uses a vector with a "one hot" bit to determine which register to be read and written from. These are all default values when creating the peripheral in the Xilinx EDK tool but they have been altered to get a more readable and maintainable code. An important property already mentioned in Chapter 4Development of the systemchapter.4 is the rotation of the input vector from the software registers. This is implemented with a simple function to enable a simplistic read and write to the NoC.

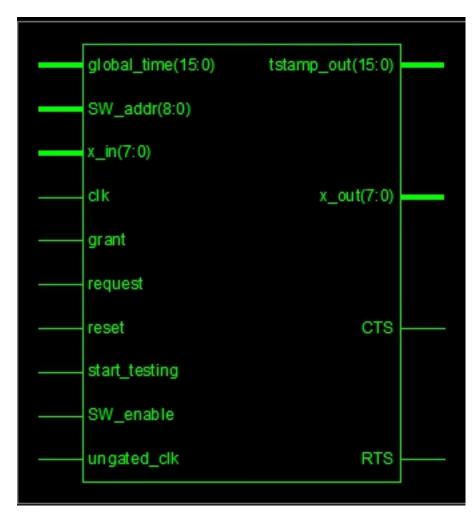

## 5.3 Traffic generator

The traffic generator is the core of the test and benchmarking system and is the component that produces traffic in the system. The original generator designed by Hepsø [25] provided limited functionality for producing data to the system. It was based on three Finite State Machines (FSMs) handling the receiving, throughput of the generator and sending procedures. The designed structure of the routers, interface module and test generators was the same. To remain compatible with the rest of the system it is reasonable to keep the test generators in this way. The use of FSMs is also proposed as a good way of designing test generators, this as described in [14, p.7].