# Embedded System for Electronic Circuit Education

Kai André Venjum

Master of Science in Electronics Submission date: June 2010 Supervisor: Per Gunnar Kjeldsberg, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

In many situations, like school visits at NTNU, Forskningstorget and Elektronikk- & telekommunikasjonsdagen, it is desirable for Department of Electronics and Telecommunication to demonstrate good examples of electronic systems. Embedded systems are well suited as demonstrators since the combination of hardware and software gives both flexibility and wide possibilities for optimization.

In this task, the student will implement a specified system for demonstration of topics related to courses provided by the department. In order to make a good demonstration, necessary presentation material is also to be made, together with a plan on how to demonstrate the embedded system.

Assignment given: 22. January 2010 Supervisor: Per Gunnar Kjeldsberg, IET

# Abstract

Embedded systems are ideal as electronic demonstrators because they provides the designer with wide possibilities for optimization through codesign. In many situations, like school visits at the Norwegian University of Science and Technology (NTNU), "Forskningstorget" and "Elektronikk- & Telekommunikasjonsdagen", it is desirable for the Department of Electronics and Telecommunication to both motivate and recruit new students to a future career in electronics. Thus, a demonstrator with an interesting presentation may give students an insight in what is possible when studying electronics at NTNU, in addition to a good examples of an electronic system. A good demonstrator for the department include one or more electronic topics and presents the relevant theory in different educational levels

This master thesis includes the implementation of an embedded system used for demonstrating basic electronics. The Embedded System for Electronic Circuit Education is a platform for easy implementation of several scenarios with different topics within electronics. The system is designed with respect to a pedagogical view, and is implemented on both the Altera DE2 and the Atmel AVR STK600. In addition the embedded demonstrator includes a monitor for user interface and demonstration materiel. The main modules in the demonstrator is the Cyclone II 2C35 FPGA and the AVR AT90USB1287 microcontroller used to control the system behavior and the user interface. The demonstrator already includes two example scenarios, namely the "Automatic Adjustment of Light" and "How to Count in Binary, Hexadecimal and Decimal" with the topics Electronic Components and Numerical Systems respectively.

With both existing and future scenarios, the embedded demonstrator has the possibility to both motivate and activate students with an interactive interface. In addition, the demonstrator may individualize educational levels to the different target groups with the demonstration material displayed on the monitor. Thus, the Embedded System for Electronic Circuit Education is a well suited demonstrator to recruit and motivate students to a future carrier in electronics. II

# Preface

This master thesis is the finish line of my five years as a student in Trondheim. These years have without a doubt been the best years of my life and I will always carry the memories with me.

The goal with this project has been to design and implement an embedded demonstrator for Department of Electronics and Telecommunication at NTNU. This demonstrator is intended to help the department to recruit future students to NTNU. The thoughts of motivating younger pupils to a five years master study, hopefully with much fun and future good memories, together with practical use of courses through time, was the main motivation for this project.

The last six months have been both exciting and challenging at the same time. It seemed like the learning process through this project would never stop. Now a new era of my life begins with new challenges. The literature study of both the Altera DE2 and Atmel STK600 have been fulfilling. However, due to time constrains, a dynamic frame buffer could not be implemented.

Several people have contributed to this report, without them, both the report and the product had not been the same. I want to thank my supervisor Per Gunnar Kjeldsberg at Department of Electronics and Telecommunication for advices and guidelines through the whole process. I am also thankful to Cato Marwell Jonassen and Jarle Larsen for their collaboration through the five years and particularly this last six months. I am also thankful to Cato Marwell Jonassen and Jarle Cator" and to Ingulf Helland for his help with the VGA-Controller. Finally, I am particularly grateful for the support from Jarle Larsen and Ingrid Vågan Tøgersen.

Kai André Venjum NTNU, Trondheim June 2010 IV

# Definitions

| ADC   | : | Analog-to-Digital Converter - converts continuous signals to discrete dig-<br>ital numbers                                                                                     |

|-------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASIC  | : | Application-Specific Integrated Circuit - a hardware circuit of a application in silicone                                                                                      |

| DAC   | : | Digital-to-Analog Converter - converts a digital code to an analog signal                                                                                                      |

| DMA   | : | Direct Memory Access - allows certain hardware subsystems within a computer to access system memory for reading and/or writing independently of the central processing unit    |

| FIFO  | : | First In, First Out - This expression describes the principle of a queue processing technique or servicing conflicting demands by ordering process by first-come, first-served |

| FLASH | : | Flash memory - a non-volatile computer storage technology that can be electrically erased and reprogrammed                                                                     |

| FPGA  | : | Field-Programmable Gate Array - an integrated circuit designed to be<br>configured by the customer or designer after manufacturing                                             |

| HAL   | : | Hardware Abstraction Layer - an abstraction layer, implemented in soft-<br>ware, between the physical hardware of a computer and the software that<br>runs on it               |

| HDL   | : | Hardware Descriptive Language - a language for describing hardware                                                                                                             |

| ISR   | : | Interrupt Service Routine - a callback subroutine in an operating system<br>or device driver whose execution is triggered by the reception of an<br>interrupt                  |

| LSB   | : | Least Significant Bit - the bit position in a binary number having the smalest value                                                                                                                                  |

|-------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSB   | : | Most Significant Bit - the bit position in a binary number having the greatest value                                                                                                                                  |

| PLL   | : | Phase-locked loop - generate a frequency that is a multiple of the input frequency                                                                                                                                    |

| PWM   | : | Pulse-Width Modulation - uses a rectangular pulse wave whose pulse width is modulated resulting in the variation of the average value of the waveform                                                                 |

| RISC  | : | Reduced Instruction-Set Computing - a CPU design strategy based on<br>the insight that simplified instructions can provide higher performance<br>if this simplicity enables much faster execution of each instruction |

| SDRAM | : | Synchronous Dynamic Random Access Memory - a type of volatile mem-<br>ory which needs to be periodically refreshed                                                                                                    |

| SPI   | : | Serial Peripheral Interface - is a synchronous serial data link standard that operates in full duplex mode                                                                                                            |

| SRAM  | : | Static Random Access Memory - a type of volatile memory which do<br>not need to be refreshed, but it still need power to contain its data                                                                             |

| USB   | : | Universal Serial Bus - a specification to establish communication be-<br>tween devices and a host controller                                                                                                          |

| VGA   | : | Video Graphics Array - may refere to the analog computer display stan-<br>dard, the 15 pin d-sub connector or the 640x480 resolution                                                                                  |

# Contents

| 1        | Intr | oducti | ion                                | 1  |

|----------|------|--------|------------------------------------|----|

|          | 1.1  | Prelim | inary Work                         | 1  |

|          | 1.2  | Embeo  | dded systems                       | 2  |

|          | 1.3  | Codes  | ign                                | 3  |

|          | 1.4  | Chara  | cteristics for a good demonstrator | 4  |

|          | 1.5  | Main ( | Contributions                      | 4  |

|          | 1.6  | Struct | sure of Report                     | 5  |

| <b>2</b> | Des  | ign To | ools                               | 7  |

|          | 2.1  | Quart  | us II                              | 7  |

|          | 2.2  | Nios I | I Embedded Design Suite            | 8  |

|          | 2.3  | Model  | Sim                                | 9  |

|          | 2.4  | AVR S  | Studio 4                           | 9  |

| 3        | Alte | era DE | 2 and Related Theory               | 1  |

|          | 3.1  | Featur | res of the Altera DE2              | 11 |

|          | 3.2  | Altera | Cyclone II 2C35                    | 12 |

|          | 3.3  | Nios I | Ι                                  | 12 |

|          | 3.4  | 7-Segn | nent Display                       | 14 |

|          | 3.5  | Monite | or Control                         | 14 |

|          |      | 3.5.1  | Video Display Technology           | 15 |

|          |      | 3.5.2  | Video Refresh                      | 17 |

|          |      | 3.5.3  | ADV7123 VGA-DAC                    | 18 |

|          | 3.6  | Memo   | ry                                 | 20 |

|          |      | 3.6.1  | IS42S16400 SDRAM                   | 20 |

|          |      | 3.6.2  | S29AL032D Flash Memory             | 21 |

|          |      | 3.6.3  | Frame Buffer                       | 21 |

| <b>4</b> | Atn  | nel AV | TR STK600 and Domain Conversion    | 23 |

|          | 4.1  | Featur | res of the $STK600$                | 23 |

|          | 4.2  |        |                                    | 23 |

|          |      | 4.2.1  |                                    | 24 |

|          |      | 4.2.2  | 5 5                                | 25 |

|          |                 | 4.2.3          | Pulse Width Modulation                                    | 26              |

|----------|-----------------|----------------|-----------------------------------------------------------|-----------------|

| <b>5</b> | Cor             | nmuni          | cation Interface                                          | 27              |

|          | 5.1             | Serial         | Peripheral Interface                                      | 27              |

|          | 5.2             | Univer         | rsal Serial Bus                                           | 28              |

| 6        | Eleo            | ctronic        | Components                                                | <b>31</b>       |

|          | 6.1             |                | 1                                                         | 31              |

|          | 0.1             | 6.1.1          |                                                           | 31              |

|          |                 | 6.1.2          |                                                           | 32              |

|          | 6.2             |                | 0                                                         | 32              |

|          | 6.3             |                |                                                           | 33              |

|          | 6.4             | 0              | 1                                                         | 33              |

| 7        | Nur             | nerical        | l Systems                                                 | 35              |

| •        | 7.1             |                | 5                                                         | 35              |

|          | 7.2             |                | U U                                                       | 36              |

|          | 7.3             |                |                                                           | 36              |

|          | 7.4             |                | ·                                                         | $\frac{30}{37}$ |

|          |                 | 7.4.1          |                                                           | $\frac{37}{37}$ |

|          |                 | 7.4.2          |                                                           | $\frac{38}{38}$ |

|          |                 | 7.4.3          |                                                           | 38              |

| 8        | Sve             | tom M          | odules and Scenarios                                      | 41              |

| 0        | 8.1             |                |                                                           | <b>4</b> 1      |

|          | 8.2             |                |                                                           | 42              |

|          | 0.2             | 8.2.1          |                                                           | $\frac{12}{42}$ |

|          |                 | 8.2.2          |                                                           | 44              |

| 0        | <b>C</b>        | tom Ta         | nplementation and Discussion                              | 45              |

| 9        |                 |                | 1                                                         | <b>45</b><br>46 |

|          | 9.1             | 9.1.1          |                                                           |                 |

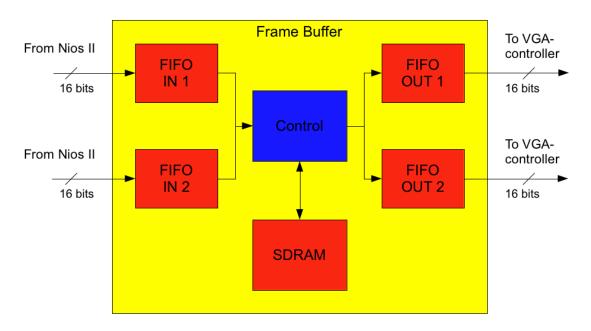

|          |                 | 9.1.1          | Frame Buffer                                              |                 |

|          |                 | 0.1.1          |                                                           | $50 \\ 52$      |

|          |                 | 9.1.3<br>9.1.4 |                                                           | $\frac{52}{54}$ |

|          | 9.2             | -              |                                                           | $\frac{54}{55}$ |

|          | 9.2             | 9.2.1          | •                                                         | $55 \\ 55$      |

|          |                 | 9.2.1<br>9.2.2 |                                                           | $\frac{55}{56}$ |

|          | 9.3             | 0              |                                                           | $\frac{50}{57}$ |

|          | 9.5             | 9.3.1          |                                                           | 57<br>57        |

|          |                 | 9.3.1<br>9.3.2 |                                                           | 57<br>58        |

|          |                 | 9.3.2<br>9.3.3 | 0                                                         | $\frac{50}{59}$ |

|          | 9.4             |                |                                                           | 59<br>60        |

|          | $\mathcal{J}.4$ | 9.4.1          |                                                           | 60<br>60        |

|          |                 |                | $\sim 100000$ $\sim 100000000000000000000000000000000000$ | <b>W</b>        |

|              | 9.5  | 9.4.3   | Tasks for the NIOS II     | 62 |

|--------------|------|---------|---------------------------|----|

| 10           | Den  | nonstra | ation                     | 65 |

| 11           | Con  | clusio  | ıs                        | 69 |

| $\mathbf{A}$ | VH   | DL-coo  | le: VGA-Controller        | 75 |

| в            | Veri | log-co  | de: One Pulse Generator   | 79 |

| С            | VH   | DL-coo  | le: Seven-Segment Decoder | 81 |

### CONTENTS

# Chapter 1

# Introduction

In many situations, like "Elektronikk- & Telekommunikasjonsdagen" and school visits at NTNU, it is important for Department of Electronics and Telecommunication to get peoples' attention, and to promote themselves to potential future students. In these situations, a demonstrator may be used to present the courses provided by the department, what electronic is and where it can be used. A demonstration may consist of a professor talking about the mentioned topics, but in this project it is desired to show concrete examples of practical use of electronics.

The main goal with a demonstration is to get people interested in the presented topics. To achieve this, the demonstrator should both be interactive and have familiar topics from the students everyday life. In addition, an ideal demonstrator should also provide a level of education in its demonstration.

This report implements the specifications of an embedded demonstrator described in [33]. The demonstrator specifies a platform for easy implementation of different scenarios for electronic topics. Two scenarios are already included, and provides education in both numerical systems and automatic adjustment of light. The platform and the included scenarios are specified with the theory influenced by a pedagogical view.

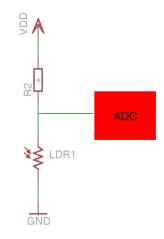

### 1.1 Preliminary Work

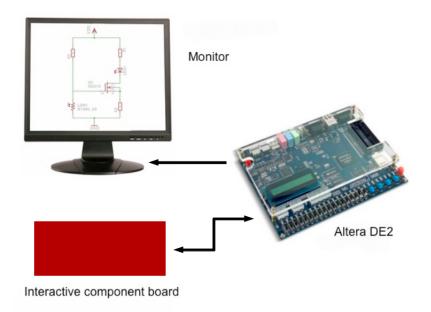

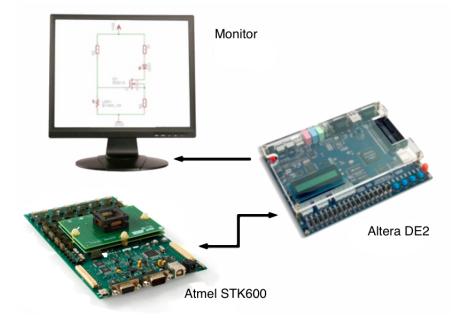

The motivation and the purpose of the mentioned report was to make a demonstrator to recruit new students to Department of Electronics and Telecommunication at NTNU. The implemented demonstrator should be both interactive and include electronic educational aspects. The best solution to achieve the requirements was considered to be the design of a platform for easy implementation of several scenarios with different educational levels, called an Embedded System for Electronic Circuit Education. This system provides the designer with the opportunity to implement several scenarios with the use of different methods implemented in the Altera DE2 and an interactive component board. The interactive component board is used as an interface between the user and the digital domain, and contains both an analog-to-digital converter (ADC) and a digital-to-analog converter (DAC), together with a selection of analog components indented for user interaction. In addition to these two modules, the Altera DE2 is connected to a monitor used to present scenario information and relevant theory that may be adjusted to the educational level, as shown in Figure 1.1.

Figure 1.1: Preliminary System Overview

The idea for this system is to let the user choose between the scenarios that is most interesting for him or her. An example of a scenario is Automatic Adjustment of Light, where the interactive component board is used together with Altera DE2 to demonstrate the effects of LDRs and LEDs. In addition, a virtual circuit on the monitor displays how the currents and the voltages changes in the circuit during operation, thus providing the user with a basic education in electronic circuit theory.

### 1.2 Embedded systems

According to John Catsoulis [14], computer systems fall into two categories. The first is the desktop computer. When someone says computer, this is the machine that usually come to their mind. The second type of computer is the embedded computer, a computer that is integrated into another system for the purpose of control and/or monitoring. The term embedded means being part of a larger unit and providing a dedicated service to that unit [24].

#### 1.3. CODESIGN

Both desktop computers and embedded computers consist of a processor, memory and often several forms of input and output [14]. Embedded hardware is often much simpler than a desktop hardware, but it can also be more complex. An embedded system can be implemented on a single chip with just a few support components, or it can consist of hundreds of processors working in parallel. The main difference between them is their intend in use. Desktop computers can run a variety of application programs, with system resources assigned by an operating system. In contrast, the embedded computer is normally dedicated to a specific task. In many cases, an embedded computer is used to replace application-specific electronics.

The embedded system typically has one application and only one, which is permanently running. The embedded computer may or may not have an operating system, and it rarely provides the user with the ability to arbitrarily install new software. The software is normally contained in the system's nonvolatile memory.

The advantage of using an embedded microprocessor over dedicated electronics is that the functionality of the system is determined by the software, not the hardware. This makes the embedded system easier to produce, and much easier to develop, than a complicated circuit [14].

### 1.3 Codesign

Hardware/software co-design means meeting system-level objectives by exploiting the synergism of hardware and software through their concurrent design [24].

The process of performing hardware/software tradeoffs requires a direct interaction between hardware and software design [21]. Hardware/software tradeoffs refer to decisions regarding the allocation of functions into hardware and software that attempt to satisfy a set of objectives. Thus hardware/software tradeoffs affect the amount and mixture of software and hardware employed, and lead to other kinds of tradeoffs, such as performance versus cost.

The introduction of field-programmable gate array (FPGA) technologies blurred the distinction between hardware and software. With field-programmable technology it is possible to configure the gate-level interconnection of hardware circuits after manufacturing. This flexibility opens new applications of digital circuits, and new hardware/software co-design problems arise. For example, one FPGA circuit may be configured on-the-fly to implement a specific software function with better performance than executing the corresponding code on a microprocessor [24].

#### 1.4 Characteristics for a good demonstrator

Some of the principles for good teaching is motivation, activation and individualization [17]. When teaching a group or a student, it is important that the teaching motivates and falls in interest for the target group. If the topics presented are known through their everyday life, it is easier to be motivated and to learn from the presentation. In order to achieve this, it can be a good idea to include the target group in activities where the group is included in the learning process.

People are different from each other, and they learn by different methods. Thus individualization is important to adjust the education to the individual needs and qualifications [16]. This is why schools have classes based on age, and why teaching is different in kindergarden and high school. Differentiation is the name of this theory, and age is one of the oldest methods to differentiate in the school system. In theory, the most perfect differentiation of a group is individualization, but in practice this is not possible with large groups[17].

When designing an embedded demonstrator it is important to have topics like differentiation, activation and motivation, as discussed above, in mind. The goal with this demonstrator is to recruite new students from higher secondary school. However, it is also desirable to motivate other students from lower levels to consider electronics as a future career. The age of the target group is thus important for the design, and it should be possible to adjust the difficulty according to the person or group who attends the presentation. Whether someone presents the demonstrator or the demonstrator is capable of introducing itself, it is important to remember that students have different qualifications related to their background. Due to this, a demonstrator should include the possibility for different levels of understanding.

To maintain the students interest in the demonstration, it is a good idea to allow the presentation to be interactive. When the user is interactive with the system, it is easier to keep him or her motivated. Another method for motivating pupils or students, is to relate the topics of the demonstrator to familiar devices in their everyday life. In addition, since the demonstrator will be used to recruit students to the department, it should also be relevant for courses that the department provides. In this way it can strengthen the future students idea of what electronics are and where it can be used.

### **1.5** Main Contributions

The main contributions in this report are:

- A presentation of the necessary theory to design both the platforms and scenarios

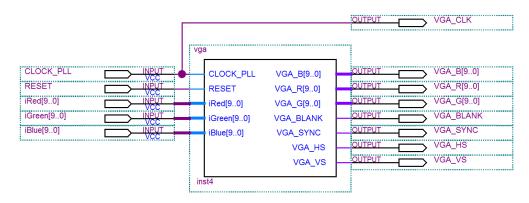

- The implementation of a VGA-Controller in VHDL

- The realization of a platform for implementation of scenarios

- The implementation of two different scenarios

- A implementation guide to future scenarios

### **1.6** Structure of Report

This report is divided into the following chapters: Chapter 2 presents the design tools used to implement the embedded demonstrator. In Chapter 3 and 4 the platforms used in the implementation process, namely the Altera DE2 and the Atmel STK600, and their related theory, are described in detail. Further, in Chapter 5, the communication interface between the two development platforms are discussed. Chapter 6 and 7 describes the theory needed to understand the implemented scenarios, while Chapter 8 and 9 presents the system overview and an in-depth discussion of the system implementation, together with a description on how to implement future scenarios. In Chapter 10, a guide to how the example scenarios should be demonstrated is presented. The final chapter, Chapter 11, presents the main conclusions of the system implementation.

# Chapter 2

# **Design** Tools

This chapter describes the design tools used for the design and test of the Embedded System for Electronic Circuit Education. When designing an embedded system, either an ASIC or a FPGA are needed for hardware circuits. Designing one ASIC is very expansive, thus a FPGA is a reasonable choice. There are in general two options for FPGAs and their design tools. Xilinx and Altera are the market leaders in FPGAs, and together they control over 80 percent of the market [1]. However, there are several options for microcontrollers, for example Atmel, Texas Instruments and ARM, and the choice of tools and hardware for this system was based on their availability at the department, and the design tools already familiar.

### 2.1 Quartus II

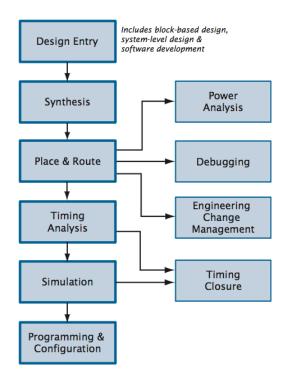

There are several EDA (Electronic Design Automation) tools available for circuit synthesis, implementation and simulation using VHDL or Verilog. The Altera Quartus II is one of them[28]. This design software includes a multi-platform design environment that can adapt to the user specific design needs. The Quartus II software includes solutions for the different phases of FPGA design, as seen in Figure 2.1.

The Quartus II software allows the designer to use the a graphical user- and commandline interface for each phase of the design flow. It is possible to use one of these interfaces for the entire flow, or use different options at different phases [6].

#### SOPC Builder

The SOPC (System-On-a-Programmable-Chip) Builder is a system development tool for creating systems based on processors, peripherals, memories and communication interfaces like USB and SPI [25]. USB and SPI are described in Chapter 5. SOPC

Figure 2.1: Quartus II Design Flow [6]

Builder enables the designer to define and generate a complete SOPC, and in a system design is included as part of the Quartus II software [9].

The SOPC Builder automates the task of integrating hardware components [9]. When using traditional design methods, the designer must manually write HDL modules to wire together the pieces of the system. With SOPC Builder, the designer only needs to specify the system components in a GUI, and SOPC Builder generates the interconnect logic automatically. SOPC Builder generates HDL files that defines all components of the system, and a top-level HDL file that connects all the components together. SOPC Builder generates either Verilog HDL or VHDL equally [9].

An another approach, is to use the MegaWizard plug-in manager. The MegaWizard can create most of same modules as SOPC builder. However, the MegaWizard can run as a stand-alone utility. Thus a SOPC system is not needed. An example of use, is when a hardware system only needs a PLL [9].

### 2.2 Nios II Embedded Design Suite

Writing software for the Nios II processor is similar to the software development process for any other microcontroller family [8]. The Nios II EDS provides a consistent software

#### 2.3. MODELSIM

development environment that works for all Nios II processor systems. It also includes many proprietary and open-source tools such as the GNU C/C++ tool chain for creating Nios II programs. In addition, the Nios II EDS has a build-in Hardware Abstraction Layer (HAL), which is a lightweight runtime environment that provides a simple device driver interface for programs to communicate with the underlying hardware [7]. The HAL application program interface, or API, is integrated with the ANSI C standard library.

With a PC, an Altera FPGA and a JTAG download cable, it is possible to write programs for, and communicate with, any Nios II processor system. The Nios II processor's JTAG debug module provides a single, consistent method to communicate with the processor using a JTAG download cable. Accessing the processor is the same, regardless of whether a device only implements a Nios II processor system, or whether the Nios II processor is embedded deeply in a complex multiprocessor system. Furthermore, the Nios II EDS includes a flash programmer utility that allows to program flash memory chips on a target board [8].

### 2.3 ModelSim

ModelSim is a verification and simulation tool for VHDL, Verilog, SystemVerilog, and mixed-language designs [23]. The ModelSim includes a graphical user interface which consists of various windows that provides access to parts of the design and numerous debugging tools.

### 2.4 AVR Studio 4

The AVR Studio 4 is an Integrated Development Environment, IDE, for debugging AVR software [27]. The AVR Studio allows chip simulation, debugging and in-circuit emulation for the AVR family of microcontrollers. In addition, AVR Studio 4 provides a complete set of features, as well as target configuration and management, and full programming support for stand-alone programmers.

# Chapter 3

# Altera DE2 and Related Theory

In this chapter, different modules for the Altera Development and Education board are presented, in addition to the background theory for the VGA-control and the frame buffer.

#### 3.1 Features of the Altera DE2

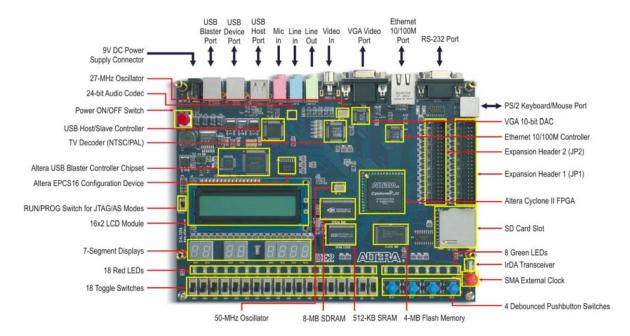

The Altera DE2 is a development board for test and design of systems. The development board has many features the designer may implement to improve the system functionality. Some of them are memory extensions like SRAM, SDRAM, flash memory and an SD-card socket [3]. For communication, the DE2 board has one USB host and one slave controller. It also provides RS-232, an IrDA transceiver, ethernet and the possibility for two expansion cards. The card also includes modules for audio and video implementation. For audio it is implemented a 24-bit CD quality audio codec. A VGA-module and a TV-decoder are included for video applications. The most important feature on the DE2 board is the Altera Cyclone II FPGA device that requires the Quartus II and Nios II Embedded Design suite for programming. The board has different switches and LEDs, plus a PS/2 connector for keyboard or mouse. In addition, it has a 2x16 digit LCD display and eight 7-segment displays. Figure 3.1 shows the Altera DE2 card and how the modules are placed.

When configuring the DE2 board there is an on board USB blaster that supports programming and user API control. These modules allow the user to implement a wide range of designed circuits, from simple circuits to various multimedia projects [3].

Figure 3.1: Altera DE2 Development and Education Board [3]

## 3.2 Altera Cyclone II 2C35

Cyclone II devices contain a two-dimensional row- and column-based architecture to implement custom logic [2]. Column and row interconnects of varying speed provide signal interconnects between logic array blocks, (LABs), embedded memory blocks, and embedded multipliers. The logic array consists of LABs, with 16 logic elements, (LEs) in each LAB. An LE is the smallest unit of logic in the Cyclone II architecture that provides efficient implementation of user logic functions. LABs are grouped into rows and columns across the device. The Cyclone II 2C35 FPGA includes 33,216 LEs [3].

The FPGA also contains 475 user I/O pins, a total memory of 105 M4K memory RAM blocks with 4608 bits in each block, 35 embedded multipliers and 4 PLLs. The M4K memory RAM blocks and the embedded multipliers are arranged in columns across the device. Cyclone II PLLs provide general-purpose clocking with clock synthesis and phase shifting as well as external outputs for high-speed differential I/O support [3].

#### 3.3 Nios II

The Nios II processor core is a soft-core central processing unit, CPU, that can be programed along with other hardware components that comprise the Nios II system onto an Altera FPGA [7].

#### 3.3. NIOS II

A Nios II processor system is equivalent to a microcontroller that includes a processor and a combination of peripherals and memory on a single chip [7]. A Nios II processor system consists of a Nios II processor core, a set of on-chip peripherals, on-chip memory, and interfaces to off-chip memory, all implemented on a single Altera device.

There are three different types of the Nios II core; economic, standard and fast. The Nios II/f fast core is designed for high execution performance[7]. Thus, the performance is gained at the expense of core size. The Nios II/s standard core is designed for small core sizes. Since the Nios II/s core uses less logic than the Nios II/f core, the execution performance drops by roughly 40%. The last one is the Nios II/e economy core. This core is designed to achieve the smallest possible core size. This core is roughly half the size of the Nios II/s core, but the execution performance is considerably lower [7].

With the Altera Nios II embedded processor, the system designer can accelerate timecritical software algorithms by adding custom instructions to the Nios II processor instruction set. When using custom instructions, it is possible to reduce a complex sequence of standard instructions to a single instruction implemented in hardware [4].

#### Interrupts

Like most microprocessors, the NIOS II supports interrupts [7]. Interrupts are a technique of diverting the processor from the execution of the current program so that it may deal with some event that has occurred [14]. Such an event may be an error from a peripheral, or simply that an I/O device has finished the last task it was given and is now ready for another.

Interrupts free the processor from having to continuously check the I/O devices to determine whether they require service [14]. Instead, the processor may continue with other tasks. The I/O devices will notify it when they require attention by asserting one of the processor's interrupt inputs.

When an interrupt occurs, the usual procedure is for the processor to save its state by pushing its registers and program counter onto the stack [14]. The processor then loads an interrupt-vector into the program counter. The interrupt-vector is the address at which an interrupt-service-routine (ISR) lies. Thus, loading the vector into the program counter causes the processor to begin execution of the ISR, performing whatever service the interrupting device requires. The last instruction of the ISR is always a return from interrupt instruction. This causes the processor to reload its saved state from the stack and resume its original program.

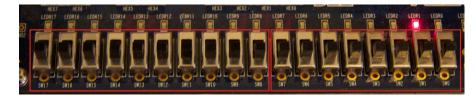

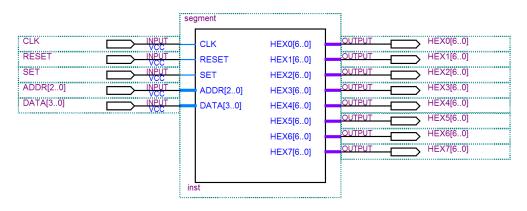

### **3.4 7-Segment Display**

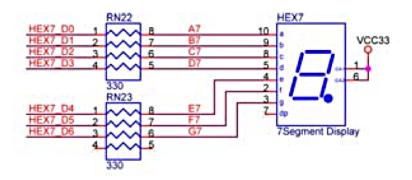

The 7-segment display is a package of seven LEDs [34]. The purpose of the 7-segment displays are to display information in form of numbers and some alphabetic characters. In addition, most 7-segment displays include a decimal point. Each segment needs one pin for cathode and one for anode. This means a total of sixteen pins for one single 7-segment display. To reduce the number of pins, common cathode or anode are usually applied. This reduces the number of pins to nine connections, one for each segment and one for power or ground.

The Altera DE2 Board has eight 7-segment displays [3]. These displays are arranged into two pairs and a group of four, with the intent of displaying numbers of various sizes. As indicated in the schematic in Figure 3.2, the seven segments are connected to pins on the Cyclone II FPGA. It is also worth mentioning that the dot in each display is unconnected and cannot be used. Each segment in a display is identified by an index from 0 to 6, with the positions given in Figure 3.3. Applying a low logic level to a segment causes it to light up, and applying a high logic level turns it off [3].

Figure 3.2: Schematic diagram of the 7-Segment Displays [3]

Figure 3.3: Position and index of each segment in a 7-Segment Display [3]

### 3.5 Monitor Control

VGA, or Video Graphics Array, is an analog video display port that is capable of displaying an unlimited number of colors by varying the level of red, green and blue per pixel on screen [31][19]. The VGA video signal contains five active signals. The horizontal sync and vertical sync are used for synchronization of the video, and three analog signals with range from 0.7V to 1.0V peak-to-peak are used to control the color. The color signals are often collectively referred to as the RGB signals.

#### 3.5.1 Video Display Technology

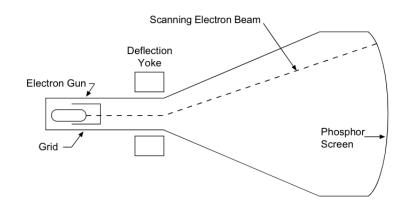

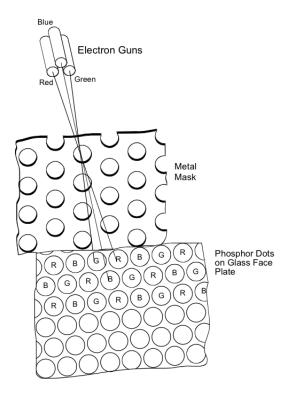

The major component inside early VGA computer monitors was the color CRT or Cathode Ray Tube shown in Figure 3.4 [19][10]. The electron beam must be scanned over the viewing screen in a sequence of horizontal lines to generate an image. The deflection yoke uses magnetic or electrostatic fields to deflect the electron beam to the appropriate position on the face of the CRT. The RGB color information in the video signal is used to control the strength of the electron beam. Light is generated when the beam is turned on by a video signal and it strikes a color phosphor dot or line on the face of the CRT. Figure 3.5 shows that the face of a color CRT contains a series of rows with three different phosphors. One type of phosphor is used for each of the primary colors of red, green and blue.

Figure 3.4: Color CRT [19]

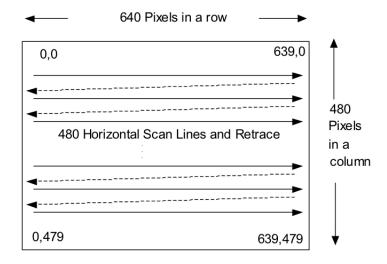

In standard VGA format, as seen in Figure 3.6, the screen contains 640 by 480 picture elements or pixels [19]. The video signal must redraw the entire screen 60 times per second to provide for motion in the image and to reduce flicker. This period is called the refresh rate. The human eye can detect flicker at refresh rates less than 30 to 60Hz.

To reduce flicker from interference from fluorescent lighting sources, refresh rates higher than 60 Hz at around 70Hz are sometimes used in PC monitors [19][10]. The color of each pixel is determined by the value of the RGB signals when the signal scans across each pixel. In 640 by 480-pixel mode, with a 60Hz refresh rate, this is approximately 40 ns per pixel. A 25MHz clock has a period of 40 ns. A slightly higher clock rate will produce a higher refresh rate.

Figure 3.5: Phosphor Dots on Face of Display [19]

Figure 3.6: VGA Image - 640 by 480 Pixel Layout [19]

#### 3.5. MONITOR CONTROL

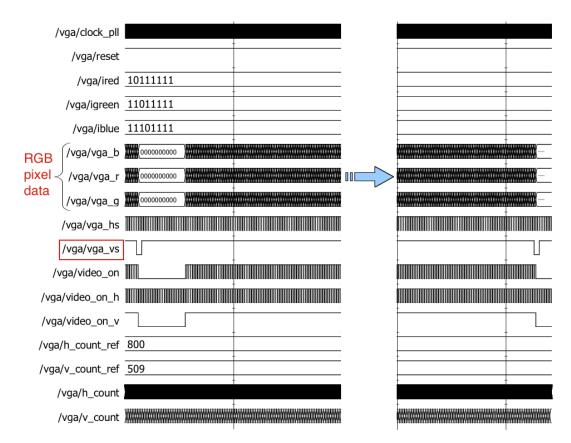

#### 3.5.2 Video Refresh

The screen refresh process seen in Figure 3.6 begins in the top left corner and "paints" 1 pixel at a time from left to right [19]. At the end of the first row, the row increments and the column address is reset to the first column. Each row is "painted" until all pixels have been displayed. Once the entire screen has been "painted", the refresh process begins again.

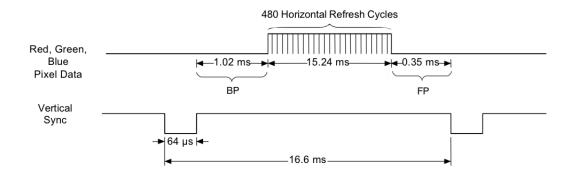

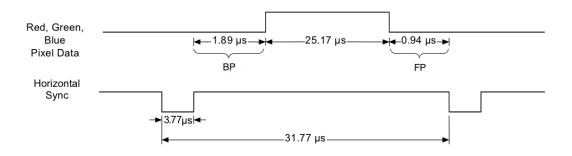

The following process describes how the video signal "paints" or refreshes each image [19]. The vertical sync signal, as shown in Figure 3.7, tells the monitor to start displaying a new image or frame, and the monitor starts in the upper left corner with pixel 0,0. The horizontal sync signal, as shown in Figure 3.8, tells the monitor to refresh another row of 640 pixels.

Figure 3.7: Vertical Sync Signal Timing for 640 by 480 at 60Hz [19]

Figure 3.8: Horizontal Sync Signal Timing for 640 by 480 at 60Hz [19]

After 480 rows of pixels are refreshed with 480 horizontal sync signals, a vertical sync signal resets the monitor to the upper left corner and the process continues [19]. The time when pixel data is not being displayed is called Back Porch and Front Porch. During this time, the beam is returning to the left column to start another horizontal scan and the RGB signals should all be set to the color black. This means all bits set to zero.

Many VGA monitors will shut down if the two sync signals are not the correct values [19]. Most PC monitors have an LED that is green when it detects valid sync signals and yellow when it does not lock in with the sync signals. Modern monitors will sync up to an almost continuous range of refresh rates up to their design maximum. In a PC graphics card, a dedicated video memory location is used to store the color value of every pixel in the display. This memory is read out as the beam scans across the screen to produce the RGB signals. There is not enough memory storage inside the current generation of FPGA chips, so for this approach, the FPGA must use external memory [19].

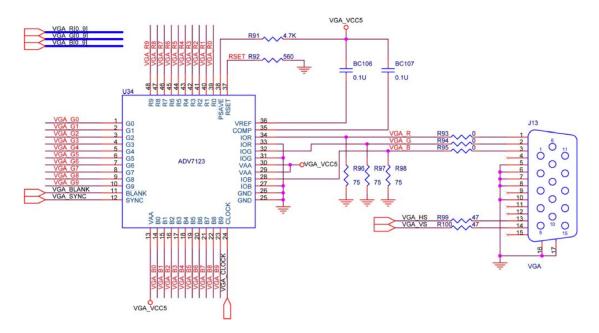

#### 3.5.3 ADV7123 VGA-DAC

The DE2 board includes a 16-pin D-SUB connector for VGA output [3]. The VGA synchronization signals are provided directly from the Cyclone II FPGA, and the Analog Devices ADV7123 triple 10-bit high-speed video DAC is used to produce the analog data signals red, green, and blue. Figure 3.9 shows the associated schematic for the VGA-DAC.

Figure 3.9: VGA circuit schematic [3]

The VGA-DAC supports multiple screen resolutions and refresh rates. The tables in Figure 3.10 and Figure 3.11, different screen resolutions, refresh rates and their horizontal or vertical timing specifications are shown. Table 3.1 explains the meaning of the letters a, b, c and d in these two figures.

| Character | Explanation                 |

|-----------|-----------------------------|

| a         | Horizontal or Vertical sync |

| b         | Back porch                  |

| с         | Display interval            |

| d         | Front porch                 |

Table 3.1: Explanation for letters in Figure 3.10 and Figure 3.11

| VGA             | Horizontal Timing Spec |       |       |       |       |       |            |

|-----------------|------------------------|-------|-------|-------|-------|-------|------------|

| Configuration   | Resolution(HxV)        | a(us) | b(us) | c(us) | d(us) | Pixel | clock(Mhz) |

| VGA(60Hz)       | 640x480                | 3.8   | 1.9   | 25.4  | 0.6   | 25    | (640/c)    |

| VGA(85Hz)       | 640x480                | 1.6   | 2.2   | 17.8  | 1.6   | 36    | (640/c)    |

| SVGA(60Hz)      | 800x600                | 3.2   | 2.2   | 20    | 1     | 40    | (800/c)    |

| SVGA(75Hz)      | 800x600                | 1.6   | 3.2   | 16.2  | 0.3   | 49    | (800/c)    |

| SVGA(85Hz)      | 800x600                | 1.1   | 2.7   | 14.2  | 0.6   | 56    | (800/c)    |

| XGA(60Hz)       | 1024x768               | 2.1   | 2.5   | 15.8  | 0.4   | 65    | (1024/c)   |

| XGA(70Hz)       | 1024x768               | 1.8   | 1.9   | 13.7  | 0.3   | 75    | (1024/c)   |

| XGA(85Hz)       | 1024x768               | 1.0   | 2.2   | 10.8  | 0.5   | 95    | (1024/c)   |

| 1280x1024(60Hz) | 1280x1024              | 1.0   | 2.3   | 11.9  | 0.4   | 108   | (1280/c)   |

Figure 3.10: VGA horizontal timing specification [3]

| VGA             | mode             | Vertical Timing Spec |          |          |          |  |  |

|-----------------|------------------|----------------------|----------|----------|----------|--|--|

| Configuration   | Resolution (HxV) | a(lines)             | b(lines) | c(lines) | d(lines) |  |  |

| VGA(60Hz)       | 640x480          | 2                    | 33       | 480      | 10       |  |  |

| VGA(85Hz)       | 640x480          | 3                    | 25       | 480      | 1        |  |  |

| SVGA(60Hz)      | 800x600          | 4                    | 23       | 600      | 1        |  |  |

| SVGA(75Hz)      | 800x600          | 3                    | 21       | 600      | 1        |  |  |

| SVGA(85Hz)      | 800x600          | 3                    | 27       | 600      | 1        |  |  |

| XGA(60Hz)       | 1024x768         | 6                    | 29       | 768      | 3        |  |  |

| XGA(70Hz)       | 1024x768         | 6                    | 29       | 768      | 3        |  |  |

| XGA(85Hz)       | 1024x768         | 3                    | 36       | 768      | 1        |  |  |

| 1280x1024(60Hz) | 1280x1024        | 3                    | 38       | 1024     | 1        |  |  |

Figure 3.11: VGA vertical timing specification [3]

#### 3.6 Memory

When the FPGA design uses external memory, it is common to use flash memory for permanently storage [14]. If the system needs a faster program memory, SRAM or SDRAM are commonly used.

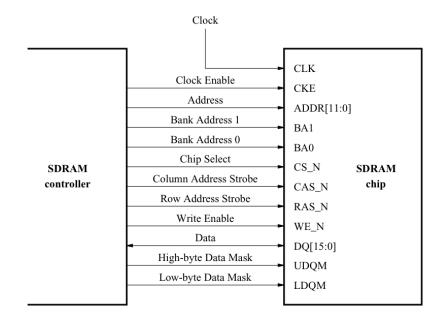

#### 3.6.1 IS42S16400 SDRAM

Synchronous Dynamic Random Access Memory (SDRAM) can be used as temporary memory for a system [14]. SDRAM is a volatile memory, meaning that the SDRAM lose its contents when the system loses power. The DRAM technologies uses arrays of what are essentially capacitors to hold individual bits of data. The capacitor arrays will hold their charge only for a short period before it begins to diminish. Thus, The SDRAM need continuous refreshing, every few milliseconds or so.

The SDRAM chip on the Altera DE2 board has the capacity of 64 Mbits, or 8 Mbytes. It is organized as 1M x 16 bits x 4 banks [18]. The signals needed to communicate with this chip are shown in Figure 3.12. All of the signals, except the clock, can be provided by an SDRAM controller that may be generated through the SOPC builder. The clock signal has to meet the clock-skew requirements of the SDRAM, and can be provided by a PLL.

Figure 3.12: The SDRAM Signals [5]

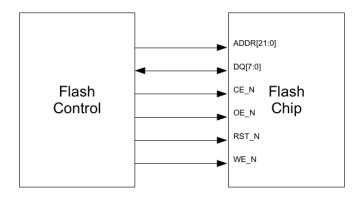

#### 3.6.2 S29AL032D Flash Memory

Flash is a nonvolatile memory, meaning that it do not require any power to retain its content [14]. The primary purpose for flash is to hold system code and other data the system needs to be present at power-up. The reason why this technology is not used as program memory, is because it is generally slower than RAM.

The Altera DE2 board contains a flash memory that may store up to 4 Mbytes of data, and is organized as 4M x 8 bits [32]. The signals needed for communicating with the flash memory chip can be generated by the SOPC builder. A figure of this communication interface is shown in Figure 3.13.

Figure 3.13: The Flash Memory Signals [32]

HAL, as described in Section 2.2, provides a simple interface for reading and writing to the flash memory[7]. With these methods it is possible to read and write bytes anywhere in the flash memory. In addition, Altera provides a read-only zip file system also for use with the HAL. The read-only zip file system provides access to a simple file system stored in flash memory. The flash drivers take advantage of the HAL generic device driver framework for file subsystems. Therefore, it is possible to access the zip file subsystem using the ANSI C standard library I/O functions, such as fopen() and fread().

#### 3.6.3 Frame Buffer

Almost all graphic systems are raster based [10]. A picture is produced as an array of picture elements, or pixels, within the graphic system. Collectively, the pixels are stored in a part of memory called the frame buffer. The frame buffer can be viewed as the core element of a graphic system. The resolution of the frame buffer, that is the number of pixels in the frame buffer, determines the detail that it is possible to see in the image. The depth, or precision, of the frame buffer, defined as the number of bits that are used for each pixel, determines properties such as how many colors can be represented on a given system. For example, a 1-bit deep frame buffer allows only two colors, whereas an

8-bit deep frame buffer allows  $2^8$ , or 256, colors. In full-color systems, there are at least 24 bits per pixel. Such systems can display sufficient colors to represent most images realistically. They are also called RGB-color systems, because individual groups of bits in each pixel are assigned to each of the tree primary colors; red, green and blue, used in most displays [10].

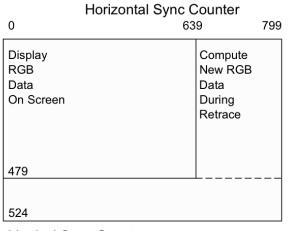

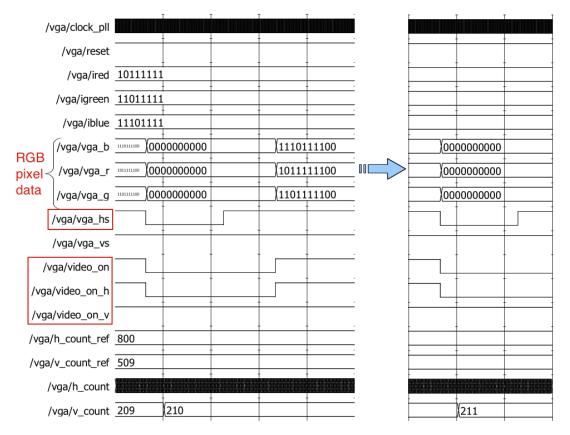

The frame buffer is usually implemented with special types of memory chips that enables fast redisplay of the contents of the frame buffer [10]. Pixel memory must always be in read mode whenever RGB data is displayed [19]. To avoid flicker and memory access conflicts on single port memory, designs should update pixel RAM and other signals that produces the RGB output, during the time the RGB data is not being displayed. When the scan of each horizontal line is complete, there are typically over 100 clock cycles before the next RGB value is needed, as seen in Figure 3.14. Additional clocks are available when a vertical sync signal resets the monitor to the first display line. The exact number of clocks available depends on the video resolution and refresh rate. In most cases, calculations that change the video image should be performed during this off-screen period of time to avoid memory conflicts with the readout of video RAM or other registers which are used to produce the RGB video pixel color signals [19].

Vertical Sync Counter

Figure 3.14: Display and Compute clock cycles available in a 640 by 480 Video Frame [19]

## Chapter 4

# Atmel AVR STK600 and Domain Conversion

In this chapter the Atmel AVR STK600 and the microcontroller AT90USB1287 are presented, in addition to theory of domain conversion for analog and digital signals.

## 4.1 Features of the STK600

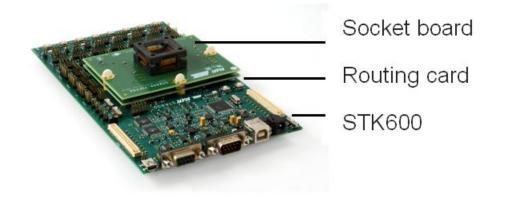

The Atmel AVR STK600 is a complete starter kit and development system for the AVR and AVR32 flash microprocessors from ATMEL Corporation [11]. It is designed to give designers a quick start to develop code on the AVR, combined with advanced features for using the starter kit to prototype and test new designs. The STK600 is programmed using USB communication to PC, in addition, it supports communication interfaces for data exchange, such as CAN, RS232 and USB-client. The developments board also includes buttons and LEDs as user interface. The STK600 provides the opportunity to use most of the AVR microprocessors through different routing cards and socket boards. Figure 4.1 shows a picture of the different modules and how they are placed according to each other [11].

## 4.2 AVR AT90USB1278 Microcontroller

The Atmel AVR AT90USB1287 is an 8-bit microprocessor based on RISC architecture [12]. The microcontroller provides features like ten PWM channels, one Universal Synchronous and Asynchronous serial Receiver and Transmitter (USART), an 8-channels 10-bit ADC, master and slave SPI, and USB. The microcontroller does also support enabling of interrupt on communication interfaces and I/O pins. Interrupt is described in Section 3.3. Furthermore, both USB and SPI will be presented in Chapter 5

Figure 4.1: STK600 socket and routing system [11]

#### 4.2.1 Analog to Digital Conversion

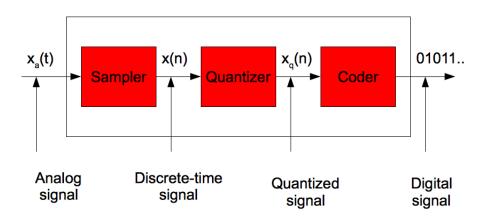

Most signals of practical interest, such as speech, radar signals, sonar signals and various communications signals such as audio and video signals, are analog [29]. To process analog signals by digital means, it is first necessary to convert them into digital form, that is, to convert them to a sequence of numbers having finite precision. This procedure is called analog-to-digital-, or A/D-conversion, and the corresponding devices are called ADCs. The A/D conversion can be described in a three-step process. Figure 4.2 illustrates this process [29].

Figure 4.2: Basic parts of an analog-to-digital converter [29]

- 1. Sampling: This is the conversion of a continuous time signal into a discrete time signal obtained by taking samples of the continuous time signal at discrete time instants. Thus, if  $x_a(t)$  is the input to the sampler, the output is  $x_a(nT) \equiv x(n)$ , Where T is called the sampling interval.

- 2. Quantization: This is the conversion of a discrete time continuous valued signal

#### 4.2. AVR AT90USB1278 MICROCONTROLLER

into a discrete time, discrete-valued, digital signal. The value of each signal sample is represented by a value selected from a finite set of possible values. The difference between the unquantized sample x(n) and the quantized output  $x_q(n)$  is called the quantization error.

3. Coding: In the coding process, each discrete value  $x_q(n)$  is represented by a bit binary sequence.

Although we model the ADCs as a sampler followed by a quantizer and coder, in practice the A/D conversion is performed by a single device that takes  $x_a(t)$  and produces a binary-coded number [29]. The operations of sampling and quantization can be performed in either order, but in practice, sampling is always performed before quantization.

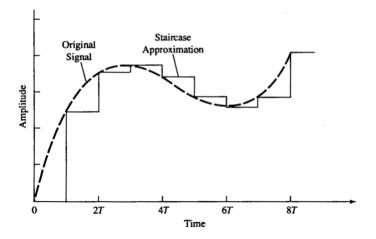

#### 4.2.2 Digital to Analog Conversion

In many cases of practical interest, for example speech processing, it is desirable to convert the processed digital signals into analog form [29]. The process of converting a digital signal into the analog domain is known as digital to analog conversion, D/A Conversion. All digital to analog converters (DACs), "connects the dots" in a digital signal by performing some kind of interpolation, whose accuracy depends on the quality of the D/A conversion process. Figure 4.3 illustrates a simple form of D/A conversion, called a zero-order hold or a staircase approximation [29]. The original signal is the input signal to ADC, and the staircase approximation is the output of the same signal after both an AD- and DA-conversion. Before the staircase approximated signal is used, it is sent through a filter to smooth up the edges.

Figure 4.3: Zero-order hold D/A conversion [29]

#### 4.2.3 Pulse Width Modulation

Using a DAC may seem the obvious way to generate an analog output voltage from a digital system, but there is another way that uses noting more than a digital I/O line configured as an output [14]. This technique is known as Pulse Width Modulation (PWM).

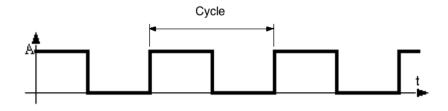

**Figure 4.4:** 50% duty cycle [14]

Consider the average square wave shown in Figure 4.4. The width of the logic high is equal to the width of the logic low, so this wave is said to have a 50% duty cycle. In other words, it is high for exactly half the cycle. If the amplitude A of this square wave is 5V, the average voltage over the cycle is 2,5V [14].

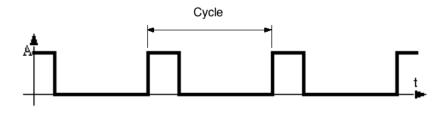

Figure 4.5: 25% duty cycle [14]

Now consider the square wave in Figure 4.5. This wave has a 25% duty cycle, which means that the average voltage over the cycle is 1,25V. An averaging filter, like a low-pass filter, on the PWM output will convert the pulses to an analog voltage, proportional to the duty cycle of the PWM signal. By varying the duty cycle it is possible to vary the analog voltage [14].

## Chapter 5

## **Communication Interface**

A communication interface is included in both the Altera DE2 and the Atmel AVR STK600. Thus, the theory for this implementation is presented in this chapter.

## 5.1 Serial Peripheral Interface

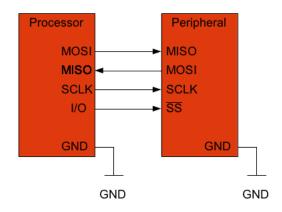

SPI, or Serial Peripheral Interface, is a synchronous protocol in which all transmissions are referenced to a common clock generated by the master processor [14]. SPI is used for data storage in memory, in peripherals like ADCs and DACs, and even between processors. The receiving peripheral, or slave, uses the clock to synchronize incoming bits of the serial bit stream, thus the data rate is decided by the master clock. Many chips may be connected to the same SPI interface of a master. A master selects a slave to receive by asserting the slave's chip select input. A peripheral that is not selected will not take part in a SPI transfer.

| Signal                                               | Description                 |

|------------------------------------------------------|-----------------------------|

| MOSI                                                 | Master Out Slave In         |

| MISO                                                 | Master In Slave Out         |

| SCLK or SCK                                          | Serial Clock                |

| $\overline{\mathbf{CS}}$ or $\overline{\mathbf{SS}}$ | Chip Select or Slave Select |

Table 5.1:SPI signals [14]

In Table 5.1, the four main SPI signals are shown [14]. MOSI is generated by the master and is received by the slave. MISO is produced by the slave, but its generation is controlled by the master. The chip select to the peripheral is normally generated by simply using a spare pin on the master. Figure 5.1 shows a microprocessor interfaced to a peripheral using SPI.

Figure 5.1: Basic SPI interface [14]

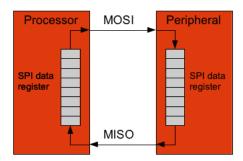

Both master and slave contains a serial shift register [14]. The master starts a transfer of a byte by writing it to its SPI shift register. As the register transmits the byte to the slave on the MOSI signal line, the slave transfers the contents of its shift register back to the master on the MISO signal line. In this way, the contents of the two shift registers are exchanged. Both a write and a read operation are performed simultaneously. Figure 5.2 illustrates this process.

Figure 5.2: SPI transmission [14]

If only a write operation is desired, the master just ignores the byte it receives [14]. On the other hand, if the master wishes to read from the slave, it must transfer a dummy byte to initiate a slave transmission.

## 5.2 Universal Serial Bus

Universal serial bus, or USB, is a high speed bus that allows up to 127 peripherals to be connected to a host, at a data rate of 480Mbps [14]. USB allows peripherals and computers to interconnect in a standard way with a standard protocol. In addition,

#### 5.2. UNIVERSAL SERIAL BUS

USB can provide power to the peripherals connected to the host through the same cable as they use for communication. Since peripherals are able to self-identify to a host computer, the USB is popular among devices like printers, cameras, mice and keyboards. However, this is also why the developing with USB is more complex than with for example SPI. USB add an extra layer of complexity to the software, since the system must interact with the host in the appropriate way.

| Signal    | Purpose                 |

|-----------|-------------------------|

| $V_{BUS}$ | USB device $power(+5V)$ |

| D+        | Differential data line  |

| D-        | Differential data line  |

| GND       | Power and signal ground |

Table 5.2:USB Signals [14]

The USB standard uses a shielded, four-wire cable to interconnect devices on the network [14]. As shown in Table 5.2, the data transmission is accomplished over a differential twisted pair D+ and D-. The other two wires are  $V_{BUS}$ , which carries power to USB devices, and GND.

## CHAPTER 5. COMMUNICATION INTERFACE

## Chapter 6

## **Electronic Components**

In this chapter the basic electronic components; resistor, transistor, LED and LDR are presented. In addition the Ohm's law and voltage division is described.

### 6.1 Resistor

Resistance is the capacity of materials to impede the flow of current or, more specifically, the flow of electric charge [26]. The circuit element used to model this behavior is the resistor, and it is measured in ohm  $(\Omega)$ .

#### 6.1.1 Ohm's law

For purposes of circuit analysis, it is important to reference the current in the resistor to a terminal voltage [26]. This can be done in two ways, either in the direction of the voltage drop across the resistor or in the direction of the voltage rise across the resistor. If the first method is chosen the relationship between the voltage and current is shown in Equation (6.1), and the second is shown in Equation (6.2).

$$v = i \cdot R, \tag{6.1}$$

$$v = -i \cdot R, \tag{6.2}$$

In these equations v represents voltage measured in volts, i represents current measured in amperes and R represents resistance measured in  $\Omega$ . These equations are called Ohm's law [26].

#### 6.1.2 Voltage divider

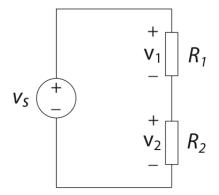

When voltage is divided between series resistors, as shown in Figure 6.1, the voltage across each resistor can be found according to the Equation (6.3) and (6.4) [26].

$$v_1 = \frac{R_1}{R_1 + R_2} \cdot v_s \tag{6.3}$$

$$v_2 = \frac{R_2}{R_1 + R_2} \cdot v_s \tag{6.4}$$

Figure 6.1: Voltage divider [26]

### 6.2 Transistor

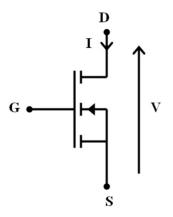

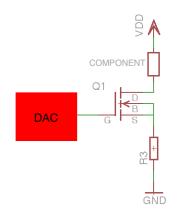

The MOSFET transistor has three signal terminals: Gate (G), drain (D) and source (S), plus the bulk terminal (B), to which the gate, drain and source voltages are referenced [30]. In Figure 6.2 the three signal terminals are shown.

The simplest view of MOSFET logic operation treats the transistor as a switch. The gate terminal is analogous to the light switch on the wall. When the gate has a sufficient high voltage, the transistor closes like a switch, and the drain and source terminals are electrically connected. Just as a light switch requires a certain force level to activate it, the transistor needs a certain voltage level to connect the drain and source terminals. This voltage is called the transistor threshold voltage  $V_t$ , and is a fixed voltage.

Transistors act as switches with two conducting states, on and off, depending on the control (Gate) terminal voltage. An ideal transistor has a zero ohm resistance between the drain and source when it is in the on-state, and an infinite resistance between these terminals in the off-state [30].

32

Figure 6.2: MOSFET transistor with signal terminals [30]

## 6.3 Light Dependent Resistor

A light dependent resistor (LDR) consists of a disc of semiconductor material with two electrodes on its surface [13].

When dark or in dim light, the material of the disc contains relatively few free electrons, thus there are few electrons to carry electric charge. This means that it is a poor conductor of electric current, thus its resistance is high. In contrast, with more light, a larger number of electrons escape from the atoms of the semiconductor. Thus there are more electrons to carry electric charge and it becomes a good conductor, which means its resistance is low. The more light, the more electrons, the lower resistance [13].

### 6.4 Light Emitting Diode

Light emitting diodes, usually known as LEDs, provideslight when a current flows through them [13]. A typical LED is in a domed plastic package with a rim. There are two terminal wires at the bottom, and usually the cathode wire is shorter than the anode wire.

An LED needs about 20 mA to be lit to its full brightness, though as little as 5 mA still produces a clearly visible glow. The forward voltage drop of an LED averages about 1.5V, so a 2 V supply will light most types to their maximum brightness. When lit by a higher voltage, the LED may be burned out if the forward voltage across it exceeds 2V. It is thus essential to wire a current limiting resistor in series with it[13].

## CHAPTER 6. ELECTRONIC COMPONENTS

## Chapter 7

## Numerical Systems

A numbering system is a mechanism used for representing numeric values. In today's society, people most often use the decimal numbering system while most computers uses binary representation. In this chapter, the general positional number system is explained. Further, the hexadecimal and binary number systems are introduced together with an introduction to the conversion between them.

### 7.1 Positional Number Systems

To understand the binary number system used in computer design, it is important to recognize that the number system used in our every day life is a positional number system [22]. In such a system, any number is represented by a string of digits in which the position of each digit has an associated weight. The value of a given number, then, is equivalent to the weighted sum of all its digits. An example of this is shown in Equation (7.1).

$$1234 = 1 \cdot 1000 + 2 \cdot 100 + 3 \cdot 10 + 4 \cdot 1 \tag{7.1}$$

In this example, each weight is a power of 10 that is equal to  $10^i$ , where *i* corresponds to the digit's position counting from the right [22]. In general, any decimal number D of the form  $d_3d_2d_1d_0$  has the value  $D = d_3 \times 10^3 + d_2 \times 10^2 + d_1 \times 10^1 + d_0 \times 10^0$ . Here, 10 is called the radix of the number system. In a general positional, the radix may be any integer *r*, and a digit in position *i* then has the weight  $r^i$ . Thus, a general system can be described with Equation (7.2) where m is the total of digits. Equation (7.3) shows that the value of this number is the sum of products of each digit multiplied by the corresponding power of the radix.

$$d_{m-1}d_{m-2}\cdots d_1d_0\tag{7.2}$$

$$D = \sum_{0}^{m-1} d_i \cdot r^i \tag{7.3}$$

In positional number systems the leftmost digit is called the most-significant digit (MSD) and the rightmost is the least-significant digit (LSD).

## 7.2 The Binary Number System

Since digital systems use binary digits, binary radix is used to represent any given number in a digital system [22][20]. Equation (7.4) shows the general form of such a binary number, and Equation (7.5) represent the equivalent to its value.

$$b_{m-1}b_{m-2}\cdots b_1b_0\tag{7.4}$$

$$B = \sum_{0}^{m-1} b_i \cdot 2^i$$

(7.5)

When working with other non-decimal numbers, it is common to use a subscript to indicate the radix of each number, although the radix is often clear from the context [22][15]. Equation (7.6) and Equation (7.7) shows some examples of binary numbers and their decimal equivalents.

$$10101_2 = 1 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0 = 21_{10}$$

(7.6)

$$110101_2 = 1 \cdot 2^5 + 1 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 0 \cdot 2^1 + 1 \cdot 2^0 = 53_{10}$$

(7.7)

## 7.3 The Hexadecimal Number System

The hexadecimal number system uses radix 16, and is often used to provide convenient shorthand representations for binary numbers, reducing the need for long strings of binary digits [22][15]. Since the hexadecimal number system needs to express sixteen different values, it uses the digits 0 through 9 and supplements with the letters A through F.

The rules for positional number systems also applies for the hexadecimal number system. Equation (7.8) shows an example of hexadecimal numbers and their decimal equivalent.

$$12EF_{16} = 1 \cdot 16^3 + 2 \cdot 16^2 + 14 \cdot 16^1 + 15 \cdot 16^0 = 4847_{10}$$

(7.8)

| Decimal | Binary | Hexadecimal  |

|---------|--------|--------------|

| 0       | 0      | 0            |

| 1       | 1      | 1            |

| 2       | 10     | 2            |

| 3       | 11     | 3            |

| 4       | 100    | 4            |

| 5       | 101    | 5            |

| 6       | 110    | 6            |

| 7       | 111    | 7            |

| 8       | 1000   | 8            |

| 9       | 1001   | 9            |

| 10      | 1010   | А            |

| 11      | 1011   | В            |

| 12      | 1100   | $\mathbf{C}$ |

| 13      | 1101   | D            |

| 14      | 1110   | E            |

| 15      | 1111   | $\mathbf{F}$ |

| 16      | 10000  | 10           |

| 17      | 10001  | 11           |

| 18      | 10010  | 12           |

In Table 7.1, the hexadecimal numbers from 0 through 12 with there decimal and binary equivalents are shown [22].

Table 7.1: Different representation of numbers 0 through 18

### 7.4 Conversion Between Number Systems

Different number systems for different occasions are useful. But before a computer presents a decimal number or a designer programs low-level code, they need to know how to convert between the different number systems.

#### 7.4.1 Conversion From Binary

It is very easy to convert a binary number to a hexadecimal form [22][15]. Starting at the LSB and working left with separating bits in groups of 4 and replace each group with the corresponding hexadecimal digit in Table 7.1. An example of this is shown in Equation (7.9). In this example, zeroes are added to the left to make the total number of bits a multiple of 4.

$$1010011100_2 = 0010\ 1001\ 1100 = 29C_{16} \tag{7.9}$$

Conversion from binary to decimal was introduced in Equation (7.6) and Equation (7.7), and these equations are derived from Equation (7.5) with m = 4 and m = 5 respectively [22][20]. As seen in the equations each digit is multiplied with the corresponding power of the radix.

#### 7.4.2 Conversion From Hexdecimal

The conversion between hexadecimal and binary is as easy as the conversion from binary to hexadecimal. Each hexadecimal digit are replaced by the corresponding 4 bits in Table 7.1 [22]. Equation (7.10) shows an example of this conversion.

$$7E5D_{16} = 0111\,1110\,0101\,1101 = 1111110010111101_2 \tag{7.10}$$

The progress to obtain the decimal value from a hexadecimal number, is the same as for the binary number [22][15]. The Equation (7.3) can modified to Equation (7.11), where r is the hexadecimal radix 16, and m indicates the number of digits. The example in Equation (7.8) is derived from Equation (7.11).

$$D = \sum_{0}^{m-1} h_i \cdot 16^i \tag{7.11}$$

#### 7.4.3 Conversion From Decimal

Equation (7.3) can be rewritten as Equation (7.12). This can be used when converting a decimal number D to a number in radix r [22][20].

$$D = ((\cdots ((d_{m-1})r + d_{m-2})r + \cdots)r + d_1)r + d_0$$

(7.12)

If Equation (7.12) is divided by r, the parenthesized part of Equation (7.12) represents the quotient in Equation (7.13) while the rest is the remainder shown in Equation (7.14) [22].

$$Q = (\cdots ((d_{m-1})r + d_{m-2})r + \cdots)r + d_1$$

(7.13)

$$R = d_0 \tag{7.14}$$

In other words,  $d_0$  is obtained as a remainder of the division of D by r [22]. Furthermore, since the quotient Q in Equation (7.13) has the same form as the original number, it is known that successive division by r yields successive digit of D from right to left until all

the digits of D have been derived. Equation (7.15) and Equation (7.16) show an example how conversion between decimal and binary, and decimal and hexadecimal respectively are done.

$$179 \div 2 = 89 \qquad remainder \ 1 \ (LSB) \\89 \div 2 = 44 \qquad remainder \ 1 \\44 \div 2 = 22 \qquad remainder \ 0 \\22 \div 2 = 11 \qquad remainder \ 0 \\11 \div 2 = 5 \qquad remainder \ 1 \\5 \div 2 = 2 \qquad remainder \ 1 \\2 \div 2 = 1 \qquad remainder \ 1 \\2 \div 2 = 1 \qquad remainder \ 0 \\1 \div 2 = 0 \qquad remainder \ 1 \ (MSB) \\Thus, 179_{10} = 10110011_{2}$$

$$\begin{array}{rcl} 3417 \div 16 &=& 213 & remainder & 9 \ (LSB) \\ 213 \div 16 &=& 13 & remainder & 5 \\ 13 \div 16 &=& 0 & remainder & 13 \ (MSB) \\ Thus, \ 3417_{10} &=& D59_{16} \end{array}$$

(7.16)

## CHAPTER 7. NUMERICAL SYSTEMS

## Chapter 8

## System Modules and Scenarios

This chapter presents an overview of the system and the two example scenarios. The supporting theory of the development boards, namely the Altera DE2 and the Atmel AVR STK600 may be found in Chapter 3 and Chapter 4 respectively. Furthermore, the scenario theory can be found in Chapter 6 and Chapter 7.

## 8.1 Overview of System

The purpose for this embedded demonstrator is to teach basic circuit theory and demonstrate how a selection of simple circuits work. The parameters; area, power and performance have no restriction in this system except the limitations of resources on the Altera Development and Education Board and the microprocessor on the Atmel AVR STK600. The demonstrator includes different interactive scenarios that the user may choose between through a user interface. Each scenario has a topic that it tries to convey through the system interface.

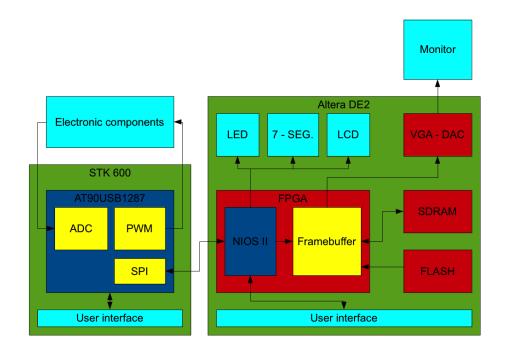

As seen in Figure 8.1, this system consists of three modules; a monitor, an Altera DE2 and an Atmel STK600. The purpose for the monitor is to show information about the current scenario, and at the same time display images of virtual circuits. In these scenarios the voltages and currents in the virtual circuit are changing depending on how the user operates the system. The monitor is connected to a VGA-DAC onboard the Altera DE2.

As mentioned in Chapter 2, both the hardware and software were chosen based on their availability at the department, and the design tools already familiar. However, a dedicated circuit board was thought of as an alternative to the Atmel STK600. The implementation of this dedicated board would have to be produced from scratch, thus the implementation of the Atmel STK600 was both easier and faster.

The Altera DE2 is the master communication device that controls both the monitor

Figure 8.1: System overview

and the STK600. In addition, it includes a user interface and a memory-controller that controls a frame buffer.

The purpose for the last module, the Atmel STK 600, is reading and writing to analog electrical components using ADC and PWM. These electrical components are used in different scenarios, and are chosen from the Altera Development and Education Board. This module also includes a user interface which is controlled from the microprocessor mounted on the STK 600.

## 8.2 Overview of Scenarios

The system is designed as a platform for easy implementation of scenarios. Through the use of methods in both hardware and software, a developer can control both the interface and the behavior of the system. This section describes two, already implemented, scenarios that uses different modules in the system.

### 8.2.1 Automatic Adjustment of Light

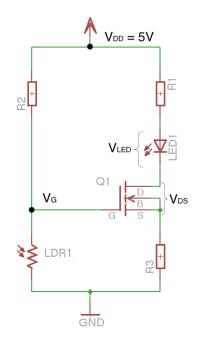

One of the scenarios implemented is the automatic adjustment of light. The topics for this scenario are Ohm's law and voltage dividing presented in Chapter 6, in addition to the basic functionality of a transistor, a LDR and a LED.

#### 8.2. OVERVIEW OF SCENARIOS

In Figure 8.2, the virtual circuit of this scenario is shown. This circuit along with supporting theory are displayed on the system monitor. Depending on the amount of light surrounding the LDR, the brightness of the LED will vary. If the light intensity on the LDR increases, the brightness of the LED will decrease. On the other hand, if the light intensity on the LDR decreases, the brightness of the LED will increase. The analog circuits do not exist in the system, it is the soft processor, the Nios II, that simulates both the voltages and currents in the virtual circuits. The LDR and LED are controlled by the ADC and PWM respectively, implemented on Atmel's STK600.

Figure 8.2: Automatic adjustment of light

In a real analog circuit, the reduction of resistance caused by an increase in brightness, and the voltage dividing between R2 and LDR, would decrease the voltage between ground and gate,  $V_G$ , on the transistor Q1. Thus, the voltage between gate and source,  $V_{GS}$ , decreases. This causes the voltage between drain and source,  $V_{DS}$ , to increase, thus the voltage over LED will decrease and the light will fade out. On the other hand, if the light intensity on the LDR increases, the  $V_G$ , and  $V_{GS}$ , will increase. This causes the  $V_{DS}$  to decrease, and the voltage over the LED will increase and thus its light intensity, will increase.

This scenario is considered to be a good demonstrator due to its ability to demonstrate how a relatively simple electrical circuit provides a functionality present in many well known electronic devices. In mobile phones, a circuit like this may be used to turn the LCD-display of the device off when the user holds the phone to his or her ear. Thus, the Automatic Adjustment of Light scenario provides a good demonstration of topics related to the user's everyday life.

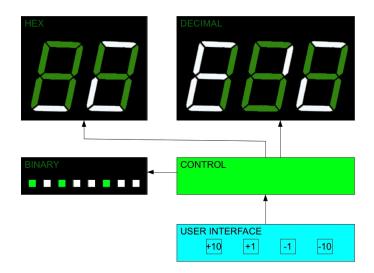

#### 8.2.2 How to Count in Binary, Hexadecimal and Decimal