## Embedded Demonstrator for Video Presentation and Manipulation

Cato Marwell Jonassen

Master of Science in Electronics Submission date: June 2010 Supervisor: Per Gunnar Kjeldsberg, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Problem Description**

In many situations, like school visits at NTNU, Forskningstorget and Elektronikk-& telekommunikasjonsdagen, it is desirable for Department of Electronics and Telecommunication to demonstrate good examples of electronic systems. Embedded systems are well suited as demonstrators since the combination of hardware and software gives both flexibility and wide possibilities for optimization.

In this task, the student will implement a specified system for demonstration of topics related to courses provided by the department. In order to make a good demonstration, necessary presentation material is also to be made, together with a plan on how to demonstrate the embedded system.

Assignment given: 15. January 2010 Supervisor: Per Gunnar Kjeldsberg, IET

## Abstract

In this master thesis there has been implemented an embedded demonstrator for video presentation and manipulation, based on the specification presented in the project thesis written last semester. The demonstrator was created with the intention of being used by Department of Electronics and Telecommunication in situations where the department needed good examples of electronic systems. These systems can be used to motivate, educate and possibly recruit new students.

By combining the use of video as a motivational medium with a practical approach to the theory, the demonstrator is designed to emphasize the importance of hardware/software codesign in electronic systems. The demonstrator is designed with a combination of dedicated hardware modules and the Nios II/f embedded soft processor from Altera. Video is processed in both hardware and software to demonstrate the difference in obtainable video quality. A measured frame rate of 25 fps in hardware and less than 1 fps in software is considered to be a good demonstration of the difference in processing power. An additional color processing demonstration is also created to visually demonstrate the performance differences when processing colors using software versus using custom floating-point instructions. It is concluded that an average performance increase of 300% is archived when using custom instructions, which is concidered to be noticeable visually. A poster with the necessary theory, usage guidelines and results has been created to support the demonstration together with a plan of how the demonstration should be performed based on the age and educational background of the observer.

The embedded demonstrator was implemented using the Altera DE2 platform in combination with the TRDB D5M camera and hardware description from Terasic.

## Preface

One of the most important reasons for choosing this task for my master thesis was that it gave me the possibility to use the theory and knowledge I have gained over the years here at NTNU to make something useful and practical. I also believed that the design task would be a good preparation for the challenges I will meet when I start working. I have always been fascinated by electronics and the wide area of application this technology presents. Since my interests include both computers and different forms of visual media, this project became a great opportunity to combine my interest and education. This combination is in my opinion the most effective and motivating way to learn new things.

The task of implementing and creating an embedded demonstrator system has been both challenging and rewarding. It is always frustrating when not even the simplest things work as they are supposed to, but it is an even bigger reward when one finally solves the problem. One of the biggest challenges this past semester has been time. It is not easy to predict how much time it will take to get things to work the way they are are supposed to. This has been a very intense semester, especially the last couple of months. But now, when I am finished, I look back and see it all as a very exciting time from which I have learned a lot, and even got to create a new system. I have learned a lot about embedded systems, hardware/software codesign, cameras and video and much more. The Altera DE2 platform was a very good platform to work with and it gave room much creativity. I have created the embedded demonstrator by using Terasic's existing camera hardware platform, and I have also used much of the theory from the project in this master thesis.

This project would not have been possible without all the help and support I have received. I would like to thank my supervisor, Professor Per Gunnar Kjeldsberg for all the support, help and fresh perspectives I have gotten. I would also like to thank my two best friends Jarle Larsen and Kai Andre Venjum, for sticking with me, through thick and thin. Thanks for all the constructive discussions, shared knowledge and all the fun we have had together when creating our systems. Finally, I would also like to give my thanks to my better half, Tia. Without your great support, optimism and interest, this would not have been possible.

> Cato Marwell Jonassen NTNU, Trondheim June 2010

## Contents

| 1          | Intr<br>1.1<br>1.2<br>1.3                                                   | roduction         Preliminary Work         Description         Main Contributions | 1<br>2<br>3<br>3                                                |

|------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------|

| <b>2</b>   | $\mathbf{Em}$                                                               | bedded Processors                                                                 | 4                                                               |

|            | 2.1                                                                         | About the Embedded Processor                                                      | 5                                                               |

|            | 2.2                                                                         | Nios II                                                                           | 7                                                               |

|            | 2.3                                                                         | Interrupt                                                                         | 10                                                              |

|            | 2.4                                                                         | Performance                                                                       | 12                                                              |

| 3          | Har                                                                         | rdware/Software Codesign                                                          | 15                                                              |

|            | 3.1                                                                         | Embedded Systems and HW/SW Codesign                                               | 16                                                              |

|            | 3.2                                                                         | Hardware Acceleration and Custom Instructions                                     | 17                                                              |

|            |                                                                             | 3.2.1 Custom Instructions                                                         | 17                                                              |

|            |                                                                             | 3.2.2 Hardware Acceleration                                                       | 18                                                              |

|            |                                                                             |                                                                                   |                                                                 |

| 4          | Vid                                                                         | eo and Images                                                                     | 20                                                              |

| 4          | <b>Vid</b><br>4.1                                                           | eo and Images<br>Resolution, frame rate and compression                           | <b>20</b><br>20                                                 |

| 4          |                                                                             |                                                                                   |                                                                 |

| 4          | 4.1                                                                         | Resolution, frame rate and compression                                            | 20                                                              |

| 4          | 4.1                                                                         | Resolution, frame rate and compression                                            | 20<br>21                                                        |

| 4          | 4.1                                                                         | Resolution, frame rate and compression                                            | 20<br>21<br>23                                                  |

| 4          | 4.1                                                                         | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24                                            |

| 4          | 4.1<br>4.2                                                                  | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24<br>24                                      |

| 4          | 4.1<br>4.2                                                                  | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24<br>24<br>25                                |

| 4          | 4.1<br>4.2                                                                  | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24<br>24<br>25<br>25<br>25                    |

| <b>4 5</b> | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                   | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24<br>24<br>25<br>25<br>26                    |

| -          | <ul><li>4.1</li><li>4.2</li><li>4.3</li><li>4.4</li></ul>                   | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24<br>24<br>25<br>25<br>26<br>28              |

| -          | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Too</li> </ul> | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24<br>24<br>25<br>25<br>26<br>28<br><b>29</b> |

| -          | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Too</li> </ul> | Resolution, frame rate and compression                                            | 20<br>21<br>23<br>24<br>24<br>25<br>25<br>26<br>28<br><b>29</b> |

|    | 5.3  | Nios II Embedded Design Suite                                                                                          |  |

|----|------|------------------------------------------------------------------------------------------------------------------------|--|

| 6  | Dev  | lopment Platforms and Hardware 34                                                                                      |  |

|    | 6.1  | Available platforms       34                                                                                           |  |

|    | 6.2  | DE2 and Components                                                                                                     |  |

|    |      | 6.2.1 The FPGA - Cyclone II EP2C35                                                                                     |  |

|    |      | 6.2.2 The VGA DAC - ADV7123                                                                                            |  |

|    |      | $6.2.3  \text{The I}/0  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                               |  |

|    |      | $6.2.4  \text{The SDRAM - S29AL032D}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                 |  |

|    |      | 6.2.5 The FPGA-OnChip Memory                                                                                           |  |

|    |      | 6.2.6 Megafunction - Shift Register                                                                                    |  |

|    |      | 6.2.7 Nios II Floating-Point Unit                                                                                      |  |

|    | 6.3  | The Camera - Terasic TRDB D5M    43                                                                                    |  |

| _  | ~    |                                                                                                                        |  |

| 7  |      | nunication 46                                                                                                          |  |

|    | 7.1  | Altera Avalon PIO                                                                                                      |  |

|    | 7.2  | $2C \dots \dots$ |  |

| 8  | Ped  | gogics 50                                                                                                              |  |

|    | 8.1  | Embedded Systems in Education                                                                                          |  |

|    | 8.2  | Pedagogic in Teaching and Learning                                                                                     |  |

|    |      |                                                                                                                        |  |

| 9  | Imp  | ementation and Discussion 53                                                                                           |  |

|    | 9.1  | System Overview                                                                                                        |  |

|    |      | 0.1.1 Hardware Video Signal Flow                                                                                       |  |

|    |      | 0.1.2 Software Video Signal Flow                                                                                       |  |

|    |      | 0.1.3 System and Platform Discussion                                                                                   |  |

|    |      | 0.1.4 Programs and Tools                                                                                               |  |

|    | 9.2  | mplementation of Nios II                                                                                               |  |

|    |      | 0.2.1 Hardware Peripheral Selection                                                                                    |  |

|    |      | 0.2.2 PIO and Interrupt                                                                                                |  |

|    |      | 0.2.3 Custom Instructions                                                                                              |  |

|    |      | 0.2.4 Software Implementation                                                                                          |  |

|    | 9.3  | Camera Configuration and Operation                                                                                     |  |

|    |      | $0.3.1  \text{Configuration}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                         |  |

|    |      | $0.3.2  \text{Operation Modes}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                       |  |

|    | 9.4  | Hardware/Software Selection Process    73                                                                              |  |

|    | 9.5  | Video Processing                                                                                                       |  |

|    |      | 0.5.1 Hardware and Software Operation and Quality                                                                      |  |

|    |      | $0.5.2  \text{Resolutions}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                           |  |

|    | 9.6  | Color Processing                                                                                                       |  |

| 10 | Ð    |                                                                                                                        |  |

| 10 |      | onstration 81                                                                                                          |  |

|    | 10.1 | The Presentation    82                                                                                                 |  |

|    | 10.2 The Interaction                                      | 85 |

|----|-----------------------------------------------------------|----|

| 11 | 10.4 Target Group       Conclusions      11.1 Future Work | 87 |

| A  | Software Code                                             | 94 |

| в  | Hardware Code                                             | 97 |

# List of Figures

| NIOS II processor core - from [19]                                                                                                                                                                                                       | 7<br>11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

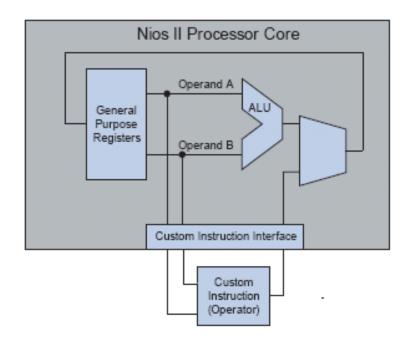

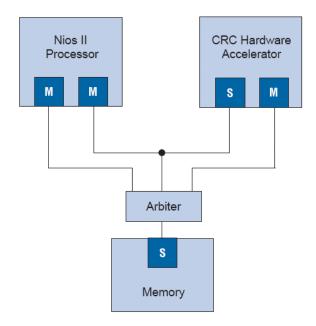

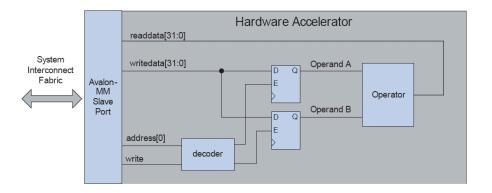

| Target architecture for hardware/software partitioning - from [60]Custom Instructions with Nios II soft processor - from [19]Example of a CRC Hardware Accelerator with Nios II - from [19]Example of a Hardware Accelerator - from [19] | 15<br>17<br>18<br>19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

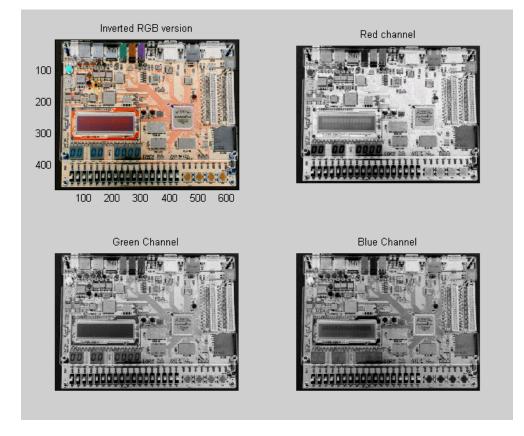

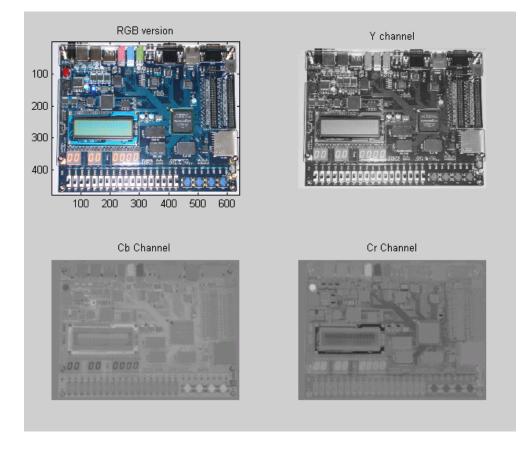

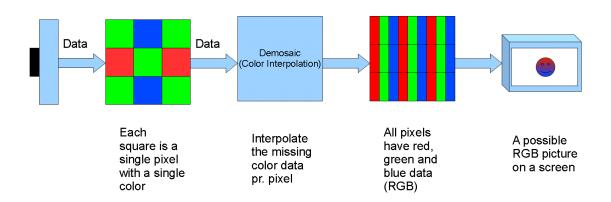

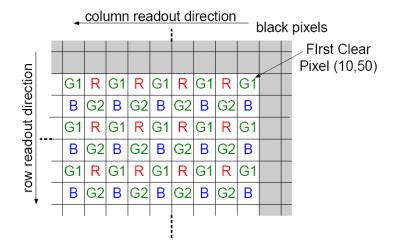

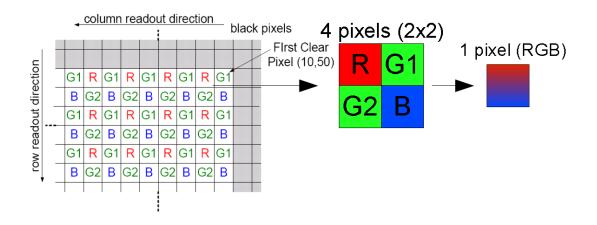

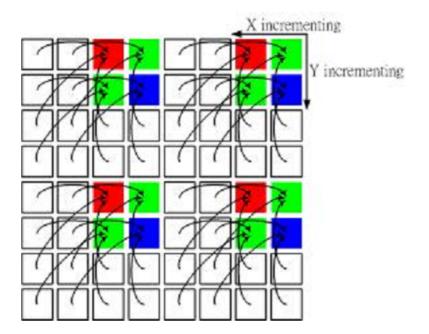

| An inverted color representation of an image                                                                                                                                                                                             | 23<br>24<br>25<br>26<br>27<br>28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

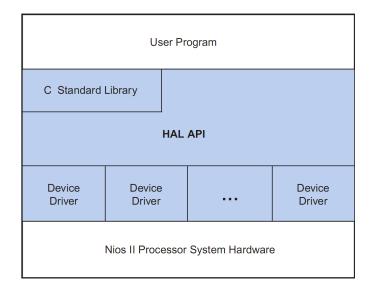

| HAL BSP After Generating Files - from [20]                                                                                                                                                                                               | 32<br>33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

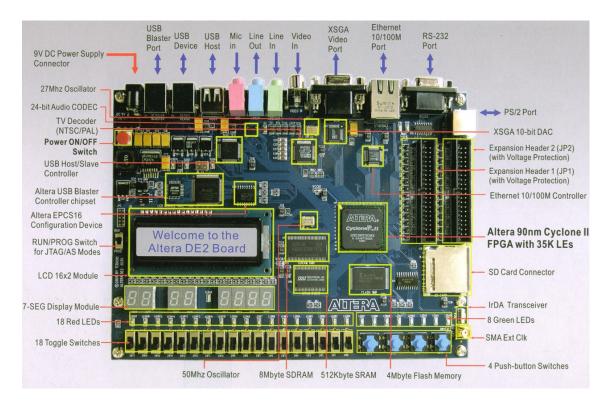

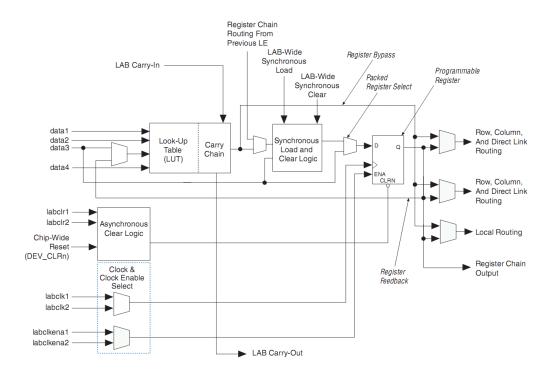

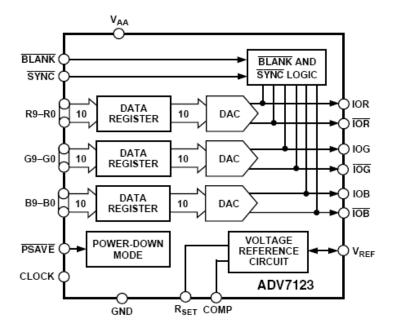

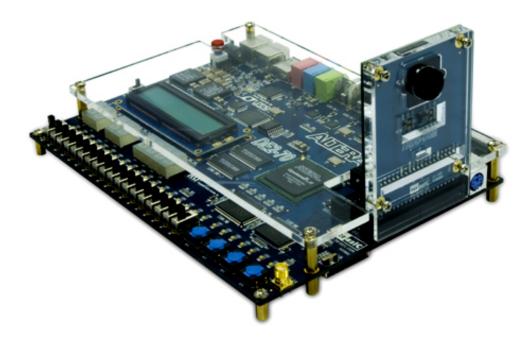

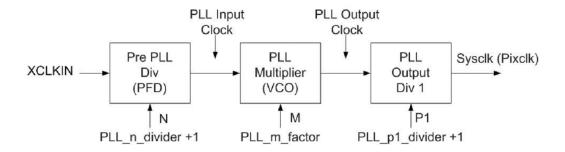

| Altera DE2 development board - from [12]                                                                                                                                                                                                 | 35<br>36<br>37<br>41<br>43<br>44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

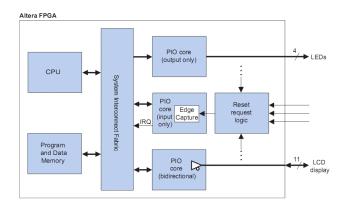

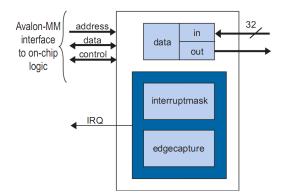

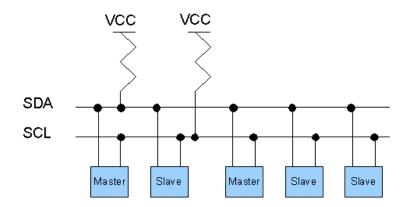

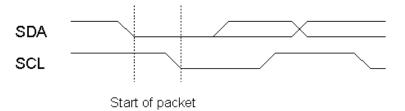

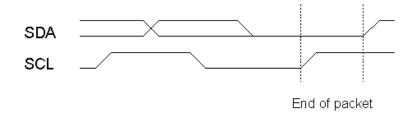

| NIOS II sample system with multiple PIO cores - from [21] PIO core - from [21]                                                                                                                                                           | 46<br>47<br>48<br>48<br>49<br>49<br>49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

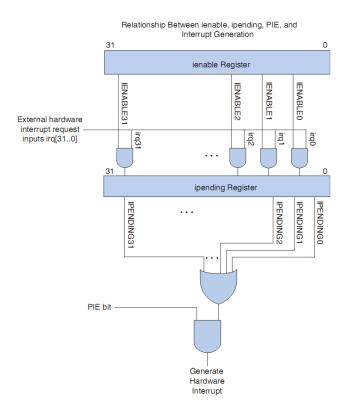

|                                                                                                                                                                                                                                          | Relationship between ienable, ipending, PIE and Hardware Interrupts -         from [19]         Target architecture for hardware/software partitioning - from [60]         Custom Instructions with Nios II soft processor - from [19]         Example of a CRC Hardware Accelerator with Nios II - from [19]         Example of a Hardware Accelerator - from [19]         An inverted color representation of an image         A YCbCr color image and its channels         The process of transforming raw image data to viewable RGB image data         Pixel color readout pattern (Bayer) - from [56]         Color interpolation by using neighboring pixels to determine one full range         RGB pixel - combined with figure from [56]         2X binning on Terasic D5M - from [56]         2X binning on Terasic D5M - from [56]         Mattera DE2 development board - from [12]         Logic Element in Cyclone II - from [13]         Functional Block diagram of the VGA DAC - from [26]         Megafunction shift register (ALTSHIFT_TAPS) - from [14]         The Terasic Digital Camera with the Altera DE2 - from [56]         NIOS II sample system with multiple PIO cores - from [21]         PIO core - from [21]         PIO core - from [30]         PIO core - from [30] |

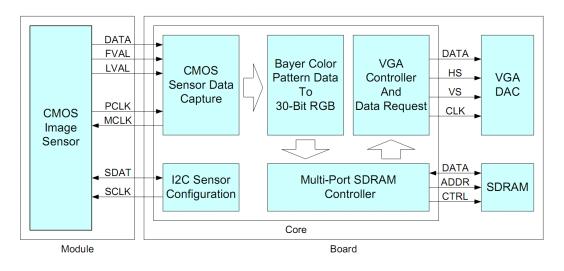

| 9.1  | A block diagram of the Terasic camera system - from [55]                   | 54 |

|------|----------------------------------------------------------------------------|----|

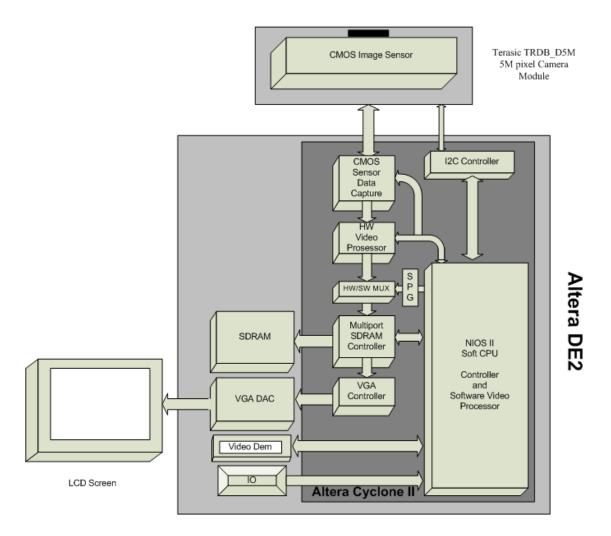

| 9.2  | A block diagram of the system and the communication flow                   | 55 |

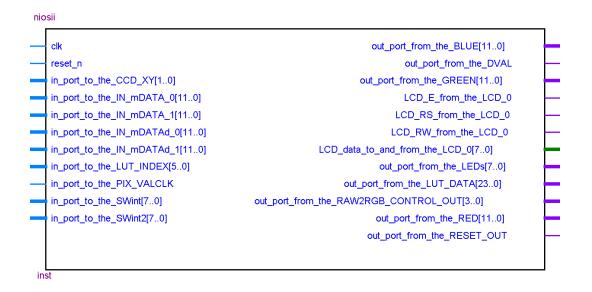

| 9.3  | The Nios II/f-module created for this system                               | 63 |

| 9.4  | Nios II's peripherals with memory map and interrupt                        | 67 |

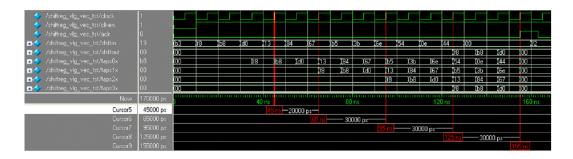

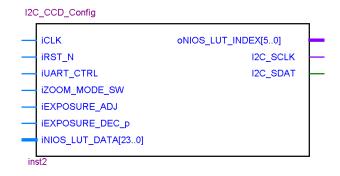

| 9.5  | The $I^2C$ configuration module                                            | 70 |

| 9.6  | The HW/SW MUX module, used for switching between video sources $~$         | 73 |

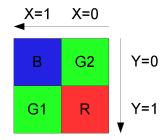

| 9.7  | A group of four pixels in mirror readout pattern                           | 74 |

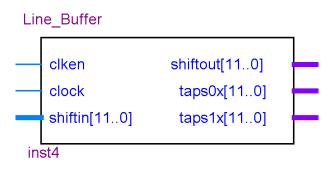

| 9.8  | The Line-buffer used by both hardware and software for color interpolation | 74 |

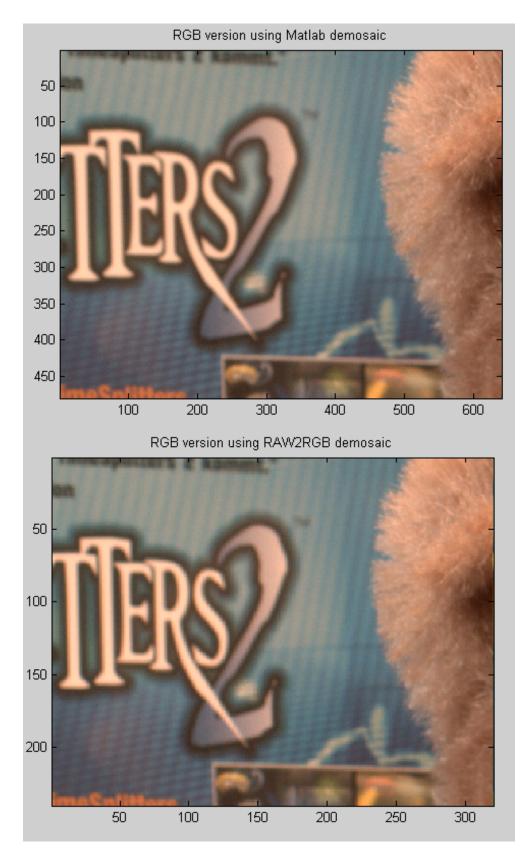

| 9.9  | Comparison of quality of Matlab demosaic and RAW2RGB demosaic $\ . \ .$    | 76 |

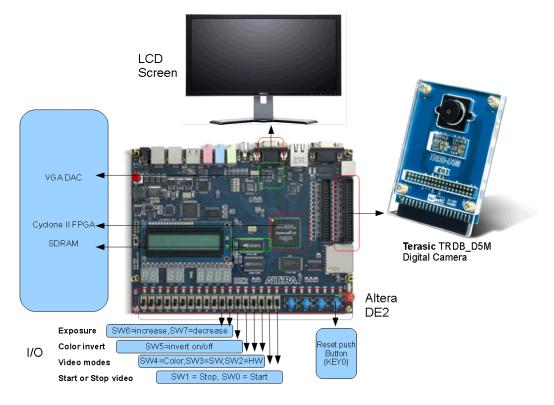

| 10.1 | An overview of the demonstrator and its I/O                                | 83 |

## List of Tables

| 2.1<br>2.2<br>2.3                                                                         | NIOS II core implementations comparison part 1 - from [19]NIOS II core implementations comparison part 2 - from [19]Embedded Processor Performances Using Dhrystone Version 2.1 - from[43, 18, 19, 2, 35] | 8<br>9<br>14         |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| $     \begin{array}{r}       6.1 \\       6.2 \\       6.3 \\       6.4     \end{array} $ | VGA vertical timing specification - from [12]                                                                                                                                                             | 39<br>39<br>41<br>42 |

| 9.1                                                                                       | Overview of the hardware modules on the FPGA and their origin part 1                                                                                                                                      |                      |

| 9.2                                                                                       | of 2 Overview of the hardware modules on the FPGA and their origin part 2 of 2                                                                                                                            | 57<br>58             |

| $9.3 \\ 9.4$                                                                              | Programs and tools used to implement the system                                                                                                                                                           | 62                   |

| 9.5                                                                                       | ules they are connected to, part 1 of 2                                                                                                                                                                   | 65                   |

|                                                                                           | ules they are connected to, part 2 of 2                                                                                                                                                                   | 66                   |

| $9.6 \\ 9.7$                                                                              | Camera control registers and description                                                                                                                                                                  | 72                   |

| 9.1                                                                                       | and without the use of custom floating-point instructions                                                                                                                                                 | 79                   |

| 10.1                                                                                      | Switches and their purpose. Each switch needs to be "toggled" in order to do its function, except KEY[0]                                                                                                  | 84                   |

| 10.2                                                                                      | Demonstration modes, their purpose and active switches                                                                                                                                                    | 84                   |

|                                                                                           | The conclusion of the different demonstration modes $\ldots \ldots \ldots \ldots$                                                                                                                         | 85                   |

| 10.4                                                                                      | Target Groups                                                                                                                                                                                             | 86                   |

## Definitions

| ASIC | : | Application-Specific Integrated Circuit - a hardware circuit of the appli-<br>cation in silicone                                                                                                                 |

|------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BSP  | : | Board Support Packages - A NiosII BSP project is a specialized library containing system-specific support code                                                                                                   |

| CCD  | : | Charge-Coupled Device - a device for movement of electric charge. When<br>combined with a image sensor and a Bayer filter it serves a great purpose<br>for digital imaging                                       |

| CFA  | : | Color Filter Array - a mosaic of tiny color filters placed over the pixel sensors of an image sensor to capture color information                                                                                |

| FIFO | : | First-In First-Out - refers to a way of queuing and organizing data by giving highest priority to the data arriving first (First-Come First-Served - principle). A FIFO buffer is a buffer organized in this way |

| FPGA | : | Field-Programmable Gate Array - a programmable device for realizing hardware                                                                                                                                     |

| FPS  | : | Frames Per Second - the rate or frequency of which unique pictures or frames is produced                                                                                                                         |

| HAL  | : | Hardware Abstraction Layer - an abstraction layer, implemented in soft-<br>ware, between the physical hardware of a computer and the software<br>that runs on it                                                 |

| HDD  | : | Hard Disk Drive - a none volatile storage device for digital data                                                                                                                                                |

| HDL  | : | Hardware Descriptive Language - a language for describing hardware                                                                                                                                               |

| IP                   | : | Intellectual Property - a term referring to a number of distinct types of creations of the mind for which property rights are recognized and owned                                                                     |

|----------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IRE                  | : | Institute of Radio Engineers - is a unit used in the measurement for composite video signals. It is a relative measurement (procent). 100 IRE was originally designed to be the range from black to white video signal |

| LE                   | : | Logic Element - a basic element used in FPGAs. The number of LEs is often used as one of the paramters for an indicator of total area                                                                                  |

| MMU                  | : | Memory Management Unit - a unit that is responsible for handeling all communication between CPU and memory                                                                                                             |

| MPU                  | : | Memory Protection Unit - a unit that protects the memory. Sectors that<br>are critical would be secured against unauthorized alterations                                                                               |

| $\operatorname{PLL}$ | : | Phase-Locked Loop - a unit that is used to create a new signal with equal<br>or different phase and frequency by using a reference signal                                                                              |

| RISC                 | : | Reduced Instruction-Set Computing - a processor architecture which uses<br>a reduced number of different instructions                                                                                                  |

| SDRAM                | : | Synchronous Dynamic Random Access Memory - a type of volatile mem-<br>ory which needs to be periodically refreshed                                                                                                     |

| SRAM                 | : | Static Random Access Memory - a type of volatile memory that does not need to be refreshed, but still needs power to hold data                                                                                         |

| VGA                  | : | Video Graphics Array - can refere to both the analog computer display standard for the d-sub connector or the 640x480 resolution                                                                                       |

# Chapter 1 Introduction

Today, in our modern society, people are surrounded by many different forms of multimedia every day. Video, images and sound have become an important part of how people communicate and gain knowledge, as well as an important medium for entertainment and a part of culture. Thanks to great improvements in the field of technology and electronics many things that were deemed impossible has become possible. People can talk and see each other in real-time across continents with use of video conference tools in a quality that give the sense of talking to a person right next to you. The mobile phones today are filled with sophisticated electronics that let people watch TV, listen to music streamed from the Internet, take photos and share them with friends, surf the Web, talk to people with or without video and one can even watch movies. The possibilities are endless, but in order to make enhancements in the field of technology and electronics there is a need for engineers that possess the knowledge and interest to make those things come true. Universities, like NTNU, are always searching for new students and to recruit them. In order to promote the field of electronics, Department of Electronics and Telecommunication desires to demonstrate good examples of electronic systems that can be used on occasions like school visits at NTNU, Forskningstorget and Elektronikk- & Telekommunikasjonsdagen. Hopefully, this could result in an increased number of applicants for this field of study and as a consequence get clever students who have the ability to take part in making the next generation of electronic systems.

Most part of the electronic systems people surround themselves with have some form of computational properties. These systems are "small" computers, dedicated to perform the task they where designed to do. Such systems are often referred to as embedded systems. Embedded systems consist of a combination of hardware and software which gives both great flexibility and wide possibilities for optimization. Systems with such properties are great platforms for making demonstrators and let the designer be creative.

Most forms of multimedia processing are very complex and puts a high demand on available computational power. Many devices that do this form of computation is running on battery, and battery lifetime is important. Not being able to watch a whole movie on a device before it runs out of battery would be unacceptable to most people. As performance costs power, the designer needs to be smart when creating the device. Hardware/Software codesign is about meeting system objectives by exploiting the synergism between hardware and software trough their concurrent design [48]. Performing the calculations where it's most efficient, both in relation to performance and power, would be a HW/SW codesign choice. Such choices are an important part of the designers job and could mean the difference between meeting system objectives or not.

FPGA or Field-Programmable Gate Array is a programmable device that allows the designer to create almost any form of hardware from a description made in a hardware language. It is also possible to create software processors on the device and run them side by side with custom designed hardware. In other words, it is a great platform for hardware/software codesign.

#### 1.1 Preliminary Work

Prior to this thesis there has been done some research. This research was a study on different educational challenges related to demonstration of electronic systems. In addition there was considered many different types of applications in relation to demonstration before one final system was specified.

From research and discussions in the project report it was concluded that the application of the demonstration should focus on a specific topic in order to keep the focus on what the demonstrator should demonstrate. In addition there was also concluded that the demonstrator should demonstrate something the observer could relate to in order to motivate him or her. It was also considered that a visual demonstration on a technical topic would help bring interest and also be effective when trying to get the observer to learn something from the demonstration. Also, by letting the observer take an active part in the demonstration it would support the observer in coming to his or her own conclusion about the demonstration. This is considered as a good pedagogical approach.

Many different systems were considered, but two prevailed themselves as the most promising candidates. One of the ideas was an embedded demonstrator for visual demonstration of audio properties. The other idea was an embedded demonstrator for video presentation and manipulation. Both candidates had the ability to become good demonstrators, but idea number one presented some additional challenges. The challenges were related to creating a visual interface in the available timeframe. Idea number two was selected and a specification of a possible implementation was suggested.

#### 1.2 Description

In this master thesis an embedded system for presenting and manipulating video will be described and implemented. In addition, the necessary presentation material will be made. The system's purpose is to emphasize the importance of hardware/software codesign when designing an electronic system. Without the unique combination of hardware and software it might not be possible to achieve system objectives and specification. The demonstrator is going to demonstrate this importance by processing video from a camera through hardware or software. The observer is then able to select between the two and evaluate the difference in obtainable video quality. In addition the observer will be able to select between normal color representation and inverted color representation. The system is also going to visually present the time difference by doing color manipulation in software or by using dedicated hardware by means of custom instructions.

This system presents many design challenges. One of the main challenges this project brings to surface is the available performance of the embedded software processor and the uncertainty of its ability to present some form of viewable video. The final solution offers a demonstration of video processing and manipulation. The ability to observe cameravideo, processed in either software or hardware in real-time is considered to be a good concept for a demonstration. In addition, the platform shows great promise for further development and can easily be adapted to be used in other educational situations.

This report is divided into ten main chapters. The first seven chapters (Chapter 2 - Chapter 8) present theory about different topics related to the demonstrator. Chapter 9 presents the implementation of the complete system and a discussion of the challenges, different solutions and other topics related to the design process. Chapter 10 presents a walk through of a hypothetical demonstration of the system. Presented in the final chapter (Chapter 11) is a conclusion and suggestions for future work.

#### **1.3** Main Contributions

The main contributions of this master thesis will be:

- A fully functional embedded demonstrator that processes recorded video in both hardware and software

- A hardware video processing performance of up to 25 frames per second

- A system that demonstrates the benefits of using custom floating-point instructions to accelerate color processing, with up to 300% increase in performance compared to software processing

- A poster with necessary material to give a full demonstration of the embedded demonstrator

### Chapter 2

## **Embedded Processors**

First, a little introduction as to what an embedded system actually is. Most people are familiar with the desktop computer. The desktop computer is a very versatile computing machine which can be used for numerous applications, like playing games, checking mail and much more. An embedded system can also be defined as a computer system, but which is designed to perform a specific task [30]. This as opposed to the desktop computer which is designed with the purpose to be much more generic. As a result the embedded system can be constructed to perform the individual tasks in a much more effective manner, both in relation to size, power consummation and performance. Embedded systems are actually much more common than the desktop computer, although they are not always as easy to spot. About 99% of all the microprocessors being made is used in embedded systems [29]. You can find embedded systems in almost any kind of electronic consumer products, like cars, washing machines, coffee makers, toys, TVs, Blu-Ray players and the like. Embedded systems are also very common and important in industry and are often used to control mechanical systems many of which have hard demands in relation to responsiveness and speed. These systems are often referred to as a real-time system [29]. Many of these systems have hard demands which would not have been possible to achieve with a conventional desktop computer. Possible reasons could be insufficient processing power or to slow response time. Embedded systems usually consist of a combination of hardware (e.g. I/O, memory, peripherals, accelerators, co-processors) and software (some kind of program to tell the system what to do). This combination gives flexibility and wide possibilities for optimization and customization. For an embedded system to be able to run software a microprocessor for executing instructions is needed.

#### 2.1 About the Embedded Processor

The main function of a processor is to manipulate data in a way specified by a sequence of instructions [30]. The series of instructions is what constitutes a software program, written in some kind of language (e.g. C and C++). The software is stored in a memory (e.g. Flash, SRAM, SDRAM, HDD) and the processor fetches the instructions sequentially by use of extra logic for translating the instructions into control signals and a program counter to point to the next instruction. A microcontroller is a processor which incorporates all necessary hardware in order to function as a computing unit. Consisting of a CPU (Central Processing Unit) and different kinds of peripherals including memory. The peripherals could be user-designed or generic (standardized). Some examples of generic peripherals are: SPI (Serial Peripheral Interface Bus), UART (Universal Asynchronous receiver/transmitter), JTAG(Joint Test Action Group - for debugging and test), OnChipMemory (Flash, SRAM or something similar) and I<sup>2</sup>C (Inter-Integrated Circuit - serial bus system). The peripherals are used to give the processor purpose. A processor with no means of communication to the analog world would not be very useful.

There are two main types of embedded processors: Soft processors and hard processors, as stated in [34]. The soft processor is typically made out of logical elements found in FPGAs and described in a Hardware Descriptive Language (HDL), like VHDL or Verilog. The hard processor is, on the other hand, not possible to alter once it has been created in silicone. This is because the processor does not consist of reconfigurable elements like the soft processor does. Hard processors can appear in both ASIC (Application-Specific Integrated Circuit) and as a part of a FPGA. One example of a FPGA which includes a hard processor is the Xilinx FPGA Vertex-V FXT family [4]. It includes the PowerPC 440 embedded processor architecture from IBM.

There are both advantages and disadvantages in using a soft or a hard embedded processor [51, 63, 34]. In [34] there is described four advantages by using the soft processor: Customization, increased lifespan, component and cost reduction and hardware acceleration. The hard processor's main advantage is its high performance and low unit cost.

The soft processor is very customizable and can easily be altered to fit the current need. This gives the designer the possibility to be flexible when selecting a combination of peripherals and controllers. The designer can even invent unique peripherals that can be connected directly to the processor's bus, as opposed to the hard processor where the designer must choose between the off-the-shelf embedded processors that are currently available, many of which are too large or too small for the task the designer wants to solve. If the hard processor is combined with a FPGA, like the Xilinx Vertex-V FXT, one can benefit from both and gain some customization, but the processor core itself can not be altered.

Peripherals can be constructed by the designer or bought from a vendor. The available cores are often distributed with an IP (Intellectual Property) which means that someone owns the source code for the block [9]. The use of IP cores can greatly reduce the overall

design time and reduce the time-to-market. The FPGA vendor Altera offers a wide range of IP cores from Altera and other third-parties [9]. For implementing these cores Altera users can use Quartus and SOPC builder, which is described in more detail in Section 5.1. Hardware cores are also available as a free and open source solution under the free Lesser General Public License (LGPL) at www.OpenCores.org [50].

Since the hardware is described in a HDL like language, the lifespan of the product is much longer. It can be re-implemented on future FPGA platforms and can easily be altered to become an even better product. Another advantage in using a soft processor is component and cost reduction. The versatility of the FPGA enables the designer to use only one FPGA to replace a system that required multiple components. By reducing the number of components, the company can also reduce board size and inventory management, both of which will save design time and money.

Hardware acceleration is one of the most compelling reasons to choose an FPGA embedded processor [61]. This gives the designer the unique ability to combine and make trade-offs between hardware and software to maximize performance [48]. More theory about this subject is presented in Section 3.

There are a lot of advantages in choosing a soft processor architecture, but there are still cases when a hard processor might be a better choice. While the hard processor can be bought in a completely ready-to-use state, the soft processor has to be constructed and the designer has to be able to both construct hardware as well as software. Luckily, tools like SOPC builder (Section 5.1) makes this job much easier and it requires less knowledge about hardware contruction. Another disadvantage is that the soft processor needs more complex tools and the design methodology needs more attention. Another aspect to consider is device cost. If the designer is about to solve a "simple" problem that does not require much processing power or unique features, an off-the-shelf processor could be a much cheaper and better choice. If there already is an FPGA present in the system, the designer might want to consider moving much of the external hardware into the reconfigurable chip and also include a soft processor.

#### 2.2 Nios II

Nios II, as stated in [19], is a 32-bit soft embedded processor architecture designed for the Altera family of FPGAs. The older Nios was introduced in 2001 [10] and was the industry's first viable commercial processor created specifically for embedded system design in FPGAs. Nios II displayed several enhancements over the older Nios, thus making it more suitable for a wider range of embedded computing applications [19]. Since Nios first was introduced, tens of thousands of FPGA users have adopted Nios or Nios II processors from Altera. Xilinx's MicroBlaze is an example of a very similar product [3]. This is also a 32-bit soft embedded processor. The processor is designed to be used on Xilinx's family of FPGAs.

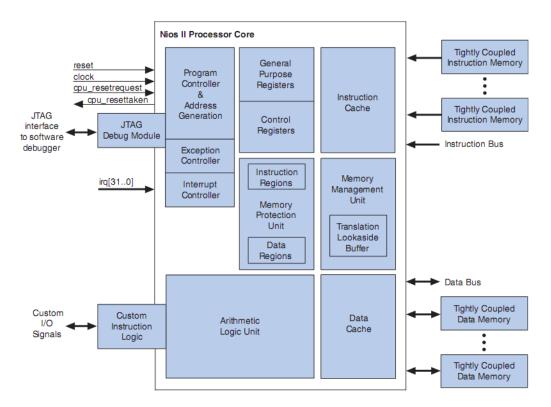

Figure 2.1: NIOS II processor core - from [19]

The processor core of the Nios II is displayed in Figure 2.1. It provides a full 32-bit instruction set, data path and address space. This makes it possible to access up to 4 GB of external memory. In addition the core has 32 general-purpose registers which can be used to store and alter time critical data. The core also supports 32 external interrupt sources which can be used by external components to get the processor's attention. More information about interrupt can be found in Section 2.3. The core can also execute complex instructions like 32x32 multiplication or division, and instruction barrel shifter. For

debugging the core supports JTAG, which is a standard for hardware-assisted debugging. This enables possibilities like start, stop, step and trace execution in run-time. The software development environment is based on GNU C/C++ tool chain and Eclipse IDE. Code creation, simulation, execution and debugging can be done in this environment. More information about this embedded design suite can be found in Section 5.3.

|                 |                           |                   | Core            |                      |  |

|-----------------|---------------------------|-------------------|-----------------|----------------------|--|

|                 | Feature                   | Nios II/e         | Nios II/s       | Nios II/f            |  |

| Objective       |                           | Minimal core size | Small core size | Fast execution speed |  |

| Performance     | DMIPS/MHz (1)             | 0.15              | 0.74            | 1.16                 |  |

|                 | Max. DMIPS (2)            | 31                | 127             | 218                  |  |

|                 | Max. f <sub>Max</sub> (2) | 200 MHz           | 165 MHz         | 185 MHz              |  |

| Area            |                           | < 700 LEs;        | < 1400 LEs;     | Without MMU or MPU:  |  |

|                 |                           | < 350 ALMs        | < 700 ALMs      | < 1800 LEs;          |  |

|                 |                           |                   |                 | < 900 ALMs           |  |

|                 |                           |                   |                 | With MMU:            |  |

|                 |                           |                   |                 | < 3000 LEs;          |  |

|                 |                           |                   |                 | < 1500 ALMs          |  |

|                 |                           |                   |                 | With MPU:            |  |

|                 |                           |                   |                 | < 2400 LEs;          |  |

|                 |                           |                   |                 | < 1200 ALMs          |  |

| Pipeline        |                           | 1 stage           | 5 stages        | 6 stages             |  |

| External Addres | s Space                   | 2 GBytes          | 2 GBytes        | 2 GBytes without MMU |  |

|                 |                           |                   |                 | 4 GBytes with MMU    |  |

#### Processor core implementations

Table 2.1: NIOS II core implementations comparison part 1 - from [19]

The Nios II core is available as three different types. All cores support the Nios II instruction set architecture and the implementation differs in some of the feature they support and their main objective. The implementations are Nios II/e, Nios II/s and Nios II/f. Their objectives are minimal core size, small core size and fast execution speed. Table 2.1 gives an overview of some of the differences between the three. Some of these differences are related to: Maximum obtainable clock frequency, maximum DMIPS/MHz (performance, se more in Section 2.4) and the amount of area the core consumes. The Nios II/s uses approximately 1400 LEs (Logic Elements) as opposed to the Nios II/f which uses around 1800 LEs (without MMU or MPU). The difference in area consumation is about 20%, but the increase in performance if chosing Nios II/f would be about 40%. Nios II/e uses about half the size of the Nios II/s, but is still able to support the whole Nios II instruction set. Depending on the designer's need it should be a simple choice to select the right core for the job. All values presented in Table 2.1 are based on choosing the fastest options and using Altera's fastest FPGAs. If the designer uses an FPGA with a lower speedgrade, this will result in some speed reduction.

| Feature               |                                                   | Core                                                                                          |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                                                   | Nios II/e                                                                                     | Nios II/s                                                                                     | Nios II/f                                                                                                                                                                                                                                                                                                                                                                              |

| Instruction<br>Bus    | Cache                                             | -                                                                                             | 512 bytes to<br>64 KBytes                                                                     | 512 bytes to 64 KBytes                                                                                                                                                                                                                                                                                                                                                                 |

|                       | Pipelined Memory Access                           | -                                                                                             | Yes                                                                                           | Yes                                                                                                                                                                                                                                                                                                                                                                                    |

|                       | Branch Prediction                                 | -                                                                                             | Static                                                                                        | Dynamic                                                                                                                                                                                                                                                                                                                                                                                |

|                       | Tightly-Coupled Memory                            | -                                                                                             | Optional                                                                                      | Optional                                                                                                                                                                                                                                                                                                                                                                               |

| Data Bus              | Cache                                             | -                                                                                             | -                                                                                             | 512 bytes to 64 KBytes                                                                                                                                                                                                                                                                                                                                                                 |

|                       | Pipelined Memory Access                           | -                                                                                             | -                                                                                             | -                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | Cache Bypass Methods                              | -                                                                                             | -                                                                                             | <ul> <li>I/O instructions</li> <li>Bit-31 cache bypass</li> <li>Optional MMU</li> </ul>                                                                                                                                                                                                                                                                                                |

|                       | Tightly-Coupled Memory                            | -                                                                                             | -                                                                                             | Optional                                                                                                                                                                                                                                                                                                                                                                               |

| Arithmetic            | Hardware Multiply                                 | -                                                                                             | 3-cycle (3)                                                                                   | 1-cycle (3)                                                                                                                                                                                                                                                                                                                                                                            |

| Logic Unit            | Hardware Divide                                   | -                                                                                             | Optional                                                                                      | Optional                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Shifter                                           | 1 cycle-per-bit                                                                               | 3-cycle shift (3)                                                                             | 1-cycle barrel<br>shifter <i>(3)</i>                                                                                                                                                                                                                                                                                                                                                   |

| JTAG Debug<br>Module  | JTAG interface, run control, software breakpoints | Optional                                                                                      | Optional                                                                                      | Optional                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Hardware Breakpoints                              | -                                                                                             | Optional                                                                                      | Optional                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Off-Chip Trace Buffer                             | -                                                                                             | Optional                                                                                      | Optional                                                                                                                                                                                                                                                                                                                                                                               |

| Memory Mana           | gement Unit                                       | -                                                                                             | -                                                                                             | Optional                                                                                                                                                                                                                                                                                                                                                                               |

| Memory Prote          | ction Unit                                        | -                                                                                             | -                                                                                             | Optional                                                                                                                                                                                                                                                                                                                                                                               |

| Exception<br>Handling | Exception Types                                   | Software trap,<br>unimplemented<br>instruction, illegal<br>instruction, hardware<br>interrupt | Software trap,<br>unimplemented<br>instruction, illegal<br>instruction, hardware<br>interrupt | Software trap,<br>unimplemented<br>instruction,<br>illegal instruction,<br>supervisor-only<br>instruction,<br>supervisor-only instructio<br>address, supervisor-only<br>data address, misaligned<br>destination address,<br>misaligned data address,<br>division error, fast TLB<br>miss, double TLB miss,<br>TLB permission violation,<br>MPU region violation,<br>hardware interrupt |

|                       | Integrated Interrupt<br>Controller                | Yes                                                                                           | Yes                                                                                           | Yes                                                                                                                                                                                                                                                                                                                                                                                    |

| User Mode Support     |                                                   | No; Permanently in<br>supervisor mode                                                         | No; Permanently in<br>supervisor mode                                                         | Yes; When MMU or MPU present                                                                                                                                                                                                                                                                                                                                                           |

**Table 2.2:** NIOS II core implementations comparison part2 - from [19]

As mentioned before, the Nios II/f focuses on fast execution speed. Compared to the Nios II/e which uses a minimum of 6 cycles per instruction, the Nios II/f uses an average of 1 cycle per ALU instruction [19]. The performance of the Nios II/f is achieved by maximizing the max frequency of the processor core and a high instructions-per-cycle execution efficiency. This core employs a 6-stage pipeline to achieve a high DMIPS/MHz as seen in Table 2.1. A pipeline is often used to increase data-throughput in a computing system [40]. This is done by inserting a chain of data-processing stages. Nios II/f also has separate cache (fast memory) for data and instructions. The size of these two can be adjusted to fit the designer's need. The data and instruction bus can be seen in Figure 2.1. A possible memory for this job could be the fast on-chip memory on the FPGA, described in more detail in Section 6.2.5. In addition the Nios II/f provides an optional MMU and MPU to support operating systems that require this. If an MMU is selected, the processor can access up to 4GB of external memory. Another important property of the Nios II/f is the support for custom instructions, described in more detail in Section 3.2.1. Custom instructions can seriously increase the overall performance. Table 2.2 shows more of the options and properties of the available core implementations of Nios II.

#### 2.3 Interrupt

Interrupts are a technique of diverting the processor from the execution of a current program so that it may deal with some event that has occurred [30]. The events could be many things. It could be an error from a device or simply an I/O device that has finished a result. Interrupts can be divided into two groups: Hardware interrupts and software interrupts. Hardware interrupts are interrupts from hardware like an I/O device. There are two ways of generating this interrupt. One is by using the processor itself to do the checking of the I/O device, to check if there are any new data. This is called polling. Another way to do it is to let the device itself generate an interrupt signal which "pulls" the processor away from its current job and into an Interrupt Service Routine (ISR). When such an interrupt occurs, the processor saves its state and loads the interrupt vector for the specific interrupt. The interrupt vector is an address to where the ISR can be found. The processor then executes the routine with its series of instructions before it resumes its previous state. Solution number one would demand very much processor time just for checking and waiting on the I/O device. This isn't very efficient use of processing power. The other solution would therefor be a much more efficient solution. Software interrupt is the other type of interrupt and is usually generated by an instruction, or it could be an exception occurring in a program.