## Fast Surveillance of the MKD High Voltage Pulse Generator Part of the LHC Beam Dump System at CERN

Øyvind Aakvik

Master of Science in ElectronicsSubmission date:October 2006Supervisor:Ragnar Hergum, IETCo-supervisor:Etienne Carlier, CERN

Norwegian University of Science and Technology Department of Electronics and Telecommunications

#### **Problem Description**

This project concerns the development of an electronic module for the fast surveillance of the MKD high voltage pulse generator of the LHC Beam Dumping System (LBDS).

The high voltage pulse generators of the LHC Beam Dumping System are built on the basis of a fully redundant hardware architecture. A correct surveillance of the pulsed current in the different redundant circuits of a generator is required in order to guarantee its availability and to be able to perform an early detection of an impedance sharing modification between the redundant circuits.

The work will consist in

- the capture of functional requirements, (Preliminary studies)

- the study of the possible technical solution,

- the design and the development of an electronic module able to acquire the pulse signals,

- the development of the embedded software to perform the signals analysis,

- the integration of the module within the existing control environment.

Typical keywords for this project are:

Analog and digitial electronics, Embedded software, VHDL, FPGA, PROFIBUS-DP and PLC.

Assignment given: 01. May 2006 Supervisor: Ragnar Hergum, IET

## Abstract

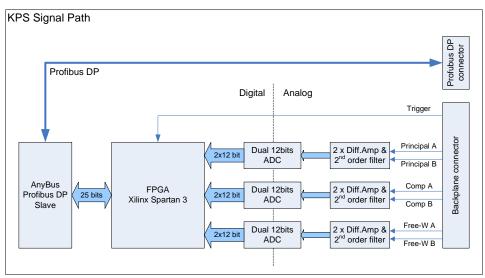

This paper contains the analysis, development, production and testing of a surveillance system for the monitoring of the MKDG, a high voltage pulse kicker in the MKD-system. The MKD-system is a part of the LHC Beam Dump System situated at point 6 in the LHC. The surveillance is active whenever the MKDs are operational.

The system is reporting any deviations from normal behaviour and runs an extensive analysis of the MKDG whenever there is a beam dump. The results are checked before a new run in the LHC can be initiated.

The final result is a working prototype which monitors and analyzes the MKDG and communicates the results to a PLC. The accomplished resolution is 10 bits for all six channels and this is acceptable.

## Preface

This master thesis is a conclusion of my 9 month stay at CERN and my time as a student at NTNU.

The work on this thesis has been the greatest educational and personal experience in my life. Just to get the opportunity to create something for the largest machine in the world, here at CERN, and to do this in wonderful countries like France and Switzerland has been extraordinary.

I want to thank Etienne Carlier for giving me directions and responsibility and for trusting my choices along the way. I also want to thank Nicolas Voumard and Gregor Grawer for helping me on the technical part; they have been a great resource.

Last I wish to thank Øystein Midttun and Torbjørn Houge for introducing me to the world of Telemark-skiing, and making my winter sport experiences complete!

Prévessin, 6<sup>th</sup> October 2006

Øyvind Aakvik

# Content

| C | ontent        |                                    | xi   |

|---|---------------|------------------------------------|------|

| L | ist of Fig    | ures                               | xiii |

| L | ist of Tal    | bles                               | xiv  |

| A | bbreviat      | ions                               | XV   |

| 1 | Intro         | duction                            | 1    |

|   | 1.1           | CERN                               | 1    |

|   | 1.2           | LHC                                | 2    |

|   | 1.3           | LBDS                               | 4    |

|   | 1.4           | MKD                                | 5    |

|   | 1.5           | MKDG                               | 6    |

| 2 | Svstei        | m requirements                     | 7    |

| 3 | •             | ninary Studies                     |      |

| 3 |               | Introduction                       |      |

|   |               | Tools                              |      |

|   |               | Measurements on the MKDG           |      |

|   | 3.3.1         | Principal Circuit                  |      |

|   | 3.3.2         | ÷                                  |      |

|   | 3.3.3         | Free-Wheel Circuit                 |      |

|   |               | FPGA                               |      |

|   | 3.4.1         | Xilinx Spartan 3, XC3S1000-4FT256. |      |

|   | 3.5           | Profibus DP                        |      |

|   | 3.5.1         | AnyBus-S module                    | 27   |

| 4 | VHD           | L Entity description               | 29   |

|   |               | Introduction                       |      |

|   | 4.2           | Tools                              | 29   |

|   | 4.3           | KPS                                |      |

|   | 4.3.1         | UserSettings-package               |      |

|   | 4.3.2         | Clock_Source                       |      |

|   |               | PowerOn_Reset                      |      |

|   | 4.3.4         | TriggerDetect                      |      |

|   | 4.3.5         | Topspeed_filter                    |      |

|   | 4.3.6         | ADC_Control                        |      |

|   | 4.3.7         | Analysis                           |      |

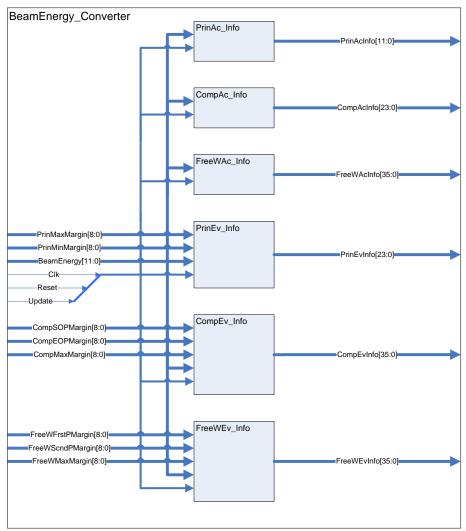

|   | 4.3.8         | BeamEnergy_Converter               |      |

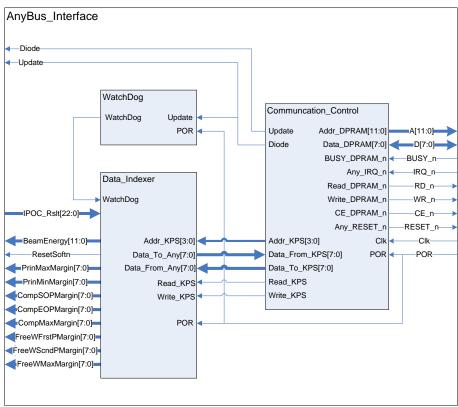

|   | 4.3.9         | AnyBus_Interface                   |      |

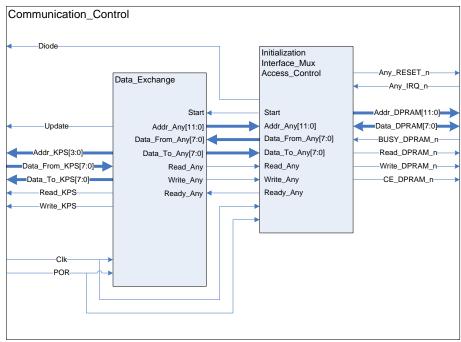

|   | 4.3.10<br>4 4 |                                    |      |

|   | 4.4           | KPS behaviour<br>Power up          |      |

|   | 4.4.1         | Reset                              |      |

|   | 4.4.3         | Armed                              |      |

|   |               |                                    |      |

|    | 4.4.4  | 1 0                                                           |    |

|----|--------|---------------------------------------------------------------|----|

|    | 4.4.5  | Analysis                                                      | 66 |

|    | 4.4.6  | Finished                                                      | 66 |

| 5  | Hare   | lware                                                         | 67 |

| 3  | 5.1    | Introduction                                                  |    |

|    | 5.2    | Tools                                                         |    |

|    | 5.2    | Analog Acquisition Circuitry                                  |    |

|    | 5.3.1  |                                                               |    |

|    | 5.3.2  |                                                               |    |

|    | 5.3.2  |                                                               |    |

|    | 5.3.4  |                                                               |    |

|    | 5.3.4  |                                                               |    |

|    | 5.3.6  |                                                               |    |

|    | 5.3.0  |                                                               |    |

|    |        |                                                               |    |

|    | 5.4    | Digital acquisition, analysis and reporting circuitry<br>FPGA |    |

|    | 5.4.1  |                                                               |    |

|    | 5.4.2  |                                                               |    |

|    | 5.4.3  |                                                               |    |

|    | 5.4.4  | J                                                             |    |

|    | 5.4.5  |                                                               |    |

|    | 5.4.6  |                                                               |    |

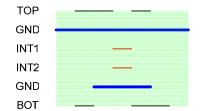

|    | 5.5    | Board layout                                                  |    |

| 6  | User   | Interfaces                                                    |    |

| Ũ  | 6.1    | Front Panel-interface                                         |    |

|    | 6.2    | KPS test-interface                                            |    |

|    |        | -                                                             |    |

| 7  | Meas   | surements and test                                            | 83 |

|    | 7.1    | Introduction                                                  | 83 |

|    | 7.2    | Test Equipment                                                | 83 |

|    | 7.3    | Test Procedure                                                | 84 |

|    | 7.4    | Step 1: Measurements                                          | 84 |

|    | 7.5    | Step 2: Testing of digital circuitry                          | 85 |

|    | 7.6    | Step 3: Testing the KPS behaviour                             |    |

|    | 7.6.1  | Installing                                                    |    |

|    | 7.6.2  |                                                               |    |

|    | 7.6.3  |                                                               |    |

|    | 7.6.4  | ÷                                                             |    |

|    | 7.6.5  | 1                                                             |    |

|    | 7.6.6  |                                                               |    |

|    | 7.6.7  | e i                                                           |    |

| 8  | Discu  | ussion                                                        |    |

| 6  | c      |                                                               |    |

| 9  | Conc   | clusion                                                       |    |

| 1( | ) List | of References                                                 |    |

| AppendixI |                               |        |

|-----------|-------------------------------|--------|

| A         | Tests                         |        |

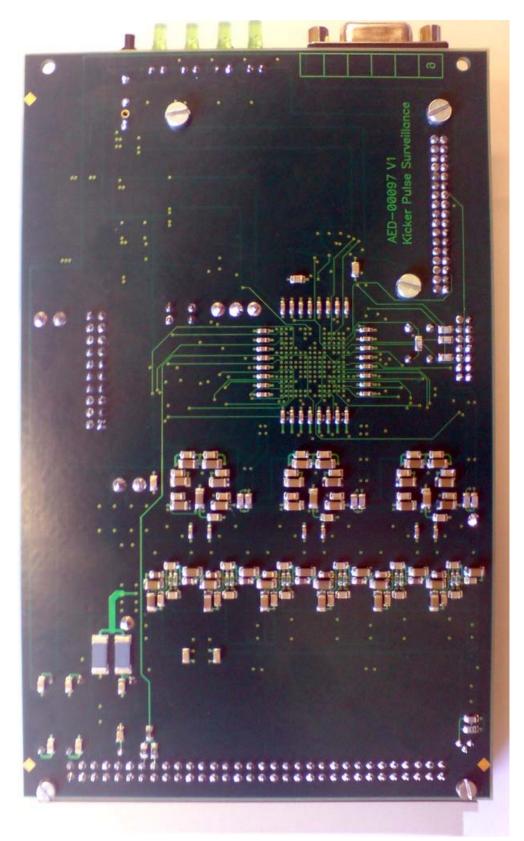

| В         | Pictures of the circuit board | XXI    |

| С         | PCB layout                    | CD-ROM |

| D         | KPS FPGA Pinning V1           | CD-ROM |

| E         | VHDL-code                     | CD-ROM |

| F         | Circuit Schematics            | CD-ROM |

# List of Figures

| Figure 1. Building 40 and 39 on the Meyrin-site of CERN.                         | 1    |

|----------------------------------------------------------------------------------|------|

| Figure 2. Overall view of the LHC experiment.                                    |      |

| Figure 3. LEP and LHC underground structures.                                    | 3    |

| Figure 4. Schematic top view layout of beam dumping system elements around       | b    |

| LHC point 6.                                                                     |      |

| Figure 5. Beam spot figure on absorber block.                                    |      |

| Figure 6. Dual branch generator circuit principal layout                         |      |

| Figure 7. Principal circuit pick-up voltage, Branch A. The lowest graph is for t | he   |

| 450 GeV and the highest for the 7 TeV                                            |      |

| Figure 8. Principal circuit pick-up voltage, Branch B. The lowest graph is for   | the  |

| 450 GeV and the highest for the 7 TeV                                            | . 11 |

| Figure 9. Principal circuit pick-up voltage, Branch A(red) and B(blue)           |      |

| Figure 10. Maximum values of both branches w.r.t. beam energy.                   | . 12 |

| Figure 11. Minimum values of both branches w.r.t. beam energy.                   | . 13 |

| Figure 12. Compensation circuit pick-up(CTc1B) voltage for branch B. The         |      |

| lowest graph is for the 450 GeV and the highest for the 7 TeV.                   | . 16 |

| Figure 13. Amplitude vs. beam energy for 15 points between 50µs and 80µs         | . 17 |

| Figure 14. Free-wheel circuit currents vs. Beam Energy, Branch A. The lowest     | t    |

| graph is for the 450 GeV and the highest for the 7 TeV.                          | . 20 |

| Figure 15. Free-wheel circuit currents vs. Beam Energy, Branch B. The lowest     | t    |

| graph is for the 450 GeV and the highest for the 7 TeV.                          | . 21 |

| Figure 16. Free-wheel circuit currents vs. Beam Energy, Branch A(blue) and       |      |

| B(red)                                                                           | . 21 |

| Figure 17. Free-wheel circuit currents vs. Beam energy, branch A, zoom on sta    | art- |

| spike. The lowest graph is for the 450 GeV and the highest for the 7 TeV         | . 22 |

| Figure 18. Maximum values vs. beam energy in Free-wheel circuit in branch        |      |

| A(blue), and linear approximation function(red).                                 | . 23 |

| Figure 19. Picture shows a Xilinx Spartan 3,                                     | . 26 |

| Figure 20. User interface of the AnyBus-S module.                                | . 27 |

| Figure 21. The AnyBus-S module                                                   |      |

| Figure 22. Hierarchical presentation of the entities in the KPS.                 | . 30 |

| Figure 23. Block diagram of KPS-entity.                                          | . 31 |

| Figure 24. Block diagram of the Analysis-entity.                                 | . 35 |

| Figure 25. Block diagram of the Prin_Acqui-entity                                | . 37 |

| Figure 26. Block diagram of the Prin_Acqui_X-entity.                             | . 38 |

| Figure 27. Block diagram of the Comp_Acqui-entity                                |      |

| Figure 28. Block diagram of the Comp Acqui X-entity                              | . 44 |

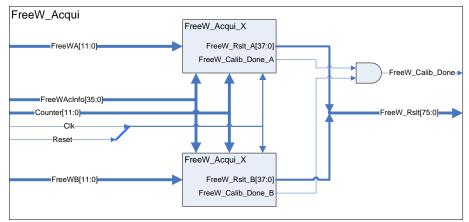

| Figure 29. Block diagram of the FreeW_Acqui-entity                              | 47 |

|---------------------------------------------------------------------------------|----|

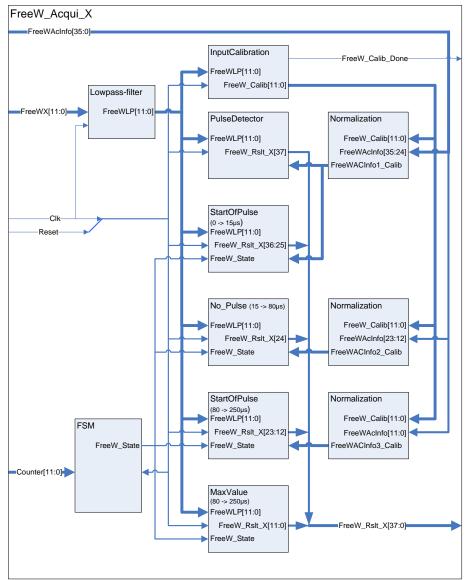

| Figure 30. Block diagram of the FreeW_Acqui_X-entity                            | 49 |

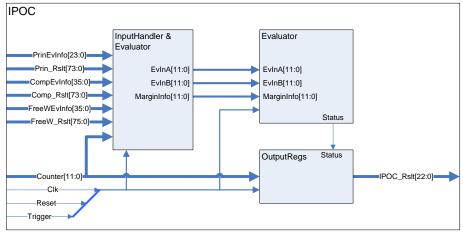

| Figure 31. Block diagram of the IPOC-entity.                                    | 52 |

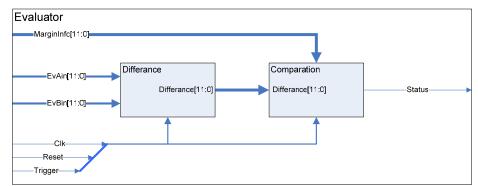

| Figure 32. Block diagram of the Evaluator-entity                                | 54 |

| Figure 33. Block diagram of the BeamEnergy_Converter-entity                     | 55 |

| Figure 34. Block diagram of the AnyBus_Interface-entity.                        | 57 |

| Figure 35. Block diagram of the Communication_Control-entity.                   | 61 |

| Figure 36. Block diagram of the system.                                         | 67 |

| Figure 37. Principal circuit with its different part boxed in.                  | 69 |

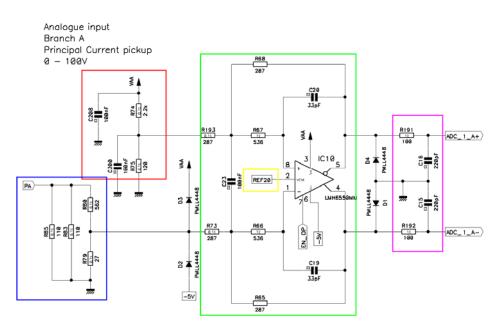

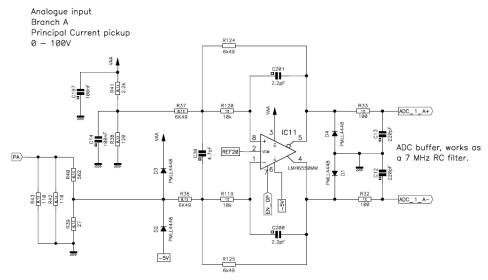

| Figure 38. Annotation and filter for the principal current pickup in branch A   | 73 |

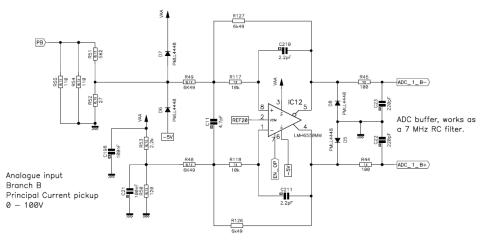

| Figure 39. Annotation and filter for the principal current pickup in branch B   | 73 |

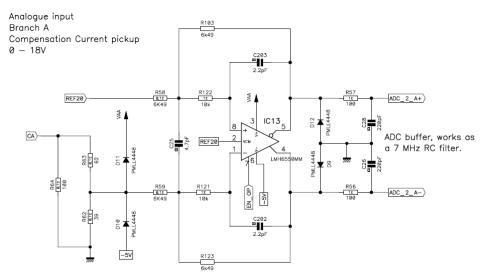

| Figure 40. Annotation and filter for the compensation current pickup in branch  | A. |

|                                                                                 | 74 |

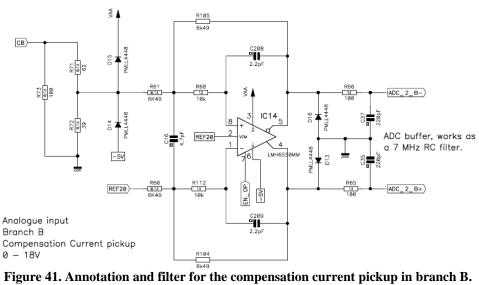

| Figure 41. Annotation and filter for the compensation current pickup in branch  | В. |

|                                                                                 | 74 |

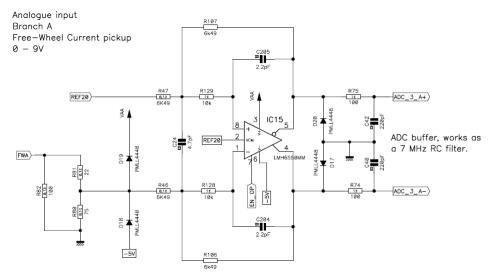

| Figure 42. Annotation and filter for the free-wheel current pickup in branch A. | 75 |

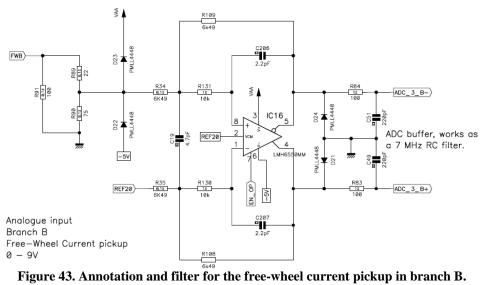

| Figure 43. Annotation and filter for the free-wheel current pickup in branch B. | 75 |

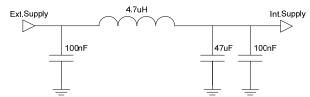

| Figure 44. LC-filter for filtering the supply voltages.                         | 77 |

| Figure 45. An illustration of ground cuts (blue line and boxes)                 | 78 |

| Figure 46. Layout of differential clock lines to the ADCs.                      | 79 |

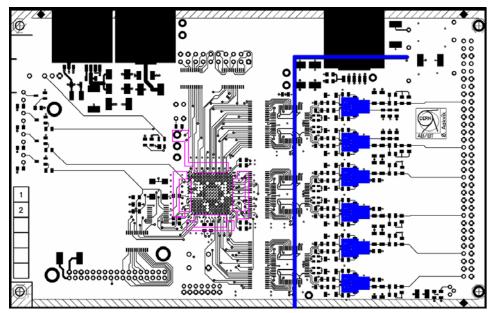

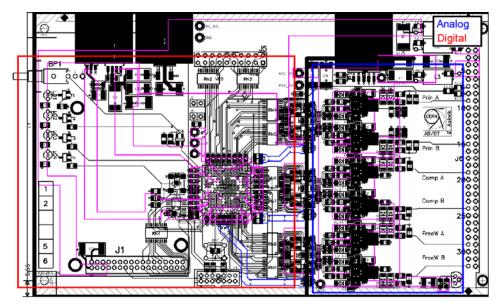

| Figure 47. The top view component-layout of the board, with frames              |    |

| encapsulating the digital (red) and analog (blue) part of the board             | 79 |

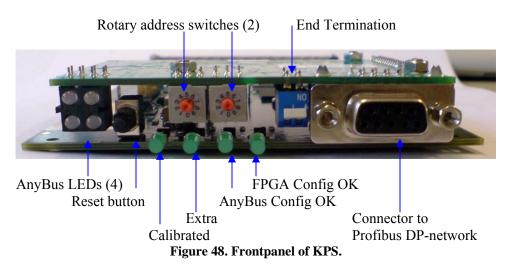

| Figure 48. Frontpanel of KPS                                                    | 81 |

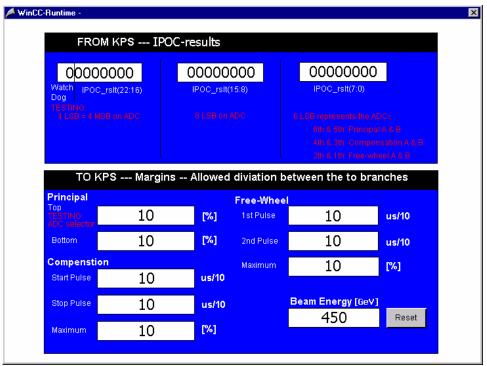

| Figure 49. Software-interface of the KPS.                                       | 82 |

# List of Tables

| Table 1. Description of in- and outputs of the KPS-entity.              | 32 |

|-------------------------------------------------------------------------|----|

| Table 2. Description of in- and outputs of the Clock_Source-entity      | 33 |

| Table 3. Description of in- and outputs of the PowerOn_Reset-entity     | 33 |

| Table 4. Description of in- and outputs of the TriggerDetect-entity     | 33 |

| Table 5. Description of in- and outputs of the Topspeed_filter-entity   | 34 |

| Table 6. Description of in- and outputs of the Topspeed_filter-entity   | 34 |

| Table 7. Description of in- and outputs of the Analysis-entity.         | 36 |

| Table 8. Description of in- and outputs of the Prin_Acqui-entity        | 37 |

| Table 9. Time dependency of the processes in the Prin_Acqui_X-entity    | 38 |

| Table 10. Description of in- and outputs for the Prin_Acqui_X-entity    | 39 |

| Table 11. Description of in- and outputs of the Lowpass-Filter-entity   | 39 |

| Table 12. Description of in- and outputs of the InputCalibration-entity | 39 |

| Table 13. Description of in- and outputs of the Normalization-entity.   | 40 |

| Table 14. Description of in- and outputs of the PulseDetector-entity    | 40 |

| Table 15. Description of in- and outputs of the MaxValue-entity         | 40 |

| Table 16. Description of in- and outputs of the MinValue-entity.        | 41 |

| Table 17. Description of in- and outputs of the Comp_Acqui-entity       | 42 |

| Table 18. Time dependency of the processes in the Comp_Acqui_X-entity   | 43 |

| Table 19. Description of in- and outputs for the Comp_Acqui_X-entity    | 44 |

| Table 20. Description of in- and outputs of the StartOfPulse-entity             | 45  |

|---------------------------------------------------------------------------------|-----|

| Table 21. Description of in- and outputs of the EndOfPulse-entity.              | 46  |

| Table 22. Description of in- and outputs of the FreeW_Acqui-entity              | 47  |

| Table 23. Time dependency of the processes in the FreeW_Acqui_X-entity          | 48  |

| Table 24. Description of in- and outputs for the FreeW_Acqui_X-entity           | 50  |

| Table 25. Description of in- and outputs of the CounterModule-entity            | 51  |

| Table 26. Description of in- and outputs of the IPOC-entity.                    | 52  |

| Table 27. Description of the IPOC output-vector IPOC_Rslt                       | 53  |

| Table 28. Description of in- and outputs of the Evaluator-entity.               | 54  |

| Table 29. Description of in- and outputs of the BeamEnergy_Converter-entity.    | 56  |

| Table 30. Description of in- and outputs of the AnyBus_Interface-entity         | 58  |

| Table 31. Description of in- and outputs of the Data_Indexer-entity             | 59  |

| Table 32. Description of the in- and out-bytes for the AnyBus_Interface-entity. | 60  |

| Table 33. Description of in- and outputs of the Communication_Control-entity.   | .62 |

| Table 34. Description of in- and outputs of the Data_Exchange-entity            | 63  |

| Table 35. Different modes in MKDG.                                              | 66  |

| Table 36. Annotation for the four different input types on the KPS.             | 70  |

# Abbreviations

| Ac    | Acquisition                                    |

|-------|------------------------------------------------|

| ADC   | Analog-to-Digital Converter                    |

| BGA   | Ball-Grid Array                                |

| CERN  | Conseil Européen pour la Recherche Nucléaire - |

|       | European Organization for Nuclear Research     |

| Comp  | Compensation                                   |

| DPRAM | Dual-Port Random Access Memory                 |

| Ev    | Evaluation                                     |

| eV    | electron Volts                                 |

| FPGA  | Field-Programmable Gate Array                  |

| FreeW | Free-wheel                                     |

| G     | $Giga = 10^9$                                  |

| IPOC  | Internal Post Operation Check                  |

| KPS   | Kicker Pulse Surveillance                      |

| LBDS  | LHC Beam Dump System                           |

| LHC   | Large Hadron Collider                          |

| MKD   | Magnet Kicker Dump                             |

| MKDG  | MKD generator                                  |

| Opamp | Operational amplifier                          |

| PCB   | Printed Circuit Board                          |

| PLC   | Programmable Logic Controller                  |

| Prin  | Principal                                      |

| SMD   | Surface Mounted Device                         |

| Т     | $Tera = 10^{12}$                               |

| VHDL  | VLSI Hardware Description Language             |

| VLSI  | Very Large Scale Integrated circuit            |

|       |                                                |

## 1 Introduction

This chapter starts with an introduction of CERN and step by step narrowing it down and in the last section of this chapter, ending up in a description of the field of interest for this project. The content of this chapter is just to introduce CERN, the LHC and its dump-systems to the reader.

1

## **1.1 CERN**

CERN (Conseil Européen pour la Recherche Nucléaire) is the world's largest particle physics laboratory. It was founded back in 1954, formed as collaboration between 12 countries with a goal to gather the intellect of the nations and create a centre of nuclear research. This collaboration has expanded over the years, and there are now 20 member states. These member states are funding the projects and are therefore allowed to contribute in the decision-making process of the Council. There are also many countries and organizations which are involved as observers, which means that they are not in any way involved in the decisionmaking, but only observe and participate in projects at CERN.

Figure 1. Building 40 and 39 on the Meyrin-site of CERN.

There are at the moment a little less than 3000 employees at CERN, additionally there are 6500 visiting personnel, representing 500 different universities and over 80 different countries, doing research at CERN. The newest accelerator project at CERN is the development of the Large Hadron Collider (LHC).

## 1.2 LHC

The Large Hadron Collider (LHC) is the name of the world's largest machine ever. The particle accelerator is being built in a circular tunnel 27 km in circumference. This tunnel is situated between 50 to 175 meters underground, in which straddles the Swiss and French borders on the outskirts of Geneva. The same tunnel originally housed the accelerator for the LEP project, which was terminated and removed form the tunnel in 2005.

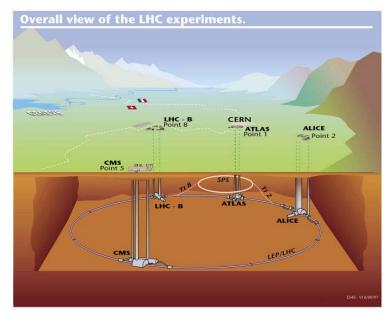

Figure 2. Overall view of the LHC experiment.

The purpose of the LHC is to collide two counter rotating beams of protons or heavy ions. The purpose is to make them collide inside one of the four detectors (Alice, Atlas, CMS and LHCb) places around the ring. Proton-proton collisions are foreseen at energies of 7 TeV per beam. The project is expected to be operational in autumn 2007.

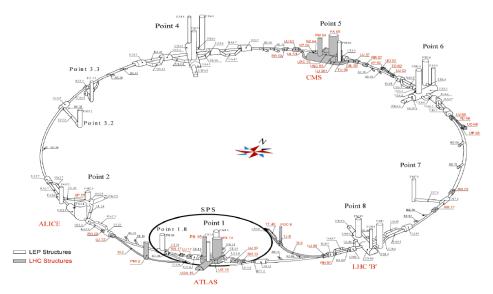

Figure 3. LEP and LHC underground structures.

The accelerator is using super-conductive magnets to guide and accelerate the two counter-rotating particle beams in the ring. Traveling close to the speed of light, it takes the beam less than 90 $\mu$ s to complete one lap in the 27km long accelerator. Each beam has a particle-free gap of  $3\mu$ s.

The high amount of energy of the beams makes absolute control of them at all times necessary. Should the beams deviate from their path around the ring, this could result in severe or even fatal equipment damage.

### 1.3 LBDS

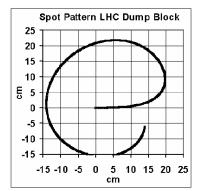

The LHC Beam Dumping System (LBDS) is the safety net of the LHC. This is located at Point 6, situated up to the right in Figure 3. At the end of a physics run or in case of emergency, both beams must be extracted from the accelerator and lead into two separate dump block caverns placed approximately a kilometre away from where the beam leaves the accelerator. A schematic layout of the LBDS can be seen in Figure 4. These dump blocks are built to fully absorb the energy of the beam. The pattern made by the beam on the dump blocks will look like the one shown in Figure 5. The reason of this shape is that the beams are being diluted to spread the beams energy over a larger impact area.

Figure 4. Schematic top view layout of beam dumping system elements around LHC point 6.

To extract the beams, 15 electro-magnets for each beam are placed side by side, which combined deliver a magnetic force strong enough to divert the beam from the ring and into the dump blocks. To avoid partial deflection of the beam, each of the magnets must be turned on in the  $3\mu$ s particle-free gap.

Figure 5. Beam spot figure on absorber block.

The current into the extraction magnets are provided by high-voltage kicker generators, the generator is called a Magnet Kicker Dump Generator (MKDG). When a beam dump is requested it is crucial that at least 14 of the 15 generators

4

are functional. If not, the beam is not properly extracted. The locations of the MKD-systems are at the two 200 meter marks in Figure 4.

To verify that each of the 15 high-voltage pulse generators is fully functional a system to analyze each generator after each run is required. Any small deviations from normal behaviour can then be detected and checked before the next run is initiated.

## 1.4 MKD

The Magnet Kikcer Dump (MKD) is a system consisting of a pulse-generator and an electromagnet. Its task is to horizontally deflect the beam and to send it in the direction of the dump caverns called TCDS. When this is done by 15 MKDs together the beam is extracted completely. Each electromagnet is deflecting the beam an angle of 0.27 mrad. This means that if one MKD is failing the beam would not be properly deflected. The worst case is if the first of the 15 MKDs is failing. This means that the beam deflection will be just below 92% of the total, resulting in possible damage to the LBDS-system. It is therefore crucial that all the 15 MKDs are working.

## 1.5 MKDG

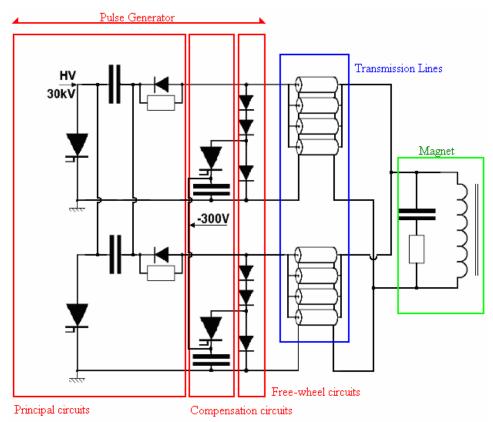

The Magnet Kicker Dump Generator (MKDG) is a high-voltage pulse generator. Its purpose is to deliver a high-voltage pulse to the extraction kicker magnets. This pulse has to reach its maximum value in the time of the particle-free gap in the beam. The MKDG is built with redundancy and contains two equal branches which can cover for each other if one is malfunctioning. This means that at maximum beam energy level and normal behaviour the MKDG is only working at half of what it is capable of, meaning less strain on the electronics and a higher durability.

Each branch can be divided into sub-circuits; these are called the principal-, the compensation- and the free-wheel circuit. The different sub-circuits are illustrated in Figure 6. Each of these sub-circuits has a current pickup sensing the current going through. In sum, there are six current pickups that can be utilized for the analysis of the MKDG. The functional description of the generator falls outside the scope of this paper.

Figure 6. Dual branch generator circuit principal layout.

## 2 System requirements

The Kicker Pulse Surveillance (KPS) is to handle the Internal Post Operation Check (IPOC) of a Magnet Kicker Dump Generator (MKDG) in the Magnet Kicker Dump-System (MKD-system).

The task is to develop a full functional prototype, able to acquire the six output signals from the MKDG, to analyze them and then communicate the results to a PLC via a Profibus DP-network.

The firmware on the KPS has to be implemented in VHDL, and the code has to be structured as a state machine with a finite lifecycle. The system should have to be rearmed before use after an analysis. It will spend most of its time in a wait-state, waiting for the MKDG to pulse.

The KPS has to be able to adjust the analysis to the beam energy level and the margins of tolerated error communicated over the Profibus DP-network.

The KPS has to be able to make a thorough analysis of the MKDG to ensure that it is ready for a new run.

The system has to be able to handle and acquire input voltages from -33V up to 55V, and be able to withstand in a worst case scenario input voltages from -66V up to 100V.

The whole system should be fitted on a 160mm x 100mm sized printed circuit board (PCB).

## 3 Preliminary Studies

## 3.1 Introduction

This chapter present this projects earliest conducted studies, before starting the design of the Kicker Pulse Surveillance-prototype (KPS). It contains a complex study of six outputs on the MKDG and some information on the programmable device and the communication interface.

### **3.2 Tools**

The tools used for the preliminary studies were an oscilloscope with a dataoutput terminal and a computer with Matlab. The oscilloscope provided the rawdata for the analysis. Matlab and Excel were used for the processing, analysis and for drawing and displaying plots.

## **3.3** Measurements on the MKDG

This section presents the measurements conducted on the MKDG. The section is the base for the designing of the analog hardware and the digital firmware. The plots in sections 3.3.1, 3.3.2 and 3.3.3 shows the behaviour of the currents in the pick-ups named CTs1, CTc1 and CTf1 respectively. The pickup names are from the "MKD system, Extended Circuit Diagram – High Voltage Power Part" – schematics [8]. The objective of these measurements is to characterize the different parts of the MKDG.

## 3.3.1 Principal Circuit

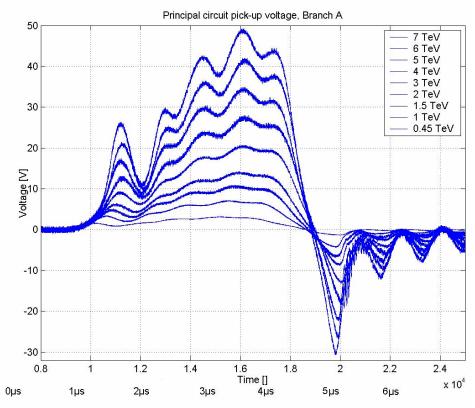

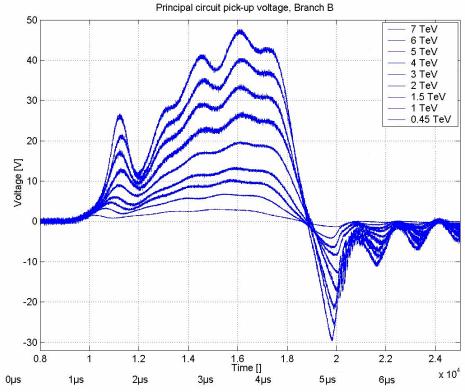

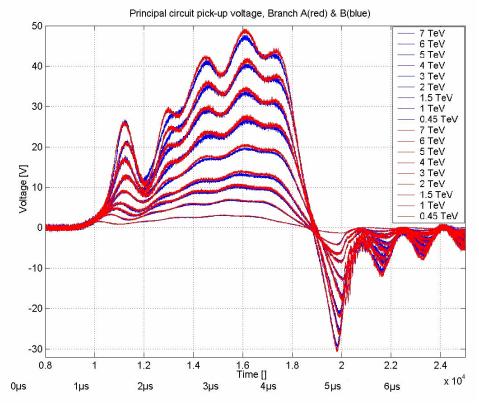

The plots in Figure 7 and Figure 8 illustrates the behaviour of the voltage in the pickup induced by the currents in the principal circuit for branches A and B and Figure 9 shows the current in the two branches together, for comparison. The currents are measured at nine different beam energy levels, starting at 450 GeV, which is the injection beam energy level, hence the lowest for the LHC, and ending at 7 TeV, which is theoretically the highest beam energy level for the LHC.

The sensitivity of the pickup is 10 mV/A, resulting in a 5 mV/A sensitivity on the output of a 50 $\Omega$  terminated transmission line.

The range of the signal is as Figure 9 shows, from approximately +50 V to -30 V. The input range should at least be 80 V. The ground level of the signal is at 3/8 of the total range.

There is a factor of 16 from the lowest input signal to the highest. This change can be represented is 4 bits.

Figure 7. Principal circuit pick-up voltage, Branch A. The lowest graph is for the 450 GeV and the highest for the 7 TeV.

Figure 8. Principal circuit pick-up voltage, Branch B. The lowest graph is for the 450 GeV and the highest for the 7 TeV.

Figure 9. Principal circuit pick-up voltage, Branch A(red) and B(blue)

### 3.3.1.1 Measurements Analysis

The required analyses on the principal circuits are to confirm that both the positive and the negative peak currents through the pick-ups are within the margins and to confirm that the positive peak currents are at maximum before 4  $\mu$ s.

#### 3.3.1.1.1 Analog Domain

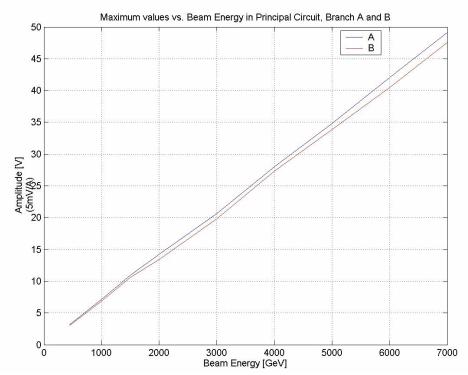

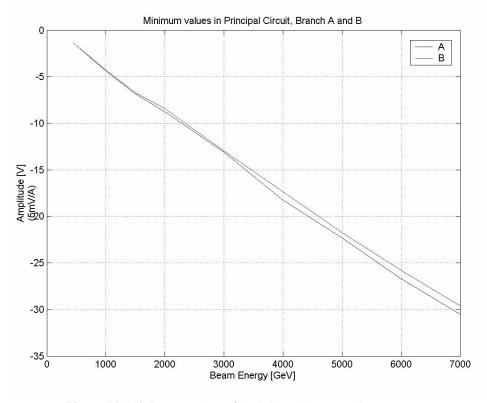

Processing of the measurements reveals that the maximum and minimum amplitudes are linearly proportional with respect to the beam energy levels. These dependencies can be seen in Figure 10 and Figure 11. Calculations show that these graphs are above 99% linear and have a crossing through origo.

Figure 10. Maximum values of both branches w.r.t. beam energy.

Figure 11. Minimum values of both branches w.r.t. beam energy.

Figure 10 shows the maximum amplitude of the two branches with respect to the beam energy, when both are pulsing. The linearity of the current with respect to the beam energy is appreciated and will simplify the implementation of the analysis in hardware.

The function for the plot in Figure 10 is:

Maximum values[V] =  $\frac{52 \text{ V}}{7500 \text{ GeV}}$  \* BeamEnergy[GeV]

The function for the plot in Figure 11 is:

Minimum values[V] =

$$\frac{32 \text{ V}}{7500 \text{ GeV}}$$

\* BeamEnergy[GeV]

The functions are interpolated to 7500 GeV to ease the implementation in hardware, since 7500 GeV corresponds to  $FFFF_{hex}$  in digital representation. The obtained functions are middling functions, made from the values of both branches.

These functions are only to be used in the computation of the margins for the deviation within the branches. This means that these functions are to be multiplied with the allowed percentage of deviation within the branches. Since the linearity of the plot is not total, the set percentage for the margins may have a

deviation of about 1%. This means that setting the margins to 10%, can at some beam energy levels mean that the actual margin is only 9% or as much as 11%.

The range of the signal on the input is as previously mentioned from approximately +50V to -30V, but this is for 7 TeV, the system has to take into account the possibility of the generator pulsing at 7.5 TeV. To do this an additional 10% is added, making the input signal range approximately from +55V to -33V. The total range is then approximately 88V.

#### 3.3.1.1.2 Digital domain

The analog input signal range has to be annotated down to a small signal electronics level before entering the converter:

Input annotation =  $\frac{\text{Maximum input range of input signal}}{\text{Maximum input range of converter}} = \frac{88 \text{ V}}{4 \text{ V}} = 22 \text{ times}$

If using a 12 bit ADC the resolution of the measurements is:

LSB:

$$\frac{88 \text{ V}}{2^{12}} = 21.4 \text{ mV}$$

If the ADC is 12 bits there is no need for all the 16 bits of resolution that the beam energy are presented in. This is solved by looking at the 12 MSB of the beam energy. The range of the beam energy, as with the output of the converters will then be  $000_{hex} - FFF_{hex}$  or  $0_{dec} - 4095_{dec}$ .

There are three functions necessary for the principal circuit. The first function is for the acquisition. This is the threshold for detecting that there is current in the pickup. It is set to approximately 50% of the maximum of the pulse with respect to the beam energy. The second and third function is for the analysis. These functions output the margins for the allowed deviation between the two branches.

#### **Equation 1. Threshold function in binary:**

Trigger - level[LSB] =  $\frac{2}{8}$  \* BeamEnergy[GeV]

#### **Equation 2. Maximum-value function in binary:**

Maximum - value conversion, analog to digital  $\Rightarrow$

$\frac{\text{Maximum - value}}{\text{LSB}} = \frac{52 \text{ V}}{21.4 \text{ mV}} = 2442 \text{ LSB}$

Maximum - value margin[LSB] =  $\frac{2442}{4095}$  \* Beam Energy[GeV] \*  $\frac{\text{Margin}[\%]}{100}$

Maximum - value margin[LSB] =  $\frac{2442}{4095 * 100}$  \* Beam Energy[GeV] \* Margin[%]

Maximum - value margin[LSB]  $\approx \frac{49}{2^{13}} * \text{Beam Energy}[\text{GeV}] * \text{Margin}[\%]$

#### **Equation 3. Minimum-value function in binary:**

Minimum - value conversion analog to digital  $\Rightarrow$

$\frac{\text{Minimum - value}}{\text{LSB}} = \frac{32\text{V}}{21.4\text{mV}} = 1503 \text{ LSB}$ Minimum - value margin[LSB] =  $\frac{1503}{4095}$  \* Beam Energy[GeV] \*  $\frac{\text{Margin}[\%]}{100}$ Minimum - value margin[LSB] =  $\frac{1503}{4095}$  \* Beam Energy[GeV] \*  $\frac{\text{Margin}[\%]}{100}$ Minimum - value margin[LSB] =  $\frac{1503}{4095 * 100}$  \* Beam Energy[GeV] \* Margin[%]

Minimum - value margin[LSB]  $\approx \frac{15}{2^{12}}$  \* Beam Energy[GeV] \* Margin[%]

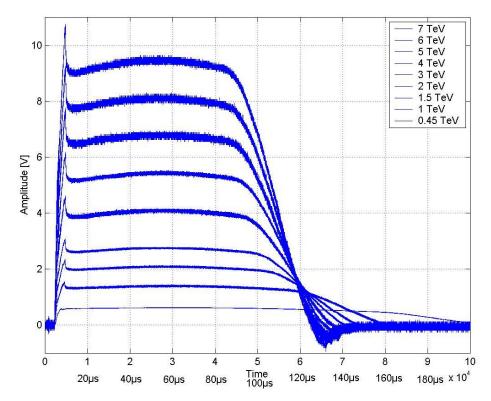

## 3.3.2 Compensation circuit

The plot in Figure 12 illustrates the behaviour of the voltage in the pickup induced by the currents in the compensation circuit for branch B. The current is measured at nine different beam energy levels, starting at 450 GeV, which is the injection beam energy level for the LHC, and ends at 7 TeV, which is the highest beam energy level.

The sensitivity of the pickup is 1 mV/A, resulting in a 0.5 mV/A sensitivity on the output of a  $50\Omega$  terminated transmission line.

The range of the signal is as Figure 12 shows, from 0 V to approximately 9.5 V. This is when the spike at the beginning is excluded. The ground level of the signal is at zero of the total range.

There is a factor of 16 from the lowest input signal to the highest. This change can be represented is 4 bits.

Figure 12. Compensation circuit pick-up voltage for branch B. The lowest graph is for the 450 GeV and the highest for the 7 TeV.

#### **3.3.2.1** Measurements Analysis

The acquisition points needed on the compensation circuit is a confirmation of that the start and stop of the pulse and the maximum value of the midsection on the pulse are within the margins.

#### 3.3.2.1.1 Analog Domain

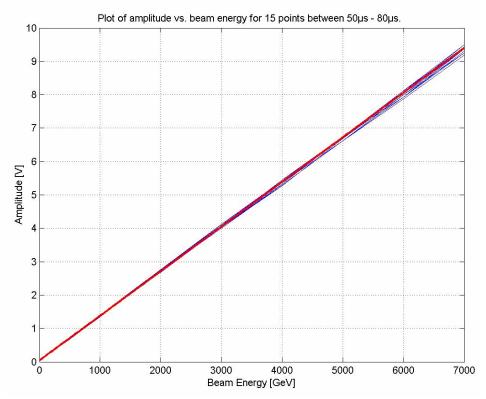

Processing of the measurements reveals that the behaviour of the midsections maximum amplitude is linearly proportional with respect to the beam energy. This is illustrated in Figure 13. Calculations show that these graphs are above 99% linear and have a crossing through origo.

Figure 13. Amplitude vs. beam energy for 15 points between 50µs and 80µs.

Figure 13 shows the amplitude of the midsection of the pulses in Figure 12. The points are taken at 15 different points between  $50\mu s$  and  $80\mu s$  and on nine different beam energy levels. The thick (red) line in Figure 13 shows the linear approximation of these points.

The function for the plot in Figure 13 is:

Maximum values[V] =

$$\frac{10 \text{ V}}{7500 \text{ GeV}}$$

\* BeamEnergy[GeV]

The function is also here, as with the principal circuit, interpolated to 7500 GeV to ease the implementation in hardware, since 7500 GeV corresponds to  $FFFF_{hex}$  in digital representation.

The function is only to be used in the computation of the margins for the deviation within the branches. This means that the function is to be multiplied with the allowed percentage of deviation within the branches.

The range of the signal on the input is as illustrated in Figure 8 from approximately 0 V to 9.34 V, but this is for 7 TeV, the system has to take into account the possibility of the generator pulsing at 7.5 TeV. To do this an additional 10% is added, making the input signal range approximately from 0 V to  $\pm 10.3$  V.

The threshold for the triggering of a counter to measure the start and stop of the pulse can be set to half the beam energy level. This can be done since the maximum amplitude at the maximum beam energy level corresponds approximately to the maximum values of the ADC. Meaning that setting the threshold to half the value of the beam energy will be the same as setting the threshold at approximately 50% of the maximum pulse value with respect to the beam energy.

#### **3.3.2.1.2** Digital domain

The analog input signal range has to be annotated down to a small signal electronics level before entering the converter:

Input annotation =  $\frac{\text{Maximum input range of input signal}}{\text{Maximum input range of converter}} = \frac{10.3 \text{ V}}{4 \text{ V}} = 2.58 \text{ times}$

If using a 12 bit ADCs the resolution of the measurements is:

LSB:

$$\frac{10.3 \text{ V}}{2^{12}} = 2.52 \text{ mV}$$

As in the principal circuit, if the ADC is 12 bits there is no use for all 16 bits of resolution that the beam energy are presented in. Only the 12 MSB of the beam energy are used. The range of the beam energy, as with the output of the converters will then be  $000_{hex} - FFF_{hex}$  or  $0_{dec} - 4095_{dec}$ .

There are two functions necessary for the compensation circuit. The first function is for the acquisition. This is the threshold for triggering a sampling of the startand the stop-time of the pulse. It is set to approximately 50% of the maximum of the pulse with respect to the beam energy. This function can be made more accurate, but this might not be necessary. The second function is for the analysis. The function outputs the margin for the allowed deviation between the two branches.

#### **Equation 4. Threshold function in binary:**

Threshold[LSB] =  $\frac{1}{2}$  \* BeamEnergy[GeV]

#### **Equation 5. Maximum-value function in bits:**

Maximum - value conversion analog to digital  $\Rightarrow$

$$\frac{\text{Max Value}}{\text{LSB}} = \frac{10 \text{ V}}{2.52 \text{ mV}} = 3968 \text{ LSB}$$

Maximum - value margin[LSB] =  $\frac{3968}{4095}$  \* BeamEnergy[GeV] \*  $\frac{\text{Margin}[\%]}{100}$

Maximum - value margin[LSB] =  $\frac{3968}{4095 * 100}$  \* BeamEnergy[GeV] \* Margin[%]

Maximum - value margin[LSB]  $\approx \frac{5}{2^9} * \text{BeamEnergy}[\text{GeV}] * \text{Margin}[\%]$

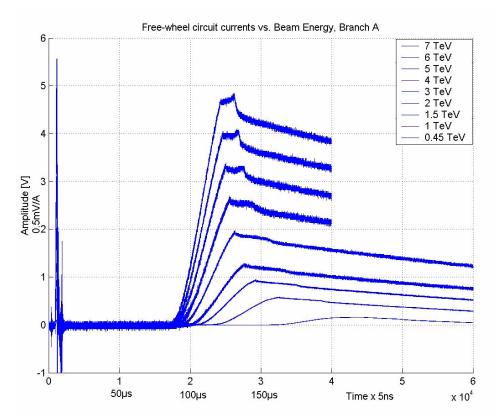

### **3.3.3 Free-Wheel Circuit**

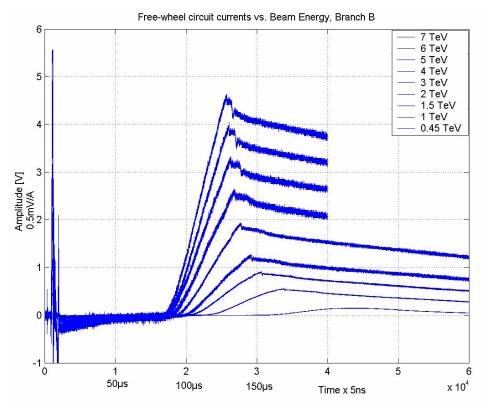

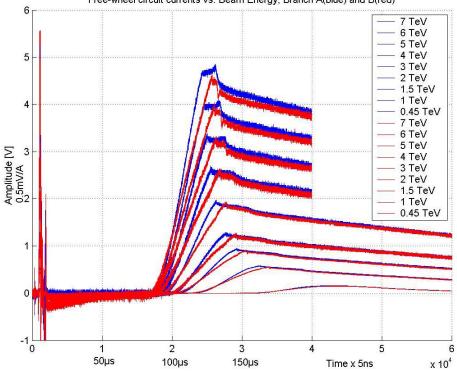

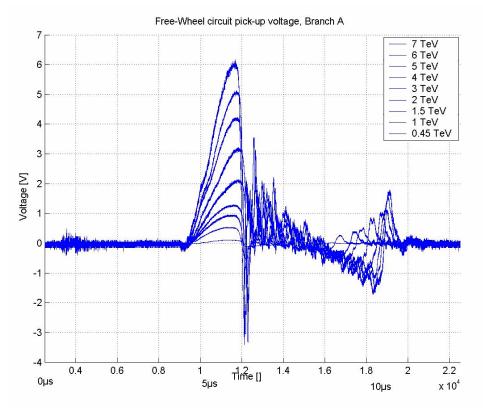

The plots in Figure 14 and Figure 15 illustrates the behaviour of the voltage in the pickup in the branches A and B, as a function of time at different beam energy levels. Figure 16 shows both functions in one plot. A zoom in on the spikes in the first  $10\mu$ s of these three plots are depicted in Figure 17. The current is measured at nine different beam energy levels, from 450 GeV to 7 TeV.

The sensitivity of the pickup is 2 mV/A, resulting in a 1 mV/A sensitivity on the output of a 50 $\Omega$  terminated transmission line.

The range of the signal is as Figure 12 shows, from 0 V to approximately 4.9 V. This is when the spike at the beginning is excluded. The ground level of the signal is at zero of the total range.

There is a factor of 16 from the lowest input signal to the highest. This change can be represented is 4 bits.

Figure 14. Free-wheel circuit currents vs. Beam Energy, Branch A. The lowest graph is for the 450 GeV and the highest for the 7 TeV.

Figure 15. Free-wheel circuit currents vs. Beam Energy, Branch B. The lowest graph is for the 450 GeV and the highest for the 7 TeV.

Free-wheel circuit currents vs. Beam Energy, Branch A(blue) and B(red)

Figure 16. Free-wheel circuit currents vs. Beam Energy, Branch A(blue) and B(red)

Figure 17. Free-wheel circuit currents vs. Beam energy, branch A, zoom on startspike. The lowest graph is for the 450 GeV and the highest for the 7 TeV.

### **3.3.3.1** Measurements Analysis

The required analysis on the free-wheel circuit is to confirmation that the first and then the second pulse comes simultaneously in the two branches, that there are now current in the section between the two pulses and that the maximum value of the second pulse is within the margins.

#### 3.3.3.1.1 Analog domain

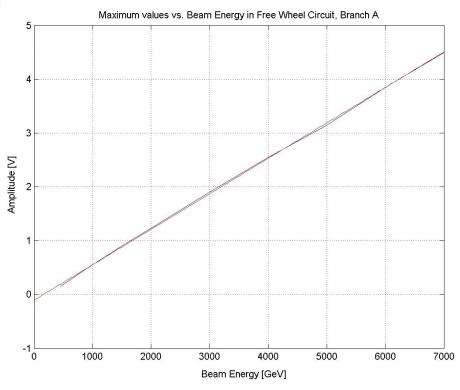

Processing of the measurements reveals that the behaviour of the second pulse maximum amplitude with respect to the beam energy is linearly proportional with respect to the beam energy levels. This is illustrated in Figure 18. The linear approximation to the measurement is close to 100% accurate.

Figure 18. Maximum values vs. beam energy in Free-wheel circuit in branch A(blue), and linear approximation function(red).

Figure 18 shows the maximum amplitude of the second pulse starting at about 90µs in Figure 16. The function is not totally linear so a linear approximation has been made. This is laid on top(red) of the point of the maximum amplitude(blue).

The function for the plot in Figure 18 is:

Maximum values[V] =  $\frac{5.4 \text{ V}}{7500 \text{ GeV}} * \text{BeamEnergy[GeV]}$

The function is also here, as with the principal and compensation circuit, interpolated to 7500 GeV to ease the implementation in hard-ware, since 7500 GeV corresponds to  $FFFF_{hex}$  in digital representation.

The function is only to be used in the computation of the margins for the deviation within the branches. This means that the function is to be multiplied with the allowed percentage of deviation within the branches.

The range of the signal on the input is as illustrated in Figure 17 from approximately 0 V to 4.9 V, but this is for 7 TeV, the system has to take into account the possibility of the generator pulsing at 7.5 TeV. To do this an additional 10% is added, making the input signal range approximately from 0 V to +5.4 V.

The threshold for the triggering of a counter to measure the start of the two pulses, the thresholds can also here as with the compensation circuit, be set to half the beam energy level. This can be done since the maximum amplitude at the maximum beam energy level corresponds approximately to the maximum values of the ADC. Meaning that setting the threshold to half the value of the beam energy will be the same as setting the threshold at approximately 50% of the maximum pulse value with respect to the beam energy.

### 3.3.3.1.2 Digital Domain

The analog input signal range has to be annotated down to a small signal electronics level before entering the converter:

Input annotation =  $\frac{\text{Maximum input range of input signal}}{\text{Maximum input range of converter}} = \frac{5.4 \text{ V}}{4 \text{ V}} = 1.35 \text{ times}$

If using a 12 bit ADCs the resolution of the measurements is:

LSB:

$$\frac{5.4 \text{ V}}{2^{12}} = 1.32 \text{ mV}$$

The used ADCs are 12 bits so there is also here no point in using all 16 bits of resolution that the beam energy are presented in. This is solved by looking at the 12 MSB of the beam energy. The range of the beam energy is  $000_{hex} - FFF_{hex}$  or  $0_{dec} - 4095_{dec}$ .

There are three functions necessary for the free-wheel circuit. The first two functions are for the acquisition; one for the threshold for sampling the start-time of the two pulses and the other for the threshold for the no pulse section. The threshold for the first and second pulse is set to approximately 50% of the maximum of the pulse with respect to the beam energy. This function can be made more accurate, but this might not be necessary. The third function is for the analysis. This is linearly proportional to the beam energy and output the margins for the allowed deviation between the two branches.

### Equation 6. First and second threshold function in binary:

Threshold[LSB] =  $\frac{1}{2}$  \* BeamEnergy[GeV]

### Equation 7. No pulse section threshold function in binary:

Threshold[LSB] =  $\frac{1}{2^6}$  \* BeamEnergy[GeV]

#### **Equation 8. Maximum-value function in binary:**

Maximum - value conversion, analog to digital  $\Rightarrow$

$$\frac{\text{Max Value}}{\text{LSB}} = \frac{4.82 \text{ V}}{1.32 \text{ mV}} = 3652 \text{ LSB}$$

Maximum - value margin[LSB] =  $\frac{3652}{4095}$  \* BeamEnergy[GeV] \*  $\frac{\text{Margin}[\%]}{100}$

Maximum - value margin[LSB] =  $\frac{3652}{4095 * 100}$  \* BeamEnergy[GeV] \* Margin[%]

Maximum - value margin[LSB]  $\approx \frac{9}{2^{10}} * \text{BeamEnergy}[\text{GeV}] * \text{Margin}[\%]$

# **3.4 FPGA**

For these kinds of applications the preferred device to use is a FPGA. The flexibility and low cost makes it a perfect choice for prototyping and minor production quantities.

The use of FPGAs in electronics at CERN is rather common and the most used device in the Electronics Control-section is the Xilinx Spartan 3, XC3S1000-4FT256, thus the knowledge and data on this device is extensive.

# 3.4.1 Xilinx Spartan 3, XC3S1000-4FT256.

This device has great possibilities. It has:

- 256 pins including power and ground.

- 173 pins can be assigned as in- or outputs.

- 15000 flip-flops and 4-input LUTs.

- 24 block RAMs, each can contain 18kbits.

- 24 18bit multipliers.

- 4 DCM, digital clock managers.

- 1 Boundary Scan.

All this helps making it into a very powerful and user-friendly device. [9]

Figure 19. Picture shows a Xilinx Spartan 3, XC3S1000-4FT256C (17x17mm).

# 3.5 Profibus DP

The KPS and a PLC are to communicate through an industrial network standard called Profibus DP. Profibus DP is the most used third-party embedded fieldbus standard today. This is because of its robustness and the rather high transfer rates. The maximum transfer rate is 12Mbit/s.

Communication over a Profibus DP-network is common in electronics at CERN, thus the problem has been solved before. It has been solved by using a module provided by HMS Industrial Networks in Sweden. This module is called AnyBus-S and is configured as a slave in this network.

# 3.5.1 AnyBus-S module

The time saved by using this module is a great advantage in a time-limited design process. This module has a 34 pin connector, using 25 of them to communicate with a FPGA, a CPLD or a microcontroller of any sort. The module is depicted in Figure 20 and Figure 21.

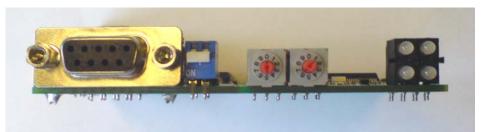

There can be 126 other slaves connected to one master. To utilize 127 slaves, this has to be done in the modules software, this because in hardware the two rotary switches on the front panel only allow 100 different addresses. The interface towards the Profibus DP-network is a 9-pins D-connector. Other interfaces on the module are, as can be seen in Figure 20, two rotary switches and a 34-pin connector as before mentioned, an end termination on/off switch and 4 LEDs, although one of the LEDs are not in use. [5][6]

Figure 20. User interface of the AnyBus-S module.

# 3.5.1.1 Initialization

When powering up the AnyBus-S module, it has to be initialized. This is done by writing three messages to the Mailbox In area, and then verifying the response from the network master, this is read from the Mailbox Out area. The middle one of the three messages contains information about the length of the input and output frames.

The initialization sequence is described in detail in the AnyBus Slave Design Guide [5], alternative 1.

### 3.5.1.2 Interface

The module is easy to use because the interface to the module is equivalent to that of a RAM. The thing is that the AnyBus-S module interface actually is a Dual-Port RAM, which the user can access on one side and the network can access on the other side. Every time there is an update on this RAM a bit is sat and either the user or the network reads the content of the RAM.

Figure 21. The AnyBus-S module.

# 4 VHDL Entity description

# 4.1 Introduction

This chapter presents the structure of the VHDL-code used to configure the FPGA on the KPS. The code is presented in steps starting at the top of the hierarchy, presenting block-diagram, tables and text explaining every sub-entity. The development of firmware for the FPGA was an important part of this project.

### **4.2** Tools

Xilinx<sup>TM</sup> ISE 7.1i was used for handling every aspect of the VHDL-code, from code-editing to making the programming-file for the FPGA. The early stage simulations and debugging of the code was done in the ModelSim<sup>TM</sup> XE III 6.0a Simulator. The finishing touches of debugging was done using ChipScope<sup>TM</sup> Pro 7.1i, a add-on program for Xilinx<sup>TM</sup> ISE enabling realtime debugging on the FPGA. This is done my implementing a separate core in the FPGA which communicates with the Chipscope<sup>TM</sup>-application on the PC through the JTAG-interface. Every value inside the FPGA can then be monitored.

# 4.3 KPS

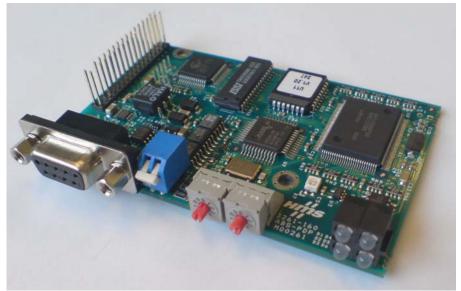

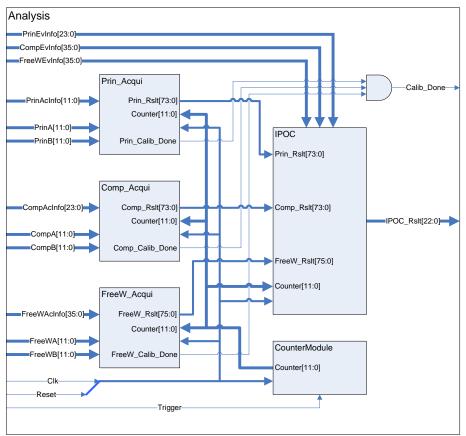

The Kicker Pulse Surveillance (KPS)-entity is the top-entity containing all firmware descriptions for the FPGA. These descriptions are divided into smaller entities. The system hierarchy of entities is shown in Figure 22 and the entities with connections are illustrated in Figure 23. The entity-names with numbers behind in Figure 22 are instantiated multiple times. The analysis part of the system is designed with 12bits and the transfer part is 8bits.

Figure 22. Hierarchical presentation of the entities in the KPS.

There are eight sub-entities in the KPS-entity:

The Clock\_Source-entity consists of a Xilinx Clock-DLL. This is providing the FPGA with a clean clock-signal out of the input from the external crystal.

The PowerOn\_Reset-entity is making sure that the FPGA is properly reset during power up.

The TriggerDetect-entity detects the triggering pulse and indicates that there has been a triggering until reset.

The Topspeed\_filter-entity is an oversampling-filter converting four samples in to one.

The ADC\_Control-entity handles the signals concerning the ADCs and the Opamps.

The Analysis-entity is doing all the acquisition and analysis of the input values.

The BeamEnergy\_Converter-entity is converting the beam energy level into thresholds and margins used in the acquisition and analysis of the input signals.

The AnyBus\_Interface-entity controls the transfers between the external AnyBus-module and the rest of the FPGA.

Figure 23. Block diagram of KPS-entity.

| Table 1. Description of m- and outputs of the KFS-entity. |       |                                                                                         |  |

|-----------------------------------------------------------|-------|-----------------------------------------------------------------------------------------|--|

| BDTrigger                                                 | in    | Input for beam dump triggering signal.                                                  |  |

| PrinA[11:0]                                               | in    | Signals from the ADC sampling the principal                                             |  |

| PrinB[11:0]                                               | in    | circuit pickups branches A and B.                                                       |  |

| CompA[11:0]                                               | in    | Signals from the ADC sampling the compensation                                          |  |

| CompB[11:0]                                               | in    | circuit pickups branches A and B.                                                       |  |

| FreeWA[11:0]                                              | in    | Signals from the ADC sampling the free-wheel                                            |  |

| FreeWB[11:0]                                              | in    | circuit pickups branches A and B.                                                       |  |

| Calib_Done                                                | out   | Connected to the left-most LED. Signal is high and LED is on when calibration complete. |  |

| ADC_Clk_P                                                 | out   | Positive and pogetive differential clock signal                                         |  |

| ADC_Clk_N                                                 | out   | Positive and negative differential clock signal.                                        |  |

| ADC_PDn                                                   | out   | To power down ADCs.                                                                     |  |

| Opamp_E                                                   | out   | To power down the Opamps.                                                               |  |

| Xtal                                                      | in    | Input from crystal oscillator.                                                          |  |

| ResetHardn                                                | in    | Input from pushbutton.                                                                  |  |

| A[11:0]                                                   | out   | For addressing the AnyBus-S module.                                                     |  |

| D[11:0]                                                   | inout | Bidirectional databus for data exchange with the AnyBus-S module.                       |  |

| BUSY_n                                                    | in    |                                                                                         |  |

| IRQ_n                                                     | in    |                                                                                         |  |

| RD_n                                                      | out   | Control signals for AnyBus-S module.                                                    |  |

| WR_n                                                      | out   | Control signals for AnyBus-5 module.                                                    |  |

| CE_n                                                      | out   |                                                                                         |  |

| RESET_n                                                   | out   |                                                                                         |  |

| Diode                                                     | out   | Connected to LED, indicates correct initialization of AnyBus-S module.                  |  |

Table 1. Description of in- and outputs of the KPS-entity.

# 4.3.1 UserSettings-package

This is a package-file containing all the presets that can be made to the KPS system. These are all constants that set the initial values for registers in some of the many entities.

# 4.3.2 Clock\_Source

This is a sub-entity of the KPS-entity, illustrated in Figure 23. The Clock\_Source entity will provide a clock signal to all the entities requiring it. It will utilize the architecture-specific Clock-DLL (Delay-Locked Loop) of the Xilinx Spartan 3 family. The entity will provide a clean, stable clock signal from the hardware crystal oscillator on the board. The Clock-DLL will ensure fast transitions and a 50% duty cycle. It will cancel out any clock delay within the FPGA which minimizes clock skews and timing problems. The entity outputs a 10 and 40 MHz clock-signal.

Table 2. Description of in- and outputs of the Clock\_Source-entity.

| Xtal    | in  | Input from crystal oscillator.            |

|---------|-----|-------------------------------------------|

| Clk     | out | 10 MHz clock divided and shaped in DCM.   |

| Clk_Org | out | 40 MHz clock undivided and shaped in DCM. |

# 4.3.3 PowerOn\_Reset

This is a sub-entity of the KPS-entity, illustrated in Figure 23. The PowerOn\_Reset-entity will issue a power-on reset (POR) pulse to the AnyBus\_Interface-entity to bring it into a known and defined state. The entity will be implemented using registers from the Xilinx Primitives library, which have a known start-up value.

Table 3. Description of in- and outputs of the PowerOn\_Reset-entity.

| Clk | in  | System-clock. 10MHz.                                             |

|-----|-----|------------------------------------------------------------------|

| POR | out | Reset signal which stays high for 5 clock-cycles after power on. |

# 4.3.4 TriggerDetect

This is a sub-entity of the KPS-entity, illustrated in Figure 23. The TriggerDetect-entity is set to keep the output high when there has been issued a beam dump. The output returns to low when it is reset.

| Table 4. Description of m <sup>2</sup> and outputs of the Trigger Detect-entity. |     |                                                         |  |

|----------------------------------------------------------------------------------|-----|---------------------------------------------------------|--|

| BDTrigger                                                                        | in  | Input from the beam dump triggering signal              |  |

| Trigger                                                                          | out | Indication of that a beam dump triggering has occurred. |  |

Table 4. Description of in- and outputs of the TriggerDetect-entity.

# 4.3.5 Topspeed\_filter

This is a sub-entity of the KPS-entity, illustrated in Figure 23. The Topspeed\_filter is working as a bridge between the FPGA and the ADCs, converting four and four samples from the ADCs running at 40MHz to one sample for the FPGA running at 10MHz. Its function is an oversampling filter removing noise from the inputs of the FPGA.

| Clk             | in  | System-clock. 10MHz.   |

|-----------------|-----|------------------------|

| ClkOrg          | in  | Original Clock. 40MHz. |

| PrinA[11:0]     | in  | 40MHz input.           |

| PrinB[11:0]     | in  | 40MHz input.           |

| CompA[11:0]     | in  | 40MHz input.           |

| CompB[11:0]     | in  | 40MHz input.           |

| FreeWA[11:0]    | in  | 40MHz input.           |

| FreeWB[11:0]    | in  | 40MHz input.           |

| PrinAout[11:0]  | out | 10MHz output.          |

| PrinBout[11:0]  | out | 10MHz output.          |

| CompAout[11:0]  | out | 10MHz output.          |

| CompBout[11:0]  | out | 10MHz output.          |

| FreeWAout[11:0] | out | 10MHz output.          |

| FreeWBout[11:0] | out | 10MHz output.          |

Table 5. Description of in- and outputs of the Topspeed\_filter-entity.

# 4.3.6 ADC\_Control

This is a sub-entity of the KPS-entity, illustrated in Figure 23. The ADC\_Control is controlling all the control-signals to the ADCs and Opamps. This means powering up the ADCs and Opamps on reset and powering them down when the KPS-status is set to "Finished".

| Table 6. Descri | ption | of in- and outputs of the Topspeed_filter-entity. |

|-----------------|-------|---------------------------------------------------|

| 011.0           | •     |                                                   |

| ClkOrg      | in  | Original Clock. 40MHz.                                 |

|-------------|-----|--------------------------------------------------------|

| Active[2:0] | in  | Input from the IPOC_rslt, only the KPS-status. (3bits) |

| P_Clk_P     | out | Positive output clock to the principal ADC.            |

| P_Clk_N     | out | Negative output clock to the principal ADC.            |

| C_Clk_P     | out | Positive output clock to the compensation ADC.         |

| C_Clk_N     | out | Negative output clock to the compensation ADC.         |

| F_Clk_P     | out | Positive output clock to the free-wheel ADC.           |

| F_Clk_N     | out | Negative output clock to the free-wheel ADC.           |

| P_PDn       | out | Power-down signal for principal ADC. Active-low.       |

| C_PDn       | out | Power-down signal for compensation ADC. Active-low.    |

| F_PDn       | out | Power-down signal for free-wheel ADC. Active-low.      |

| Opamp_E     | out | Power-down signal for the Opamps. Active-high.         |

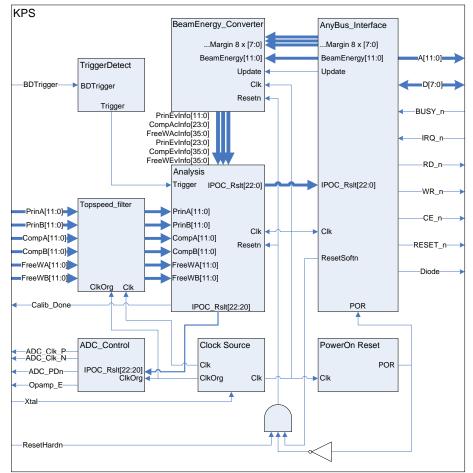

# 4.3.7 Analysis

This is a sub-entity of the KPS-entity, illustrated in Figure 23. This entity handles all acquisition and analysis of the signals from the KPS. The entity is illustrated in Figure 24 and the different in- and outputs are described in Table 7.

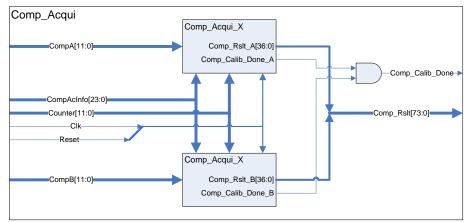

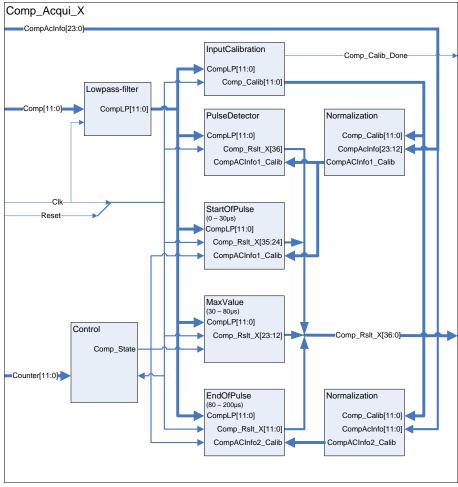

The Prin\_Acqui-, Comp\_Acqui- and FreeW\_Acqui-entities acquires the two principal circuit signals, the two compensation circuit signals and the two free-wheel circuit-signals respectively. These entities are better describes in sections 4.3.7.1, 4.3.7.2 and 4.3.7.3.

The IPOC-entity is making the analysis when the three acquisition entities are finished. The analyses are made with respect to the three inputted evaluation vectors (-EvInfo). The entity is better described in section 4.3.7.5.

The evaluation and acquisition information are updated each time the AnyBus-S module receives a beam energy or margin update. This information is then sent from the BeamEnergy\_Converter, described in section 4.4.

The CounterModule-entity is the heartbeat of the system and coordinates all the different acquisitions and analysis. It is set of by the beam dump trigger. The entity is better described in section 4.3.7.4.

Figure 24. Block diagram of the Analysis-entity.

| Clk               | in  | System clock. Running at 10MHz.                                                                                               |

|-------------------|-----|-------------------------------------------------------------------------------------------------------------------------------|

| Reset             | in  | System reset. Active low.                                                                                                     |

| Trigger           | in  | Trigger signal from TriggerDetect-entity.                                                                                     |

| Counter[11:0]     | in  | Input-signal from the CounterModule-entity, which<br>outputs the number of clock-cycles since the Trigger-<br>signal was set. |

| PrinAcInfo[11:0]  | in  | Inputs from the BeamEnergy_Converter-entity                                                                                   |

| CompAcInfo[23:0]  | in  | containing the thresholds for sampling in the acquisitions for the Prin_Acqui-, the Comp_Acqui-                               |

| FreeWAcInfo[35:0] | in  | and the FreeW_Acqui-entities.                                                                                                 |

| PrinEvInfo[23:0]  | in  | Inputs from the BeamEnergy_Converter-entity                                                                                   |

| CompEvInfo[35:0]  | in  | containing the margin of allowed error between the two branches for the Prin_Acqui-, Comp_Acqui- and                          |

| FreeWEvInfo[35:0] | in  | the FreeW_Acqui-entities.                                                                                                     |

| PrinA[11:0]       | in  | Inputs for the ADC sampling the principal circuit                                                                             |

| PrinB[11:0]       | in  | current pickup in branch A and B.                                                                                             |

| CompA[11:0]       | in  | Inputs for the ADC sampling the compensation                                                                                  |

| CompB[11:0]       | in  | circuit current pickup in branch A and B.                                                                                     |

| FreeWA[11:0]      | in  | Input for the ADC sampling the free-wheel circuit                                                                             |

| FreeWB[11:0]      | in  | current pickup in branch A and B.                                                                                             |

| CalibDone         | out | Connected to the left-most LED. Signal is high and LED is on when calibration complete.                                       |

| IPOC_Rslt[22:0]   | out | Output for the result of the analysis of the MKDG. See .                                                                      |

Table 7. Description of in- and outputs of the Analysis-entity.

# 4.3.7.1 Prin\_Acqui

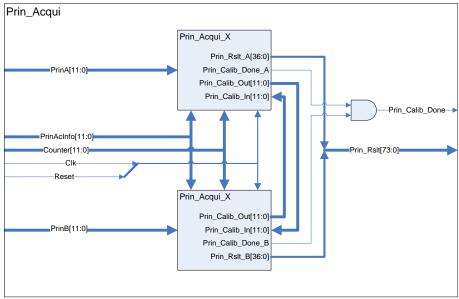

This entity is a sub-entity of the Analysis-entity, illustrated in Figure 24. This entity contains two equal entities, named Prin\_Acqui\_X, illustrated in Figure 26. The Prin\_Acqui-entity is illustrated in Figure 25 and the different in- and outputs are described in Table 8.

Figure 25. Block diagram of the Prin\_Acqui-entity.

| Table of 2 estimation of the and outputs of the 1 minuted at entry? |     |                                                         |

|---------------------------------------------------------------------|-----|---------------------------------------------------------|

| Clk                                                                 | in  | System clock. Running at 10MHz.                         |

| Reset                                                               | in  | System reset. Active low.                               |

|                                                                     |     | Input-signal from the CounterModule-entity, which       |

| Counter[11:0]                                                       | in  | outputs the number of clock-cycles since the Trigger-   |

|                                                                     |     | signal was asserted.                                    |

| PrinA[11:0]                                                         | in  | Input for the ADC sampling the principal circuit        |

| PrinB[11:0]                                                         | in  | current pickup in branch A and B.                       |

| Prin_Rslt[73:0]                                                     | out | Results. Goes to the IPOC-entity.                       |

| Prin_Rslt_A[36:0]                                                   |     | Built up by two signals. Outputs for the results of the |

| Prin Rslt B[36:0]                                                   |     | acquisition of the signals from branch A and B.         |

| Table 8. Description of | in- and outputs of | the Prin_Acqui-entity. |

|-------------------------|--------------------|------------------------|

|-------------------------|--------------------|------------------------|

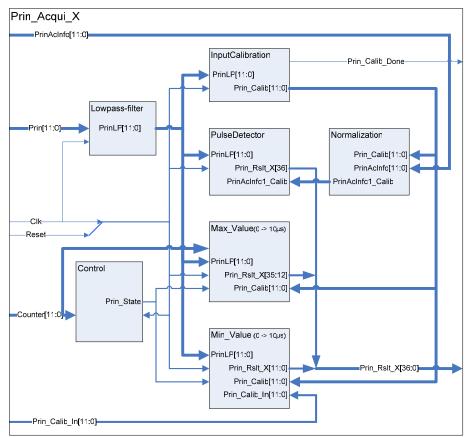

### 4.3.7.1.1 Prin\_Acqui\_X

This is a sub-entity of the Prin\_Acqui-entity, illustrated in Figure 25. This entity is used two times in the design, one for each branch, and contains all the processes for acquiring one of the signals from the two principal circuit pickups.

There are three sub-entities concerning the acquisition in this entity; one is running continuously and the last two are time dependent and are only active in a given time period after a beam dump has been issued. The time is controlled by the Control-process.

| Time after Trigger | Description                                             |

|--------------------|---------------------------------------------------------|

|                    | The PulseDetector-entity is always running, except when |

|                    | KPS is calibrating.                                     |

| 0 - 10µs           | The MaxValue-entity finds the largest inputted.         |

| 0 - 10µs           | The MinValue-entity finds the lowest value inputted.    |

Table 9. Time dependency of the processes in the Prin\_Acqui\_X-entity.

By adding new processes in this entity one can extend the analysis of the principal circuit. The entity is illustrated in Figure 26 and the different in- and outputs are described in Table 10.

Figure 26. Block diagram of the Prin\_Acqui\_X-entity.

| <u></u>            |     |                                                     |

|--------------------|-----|-----------------------------------------------------|

| Clk                | in  | System clock. Running at 10MHz.                     |

| Reset              | in  | System reset is active low.                         |

| Prin[11:0]         | in  | Input for the ADC sampling the principal circuit.   |

|                    |     | Signal from the CounterModule, which outputs the    |

| Counter[11:0]      | in  | number of clock-cycles since the Trigger-signal was |

|                    |     | asserted.                                           |

| PrinAcInfo[11:0]   | in  | Threshold for the PulseDetector-entity.             |

| Prin_Calib_In      | in  | Input for the calibration level from the opposite   |

|                    |     | branch.                                             |

| Prin_Calib_Done    | out | Goes high when calibration is done.                 |

| Prin_Rslt_X[36:0]  | out | <b>Results.</b> Goes to the IPOC-entity.            |

| Prin_Rslt_X[36]    |     | Result from the PulseDetector-entity.               |

| Prin_Rslt_X[35:12] |     | Result from the MaxValue-entity.                    |

| Prin_Rslt_X[11:0]  |     | Result from the MinValue-entity.                    |

Table 10. Description of in- and outputs for the Prin\_Acqui\_X-entity.

### 4.3.7.1.1.1 Lowpass-filter

The Lowpass-filters order is set with a constant in the UserSettings-configuration file. The choices are to disable it or having a  $2^{nd}$ ,  $4^{th}$  or  $8^{th}$  order low-pass filter.

| Clk    | in  | System clock. Running at 10MHz.                       |

|--------|-----|-------------------------------------------------------|

| Reset  | in  | System reset. Active low.                             |

| Input  | in  | Input values in which the filter is calculating from. |

| Output | out | The filtered values.                                  |

Table 11. Description of in- and outputs of the Lowpass-Filter-entity.

### 4.3.7.1.1.2 InputCalibration

InputCalibration is for finding the average of the input signal and setting this as the zero-level for any calculations. The calibration is active 20 clock cycles after reset. It is therefore crucial that there is no other activity on the input other than maybe noise from the pickup. The purpose of this functionality is to remove any offset caused by deviations in the analog circuitry.

Table 12. Description of in- and outputs of the InputCalibration-entity.

| Clk          | in System clock. Running at 10MHz. |                                                                                  |

|--------------|------------------------------------|----------------------------------------------------------------------------------|

| Reset        | in                                 | System reset. Active low.                                                        |

| Input[11:0]  | in                                 | Input values from the ADC, in which the average is calculated from.              |

| Output[11:0] | out                                | The average value. The output is held at a constant value after 20 clock-cycles. |

| Calib_Done   | out                                | Goes high when the calibration is done.                                          |

### 4.3.7.1.1.3 Normalization

Normalization is for adapting the calculated thresholds for the acquisition. This means that the zero-level set by the calibration is added as an offset to the threshold to make them exactly alike for both branches.

| Table 15. Description of m- and outputs of the Normanzation-entity. |     |                                         |  |

|---------------------------------------------------------------------|-----|-----------------------------------------|--|

| Clk in Syst                                                         |     | System clock. Running at 10MHz.         |  |

| Input[11:0]                                                         | in  | Input of the trigger level.             |  |

| Calib_In[11:0]                                                      | in  | Input from the InputCalibration-entity. |  |

| NormalizedOutput[11:0]                                              | out | The normalized trigger level.           |  |

Table 13. Description of in- and outputs of the Normalization-entity.

### 4.3.7.1.1.4 PulseDetector

PulseDetector is to detect if there is any current in the pickup. This entity's output goes high whenever the value on the input excides the value of an inputted threshold. The threshold changes with respect to the beam energy level.

| Tuble I in 2 estimption of in and outputs of the I dise2 effector entry? |                              |                                                                                      |  |

|--------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------|--|

| Clk                                                                      | in                           | System clock. Running at 10MHz.                                                      |  |

| Reset                                                                    | in System reset. Active low. |                                                                                      |  |

| Input[11:0]                                                              | in                           | Input values from the ADC.                                                           |  |

| Threshold[11:0]                                                          | in                           | The threshold in which the input has to be above to trigger a pulse detected report. |  |

| PulseDetector                                                            | out                          | The signal goes high when reporting a pulse detected.                                |  |

Table 14. Description of in- and outputs of the PulseDetector-entity.

#### 4.3.7.1.1.5 MaxValue

MaxValue basically just compare one input value to another, remembering both the highest input value and at what time it was taken.

| rubic ret Debeription |     | und outputs of the what and childy.                                                                                               |  |

|-----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|--|