## Power optimized multipliers

Stian Mathiassen

Master of Science in Electronics

Submission date: April 2010

Supervisor: Per Gunnar Kjeldsberg, IET Co-supervisor: Johnny Pihl, Atmel Norge

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## Problem Description

In earlier work at NTNU, high speed multipliers have been studied[1]. The result of that work is available as a netlist generator for optimized high speed multiplier structures at http://modgen. dnsalias.com. The cost function here involves minimizing the number of carries fed forward between columns in the multiplier tree structure. This project assignment will investigate how this cost function can be extended to include power cost. It involves working with an existing optimization algorithm coded in C, and extend it with power estimation functionality based on[2].

[1] E. Sand, VLSI architectures for speech recognition, 1994[2] S. T. Oskuii, Design of Low-Power Reduction-Trees in Parallel Multipliers, 2008

Assignment given: 18. November 2009 Supervisor: Per Gunnar Kjeldsberg, IET

### Abstract

Power consumption becomes more important as more devices becomes embedded or battery dependant. Multipliers are generally complex circuits, consuming a lot of energy. This thesis uses Sand's [1] multiplier generator, made for his master thesis, as a basis. It uses tree structures to perform the multiplication, but does not take power consumption into account when generating a multiplier.

By adding power optimization to the generator, multipliers with low energy consumption could be made automatically. This thesis adds different reduction tree algorithms (Wallace [2], Dadda [3] and Reduced Area [4]) to the program, and an optimal algorithm might be found. After the multiplier tree generation, an optimization step is performed, trying to exploit the delay and activity characteristics of the generated multiplier. A simplified version of Oskuii's [5] algorithm is used. To be able to compare the different algorithms with each other, a pre-layout power estimation routine was implemented. The estimator is also used by the post-generation optimization. Since accuracy is important in an estimator, the delay through a multiplier was also investigated.

Taking the previous mentioned steps into account, we are able to get a 10% decrease in overall power reduction in a  $0.18/0.15 \,\mu\mathrm{m}$  CMOS technology, reported by "IC Compiler". Delay characteristics of a multiplier is also supplied, and can be used by other power estimators.

This thesis shows how to achieve less power consumption in multipliers. It also shows that the delay model is important for estimation purposes, and how an estimator is used to optimize a multiplier. The findings in this thesis can be used as is, or be used as a basis for further study.

### **Preface**

This thesis is written as the final assignment for my Master's degree. The assignment was first given to me as a project assignment, corresponding to half a semester's work, and I chose the subject it involved C programming and optimization routines, which i find exciting.

Most of the research for this thesis was done by reading the work of Oskuii, and later further investigating other books and articles about the subject. The supplied code was also read, but some of the code was hard to understand. A lot of work was put in coding the estimator, and the tools trying to extract delay information from post-layout multiplier designs. An optimization routine was also build, using the theory by Oskuii.

Since the thesis uses a previous assignment as basis, some of the content in this thesis are reused from this assignment. The code and proposed algorithms generating multiplier tree are from the previous project. Parts of Chapter 2 are also from that report. The estimator was built by expanding the estimator coded for the previous assignment, but most of the code has been rewritten. Section 6.1.1 and 6.1.2 are also reused from the project assignment.

I want to thank Johnny Pihl and Per Gunnar Kjeldsberg for their advice while I was working on this thesis. They always had ideas and opinions on how I should proceed. Their interest for the field also seemed obvious, when I had to remind them that my time was running out, and I was not able to do everything they suggested. This made the assignment fun to work with. I would also want to thank Karoline Hovstad and Torgeir Thoresen for trying to understand and proof-read my thesis.

Stian Mathiassen

## Contents

| $\mathbf{A}$  | bstra | ct                                       | iii            |

|---------------|-------|------------------------------------------|----------------|

| Pı            | efac  | e                                        | v              |

| $\mathbf{Li}$ | st of | abbreviations                            | xvii           |

| 1             | Intr  | roduction                                | 1              |

|               | 1.1   | Power Usage in CMOS                      | 2              |

|               |       | 1.1.1 Static Power Consumption           | 2              |

|               |       | 1.1.2 Dynamic Power Consumption          | 2              |

|               |       | 1.1.3 Glitching                          | 3              |

|               | 1.2   | VHDL netlister                           | 4              |

|               | 1.3   | Outline of this Thesis                   | 4              |

|               | 1.4   | Main contributions                       | 5              |

| 2             | Mu    | ltiplication                             | 7              |

|               | 2.1   | Terminology                              | 7              |

|               | 2.2   | Partial products                         | 8              |

|               | 2.3   | Array multipliers                        | 8              |

|               |       | 2.3.1 Ripple-Carry Array                 | 8              |

|               |       | 2.3.2 Carry-Save Array                   | 9              |

|               | 2.4   | Tree multipliers                         | 10             |

|               |       | 2.4.1 Wallace-tree                       | 12             |

|               |       | 2.4.2 Dadda-trees                        | 15             |

|               |       | 2.4.3 Reduced Area multiplier            | 15             |

| 3             | Pow   | ver estimation                           | 17             |

|               | 3.1   | Probabilistic based methods              | 17             |

|               | 3.2   | Statistic based estimations              | 18             |

|               | 3.3   | A Monte Carlo approach                   | 19             |

|               |       | 3.3.1 Flow of the method                 | 20             |

|               |       | 3.3.2 Calculating Maximum expected error | 21             |

|               | 3.4   | Random number generator                  | 21             |

| 4             | Pow   | ver optimization                         | 23             |

|               | 4.1   | Algorithm optimization                   | 23             |

|               | 4.2   | Interconnect optimization                | $\frac{1}{24}$ |

|               |       | 4.2.1 Reduction of search space          | 24             |

|               | 4.3   | Vector Merging adder                     | 26             |

| 5             | Imp   | plementing the power estimator           | 29             |

viii *CONTENTS*

|                  | 5.1  | The input data-structure                   | 29         |

|------------------|------|--------------------------------------------|------------|

|                  | 5.2  | Preprocessing of the multiplier            | 30         |

|                  | 5.3  | Simulation                                 | 31         |

|                  | 5.4  | Timing model                               | 33         |

|                  |      |                                            | 33         |

|                  |      | 5.4.2 Implementation of data extraction    | 34         |

| 6                | Imr  | plementation of power optimization 3       | 37         |

| •                | 6.1  | 1 1                                        | 37         |

|                  | 0.1  | 0 1                                        | 37         |

|                  |      |                                            | 38         |

|                  | 6.2  |                                            | 39         |

|                  |      | 1                                          | 39         |

|                  |      | 1                                          | 41         |

| 7                | Res  | ults and discussion                        | 13         |

| •                | 7.1  |                                            | 43         |

|                  | 7.2  |                                            | 16<br>16   |

|                  | 7.3  |                                            | 18         |

|                  | 7.4  | •                                          | 53         |

| _                | ~    |                                            | _          |

| 8                |      |                                            | 57         |

|                  | 8.1  | v C                                        | 57         |

|                  | 8.2  | 1 9                                        | 57         |

|                  | 8.3  | Directions for further work                | 58         |

| $\mathbf{A}_{]}$ | ppen | dices                                      |            |

| $\mathbf{A}$     | Tim  | ning models                                | 59         |

|                  | A.1  | Modgen multiplier, min PVT                 | 59         |

|                  |      |                                            | 33         |

|                  |      | A.2.1 Optimized for minimum power, max PVT | 63         |

|                  |      | A.2.2 Optimized for maximum power, max PVT | 67         |

|                  | A.3  | Estimator time usage                       | 71         |

|                  | A.4  | Estimator accuracy of sample size          | 73         |

|                  | A.5  | Power usage after optimization             | 75         |

|                  | A.6  | Multipler adder usage                      | 77         |

| В                | Per  | l-code for reading SDF-files 7             | <b>7</b> 9 |

|                  | B.1  | SDF-reader library                         | <b>7</b> 9 |

|                  | B.2  | Gate counter                               | 32         |

|                  | B.3  | Gate printer                               | 33         |

|                  | B.4  | SDF to datafile generator                  | 35         |

| $\mathbf{C}$     | C-c  | ode 8                                      | 39         |

|                  | C.1  | Estimation                                 | 39         |

|                  |      |                                            | 39         |

|                  |      | C.1.2 estimation.c                         | 91         |

|                  | C.2  | Optimalization                             | )5         |

|                  |      | C.2.1 optimize.c                           | )5         |

| ix |

|----|

|    |

| Bibliography | 115 |

|--------------|-----|

|              |     |

## List of Tables

| 3.1 | Truth table for NOR-gate                                                         | 17 |

|-----|----------------------------------------------------------------------------------|----|

| 4.1 | Comparison of well-known tree generation algorithms. Numbers from [4] and [6]    | 23 |

| 4.2 | List of surveyed adder types in Nagendra [7]                                     | 26 |

| 4.3 | Area and number of transistors in adders from Nagendra [7] survey                | 26 |

| 4.4 | Transistor count for each element used in Nagandra [7]                           | 27 |

| 4.5 | Comparison of reduction trees and VMA                                            | 27 |

| 5.1 | Technology mapping for adders                                                    | 36 |

| 6.1 | Priority used by the optimizer. High priority means high power consumption.      |    |

|     | Port names from Figure 2.5 on page 11                                            | 40 |

| 6.2 | Comparison of Oskuii's [5] optimization algorithm and the one used in the thesis | 41 |

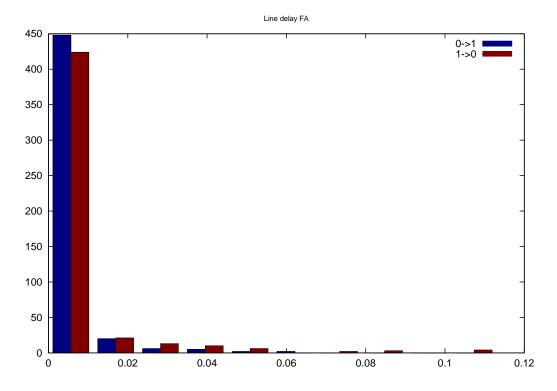

| 7.1 | Mean delay through elements                                                      | 48 |

| 7.2 | Improvement by optimization                                                      | 52 |

| 7.3 | Effect used by complete multipliers, before and after interconnect optimization  | 56 |

| A.1 | Number of adders, depth and size of VMA for a 8x8 multiplier                     | 77 |

| A.2 | Number of adders, depth and size of VMA for a 16x16 multiplier                   | 77 |

| A.3 | Number of adders, depth and size of VMA for a 32x32 multiplier                   | 77 |

# List of Figures

| 1.1<br>1.2                                                          | Switching power usage in CMOS                                                                                           |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | Basic bit-level multiplication                                                                                          |

| 3.1<br>3.2                                                          | Flow diagram of Monte Carlo. From Burch [10]                                                                            |

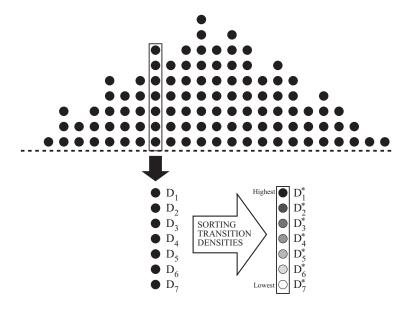

| 4.1<br>4.2                                                          | Sorting partial products based on activity. From [5]                                                                    |

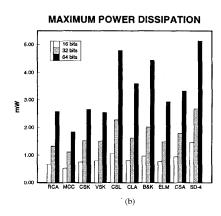

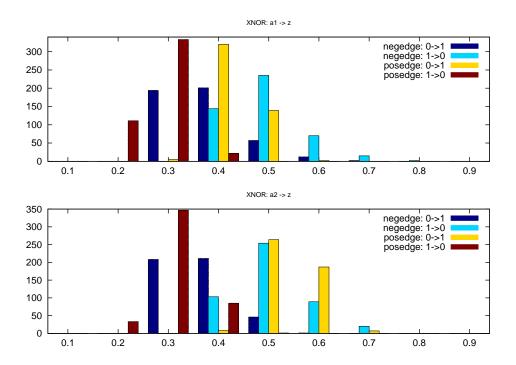

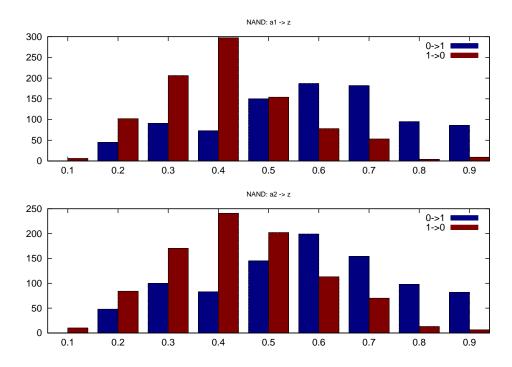

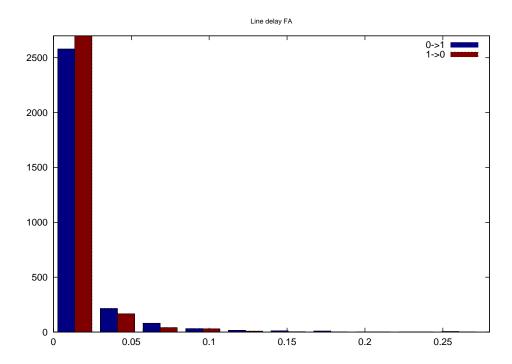

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5                                     | Multiplier trees as they are represented in the netlister. Figure taken from Sand [1]                                   |

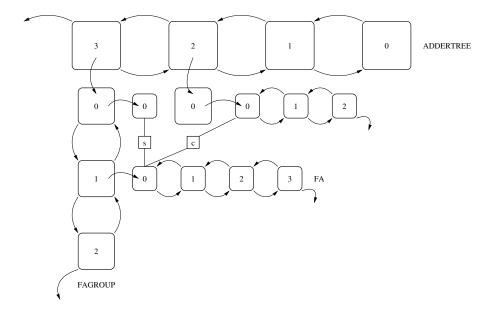

| 6.1<br>6.2<br>6.3                                                   | Left: Propagation of an extra carry bit using FAs only. Right: Propagation of an extra carry bit using both FAs and HAs |

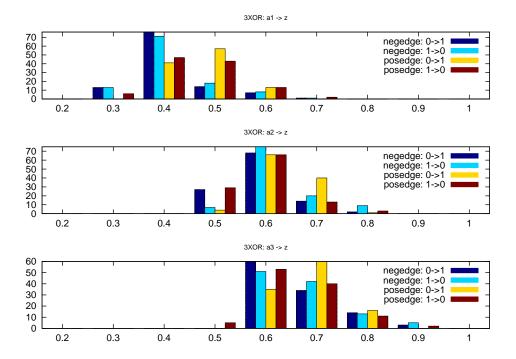

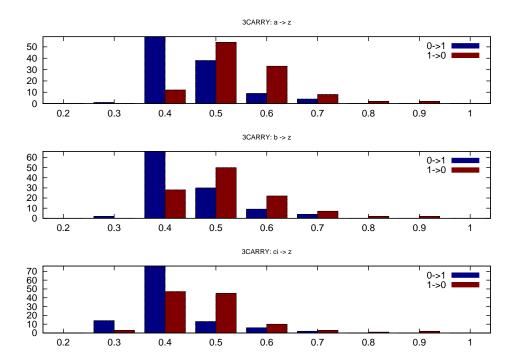

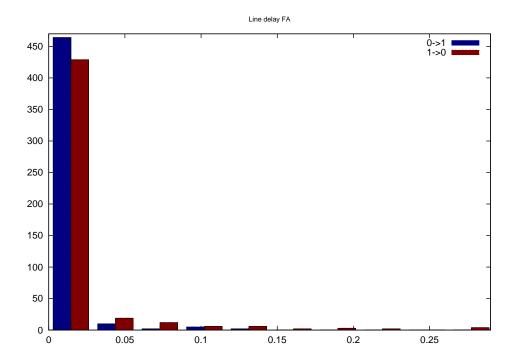

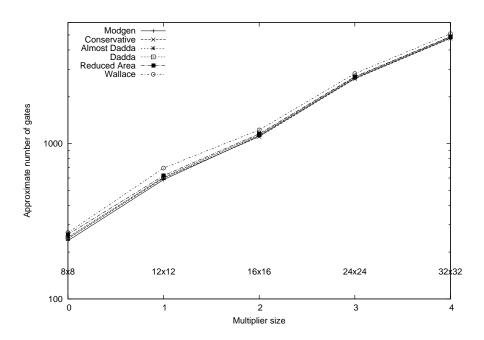

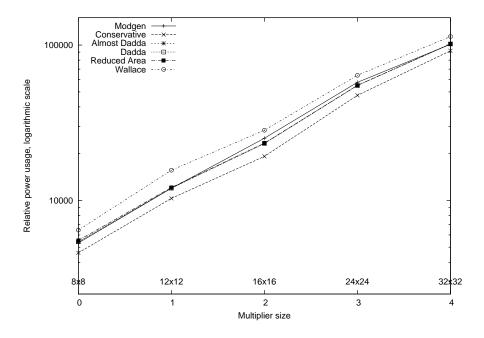

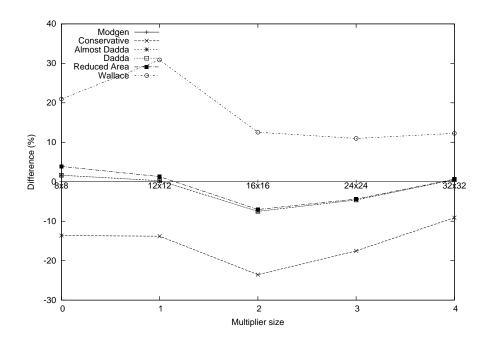

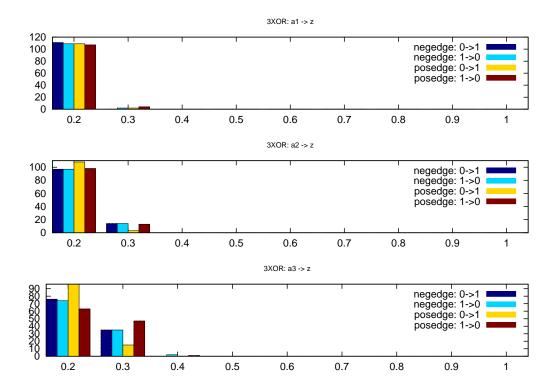

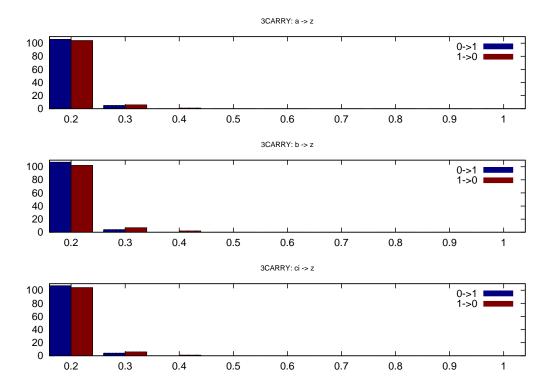

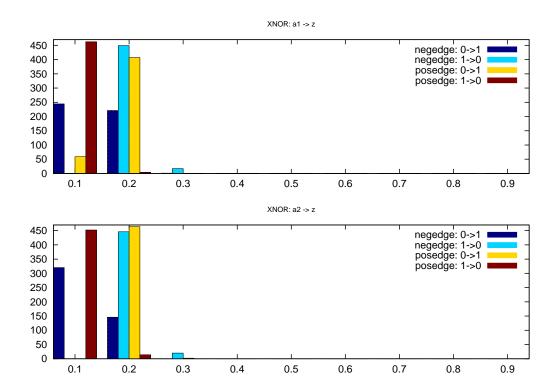

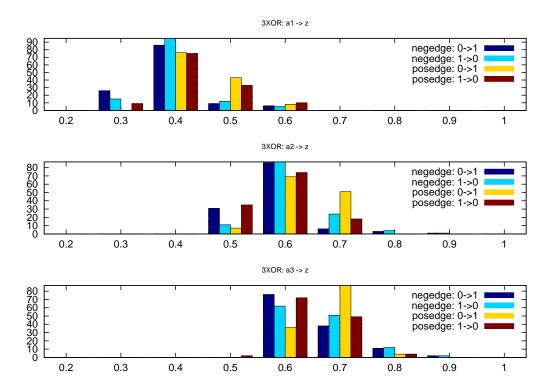

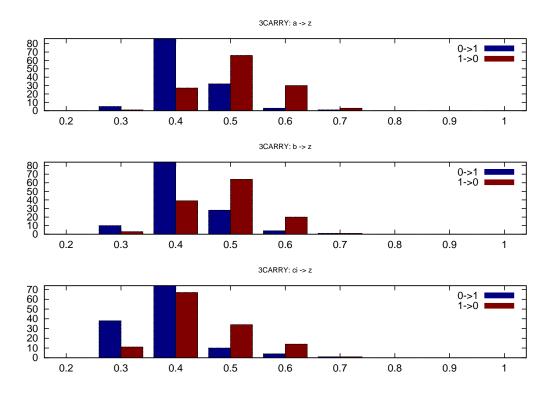

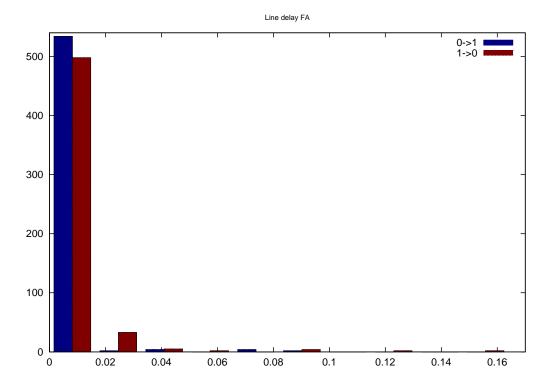

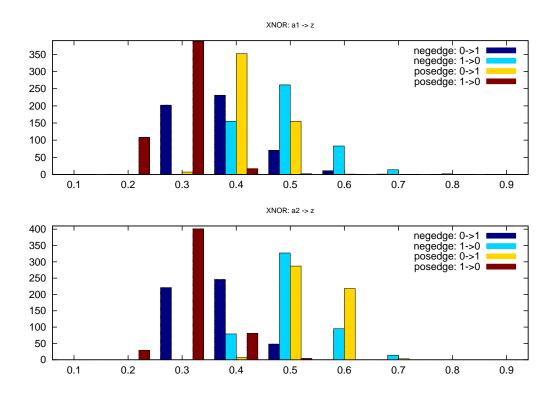

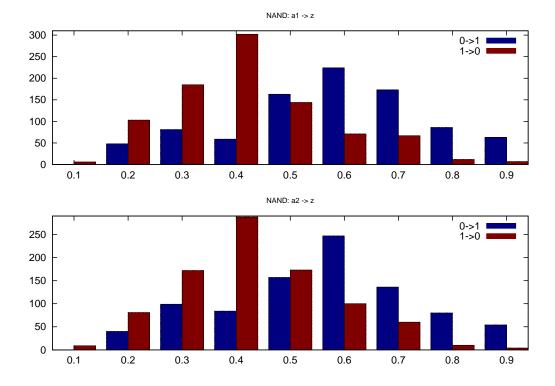

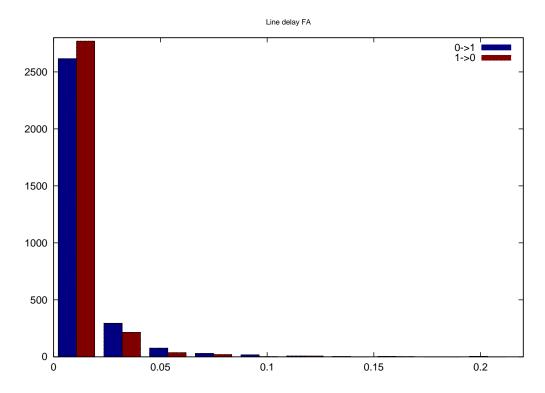

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>7.8                | Timing through full-adder, from input to sum output                                                                     |

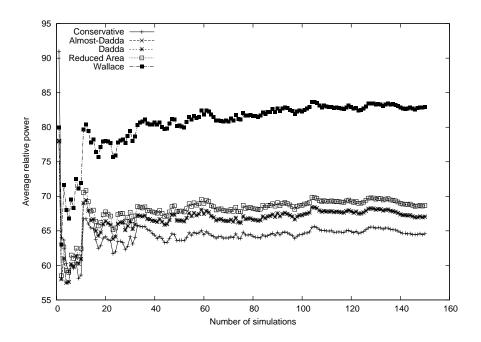

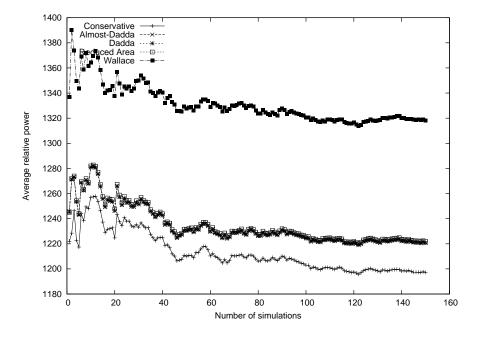

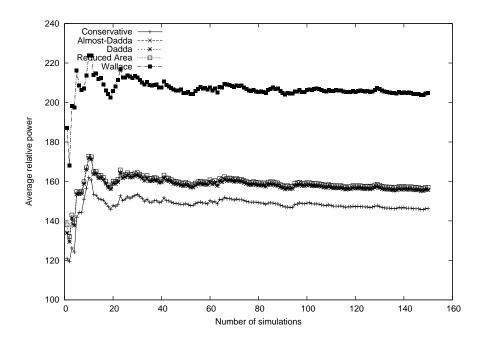

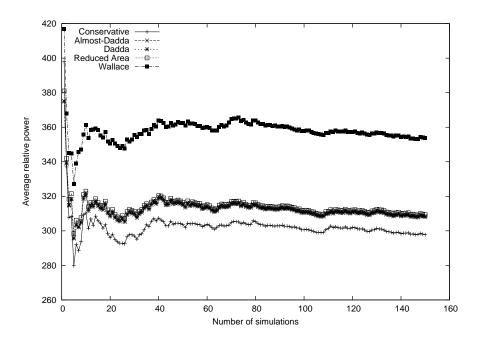

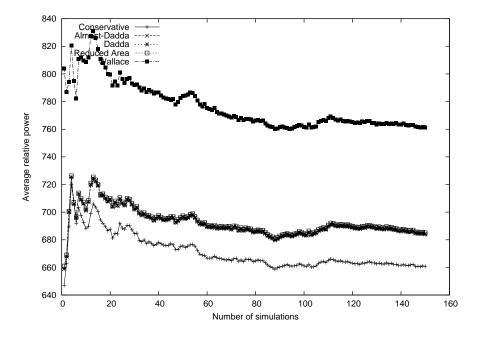

| 7.9                                                                 | Power estimation accuracy of simulations size, $8 \times 8$ multiplier                                                  |

xiv LIST OF FIGURES

| 7.10 Power estimation accuracy of simulations size, 32 × 32 multiplier | 50<br>51<br>52<br>54<br>54<br>55 |

|------------------------------------------------------------------------|----------------------------------|

|                                                                        |                                  |

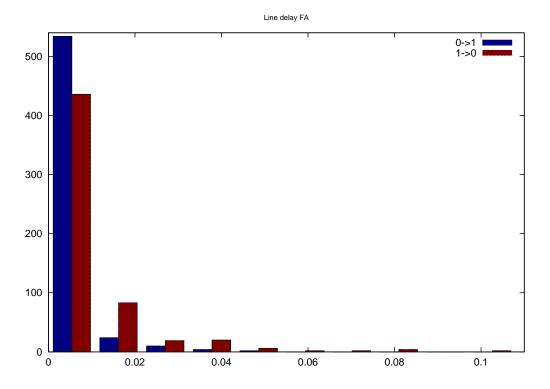

| A.1 Timing through full-adder, from input to sum output                | 59                               |

| A.2 Timing through full-adder, from input to carry output              | 60                               |

| A.3 Line timing from full-adder to next element                        | 60                               |

| A.4 Timing through half-adder, from input to sum output                | 61                               |

| A.5 Timing through half-adder, from input to sum output                | 61                               |

| A.6 Line timing from half-adder to next element                        | 62                               |

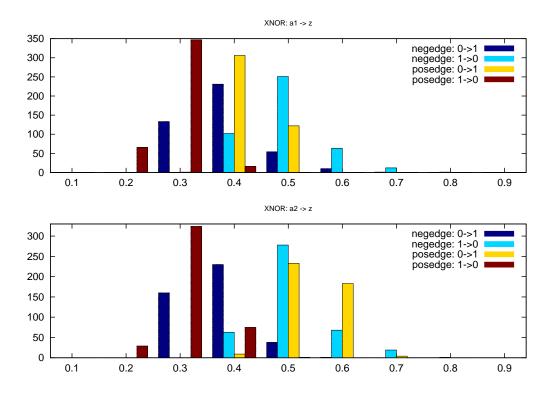

| A.7 Timing through full-adder, from input to sum output                | 63                               |

| A.8 Timing through full-adder, from input to carry output              | 64                               |

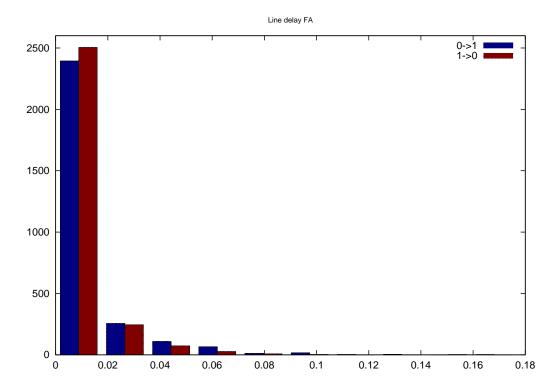

| A.9 Line timing from full-adder to next element                        | 64                               |

| A.10 Timing through half-adder, from input to sum output               | 65                               |

| A.11 Timing through half-adder, from input to sum output               | 65                               |

| A.12 Line timing from half-adder to next element                       | 66                               |

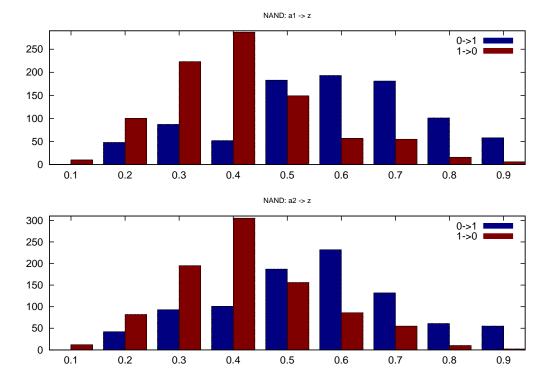

| A.13 Timing through full-adder, from input to sum output               | 67                               |

| A.14 Timing through full-adder, from input to carry output             | 68                               |

| A.15 Line timing from full-adder to next element                       | 68                               |

| A.16 Timing through half-adder, from input to sum output               | 69                               |

| A.17 Timing through half-adder, from input to sum output               | 69                               |

| A.18 Line timing from half-adder to next element                       | 70                               |

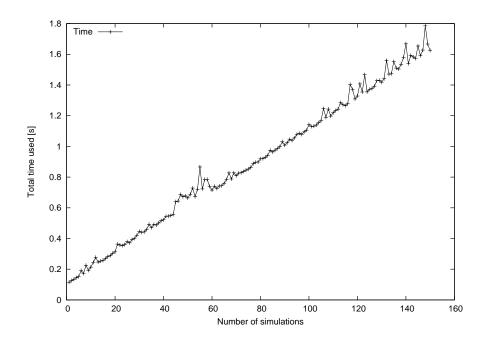

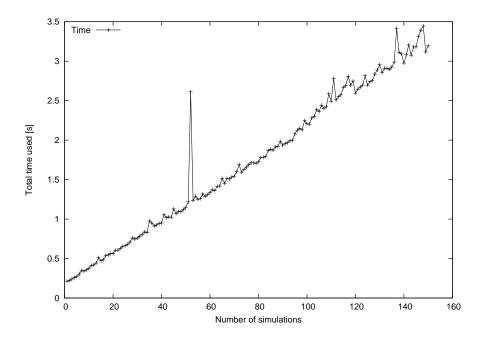

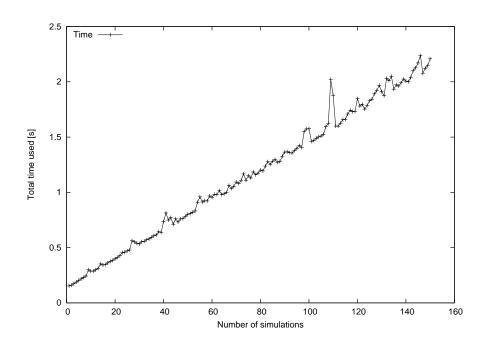

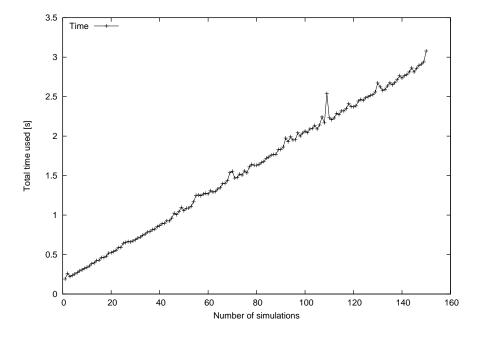

| A.19 Time usage of the estimator, 12x12 multiplier                     | 71                               |

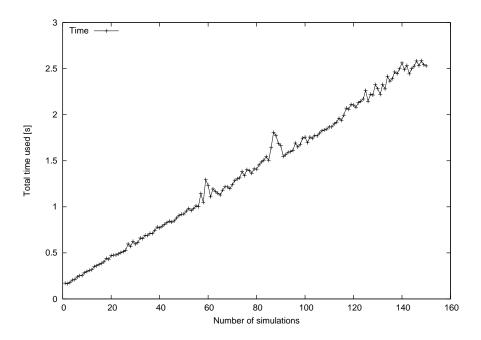

| A.20 Time usage of the estimator, 16x16 multiplier                     | 72                               |

| A.21 Time usage of the estimator, 24x24 multiplier                     | 72                               |

| A.22 Power estimation accuracy of simulations size, 12x12 multiplier   | 73                               |

| A.23 Power estimation accuracy of simulations size, 16x16 multiplier   | 74                               |

| A.24 Power estimation accuracy of simulations size, 24x24 multiplier   | 74                               |

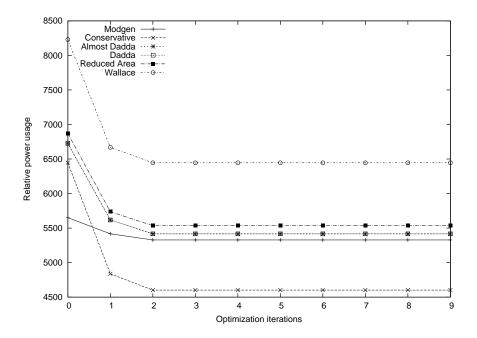

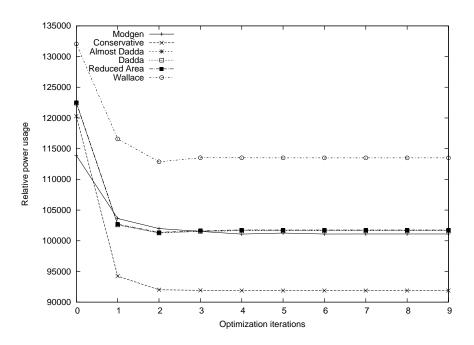

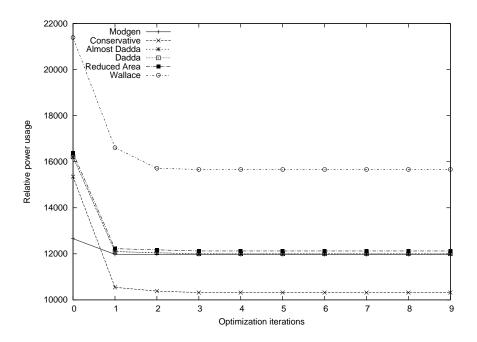

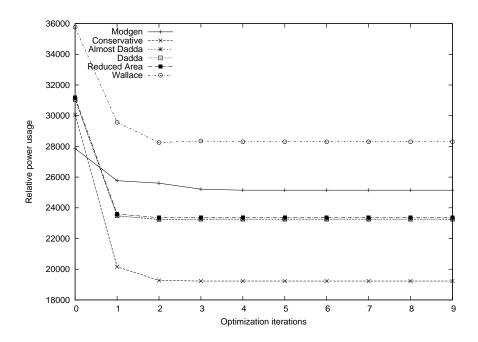

| A.25 Power usage after each optimization step, 12x12 multiplier        | 75                               |

| A.26 Power usage after each optimization step, 16x16 multiplier        | 76                               |

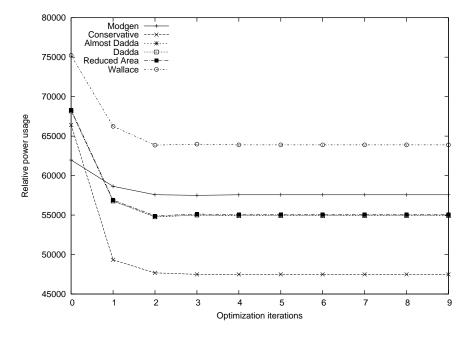

| A.27 Power usage after each optimization step, 24x24 multiplier        | 76                               |

|                                                                        |                                  |

## Source code

| 3.1 | 32-bit LFSR implemented in software (C code)           | 22 |

|-----|--------------------------------------------------------|----|

| 5.1 | C definitions of data structures used in the simulator | 32 |

| B.1 | SDF-reader library                                     | 79 |

| B.2 | Code to count each element in multiplier tree          | 82 |

| B.3 | Prints of part of the multiplier tree                  | 83 |

| B.4 | Generates datafiles for delay histograms               | 85 |

| C.1 | Header file for estimator                              | 89 |

| C.2 | Source file for estimator                              | 91 |

| C.3 | Source file for optimalization routine                 | 05 |

## List of abbreviations

**BDD** Binary Decision Diagram [11]

**FA** Full-adder

**HA** Half-adder

**PP** Partial product

**PVT** Process, voltage and temperature

**LFSR** Linear feedback shift register [12, 13]

**SDF** Standard Delay Format [14]

**VMA** Vector Merging Adder

### Chapter 1

### Introduction

Multipliers are used in a wide range of devices, from large scale processors to small embedded DSP chips. As multipliers are large, slow and complex components, a lot of research has been done to make the components smaller and faster [2, 3, 4, 15, 16]. As more of the electronic devices becomes embedded or handheld, they become more dependant on battery as a power source. To improve battery life-time, the research focus has shifted to improve power consumption [17, 18, 19, 20, 5]. By reducing power-usage, it is possible to drastically improve the battery-life of handheld devices.

Since tree multipliers, like Wallace [2] and Dadda [3], are faster and use less power than traditional array multipliers [21] (though have larger area), this thesis concentrates its focus on tree multipliers. The wires inside the tree multipliers have very different length, because of the irregular layout of such multipliers, and signal delay and power impacts the design more than in array multipliers. Over half of the used power is because of excess switching, which produces nothing to the end result [22], and should therefore have lot of optimization potential [5].

By employing different kind of tree multiplier generating algorithms, we can find what kind of algorithm performs best. Since there also are a lot of spurious switching activity in multipliers, another way to power optimize multipliers are to reduce these glitches. By altering how the adders inside the multiplier are interconnected, it should be possible to get decreased power usage [5].

This thesis uses six different algorithms to design tree multipliers: Wallace [2], Dadda [3], Reduced area [4], algorithm used by Sand's multiplier generator [1] and algorithms proposed here and in a project prior to this master thesis work [23]. To compare these algorithm before layout, a Monte Carlo approach for power estimation is used [10]. The result of the power estimation is used to power a post-generation optimization of each multiplier using a simplified optimization algorithm proposed by Oskuii [5].

The background theory for the different kind of algorithms that generates the tree multipliers are presented in this thesis, together with theory on power estimation for combinational CMOS circuits. An implementation of five algorithms is added to the existing VHDL-netlister program written in C by Sand [1], to produce a wide range of tree multipliers, will be presented. An implementation of an estimator is also discussed, in addition to an implementation of a simpler optimization routine based in Oskuii's model [5]. The estimator is fed real-world timing delay from an SDF-file[14] of a post-layout multiplier. The delay data is extracted using a parser implemented for this thesis. Using netlister with the implementations from this thesis, multiple  $8 \times 8$ ,  $16 \times 16$  and  $32 \times 32$  multipliers are generated and compared using the said estimator. Power estimates for two algorithms from post-layout analysis are also presented, to verify if an improvement are found.

#### 1.1 Power Usage in CMOS

The power used in CMOS-circuits consists of two parts, dynamic and static power dissipation [18]:

$$P = P_{dynamic} + P_{static} (1.1)$$

The dynamic power consumption is power used as a function of activity. The static component is power consumed as a function of time.

#### 1.1.1 Static Power Consumption

The part describes power used even though there is no activity in the circuit. Ideally CMOS components should not have any static power consumption, since there are no direct paths from  $V_{dd}$  to ground. In practical applications this is not the case, since MOS transistors are not perfect switches. There will always be leakage currents in MOS transistors [18].

Reverse biased currents flows through the source or drain and the substrate, because parasitic diodes in the MOS transistors are one of the static leakage currents. The subthreshold leakages current run through the transistors (from source to drain), because the gate of the transistor is close to the threshold voltage, and therefore lets some current flow through. These currents used to be negligible, however it seems to become more prominent as transistors become smaller [19, 24] and really starts to emerge at  $0.13 \,\mu\text{m}$  [25]. The static power dissipation is primarily determined by fabrication technology [26].

#### 1.1.2 Dynamic Power Consumption

The dynamic part of the power consumption in CMOS can be divided into two parts [20].

$$P_{dynamic} = P_{short-circuit} + P_{switching} (1.2)$$

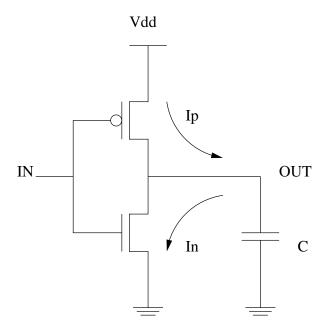

The short circuit happens when both the PMOS and the NMOS transistor is open at the same time. This happens during a switch, because the PMOS and NMOS does not switch instantly, but has a switching delay. This makes a short circuit line from  $V_{dd}$  to ground through the CMOS component. As we can see in figure 1.1, if the NMOS and PMOS transistors in the inverter are both open at the same time, a short-circuit path i available from  $V_{dd}$  to ground. The phenomena is described in equation 1.3, where  $V_{dd}$  is the supply voltage and  $I_{sc}$  is the current flowing through during the short circuit period of the switch. As long as the inputs of the NMOS and PMOS transistors are properly balanced, this power dissipation should be less than 20% of the dynamic power dissipation [27].

$$P_{short-circuit} = V_{dd}I_{sc} (1.3)$$

The power used in switching the CMOS from one state to another is largely used to charge parasitic capacitance in lines between the CMOS-cells [18]. When the output of a gate is turned from  $0 \to 1$ , the NMOS part of the CMOS cuts off the connection to ground, and the PMOS part of the CMOS enables a connection from  $V_{dd}$  to the output. This causes the capacitance on the output port and line to be charged, with the energy equal to:

$$Energy_{transition} = CV_{dd}^2$$

(1.4)

Where  $V_{dd}$  is the power source. Half of this power is dissipated at once in the PMOS transistors, while the other half is stored in the capacitance [18]. When the port is turned

Figure 1.1: Switching power usage in CMOS

from '1' to '0', the line is connected to ground, and the energy stored in the capacitance is also dissipated (see figure 1.1).

Since an equal amount of energy is used to charge the circuit for each  $0 \to 1$  transitions, it is possible to get an equation for power used in switching. Considering the frequency f of the circuit, and the probability for a  $0 \to 1$  switch at the gate  $\alpha$ , we get the equation[18]:

$$P_{switching} = \alpha f C V_{dd}^2 \tag{1.5}$$

Although the other sources of power dissipation have increased their share, switching power consumption is still by far the largest source for power usage in CMOS today [27, 18, 22], and is therefore a prime candidate for optimization.

As we can see from the equation, there are three elements to improve power usage: Voltage, physical capacitance and activity. Over the years, lower voltage has been employed in CMOS, causing a reduction in switching power usage [19, 25]. Physical capacitance is strongly correlated to the line length between transistors and the kind of technology being used (size of transistors and lines) [18]. Activity is maybe the most system-dependant factor in the equation. By reducing the activity in the design, it is possible to reduce the amount of power used in the design.

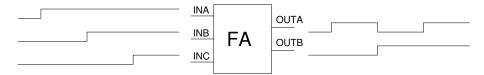

#### 1.1.3 Glitching

So far we have looked at where the power is dissipated. As we have seen, switching activity dictates some of the power usage in CMOS. A problem arises when the inputs on an element do not change at the same time. This might cause the element to use energy two times instead of one. This leads to the problem that some circuits switch more than they need, to reach their final state. This effect is called glitching. This happens when the inputs on an element are not balanced, and the inputs enter the element at different times, as we can see in figure 1.2. Here we can see the output OUTA first become '1', then '0' and finally '1', which is its final state. The adder's OUTA uses double amount of energy (i.e.  $\alpha > 1$  in equation

1.5) to get to the final state. If we have even more combinatorial elements following this FA, these spurious switching activities will spread down the whole design, until a buffer or register halt the propagation. According to Kalis [22], tree multipliers uses 30% to 75% of its power in this kind of spurious switching. This shows there is a lot of potential of reducing energy consumption by reducing glitching.

Figure 1.2: Glitching on an adder

#### 1.2 VHDL netlister

The netlister this thesis uses as a foundation for the implementation of the multiplier generator algorithms, the estimator and the optimization routine is originally written by Espen Sand for his master thesis [1]. The code generates a multiplier, and write out the resulting multiplier using VHDL. The application takes arguments for the size of the multiplier, as well as different options to add Booth-recoding [15], pipelining and a vector merging adder. The program is used without these functions in this thesis, and is only used to generate VHDL for a multiplier tree.

The program is divided into several parts, and generates a list of partial products that it passes to a reduction tree generator module of the program. The netlister already has a tree generator build in, but several new tree generators can easily be added to the program, as long as the same data structures are used. Since the generation is sequential, it is easy to add step between the tree generator, and the writing of VHDL-file, making it possible to add an optimization step before writing the multiplier to VHDL.

#### 1.3 Outline of this Thesis

Chapter 1 contains a small introduction to what power consumption in electronics are, and a brief explanation of the netlister program that is used as a basis for this thesis. Chapter 2 explains how multipliers in electronic circuits work, and how the partial products are generated. Since multipliers contains two schools of generation, the chapter gives a brief explanation of array multipliers. A more in-depth study of different tree multipliers is given, containing the theory behind the tree multiplier generation algorithms used in this thesis.

Chapter 3 reviews both probalistic approaches, as well as simulation approaches to estimate energy consumption. It also contains theory about the chosen simulation estimation, using the Monte Carlo approach [10].

Chapter 4 contains a comparison of the different tree multiplier generator algorithms, and some insight on the advantage and disadvantage of each algorithm. Oskuii's [5] algorithm for reducing power through changing the interconnection between the adders in the multiplier is also studied, together with a simplified version of said algorithm. The Optimization alternatives for the vector merging adder are discussed last.

Chapter 5 examines the implementation of the estimator used in this thesis. The estimator is implemented as a simulator at gate level, counting activity at each gate. It explains how

the simulator uses an event-based scheme to keep the run-time as low as possible. It also discusses what kind of timing-data is available to use in the estimator, and what data is beneficial to use. An SDF-parser was written for this thesis, and the implementation and choices made during the implementation are showed to the reader.

Chapter 6 contains details on how the optimization routine are implemented. Choices of implementation are also discussed.

Chapter 7 have results and discussions about the extraction of the delay model from existing multipliers. It also contains graphs over the performance of the estimator, and results on how good the line optimization are and discussions about the topics.

Chapter 8 has the conclusion of this thesis, and a suggestion of future work. It is follows by appendices and a bibliography

#### 1.4 Main contributions

This thesis has made the following contributions to the field, and this are outlined here:

- An implementation of a gate-level estimator, that estimates power-usage before synthesis.

- Comparison of different algorithms power usage, using implemented estimator.

- Evaluation of the effect of line-optimization

- Timing data from post-layout multipliers.

- Implementation of a simplified version of Oskuii's [5] optimization routine.

- Added five algorithms for generating multiplier trees to the existing netlister [1].

- A tool to read SDF-files [14], to extract timing data to use in a timing model.

The SDF-parser is written in Perl. The netlister build upon during this thesis is written in C , and the added algorithms for generating multiplier trees, the estimator and the optimization routine is therefore also written in C.

### Chapter 2

### Multiplication

Multiplication is a very common task in modern digital electronics. The two most important methods used is to either perform shift and add operations and use existing components in a CPU, or add a multiplier unit. Further information about shift and add operation can be found in Parhami[9].

Multipliers in digital design are often divided into two subgroups: Array multipliers and tree multipliers[9, 28]. Array multipliers use a rigid pattern to construct their multipliers. This leads to compact designs and an evenly distributed delay. Tree multipliers on the other hand reduces the number of bits in each level in the tree until the calculation is done. Since this produces a complex tree structure, the delay is not evenly distributed. This may cause glitches that uses power. And the tree structure uses a lot of interconnection, end therefor uses a lot more area. Despite the larger area and not so evenly distributed delay, the tree multipliers use less power than array multipliers[21].

Another advantage tree multiplier have, is that they are a lot faster. The depth of an array multiplier is O(n) = n while it is  $O(n) = \log_2 n$  for multiplier trees[28] Even though the wiring cause more delay for multiplier trees, it still perform faster than array multipliers[21, 29].

### 2.1 Terminology

This thesis contains a lot of discussion around how multipliers are generated and different parts of the multiplier. To make the discussion understandable to the reader, it is important to be on the same terms when using different words. The three words: column, row and stage, will be used to describe different parts of a tree multiplier in this thesis. Partial products (see section 2.2) are organized into rows and columns. This is shown in figure 2.1, where all the partial products containing the bit  $b_0$  share the same row. An example of a column is  $[a_1b_0, a_0b_1]$ . Each column contains partial products width different weight or value. By this we mean that each PP (partial product) in the rightmost column has the value of  $2^0 = 1$ , and in the next column  $2^1 = 2$  and so forth. This is show in figure 2.7. To describe the value or weight of a partial product, the word bitweight or columnweight is used in this thesis.

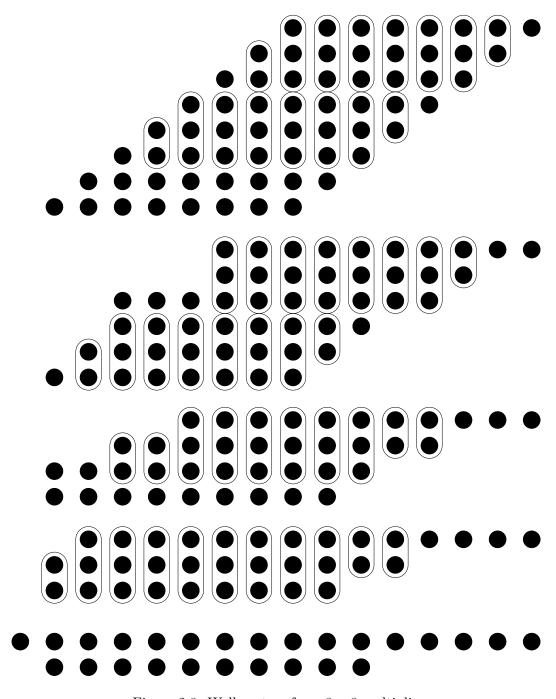

During the reduction of partial products, full- and half-adders are added to the design, and a new set of partial products emerges (since adders reduce the number of partial products). During the thesis, each of these sets are called stages. The first stage is the initial set of partial products, the second stage is the set of partial products after the first reduction. Figure 2.8 show five stages, where the topmost tree contains the original partial products (denoted as • in the tree), and the next tree contains the tree at the second stage, after the first reduction.

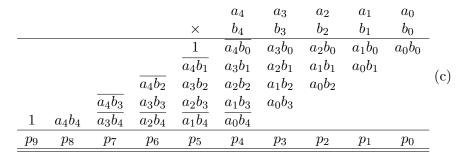

#### 2.2 Partial products

|                   |          | $a_3$    | $a_2$    | $a_1$    | $a_0$    | Input            |

|-------------------|----------|----------|----------|----------|----------|------------------|

|                   | ×        | $b_3$    | $b_2$    | $b_1$    | $b_0$    |                  |

|                   |          | $a_3b_0$ | $a_2b_0$ | $a_1b_0$ | $a_0b_0$ |                  |

|                   | $a_3b_1$ | $a_2b_1$ | $a_1b_1$ | $a_0b_1$ |          | Partial products |

| $a_3b_2$          | $a_2b_2$ | $a_1b_2$ | $a_0b_2$ |          |          |                  |

| $a_3b_3  a_2b_3$  | $a_1b_3$ | $a_0b_3$ |          |          |          |                  |

| $p_7$ $p_6$ $p_5$ | $p_4$    | $p_3$    | $p_2$    | $p_1$    | $p_0$    | Result           |

Figure 2.1: Basic bit-level multiplication

Multiplication is often done by dividing the problem into smaller multiplications, calculating the smaller multiplications and accumulate the result. In hardware this is often done by dividing the problem down to multiplying one bit with another, as this can be done with a regular AND operation. Each of these one bit multiplications are called a partial product (PP). The partial products are then added together to form the result of the multiplication. Figure 2.1 show how a is multiplied with b using unsigned integers as input, where value  $a_i$  is the bit in position i. Each bit from a is multiplied with each bit in b. This does however not account for signed numbers, and several other methods of generating partial products has been proposed [9].

When using two's complement form for signed integers, the corresponding partial products are given in Figure 2.2.(a). This PP generation does however require signed arithmetic to sum the partial products. This was improved by the Baugh-Wooley [8], and is shown in Figure 2.2.(b). This partial product generator uses NOT ports in addition to AND ports, but does not require signed arithmetic. The method does however require more additions, but this is usually outweighed by only requiring addition. The Baug-Wooley generator has been modified to require less additions, as shown in Figure 2.2.(c). This generator requires a minimal amount of extra additions to perform signed multiplication.

#### 2.3 Array multipliers

Array multipliers use the fact that multiplications form a recurring pattern. In Figure 2.1 we see a basic setup for a bitwise multiplication. We multiply each bit in one multiplicand, with every bit in the other multiplicand. This is done for every bit in the first multiplicand, and then shifted position of the bit. Then all the bits are summed together, and produce the result of the multiplication.

#### 2.3.1 Ripple-Carry Array

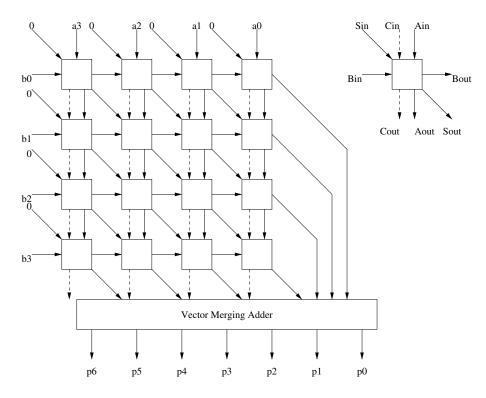

Using Ripple-Carry adders, we can exploit the recurring operation, and make an adder array. In Figure 2.3 we see the each column represents the first multiplicand that gets multiplied with each bit in the second multiplicand. The elements are actually an adder and an AND-gate that performs the actual multiplication.  $Ain \cdot Bin$  is put into the adder together with Cin from the previous column and Sin. The adder then produces Sout (Sum out) and Cout (Carry out). Aout and Bout is just an extension of Ain and Bin respectively[28].

A problem with the Ripple-Carry approach is that it is very slow for larger implementations. Since the carry have to propagate through every row in the column, we get a very long critical path with this implementation.

Figure 2.2: (a) 2's complement (b) Baugh-Wooley [8] (c) Modified Baugh-Wooley [9]

#### 2.3.2 Carry-Save Array

A solution to the slow Ripple-Carry problem with a long critical path, is to let the carry travel down the column. This way the columns are not dependent on the column to the right, like they are with Ripple-Carry. In Figure 2.4 a Carry-Save Array is implemented. The element in the figure is an adder and an AND-gate that performs the actual multiplication.  $Ain \cdot Bin$  is put into the adder together with Cin from the previous column and Sin. The adder then produces Sout (sum out) and Cout (carry out). Aout and Bout is just an extension of Ain and Bin respectively[28].

Since the carry only propagates down in each column, the result from the array is not completely finished. Some of the lines now consists of two outputs for a given bit level. Because of this, the result needs to be put into a Vector Merging Adder (VMA) to get only one output per bit level. This unit can be designed using different types for adder techniques, eg. Ripple-Carry or Carry-Look-ahead. Even though the array needs this extra calculation,

Figure 2.3: Ripple-carry array multiplier

the Carry-Save multiplier is faster than the Ripple-Carry Array in most cases [28]

#### 2.4 Tree multipliers

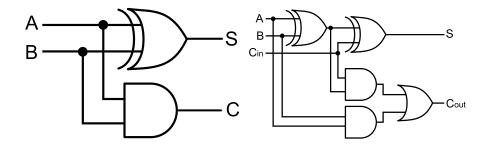

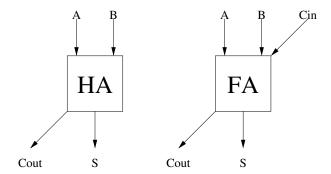

Tree multipliers use different approach. They still use the same scheme for carry propagation, as Carry-Save adders used in previous section. But in addition to regular adders (hereby referred to as a full adder), they also use an element called a half adder. The full adder is a regular adder, with three inputs and two outputs (a 3,2 counter), while a half adder is an adder with two inputs and two outputs (a 2,2 counter). The output Sum is the same bitweight as the input, while Cout is one value higher. As showed in the equation below  $(C_{in} = 0 \text{ for HA})[9]$ :

$$A + B + C_{in} = S + 2C_{out} \tag{2.1}$$

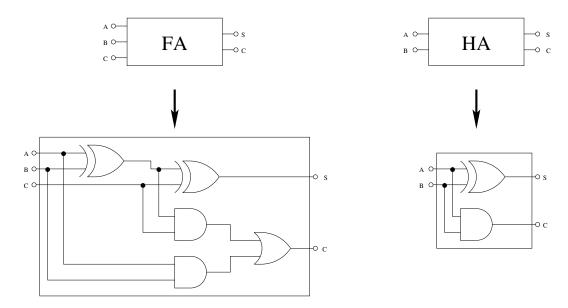

The block schematic of the full adder (FA) and the half adder (HA) is given i Figure 2.6, and standard gate-level designs for those two components is given in Figure 2.5. They have the following algorithmic output[9]: HA:

$$S = A \oplus B \tag{2.2}$$

$$C_{out} = A \cdot B \tag{2.3}$$

FA:

$$S = (A \oplus B) \oplus C_{in} \tag{2.4}$$

$$C_{out} = (A \cdot B) + (C_{in} \cdot (A \oplus B)) = (A \cdot B) + (C_{in} \cdot A) + (C_{in} \cdot B)$$

(2.5)

The result may have up to two outputs per bitweight (or column). By using a vector merging adder, one can reduce the output to a valid binary result. As said in Section 2.3.2, there are a lot of different ways to design a VMA. More discussion of the impact of VMA is done in section 4.3.

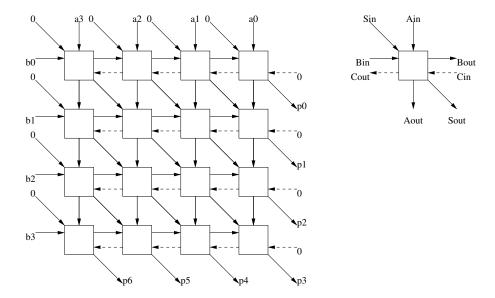

Figure 2.4: Carry-Save array multiplier

All of the algorithms use a matrix where the columns represents each bitweight and the number of rows represent how many partial products that bitweight has. Figure 2.7 shows an example of such a matrix, and how it is calculated. Each partial product is also often only represented by a dot (•) in the graph. The algorithm then reduces the matrix by adding FAs and HAs to it, which produces an output matrix, which represents the partial products for the next stage of the algorithm. The output matrix contains the partial products that still needs reduction. This task is repeated several times, until the output matrix contains only columns with one or two partial products. Each bitweight will then only have two outputs, and the result from the tree can be put into a vector merging adder (VMA). By connecting the FAs and HAs from each reduction stage, we will get a structure that looks very similar to a tree, hence the name: tree multiplier.

Because tree multipliers are faster and use less power than array multipliers [9, 21], the

Figure 2.5: Full adder (FA) and half adder (HA)

Figure 2.6: Half-adder and Full-adder elements used in Carry-Save adders

|            |          |          |          | $a_3$    | $a_2$    | $a_1$    | $a_0$     |

|------------|----------|----------|----------|----------|----------|----------|-----------|

|            |          |          |          | $b_3$    | $b_2$    | $b_1$    | $b_0$     |

|            | $a_3b_3$ | $a_3b_2$ | $a_3b_1$ | $a_3b_0$ | $a_2b_0$ | $a_1b_0$ | $a_0b_0$  |

|            |          | $a_2b_3$ | $a_2b_2$ | $a_2b_1$ | $a_1b_1$ | $a_0b_1$ |           |

|            |          |          | $a_1b_3$ | $a_1b_2$ | $a_0b_2$ |          |           |

|            |          |          |          | $a_0b_3$ |          |          |           |

| Inputs:    | 1        | 2        | 3        | 4        | 3        | 2        | 1         |

| Bitweight: | $6(2^6)$ | $5(2^5)$ | $4(2^4)$ | $3(2^3)$ | $2(2^2)$ | $1(2^1)$ | $0 (2^0)$ |

Figure 2.7: Setup of partial products in a tree multiplier

power optimizing done in this project is to decrease the power used in well-known tree multiplier schemes. The rest of this section contains explanation on how three tree algorithms function.

#### 2.4.1 Wallace-tree

The Wallace algorithm[2] is the oldest of the algorithms presented here. It reduces the input matrix by grouping the rows together, and performs reductions on each group. Rows that are not part of any group is just transferred to the next stage of the algorithm. The algorithm is as following:

- 1 Group the rows into sets of three (see Figure 2.8)

- 2 Add FA for each group with three wires in, and a HA for each group with two wires in. This produces a new set of partial products, which represent the next stage.

- 3 If one or more columns contains more than two bits/rows, repeat the process.

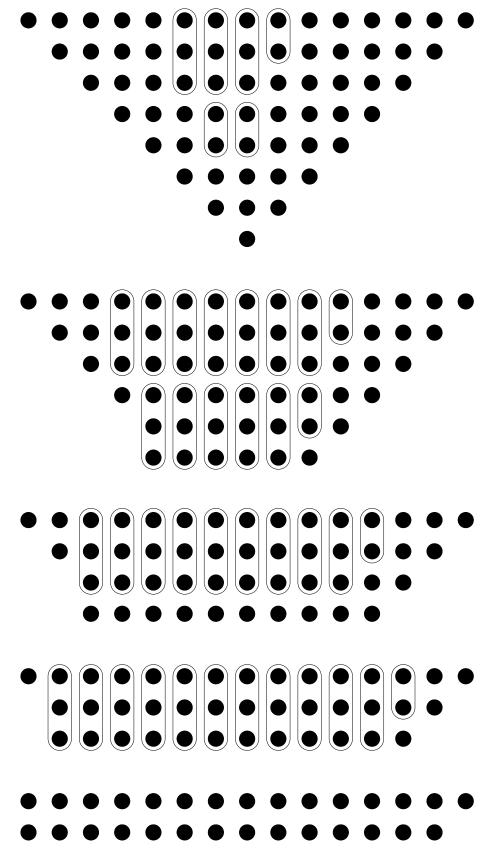

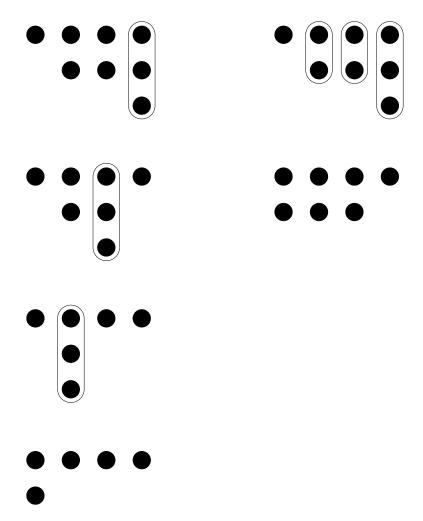

In Figure 2.8 we see a  $8 \times 8$  multiplier, that uses 39 FAs and 14 HAs. If we compare the resulting multiplier with the Carry-Save array, it uses less adder elements ( $8 \times 8$  Carry-Save array uses 64 adders). And the delay is a lot smaller. The Wallace tree needs for reduction stages, and therefore have a critical path of four elements, but the  $8 \times 8$  Carry-Save array have a critical path consisting of eight elements. Tree structure does not have such a nice repetitive structure as the array, so it uses a lot more area on wiring[21].

Figure 2.8: Wallace tree for a  $8 \times 8$  multiplier

Figure 2.9: Dadda tree for a  $8 \times 8$  multiplier

#### 2.4.2 Dadda-trees

The Dadda algorithm reduces the tree by reducing columns instead of rows. The goal of the algorithm is to use the least amount of elements as possible. To accomplish this, the algorithm adds elements as late as possible. The algorithm is as follows[3, 30]:

- 1 Let  $d_1 = 2$  and  $d_{j+1} = \lfloor 3 \cdot d_j/2 \rfloor$ , where  $d_j$  is the maximum height of the tree at the j-the reduction stage. Find the largest j, so that at least one of the columns has more bits than  $d_j$ .

- 2 Use FAs and HAs to reduce the partial products, so that no column has more than  $d_j$  bits left (see Figure 2.9)

- 3 If one or more columns contains more than two bits/rows, let j = j 1 and repeat step 2.

The Dadda algorithm uses less FAs and HAs than Wallace. According to Habibbi and Witz[16] it uses the optimum amount of FAs. It is possible to make algorithms that use less HAs, but they would require more FAs.

And since it allocates elements as late as possible, it requires a larger VMA than Wallace. This is because the least significant bit would not get reduces until the last stage, and we will always start at bit two for the VMA. Therefore the VMA would always need  $(n \cdot m) - 2$  bits for a Dadda multiplier. But the Dadda tree uses a lot less HAs, and is in studies found to be faster and smaller than the Wallace tree[31], despite the larger VMA.

#### 2.4.3 Reduced Area multiplier

Since Dadda uses a larger VMA and Wallace uses HAs extensively, Bickerstaff et. al.[4] proposes an algorithm that tries to improve those drawbacks. Their "Reduced Area Multiplier" uses few HAs (about the same as Dadda) and needs a smaller VMA than Wallace. Since this algorithm also tries to reduce the number of wires as early as possible, this algorithm should produce less interconnection and smaller area than both Dadda and Wallace[4]. The Reduced Area multiplier uses this algorithm[4]:

- 1 Add  $|b_i/3|$  FAs in each column, where  $b_i$  is the number of bits in column i.

- 2 HAs are used only when

- 2.1 When required to reduce the number of bits in a column to the number of bits specified in the Dadda series (see Chapter 2.4.2).

- 2.2 To reduce the rightmost column containing only two bits

As we can see from step 2.2, this algorithm always tries to reduce the least significant two-wire output. Because of this, it will reduce the VMA with at least one for every row. This is the reason it gets smaller VMA-sizes. And since it has the least interconnection[4] it should dissipate the least amount of power through interconnections.

Figure 2.10: Reduced Area tree for a  $8 \times 8$  multiplier

# Chapter 3

# Power estimation

Power estimation is the technique to find the power usage of a design, without having to do the actual implementation on silicon. Several different types of power can be measured, but finding the average or worst case power consumption is widely the most used application. By doing this before implementing, developers are able to cut the cost, since computer based estimations are much cheaper than actual silicon implementations. As the requirement for low power increases, the research and need for high level power estimation also increases [32].

Numerous methods for estimating power exists, often divided into two categories [33]: probabilistic and statistic. Inside each sub category, there are also different techniques based whether the estimation is done on system-, block-, gate- or transistor-level, and if the circuit is strongly combinatorial or not. In section 1.1.2 we show that the power usage is strongly correlated with the activity in the circuit. This is therefore the most used variable in the estimation. Several techniques considers the other power elements too small to be of any value to estimate [33]. The power consumed is also dependant on chip heating and temperature, but these variables are often set to a constant value when doing estimations [34]. The effect estimate of the chip might be higher or lower than an real world application This since corner values often are chosen, instead of typical operation temperatures. The estimate relative to other estimates using the same parameters will still be accurate.

The importance of accurate timing data are also important, since a lot of the switching activity comes from glitches (explained in section 1.1.3) in multipliers [22]. Without proper delay values, the power estimation will be considerably less accurate. This is especially true in circuits with high probability of glitches, such as multipliers.

## 3.1 Probabilistic based methods

Probabilistic approaches are based on calculating the probability of a change in a gate, and using that information to determine the probable power consumption. Several different techniques exists, but a common foundation is that it is easy to calculate a gate probable

| В | OUT         |

|---|-------------|

| 0 | 1           |

| 1 | 0           |

| 0 | 0           |

| 1 | 0           |

|   | 0<br>1<br>0 |

Table 3.1: Truth table for NOR-gate

power consumption. Given that a gate consumes power during  $0 \to 1$  transitions (see Equation 1.5 on page 3), it is only necessary to calculate the probability for this scenario to happen. Using the truth table of a NOR-gate, given in table 3.1, in a zero delay environment produces this equation:

$$p(0 \to 1) = p(0) \cdot p(1) = \frac{3}{4} \cdot \frac{1}{4} = 0.1875$$

(3.1)

This calculation does, however, not take glitching into account, or consider that gates have delays between them. This kind of delay is shown to have a large impact on larger combinatorial circuits, such as multipliers [22]. This model also considers the probability for the inputs to be uniformly distributed. It is often assumed that signals are independent of each other, but that is not often the case. Two signals may never be high at the same time. This is called spatial correlation [34].

Another assumption is that a signals value over two clock cycles are independent of each other. This is often also not the case. This is called temporal correlation. The signals in equation 3.1 are considered both spatial and temporal independent [34].

To overcome the limitations of the simple signal probability model, several other methods have been proposed [34]. A proposition to use waveforms to solve the temporal dependency has been used, and by this changing the probability for each gate inputs based on time. This method might look similar to an event-driven simulation approach. A similar method is also used by Oskuii [5] in his optimization work. Another approach is to calculate the average number of transitions in each node in a circuit, using a single pass algorithm using the concept of Boolean difference. A third method tries to handle both spatial (though only internally) and temporal by using binary decision diagram [11]. The method defines the boolean function for each node, and uses this information to generate BDD-diagrams for the node, and using this information to calculate power usage. The disadvantage with BDD is that it is slow. A overview over these techniques is found in Najm [34].

All but one (BDD) of the techniques ignores spatial dependency. They are fast to compute, according to Najm [34]. BDD does take spatial dependency into account, but are also a slow algorithm. They are also less pattern dependent than their statistic counterpart. This is because the designer can specify the probability of the inputs, which is often more available to designers than specific input patterns. Another solution is to calculate the probabilities by surveying a large set of input patterns. Since the only calculation that needs to be done to the input patterns, is the calculation of probability for, large data sets can be used. They are however quite complex, and can be more difficult to implement than their counterpart. The accuracy is also slightly lower than statistical approaches, but they can be faster [34].

## 3.2 Statistic based estimations

Statistic approaches are simpler. The basic idea is to mimic a system, and do simulation with different input patterns, and then sum up the power used during the simulation. We only look at switching power, which is common in simulation techniques. This is because the majority of power dissipates from switching. Naming each input  $x_i$ , and combining this with Equation 1.4, the energy consumption of transition in each signal is [10]:

Energy<sub>transition of x<sub>i</sub></sub> =

$$\frac{1}{2}C_iV_{dd}^2$$

(3.2)

By counting transitions in each node, it it possible to calculate the energy used by summing the energy used in each gate [10]:

$$Energy_{total} = \frac{1}{2} \sum_{i=1}^{N} n_{x_i} C_i V_{dd}^2$$

(3.3)

Where N is the number of gates and  $n_{x_i}$  is the number of transitions in signal  $x_i$ . If we introduce  $n_{x_i}(T)$  instead of  $n_{x_i}$ , which is the number of transitions happening during time T, one can compute the power effect of the system [10]:

$$P_T = \frac{1}{2} \sum_{i=1}^{N} \frac{n_{x_i}(T)}{T} C_i V_{dd}^2$$

(3.4)

Since we usually need an average power dissipation over time, the average power dissipation is therefore given by the following equation [10]:

$$P_{switching} = \lim_{T \to \infty} P_T = \lim_{T \to \infty} \frac{1}{2} \sum_{i=1}^{N} \frac{n_{x_i}(T)}{T} C_i V_{dd}^2$$

$$(3.5)$$

Simulation techniques use this as a basis to calculate the power used. The time T is in the equation set to be infinite, but that is not very feasible. In practical application simulation is done over a finite time interval, and the measured power is then believed to converge close to the actual power usage of the system [34].

These techniques are however very pattern dependent. Different input patterns could result in very different results of the power optimization, and is therefore hard to determine the accuracy of the result. And if we were to test all possible input variables, it would be too time consuming.

# 3.3 A Monte Carlo approach

To address the problems outline in the previous section, Burch [10] proposed a Monte Carlo approach for power estimation. By defining it  $x_i(t)$  as a stochastic process, it is possible to calculate the error of the estimation. When the error is known, it is possible to know when to stop simulating, by stopping when the desired level of error is reached.

By defining  $x_i(t)$  a stochastic process,  $\mathbf{x}_i(t)$ , one can define  $\mathbf{P}_T$  as the random power of  $\mathbf{x}_i(t)$  over the interval  $(-\frac{T}{2}, +\frac{T}{2}]$ :

$$\mathbf{P}_{T} = \frac{1}{2} \sum_{i=1}^{N} \frac{\mathbf{n}_{x_{i}}(T)}{T} C_{i} V_{dd}^{2}$$

(3.6)

Burch [10] show that the expected value of  $\mathbf{P}_T$  is the same for any T, and thus showing:

$$P_{switching} = \text{expected value}[\mathbf{P}_T]$$

(3.7)

The problem is now reduced to a mean estimation problem, which is common in statistics. The whole deduction is available in Burch [10].

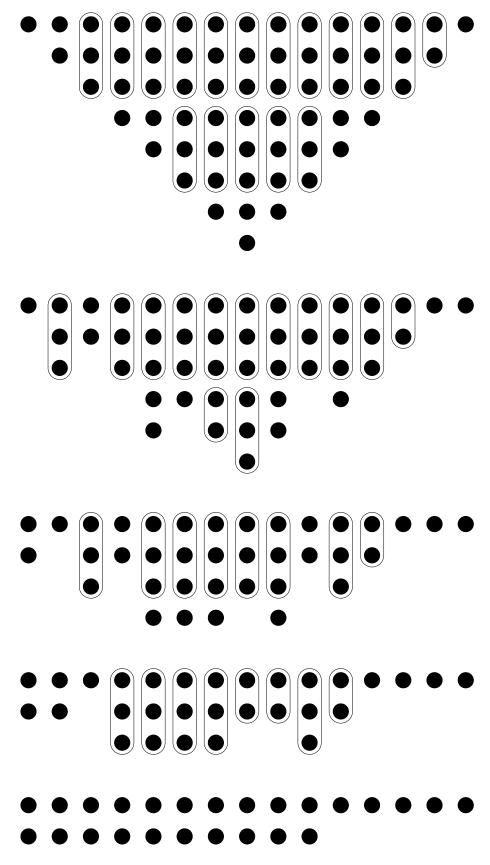

Figure 3.1: Flow diagram of Monte Carlo. From Burch [10]

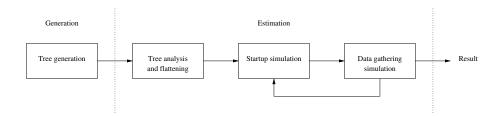

### 3.3.1 Flow of the method

The Monte Carlo approach defines the flow-chart in figure 3.1 as its method. The first thing to do is to load the circuit and simulation information. The next step is the setup phase. The point of this is to put the circuit in a working state, so the power information extracted from the circuit is as accurate as possible. The length of the setup is determined by the length of the critical path. It is important that all elements in the design switch at stable rates before the recording of power information starts.

When the setup is done, it is possible to extract power information from the circuit. This is very similar to the setup step. By restarting the simulator, it is possible to record power usage in the circuit during this stage of the simulation. A problem of the approach, is that there are not easy to compute the length of this part of the simulation. The variable is most feasible to find through experiments, or by setting it larger enough by a good margin.

The power result is then analyzed, and the maximum expected error is calculated. If the maximum expected error is larger than the desired error, one has to run the simulation for another round. By doing the iterations until the expected maximum error is below the desired error, one has a power estimate that is sufficient.

#### 3.3.2 Calculating Maximum expected error

An important aspect in the Monte Carlo approach is to calculate the, since the is the stop criteria for the algorithm. By computing the error, the algorithm becomes easier to use, since the user can specify if one wants very fast but not very accurate or a very accurate estimate of power.

By assuming  $\mathbf{P}_T$  is normally distributed, Burch [10] gives the following equation for a stop criteria:

$$\frac{t_{\alpha/2}s_T}{\eta_T\sqrt{N}} < \epsilon \tag{3.8}$$

Where  $\epsilon$  is the desired percentage error,  $\eta_T$  is the sample average and  $s_T$  is the sample standard deviation over the N different  $P_T$ -values found through simulation. The variable  $t_{\alpha/2}$  is obtained through the t distribution [35]. Burch [10] also claims the number of simulations (i.e. the number of different  $P_T$  values) need to be done remains almost constant in proportion to the circuit size. The number of iterations should infant decrease slightly when used on larger circuits. This makes the Monte Carlo technique independent of circuit size, and places the run-time of the estimation in the hands of the simulator.

This stop criteria determines when to stop to get the power estimation of the whole circuit under the desired percentage error. A problem in optimization problems is that one often need information about where in the circuit is the power dissipated.

Xakellis [36] proposes a slightly different stop criteria, that simulates the circuit longer, to get accurate power results on gate level. Dividing the gates into regular density nodes and low density nodes, the algorithm uses a different stop criteria for each group. The regular density nodes have an average amount of transitions during the simulation, and can therefore with few iterations give power estimates within the acceptable error level. The low density nodes however have far less transitions during the simulation, and would require a lot more stimuli to get power estimates within the accepted level of error. Xekallis [36] therefore sets another stop criteria for those nodes. Since the low density nodes have few transition, they have the least impact on power usage, it should be acceptable with higher margin of error in these nodes. By dividing the nodes like this, the run time of the algorithm gets significantly reduces, compared to treating all nodes as regular nodes, with almost no decrease in the overall accepted level of error.

# 3.4 Random number generator

Since simulation approaches are in need of input patterns to perform power estimation, it is common to use a random or pseudo random number generator. By using a pseudo random number generator with a seed, it is possible to get the same random numbers for each set of numbers the random number generator delivers. This means the the generator can deliver the same input-patterns for several circuits that are under test, or even several different programs, without having to save the input-patterns.

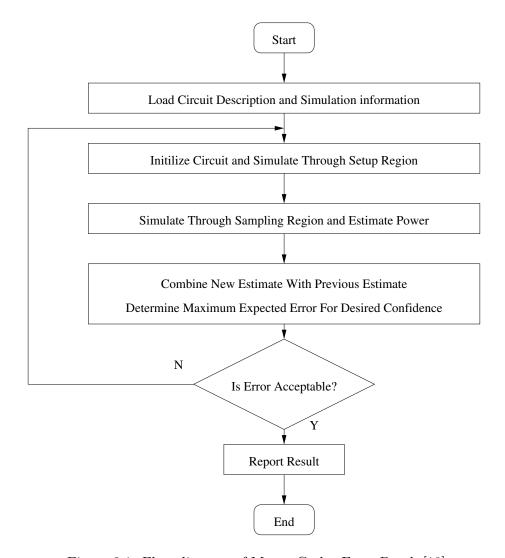

A linear feedback shift register [12, 13] (LFSR) can be used as a pseudo random number generator, and produces the same sequence of random numbers, given the same seed. A LFSR is very easy to implement in both hardware and software, as it only uses a shift register and a set of XOR-ports. It delivers good random numbers, almost equal to the statistical expectation value of true random events. The LFRS has a sequence of  $2^n - 1$  states, where n is the size of the shift register.

The LFSR can be implemented with either XOR or XNOR ports. This section will show an example of an XOR implementation. The LFRS has all 0's as an illegal state

when implementing with XOR, since the register would then be locked in the same state indefinitely. When using XNOR, the illegal state is all 1's. The LFSR uses XOR/XNOR ports on selected bits in the register as a feedback into the register. This way it produces a new unique sequence for each shift, if the XOR/XNOR ports are placed to get maximum sequence length [12, 13].

Figure 3.2: A 32-bit LFSR, implemented in hardware

Figure 3.2 show an example of an implementation in hardware. Here bits 1, 2, 22 and 32 are XOR'ed, and used as a feedback for the register. The placement of the XOR elements ensures a maximum length of the sequence. A list of placement of XOR elements for maximum length can be found in [12, 13]. The bit shifted out of the register is in most cases used as the output. This means that one has to do a shift operation for each pseudo random bit, to ensure statistical properties needed for a random number generator. Listing 3.1 show an implementation in software, although using the alternative output from Figure 3.2 instead of the regular output, and a startup seed of 1.

# Chapter 4

# Power optimization

Optimization may be applied in most stages of the generation of multiplier. Most optimizations are done at either block-level or at transistor-level. This chapter focuses on three types of optimizations done at block-level. Algorithm optimization concentrates on how different reduction schemes differ from each other, and that some might have better power-characteristics than others.

Interconnect optimization focuses on connections between adders inside the multiplier tree. There are several different ways of connecting the adders together, and some mutations might be better than others. Since the multiplier trees use Carry-Save scheme, there is a need for a VMA as last stage of the multiplier. The last section look at sizes of VMAs, and their impact on the overall power consumption.

# 4.1 Algorithm optimization

There are several algorithms used to generate multiplier trees, as explained in Section 2.4. Since they use different reduction schemes, they will also use a different amount of adders, as seen in Table 4.1. This gives each scheme different delays and power consumption properties. The difference in the adders also makes the bit width of the VMA different, which in turn influences how much power the VMA will use. The smaller the VMA is, the less power consumption it will have.

Research effort has been made to compare array multipliers with tree multipliers, and most sources agree that tree multipliers have less delay and use equal or less power, at the

| Generation algorithms | Size           | FA  | HA  | Adder size |

|-----------------------|----------------|-----|-----|------------|

| Wallace [2]           | $8 \times 8$   | 38  | 15  | 11         |

| Dadda [3]             | $8 \times 8$   | 35  | 7   | 14         |

| Reduced Area [4]      | $8 \times 8$   | 39  | 7   | 10         |

| Wallace [2]           | $12 \times 12$ | 102 | 34  | 18         |

| Dadda [3]             | $12 \times 12$ | 99  | 11  | 22         |

| Reduced Area [4]      | $12 \times 12$ | 104 | 11  | 17         |

| Wallace [2]           | $16 \times 16$ | 200 | 54  | 25         |

| Dadda [3]             | $16 \times 16$ | 195 | 15  | 30         |

| Wallace [2]           | $32 \times 32$ | 906 | 164 | 55         |

| Dadda [3]             | $32 \times 32$ | 899 | 31  | 62         |

Table 4.1: Comparison of well-known tree generation algorithms. Numbers from [4] and [6]

cost of area on the chip [21, 29]. There are however less research about how power usage of different tree multipliers is compared to each other.

Several studies have investigated the delay and size differences of the different multipliers [16, 31, 4, 6]. The conclusion of all of them is that Dadda multipliers use less area then a Wallace type multiplier, while having about equal delay. Since the Dadda multipliers use less area and adder elements, there is reason to believe they also use less power. This is however not confirmed by any of the studies.

The Reduced Area (RA) multiplier by Bickerstaff [4] uses less area than the Dadda multiplier, but uses a few more adder elements. The main reason RA multipliers are smaller, are because they use less area on wiring. Since Dadda reduces as late as possible, it should be more prone to glitching problems than RA. These two properties (less area and earlier reduction) of the RA multiplier should lead to less power consumption than Dadda, and therefore also Wallace. In addition to using less power, the RA multiplier needs the smallest VMA of all three algorithms, and should therefore save energy in that part of the multiplier as well.

This comparison leads us to believe that the Wallace uses the most power of the three algorithms. Which algorithms, the Dadda or the RA, that uses the least amount of power is not easily determined. RA uses slightly more adders, while using less wires than Dadda. It would seem as if the RA algorithm would perform better than Dadda.

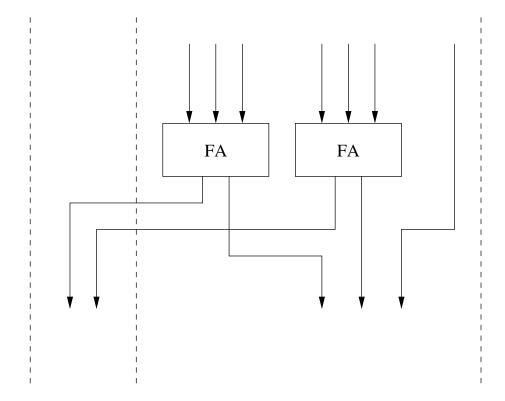

# 4.2 Interconnect optimization

Each algorithm produces a tree structure of adders. However, the algorithms do not describe how the interconnections between the adders are supposed to be. Changing the interconnections inside a column does not change the functionality. A column containing four partial products might get reduced with one FA. Three of the PPs are then connected to the adder, and the fourth PP is just a feed-through line to the next stage in the reduction process. This causes different delays for different partial products, and raises the question: How should the lines be connected to consume the least amount of power? An exhaustive search of all possible mutations would be too time consuming to compute.

#### 4.2.1 Reduction of search space

Oskuii [5] suggests that the lines with the highest activity should be connected to the least amount of adders. This will lead to less transitions in the circuit. He also extends the assumptions, and proposes that lines with the most activity should be connected to gates with the least amount of delay. Since glitches are caused by unbalanced inputs, it should be energy efficient to let the lines with highest probability for transition traverse as fast as possible in the tree. This will let the high transition lines less likely to cause glitches.

Najm [34] introduced the notation of transition density, which Oskuii [5] also adopts. The density describes the average amount of transitions in a gate:

$$D_i = \lim_{T \to \infty} \frac{n_{x_i}(T)}{T} \tag{4.1}$$

Since each column adds PPs to the same column on the next reduction stage, or the column with a larger bit weight, optimizing should be done from the rightmost columns (least significant bits) to the rightmost columns (most significant bits), and from the first stage to the last stage. This should prevent the optimization to change the power consumption of previous optimizations. Oskuii [5] therefore assumes it is safe to optimize each column separately, if done in this order. By doing this, one might end up at a local minima, but this is a good trade-off compared to doing a brute force search of all possibilities. Since the problem is NP hard [37], local solution is an acceptable solution, since a global minima would require a full test of all possibilities.

Oskuii [5] proposes to do a post-optimization, after the multiplier tree is generated. Iterating through every column in every stage, each partial product is sorted by transition density (like in Figure 4.1). In each column, a set of interconnect mutations believed to give low power consumption is made. This reduces the problem dramatically, since it discards most mutations in this step. Each low power mutation runs through a power estimator, and the mutation yielding the lowest power consumption is used for the column. This is done for all columns in the multiplier.

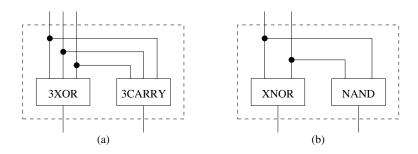

The reduction of interconnect mutation is done with the knowledge that FAs and HAs have different delay. An HA only has one gate in its critical path for both inputs, which is less then the FA. The HA should therefore have higher density partial products as inputs, than an FA. A feed-through (a partial product not connected to a adder in the stage) has no gates, and should therefore have a very small delay. The partial products with the highest density should therefore not be connected to an adder, but rather get redirected to the next stage of the reduction. We now have two rules, which should reduce the amount of mutations in each column.

Looking at Figure 2.5 on page 11, we can see that an FA does not have balanced inputs. The C input has less gates to both outputs than input A and B. This means that input C has less delay through the adder than A and B. Adding the partial products with least density to input A and B should give less power consumption. This makes three rules to reduce the amount of interconnect mutations. By employing these rules when construction a set of possible interconnections, we get a much smaller set then by using all possible mutations.

Figure 4.1: Sorting partial products based on activity. From [5]

The algorithm can be rather computing exhaustive, since it is mandatory to do power estimates for each mutation, and then choose the mutation that uses the least amount of energy. It is therefore critical to have a fast power estimator. The optimization routine can

also be used to optimize against highly correlated input data. By estimating power usage using correlated data, the optimization will optimize towards the least amount of power usage for that kind of input. This shows that the optimization routine proposed is very dependent on the estimation for accurate results.

# 4.3 Vector Merging adder

ASYMPTOTIC TIME AND AREA REQUIREMENTS OF n-bit ADDERS

| Adder Type                      | Abbreviation | Time             | Area          |

|---------------------------------|--------------|------------------|---------------|

| Ripple Carry Adder              | RCA          | O(n)             | O(n)          |

| Manchester Carry Chain adder    | MCC          | O(n)             | O(n)          |

| Constant width carry SKip adder | CSK          | $O(\sqrt{n})$    | O(n)          |

| Variable width carry SKip adder | VSK          | $O(\sqrt{n})$    | O(n)          |

| Carry SeLect adder              | CSL          | $O(\sqrt{n})$    | O(n)          |

| Carry Lookahead Adder           | CLA          | $O(\log n)$      | $O(n \log n)$ |

| Brent and Kung adder            | B&K          | $O(\log n)$      | $O(n \log n)$ |

| ELM adder                       | ELM          | $O(\log n)$      | $O(n \log n)$ |

| Signed Digit adder (base- $r$ ) | SD-r         | $O(b)^{\dagger}$ | O(n)          |

| Carry Save Adder                | CSA          | O(1)             | O(n)          |

b is the number of bits per digit.

Table 4.2: List of surveyed adder types in Nagendra [7]

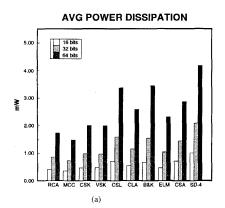

There are a lot of different types of adders that can be used as a Vector Merging Adder, to convert the result to a regular binary number. Nagendra [7] has an excellent overview over commonly used adders, and Table 4.2, Table 4.3 and Figure 4.2 are from that survey.

ADDER CIRCUIT DESCRIPTION

|       |                                |        | 7 100  | EK CIKCOI | DESCRI             | 110.1  |        |                           |        |  |

|-------|--------------------------------|--------|--------|-----------|--------------------|--------|--------|---------------------------|--------|--|

| Adder | Area $(\times 10^6 \lambda^2)$ |        |        | No.       | No. of transistors |        |        | Max transistor size (n/p) |        |  |

| Type  | 16-bit                         | 32-bit | 64-bit | 16-bit    | 32-bit             | 64-bit | 16-bit | 32-bit                    | 64-bit |  |

| RCA   | 0.40                           | 0.80   | 1.60   | 596       | 1204               | 2420   | 3/3    | 3/3                       | 3/3    |  |

| MCC   | 0.48                           | 0.96   | 1.90   | 642       | 1298               | 2610   | 4/4    | 4/4                       | 4/4    |  |

| CSK   | 0.82                           | 1.62   | 3.22   | 682       | 1410               | 2866   | 4/4    | 4/4                       | 4/4    |  |

| VSK   | 0.81                           | 1.76   | 3.44   | 706       | 1440               | 2900   | 3/3    | 3/3                       | 3/3    |  |

| CSL   | 0.76                           | 1.45   | 2.75   | 914       | 1982               | 4128   | 5/7    | 6/10                      | 8/13   |  |

| CLA   | 1.14                           | 2.27   | 4.55   | 1038      | 2132               | 4348   | 4/4    | 4/4                       | 4/4    |  |

| B&K   | 1.25                           | 3.00   | 6.76   | 1072      | 2442               | 5444   | 3/3    | 3/3                       | 3/3    |  |

| ELM   | 1.08                           | 2.36   | 5.38   | 892       | 2078               | 4752   | 3/5    | 5/7                       | 8/12   |  |

| CSA   | 1.05                           | 2.03   | 3.90   | 1176      | 2360               | 4728   | 3/3    | 3/3                       | 3/3    |  |

| SD-4  | 1.36                           | 2.71   | 5.41   | 1550      | 3166               | 6398   | 3/5    | 3/5                       | 3/5    |  |

| SD-8  | 1.11                           | 2.42   | 4.61   | 1228      | 2812               | 5452   | 3/5    | 3/5                       | 3/5    |  |

| SD-16 | 1.09                           | 2.17   | 4.32   | 1186      | 2490               | 5098   | 3/5    | 3/5                       | 3/5    |  |

| SD-32 | 0.97                           | 2.25   | 4.16   | 1020      | 2572               | 4900   | 3/5    | 3/5                       | 3/5    |  |

| SD-64 | 1 12                           | 2 23   | 4.07   | 1180      | 2530               | 4780   | 3/5    | 3/5                       | 3/5    |  |

Table 4.3: Area and number of transistors in adders from Nagendra [7] survey

Table 4.2 contains the different adders surveyed, and their delay and area functions of size. Table 4.3 contains area and transistor usage information about the adder structures. Since the survey counts transistors instead of adder elements, one has to convert the tree structures in this thesis to transistors to compare the size of the VMA to the size of the multiplier tree. Nagendra uses 24 transistors for each FA and 14 transistor for each HA, and uses six transistors around each adder as buffer and driver. The total transistors for each adder element can be found in table 4.4.

Since it is beneficial to know how much impact the VMA has on the overall power usage, we will combine the information from Nagendra [7] with known sizes for multiplier trees [4].

| Element | Transistors |

|---------|-------------|

| FA      | 30          |

| HA      | 20          |

Table 4.4: Transistor count for each element used in Nagandra [7]

|                       |                |            | Transistors |           |           |  |

|-----------------------|----------------|------------|-------------|-----------|-----------|--|

| Generation algorithms | Size           | Adder size | Tree        | RCA adder | CSA adder |  |

| Wallace [2]           | $8 \times 8$   | 11         | 1440        | 836       | 1628      |  |

| Dadda [3]             | $8 \times 8$   | 14         | 1190        | 1064      | 2072      |  |

| Reduced Area [4]      | $8 \times 8$   | 10         | 1320        | 760       | 1480      |  |

| Wallace [2]           | $12 \times 12$ | 18         | 3740        | 1368      | 2664      |  |

| Dadda [3]             | $12 \times 12$ | 22         | 3190        | 1672      | 3256      |  |

| Reduced Area [4]      | $12 \times 12$ | 17         | 3340        | 1292      | 2516      |  |

| Wallace [2]           | $16 \times 16$ | 25         | 7080        | 1900      | 3700      |  |

| Dadda [3]             | $16 \times 16$ | 30         | 6150        | 2280      | 4440      |  |

| Wallace [2]           | $32 \times 32$ | 55         | 30460       | 4180      | 8140      |  |

| Dadda [3]             | $32 \times 32$ | 62         | 27590       | 4712      | 9176      |  |

Table 4.5: Comparison of reduction trees and VMA