# IV and CV characterization of 90nm CMOS transistors

Håvard Lund

Master of Science in Electronics Submission date: June 2006 Supervisor: Trond Ytterdal, IET

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

Prototype circuits produced in 90nm CMOS are to be characterized by means of a new probe station and instrumentation for IV and CV measurements. The assignment will consist of measuring the capacitance-voltage and current-voltage transistor characteristics for this 90nm technology.

Assignment given: 16. January 2006 Supervisor: Trond Ytterdal, IET

### Abstract

A 90nm CMOS technology has been characterized on the basis of IV and CV measurements. This was feasible by means of a state of the art probe station and measurement instrumentation, capable of measuring current and capacitance in the low fA and fF area respectively. From IV results it was found that the static power consumption is an increasing challenge as the technology is scaled down. The IV measurements also showed the impact from small-channel effects, which was not as prominent as expected. Investigation of literature has resulted in a methodology for accomplishing accurate CV measurements on thin-oxide transistors. By using extraction methods on the capacitance measured, key parameters have been obtained for the CMOS technology. Some of the extracted results suffer however from the choice of test setup.

### Preface

This master thesis was accomplished in the spring of 2006 at the Department of Electronics and Telecommunications (IET), The Norwegian University of Science and Technology (NTNU). NTNU was also the proposer of the master thesis.

Academic advisor and supervisor has been professor Trond Ytterdal. He has provided for the superior project guidance, by arranging regular meetings, answering questions and giving me input in numerous discussions. He has also been holding test equipment lessons and providing the test transistors for physical measurements. All of this which I am very thankful for.

In addition I would like to thank the following persons:

- Principal engineer Tore Barlindhaug, for answering questions and preparing the lab instrumentation ready for use.

- Ph.D. student Tajeswar Singh, for giving me practical training on some of the measurement equipment and for useful discussions.

- M.Sc. Anders Lund, for creating small script to split the large size of data from simulations.

Trondheim, 12 June 2006

Håvard Lund

### **Acronyms and Abbreviations**

${f MOS}$  Metal-Oxide Semiconductor

${\bf MOSFET} \ {\bf Metal-Oxide} \ {\bf Semiconductor} \ {\bf Field-Effect} \ {\bf Transistor}$

${\bf MOS-C}\,$  Metal-Oxide Semiconductor Capacitor

**CMOS** Complementary MOS

${\bf NMOS}\,$ n-channel MOSFET

$\mathbf{PMOS}\ \mathrm{p\text{-}channel}\ \mathrm{MOSFET}$

$\mathbf{DC}\ \mathrm{Direct}\ \mathrm{Current}$

$\mathbf{AC}$  Alternating Current

**IV** Current vs. (DC bias) Voltage

CV Capacitance vs. (DC bias) Voltage

**DIBL** Drain-Induced Barrier Lowering

**ISS** Impedance Standard Substrate

$\mathbf{DUT}$  Device Under Test

**ABB** Auto-Balancing-Bridge

### Nomenclature

- $V_G$ MOSFET externally applied gate voltage [V] $V_D$ MOSFET externally applied drain voltage [V] $V_B$ MOSFET externally applied bulk voltage [V] $V_S$ MOSFET externally applied source voltage [V] $V_{GS}$ MOSFET externally applied gate-to-source voltage [V] $V_{DS}$ MOSFET externally applied drain-to-source voltage [V] $V_{SB}$ MOSFET externally applied source-to-bulk voltage [V]MOSFET total parasitic gate capacitance [F] $C_{gg}$  $C_{gb}$ MOSFET parasitic gate-to-bulk capacitance [F]MOSFET parasitic gate-to-source capacitance [F] $C_{gs}$  $C_{qd}$ MOSFET parasitic gate-to-drain capacitance [F]MOSFET total parasitic bulk capacitance [F] $C_{bb}$  $C_{bq}$ MOSFET parasitic bulk-to-gate capacitance [F] $C_{bs}$ MOSFET parasitic bulk-to-source capacitance [F]MOSFET parasitic bulk-to-drain capacitance [F] $C_{bd}$ MOSFET parasitic drain-to-bulk capacitance [F] $C_{db}$  $C_{sb}$ MOSFET parasitic source-to-bulk capacitance [F]MOSFET overlap capacitance between gate-drain or gate-source [F] $C_{ol}$  $V_{th}$ MOSFET threshold voltage [V] $V_{tn}$ MOSFET threshold voltage, NMOS specific [V]MOSFET threshold voltage, PMOS specific [V] $V_{tp}$  $V_{FB}$ MOSFET flatband voltage [V] $V_{eff}$ Effective gate voltage [V]WEffective width of MOSFET gate [m]LEffective length of MOSFET gate [m] $L_{ov}$ Overlap between gate and source, or gate and drain [m]MOSFET drain current [A] $I_D$ MOSFET gate leakage current [A] $I_G$ MOSFET drain-to-source subthreshold leakage current [A] $I_{sub}$ MOSFET drain-source conductance [A/V] $g_{ds}$ MOSFET drain-source resistance  $[\Omega]$  $r_{ds}$ MOSFET transistor transconductance [A/V] $g_m$

- $t_{ox}$  Thickness of MOSFET gate oxide [m]

- $\gamma \ \lambda$

- MOSFET body-effect coefficient  $[V^{1/2}]$  MOSFET channel-length modulation parameter [1/V]

# Contents

| 1        | Pro    | ject in                     | troduction                                                          | 1  |  |  |

|----------|--------|-----------------------------|---------------------------------------------------------------------|----|--|--|

|          | 1.1    | Motiv                       | ation                                                               | 1  |  |  |

|          | 1.2    | Method                      |                                                                     |    |  |  |

|          | 1.3    | .3 Structure of the report  |                                                                     |    |  |  |

| <b>2</b> | Theory |                             |                                                                     |    |  |  |

|          | 2.1    | Basic semiconductor physics |                                                                     |    |  |  |

|          | 2.2    | The MOSFET                  |                                                                     | 6  |  |  |

|          |        | 2.2.1                       | MOSFET dependency of gate-source voltage $V_{GS}$                   | 7  |  |  |

|          |        | 2.2.2                       | MOSFET dependency of drain-source voltage $V_{DS}$                  | 10 |  |  |

|          |        | 2.2.3                       | MOSFET dependency of source-bulk voltage $V_{SB}$ (the body effect) | 12 |  |  |

|          | 2.3    | MOSE                        | FET parasitic capacitances                                          | 13 |  |  |

|          |        | 2.3.1                       | The MOS capacitor (MOS-C)                                           | 14 |  |  |

|          |        | 2.3.2                       | Oxide-related capacitances                                          | 17 |  |  |

|          | 2.4    | techno                      | s on the MOSFET from downscaling in CMOS process blogy              | 20 |  |  |

|          |        | 2.4.1                       | Decrease in MOSFET parasitic capacitances                           | 20 |  |  |

|          |        | 2.4.2                       | Increase in leakage currents                                        | 20 |  |  |

|          | 2.5    | Mathe                       | ematical foundation                                                 | 22 |  |  |

|          |        | 2.5.1                       | MOSFET first-hand model equations                                   | 22 |  |  |

|          |        | 2.5.2                       | Definition of capacitance                                           | 24 |  |  |

|          |        | 2.5.3                       | MOSFET gate capacitance                                             | 25 |  |  |

|          |        | 2.5.4                       | Summary of MOSFET oxide-related parasitic capaci-<br>tances         | 25 |  |  |

|          |                | 2.5.5 Impedance                                                  | 26   |  |  |  |

|----------|----------------|------------------------------------------------------------------|------|--|--|--|

| 3        | $\mathbf{Spe}$ | pecifications 29                                                 |      |  |  |  |

|          | 3.1            | What to be measured                                              | 29   |  |  |  |

|          | 3.2            | DC measurements                                                  |      |  |  |  |

|          | 3.3            | AC measurements                                                  | 30   |  |  |  |

|          | 3.4            | Dimensions for 90nm transistors                                  | 30   |  |  |  |

| 4        | Test setup     |                                                                  |      |  |  |  |

|          | 4.1            | DC measurements for 90nm transistors                             |      |  |  |  |

|          | 4.2            | AC measurements for 90nm transistors                             | 35   |  |  |  |

|          | 4.3            | Measurement methodology for CV characterization                  | 35   |  |  |  |

|          |                | 4.3.1 Instrumentation setup and choice of measurement method     | ł 35 |  |  |  |

|          |                | 4.3.2 Connecting the DUT to measurement instruments $\therefore$ | 37   |  |  |  |

|          |                | 4.3.3 Compensation and calibration                               | 43   |  |  |  |

|          |                | 4.3.4 Accomplishment of measurements                             | 44   |  |  |  |

|          |                | 4.3.5 $$ Extraction of capacitance from measured impedance $$ .  | 46   |  |  |  |

|          | 4.4            | Simulation setup                                                 | 47   |  |  |  |

|          |                | 4.4.1 90nm transistors                                           | 47   |  |  |  |

| <b>5</b> | $\mathbf{Res}$ | Results for DC measurements at room temperature                  |      |  |  |  |

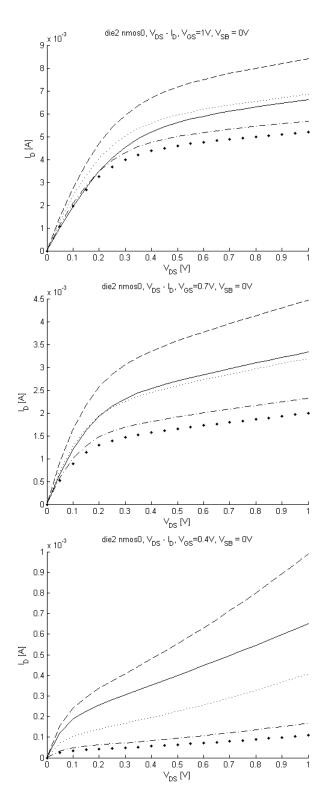

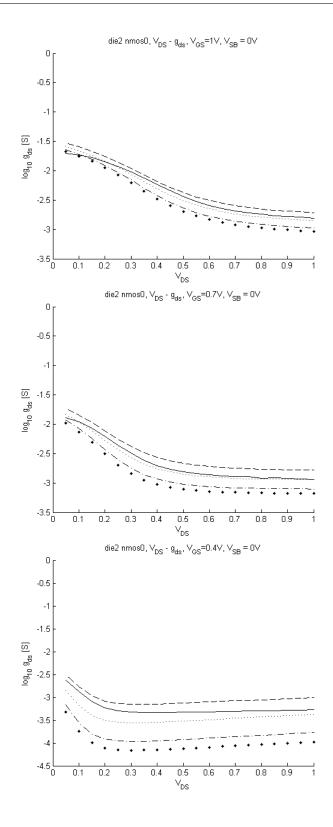

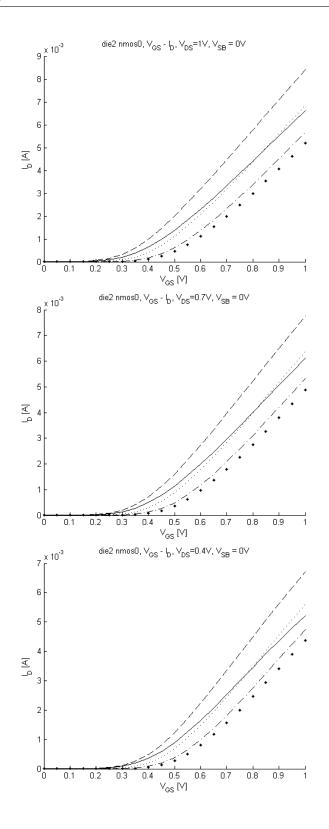

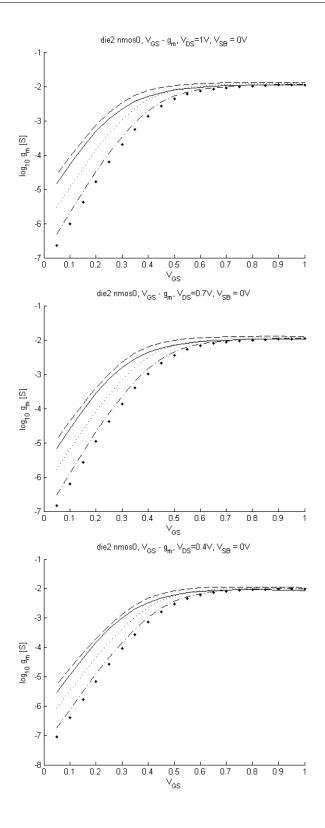

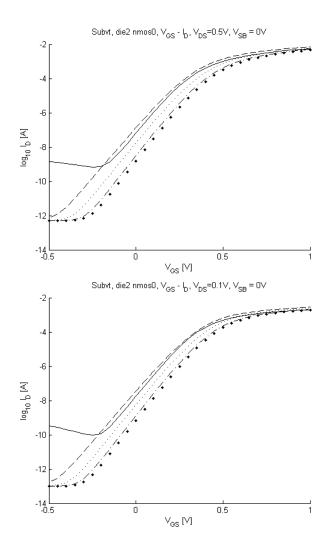

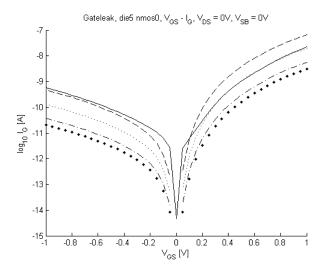

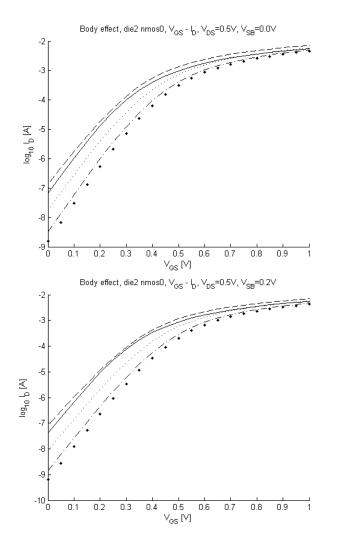

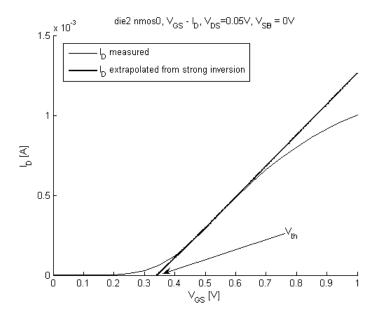

|          | 5.1            | nmos0                                                            | 51   |  |  |  |

|          | 5.2            | nmos1                                                            | 58   |  |  |  |

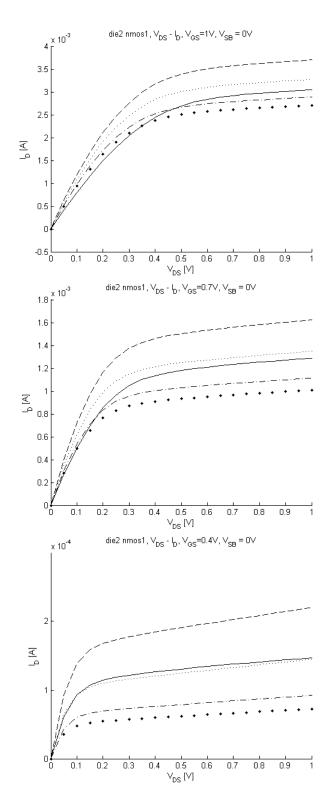

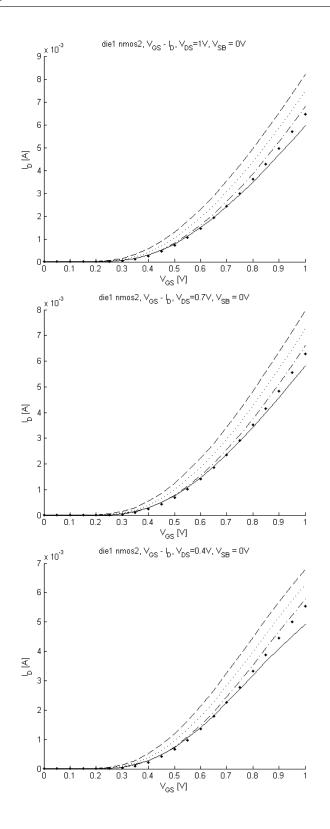

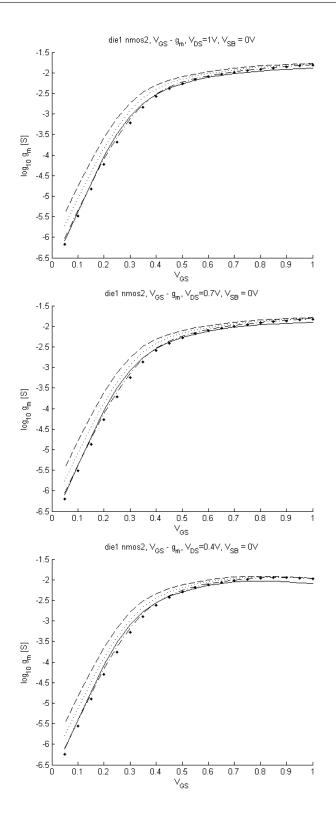

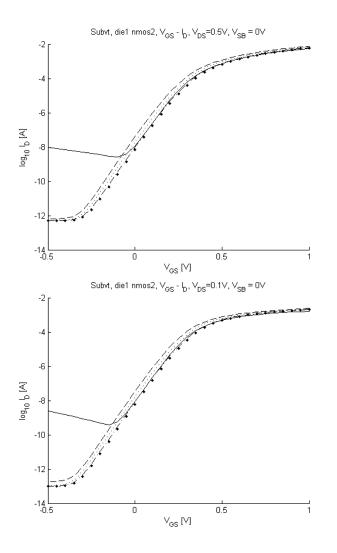

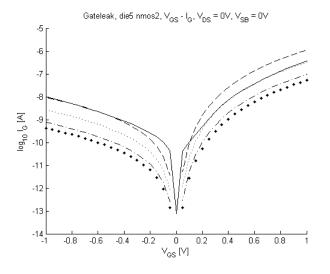

|          | 5.3            | nmos2                                                            | 65   |  |  |  |

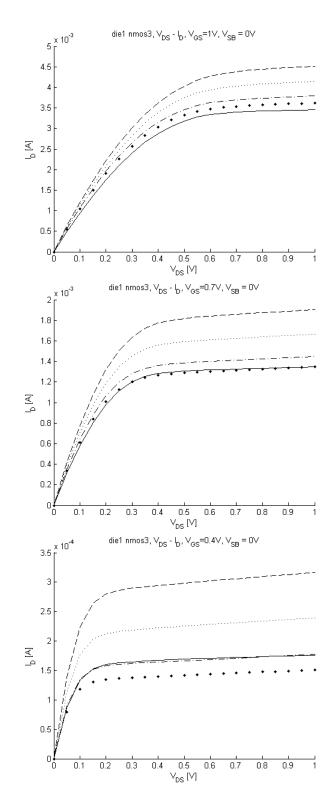

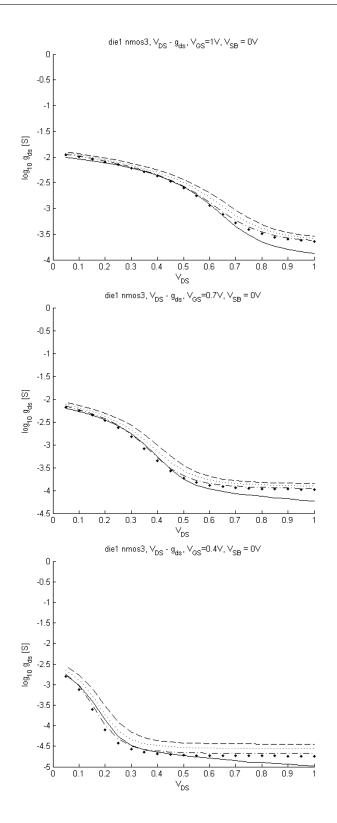

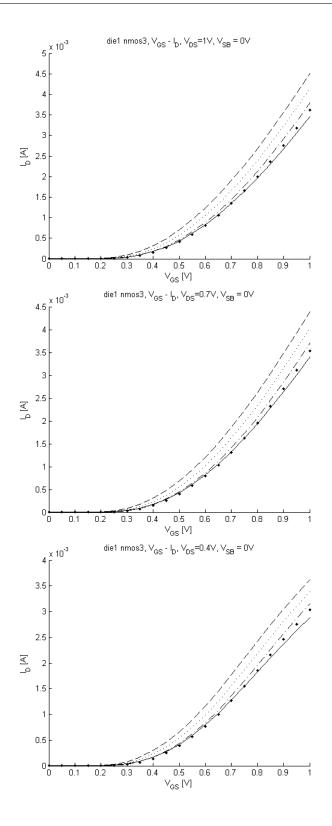

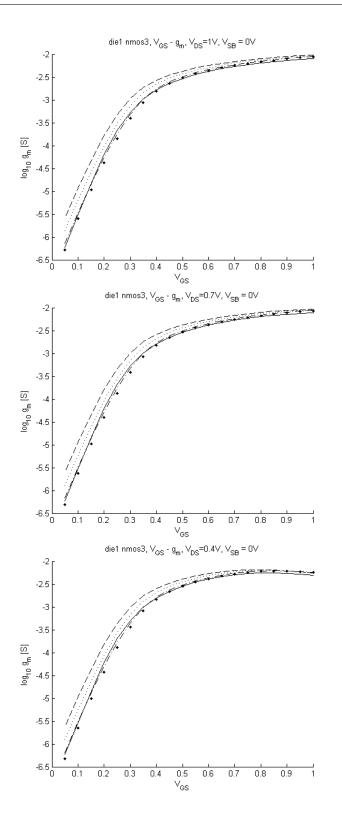

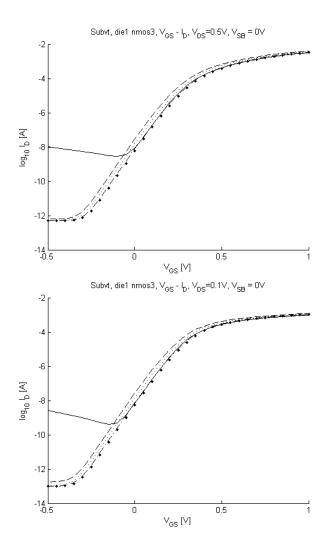

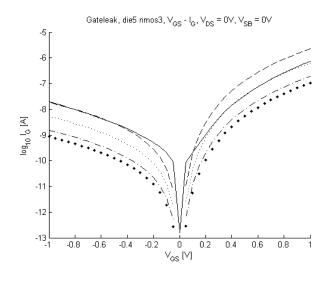

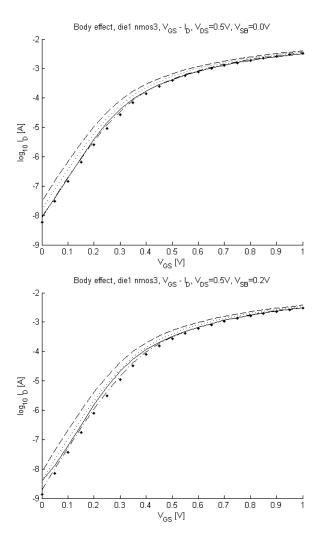

|          | 5.4            | nmos3                                                            | 72   |  |  |  |

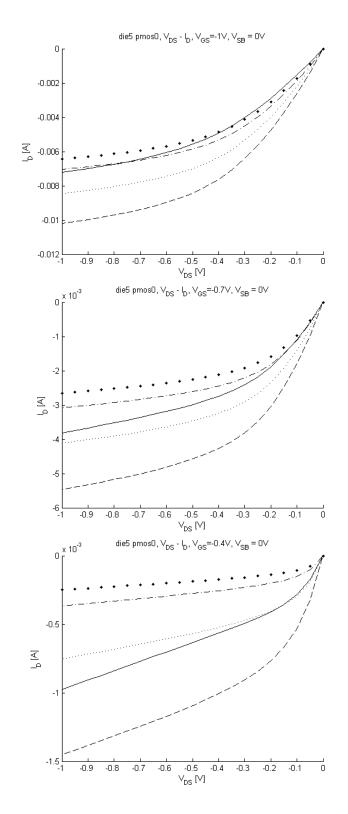

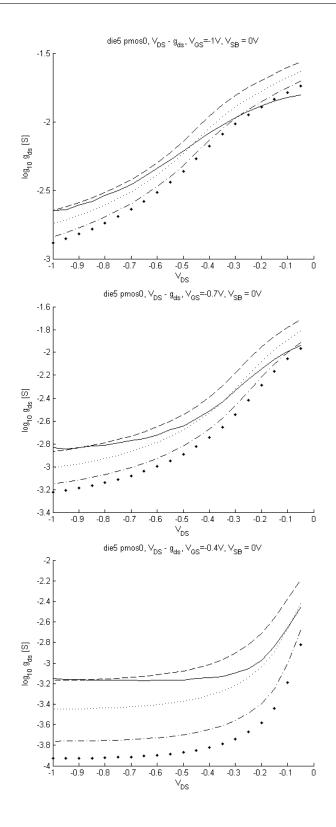

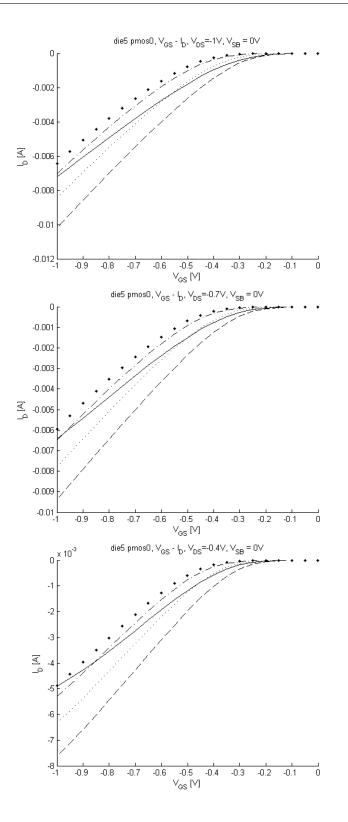

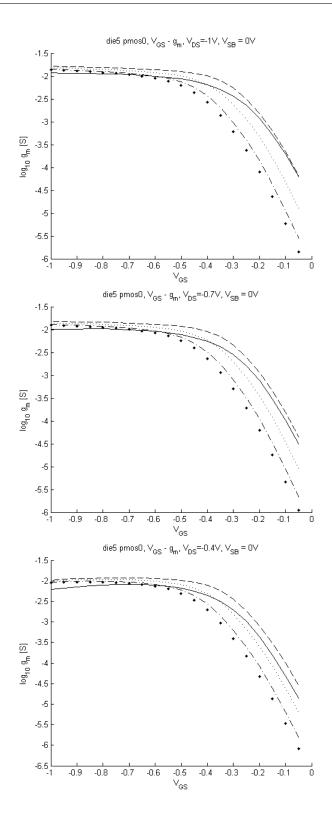

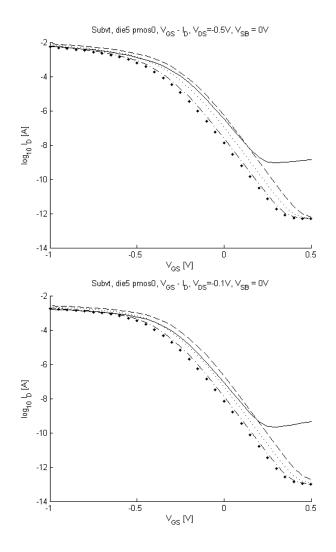

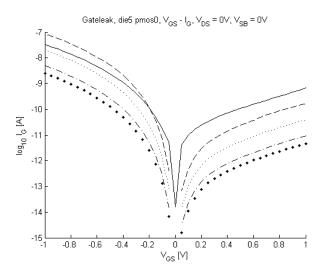

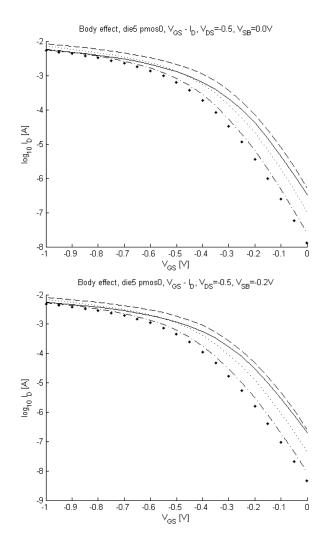

|          | 5.5            | pmos0                                                            | 79   |  |  |  |

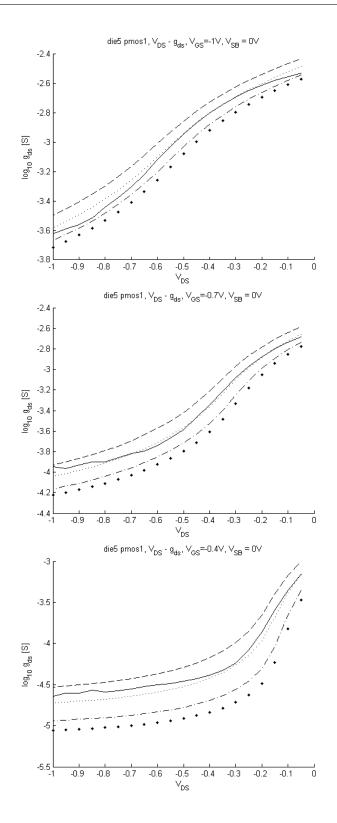

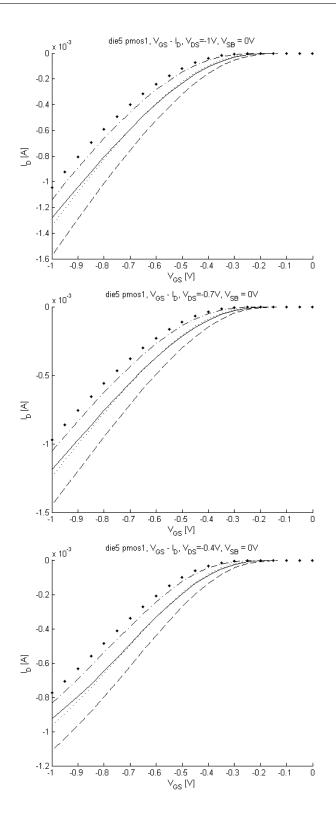

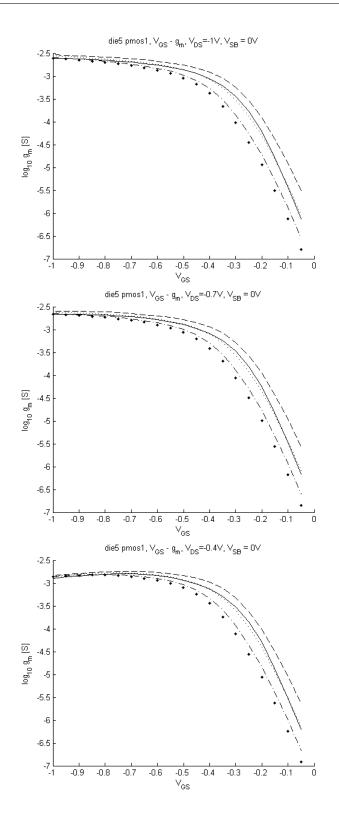

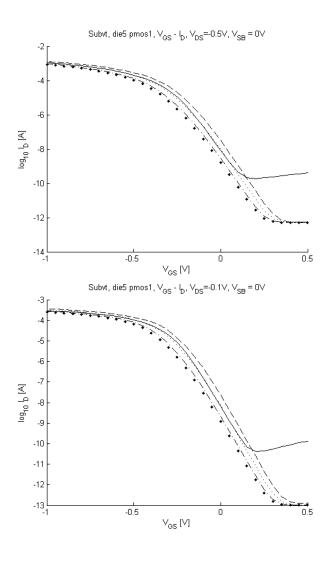

|          | 5.6            | pmos1                                                            | 86   |  |  |  |

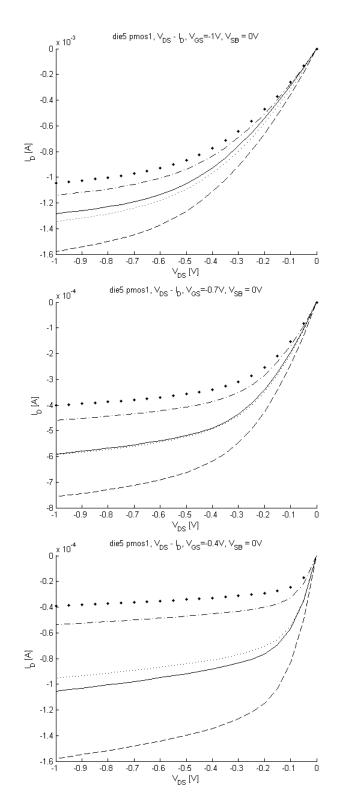

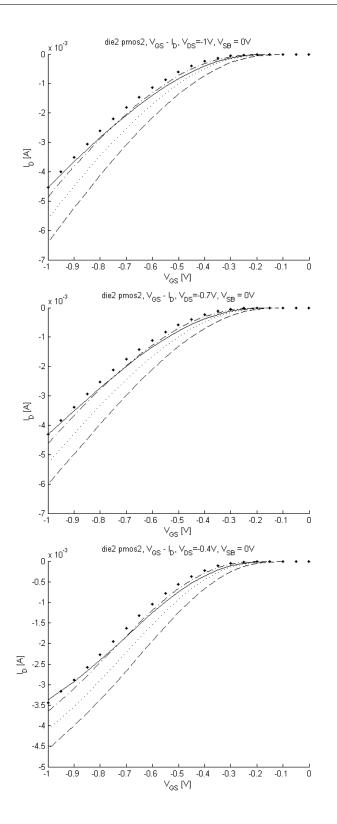

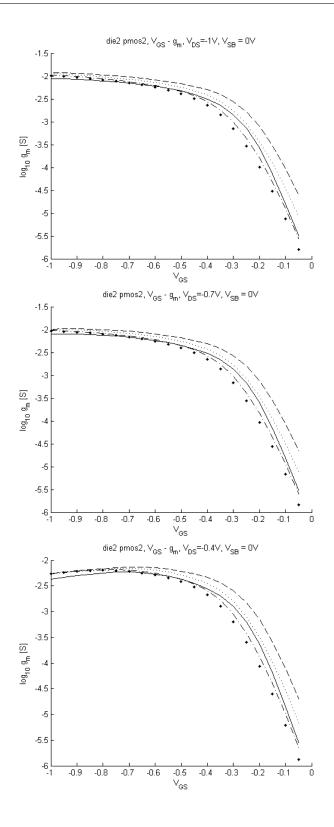

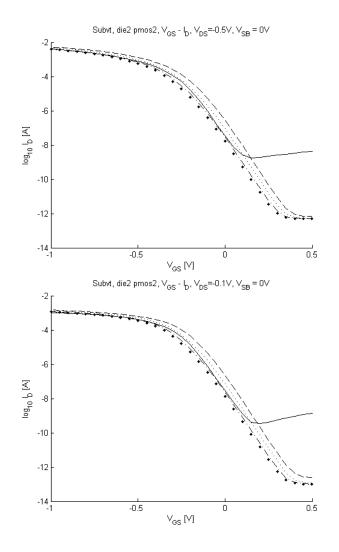

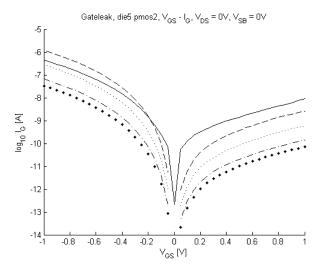

|          | 5.7            | pmos2                                                            | 93   |  |  |  |

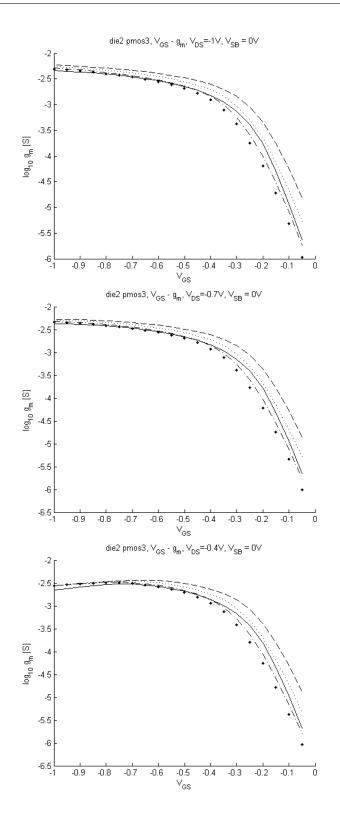

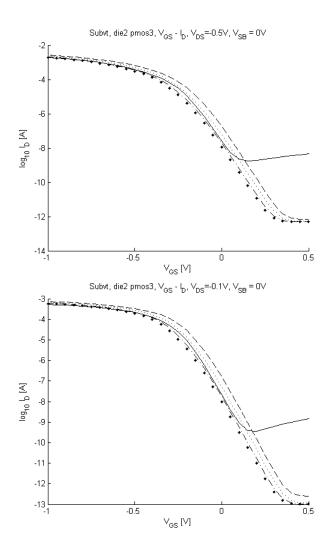

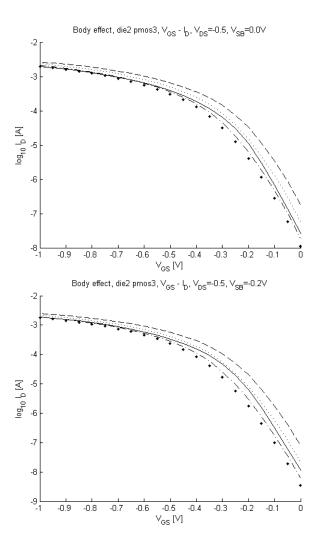

|          | 5.8            | pmos3                                                            | 100  |  |  |  |

| 6        | $\mathbf{Dis}$ | cussion for DC measurements at room temperature 1                | .07  |  |  |  |

|          | 6.1            | Experience gained when accomplishing measurements $\ldots$       | 107  |  |  |  |

|          | 6.2            | Conformity between die1, die2, die4 and die5                     | 108  |  |  |  |

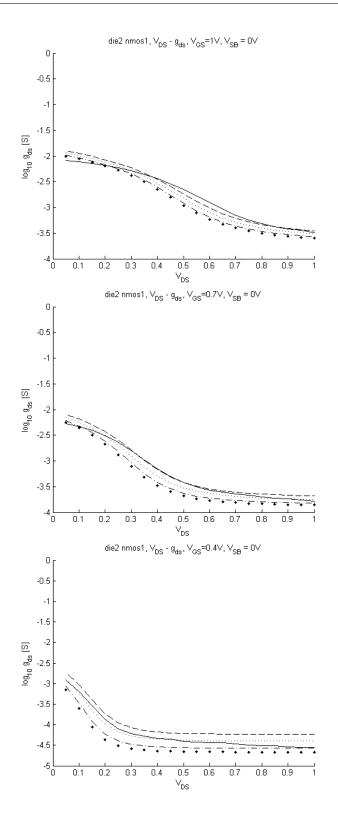

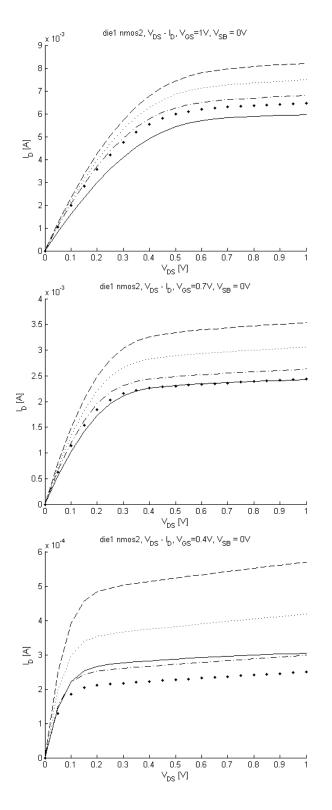

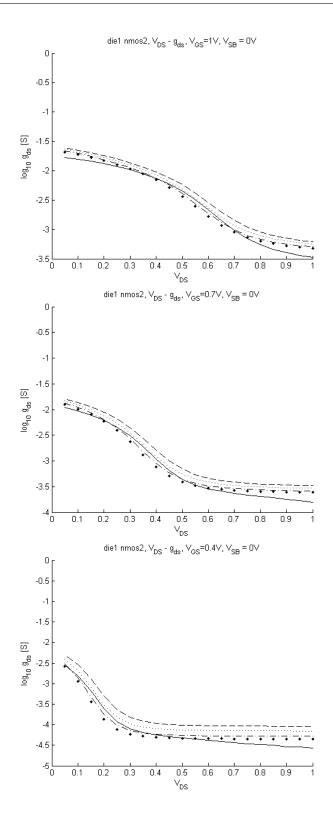

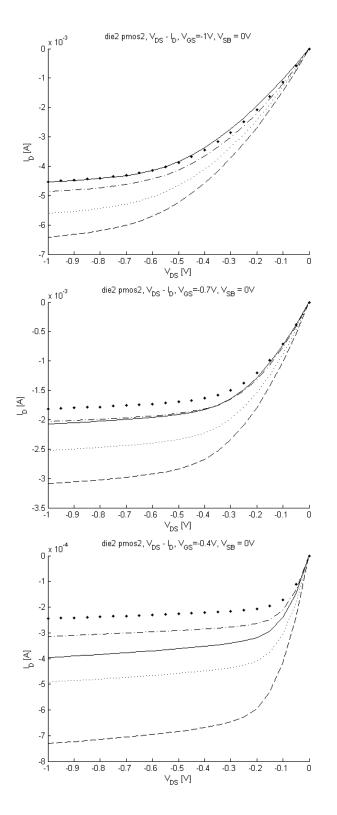

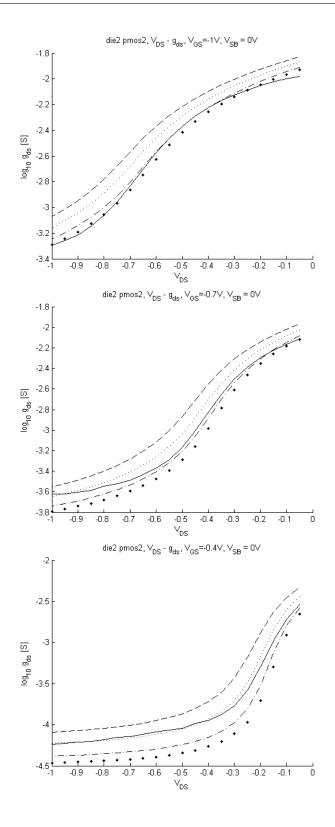

|          | 6.3            | $V_{DS}$ - $I_D$ (IV) characteristic                             | 108  |  |  |  |

|              |                                                                         | 6.3.1                                                               | Channel-length modulation                                                                                                                    | 109 |

|--------------|-------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

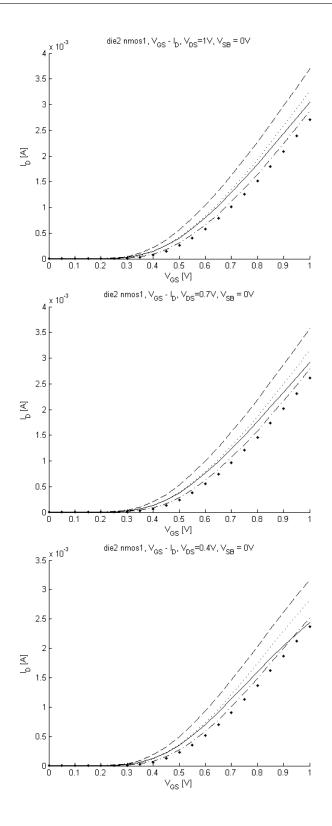

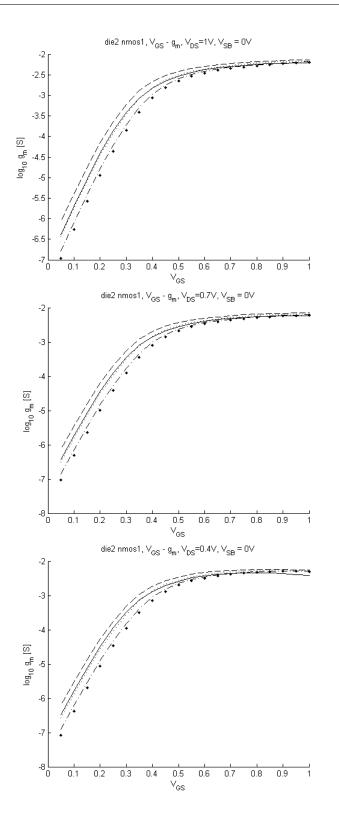

|              | 6.4                                                                     | .4 $V_{GS}$ - $I_D$ (IV) characteristic                             |                                                                                                                                              |     |

|              |                                                                         | 6.4.1                                                               | Threshold voltage $V_{th}$                                                                                                                   | 110 |

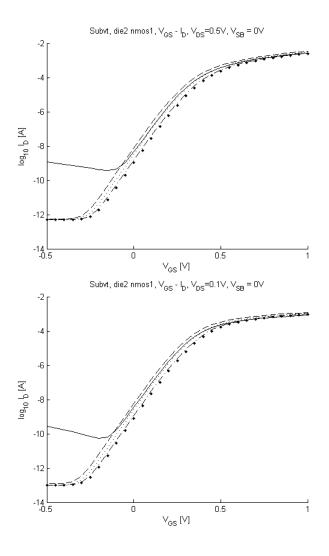

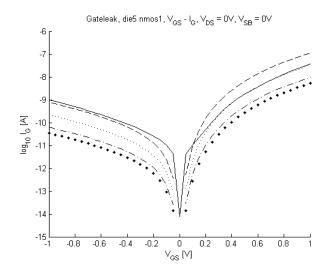

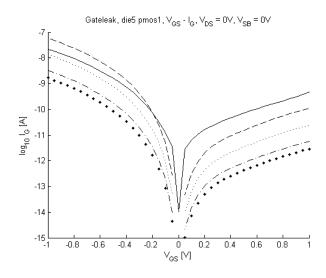

|              | 6.5                                                                     | Subth                                                               | reshold leakage current $I_{sub}$                                                                                                            | 112 |

|              | 6.6                                                                     | Gate leakage-current $I_G - V_{GS}$                                 |                                                                                                                                              |     |

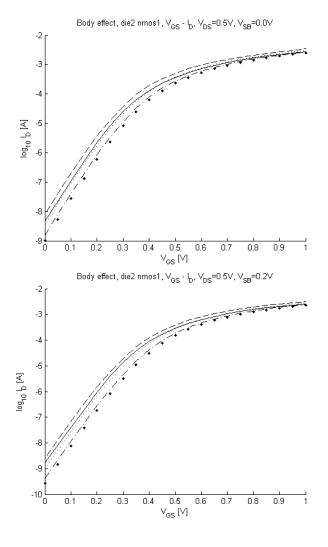

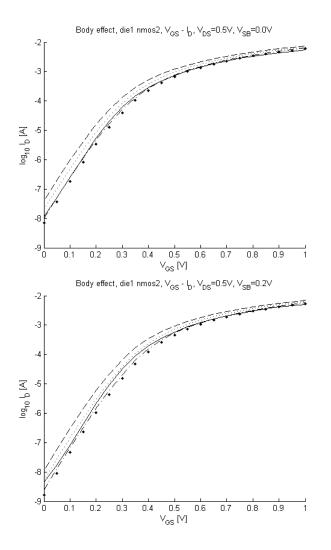

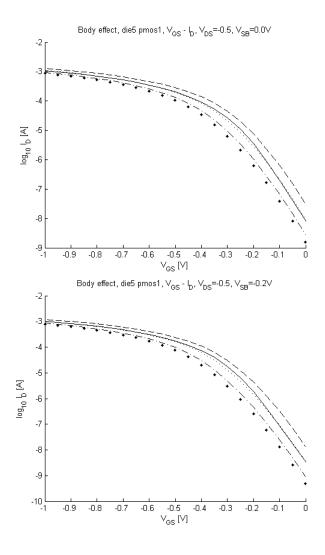

|              | 6.7                                                                     | Influence of body effect                                            |                                                                                                                                              |     |

|              | 6.8                                                                     |                                                                     | e improvements for test-structure layout of 90nm pro-<br>e dies regarding DC measurements                                                    | 114 |

| 7            | Results and discussion for AC measurements at room tem-<br>perature 115 |                                                                     |                                                                                                                                              |     |

|              | 7.1                                                                     | Exper                                                               | ience gained when accomplishing measurements $\ldots$ .                                                                                      | 117 |

|              | 7.2                                                                     | Preser                                                              | ntation of AC measurement results                                                                                                            | 118 |

|              |                                                                         | 7.2.1                                                               | Evaluation of possible CV measurement methods                                                                                                | 118 |

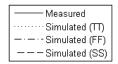

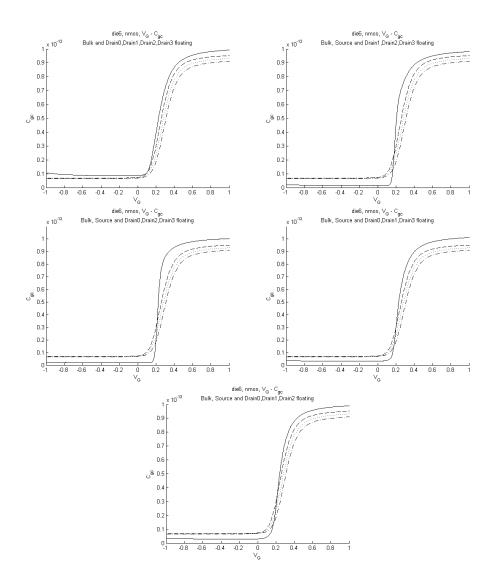

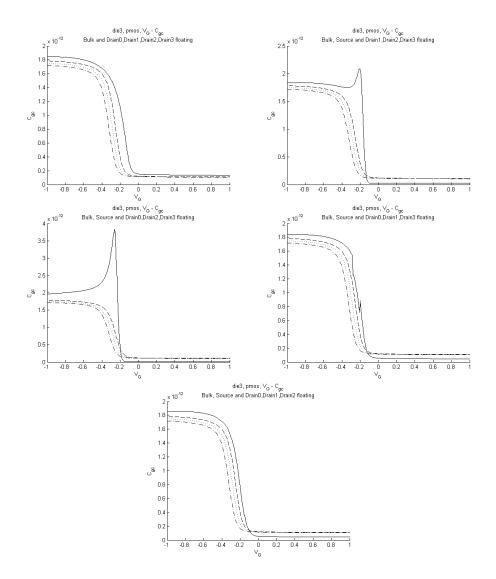

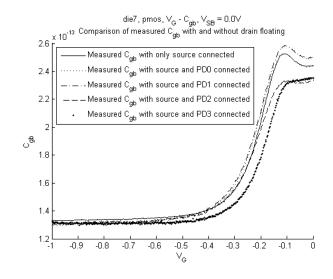

|              |                                                                         | 7.2.2                                                               | Gate-to-bulk capacitance $C_{gb}$ with drain and source floating $\ldots$                                                                    | 119 |

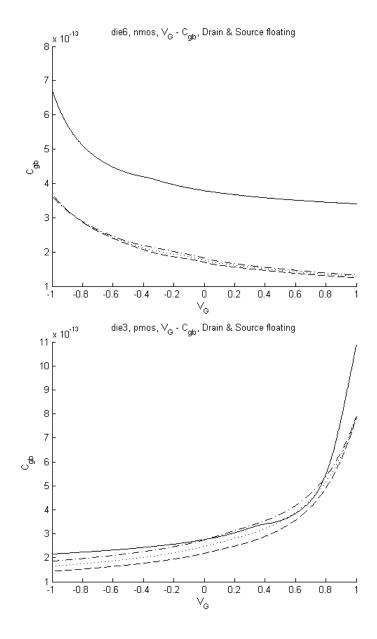

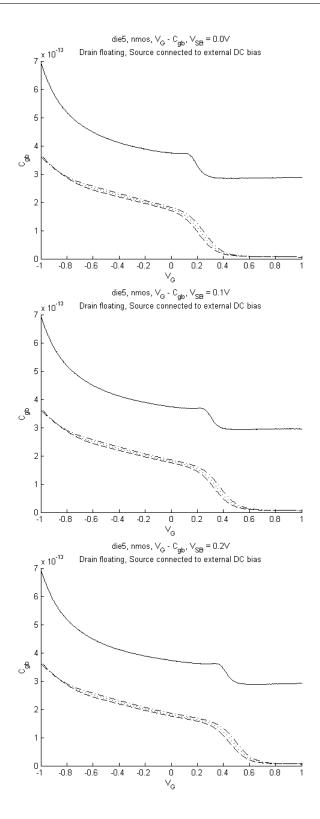

|              |                                                                         | 7.2.3                                                               | Gate-to-bulk capacitance $C_{gb}$ with drain floating and<br>source connected to external DC bias $\ldots \ldots \ldots$                     | 121 |

|              |                                                                         | 7.2.4                                                               | Gate-to-channel capacitance $C_{gc}$ with bulk and either drain or source floating $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 124 |

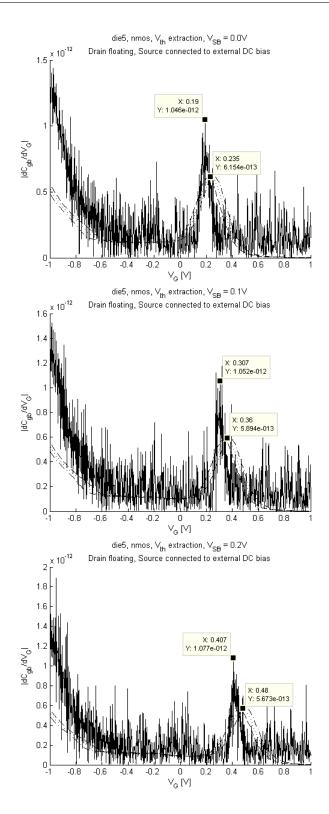

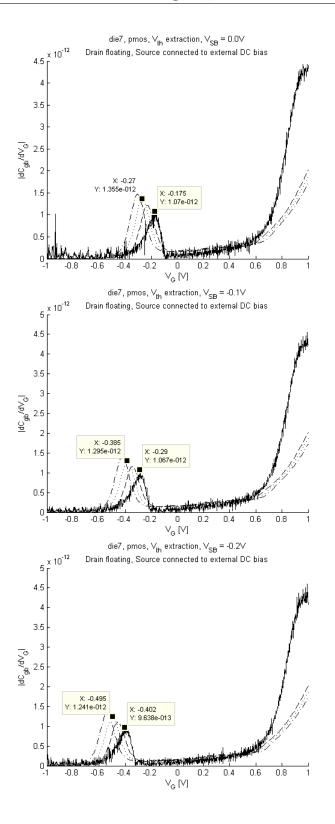

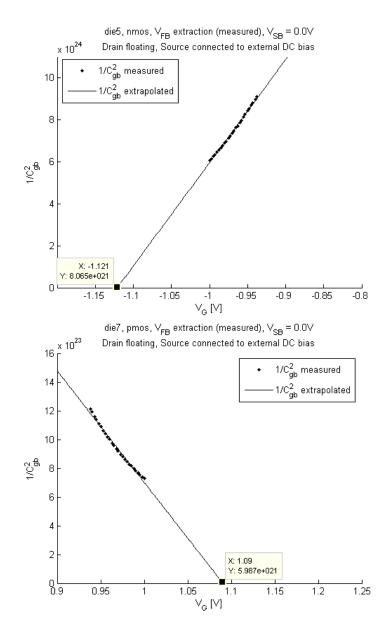

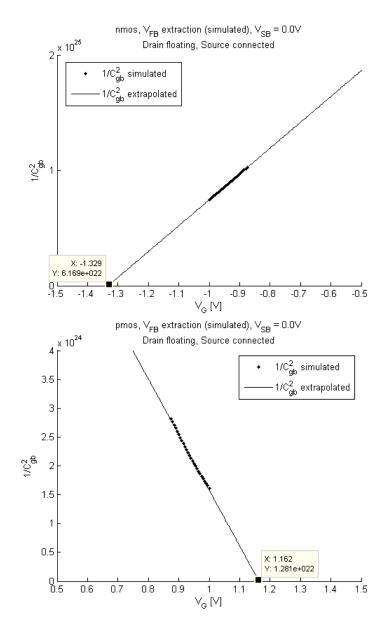

|              | 7.3                                                                     | Extra                                                               | ction of threshold voltage $V_{th}$                                                                                                          | 127 |

|              | 7.4                                                                     | Extraction of flatband voltage $V_{FB}$                             |                                                                                                                                              |     |

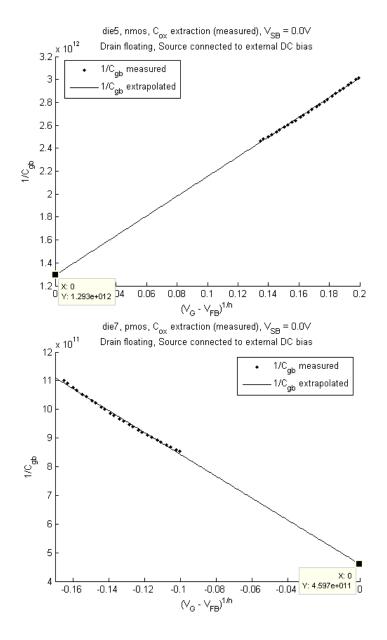

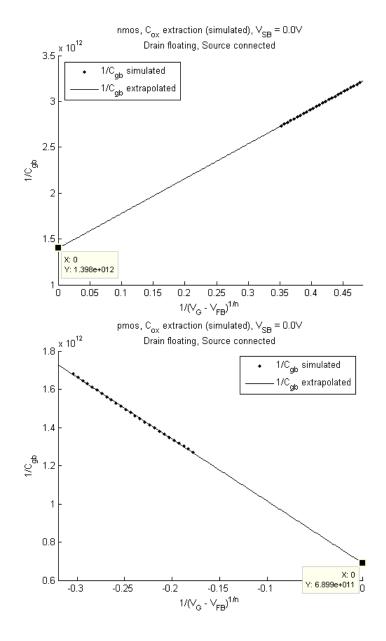

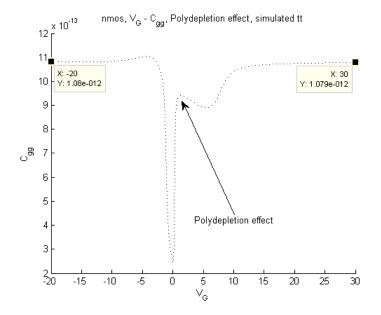

|              | 7.5                                                                     | .5 Extraction of gate capacitance $C_{ox}$ and gate oxide thickness |                                                                                                                                              | 135 |

|              |                                                                         | 7.5.1                                                               | Finding $C_{ox}$ and $t_{ox}$ from accumulation region                                                                                       | 135 |

|              |                                                                         | 7.5.2                                                               | Finding $C_{ox}$ and $t_{ox}$ from inversion region                                                                                          | 139 |

|              | 7.6                                                                     | Influe                                                              | nce of body effect on $V_{th}$                                                                                                               | 141 |

|              | 7.7                                                                     |                                                                     |                                                                                                                                              |     |

|              | 7.8                                                                     |                                                                     | e improvements for test-structure layout of 90nm pro-<br>e dies regarding AC measurements                                                    | 143 |

| 8            | Con                                                                     | clusio                                                              | n                                                                                                                                            | 147 |

| Bi           | bliog                                                                   | graphy                                                              |                                                                                                                                              | 149 |

| $\mathbf{A}$ | A List of equipment                                                     |                                                                     |                                                                                                                                              |     |

| В            | Reference guide for basic CV measurements with the Agi- |                      |                                                        |       |  |  |

|--------------|---------------------------------------------------------|----------------------|--------------------------------------------------------|-------|--|--|

|              | lent                                                    | <b>4294</b> A        | A                                                      | 155   |  |  |

| $\mathbf{C}$ | Elde                                                    | ldo simulation files |                                                        |       |  |  |

|              | C.1                                                     | IV sim               | nulations                                              | . 175 |  |  |

|              |                                                         | C.1.1                | IV simulations for nmos devices                        | . 175 |  |  |

|              |                                                         | C.1.2                | IV simulations for pmos devices                        | . 177 |  |  |

|              | C.2                                                     | mulations            | . 178                                                  |       |  |  |

|              |                                                         | C.2.1                | CV simulations for nmos devices $\ldots \ldots \ldots$ | . 178 |  |  |

|              |                                                         | C.2.2                | CV simulations for pmos devices $\ . \ . \ . \ . \ .$  | . 180 |  |  |

| D            | Con                                                     | tents (              | of electronic attachment                               | 183   |  |  |

### Chapter 1

### **Project introduction**

#### 1.1 Motivation

With the continually decrease in dimensions for the MOSFET, new characteristics come into effect. For this master thesis recently fabricated transistors in a 90nm CMOS process were available for investigation. By investigating the voltage versus current characteristics for the transistors, the impact from this technology downscaling can be investigated. This is achieved through IV measurements. CV measurement is an important method to characterize the semiconductor material ([36, chapter 5-6]). From this numerous key parameters associated with a particular MOSFET process can be investigated. New and more precise measurement equipment for these two methods of IV and CV have become available, opening for a more precise investigation of deep-submicron devices. The results from measurements can finally be used to determine the quality of the models used for simulations.

#### 1.2 Method

First the 90nm CMOS technology is characterized through IV measurements, by using a probe station and additional measurement equipment. Then the semiconductor material is investigated through CV measurements.To verify the results, the same measurements are simulated with the circuit simulator Eldo. The level of the parameters to be measured are typically very small for such deep-submicron devices. This must be taken into account, and requires theoretical input from present literature.

### **1.3** Structure of the report

The report is organized in the following main chapters:

#### • Chapter 2:

Here a theoretical foundation necessary for the master thesis is presented.

• Chapter 3:

Here the specifications for what to be accomplished and devices to be investigated throughout the project are introduced.

• Chapter 4:

Here the test plans and test setup used for simulations and physical measurements are presented.

• Chapter 5:

Here the results for DC measurements and simulations at room temperature are given.

• Chapter 6:

Here an accompanying discussion for DC measurements and simulations results at room temperature is given.

#### • Chapter 7:

Here the results and discussion for AC measurements and simulations at room temperature are given.

• Chapter 8:

Here a conclusion for the project on the basis of results and experience is stated.

### Chapter 2

### Theory

This chapter will present the fundamental theory necessary for this master thesis. First a basic review of semiconductor physics is given. Then the physical structure of the MOSFET will be examined, along with its dependency on applied bias voltage. Further the various parasitic capacitances associated with the MOSFET is explained, initially by reducing the MOS-FET into a basic MOS-C structure. That is, removing the drain and source diffusions. Finally the most important effects from downscaling with respect to the MOSFET phycical geometries are reviewed. This latter topic is important regarding the focus of this master thesis.

Most parts of this chapter have been taken from [18], [22, chapter 1] and [39, chapter 3]. Some sections also list additional references. Note that the concepts *substrate* and *bulk* are used in turns through all sections of this chapter, although they describe mainly the same. In principle the theory reviews the NMOS, that is, a MOSFET built on a p-type bulk semiconductor. But it is applicable to PMOS as well by changing the sign of every voltage and replacing the operator > with the operator < and vice versa.

#### 2.1 Basic semiconductor physics

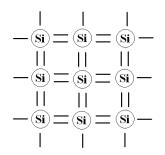

A pure semiconductor is an elemental material that conducts better than an insulator, but worse than a conductor. This characteristic is because of its 4 electrons in the outer shell, the valence shell. By sharing electrons with four other neighbouring semiconductor atoms, a perfect lattice structure is created as shown in figure 2.1. A pure lattice consisting of only semiconductor atoms is called an **intrinsic semiconductor**. Silicon (symbol Si) is one type of semiconductor that is often used in the electronics industry, and will be used to a large extent in the review to follow as well.

Electrons and holes are important when reviewing the theory of semicon-

Figure 2.1: Intrinsic semiconductor lattice, created by silicon atoms.

ductors. The term *hole* is here a concept for the absence of electrons. Holes and electrons have basically the same properties, except from the hole representing positive charge while the electron represents negative charge. In an intrinsic semiconductor lattice there will always exist some free electrons that have gained enough kinetic energy to leave the bonds between the semiconductor atoms that they usually are a part of. Since each free electron is also interpreted as a free hole, the number of electrons and holes are thus equal. Because of this the intrinsic semiconductor lattice has an equal number of electrons and holes at a given temperature, and is thus electrically neutral.

By however doping the semiconductor with other impurity materials, this impurity atom will replace a semiconductor atom in the lattice and enter the bonds with other neighbouring semiconductor atoms. The outer shell of the semiconductor atom thus achieves a number of electrons in its valence band according to the desire of the designer. Thus by introducing contamination, the number of free carriers is altered and hence the conductivity of the semiconductor is controlled. It can be doped to have either an excess of free electrons (n-doping, resulting in an excess of negative carriers) or an excess of free holes (p-doping, resulting in an excess of positive carriers). A doped lattice is called an **extrinsic semiconductor**, being different from the intrinsic semiconductor by having a net profit of carriers.

The interesting aspect of this is the combination of p- and n-type materials. Since the material has an excess of either electrons or holes, it is negatively or positively charged respectively. Placed together, these two opposite charged materials will therefore set up an inherent electrical field. An opposite directed electrical field must therefore be applied to achieve current conduction through the combined material. In this way current flow is possible in one direction only, and not the other. This opens for devices with exclusive properties, such as the MOSFET. The MOSFET is designed to be conducting current by the means of only one type of free carriers (holes or electrons), determined by the combination of materials described above. Materials try to aim for 8 electrons in its outer shell to obtain the structure of a noble gas. This works as the basic rule when designing a p- or n-type material. Two examples are useful to illustrate this process:

Figure 2.2: Silicon lattice doped with donor phosphorus, resulting in excess of negative electron.

First is when silicon is doped with a donor (5 electrons in the outer shell), e.g. phosphorus (symbol P). This results in an excess of about 1 electron per impurity atom. Hence an n-type material is created, as shown in figure 2.2. The concentration of donor doping (atoms/m<sup>3</sup>) is termed  $N_D$ .

Figure 2.3: Silicon lattice doped with donor phosphorus, resulting in excess of positive hole.

Second is when silicon is doped with an acceptor (3 electrons in the outer shell), e.g. boron. This results in an excess of about 1 hole per impurity atom. Hence a p-type material is created, as shown in figure 2.3. The concentration of acceptor doping (atoms/m<sup>3</sup>) is termed  $N_A$ .

Two important processes regarding the free carriers in a semiconductor material are that of *generation* and *recombination*. Electrons within the semiconductor lattice are exposed to an ambient temperature, which in turn can be converted to kinetic energy by the electrons in the bonds. At some point the electron have gained sufficient kinetic energy to abandon the covalent bond and become a free charge carrier, leaving a hole behind. This process is known as generation, while the opposite when the electron enters the bond again is called recombination. These two processes are to a large extent in balance, such that the concentration of free charge carriers  $n_i$  in an intrinsic semiconductor is constant at the specific temperature. On the other hand, in an extrinsic semiconductor this is not true since the carrier concentration has been altered through doping. These type of materials therefore have a much larger concentration of holes relative to electrons or vice versa. These concentrations are called *majority carriers* and *minority carriers*, to distinguish between the carriers created by doping and those created by generation.

#### 2.2 The MOSFET

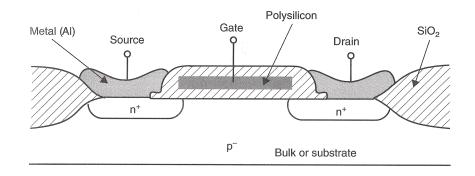

Figure 2.4: Cross-sectional view of NMOS. ([22, figure 1.6]).

The MOSFET is a four-terminal transistor device, based on the above described semiconductor material. The nodes are named *gate*, *drain*, *source* and *bulk*. It is created by diffusions of p- or n-type semiconductors placed into a bulk of n- or p-type semiconductor respectively. A cross-section of an NMOS is shown in figure 2.4. The drain and source regions consist of heavily doped  $n^+$  regions<sup>1</sup>. While the substrate or bulk region consists of a lightly doped  $p^-$  region<sup>2</sup>. It is obvious that the MOSFET may be viewed as a capacitor, consisting of the gate and the bulk as the two electrodes and the gate oxide as the dielectric in between.

There are several process and design parameters which are of importance for the electrical properties of the MOSFET. The channel length L, channel

$<sup>^1\</sup>mathrm{The}$  plus sign indicates that this region has a large number of free negative carriers available

$<sup>^2{\</sup>rm The}$  minus sign indicates that this region only has slightly more free positive carriers than free negative carriers available

width W, doping level in diffusions and bulk, and gate oxide thickness  $t_{ox}$  are some of those. They all affect the functionality of the MOSFET, in accordance with general theory of electronics but also on the basis of theory from processing. This report will investigate the effect of these parameters in terms of the electrical behavior.

A MOSFET may be used both as a switch and as an amplifier. Gate is the controlling node, by setting up the required electrical field to determine the charge concentration at the bulk-to-oxide interface. In this way it determines whether the device is fully on, in intermediate state or off. Since the gate is electrically isolated from bulk, drain and source by the gate oxide, it does in the most simplistic review not conduct any DC current. According to the charge concentration at the bulk-to-oxide interface, current may or may not flow between drain and source. The MOSFET itself is a symmetrical device, where drain and source are defined on basis of the direction of current flow. When the charge concentration is such that current is allowed to flow, the current flow itself is determined by the drain-to-source voltage  $V_{GS}$ . The purpose of the bulk node is to set the source-to-bulk voltage  $V_{SB}$ , and hence set the electrical conditions for the substrate. By setting the bulk to a lower potential than the rest of the device nodes, the initial reverse-bias of the two p-n junctions is increased such that the device is not conducting when it is intended to be on.

It has been seen that the controlling voltage parameters of the MOSFET are the gate, drain and bulk potentials with respect to the source node. This will be examined more detailed further in the upcoming sections 2.2.1, 2.2.2 and 2.2.3 respectively. The following review assumes an NMOS (i.e. p-type semiconductor) with a fixed substrate voltage if not otherwise specified.

#### 2.2.1 MOSFET dependency of gate-source voltage $V_{GS}$

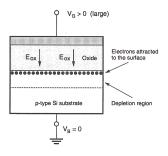

It is of particular interest to investigate the behavior of the MOSFET as a function of the gate bias. The mode of operation as a function of applied  $V_{GS}$  is typically divided into three regions. These regions are called *accumulation*, *depletion* and *inversion*. The transitions are however not abrupt. Only the MOS-C principle will be investigated initially, to particularly show the impact  $V_{GS}$  has on the charge concentration in bulk.

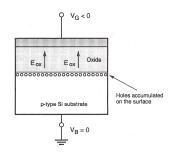

#### Accumulation region (device off)

Within the p-type substrate there is an excess of positive, majority carriers. By applying a negative gate voltage, these positive majority carriers are attracted toward the oxide-to-substrate interface. The holes accumulate, and an *accumulation layer* is thus created. Any free negative minority carriers in

Figure 2.5: p-type MOS-C in accumulation region. ([39, figure 3.5]).

the substrate are on the other hand repelled further away from the junction. Hence the device is OFF, and the resulting electric field in the gate oxide is directed upward against the gate.

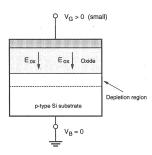

#### Depletion region (device in intermediate state)

Figure 2.6: p-type MOS-C in depletion region. ([39, figure 3.6]).

If a small, positive gate voltage is applied, the situation turns opposite. Now the positive majority carriers are pushed out of the accumulation layer and deeper into the substrate, leaving ions<sup>3</sup> of negative charge fixed in the silicon lattice ([18, chapter 1.2.1]). The gate bias at which the substrate semiconductor eventually reaches neutrality all over is called the *flatband voltage*  $V_{FB}$  ([18, chapter 2.3]). Any increase in gate voltage beyond  $V_{FB}$  causes the silicon lattice region near the bulk-to-oxide interface to become depleted from holes. This stand-off between positive gate voltage and negative ion charge near the bulk-to-oxide interface thus creates a *depletion region*, where

<sup>&</sup>lt;sup>3</sup>Ions are atoms with a net positive or negative charge (i.e. not neutral). If electrons are removed, the atom becomes positively charged. While if electrons are accepted, the atom becomes negatively charged. When holes are pushed into the substrate, this means in practice that the doped silicon atoms in the p-type substrate near the bulk-to-oxide interface accept electrons and hence becomes negatively charged ions.

there are almost no positive majority carriers left. That is, they will balance the charge of each other. This depletion region grows down into the volume of the semiconductor with increasing gate voltage. The resulting electric field in the gate oxide is directed downward against the substrate. At some point the depletion region prevails the gate voltage, and therefore stops increasing in volume. The rest of the p-type substrate is however neutral.

#### Inversion region (device on)

Figure 2.7: p-type MOS-C in inversion region. ([39, figure 3.7]).

If the applied gate voltage is further increased, negative minority carriers from the substrate are attracted toward the bulk-to-oxide interface. These negative minority carriers are a result of the positive majority carriers that were repelled deep into the substrate during depletion, activating the process of generation described in section 2.1 as a response. Since the number of positive majority carriers in the p-type substrate increase due to repulsion from the bulk-to-oxide interface, negative minority carriers must be generated to maintain neutrality. Finally a continuous n-type channel region becomes present at the bulk-to-oxide interface under gate, consisting of negative minority carriers that were just created. The semiconductor material near the bulk-to-oxide interface is said to be *inverted*, since it now has a hole-to-electron concentration similar to that of an n-type material. The device is at present thus in *inversion region*. The depleted area below the channel is still present irrespective of the conducting channel, but it does not increase. Instead, the increase in gate voltage is balanced by the increase in attracted negative minority carriers. The gate voltage at which this channel is created is called the *threshold voltage*  $V_{th}$ . The actual threshold voltage is determined by the doping profile of the substrate. The resulting electric field is still directed downward against the substrate. It is common to divide this region into the two sub-regions weak inversion and strong inversion, which refer to the regions before and after  $V_{th}$  respectively. Hence the threshold voltage indicates the point at which strong inversion is reached.

By adding n-type drain and source diffusions on each side of the MOS-C structure, the charge concentration at the bulk-to-oxide interface described above determines the condition between these two diffusions. When the device is off, the p-type region between the two diffusions acts as a barrier since it is of opposite polarity. But when the channel is present, the charge concentration at the bulk-to-oxide interface is on the other hand of the same polarity as that of the diffusions. Hence there is a direct path between drain and source where current may flow, since these minority carriers are mobile.

CMOS is a concept for technologies embracing both NMOS and PMOS fabricating, where the latter is created by interchanging the  $n^+$  regions with  $p^+$  and  $p^-$  with  $n^-$  in figure 2.4. PMOS is therefore on when the gate voltage is negative, while the NMOS is on when the gate voltage is positive. PMOS thus uses holes as minority carriers to conduct current, while the NMOS uses electrons. The current goes from source to drain for the PMOS, and from drain to source for the NMOS.

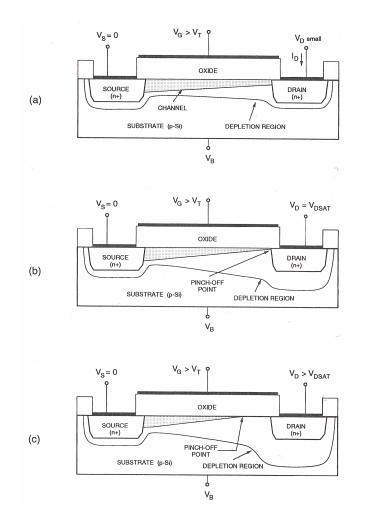

#### 2.2.2 MOSFET dependency of drain-source voltage $V_{DS}$

The MOSFET mode of operation as a function of applied drain voltage is typically divided into the three regions *cut-off*, *linear region* and *saturation region*. The two latter regions are visualized in figure 2.8. This dependency assumes that a conducting channel is already present such that the device is in inversion, as already reviewed in section 2.2.1. The drain bias is essential for establishing the current flow  $I_D$  between drain and source.

#### Cut-off

If  $V_{DS} = 0V$ , then  $I_D = 0A$  ideally. Notice from the discussion about gate bias above, that the drain current will be zero also if a conducting channel is not present.

#### Linear (triode) region ( $(V_{GS} - V_{th}) > V_{DS}$ )

This region becomes present if a small  $V_{DS}$  is applied, as seen in figure 2.8a.  $I_D$  will then be about proportional to  $V_{DS}$ , hence a linear curve characteristic is obtained. By adjusting  $V_{DS}$  within this region, the behavior of a voltagecontrolled resistor is obtained. As  $V_{DS}$  is further increased however, the size of the conducting channel starts to decrease at the drain end. At the socalled *pinch-off* voltage (figure 2.8b) the conducting channel reaches only just to about the drain diffusion. Drain current now starts to saturate, because only a depleted version of the original channel is left on the oxideto-substrate interface near drain.

Figure 2.8: MOSFET modes of operation with variable drain potential: a) linear, b) pinch-off and c) saturation ([39, figure 3.14]).

Since the MOSFET characteristics in linear region resemble that of a voltagecontrolled resistor, the output resistance of the MOSFET is a very interesting parameter for this specific region. This is modeled by the **transistor drain-to-source resistance**,  $r_{ds}$ , or the drain-to-source conductance  $g_{ds}$ which is the inverse of  $r_{ds}$ .  $g_{ds}$  is ideally infinite when the MOSFET is in cut-off.

#### Saturation (active) region $((V_{GS} - V_{th}) < V_{DS})$

As  $V_{DS}$  is further increased after pinch-off, the depleted channel gradually replaces the original channel and so the pinch-off point moves closer and closer toward the source diffusion. As a result the drain current becomes more and more saturated because of the decrease in effective channel length (figure 2.8c). As a result the velocity of the minority carriers saturates, and the  $V_{DS} - I_D$  curve characteristic flattens. A common exception from this characteristic comes as a consequence from *channel-length modulation*, which arise for short channel devices. That is, since the effective length of the channel is reduced with increasing  $V_{DS}$ , the effective  $r_{ds}$  is also reduced. This effect results in a small proportional increase in  $I_D$  even in this region. Channel-length modulation is expressed by the parameter  $\lambda$ , where  $\lambda = 0$ indicates that the slope is zero in saturation region.

The characteristics of the MOSFET in saturation region is very similar to that of a voltage-in-current-out amplifier, commonly named a *transconduc*tor. Because of this the transconductance gain of the MOSFET is a very interesting parameter for this specific region. This is modeled by the **transistor transconductance**,  $g_m$ .

## 2.2.3 MOSFET dependency of source-bulk voltage $V_{SB}$ (the body effect)

Usually both source and bulk are connected to a common voltage level, which was a prerequisite for the previous review. A different bulk voltage bias compared to the source potential however gives rise to *body effect*. This may implemented due to design issues, or unintentionally. For NMOS this body effect occurs for positive  $V_{SB}$ , while for PMOS it occurs for negative  $V_{SB}$ . The body effect increases the effective threshold voltage  $V_{th}$ , since the potential that the gate voltage must overcome is increased. As a result it also reduces the drain current capabilities of the device. That is, the maximum achievable drain current is reduced.

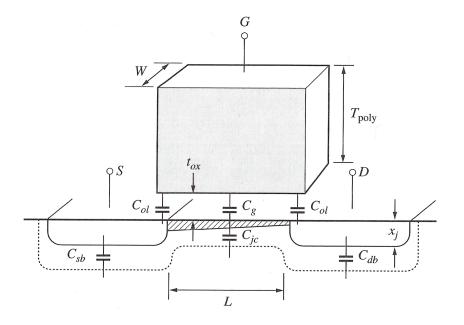

Figure 2.9: MOSFET capacitances ([31, figure 2.17)]).

#### 2.3 MOSFET parasitic capacitances

The parasitic capacitances of the MOSFET make up an important part of the total parasitic capacitance of a specific design in addition to the interconnect delays. Rise- and fall-times are determined by the necessary time to charge and discharge the internal circuit capacitances, in general determined by the time constant  $\tau = R \cdot C$ . The analysis of MOSFET capacitances is therefore very interesting regarding the speed and power consumption of a circuit.

Analysis of MOSFET parasitic capacitances is also an often-used method for characterizing a specific MOSFET technology. This is done by measuring the MOSFET equivalent capacitance, and from this vital information can be extracted. Among the MOSFET device and process parameters which can be found from CV measurements are gate oxide thickness  $t_{ox}$  and threshold voltage  $V_{th}$ . A more supplementary list can be found in [18, chapter 1.3.3].

Most parts of this section have been taken from [21], [22, chapter 1.2], [23, chapter 5.10], [28, chapters 20 and 22], [31, chapter 2.8], [32, chapter 9.3] and [39, chapter 3.6]. It will focus on MOSFET-related capacitances and not interconnect capacitances, since the latter is not the focus of this master thesis. It is however interesting to notice that interconnect capacitances begin to dominate MOSFET capacitances as the technology is scaled down toward deep-submicron ([39, chapter 6.5]).

The theory of MOSFET parasitic capacitances is in many ways based upon the general theory about parallel-plate capacitors. Any basic study of this latter topic will not be given, as this is assumed known by the reader. Going directly to the analysis of the MOSFET-specific capacitances is found more appropriate instead.

Capacitances associated with the MOSFET is typically classified into two major groups: *oxide-related capacitances* and *junction capacitances*. The former comes as a consequence of the gate oxide acting as a dielectric between various electrodes of the MOSFET, and will be discussed in section 2.3.2. While the latter is a result of the depletion region formed between the p-n junctions within the semiconductor material, acting as a dielectric between the diffusions and bulk. Junction capacitances will not be studied as part of this master thesis.

First an evaluation of the capacitance associated with the basic two-terminal MOS-C will be given. This device constitute a very important part of the four-terminal MOSFET, and is therefore of interest to create a basic understanding of the MOSFET capacitances.

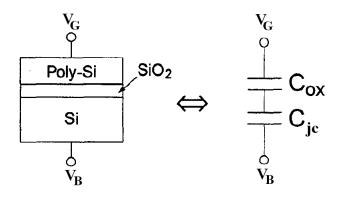

#### 2.3.1 The MOS capacitor (MOS-C)

Figure 2.10: Equivalent circuit for the capacitances represented by the MOS-C ([8, figure 2]).

A simplistic drawing of a silicon-based MOS-C is shown in figure 2.10. It consists of doped silicon as the substrate, a gate electrode made of polycrystalline silicon<sup>4</sup>, and silicon dioxide (symbol SiO<sub>2</sub>) to separate gate from the substrate. The MOS-C actually consists of two different capacitors. These are the gate capacitance per unit area  $C_{ox}$  and the channel junction capacitance  $C_{jc}$ . The dielectric of  $C_{ox}$  is the always existing gate oxide, while the dielectric of  $C_{jc}$  is the depleted region created in the semiconductor during

<sup>&</sup>lt;sup>4</sup>Polysilicon is non-crystalline silicon with a high level of doping ([22, page 17])

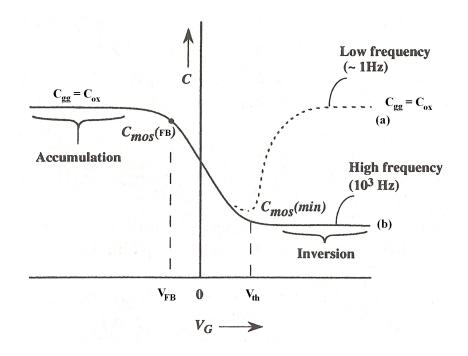

Figure 2.11: Ideal CV curve for p-type unit sized MOS-C structure, at: a) low AC test signal frequency and b) high AC test signal frequency ([32, figure 9.7a]).

depletion. The presence or non-presence of  $C_{jc}$  is hence determined by the mode of operation as will be seen, while  $C_{ox}$  is constant at all time.

By assuming a unit sized MOS-C,  $C_{ox}$  is shared between various electrodes according to the mode of operation for the MOS-C. For the review to come it is appropriate to introduce the total gate capacitance  $C_{gg}$ . It is also appropriate to introduce the gate-to-bulk capacitance  $C_{gb}$  seen between the two external electrodes  $V_G$  and  $V_B$ .

An ideal CV plot showing the total gate capacitance  $C_{qq}$  of a unit sized MOS-C under external bias is shown in figure 2.11. The three regions accumulation, depletion and inversion discussed in section 2.2.1 are clearly reflected in this plot. In accumulation region the number of positive majority carriers accumulated at the bulk-to-oxide interface is large, hence  $C_{gg}$  is on its maximum and equal to  $C_{ox}$ . With increasing gate bias in depletion region, the positive majority carriers are pushed away from the bulk-tooxide interface and the depleted area under gate expands. In this region of operation  $C_{gg}$  is therefore reduced, since the number of positive majority carriers at the bulk-to-oxide interface is only decreasing. At  $V_{th}$ ,  $C_{gg}$  reaches a minimum value. This is a result of the gate and bulk semiconductor being separated by the conducting channel. At the same time  $C_{ic}$  becomes present, created by the external node  $V_B$  and the conducting channel as the electrodes with the depleted region in the middle acting as a dielectric. Up until now  $C_{gb}$  has been equal to  $C_{gg}$ . But since the path between oxide and bulk from now on is intercepted by the channel,  $C_{gb}$  will no longer follow  $C_{qq}$ . When  $V_G$  is further increased beyond this point and into inversion, the negative minority carriers created in bulk by thermal generation are attracted towards the gate. In this region of operation the total gate capacitance  $C_{gg}$  is increasing once again, due to the increasing number of negative minority carriers at the bulk-to-oxide interface. Finally  $C_{aq}$  returns back to its maximum value  $C_{ox}$  once again, provided that the signal frequency is low enough.

It was seen that  $C_{gb}$  was intercepted by the channel when entering inversion. Hence it is appropriate to introduce the gate-to-channel capacitance  $C_{gc}$ , where the channel has replaced the electrode functionality of bulk. As  $C_{gb}$  was following  $C_{gg}$  in accumulation and depletion,  $C_{gc}$  follows  $C_{gg}$  in inversion.

In addition to the dependency of DC level on applied voltage, the MOS-C is also dependent on the signal frequency of the applied voltage. This dependency exists only in the inversion region. Inversion region is based on the supply of negative minority carriers generated in bulk as a response to the repulsion of holes. The flow of minority carriers through the substrate occurs in two directions: First is the attraction of minority carriers towards the bulk-to-oxide in inversion, while second is the repulsion of minority carriers back towards deep bulk in accumulation. The former is achieved by means of *drift*, while the latter is achieved by *diffusion*. It has been seen that the actual direction of flow is controlled by the gate voltage. The generation and recombination of these minority carriers require a finite period of time. If these negative minority carriers are not generated or recombine fast enough according to the change in gate signal voltage, the resulting capacitance will not increase again in inversion (see equation 2.9 later in this chapter). The time required for generation is larger than that required for recombination.

Plots for the n-type MOS-C are in principle exactly the same as that for the p-type MOS-C. The major difference is that the p-type uses holes as minority carriers, while the n-type uses electrons as minority carriers. Therefore the n-type MOS-C will have an accumulation region at positive gate biases, while this is opposite for the p-type MOS-C.

#### 2.3.2 Oxide-related capacitances

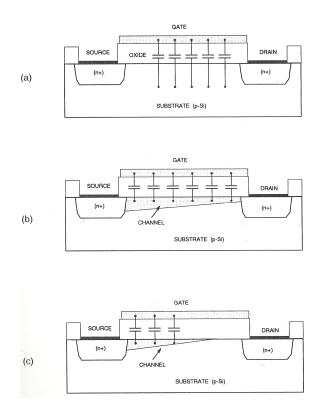

Figure 2.12: MOSFET oxide-related capacitances, dependent on shape of conducting channel according to applied bias voltage. a) cut-off b) linear c) saturation ([39, figure 3.29]).

The MOSFET oxide-related capacitances arise mainly due to a decomposition of the MOS-C total gate capacitance  $C_{gg}$  discussed in section 2.3.1, along with some fixed overlap capacitances. The value of the various decompositions depends on the region of operation for the MOSFET, as will be discussed further with reference to figure 2.12.

There are, in the most simplistic review, three locations where electrodes are overlapping each other with a non-conducting dielectric in the middle as seen in figure 2.9. The first one of these is the gate overlapping the bulk, to achieve the fundamental operation of the MOSFET as explained in section 2.2. Second and third are the gate overlapping the drain and source diffusions, respectively. These two overlaps  $L_{ov}$  are necessary to guarantee the creation of a continuous channel between the drain and source diffusions. The oxide-related parasitic capacitances associated with the MOS transistor so far thus become the gate-to-bulk  $C_{gb}$ , gate-to-drain  $C_{gd}$  and gate-to-source  $C_{qs}$  capacitance. The gate oxide in the middle acts as the dielectric.

When the MOSFET is in accumulation (equals cut-off region seen in figure 2.12a), there is no conducting channel between source and drain.  $C_{gd}$  and  $C_{gs}$  are therefore only given by the overlap  $L_{ov}$  between gate and each of the drain and source diffusions. Each of these two overlap capacitances are termed  $C_{ol}$  in figure 2.9, and are determined by the overlap area and  $C_{ox}$ .  $C_{gb}$  is however on its maximum, since there is a direct path between the bulk connection and the oxide interface.

When a conducting channel becomes present in inversion, a new situation occurs for the three oxide-related capacitances. As reviewed in section 2.3.1 the channel replaces the electrode functionality of the bulk seen by the gate, and thus effectively shields bulk from gate. Hence  $C_{ab}$  becomes zero, after gradually dropping in depletion region due to the change in carrier concentration at the bulk-to-oxide interface. On the other hand, the effective overlap area of gate to both source and drain is increased due to the conducting channel. Hence  $C_{gd}$  and  $C_{gs}$  is increased, which in sum constitute  $C_{gc}$  seen earlier and also the overlap capacitance. Two observations are thus made. First is that  $C_{qb}$  consists of a voltage-dependent capacitance component only. While second is that  $C_{gd}$  and  $C_{gs}$  consist of both a voltage-dependent capacitance component determined by the shape of the conducting channel, and a voltage-independent capacitance component determined by the fixed gate-to-diffusion overlap area. When the channel extends across the MOS-FET in linear region (figure 2.12b), the total mobile charge in the conducting channel is shared between drain and source. Hence the gate-to-channel capacitance seen by each of the drain and source nodes is given by approximately half of the total mobile charge, such that the total gate-to-channel capacitance is simply split equally between drain and source. But when saturation region is entered (figure 2.12c), drain is pinched off. Hence the

gate-to-channel capacitance seen by drain is negligible, while the effective gate-to-channel capacitance seen by source is further increased. [39, chapter 3.6] approximates  $C_{gs}$  to be of around  $\frac{2}{3} \cdot C_{gg}$  in this region, in addition to the two voltage-independent overlap capacitances  $C_{ol}$ .

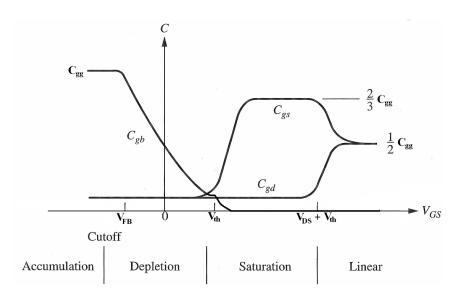

Figure 2.13: Plot of oxide-related capacitances for NMOS ([31, figure 2.18)]).

A plot showing the oxide-related capacitances for an NMOS is given in figure 2.13. It was in the introduction to this section stated that the oxide-related capacitances  $C_{gb}$ ,  $C_{gd}$  and  $C_{gs}$  comprised the total MOS capacitance  $C_{gg}$  from section 2.3.1. Hence by summing these three decompositions,  $C_{gg}$  is approximately achieved. From figure 2.13 it is seen how  $C_{gb}$  is almost equal to the total MOS capacitance  $C_{gg}$  when the device is in cut-off. Further is is shown that  $C_{gb}$  drops to zero when the device enters inversion, while  $C_{gd}$  and  $C_{gs}$  share  $C_{gc}$  according to the shape of the channel.

The frequency dependency is present for the oxide-related capacitances as well, but in a rather different way than that for the basic MOS-C. Since the structure consists of drain and source diffusions in addition to the MOS-C itself, the rate of generation of minority carriers in inversion is not so crucial. Instead the device has a quick supply of these carriers from drain or source, according to whether it is an NMOS or PMOS. Hence the upper frequency of operation for the MOSFET is limited by the cut-off frequency of the MOSFET itself rather than the rate of generation and recombination. Since this cut-off frequency usually is in the GHz area, it will not represent any challenge. However, CV measurement of thin-oxide devices will dictate requirements for the signal frequency as will be seen.

#### 2.4 Effects on the MOSFET from downscaling in CMOS process technology

There are two important aspects from downscaling in the technology geometries which are interesting specifically for this master thesis. Most parts of this section have been found in [16] and [25].

- With decreasing dimensions the parasitic capacitances associated with the MOSFET also decrease.

- As the processing technology is scaled down, the leakage currents increase.

#### 2.4.1 Decrease in MOSFET parasitic capacitances

Parasitic capacitances associated with the MOSFET decreases with decreasing dimensions of the MOSFET. The first reason for this is the reduction in area, seen from equation 2.11 in the forthcoming section 2.5. Besides, the thickness  $t_{ox}$  of the gate oxide is scaled according to the overall technology scaling, which decreases the gate capacitance per unit area as seen from equation 2.12 in section 2.5. As an example the voltage-independent gate-to-source overlap capacitance  $C_{gs_{ov}}$  can be studied, given as

$$C_{gs_{ov}} = W \cdot L_{ov} \cdot C_{ox} \tag{2.1}$$

where W is the gate width,  $L_{ov}$  is the length of overlap between gate and source, and  $C_{ox}$  is the gate capacitance per unit area. It is clear from the formula that when the dimensions and  $C_{ox}$  are decreasing, the capacitance will also decrease.

An advantage with this decrease is reduced capacitive load in the circuits, and hence reduction in charging time and power consumption. A challenge is however that this reduction in capacitance sets stronger demands to instrumentation, test setup and accomplishment of the measurements to be able to measure the small quantities.

#### 2.4.2 Increase in leakage currents

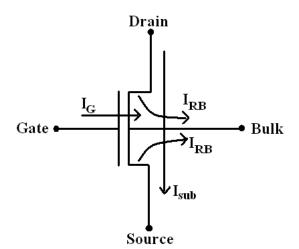

According to [25, section II], there are three main sources for leakage current in MOSFETs:

1. Reverse-bias leakage  $I_{RB}$  in the p-n junctions when the device is reversebiased.

- Figure 2.14: Leakage sources associated with MOSFETs, here represented by an NMOS ([25, figure 3]).

- 2. Subthreshold leakage current  $I_{sub}$  between drain and source when the device is reverse-biased, i.e. intended to be off.

- 3. Gate leakage current  $I_G$  between gate and bulk

The focus when investigating older technologies has traditionally been on the two former sources, while the latter is especially of interest regarding deep-submicron technologies. However, both source number 2 and 3 are within the scope of this master thesis.

The subthreshold leakage current  $I_{sub}$  refers to the current flowing between drain and source before  $V_{th}$  is reached.  $I_{sub}$  is caused by minority carriers flowing between drain and source already before a conducting channel is present. Hence there is a small current flow already before  $V_{GS}$  has reached the inherent  $V_{th}$  of the device. This leakage is further enhanced by the effect called DIBL<sup>5</sup>. With increasing  $V_{DS}$  towards inversion, substrate region at the bulk-to-oxide interface becomes partly depleted although the device is intented to be off. This makes it possible for electrons to flow. As a result, the effective  $V_{th}$  decreases and  $I_{sub}$  increases. This effect strengthens with decreasing process geometries, since the distance between drain and source typically decreases accordingly. With decreasing distance some electrons actually may become able to travel directly between the drain and source diffusions. This is called *punchthrough*, and creates a permanent on-state for the device which is not wanted.

<sup>&</sup>lt;sup>5</sup>Drain-Induced Barrier Lowering

As the process geometry is reduced, the oxide thickness  $t_{ox}$  is reduced accordingly. This decrease in oxide thickness consequently brings along an increase in gate leakage  $I_G$  between gate and bulk. Gate leakage current is caused by impurities in the dielectric material, making it possible for some electrons to move through the dielectric. This is sometimes referred to a the tunneling effect ([18, chapter 5.10]). When  $t_{ox}$  becomes thinner, the percentage share of impurities in the oxide becomes larger. In this way the gate leakage increases with decreasing gate oxide thickness. For deep-submicron technologies  $I_G$  is becoming equal to and even larger than  $I_{sub}$ . According to [25, section II],  $I_G$  is actually more than two times that of  $I_{sub}$  for some present technologies.

This static leakage current consisting of  $I_G$  and  $I_{sub}$  may be small for a single device, but for a complete design the leakage accumulates and hence becomes a challenge regarding power consumption. One of the advantages with traditional CMOS technologies used in digital design was that power consumption was mainly dynamic, that is, power was consumed only during charging and discharging of the MOSFET parasitic capacitances during switching. With the ever increasing gate leakage however, the effect of static power consumption must be taken into account as well. And where dynamic power consumption is dependent on switching activity, the static power consumption is rather dependent on what mode of operation the device is in, the total number of transistors and what type of transistors the design consists of. This overall increase in power consumption leads to an increase in circuit temperature, and also a decrease in battery lifetime when batteries are used. The former could further increase the possibility of circuit failure, and would set higher demands to additional cooling systems. New circuit techniques for dealing with and reducing these high leakage currents is also necessary (see [25, sections III, IV and V] for an overview), but this is beyond the scope of this master thesis.

CV measurements involving MOSFET oxide-related capacitances become more complicated with increasing gate leakage. This is because more and more of the AC test signal current will flow directly through the oxide. New methods is therefore necessary to make possible measurements on thin-oxide technologies.

## 2.5 Mathematical foundation

## 2.5.1 MOSFET first-hand model equations

The following equations are taken from [22, chapter 1.5] unless otherwise specified, and describe the behavior of the n-channel MOSFET in the various regions of operation. The equations are intended for first-hand modeling, and are thus not suitable for use in the transition between two different regions.

#### Effective gate voltage

$$V_{eff} = V_{GS} - V_{tn} \qquad [V] \tag{2.2}$$

#### Threshold voltage

The effective threshold voltage  $V_{th}$  of the technology, when taking the substrate bias (body effect,  $V_{SB}$ ) into account, is given as ([22, equation 1.73])

$$V_{tn}(V_{SB}) = V_{tn0} + \gamma \cdot \left(\sqrt{V_{SB} + |2\phi_F|} - \sqrt{|2\phi_F|}\right)$$

[V] (2.3)

$V_{tn0}$  = threshold voltage specifically at  $V_{SB} = 0$  [V]  $\gamma$  = body-effect coefficient  $[V^{1/2}]$   $\phi_F$  = Fermi potential [V] (not specified any further, but set to -0.35V for NMOS and 0.35 for PMOS according to [22, page 70])

## **MOSFET** in cut-off

The drain current is ideally given by

$$I_D = 0 \qquad [A] \tag{2.4}$$

In reality there will flow a small drain current in this subthreshold region as well, according to section 2.4.

#### MOSFET in linear (triode) region

The drain current in saturation region is given by ([22, equation 1.65])

$$I_D = \mu_n C_{ox} \left(\frac{W}{L}\right) \left[ (V_{GS} - V_{tn}) V_{DS} - \frac{V_{DS}^2}{2} \right] \qquad [A]$$

where the last fraction  $\frac{V_{DS}^2}{2}$  is usually ignored for the purely linear region.

Further the definition for the MOSFET drain-source conductance  $g_{ds}$  in linear region is given as ([22, equation 1.89])

$$g_{ds} \equiv \frac{\partial I_D}{\partial V_{DS}} \bigg|_{V_{GS}=const.} \qquad [A/V] \tag{2.6}$$

#### **MOSFET** in saturation (active) region

The drain current in saturation region is given by ([22, equation 1.71])

$$I_D = \frac{\mu_n C_{ox}}{2} \left(\frac{W}{L}\right) (V_{GS} - V_{tn})^2 \left[1 + \lambda (V_{DS} - V_{eff})\right] \qquad [A]$$

(2.7)

where the last term  $[1 + \gamma (V_{DS} - V_{eff})]$  models the channel-length modulation, and can usually be omitted for first-hand calculations.

$\lambda$  = channel-length modulation parameter [1/V]

Further the definition for the MOSFET transistor transconductance  $g_m$  in saturation region is given as ([22, equation 1.75])

$$g_m \equiv \frac{\partial I_D}{\partial V_{GS}} \bigg|_{V_{DS}=const.} \qquad [A/V] \tag{2.8}$$

#### 2.5.2 Definition of capacitance

The capacitance is a measure of how much electrical charge a capacitor is capable of storing, and is defined as ([6, equation 8.1])

$$C \equiv \frac{Q}{V} \qquad [F] \tag{2.9}$$

Q = charge [C]

V =potential of the body of the capacitor [V]

The intrinsic capacitance over terminals x and y of a MOSFET will be written as

$$C_{xy} = \frac{\partial Q_x}{\partial V_{xy}} \bigg|_{V_{other} = const.}$$

[F] (2.10)

Capacitances associated with MOSFETs are in many ways similar to the shape of a parallel-plate capacitor. This is possible by viewing only smaller sections of the overall MOSFET capacitance. The capacitance for a parallelplate capacitor may be expressed as ([6, equation 8.8])

$$C = \epsilon \frac{A}{d} \qquad [F] \tag{2.11}$$

$A = \text{area of plate electrodes } [m^2]$

d = distance between plate electrodes [m]

$\epsilon$  = permittivity for the dielectric between the electrodes [F/m])

### 2.5.3 MOSFET gate capacitance

$C_{ox}$  represents the gate capacitance per unit area for a MOSFET transistor, and is given by ([22, equation 1.56])

$$C_{ox} = \frac{\epsilon_{ox}}{t_{ox}} = \frac{K_{ox} \cdot \epsilon_0}{t_{ox}} \qquad [F/m^2]$$

(2.12)

$\epsilon_{ox} = \text{permittivity of gate oxide } SiO_2 [F/m]$

$K_{ox}$  = relative permittivity of gate oxide  $SiO_2$  (approximately 3.9 [dimensionless])

$\epsilon_0 = \text{permittivity of vacuum } (8.854 \cdot 10^{-12} \text{ [F/m]})$

$t_{ox}$  = thickness of gate oxide [m] (process dependent)

## 2.5.4 Summary of MOSFET oxide-related parasitic capacitances

Table 2.1 summarizes the oxide-related MOSFET capacitances resulting from the discussion in section 2.3.2.

| Capacitance | Accumulation                  | Depletion                     | Inversion                                    | Inversion                                    |

|-------------|-------------------------------|-------------------------------|----------------------------------------------|----------------------------------------------|

|             |                               |                               | (Linear)                                     | (Saturation)                                 |

| $C_{gs}$    | $C_{ox} \cdot W \cdot L_{ov}$ | $C_{ox} \cdot W \cdot L_{ov}$ | $\frac{1}{2} \cdot C_{ox} \cdot W \cdot L +$ | $\frac{2}{3} \cdot C_{ox} \cdot W \cdot L +$ |

|             |                               |                               | $\bar{C}_{ox} \cdot W \cdot L_{ov}$          | $\check{C}_{ox} \cdot W \cdot L_{ov}$        |

| $C_{gd}$    | $C_{ox} \cdot W \cdot L_{ov}$ | $C_{ox} \cdot W \cdot L_{ov}$ | $\frac{1}{2} \cdot C_{ox} \cdot W \cdot L +$ | $C_{ox} \cdot W \cdot L_{ov}$                |

|             |                               |                               | $\tilde{C}_{ox} \cdot W \cdot L_{ov}$        |                                              |

| $C_{gb}$    | $C_{ox} \cdot W \cdot L$      | Decreasing                    | 0                                            | 0                                            |

| $C_{gc}$    | $C_{gs}+C_{gd}$               | $C_{gs} + C_{gd}$             | $C_{gs} + C_{gd}$                            | $C_{gs} + C_{gd}$                            |

| $C_{gg}$    | $C_{gb} + C_{gc}$             | $C_{gb} + C_{gc}$             | $C_{gb} + C_{gc}$                            | $C_{gb} + C_{gc}$                            |

Table 2.1: Formulas for calculating the MOSFET oxide-related parasitic capacitances, including both voltage-independent and -dependent components. ([39, table 3.6]) W = width [m] L = length [m]  $L_{ov} = \text{overlap}$  distance between the gate and each of two drain and source diffusions [m]  $C_{ox} = \text{gate capacitance per unit area [F/m]}$

## 2.5.5 Impedance

A short review of basic impedance parameters is appropriate. The following has been found in [36, chapter 1-1].

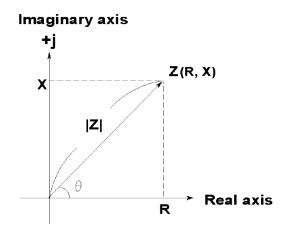

Figure 2.15: The impedance vector. ([36, figure 1-1]).

Impedance is the frequency-dependent opposition of a device. It is a complex value, consisting of a real and an imaginary part. The vector representing this complex quantity is shown in figure 2.15.

On rectangular form the impedance is given by

$$Z = R + jX \qquad [\Omega] \tag{2.13}$$

Z = impedance (complex)

j = imaginary unit

R = resistance (real)

X = reactance (imaginary)

The reactance associated with capacitance is given by

$$X_C = \frac{1}{\omega C} = \frac{1}{2\pi f C} \qquad [\Omega] \tag{2.14}$$

$X_C = \text{capacitive reactance } [\Omega]$  C = capacitance [F]  $\omega = \text{angular frequency } [rad/s]$ f = frequency [Hz]

while the reactance associated with inductance is given by

$$X_L = \omega L = 2\pi f L \qquad [\Omega] \tag{2.15}$$

$X_L$  = inductive reactance [ $\Omega$ ] L = inductance [H]  $\omega$  = angular frequency [rad/s] f = frequency [Hz]

The dissipation factor D describes the loss of energy in a reactive component, and is for a capacitor specifically given as

$$D = \frac{1}{Q} = -\frac{R}{X_C} \qquad [dimensionless] \tag{2.16}$$

D = dissipation factor [dimensionless]Q = quality factor [dimensionless] $X_C = \text{capacitive reactance } [\Omega]$  $R = \text{Resistance } [\Omega]$

## Chapter 3

# Specifications

This chapter will introduce the specifications necessary as a framework for the measurements to be investigated. These are set according to the project text [14], the transistor specification document [38], and after consulting academic advisor. IV characterization is accomplished by applying DC voltage, while CV characterization is accomplished by applying an AC test signal superimposed on a DC voltage as will be seen in section 4.3. Because of this the former is sometimes categorized as DC measurements while the latter is sometimes categorized as AC measurements in this report.

## 3.1 What to be measured

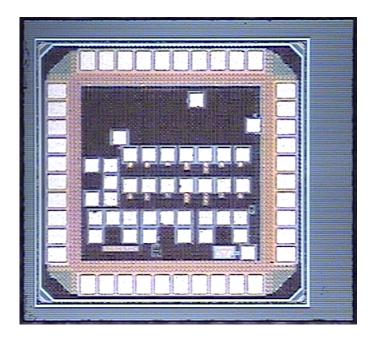

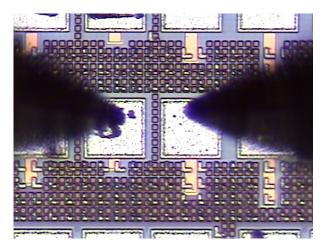

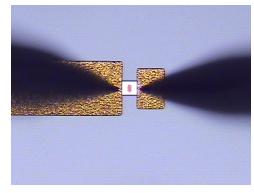

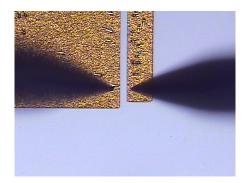

Single 90nm CMOS transistors located on 90nm prototype dies shown in figure 3.1 are to be characterized. These prototype dies have most recently been delivered by the semiconductor fabrication facility, situated on a dielevel. The fabrication of these prototype dies was initiated by IET NTNU.

## 3.2 DC measurements

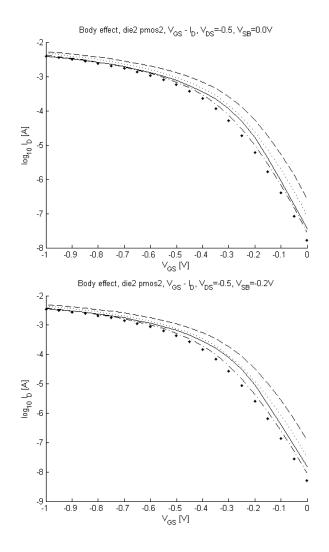

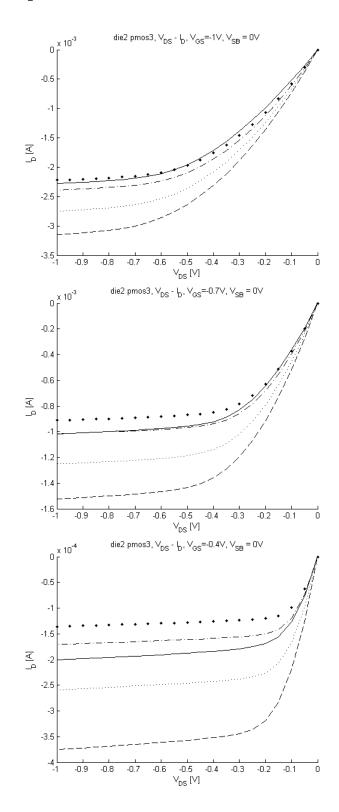

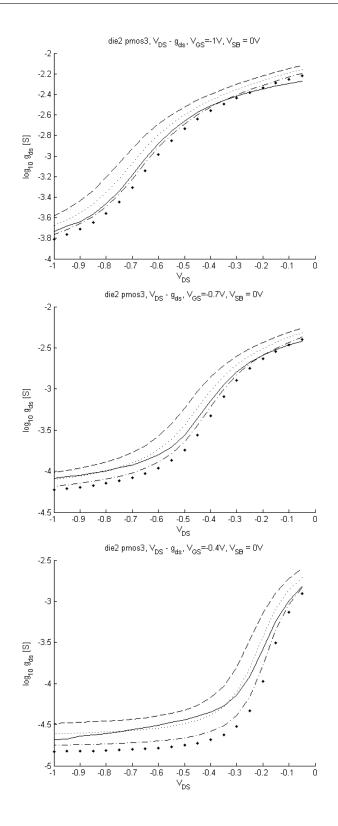

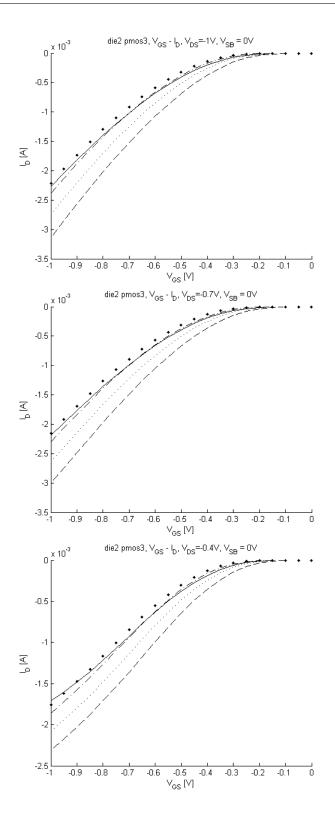

The DC characteristics of the 90nm transistors are to be investigated at room temperature. Generally the IV-characteristics for  $I_D$  as a function of both  $V_{GS}$ ,  $V_{DS}$  and  $V_{SB}$  are of interest. More specifically the leakagecurrents IG and  $I_{sub}$  are important parameters to be investigated, and also the influence of body effect and channel-length modulation.

Figure 3.1: 90nm prototype die.

## 3.3 AC measurements

Regarding AC measurements, this master thesis will include work on finding a suitable CV measurement methodology for the characterization of deep-submicron devices with very thin gate oxides. Further, measurement of MOSFET capacitance with respect to the 90nm transistors is to be accomplished, by carrying out the methodology found. More specifically the oxide-related capacitances are of interest. The work should also include in a discussion about the layout of the prototype dies regarding suitability for CV measurements.

## 3.4 Dimensions for 90nm transistors

The 90nm physical devices on the 90nm prototype dies to be investigated have dimensions as specified in table 3.1 ([38]), where all are of SVT<sup>1</sup>. The four NMOS transistors share common gate, source and bulk. This is also the case for the four PMOS transistors. Parameter m is a device multiplier, indicating that each superior device consists of 10 transistors in parallel with the given dimensions. W, and hence the gate area must therefore be multiplied with 10 to find the total geometry for each device.

<sup>&</sup>lt;sup>1</sup>Standard threshold voltage.

| Device | Width $W$ | Length L | Μ  |

|--------|-----------|----------|----|

|        | [µm]      | [µm]     |    |

| nmos0  | 1.2       | 0.1      | 10 |

| nmos1  | 1.0       | 0.2      | 10 |

| nmos2  | 4.0       | 0.5      | 10 |

| nmos3  | 4.0       | 1.0      | 10 |

| pmos0  | 3.0       | 0.1      | 10 |

| pmos1  | 1.0       | 0.2      | 10 |

| pmos2  | 8.0       | 0.5      | 10 |

| pmos3  | 8.0       | 1.0      | 10 |

Table 3.1: Dimensions for 90nm transistors

There are a total of 15 dies available, all containing the same eight MOS-FETs. These dies are identified by type-number SO9C57D4 and run-number SO9C5-7.

## Chapter 4

# Test setup

This chapter will present the overall test plans both for simulations and physical measurements, along with the setup of test equipment and instrumentation to accomplish the measurements.

A complete equipment list for instrumentation used in the physical measurements can be found in appendix A.

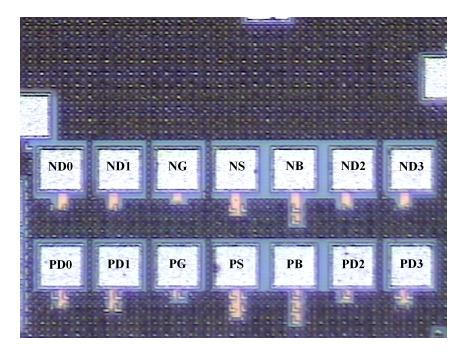

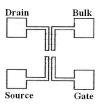

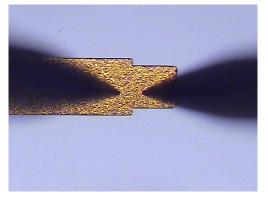

Figure 4.1: Test pads on 90nm prototype dies.

The actual test pads to be used when accomplishing measurements on the 90nm prototype dies are shown in figure 4.1. Here D, G, S and B indi-

cates drain, gate, source and bulk respectively, N and P indicates nmos and pmos, while the drain numbering refers to the device number. Each pad is approximately  $100\mu m$  on each side.

## 4.1 DC measurements for 90nm transistors

For DC measurements on the 90nm transistors there are 6 different tests of interest. These are

- Threshold voltage  $V_{th}$

- Subthreshold leakage current  $I_{sub}$

- $V_{DS}$ - $I_D$  in forward-bias, and from this extracting  $g_{ds}$

- $V_{GS}$ - $I_D$  in forward-bias, and from this extracting  $g_m$

- Gate leakage current  $I_G$ , both in reverse- and forward-bias

- Influence of body effect

Sweep combinations consisting of the following are to be used for NMOS devices:

- $V_{GS}$  swept from 0V to 1V in 0.05V steps (from -0.5V for subthreshold calculations)

- $V_{DS}$  swept from 0V to 1V in 0.05V steps

- $V_{SB}$  swept from 0V to 0.2V in 0.1V steps

While the sweep combinations to be used for PMOS devices are:

- $V_{GS}$  swept from 0V to -1V in -0.05V steps (from 0.5V for subthreshold calculations)

- $V_{DS}$  swept from 0V to -1V in -0.05V steps

- $V_{SB}$  swept from 0V to -0.2V in -0.1V steps

All physical DC measurements will be achieved by using the SUMMIT 11561B probe station from Cascade Microtech in combination with the SCS-4200 Semiconductor Characterization System from Keithley. The DC analyzer includes a Microsoft Windows-based integrated test program environment called KITE<sup>1</sup>, providing the necessary setup and control facilities for the analyzer. [20] presents the use for this DC analyzer and how to achieve the desirable IV characteristics. An introduction to the use of the probe station has been found in [33].

<sup>&</sup>lt;sup>1</sup>Keithley Interactive Test Environment

## 4.2 AC measurements for 90nm transistors

For AC measurements the following tests are of interest

- Gate-to-bulk capacitance  $C_{qb}$  (oxide-related capacitance)

- Gate-to-channel capacitance  $C_{gc}$  (oxide-related capacitance)

- Total gate capacitance  $C_{gg}$  (oxide-related capacitance)

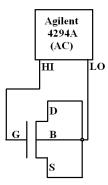

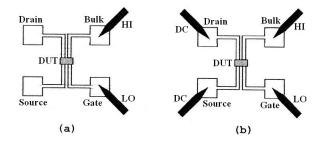

All physical AC measurements will be achieved by using the SUMMIT 11561B probe station from Cascade Microtech in combination with the 4294A Precision Impedance Analyzer from Agilent. [1] has been used as a reference for learning how to operate this instrument. In addition, [3] and [4] presents the use of the AC analyzer in combination with the Cascade Microtech probe station and measurement of very thin gate oxides. For measurements depending on external DC bias in addition to that provided by the 4294A, the Keithley 4200-SCS will be used.

## 4.3 Measurement methodology for CV characterization

According to the specifications in chapter 3, it was of special interest to find a proper test procedure for the preparation and execution of CV measurements for the oxide-related capacitances. This procedure is necessary for obtaining accurate CV results. Information about this has been found in [2], [5], [10], [11], [18], [19, appendix K], [21], [26], [27] and [36]. A guide on accomplishing basic CV measurements with the Agilent 4294A is given in appendix B.

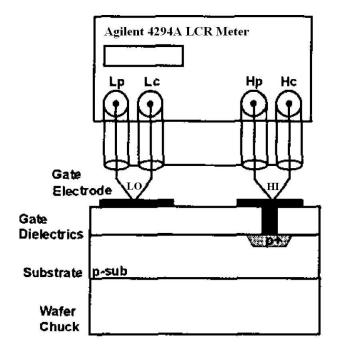

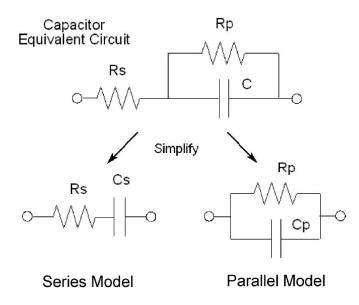

#### 4.3.1 Instrumentation setup and choice of measurement method

The Auto-Balancing Bridge method (ABB) is chosen as the measuring method, as this is suitable for impedance measurement over a wide test signal frequency range ([36, sections 2.1 and 2.3]). The Agilent 4294A is based on this method, and covers test signal frequencies from 40Hz to 110MHz. This fits very well for general measurements on a variety of devices, including the MOSFET parasitic capacitances. This 4294A is a necessity for measuring low parasitic capacitance precisely and with sufficient resolution. One limitation of the ABB method however is that it is not capable of accomplishing measurements at very high frequencies (RF), but this is not of interest for this master thesis.

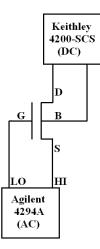

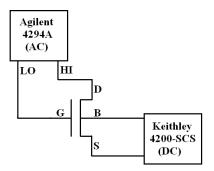

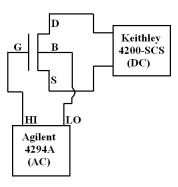

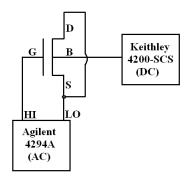

Figure 4.2: Basic setup for CV measurements ([26, figure 2]).