## ULTRA LOW POWER APPLICATION SPECIFIC INSTRUCTION-SET PROCESSOR DESIGN for a cardiac beat detector algorithm

Yahya H. Yassin

Master of Science in Electronics Submission date: June 2009 Supervisor: Per Gunnar Kjeldsberg, IET Co-supervisor: Jos Hulzink, IMEC-NL Jos Huisken, IMEC-NL

Norwegian University of Science and Technology Department of Electronics and Telecommunications

## **Problem Description**

Topic: Application Specic Instruction-set Processor (ASIP) design and application mapping of a biomedical application.

Focus: Computer architecture/arithmetic, Processor design, Continuous wavelet transform (CWT)

IMEC-NL researches and develops wireless autonomous transducer solutions for Wireless Sensor Nodes (WSN) of which each component (radio, digital signal processors (DSPs), sensors, and actuators) is tailored to meet the tight power and performance constraints. The DSPs developed at IMEC-NL process the sensor node data locally, hence reducing power costly wireless data communication in order to minimize energy dissipation of the entire WSN. For this reason, the DSPs must be designed to run a specific application as efficient as possible.

The assignment targets the design of an ASIP with Target processor design tools, and the research and mapping of a biomedical application on this processor. This task includes conversion of Matlab and/or generic C-code to platform related code, mapping it on a generic DSP, and re-target the DSP for the biomedical application.

Assignment given: 12. January 2009 Supervisor: Per Gunnar Kjeldsberg, IET

### Abstract

High efficiency and low power consumption are among the main topics in embedded systems today. For complex applications, off-the-shelf processor cores might not provide the desired goals in terms of power consumption.

By optimizing the processor for the application, or a set of applications, one could improve the computing power by introducing special purpose hardware units. The execution cycle count of the application would in this case be reduced significantly, and the resulting processor would consume less power.

In this thesis, some research is done in how to optimize a software and hardware development for ultra low power consumption. A cardiac beat detector algorithm is implemented in ANSI C, and optimized for low power consumption, by using several software power optimization techniques. The resulting application is mapped on a basic processor architecture provided by Target Compiler Technologies. This processor is optimized further for ultra low power consumption by applying application specific hardware, and by using several hardware power optimization techniques.

A general processor and the optimized processor has been mapped on a chip, using a 90 nm low power TSMC process. Information about power dissipation is extracted through netlist simulation, and the results of both processors have been compared. The optimized processor consume 55% less average power, and the duty cycle of the processor, i.e., the time in which the processor executes its task with respect to the time budget available, has been reduced from 14% to 2.8%. The reduction in the total execution cycle count is 81%.

The possibilities of applying power gating, or voltage and frequency scaling are discussed, and it is concluded that further reduction in power consumption is possible by applying these power optimization techniques. For a given case, the average leakage power dissipation is estimated to be reduced by 97.2%.

## Preface

During the work in this project, I got the opportunity to work with IMEC-NL, where I met very talented engineers and researchers. They gave me the freedom to use state of the art development tools, and to be involved in one of their research projects.

First of all, I want to thank my professor, Per Gunnar Kjeldsberg, for recommending me to some of the master thesis projects from IMEC-NL. I would also like to thank him for an inspirational guidance throughout the project, which resulted in two articles submitted to different conferences.

Further, I would like to thank Jos Hulzink, MSc, and Serdar Yildirim, BSc, for giving me very good guidance throughout this project, and for providing me the necessary training in order to quickly start using the development tools. I also want to thank them for reviewing my thesis, and for giving me good feedbacks.

I would also like to thank

- Iñaki Romero Legarreta, PhD, for the helping me understand his algorithm, and for the help he provided during the Matlab to C conversion process.

- Bernard Grundlehner, MSc, for the help in understanding some specific details related to the provided Matlab model.

- Marjam Ashouei, PhD, for some help related to the software development.

- Filipa Duarte, PhD, for the help she gave me in the creation of low power memories.

- Michael De Nil, MSc, for providing me with a memory wrapper template that I used in order to create the memories in the ASIP design.

- Ben Busze, PhD, for all the help related to synthesis, place and route, and netlist generation.

- Ashoka Sathanur, PhD, and Frank Bouwens, MSc, for the help related to power gating, and voltage scaling analysis.

- Jos Huisken, MSc, for the ideas he shared with me and for reviewing my thesis.

I want to thank Target Compiler Technologies as well for providing superb support services, and for making development tools that makes our lives easier.

In general, I want to thank the DSP team and IMEC-NL for the warm welcome and all the efforts they made to make this master thesis assignment a pleasurable experience. They definitely inspired me to continue with research in the future.

## Contents

| A             | ostra  | let                                      | $\mathbf{v}$ |

|---------------|--------|------------------------------------------|--------------|

| Pr            | reface | e                                        | vii          |

| $\mathbf{Li}$ | st of  | abbreviations                            | xix          |

| 1             | Intr   | roduction                                | 1            |

|               | 1.1    | The goal of ASIP design                  | 2            |

|               | 1.2    | Motivation and goal of work              | 4            |

|               | 1.3    | Outline                                  | 5            |

|               | 1.4    | Main contributions                       | 5            |

| <b>2</b>      | The    | e cardiac beat detection algorithm       | 7            |

|               | 2.1    | The heart and ECG                        | 7            |

|               | 2.2    | The wavelet transform                    | 9            |

|               | 2.3    | The beat detection algorithm             | 11           |

|               | 2.4    | Optimization of the algorithm            | 13           |

|               | 2.5    | The test databases                       | 15           |

|               |        | 2.5.1 The MIT/BIH database               | 15           |

|               |        | 2.5.2 The database recorded by IMEC-NL   | 16           |

| 3             | Ene    | rgy-efficient SW and HW development      | 19           |

|               | 3.1    | Software code optimization techniques    | 20           |

|               | 3.2    | Hardware optimization techniques         | 22           |

|               | 3.3    | Power management techniques              | 24           |

|               |        | 3.3.1 Dynamic power management (DPM)     | 24           |

|               |        | 3.3.2 Component-level power management   | 24           |

|               | 3.4    | Converting floating point to fixed point | 25           |

|               | 3.5    | Profiling                                | 27           |

|               | 3.6    | The energy model                         | 27           |

| <b>4</b>      | Mat    | tlab to C conversion                     | 31           |

|               | 4.1    | The flow of work                         | 31           |

|               | 4.2    | Matlab code analysis                     | 32           |

|               |        | 4.2.1 The CWT function                   | 34           |

|               |        | 4.2.2 The QRSDet3 function               | 34           |

|               |        | 4.2.3 The QRSDet function                | 34           |

|               | 4.3    | The Matlab prototype                     | 35           |

|               | 4.4    | Simulation interface and validation      | 35           |

|               | 4.5    | The floating point application           | 36           |

|   |      | 4.5.1 Implementation of the floating point application                                                                                           |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------|

|   |      | 4.5.2 Optimization of the floating point application                                                                                             |

|   | 4.6  | The fixed point application                                                                                                                      |

|   |      | 4.6.1 Changes to the floating point application                                                                                                  |

|   |      | 4.6.2 Optimization of the fixed point application                                                                                                |

|   |      | 4.6.3 Validation of the fixed point application                                                                                                  |

|   | 4.7  | Results                                                                                                                                          |

|   |      | 4.7.1 Simulation results                                                                                                                         |

|   |      | 4.7.2 Profiling results                                                                                                                          |

|   |      | 4.7.3 Application specifications for processor implementation                                                                                    |

|   | 4.8  | Discussion of the results and conclusions                                                                                                        |

|   | 1.0  |                                                                                                                                                  |

| 5 | The  | a Target Development tools 57                                                                                                                    |

| - | 5.1  | Introduction to the HW/SW Co-design methodology                                                                                                  |

|   | 5.2  | ASIP design with Target                                                                                                                          |

|   | 0.2  | 5.2.1 About Target                                                                                                                               |

|   |      | 5.2.2 ASIP design with Target                                                                                                                    |

|   | 5.3  | 5.2.2       AShi design with farget       55         The nML language       61                                                                   |

|   | 0.0  |                                                                                                                                                  |

| 6 | Δ η  | blication mapping and ASIP design 63                                                                                                             |

| U | 6.1  | The embedded environment of the processor                                                                                                        |

|   | 6.2  | Platform architecture of the BASE core                                                                                                           |

|   | 6.2  | Implementation strategy       67                                                                                                                 |

|   | 6.4  | 1 07                                                                                                                                             |

|   | 0.4  |                                                                                                                                                  |

|   |      | 0                                                                                                                                                |

|   | 0 F  | 6.4.2 Simulation interface with TCL                                                                                                              |

|   | 6.5  | Processor core modifications and optimizations                                                                                                   |

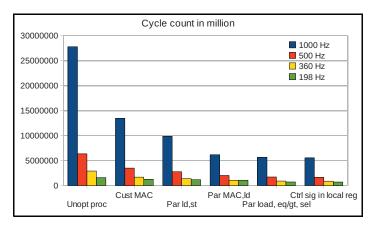

|   | 6.6  | Target profiling results    75                                                                                                                   |

|   | 6.7  | VHDL generation   77                                                                                                                             |

|   | 6.8  | Place and route                                                                                                                                  |

|   | 6.9  | Extraction of power numbers 81                                                                                                                   |

|   | 6.10 | Simulation and power consumption results                                                                                                         |

|   |      | 6.10.1 Register transfer level (RTL) and netlist simulation results 81                                                                           |

|   |      | $6.10.2 \text{ Power numbers} \dots \dots$ |

|   | 6.11 | Discussion of the results and conclusions                                                                                                        |

| _ | ~    |                                                                                                                                                  |

| 7 | Cor  | aclusions 87                                                                                                                                     |

| 0 | T. A |                                                                                                                                                  |

| 8 | Fut  | ure work 89                                                                                                                                      |

| ٨ | nnon | dices                                                                                                                                            |

| A | ppen | ultes                                                                                                                                            |

| Α | Ana  | lysis of the original Matlab model 91                                                                                                            |

|   |      | The CWT function                                                                                                                                 |

|   |      | The QRSDet3 function   93                                                                                                                        |

|   | 11.4 |                                                                                                                                                  |

| в | Det  | ailed description of the Matlab prototype 101                                                                                                    |

|   | B.1  | Changes to the CWT step and modulus maxima step                                                                                                  |

|   | B.2  | Changes to the step for finding clusters of beats                                                                                                |

|   | B.3  | Changes to the classification of beats                                                                                                           |

|   | 0.0  |                                                                                                                                                  |

#### CONTENTS

| C Calcu   | lation of convolution iteration times     | 105 |

|-----------|-------------------------------------------|-----|

| D Solvin  | ng issues related to low threshold values | 109 |

| Bibliogra | aphy                                      | 111 |

## List of Tables

|     | Chosen signals from the MIT/BIH database                                                                                             |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|----|

|     | Memory usage and cycle count with different frequencies of the ECG signal<br>Application specifications for processor implementation |    |

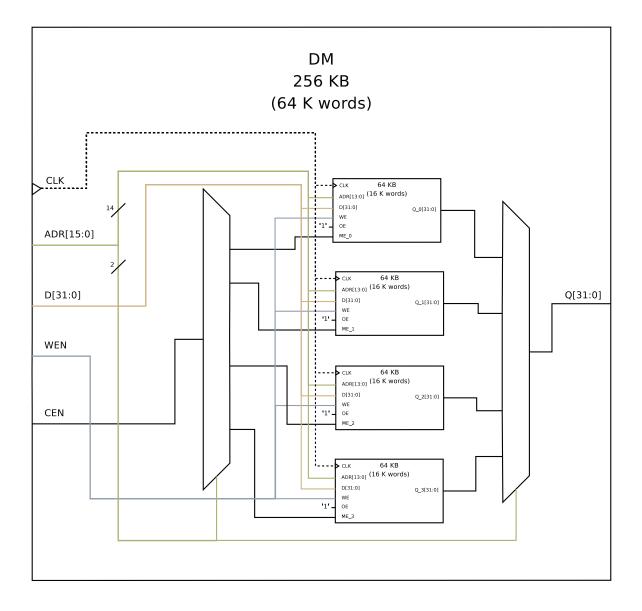

| 6.1 | Truth table for the memory enable signal of DM                                                                                       | 78 |

## List of Figures

| 1.1  | General ASIP design flow                                           |

|------|--------------------------------------------------------------------|

| 2.1  | The heart                                                          |

| 2.2  | Beat demonstration                                                 |

| 2.3  | P,Q,R,S and T waves                                                |

| 2.4  | QRS complex morphologies                                           |

| 2.5  | The Mexican hat wavelet                                            |

| 2.6  | The first algorithm, $[RLAR^+05]$                                  |

| 2.7  | The overlap window                                                 |

| 2.8  | The optimized algorithm. $15$                                      |

| 3.1  | Dominant power sources for a processor                             |

| 4.1  | An overview of the steps in the conversion process                 |

| 4.2  | The Matlab model structure                                         |

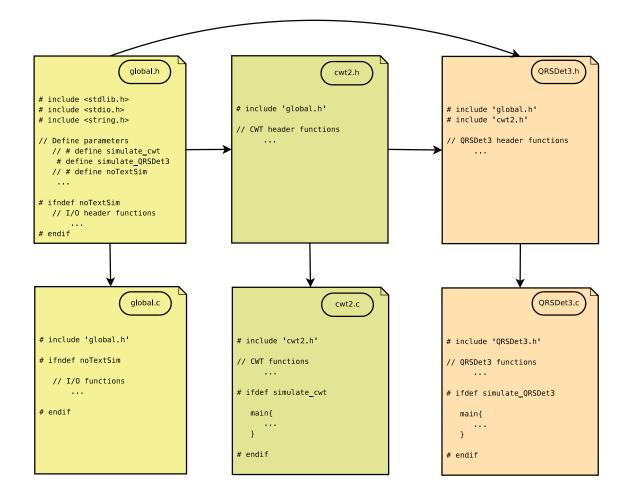

| 4.3  | The C code structure                                               |

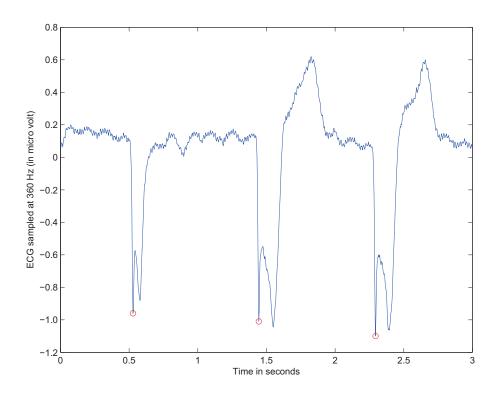

| 4.4  | Special case of an ECG sample                                      |

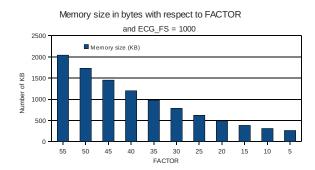

| 4.5  | Memory usage with respect to $FACTOR$ and $ECG\_FS = 100046$       |

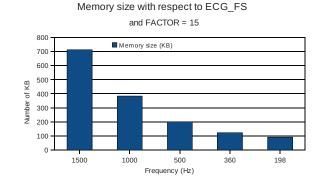

| 4.6  | Memory usage with respect to $ECG\_FS$ and $FACTOR = 15. \dots 47$ |

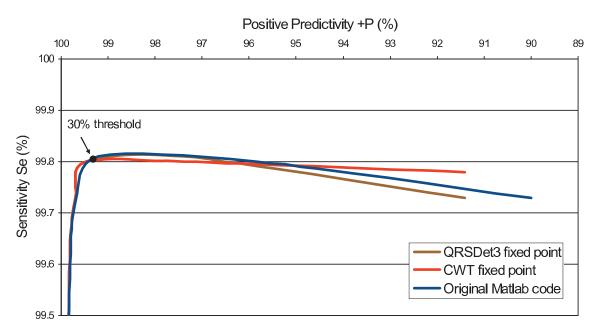

| 4.7  | The MIT/BIH test over all thresholds                               |

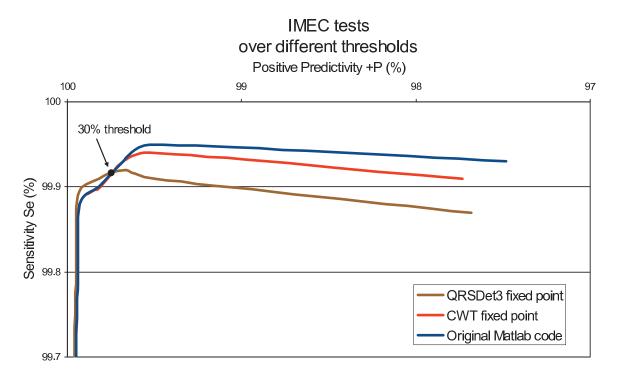

| 4.8  | The IMEC test over all thresholds                                  |

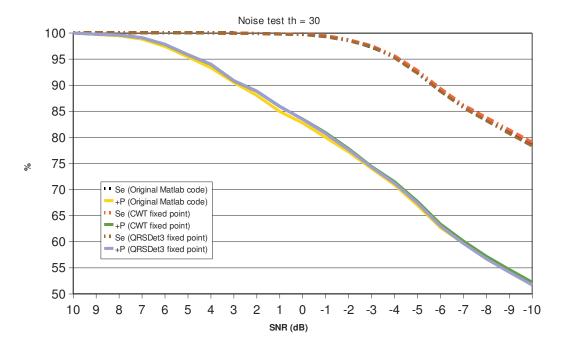

| 4.9  | Noise tests for th= $30\%$                                         |

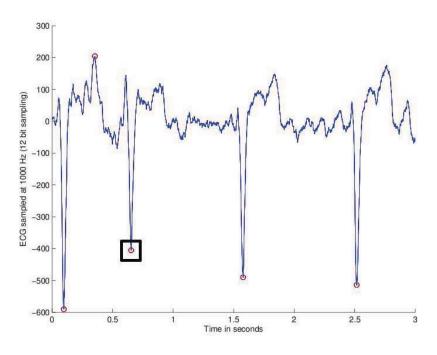

| 4.10 | The sample of an ECG signal used for profiling                     |

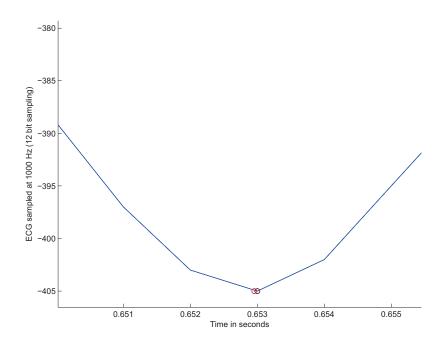

| 4.11 | The second beat detected by the sample in Figure 4.10              |

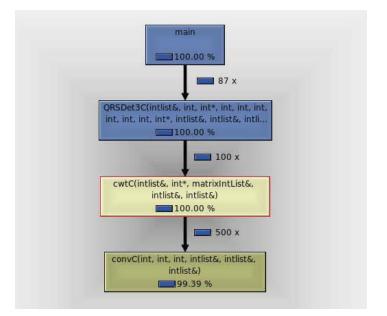

| 4.12 | The call graph with the focus on the convC function                |

| 5.1  | An outline of the Chess/Checkers environment                       |

| 6.1  | Processing interval of the processor in a real-time environment    |

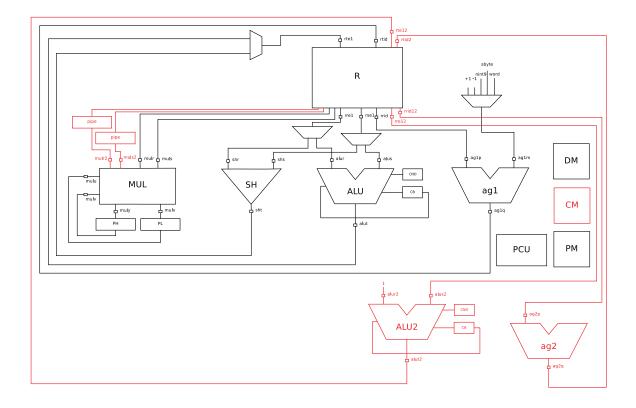

| 6.2  | The BASE processor core architecture                               |

| 6.3  | Instruction pipeline                                               |

| 6.4  | ASIP implementation strategy                                       |

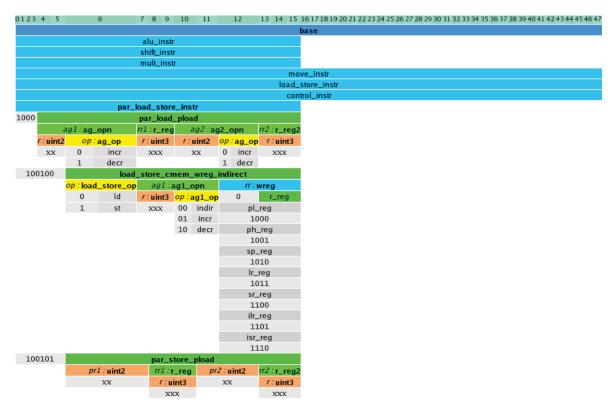

| 6.5  | Initial instruction-set of the 32-bit processor                    |

| 6.6  | Initial simulation without the MAC unit                            |

| 6.7  | Simulation with the resulting MAC unit                             |

| 6.8  | The new parallel instruction assembly code                         |

| 6.9  | The new parallel instruction                                       |

| 6.10 | The new parallel load and MAC instruction                          |

| 6.11 | The new parallel load, equal and select instruction                |

|      | The optimized BASE architecture                                    |

| 6.13 | Improvement in execution cycles after every optimization step      |

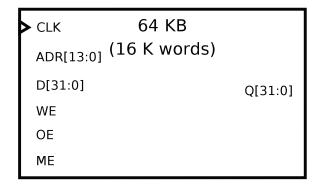

| 0.14                                   | A memory block from VLC                                                                                                                                                                                                                                                                                                                  | 77                               |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 6.15                                   | The memory wrapper of DM                                                                                                                                                                                                                                                                                                                 | 78                               |

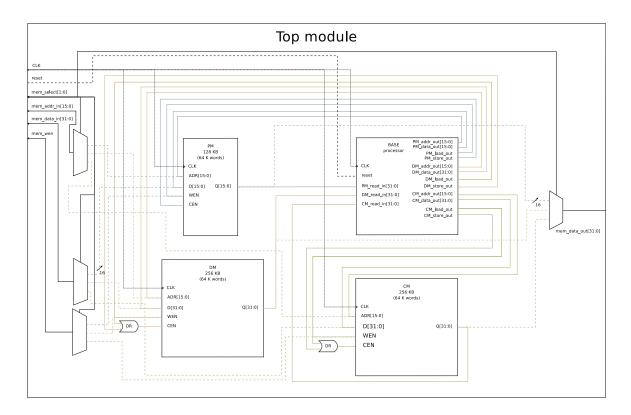

| 6.16                                   | The top module                                                                                                                                                                                                                                                                                                                           | 79                               |

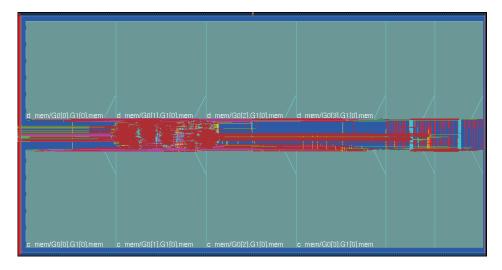

| 6.17                                   | How the memory blocks were placed on the chip                                                                                                                                                                                                                                                                                            | 80                               |

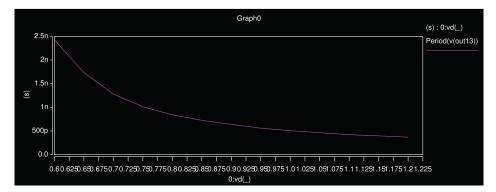

| 6.18                                   | How the delay of the circuit varies with different supply voltages                                                                                                                                                                                                                                                                       | 81                               |

| 6.19                                   |                                                                                                                                                                                                                                                                                                                                          | 82                               |

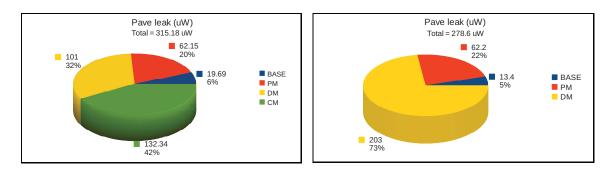

|                                        |                                                                                                                                                                                                                                                                                                                                          | 82                               |

|                                        |                                                                                                                                                                                                                                                                                                                                          | 83                               |

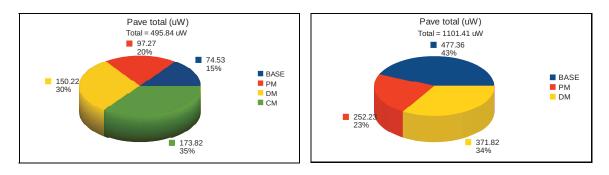

| 6.22                                   | Average dynamic power consumption of the processors                                                                                                                                                                                                                                                                                      | 83                               |

|                                        |                                                                                                                                                                                                                                                                                                                                          | 83                               |

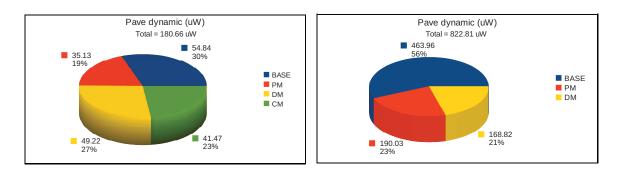

| 6.24                                   | Total average power consumption of the processors                                                                                                                                                                                                                                                                                        | 84                               |

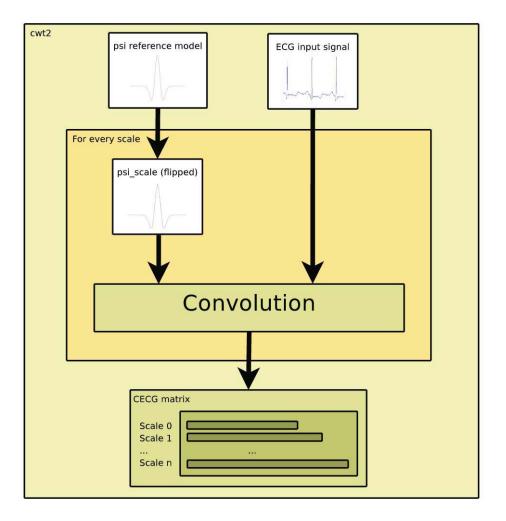

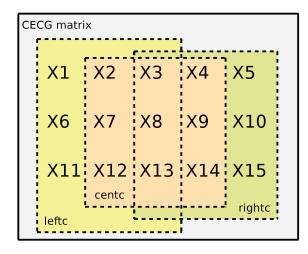

| A.1                                    | Illustration of the cwt2 function.                                                                                                                                                                                                                                                                                                       | 92                               |

|                                        |                                                                                                                                                                                                                                                                                                                                          |                                  |

| A.Z                                    | Creation of the modulus maxima matrices                                                                                                                                                                                                                                                                                                  | 94                               |

| A.2<br>A.3                             |                                                                                                                                                                                                                                                                                                                                          | $\frac{94}{94}$                  |

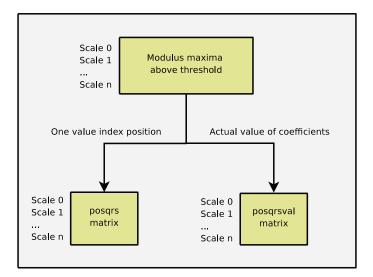

|                                        | Modulus maxima above the threshold                                                                                                                                                                                                                                                                                                       | 94                               |

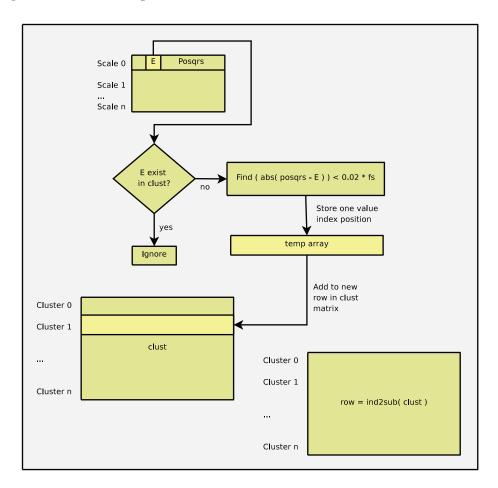

| A.3                                    | Modulus maxima above the threshold                                                                                                                                                                                                                                                                                                       | $94 \\ 95$                       |

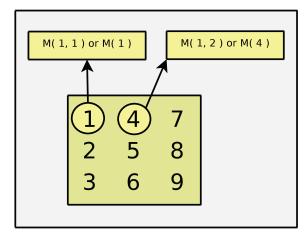

| A.3<br>A.4                             | Modulus maxima above the threshold.       9         Finding clusters of beats.       9         Matlab indexing of matrices.       9                                                                                                                                                                                                      | 94<br>95<br>96                   |

| A.3<br>A.4<br>A.5                      | Modulus maxima above the threshold.       9         Finding clusters of beats.       9         Matlab indexing of matrices.       9         Classification of beats.       9                                                                                                                                                             |                                  |

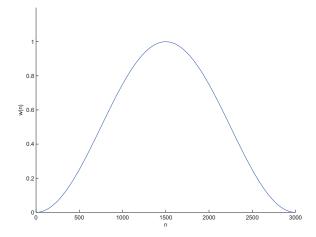

| A.3<br>A.4<br>A.5<br>A.6<br>A.7        | Modulus maxima above the threshold.       9         Finding clusters of beats.       9         Matlab indexing of matrices.       9         Classification of beats.       9         The hanning window by definition.       9                                                                                                           | 94<br>95<br>96<br>97             |

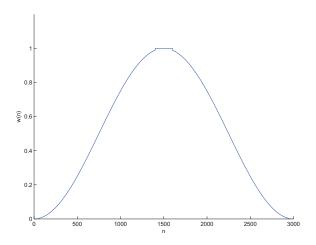

| A.3<br>A.4<br>A.5<br>A.6<br>A.7        | Modulus maxima above the threshold.       9         Finding clusters of beats.       9         Matlab indexing of matrices.       9         Classification of beats.       9         The hanning window by definition.       9         The modified hanning window.       9                                                              | 94<br>95<br>96<br>97<br>98       |

| A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8 | Modulus maxima above the threshold.       9         Finding clusters of beats.       9         Matlab indexing of matrices.       9         Classification of beats.       9         The hanning window by definition.       9         The modified hanning window.       9         Finding clusters of beats in the prototype.       10 | 94<br>95<br>96<br>97<br>98<br>98 |

## Source code

| 4.1  | Code before optimization                                         | 39  |

|------|------------------------------------------------------------------|-----|

| 4.2  | Code after optimization                                          | 39  |

| 4.3  | Code consideration of fixed point addition in a loop             | 41  |

| 4.4  | Code before fixed point conversion                               | 41  |

| 4.5  | Code using solution 1 based on Code Snippet 4.7                  | 41  |

| 4.6  | Code using solution 2 based on Code Snippet 4.7                  | 42  |

| 4.7  | Code before fixed point conversion                               | 42  |

| 4.8  | Fixed point round operations                                     | 42  |

| 4.9  | Floating point elimination                                       | 43  |

| 4.10 | Floating point cosine calculation.                               | 43  |

| 4.11 | Fixed point cosine calculation.                                  | 43  |

|      | Calculating the alternative lookup table in Matlab               | 44  |

| 4.13 | Optimization of the assignment of _psi_scale.array               | 44  |

| 4.14 | Fixed point cosine calculation.                                  | 45  |

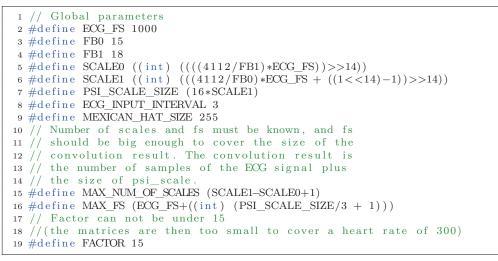

| 4.15 | Global define parameters in global.h.                            | 47  |

| 4.16 | Pre-processor macro optimization of the <i>abs</i> function in C | 47  |

| 4.17 | Call graph results from <i>gprof</i>                             | 52  |

| 5.1  | AND-rule                                                         | 61  |

| 5.2  | OR-rule                                                          | 61  |

| 5.3  | A basic ALU instruction                                          | 62  |

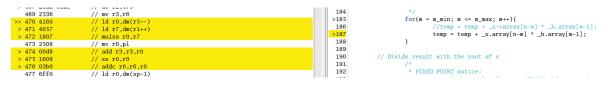

| 6.1  | 32-bit MAC unit                                                  | 71  |

| 6.2  | 32-bit MAC unit after modification                               | 71  |

| 6.3  | Direct assignment to CM.                                         | 72  |

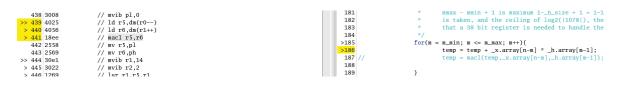

| 6.4  | Parallel load instruction.                                       | 72  |

| 6.5  | Parallel load and MAC instruction                                | 74  |

| 6.6  | Parallel load, equal and select instruction.                     | 75  |

| 6.7  | A $nop$ and select instruction.                                  | 75  |

| C.1  | Matlab code for convolution by the original definition.          | 105 |

| C.2  | C code for convolution by the Matlab definition.                 | 107 |

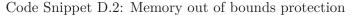

| D.1  | The code before inserting the memory protection                  | 109 |

| D.2  | Memory out of bounds protection                                  | 109 |

## List of abbreviations

$\ensuremath{\mathsf{ADC}}$  Analogue to Digital Converter

| <b>ADL</b> Architecture Description Language               |  |  |

|------------------------------------------------------------|--|--|

| <b>ALU</b> Arithmetic-Logic Unit                           |  |  |

| <b>ASA</b> Application Specific Architectures              |  |  |

| <b>ASIC</b> Application Specific Integrated Circuits       |  |  |

| <b>ASIP</b> Application Specific Instruction-set Processor |  |  |

| $\boldsymbol{AV}$ Atrio-Ventricular                        |  |  |

| <b>CCU</b> Coronary Care Unit                              |  |  |

| <b>CM</b> Coefficient Memory                               |  |  |

| <b>CPU</b> Central Processing Unit                         |  |  |

| <b>CWT</b> Continuous Wavelet Transform                    |  |  |

| <b>CWTMM</b> Continuous Wavelet Transform Modulus Maxima   |  |  |

| <b>DM</b> Data Memory                                      |  |  |

| <b>DPM</b> Dynamic Power Management                        |  |  |

| <b>DSP</b> Digital Signal Processor                        |  |  |

| <b>DTSE</b> Data Transfer and Storage Exploration          |  |  |

| <b>DVFS</b> Dynamic Voltage and Frequency Scaling          |  |  |

| <b>ECG</b> Electrocardiogram                               |  |  |

| <b>EMG</b> Electromyography                                |  |  |

| GCC GNU C Compiler                                         |  |  |

| <b>GNU</b> Gnu's Not Unix                                  |  |  |

| <b>HDL</b> Hardware Description Language                   |  |  |

| HW/SW Co-design Hardware/Software Co-design                |  |  |

$\ensuremath{\mathsf{IC}}$  Integrated Circuit

#### **IMEC-NL** Interuniversity Microelectronics Centre Netherlands

- **ISA** Instruction-Set Architecture

- **ISP** Instruction-Set Processor

- **ISS** Instruction-Set Simulator

- MAC Multiply-Accumulate

- **MSB** Most Significant Bit

- **PC** Program Counter

- **PCU** Program Control Unit

- **PDG** Primitives Definition and Generation

- **PM** Program Memory

- **RAM** Random Access Memory

- ${\ensuremath{\mathsf{RPM}}}$  Rounds Per Minute

- **RTL** Register Transfer Level

- ${\boldsymbol{\mathsf{SA}}}$  Sino-Atrial

- ${\sf SNR}$ Signal-to-Noise Ratio

- ${\bf SoC}\,$  System on Chip

- ${\boldsymbol{\mathsf{SP}}}\ {\rm Stack}\ {\rm Pointer}$

- **SPEF** Standard Parasitic Exchange Format

- TCL Tool Command Language

- **TSMC** Taiwan Semiconductor Manufacturing Company Limited

- $\boldsymbol{\mathsf{ULP}}$ Ultra Low Power

- ${\sf VCD}\,$  Value Change Dump

- **VHDL** VHSIC Hardware Description Language

- **VHSIC** Very High Speed Integrated Circuit

- **VLC** Virage Logic Corporation

- WSN Wireless Sensor Nodes

# Chapter 1

## Introduction

Cardiovascular disease is one of the most common cause of death in Western society, [LRW<sup>+</sup>03]. A Cardiovascular disease refers to the class of diseases that involve the heart or blood vessels (arteries and veins), [Wik09a] and [MHM<sup>+</sup>93]. In order to diagnose such diseases, an analysis of the heart rate is necessary, and the physiologic signal used to determine the heart rate is the electrocardiogram (ECG). By processing the ECG signal, it is possible to detect heart beats, and one can also analyze the ECG in order to classify cardiovascular diseases. Therefore, the algorithm processing the ECG signal must be as accurate as possible. Many approaches have been proposed for automatic beat detection algorithms, i.e., ECG beat detection using filter banks [ATNL99], zero-crossing [KHO03], signal derivatives [FN06], digital filters [KKA97], algorithms from the field of artificial neural networks [BFDVS<sup>+</sup>98], and algorithms using wavelet transforms [LZT95], [RLAR<sup>+</sup>05].

The requirements for an embedded device implementing applications with such algorithms, introduce several challenges that have to be solved. This is specially the case for ambulatory monitoring. Afonso et al. [ATNL99] points out that the ECG is prone to various types of noise, and it is important to reduce the noise without distorting the morphology of the ECG. However, the task is not easy, because the appearance of heartbeats varies considerably [BFDVS<sup>+</sup>98]. This variation is not only limited to different patients, but also appears as the consequences of movement, modifications of electrical characteristics of the body, etc. For such applications, embedded devices usually need processors with high performance.

According to Kucukcakar et al. [Kuc99], the use of off-the-shelf processors and memories is a common way to achieve the best time-to-market and the lowest cost. In addition, it is easy for designers to find the right processor with average performance and power consumption for an application. However, if the performance bottlenecks of the application can not be avoided through software re-organization, then a more complex processor is needed. This usually means upgrading to a higher performance processor, which most often result in higher cost and energy consumption. For applications implementing advanced heart beat detectors, this is usually the case. Instead of upgrading to a higher performance processor, one could design an Application Specific Architecture (ASA), specialized for the application. ASA refers to instruction-set processors (ISP), digital signal processors (DSPs) and integrated circuits (ICs) designed for a specific application. What kind of architecture is needed depends on the application. The use of an Application Specific Integrated Circuit (ASIC) gives the best solution for an application. However, if a newer version of the application is designed, then a complete new ASIC must be made. A more flexible solution is the use of Application Specific Instruction-set Processors (ASIP).

In embedded systems design today, there is need for high efficiency, as well as low

power consumption [KAFK<sup>+</sup>05], [GM01]. In recent years, ASIPs have been popular because they offer efficiency and short design cycles at the same time. In contrast to off-the-shelf processor cores, ASIPs show dedicated functional units and machine instructions that speed up execution of the "hot spots" in a given application [KAFK<sup>+</sup>05].

In this thesis, an Ultra Low Power (ULP) ASIP will be designed for a biomedical application, using an algorithm developed by Romero et al., [RLAR+05]. In this algorithm, the problem of automatic beat recognition in the ECG is tackled using a mathematical method called Continuous Wavelet Transform Modulus Maxima (CWTMM), [RLAR+05].

In a simulation environment, this algorithm produced very good results with world-wide known databases such as the MIT/BIH database. The algorithm has been further optimized to work in real time for implementation in an ambulatory ECG monitor by the Interuniversity Microelectronics Centre Netherlands (IMEC-NL), [RLG08a]. IMEC-NL is an independent micro- and nanoelectronics research center located in Eindhoven, Netherlands. This research center focuses on next generation electronics research, three to ten years ahead of industrial needs.

The purpose of this chapter is to provide the reader with the necessary background information for ASIP design in order to understand the work done in this master thesis.

#### 1.1 The goal of ASIP design

According to [RAP08], an ASIP is a microprocessor specialized for an application. Its instruction set is designed from scratch or extended from a known microprocessor, in order to optimize the performance of the application. Application Specific Architectures (ASA) like ASIPs are able to reach a better cost and performance ratio by exploiting the characteristics of the application they are dedicated to [DGF90], using design methodologies like hardware/-software co-design (HW/SW Co-design). The computing power is improved by introducing special purpose hardware units, exploiting the parallelism available in the application. They can also be cost effective by saving hardware resources. This is done by only implementing the resources needed by the application.

The concept of ASIPs is to fill the gap between Application Specific Integrated Circuits (ASIC) and Digital Signal Processors (DSP), [RAP08]. ASICs are highly efficient, but they lack the flexibility. On the other hand, DSPs provide software reusability with less performance and energy efficiency as compared to ASICs, [RAP08].

In general, the design of an ASA is not an easy task, and requires the scanning of the architectural space to discover the most useful choices which could efficiently support the applications features. In addition, the development requires complex tools to evaluate and provide analysis of the ASA development, and hence guide the designer towards correct design choices.

Power and performance optimization could be applied at the logic level, register transfer level (RTL), in the ASIP software, and also at system level [GM01]. De Gloria et al. [DGF90] defines some main requirements for the design of an ASA, and in [JBK01], five general steps in ASIP synthesis are presented. Different design flows for ASIP design exists, such as the methodology presented in [Kuc99], and the ASSIST methodology [KJBK04]. Those methodologies differ from one another on a detailed level. However, they are all similar to the design flow presented in [JBK01]. The rest of this section will present this design flow.

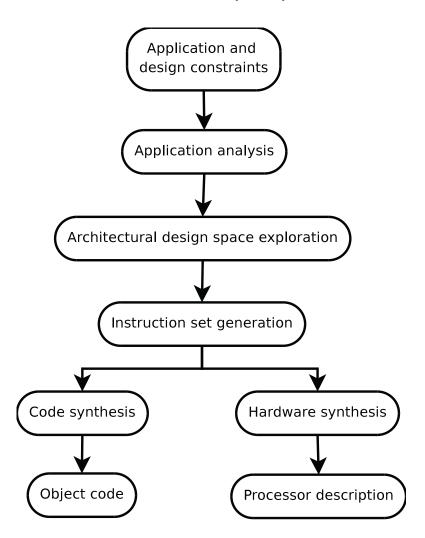

The application is first provided with its design constraints. In order to design an ASIP, it is necessary to understand the behavior of the application. The application must be analyzed statically and dynamically to get the desired characteristics and requirements which can guide the hardware synthesis as well as instruction-set generation. The next step is to identify possible architectures that meet the application constraints. In addition, the performance of possible architectures is estimated, and the architectures satisfying the performance and power constraints are chosen.

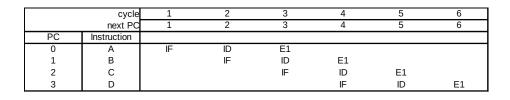

In the third step, the instruction set is generated for that particular application, and for the architectures selected. This is needed for the synthesis steps. A compiler generator or a re-targetable code generator is used in the fourth step to synthesize code for the particular application, or for a set of applications. The re-targetable compiler includes the steps of instruction mapping, resource allocation, and scheduling of the application.

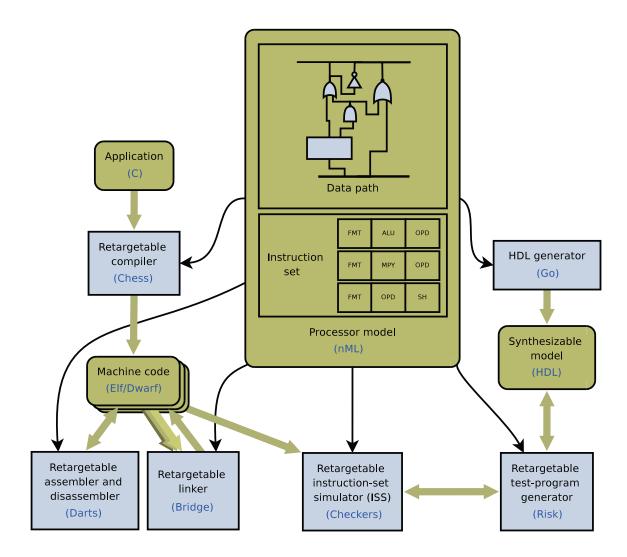

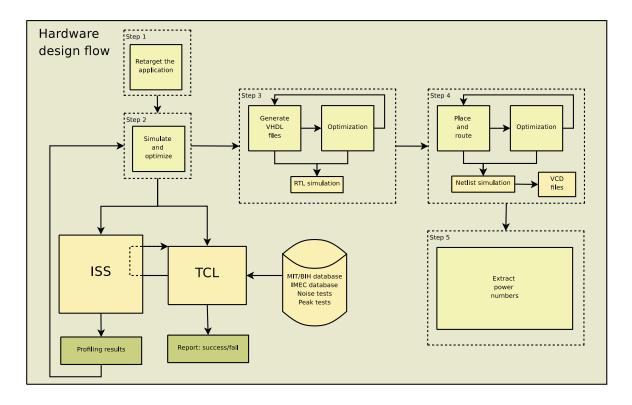

In the final step, the hardware is synthesized using the ASIP architectural template and instruction set architecture starting from a description in VHDL or Verilog. Figure 1.1 summarizes the general design flow presented in [JBK01].

Figure 1.1: General ASIP design flow based on the one presented in [JBK01].

All these steps are more or less guidelines for the development of an ASIP. If all time constraints are fulfilled, then additional optimizations can be introduced to increase power efficiency. Glokler et al. [GM01] distinguish the energy required to execute a given algorithm in hardware in three parts; intrinsic energy, routing energy, and overhead energy.

The intrinsic energy refers to the minimum required processing energy to execute a computational part, i.e., an arithmetic operation. This energy only depends on the operations

of an algorithm and the process technology. The energy is constant as long as the algorithm remains the same.

Routing energy is the energy needed to move data in the chip. For instance, memory accesses requires energy to transfer the data to local registers. As long as changes to the architecture have a limited impact on data routing, the routing energy does not change significantly.

The remaining energy is referred to as the overhead energy, i.e., caused by wasteful logic activity, control activity, etc. Performance optimization for Instruction-Set Architectures (ISA) typically also reduce overhead energy due to the decrease of the processor runtime, because the overhead power remains nearly constant.

The ASIP design flow presented in this section will be used as a guideline for the ASIP design done in this thesis.

#### **1.2** Motivation and goal of work

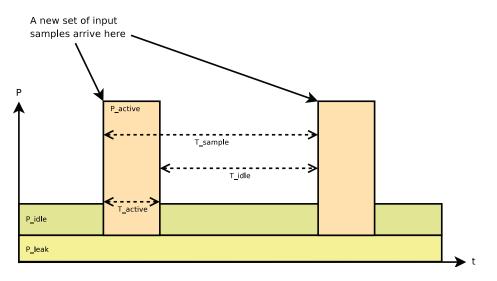

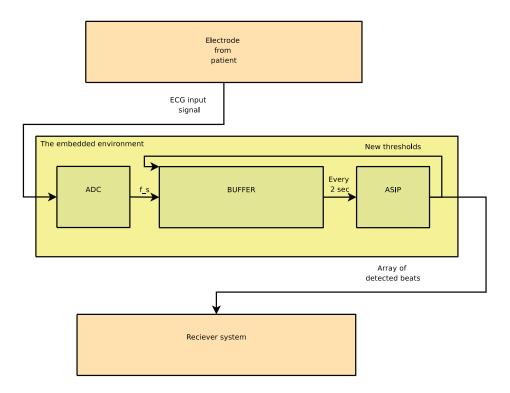

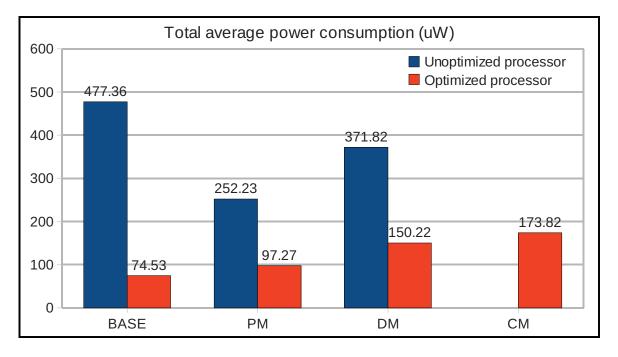

The purpose of this project is to develop knowledge and experience on how to design an ASIP for ultra low power (ULP), and map a specific application into it. In this case the application is a heart beat detector designed by Romero et al. [RLAR<sup>+</sup>05], based on the CWTMM. This application process the ECG signal by analyzing every 2 seconds at a time. In a real-time environment, every 2 seconds of an ECG signal must be sampled, and buffered before the signals are processed. The real-time requirement for this application is to finish processing this 2 second buffer before the next buffer is ready. This gives a processing deadline of 2 seconds.

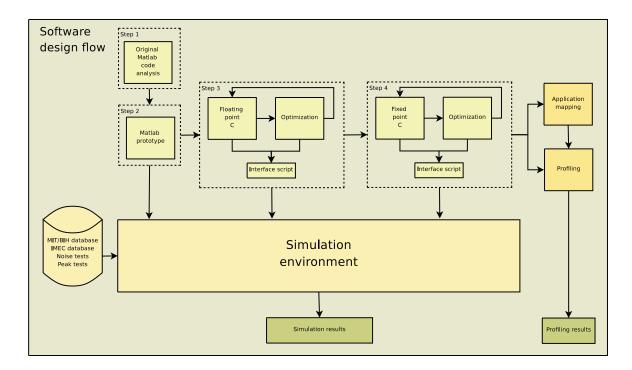

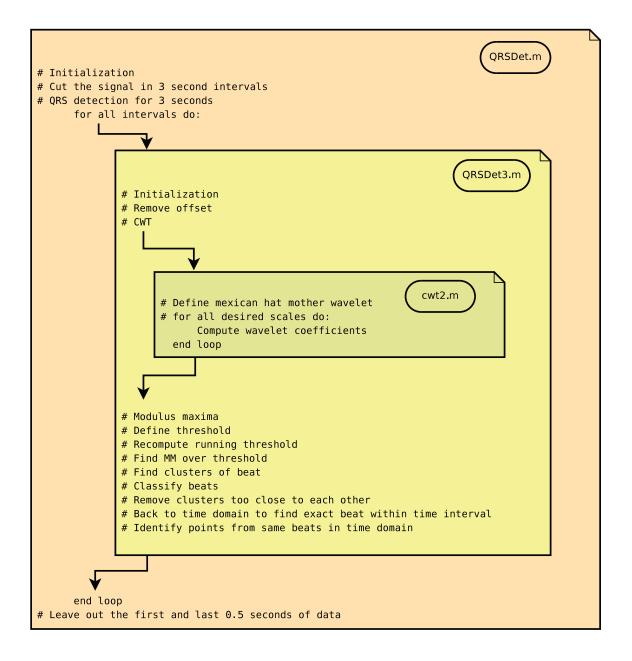

Before an algorithm can be mapped into a processor one has to go through several design steps, as presented in Section 1.1. In this case, the algorithm is modeled in Matlab, using built-in Matlab functions which do not exist in programming languages like C. Therefore, the first step would be to convert the code into an embedded software. In this thesis the program language C will be used, because it is a common language used by many processor developers. In addition, C is supported among various development tools for processor design. During the conversion, the algorithm must be tested using good test benches, i.e., with test signals from known databases. In order to increase efficiency, all floating point signals should be converted into fixed point, and heavy computational parts of the code like square roots and divisions must be optimized away if possible. By doing so, one can eliminate the need for a floating point emulator on the processor, in addition to complex logic. This would result in less power consumption. After the embedded software is optimized, the memory resources can be determined. This will be done by profiling.

After finishing the software optimizations, the work on an energy efficient processor architecture will start. Based on the constraints and optimizations made from the embeddable software application, an ASIP will be designed. This step involves architecture exploration and mapping of the software application through an iterative process. In this thesis the development tools from Target will be used. An existing basic processor architecture will be used as a base, and this architecture will be modified in order to optimize the biomedical application for ultra low power. The work on this project will include research on how to design the software and an ASIP for ULP. Design methodologies like hardware/software co-design (HW/SW Co-design) will also be used.

#### 1.3 Outline

Previous work associated with the biomedical application is presented in Chapter 2, in order to understand the given Matlab model. Theory related to the development of energy-efficient software and hardware is presented in Chapter 3, as well as some hardware and software optimization techniques that could be applied to reduce the power consumption of a processor. In the Chapter 4, the analysis of this Matlab model will be presented, including the work done to convert and optimize the application for an embedded environment. The results from the profiling and from the databases will be presented and discussed. In Chapter 5, the development tools used in this project will be introduced, before the work on the ASIP is presented in Chapter 6. The conclusions of this project is given in Chapter 7, before presenting future work objectives in Chapter 8.

#### **1.4** Main contributions

- Converted the Matlab model of the algorithm, designed by Romero et al. [RLAR<sup>+</sup>05], into a floating point C application.

- Converted the floating point C application to a fixed point application.

- Optimized the application further by using lookup tables, inline functions, reducing read and write operations to global memories, eliminating divisions with constant values where it is possible, combining loops, implementing software division for usage outside the critical loop, implementing a special cosine function using a small lookup table, insertion of pre-processor macros, and re-usage of variables.

- Reduced the run-time memory usage of the application significantly, to only 150 KB for an ECG sample frequency of 198 Hz.

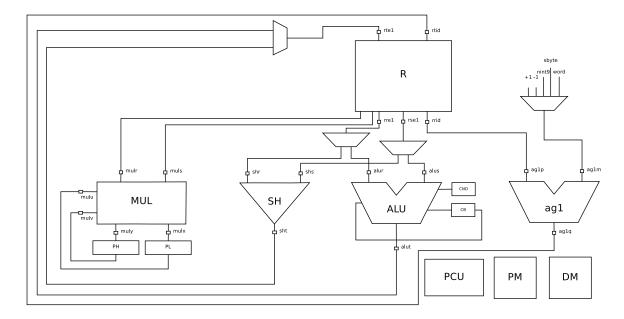

- Converted a 16-bit general purpose instruction-set processor into a 32-bit application specific instruction-set processor (ASIP).

- Designed a customized MAC instruction in the processor.

- Designed parallel custom instructions in the processor, i.e., parallel load and store instructions, and parallel load, equal/greater than, and select instructions.

- Implemented additional functional units, and divided the data memory of the processor in two smaller memories, in order to access two data memories within the same clock cycle, in parallel.

- Added instruction level parallelism with two load and one multiply-accumulate operation, reducing the main critical loop to one single clock cycle.

- Changed the factor registers of the multiplier unit, such that they could be loaded by the load operations directly. Similarly was done to the product register of the multiplier, in order to read from that register directly. Otherwise, the data would have been copied to other registers before the information could be used.

- Reduced the total execution cycle count by 81%.

- Generated VHDL code for the processor using the development tools from Target Compiler Technologies.

- Synthesized the design, using 90 nm TSMC low power memories, from Virage Logic Corporation.

- Extracted timing information and power numbers after a place and route step on a chip, using 90 nm TSMC.

- Reduced the total average power consumption by 55%.

- Suggested future work objectives for further reduction in total average power consumption.

### Chapter 2

## The cardiac beat detection algorithm

In order to understand how the application works, and in order to optimize it further for ultra low power (ULP), it is necessary to have an understanding of the theory behind the application itself and how the application works. Since the biomedical application is a heart beat detector, a general introduction of the heart, how it works, and ECG is given in Section 2.1. The theory related to the continuous wavelet transform is presented in Section 2.2, before presenting previous work in Section 2.3 and 2.4. Section 2.5 presents the test databases used in this thesis.

#### 2.1 The heart and ECG

The heart of a human being is a muscle that could be viewed as a pumping machine. It has four different blood-filled areas called chambers. The two upper chambers, the atria (left and right atrium), returns the blood from the body and lungs, and the two lower chambers, the ventricles (left and right ventricle), squirts the blood back to the body and lungs. The circulation is referred to as the movement of blood through the heart and around the body. By this circulation, the blood transports important supplies for the body like oxygen and carbon dioxide. This movement is caused by a pumping action, which is triggered by electric impulses generated from within the heart. All the information regarded to the basic theory of the heart and how a heartbeat is created was taken from [HRS] and [Abd], and the reader is referred there for further detail about the heart.

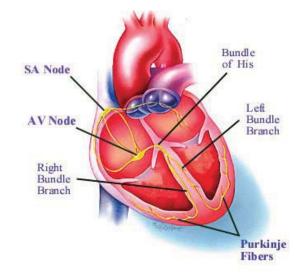

In order to create a pulse, the heart has a mechanism that generates electrical signals. These electrical signals goes through the heart, causing the muscle cells to contract. This mechanism tells the heart when to beat, and it works similarly as a spark plug of an automobile, where each "spark" travels across a specialized electrical pathway, and stimulates the muscle wall of the four chambers of the heart to contract in a certain sequence or pattern. A picture of the electrical system of the heart can be viewed in Figure 2.1. There are mainly one electrical node that generates those electrical impulses. This node sits in the upper portion of the right atrium, and is a collection of specialized electrical cells known as the sinus or sino-atrial (SA) node. The upper chambers, the atria, are first stimulated. Between the ventricles and the atria, a node known as the atrio-ventricular (AV) node, holds the electrical impulse for a brief period. This delay allows the right and left atrium to continue emptying its blood contents into the two ventricles. Therefore, the AV node acts like a "relay station", re-generating and delaying stimulation of the ventricles long enough to allow the

two atria to finish emptying. A structure called the bundle of His emerges from the AV node and divides into thin, wire-like structures called bundle branches that extend into the right and left ventricles. The electrical signal travels down the bundle branches to thin filaments known as Purkinje fibers. These fibers distribute the electrical impulse to the muscles of the ventricles, causing them to contract and pump blood into the arteries. This whole process is referred to as a heart beat, and those beats are generated several times per minute.

Figure 2.1: The heart, showing the electrical system of the heart [HRS].

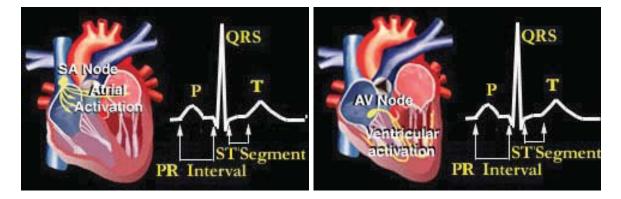

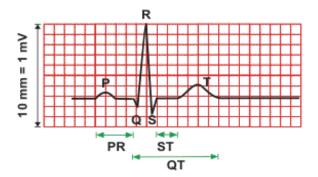

Figure 2.2 shows how the electrical signal is generated, as well as the electrical wave which can be detected from the surface of the body by an ECG monitor. When the SA node fires a signal and causes the upper chambers to contract, the wave recorded on an ECG is known as the P-wave. The delay of the electrical impulse generated when the electrical impulse moves to the AV node, is recorded as the PQ-segment. When the electrical impulse travels through the ventricles and stimulates them to contract and pump blood into the body and lungs, it generates a wave known as the QRS complex. Then, the ventricles recover from this electrical stimulation and generates the T-wave, which is recorded by the ECG.

Figure 2.2: A demonstration of a heart beat [Abd].

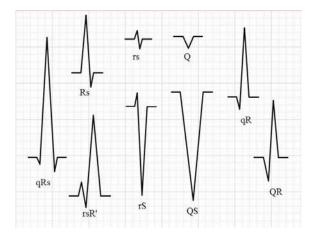

Heart beat detection algorithms usually try to detect the QRS complex, because of its high amplitude. Figure 2.3 shows how the P,Q,R,S and T waves are displayed on an ECG monitor, using one standard electrode position. There exist different morphologies (different shapes

and amplitude) of the QRS complex, and Figure 2.4 demonstrates various QRS complexes.

Figure 2.3: P,Q,R,S and T waves on an ECG monitor [RLG08a].

Figure 2.4: Various QRS complex morphologies [RLG08a].

The algorithm developed by Romero et al. [RLAR<sup>+</sup>05] has a high performance and is robust against sensible levels of noise or different morphologies of the QRS complex, according to [RLG08a] and [RLAR<sup>+</sup>05]. Since this algorithm is based on the continuous wavelet transform (CWT), the next section will describe the CWT in detail as well as the modulus maxima and the Mexican hat wavelet (which is used in the CWT as a reference wavelet), before describing the algorithm in Section 2.3.

#### 2.2 Continuous and discrete wavelet transform, modulus maxima and the Mexican hat wavelet

In this section, the theories presented are taken from [Sch05], [RLAR+05] and [RLG08a].

The wavelet transform of a continuous time signal, x(t), is defined as

$$T(a,b) = \frac{1}{\sqrt{a}} \int_{-\infty}^{+\infty} x(t)\psi^*(\frac{t-b}{a})\delta t,$$

(2.1)

where  $\psi^*(t)$  is the complex conjugate of a wavelet function  $\psi(t)$ , *a* is the dilation parameter of the wavelet (also called the scale), and *b* is the location parameter of the wavelet.

Certain mathematical criteria has to be satisfied in order to be classified as a wavelet:

- 1 A wavelet must have a finite energy:  $E = \int_{-\infty}^{+\infty} |\psi(t)|^2 \, \delta t < \infty$

- 2 If  $\hat{\phi}(f)$  is the Fourier transform of  $\psi(t)$ , i.e.,  $\hat{\phi}(f) = \int_{-\infty}^{+\infty} \psi(t) e^{-i\omega t} \delta t$ , then the following condition must hold: the admissibility condition.

$$C_g = \int_0^{+\infty} \frac{\left|\hat{\phi}(\omega)\right|^2}{\omega} \delta\omega < \infty, \qquad (2.2)$$

where the wavelet has no zero frequency component.  $C_g$  is called the admissibility constant, and the value depends on the chosen wavelet.

3 For complex (or analytic) wavelets, the Fourier transform must both be real and vanish for negative frequencies.

The contribution to the signal energy at the specific scale a and location b is given by the two-dimensional wavelet energy density function known as the scalogram:

$$E(a,b) = |T(a,b)|^2$$

(2.3)

The contribution to the total energy distribution contained within the signal at a specific scale a is given by the integral of E(a, b) with respect to b. This is known as the wavelet variance, and can be used to find dominant scales associated with the signals. The total energy in the signal may be found from its wavelet transform as follows:

$$E = \frac{1}{C_g} \int_{-\infty}^{+\infty} \int_0^\infty \frac{1}{a^2} \left| T(a,b) \right|^2 \delta a \delta b$$

(2.4)

The Fourier transform is based on a continuous sinus signal as the reference signal. On the other hand, the wavelet transform implies, from the conditions above, that the reference signal (the mother wavelet) has a finite size. In addition, it is possible to use different reference signals as mother wavelets, i.e., the Mexican hat wavelet. The frequency parameter of the Fourier transform determines how the sinus signal is stretched over different frequencies, and in the wavelet transform, the stretching of the mother wavelet is done by changing the dilation parameter (the scale).

Wavelet modulus maxima is defined as:

$$\frac{\delta \left| T(a,b) \right|^2}{\delta b} = 0, \tag{2.5}$$

and it is used for locating and characterizing singularities in the signal. The CWT allows arbitrary high resolution in the time frequency plane, allowing each modulus maxima line to be followed with certainty across different scales.

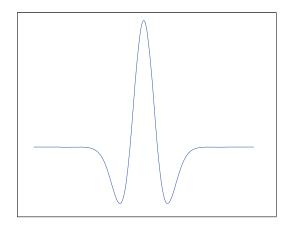

The Mexican hat wavelet is used as the mother wavelet ( $\psi(t)$  related to Equation 2.1) in the algorithm developed by Romero et al., and this wavelet is defined as the normalized (where b = 0 and a, c = 0 in Equation 2.7) negative of the second derivative of the Gaussian function. The equation is shown in Equation 2.6, and the shape is illustrated in Figure 2.5.

$$\psi(t) = (1 - t^2)e^{\frac{-t^2}{2}},\tag{2.6}$$

where the Gaussian function is the following:

$$f(t) = a \, e^{\frac{-(t-b)^2}{2C^2}} \tag{2.7}$$

Figure 2.5: The Mexican hat wavelet.

Another reason for using the Mexican hat wavelet is that the Mexican hat maxima lines are guarantied continuous across scales for singularities in the signal. The conversion from wavelet scale to wavelet frequency is given by:

$$f = \frac{f_c}{a \cdot \bigtriangleup t},\tag{2.8}$$

where a is the wavelet scale,  $f_c$  is a characteristic frequency of the wavelet,  $\Delta t$  is the sampling period ( $\Delta t = \frac{1}{f_s}$ , where fs is the sample frequency). For the Mexican hat wavelet, the characteristic frequency employed is the standard

For the Mexican hat wavelet, the characteristic frequency employed is the standard deviation of the power spectrum, given by  $f_c = \frac{\sqrt{\frac{5}{2}}}{2\pi} \approx 0.251$ .

#### 2.3 The beat detection algorithm

The CWT, as described in 2.2, is one of the building blocks in the algorithm developed by Romero et al. According to [RLAR<sup>+</sup>05], the QRS complex is part of the ECG signal that represents the greatest deflection from the baseline of the signal. Within the QRS complex, the R-wave ideally represents the positive peak. Therefore, many QRS detection algorithms try to detect the R-peak within the QRS complex. And the use of continuous maxima lines, from the modulus maxima described in Section 2.2, allows the R-wave to be followed much more accurately across frequencies in the time-frequency plane. The algorithm which will shortly be described, does not require pre-filtering, and is robust against interference signals such as electromyography (EMG) noise or movement artifacts. EMG is a technique for evaluating and recording the activation signal of muscles, and is performed using an instrument called an electromyograph, [Wik09b] and [RHY06]. The technique used in this algorithm could also be used to detect P and T waves within the ECG signal.

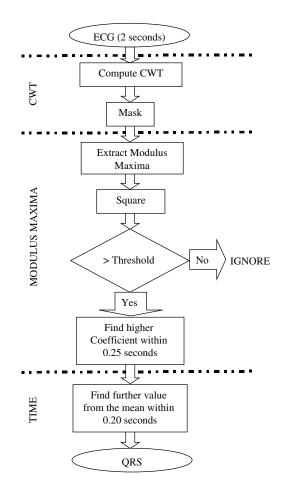

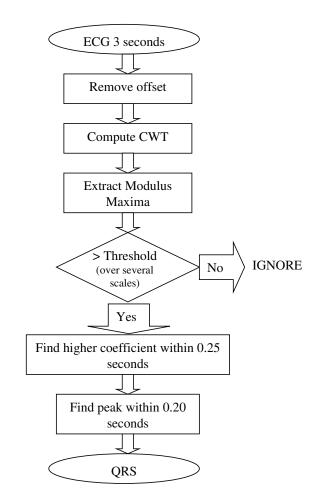

The schematic diagram of the algorithm is shown in Figure 2.6, and is described in [RLAR<sup>+</sup>05] as follows:

1 The ECG signal is analyzed within a two second window, as longer segments did not give satisfactory results. First, the CWT is calculated over this two second interval. It was then proved to work with the best performance when it operates within the frequency interval of 15-18 Hz. This frequency interval relates to the wavelet scales domain in Equation 2.8. Right after the computation of the CWT, a mask is applied

Figure 2.6: The algorithm developed by Romero et al., [RLAR<sup>+</sup>05].

to remove edge components of the result, which is set to be four times scale a of the wavelet. This mask has been found through trial and error.

- 2 In the second step, the modulus maxima of the CWT are extracted. The square of the the modulus is taken in order to emphasize the differences between coefficients. In addition, the maxima lines below a chosen threshold are ignored. The best threshold was found to be 30%.

- 3 The result from the previous step are taken to be possible R wave peaks. In order to separate the different peaks from each other, all modulus maxima points within an interval of 0.25 seconds of each other are analyzed in turn as search intervals. In every search interval, the point with the maximum coefficient value is selected as the R wave peak. The assumption in this step is that all the coefficients within each search interval of 0.25 seconds are due to the same QRS complex. Therefore, only the maximum point is chosen.

- 4 Finally, the algorithm finds the exact location of the peak in time-domain, based on the results from previous step. This is done by calculating the mean value of 0.10 seconds before and after the point detected in the wavelet domain. Then the point within the same interval of 0.2 seconds is located, where the signal is furthest from the mean. This step is necessary, because the modulus maxima line does not necessarily point to the exact location of the R wave peak in time domain.

This algorithm was tested for both positive and negative QRS complexes. In addition, the algorithm could cope with significant signal noise. Two comprehensive databases were used to test this algorithm. The MIT/BIH database and an in-house database recorded by Romero et al. within the Coronary Care Unit (CCU) at the Royal Infirmary of Edinburgh. How the sensitivity and the positive predictivity are calculated, as well as a description of the databases used in this thesis are given in Section 2.5. The results from the MIT/BIH database showed that the algorithm had a sensitivity 99.7% and a positive predictivity of 99.68%. The in-house database from the CCU resulted in 99.53% and 99.73%, respectively. However, these results were achieved from tests based on recordings done in hospitals. According to Romero et al. [RLG08a], the levels of noise and artefacts are therefore significantly lower than the levels recorded during ambulatory monitoring. For this reason, the algorithm is further optimized following the scheme as described above, but taking into account that the final application will be an ambulatory device. During the optimization of the algorithm, some changes were introduced, as described in [RLG08a]. These changes are presented in the next section.

#### 2.4 Optimization of the algorithm

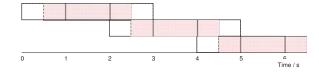

In [RLAR<sup>+</sup>05], the time window of input data to the algorithm is two seconds. During the implementation mentioned in [RLG08a], some preliminary tests resulted in some changes. It was determined that using windows of three seconds, and shifting the windows two seconds gave better results. In this case, the shifting would give a 0.5 second overlap with the previous window and again 0.5 second overlap with the next window. In order to avoid mismatches in the overlap sections, the detection in the first 0.5 seconds and the last 0.5 seconds within the window are ignored. Figure 2.7 illustrates this clearly. This was done in order to avoid boundary effects in the CWT computation. The optimization was mainly done in order to

Figure 2.7: Illustration of the overlap solution of the input to the algorithm, [RLG08a].

improve robustness to noise which is encountered under ambulatory monitoring conditions. This resulted in four optimizations of the original algorithm.

The first optimization was done in order to achieve better refinement in time domain, when searching for a specific point within the QRS complex. In theory, the general idea was to search around the detected beat to the nearest maximum. However, the unfiltered signal in time domain contains the full range of noise and artifacts. Five possible solutions were proposed in [RLG08a] to improve this issue. The chosen optimal solution was to search for the absolute maximum, and chose peaks close to the detected beat. This is done by multiplying the signal within the search interval with a Hanning window, given by Equation 2.9, [Wik08] and [CL93].

$$\omega(n) = 0.5 \left(1 - \cos(\frac{2\pi n}{N-1})\right),\tag{2.9}$$

where N is the total length of the signal and n is an integer with values from 0 to N-1. With this solution, the algorithm is able to detect the right peak, even if the negative component of the QRS complex is bigger than the positive peak. If a person suffers from premature ventricular contractions, the QRS complex might have opposite polarization. This is tackled well by the chosen solution.

The second optimization to the algorithm was done in the calculation of the threshold. Since the modulus maxima relates the peak detection to the maximum value within a search interval, it would be very sensitive to peaks in the CWT domain. From diseases or noise, peaks can occur easily. Therefore, a more robust threshold detection is desired. In [RLG08a], this is done by running average threshold, where the new threshold is partly determined as a percentage of the current maximum and partly on previous thresholds. This is identical to implementing a threshold feedback to the algorithm, in order to adjust the threshold. From [RLG08a], the formula for the threshold is given in Equation 2.10.

$$T = (1 - \mu)T_{old} + \mu T_{new}, \qquad (2.10)$$

where  $T_{new}$  is defined as

$$T_{new} = Carg \max_{w,s} |\mathbf{w}_{\mathbf{s}}| \tag{2.11}$$

Here,  $\mu$  represents the "forget rate", a value which could, according to Romero et al. [RLG08a], be equal to the constant 1/8 or 1/4. The vector  $\mathbf{w}_{s}$  represents the wavelet coefficients on a chosen scale s, and C is a constant fraction that relates the absolute maximum coefficient value to a threshold value.  $T_{old}$  is the previous threshold value. Different values for  $\mu$  was tested in [RLG08a], and resulted in a trade-off between two considerations. For high values of  $\mu$ , the algorithm is sensitive to impulsive noise, and too low values of  $\mu$  will lead to smearing of artifacts over a long period of time. Based on these considerations, the value of  $\mu$  was decided to be 0.5.

The third optimization was the removal of the squaring of the modulus maxima of the CWT. The squaring turned out not to give any actual improvements in the signals tested.

According to Romero et al. [RLG08a], if the threshold is exceeded in one scale in the initial algorithm, then this beat will be analyzed further, and there is only one threshold for all scales (see Equation 2.11). This solution will increase the probability of false detections if the number of scales is increased. The solution to this problem was to require the threshold to be exceeded in at least N out of K scales. In addition, the threshold is determined individually in each scale, giving a new equation for calculating  $T_{new}$ . This is given in Equation 2.12, [RLG08a].

$$T(s)_{new} = Carg \max_{\mathbf{w}} |\mathbf{w}_{\mathbf{s}}| \tag{2.12}$$

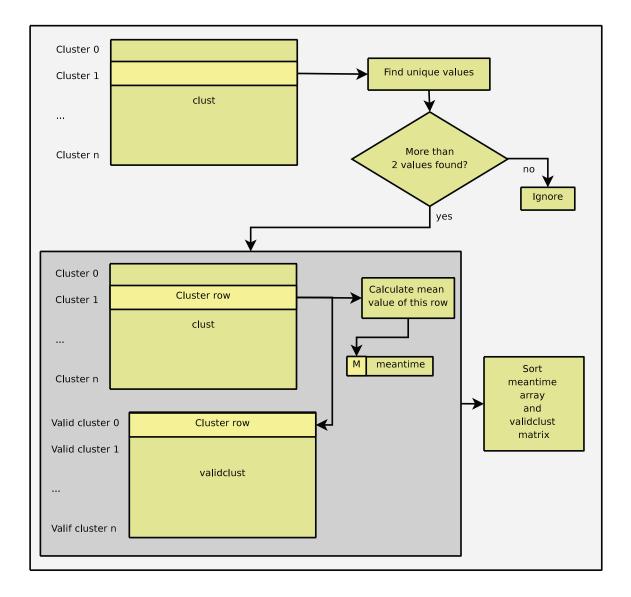

The implementation of this new threshold is described as follows (from [RLG08a]):

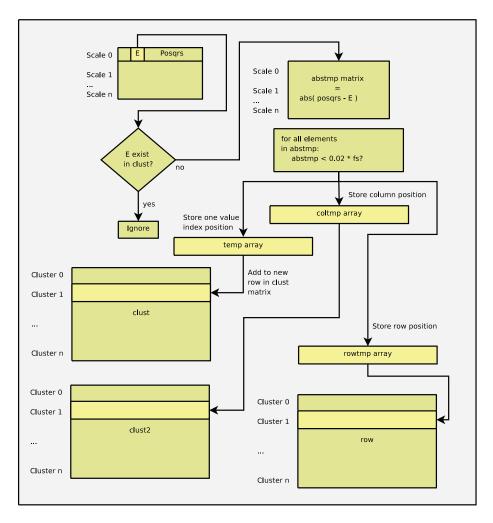

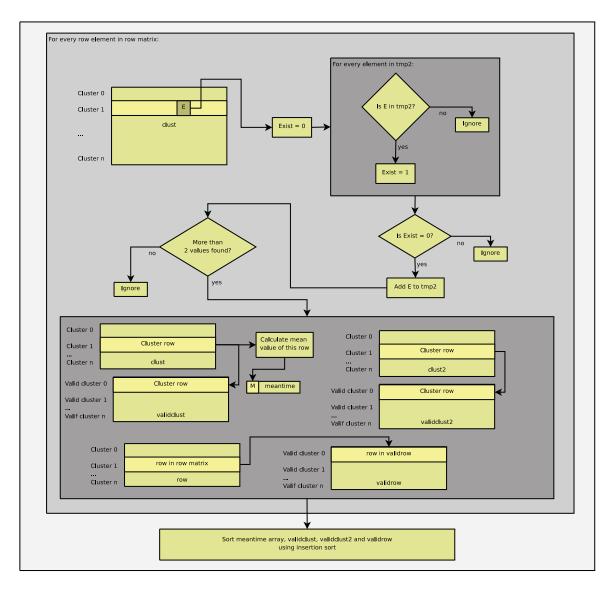

- 1 From all detected beats in all scales, clusters of beats are defined. This is done by clustering all beats within a 0.02 second time frame.

- 2 For each cluster, it is verified whether or not the beats have been detected in N out of K scales. If not, then the cluster is not analyzed any further.

From the conditions, the best results were given with N = 2 and K = 4, at a threshold of 30%.

The testing of this optimized algorithm resulted in a sensitivity of 99.68% and a positive predictivity of 99.75% on the MIT/BIH database. The results from the database created by IMEC-NL gave a sensitivity and a positive predictivity over 99.5% in most of the signals. The noise tests from the IMEC database gave satisfactory results for SNRs from 0 dB and above. Romero et al. [RLG08a] concluded from the noise tests that a key system requirement

for robust ECG beat detection is that monitoring hardware (mainly the amplification and signal conditioning stages of the system) shall provide a signal characterized by a SNR of 0 dB or above. As long as this condition is met, the optimized algorithm would achieve reliable beat detection.

The updated schematic diagram of the algorithm after the optimizations is shown in Figure 2.8.

Figure 2.8: The algorithm after the optimization done in [RLG08a].

#### 2.5 The test databases

In this section, the test databases used for the validation of the application in this project are described. The databases used are the MIT/BIH database and a recorded database done by IMEC-NL. Section 2.5.1 describes the MIT/BIH database, and in Section 2.5.2, the database recorded by IMEC-NL is presented.

#### 2.5.1 The MIT/BIH database

One of the most common databases used for testing beat detection algorithms is the MIT/BIH database. According to Goldberger et al. [GAG<sup>+</sup>13] and Romero et al. [RLG08a], the MIT/BIH database contains recordings of ECG signals done in laboratories at Boston's Beth

Israel Hospital with the support from MIT since 1975. These recordings include several datasets for different test purposes, e.g., the Arrhythmia database which is among the test signals used in this thesis. As mentioned in [GAG<sup>+</sup>13] and [RLG08a], the MIT/BIH Arrhythmia Database contains several half-hour excepts of two-channel ambulatory ECG recordings, obtained from 47 subjects studied by the BIH Arrhythmia Laboratory between 1975 and 1979. 23 recordings were chosen at random from a set of 4000 24-hour ambulatory ECG recordings collected from patients at Boston's Beth Israel Hospital. 25 other signals were selected to include a variety of clinically relevant phenomena. All signals are numbered and the signals from the ambulatory recordings are labeled with numbers below 125, while the rest of the signals are labeled with the number 200 and higher. All signals used from this database are listed in Table 2.1. All signals have been digitalized at 360 Hz. For more information about the database, the reader is referred to [pyn], where the database is publicly available.

| MIT/BIH  |     |  |

|----------|-----|--|

| database |     |  |

| 100      | 202 |  |

| 101      | 203 |  |

| 102      | 205 |  |

| 103      | 208 |  |

| 104      | 209 |  |

| 105      | 210 |  |

| 106      | 212 |  |

| 107      | 213 |  |

| 118      | 214 |  |

| 119      | 215 |  |

| 200      | 217 |  |

| 201      | 219 |  |

Table 2.1: Chosen signals from the MIT/BIH database.

#### 2.5.2 The database recorded by IMEC-NL

IMEC-NL also recorded a set of ECG signals in order to test the algorithm under different levels of activity that produce noise and motion artifacts. The database consisted of recordings from ten volunteers, with three levels of activity; low, medium and high level of activity. The low level consisted of work, sitting at a desk, the medium level was performed by riding a static bike at 70 RPM and 100 Watts. The high level of activity was recorded by running on a treadmill at 7.5 Km/h. For these recordings, a belt and a textile patch was used. The number of recordings used in each case of activity are listed in Table 2.2. These signals were sampled with 198 samples per second.

|      | Belt | Textile Patch |

|------|------|---------------|

| Work | 10   | 10            |

| Bike | 10   | 4             |

| Run  | 8    | 3             |

Table 2.2: Number of recordings in the IMEC ECG database, [RLG08a].

In addition, signal 100 from the MIT/BIH database was selected as the base signal for the noise test. It has a clean ECG signal, and noise was added gradually to that signal for different SNRs, from 10 dB to -10 dB (in steps of one). This test is similar to the MIT-BIH Noise Stress Test Database, which could also be found in [pyn].

In order to test accuracy, an exact peak test was also created. This test contained three ECG signals, with two different sampling frequencies (198 Hz and 1000 Hz). The output from this test is the percentage of correctly detected beats at its peak, the average distance from the accurate beat, standard deviation from the average distance, and total number of beats which was wrongly detected.

The MIT/BIH and IMEC databases were embedded in a Matlab script using Matlab binaries. Usually, the parameters used to compare beat detection algorithms are sensitivity and positive predictivity of the result for each test signal. The sensitivity is defined as shown in Equation 2.13.

$$Se = \frac{TP}{TP + FN} \quad , \tag{2.13}$$

where TP stands for true positives (correctly detected beats), and FN stands for false negatives (missed beats).

The positive predictivity is shown in Equation 2.14.

$$+P = \frac{TP}{TP + FP} \quad , \tag{2.14}$$

where FP are false positives (wrongly detected beats). All database signals are annotated, compared to the result of the algorithm. A beat is in this case defined to be correctly detected if there is an annotated beat within a certain time window around the detected beat. This time window is set to be +/-100 ms. These values are percentages in the range between 0% and 100%. An ideal algorithm would maximize these two parameters. Therefore the sensitivity and positive predictivity are summed together in a unique parameter to be maximized (Se + +P), where the range is from 0% to 200%. The results of the evaluation tests are stored in a text file produced by the matlab script.

## Chapter 3

# Energy-efficient software and hardware development

This chapter will provide some background theory related to energy-efficient software and hardware development in embedded systems.

In recent years, power consumption has been an important topic in embedded systems design. According to Russell et al. [RJ98], the power consumption places requirements on heat dissipation, which directly affect unit cost. Furthermore, in portable systems, the minimization of energy consumption, and the time integral of power, is critical to extending battery lifetime.

Since battery power density is increasing only at a rate of approximately 5% per year, any significant extension of battery lifetime must come from a thorough improvement of energy efficiency for each power-hungry component in a system, [CHC06].

Ultra low power or energy-efficient design refers to, in this thesis, the minimization/reduction of power and/or energy dissipation in the design, resulting in an optimal solution for a specific application.

An electronic system usually consist of a hardware platform, executing system, and a software application. In energy-efficient design, the reduction of power dissipation must be done in all parts of the design. Three major constituents consuming significant energy in hardware platforms are mentioned in [BDM00]. These are computational units, communication units, and storage units. The choices for software implementation also affect the energy consumption in those hardware components. Compilation of the software affects the instructions used by computing elements. Moreover, software storage and data accesses in memory affect energy balance, and data representation (i.e., special variables, encoding) affects power dissipation of communication resources (e.g., buses). Tackling power dissipation in every design stage is therefore important since both software and hardware platforms affect the power consumption.