# A digital audio playback system with USB interface

Espen Karlsen Magne Tørresen

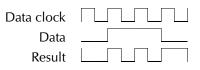

Master of Science in ElectronicsSubmission date: June 2009Supervisor:Trond Ytterdal, IETCo-supervisor:Knut Øystein Lauvland, Doxa

Norwegian University of Science and Technology Department of Electronics and Telecommunications

### **Problem Description**

The audio and music industry as a whole is going through a change towards more computerized playback systems. Today it is not uncommon to have a private music library organized on a personal computer or a media device instead of a large collection of CDs. High quality audio tracks can be downloaded directly from the internet. It is therefore desireable to be able to play back these tracks on a hifi-system with a minimal loss of quality.

The main purpose of the project is to create a high performance audio digital to analog converter (DAC) system, which can retrieve data via a USB connection. The DAC should be followed by an appropriate filter and preamplifier to directly connect to a power amplifier. Also, a digital control of source selection and analog volume circuitry should be implemented. The system should support high quality audio formats, up to 192 kHz sampling frequency with 24 bit resolution.

A modular design allows for a separate decoder for various audio formats retrieved over USB, either as a sound card or as a standalone audio player.

Assignment given: 23. January 2009 Supervisor: Trond Ytterdal, IET

#### Abstract

A high performance sound card is designed and implemented using a USB enabled microcontroller and an external dataconverter. Data is retrieved either via USB or S/PDIF. The sampling clock is generated by a precision clock synthesizer. This is programmable and can be adapted to different sampling rates of USB data. The system supports 24 bit, 192 kHz audio.

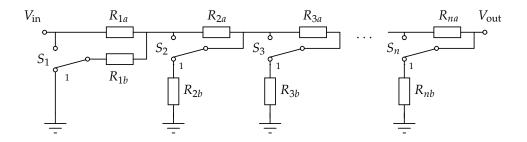

Signal attenuation is performed through a relay based stepped voltage divider with constant output impedance. 64 dB attenuation in steps of 1 dB is available.

An extensive power supply is made to support the range of required voltages. The signal to noise ratio of the power supply was measured to be 93 dB in the audio frequency band.

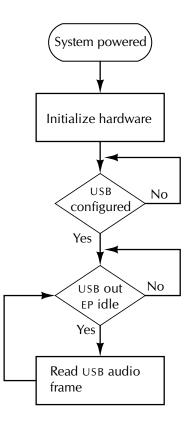

The microcontroller has been programmed to handle the USB communication and provision of control signals for the system.

The whole system is assembled on PCBS and tested. The audio performance measurements show a dynamic range of 105 dB, measured at the system output in a noisy environment. The total harmonic distortion plus noise was 0.0011 %.

## Contents

| Ac | Acronyms and abbreviations |                                         | ix |  |

|----|----------------------------|-----------------------------------------|----|--|

| 1  | Intro                      | oduction                                | 1  |  |

|    | 1.1                        | Motivation                              | 1  |  |

|    | 1.2                        | Objective                               | 2  |  |

|    | 1.3                        | System overview                         | 2  |  |

|    | 1.4                        | Report outline                          | 3  |  |

| 2  | The                        | ory                                     | 5  |  |

|    | 2.1                        | Dataconverters                          | 5  |  |

|    | 2.2                        | Power supply                            | 13 |  |

|    | 2.3                        | Noise                                   | 18 |  |

|    | 2.4                        | Printed circuit boards                  | 22 |  |

|    | 2.5                        | The Universal Serial Bus                | 23 |  |

| 3  | Imp                        | lementation                             | 27 |  |

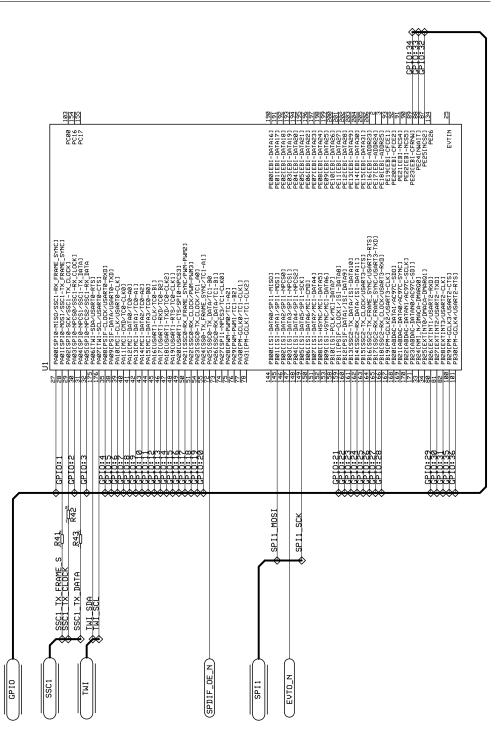

| -  | 3.1                        | Microcontroller                         | 27 |  |

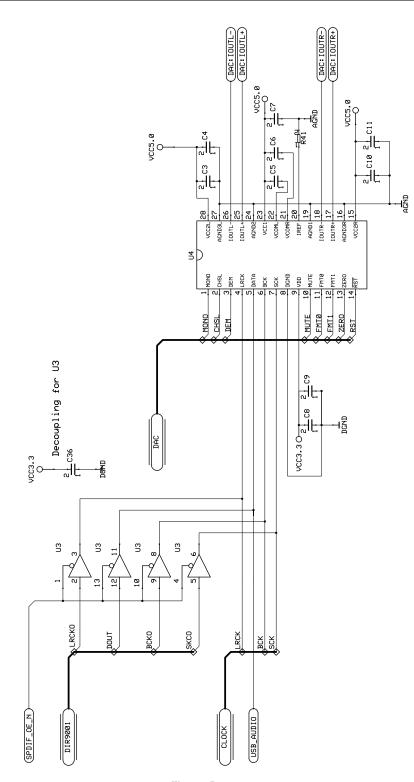

|    | 3.2                        | DAC                                     | 28 |  |

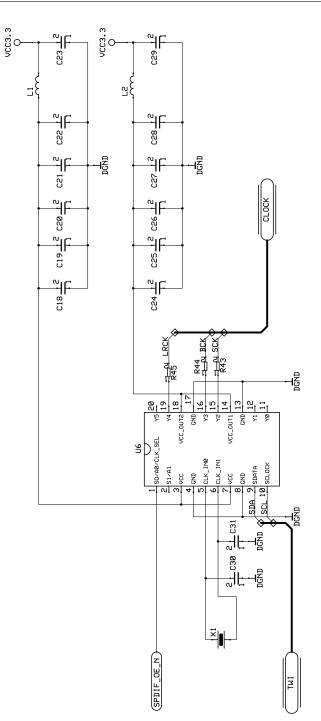

|    | 3.3                        | DAC clock                               | 29 |  |

|    | 3.4                        | DAC reconstruction filter               | 31 |  |

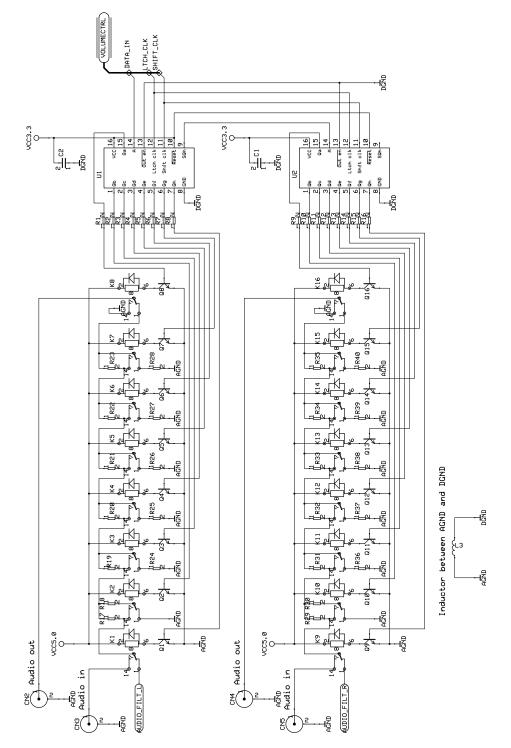

|    | 3.5                        | Attenuator                              | 32 |  |

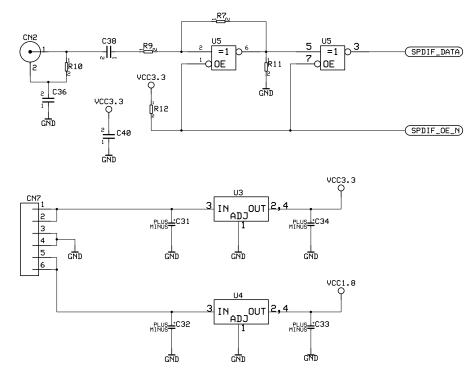

|    | 3.6                        | Sony/Philips digital interface (S/PDIF) | 34 |  |

|    | 3.7                        | User interface hardware                 | 38 |  |

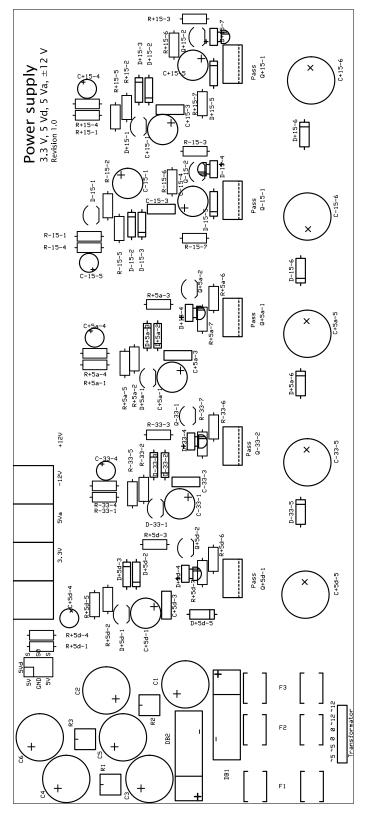

|    | 3.8                        | Power supply                            | 38 |  |

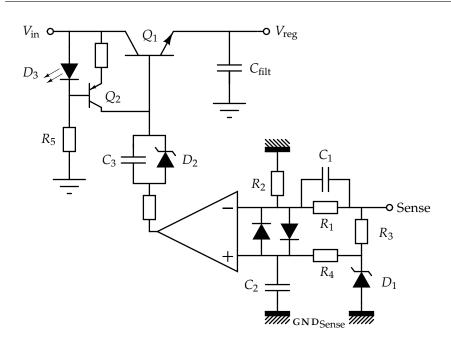

|    | 3.9                        | Prototyping                             | 41 |  |

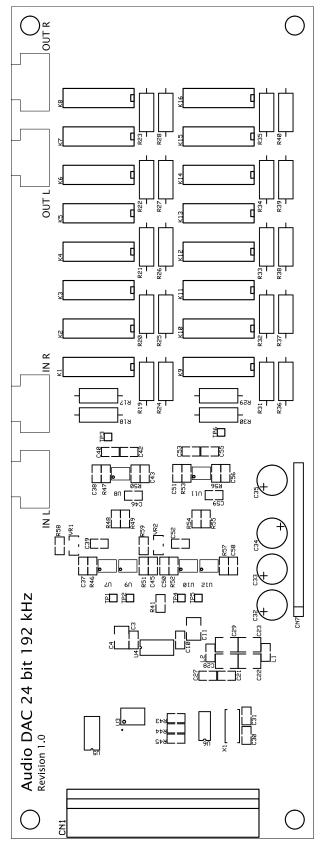

|    | 3.10                       | Printed circuit boards                  | 43 |  |

|    | 3.11                       | Firmware                                | 43 |  |

|    | 3.12                       | Final system                            | 47 |  |

| 4           | Test methodology                                                                                                                                                                                                                                                                                                                                                        | 49                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|             | 4.1 Test equipment                                                                                                                                                                                                                                                                                                                                                      | • 49                                                                                               |

|             | 4.2 Dataconverter                                                                                                                                                                                                                                                                                                                                                       | • 49                                                                                               |

|             | 4.3 Clock jitter                                                                                                                                                                                                                                                                                                                                                        | . 50                                                                                               |

|             | 4.4 Reconstruction filter                                                                                                                                                                                                                                                                                                                                               | . 51                                                                                               |

|             | 4.5 Power supply                                                                                                                                                                                                                                                                                                                                                        | . 51                                                                                               |

| 5           | Results                                                                                                                                                                                                                                                                                                                                                                 | 53                                                                                                 |

| •           | 5.1 Dataconverter                                                                                                                                                                                                                                                                                                                                                       |                                                                                                    |

|             | 5.2 Clock generator                                                                                                                                                                                                                                                                                                                                                     |                                                                                                    |

|             | 5.3 Reconstruction filter                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

|             | 5.4 Power supply                                                                                                                                                                                                                                                                                                                                                        | . 61                                                                                               |

| 6           | Discussion                                                                                                                                                                                                                                                                                                                                                              | 65                                                                                                 |

|             | 6.1 System solution                                                                                                                                                                                                                                                                                                                                                     | -                                                                                                  |

|             | 6.2 Dataconverter and filter performance                                                                                                                                                                                                                                                                                                                                | -                                                                                                  |

|             | 6.3 Clock                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

|             | 6.4 Power supply                                                                                                                                                                                                                                                                                                                                                        | . 68                                                                                               |

|             | 6.5 Printed circuit board layout                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

| 7           | Conclusions                                                                                                                                                                                                                                                                                                                                                             | 73                                                                                                 |

|             | 11                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| Aţ          | opendices                                                                                                                                                                                                                                                                                                                                                               | 75                                                                                                 |

| -           | -                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                    |

| -           | Source code                                                                                                                                                                                                                                                                                                                                                             | 77                                                                                                 |

| -           | -                                                                                                                                                                                                                                                                                                                                                                       | . 77                                                                                               |

| A           | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation                                                                                                                                                                                                                                                                          | 77<br>· 77<br>· 79                                                                                 |

| -           | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics                                                                                                                                                                                                                                                       | 77<br>. 77<br>. 79<br>81                                                                           |

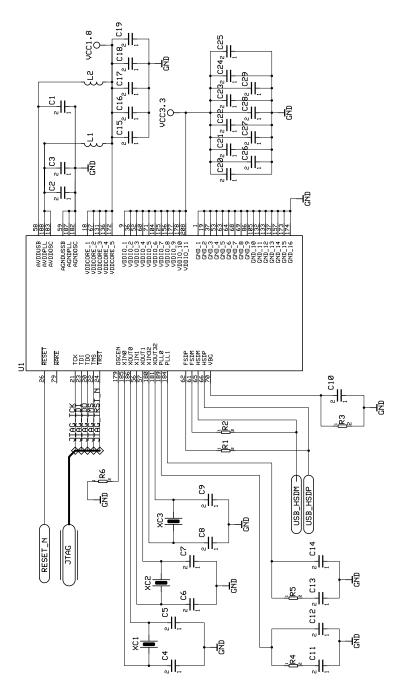

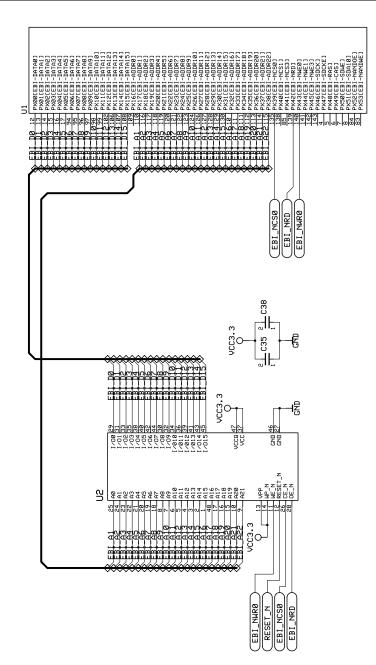

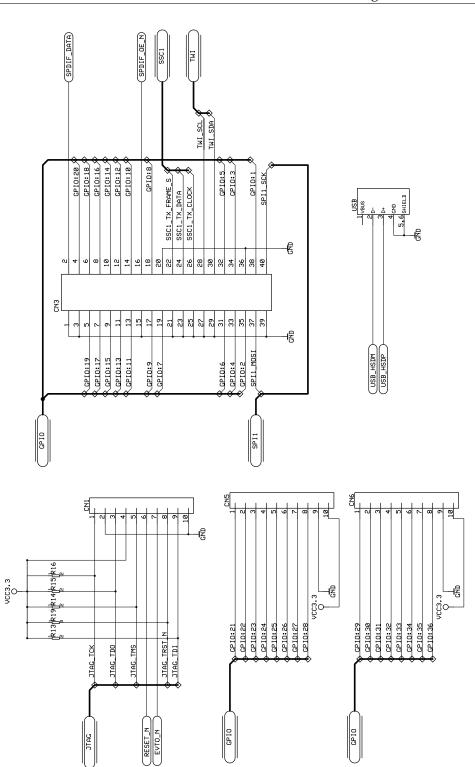

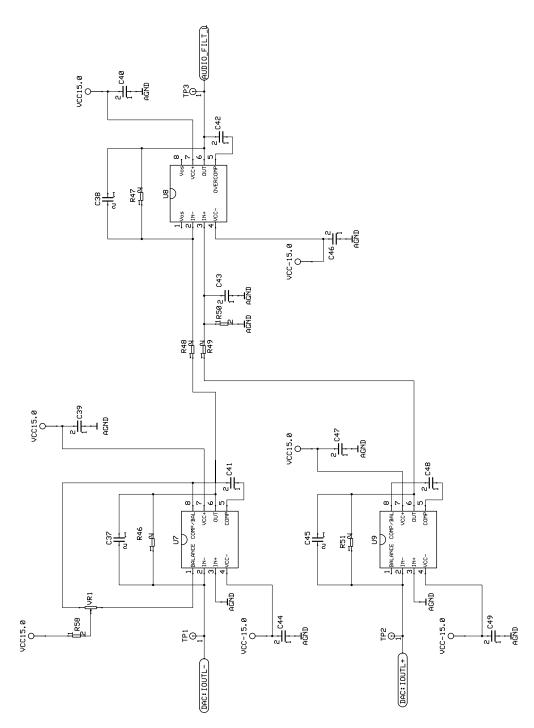

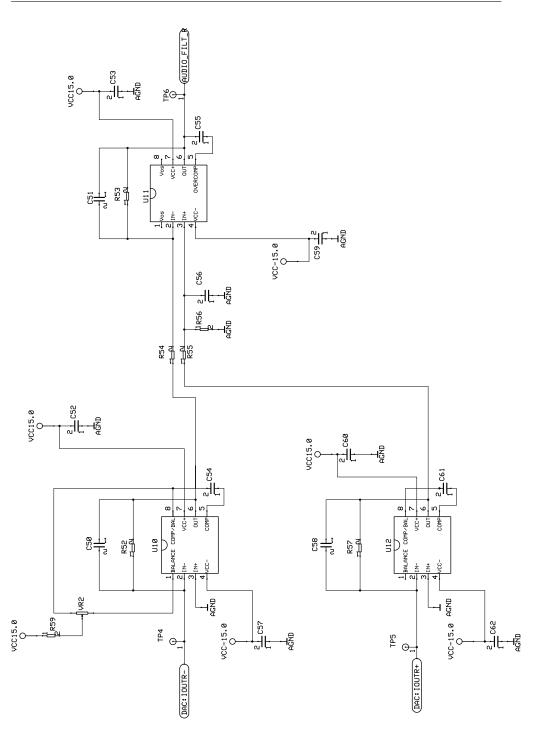

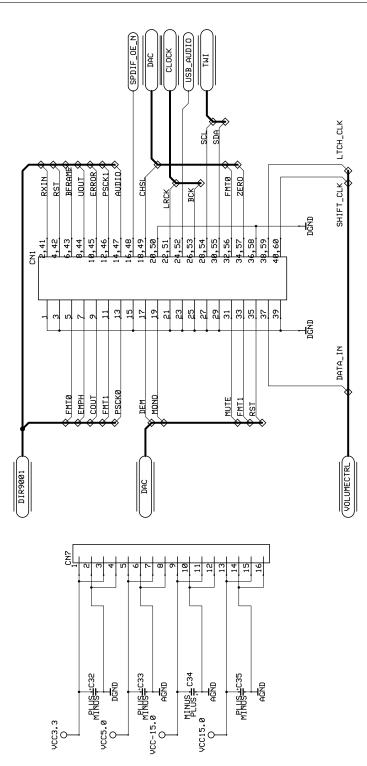

| A           | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit                                                                                                                                                                                                                      | 77<br>. 77<br>. 79<br>. 81                                                                         |

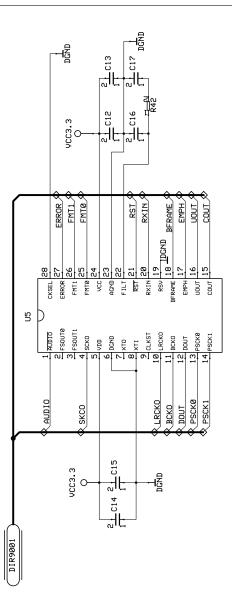

| A           | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit                                                                                                                                                                                                                      | 77<br>- 77<br>- 79<br>81<br>- 81<br>- 86                                                           |

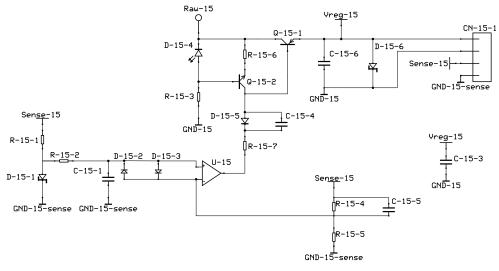

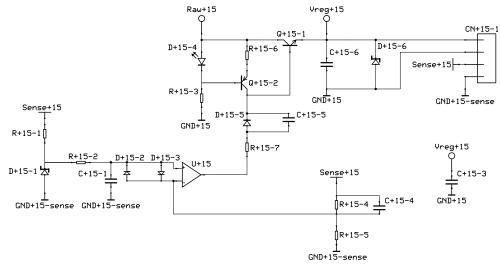

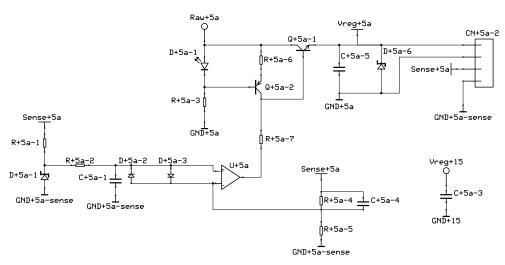

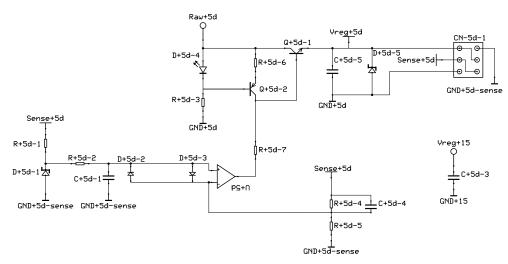

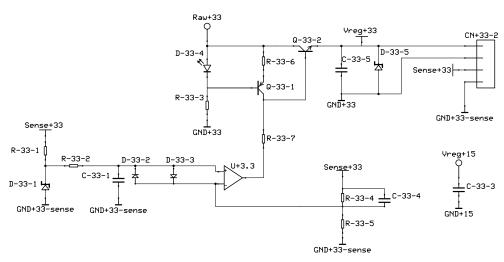

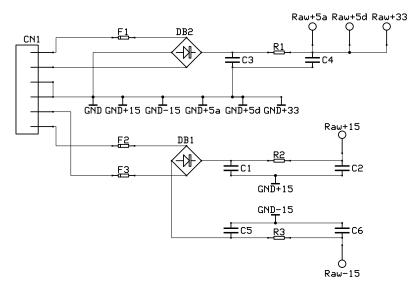

| A<br>B      | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit                                                                                                                                                                   | 77<br>77<br>77<br>79<br>81<br>. 81<br>. 86<br>. 93                                                 |

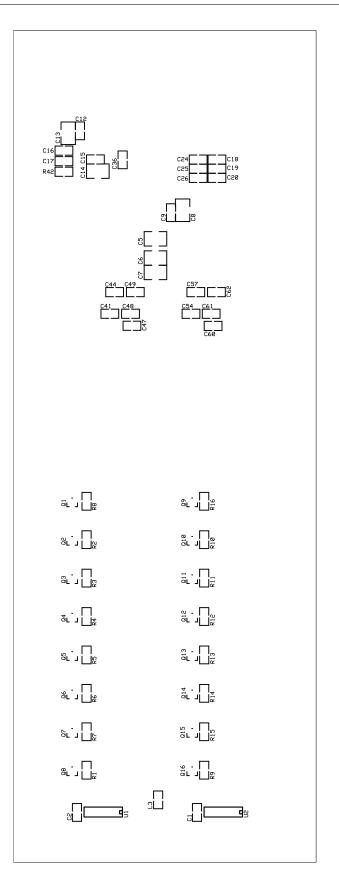

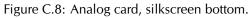

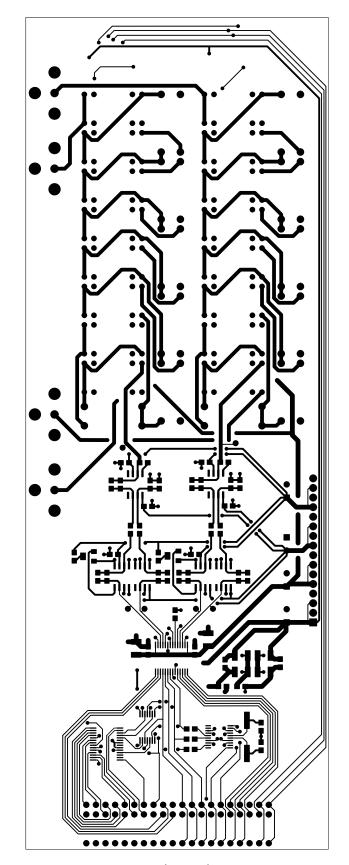

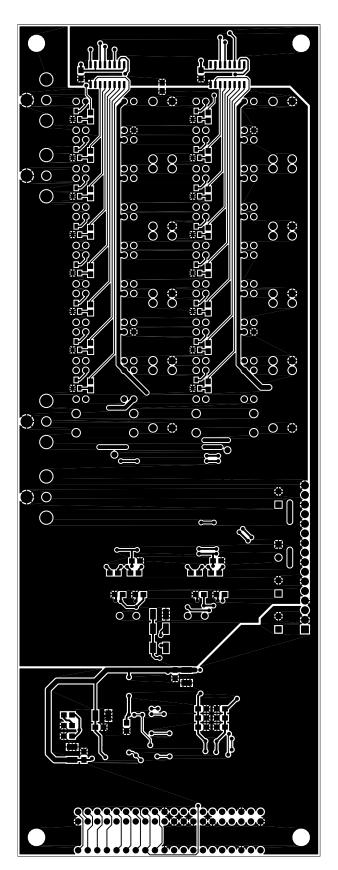

| A<br>B      | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit         PCB layout                                                                                                                                                | 77<br>77<br>77<br>79<br>81<br>81<br>86<br>93<br>97                                                 |

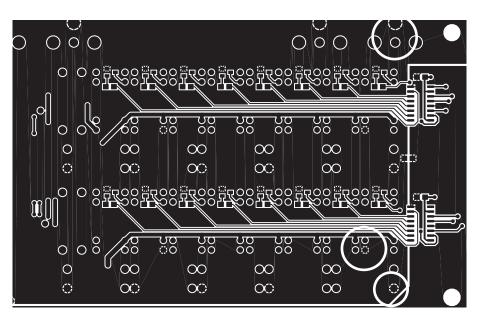

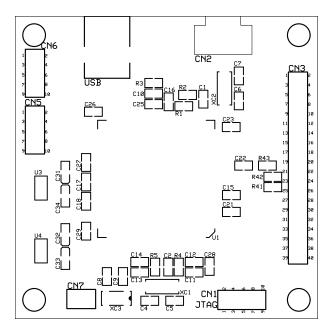

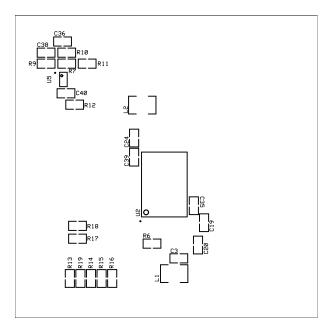

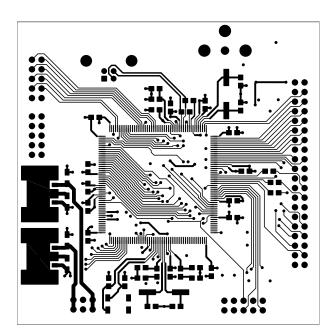

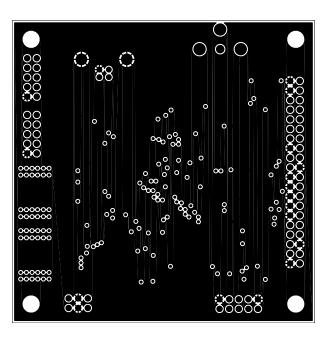

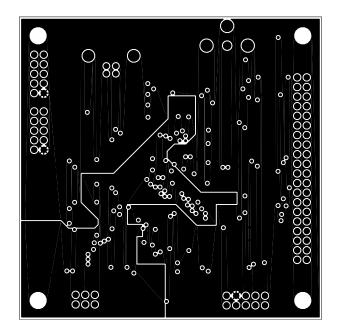

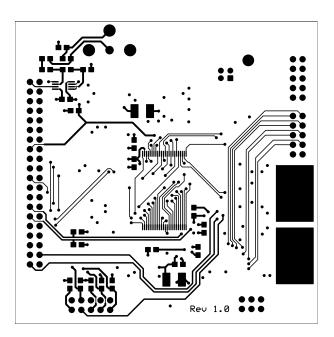

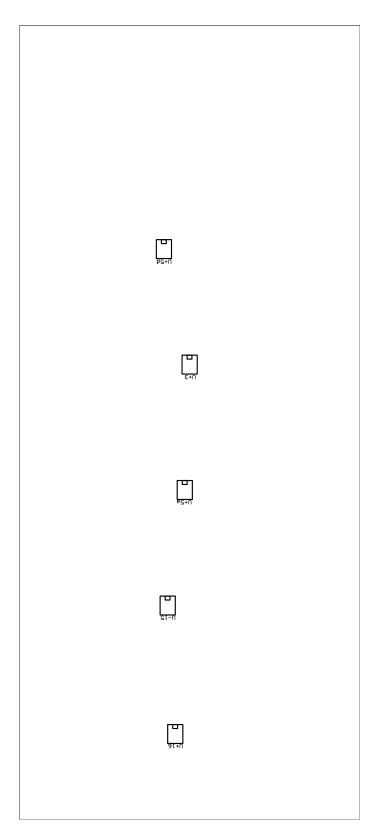

| A<br>B      | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit         PCB layout         C.1 Digital control unit                                                                                                               | 77<br>77<br>79<br>81<br>81<br>86<br>93<br>97<br>97                                                 |

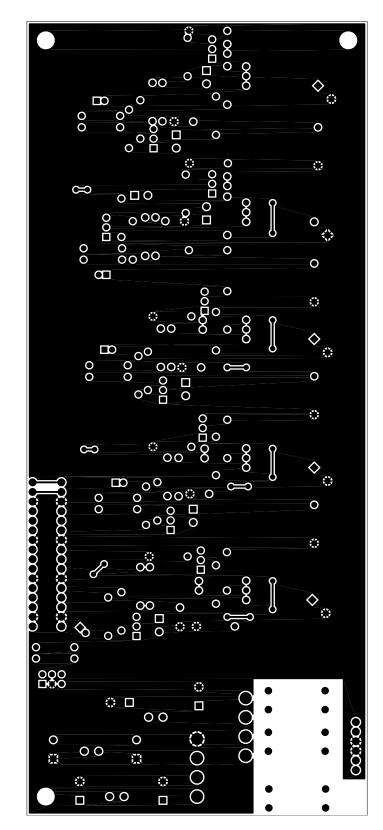

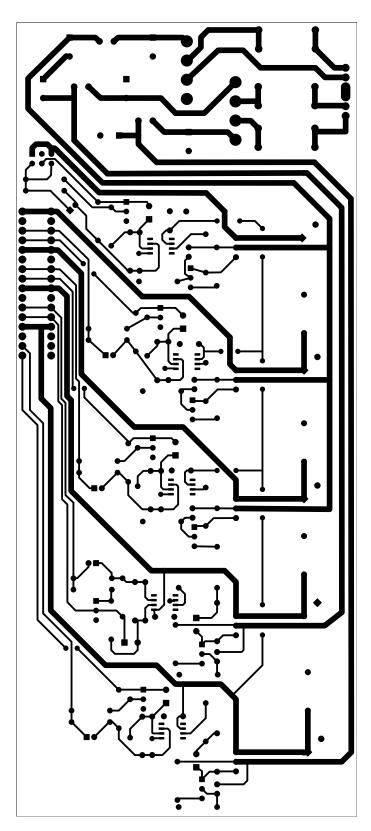

| A<br>B      | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit         PCB layout                                                                                                                                                | 77<br>77<br>79<br><b>81</b><br>81<br>86<br>93<br><b>97</b><br>97<br>101                            |

| A<br>B<br>C | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit         PCB layout         C.1 Digital control unit         C.2 DAC unit         C.3 Power supply unit                                                            | 77<br>77<br>79<br>81<br>81<br>81<br>86<br>93<br>97<br>97<br>97<br>101<br>105                       |

| A<br>B<br>C | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit         PCB layout         C.1 Digital control unit         C.2 DAC unit         C.3 Power supply unit         Bill of materials                                  | 77<br>77<br>79<br>81<br>81<br>86<br>93<br>97<br>97<br>101<br>105<br>109                            |

| A<br>B<br>C | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit         PCB layout         C.1 Digital control unit         C.2 DAC unit         C.3 Power supply unit         Bill of materials         D.1 Digital control unit | 77<br>77<br>77<br>79<br><b>81</b><br>81<br>86<br>93<br>97<br>97<br>101<br>105<br><b>109</b><br>109 |

| A<br>B<br>C | Source code         A.1 Resistor value calculation         A.2 Fourier coefficient calculation         Schematics         B.1 Digital control unit         B.2 DAC unit         B.3 Power supply unit         PCB layout         C.1 Digital control unit         C.2 DAC unit         C.3 Power supply unit         Bill of materials                                  | 77<br>77<br>79<br>81<br>81<br>81<br>86<br>93<br>97<br>97<br>101<br>105<br>109<br>109<br>111        |

# Acronyms and abbreviations

This section describes various acronyms and abbreviations used throughout the text.

| AC               | Alternating Current                         |

|------------------|---------------------------------------------|

|                  |                                             |

| ADC              | Analog to Digital Converter                 |

| AES              | Audio Engineering Society                   |

| AES/EBU          | A digital audio interface                   |

| AKM              | Asahi Kasei Microdevices Corporation        |

| AUX              | Auxiliary                                   |

| BPM              | Bi-Phase Mark                               |

| BGA              | Ball Grid Array                             |

| CAD              | Computer Aided Design                       |

| CD               | Compact Disc                                |

| CFI              | Common Flash Interface                      |

| DAC              | Digital to Analog Converter                 |

| DC               | Direct Current                              |

| DR               | Dynamic Range                               |

| EBU              | European Broadcast Union                    |

| EIAJ             | Electronic Industries Associations of Japan |

| EP               | Endpoint (USB terminology)                  |

| ENOB             | Effective Number Of Bits                    |

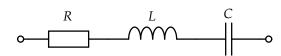

| ESL              | Equivalent Series Inductance                |

| ESR              | Equivalent Series Resistance                |

| FIFO             | First In, First Out (Buffer topology)       |

| FS               | Full Scale                                  |

| FSK              | Frequency Shift Keying                      |

| HID              | Human Interface Device                      |

| нw               | Hardware                                    |

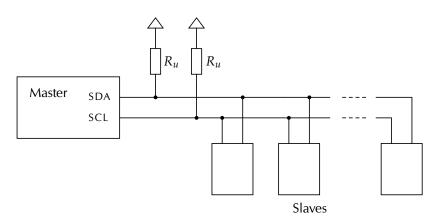

| I <sup>2</sup> C | Inter-Integrated Circuit bus                |

| IO               | Input/Output                                |

|                  | 1 1                                         |

#### Acronyms and abbreviations

| IRQInterrupt RequestJEIDAJapan Electronic Industry Development AssociationJEITAJapan Electronics and Information Technology Industries<br>Association (Merger of former ELAJ and JEIDA)LCDLiquid Crystal DisplayLEDLight Emitting DiodeLPCMLight Emitting DiodeLPCMLight Emitting DiodeLSBLeast Significant BitMACMedia Access ControllerMosMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (US B terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockScLSMBUS clock lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Corpus Serial CommunicationS/PDIFSony/Philips digital interfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise </th <th>ICOR</th> <th>Inverted Complementary Offset Binary code</th> | ICOR   | Inverted Complementary Offset Binary code              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------|

| JEIDAJapan Électronic Industry Development AssociationJEITAJapan Electronics and Information Technology Industries<br>Association (Merger of former EIAJ and JEIDA)LCDLiquid Crystal DisplayLEDLight Emitting DiodeLPCMLinear Pulse Code ModulationLSBLeast Significant BitMACMedia Access ControllerMOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPTOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSOFStart Of Frame (USB terminology)SFDRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSFDRSpurious Free Dynamic RangeSFDSerial Corpy Anagement BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSFDSerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIF <t< td=""><td></td><td></td></t<>                                                  |        |                                                        |

| JEITAJapan Electronics and Information Technology Industries<br>Association (Merger of former ELAJ and JEIDA)LCDLiquid Crystal DisplayLEDLight Emitting DiodeLPCMLinear Pulse Code ModulationLSBLeast Significant BitMACMedia Access ControllerMosMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS dota lineSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                      | -      |                                                        |

| Association (Merger of former FIAJ and JEIDA)LCDLiquid Crystal DisplayLEDLight Emitting DiodeLPCMLinear Pulse Code ModulationLSBLeast Significant BitMACMedia Access ControllerMOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                       |        |                                                        |

| LCDLiquid Crystal DisplayLEDLight Emitting DiodeLPCMLinear Pulse Code ModulationLSBLeast Significant BitMACMedia Access ControllerMOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                           | JEIIA  |                                                        |

| LEDLight Emitting DiodeLPCMLinear Pulse Code ModulationLSBLeast Significant BitMACMedia Access ControllerMOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                      | I CD   |                                                        |

| LPCMLinear Pulse Code ModulationLSBLeast Significant BitMACMedia Access ControllerMOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPILPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDAsMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSFISerial Peripheral InterfaceSRCSom/CPSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                         |        | 1 5 15                                                 |

| LSBLeast Significant BitMACMedia Access ControllerMOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionP10Programmable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSFISerial Peripheral InterfaceSRCSonrceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                  |        | 8                                                      |

| MACMedia Access ControllerMOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |                                                        |

| MOSMetal Oxide SemiconductorMSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPILPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | 8                                                      |

| MSBMost Significant BitMSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionP10Programmable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                                        |

| MSOFMicro Start Of Frame (USB terminology)NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionP10Programmable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSon/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                                        |

| NANDNegating Boolean ANDOEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPI0Programmable Input/OutputPLLPhase Locked LoopPPPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        | 8                                                      |

| OEOutput EnablePCPersonal ComputerPCMPulse Code ModulationPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopPPPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMRUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |                                                        |

| PCPersonal ComputerPCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopPPPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NAND   | 0 0                                                    |

| PCMPulse Code ModulationPCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSDASerial Copy Management SystemSDASignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OE     | -                                                      |

| PCBPrinted Circuit BoardPDFProbability Density FunctionPIOProgrammable Input/OutputPIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PC     | -                                                      |

| PDFProbability Density FunctionPIOProgrammable Input/OutputPILPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMSUS data lineSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | РСМ    |                                                        |

| PIOProgrammable Input/OutputPLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | РСВ    |                                                        |

| PLLPhase Locked LoopP-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSonrceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PDF    | 5                                                      |

| P-PPeak to PeakPSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PIO    | · · ·                                                  |

| PSRRPower Supply Rejection RatioPSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PLL    | Phase Locked Loop                                      |

| PSUPower Supply UnitRMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | P-P    | Peak to Peak                                           |

| RMSRoot Mean SquareRTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PSRR   | Power Supply Rejection Ratio                           |

| RTCReal Time ClockSCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PSU    | Power Supply Unit                                      |

| SCLSMBUS clock lineSCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RMS    | Root Mean Square                                       |

| SCMSSerial Copy Management SystemSDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RTC    | Real Time Clock                                        |

| SDASMBUS data lineSMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SCL    | sмвus clock line                                       |

| SMBUSSystem Management BusSNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SCMS   | Serial Copy Management System                          |

| SNRSignal to Noise RatioSOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SDA    | sмвus data line                                        |

| SOFStart Of Frame (USB terminology)SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SMBUS  | System Management Bus                                  |

| SFDRSpurious Free Dynamic RangeSPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | SNR    | Signal to Noise Ratio                                  |

| SPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SOF    | Start Of Frame (USB terminology)                       |

| SPISerial Peripheral InterfaceSRCSourceSSCSynchronous Serial CommunicationS/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SFDR   | Spurious Free Dynamic Range                            |

| sscSynchronous Serial Communications/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SPI    |                                                        |

| S/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SRC    | Source                                                 |

| S/PDIFSony/Philips digital interfaceTHD+NTotal Harmonic Distortion plus Noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SSC    | Synchronous Serial Communication                       |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | S/PDIF | •                                                      |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | THD+N  |                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TWI    | Two Wire Interface (Atmel's implementation of $1^2$ C) |

| USB Universal Serial Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | USB    | -                                                      |

### Chapter 1

### Introduction

$T^{\rm HIS\ THESIS}$  is written in fulfillment of the degree of master of science in electrical engineering at the Norwegian university of science and technology. The work has been done in the spring of 2009, in the last semester of a five-year master program.

#### 1.1 Motivation

The area of home audio systems is in a state of change. The time of the large physical record collections is on the wane, and music libraries contained in computer storage is taking over. One of the main benefits with a computerized playback system is ease of use. Consider a scenario where one wishes to compile a playlist consisting of tracks distributed over several records. Using compact discs (CDS), it becomes necessary to change discs between tracks, or use a player capable of handling several discs. Both methods introduce a pause in the playback, and are rather cumbersome in their execution.

Now, enter the era of the computer based music playback system, where advanced playlist creation on nearly any criteria can be done through a personal computer (PC) or a more specialized device. Some systems offer audio distribution to any room in the house, some are completely self contained and have internal audio storage, while others rely on networking or short range busses for data retrieval. Others again are only docks for portable units.

People are getting used to the instant availability of music through these playback systems, but many of the devices leave a lot to be desired audio quality wise.

#### 1.2 Objective

The paramount objective of this thesis is to design an audio playback system which receives audio data over an universal serial bus (USB) connection. These data shall be converted to analog signals and amplified suitably for driving an audio power amplifier. In the same way the system should be able to decode the digital s/PDIF signal provided by CD players.

It is preferable that the system supports 24 bit linear pulse code modulated audio data with a sampling rate as high as 192 kHz, which is today's state of the art in the audio market. In addition it should support lower sampling frequencies, among them 44.1 kHz used on CDS.

A second goal is to design a passive attenuator circuit to adjust the output volume with minimal distortion, and an input source selection functionality. This should be controlled digitally, allowing for remote control.

The work will include the selection of proper components and the interconnection of these. A microcontroller must be programmed to control the system and handle the USB data reception. Finally the system should be realized and tested for both performance and functionality.

#### **1.3** System overview

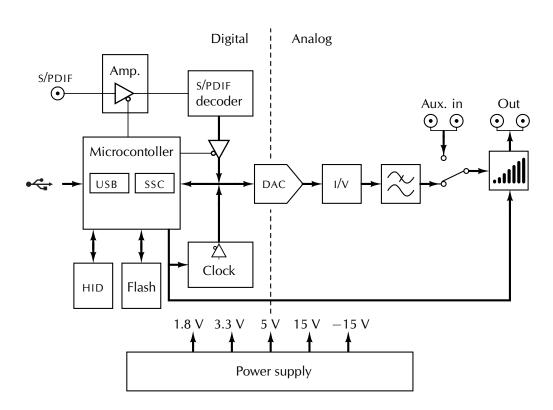

A block schematic of the system, based on the problem description, is shown in figure 1.1. The schematic is a mixture of both logical and physical building blocks.

Audio data is collected either via S/PDIF or USB, and then fed to the digital to analog converter (DAC). S/PDIF data is delivered nearly directly to the DAC from a dedicated decoder with an onchip clock generator. The microcontroller contains a USB controller module, and audio data from a host computer travels through this to the DAC, controlled from the external precision clock generator.

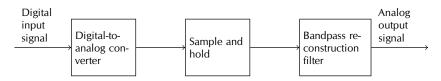

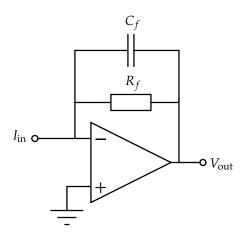

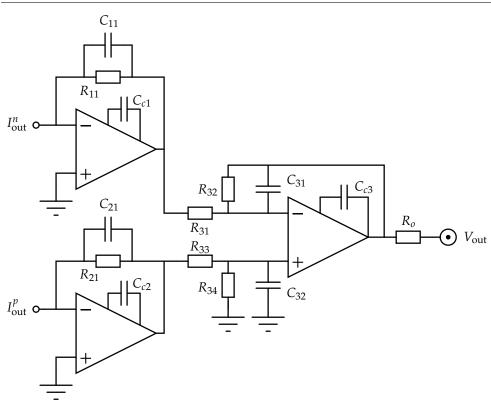

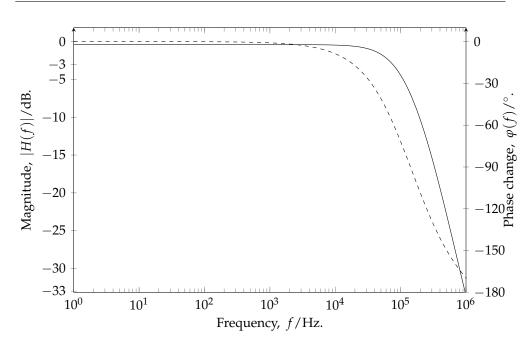

When the audio signals are back in the analog domain, they are at first converted from current to voltage in through the I/v-converter. Then a lowpass filter follows, and finally source selection and attenuation for volume control.

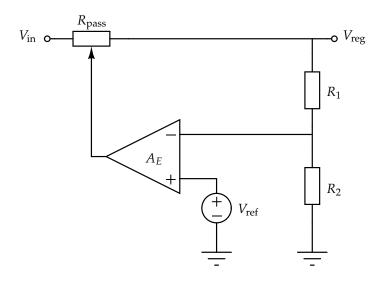

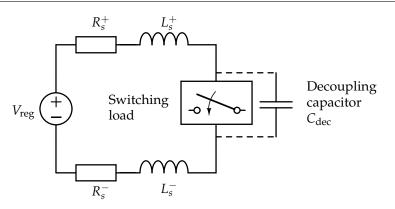

A large number of different supply voltages are needed in the system, and these are generated in a low noise power supply.

Interaction with the device is done through a human interface device (HID), consisting of a control panel with pushbuttons and status lights. The USB connection also provides the possibility of controlling the system.

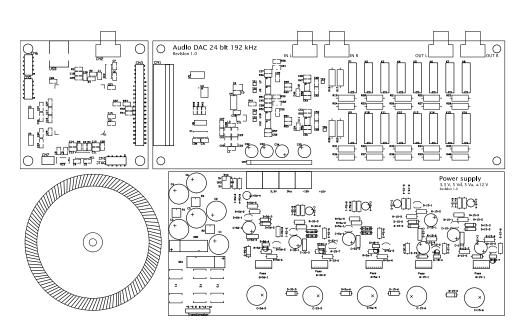

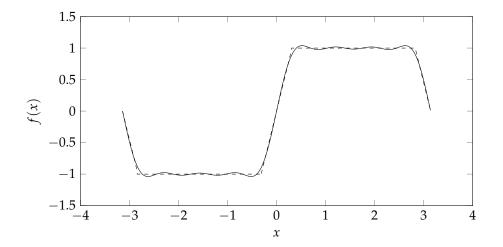

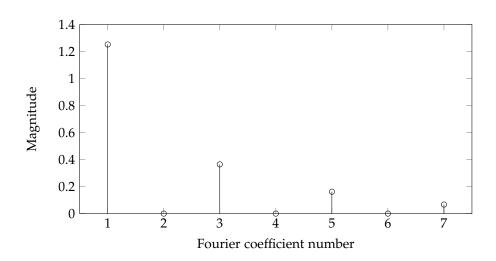

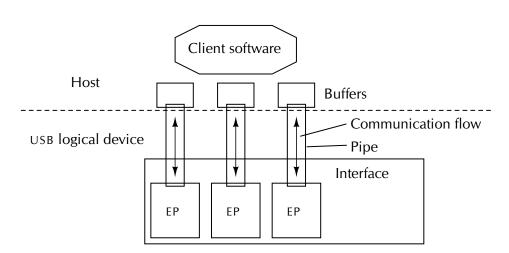

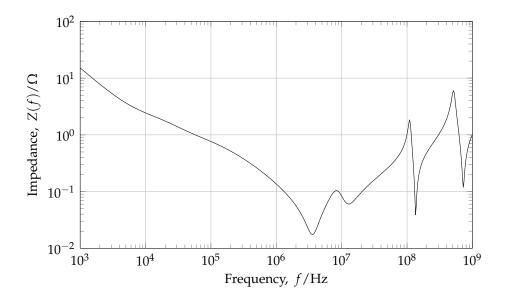

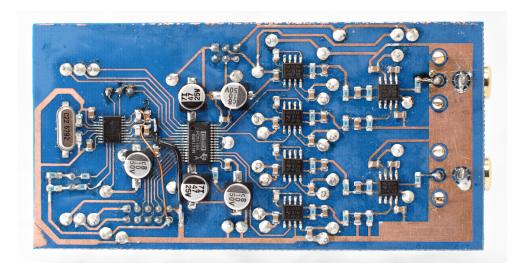

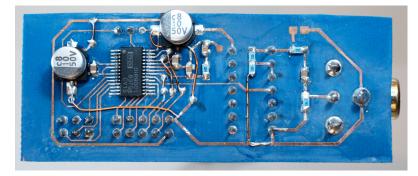

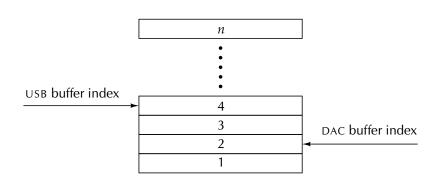

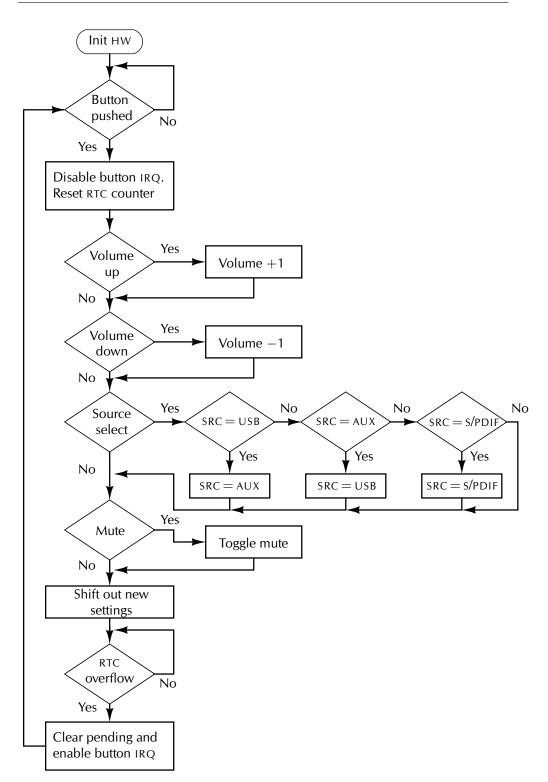

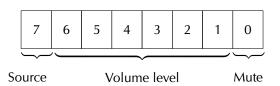

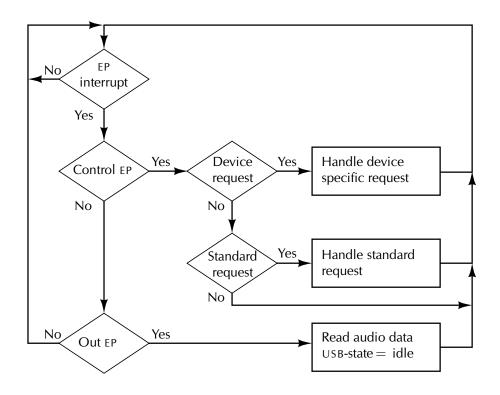

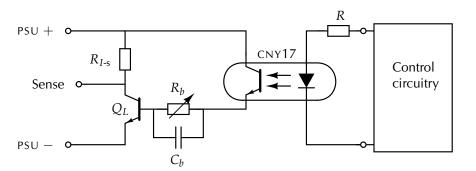

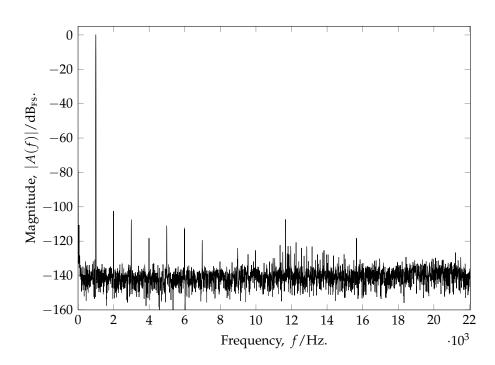

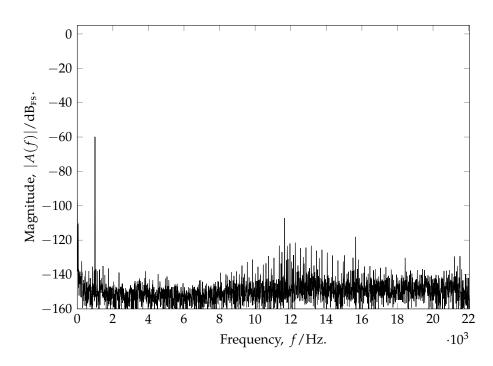

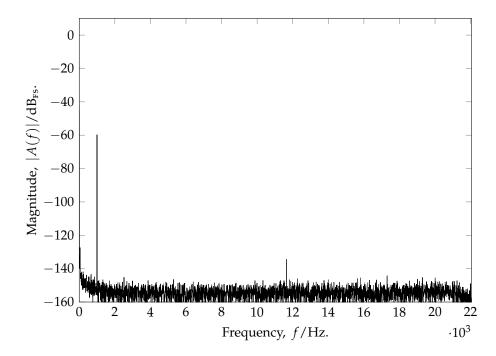

The finalized system is shown in figure 1.2. Three different printed circuit boards (PCBS) plus a mains transformer make up the device. The power supply dominates the lower half of the figure, while the digital control board is the smallest module of the system.