# Delay-Fault BIST in Low-Power CMOS Devices

**Tor Erik Leistad**

Master of Science in ElectronicsSubmission date: June 2008Supervisor:Einar Johan Aas, IETCo-supervisor:Frode Pedersen, Atmel Norway AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

Current test methodologies for CMOS devices assume that manufacturing defects in CMOS devices, such as stuck-at faults or delay faults, are invariant of operating voltage and temperature. Current low-power devices may operate at very low voltages, close to the threshold voltage, and need to operate across a wide temperature range. Because of this, delay faults are now becoming more dominant, and at-speed testing is necessary. Current designs use scan architecture for fault testing, but testing equipment is often slow and the time to scan in/out test-vectors/responses contribute to a large proportion of the test time. A study is proposed to investigate how delay fault test time can be reduced through a built-in selftest of a low-power device. The suggested solution is then to be implemented in a test chip design, which can be used for fault coverage measurements and fault model verification.

Assignment given: 15. January 2008 Supervisor: Einar Johan Aas, IET

# Abstract

Devices such as microcontrollers are often required to operate across a wide range of voltage and temperature. Delay variation in different temperature and voltage corners can be large, and for deep submicron geometries delay faults are more likely than for larger geometries. This has made delay fault testing necessary. Scan testing is widely used as a method for testing, but it is slow due to time spent on shifting test vectors and responses, and it also needs modification to support delay testing.

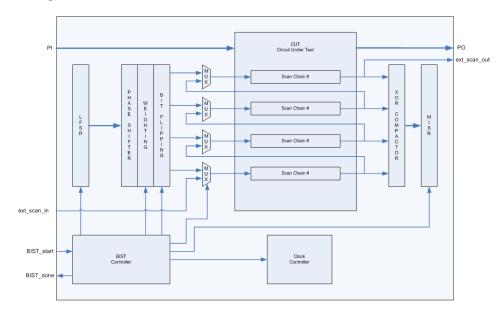

This assignment is divided into three parts. The first part investigates some of the effects in deep submicron technologies, then it looks at different fault models, and at last different techniques for delay testing and BIST approaches are investigated. The second part suggests a design for a test chip, including a circuit under test (CUT) and BIST logic. The final part investigates how the selected BIST logic can be used to reduce test time and what considerations needs to be made to get a optimal solution.

The suggested design is a co-processor with SPI slave interface. Since scan based testing is commonly used today, STUMPS was selected as the BIST solution to use. Assuming that scan already is used, STUMPS will have little impact on the performance of the CUT since it is based on scan testing. During analysis it was found that several aspects of the CUT design affects the maximum obtainable delay fault coverage. It was also found that careful design of the BIST logic is necessary to get the best fault coverage and a solution that will reduce the overall cost.

The results shows that a large amount of time can be saved during test by using BIST, but since the area of the circuit increases due to the BIST logic it necessarily don't mean that one will reduce cost on the overall design. Whether or not a BIST solution will result in reduced cost will depend on the complexity of the circuit that is tested, how well the BIST logic fits this circuit, how many internal scan chains can be used, and how fast scan vectors can be applied under BIST. In this case it looks like the BIST logic is not well suited to detect the random hard to detect faults. This results in a large amount of top up patterns. This combined with the large area of the BIST logic makes it unlikely that BIST will reduce cost of this design.

ii

# Preface

This Master's thesis is the result of work done at Atmel Norway AS during the first half of 2008. The work started as a continuation of a previous project assignment done for Atmel, and the aim was to make a circuit design that could be used for fault model analysis. To make things more interesting the design of a BIST solution was added to the assignment, with the aim to use the BIST for delay fault detection and to reduce test time. The design of the circuit and delay fault BIST would be the main part of the assignment.

The assignment was made possible with the help from Frode Pedersen, who also was my project supervisor at Atmel. I was very exited to do this assignment, not only because of its goals, but also due to the fact that it would give me great experience in circuit design and experience in working with different tools used for circuit design.

Although my experience in advance circuit design was somewhat limited in the beginning, I feel that this work has given me a lot of experience that I would not have been able to get in any other way. This became very clear in the last few weeks of the assignment, where I felt that I could have done several things different regarding the circuit design. A lot of this was probably due to the fact that I now was more familiar with the tools and how they could be used.

I wish to thank Professor Einar J. Aas, from the department of electronics and telecommunications at NTNU, for acting as my mentor and supervisor during this project. I also wish to thank him for all discussions and lectures the past few years, as they have been a great inspiration for working with circuit testing. I also wish to thank Frode Pedersen for making this assignment possible and for his inputs. My gratitude also goes to Kai Kristian Amundsen and Are Årset for their help with software tools used during the assignment.

# Contents

| Pı       | Preface iii<br>1 Introduction 1 |                                                                    |           |

|----------|---------------------------------|--------------------------------------------------------------------|-----------|

| 1        |                                 |                                                                    |           |

| <b>2</b> | The                             | ory                                                                | 3         |

|          | 2.1                             | Effects of deep-sub micron technologies                            | 3         |

|          | 2.2                             | Fault models                                                       | 5         |

|          | 2.3                             | Scan testing                                                       | 8         |

|          | 2.4                             | Delay testing                                                      | 9         |

|          | 2.5                             | Fault coverage                                                     | 11        |

|          | 2.6                             | BIST                                                               | 11        |

|          | 2.7                             | Scan based BIST                                                    | 21        |

|          | 2.8                             | Cost of test                                                       | 22        |

|          | 2.9                             | Clock source for use in delay fault testing $\ldots \ldots \ldots$ | 24        |

| 3        | Tes                             | t chip design                                                      | <b>25</b> |

|          | 3.1                             | CUT design                                                         | 25        |

|          | 3.2                             | BIST design                                                        | 30        |

|          | 3.3                             | Clock controller design                                            | 35        |

|          | 3.4                             | Oscillator design                                                  | 39        |

|          | 3.5                             | Scan chains                                                        | 40        |

| 4        | $\mathbf{Chi}$                  | p verification                                                     | 41        |

|          | 4.1                             | CUT verification                                                   | 41        |

|          | 4.2                             | BIST verification                                                  | 43        |

| 5        | Tes                             | tapproach                                                          | 45        |

|          | 5.1                             | Circuit synthesis                                                  | 45        |

|          | 5.2                             | BIST test vector generation                                        | 45        |

|          | 5.3                             | Fault simulation of BIST patterns                                  | 46        |

|          | 5.4                             | ATPG top up patterns                                               | 46        |

|          | 5.5                             | Analysing the results                                              | 47        |

| 6        | $\mathbf{Res}$                  | ults                                                               | <b>49</b> |

|          | 6.1                             | RTL code modifications                                             | 49        |

|          | 6.2                             | Stuck-at fault simulations                                         | 52        |

|          | 6.3                             | Transition delay fault simulations                                 | 57        |

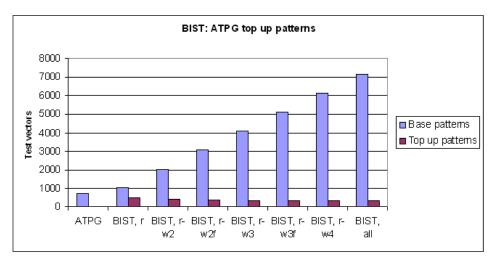

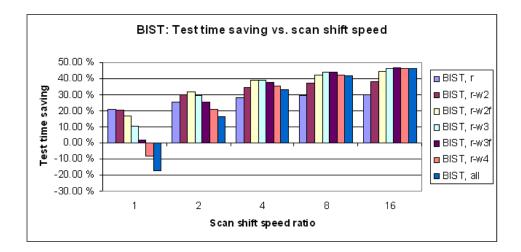

|          | 6.4                             | ATPG top up patterns                                               | 65        |

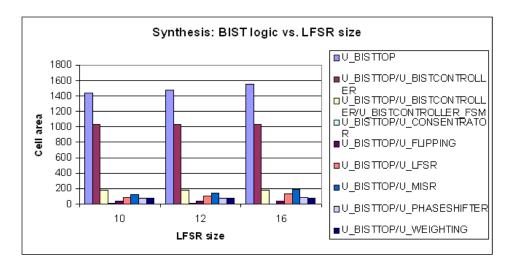

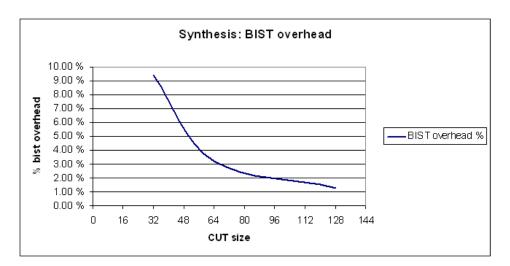

|          | 6.5                             | Area                                                               | 67        |

|          | 6.6                             | Oscillator simulations                                             | 69        |

| 7  | Discussion                                                                                               | 71 |

|----|----------------------------------------------------------------------------------------------------------|----|

|    | 7.1 Circuit design                                                                                       | 71 |

|    | 7.2 DFT design issues                                                                                    | 72 |

|    | 7.3 LFSR size                                                                                            | 74 |

|    | 7.4 Number of scan chains                                                                                | 75 |

|    | 7.5 Weighted random patterns                                                                             | 76 |

|    | 7.6 Phase shifter                                                                                        | 76 |

|    | 7.7 Primary input and output isolation                                                                   | 77 |

|    | 7.8 CUT size                                                                                             | 78 |

|    | 7.9 ATPG top up patterns                                                                                 | 79 |

|    | 7.10 BIST area                                                                                           | 79 |

|    | 7.11 CUT area                                                                                            | 80 |

|    | 7.12 Test cost $\ldots$ | 80 |

|    | 7.13 Fault coverage                                                                                      | 81 |

|    | 7.14 Oscillator design                                                                                   | 83 |

|    | 7.15 Future work and suggestions for improvement                                                         | 84 |

| 8  | Conclusion                                                                                               | 85 |

| Re | ferences                                                                                                 | 88 |

| A  | pendices                                                                                                 | 89 |

| A  | Instruction set summary                                                                                  | 89 |

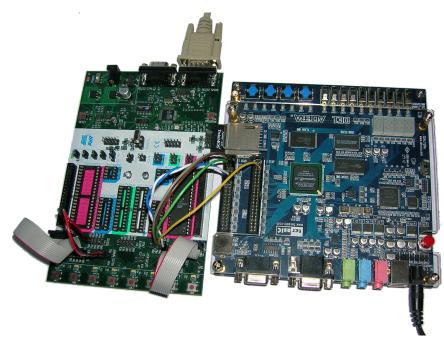

| в  | FPGA connection to STK500                                                                                | 89 |

| С  | Changes in verilog code for different simulations                                                        | 89 |

| D  | Attached files                                                                                           | 91 |

# List of Figures

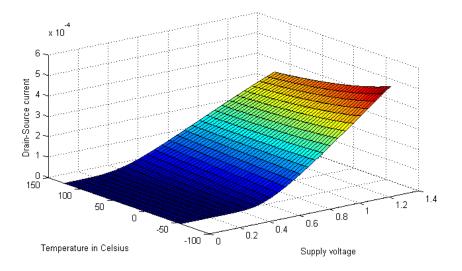

| 1  | Vdd, temperature versus Id                                                                        | 4  |

|----|---------------------------------------------------------------------------------------------------|----|

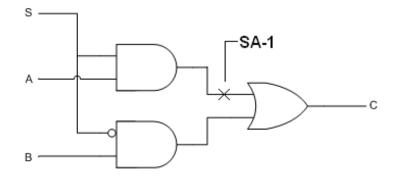

| 2  | Stuck-at one fault.                                                                               | 6  |

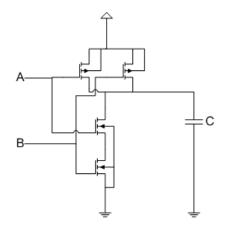

| 3  | Transistor representation of NAND-gate                                                            | 6  |

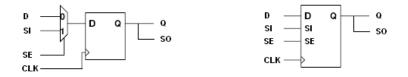

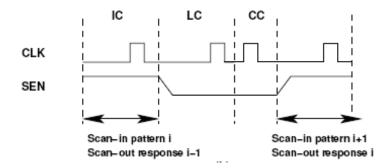

| 4  | A muxed scan flip-flop                                                                            | 8  |

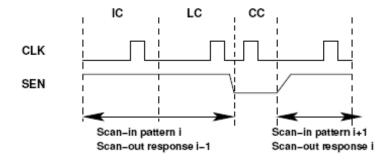

| 5  | Timing diagram for LOS                                                                            | 10 |

| 6  | Timing diagram for LOC                                                                            | 10 |

| 7  | AND-tree attached to scan chain                                                                   | 11 |

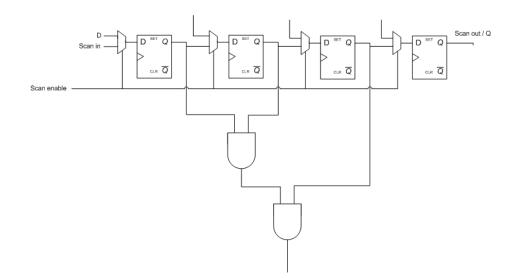

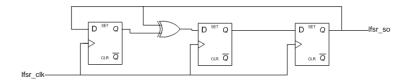

| 8  | LFSR with external feedback                                                                       | 13 |

| 9  | LFSR with internal feedback.                                                                      | 14 |

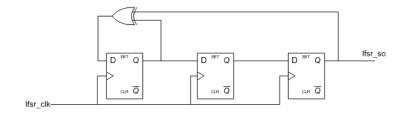

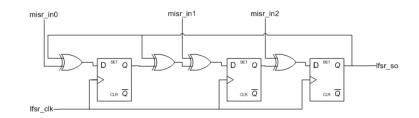

| 10 | MISR with internal feedback.                                                                      | 17 |

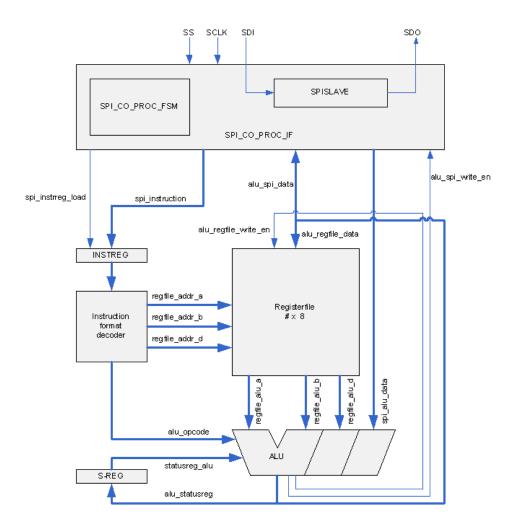

| 11 | Co-processor overview.                                                                            | 26 |

| 12 | Instruction package                                                                               | 26 |

| 13 | Instruction with data package                                                                     | 27 |

| 14 | Instruction                                                                                       | 28 |

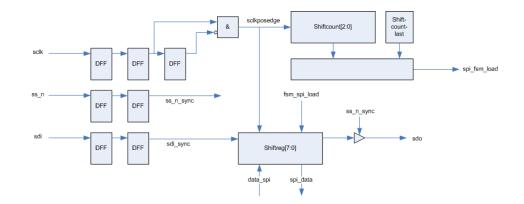

| 15 | Simplified SPI slave overview                                                                     | 29 |

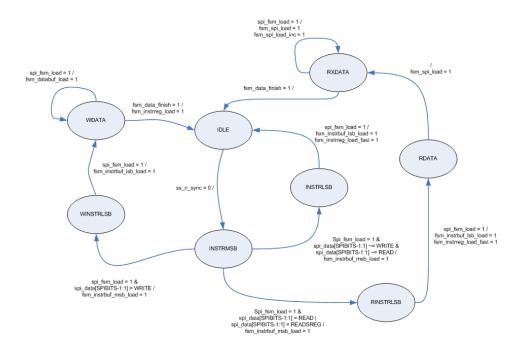

| 16 | Finite state machine controlling SPI sending and receiving                                        | 29 |

| 17 | 3 bit LFSR with internal feedback and load capability                                             | 32 |

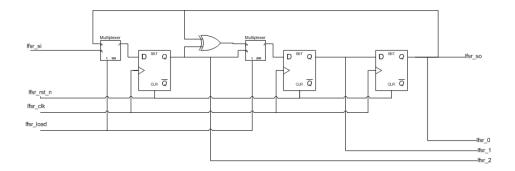

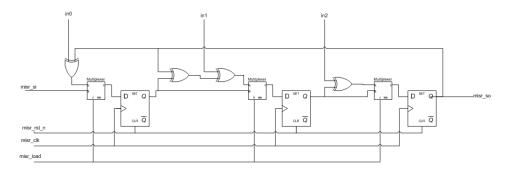

| 18 | 3 bit MISR with internal feedback and shift in/out capability.                                    | 32 |

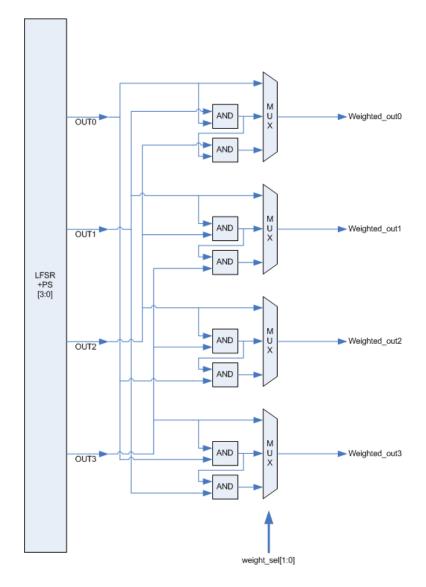

| 19 | Connection for muxes and AND-gates for weight generation                                          | 33 |

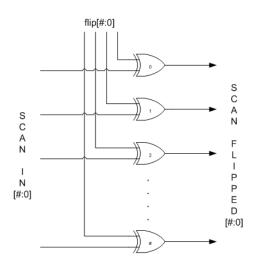

| 20 | Logic for flipping the input data to the scan chains                                              | 34 |

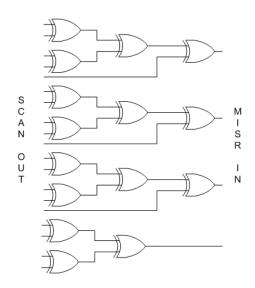

| 21 | Concentrator logic between scan outputs and MISR inputs                                           | 35 |

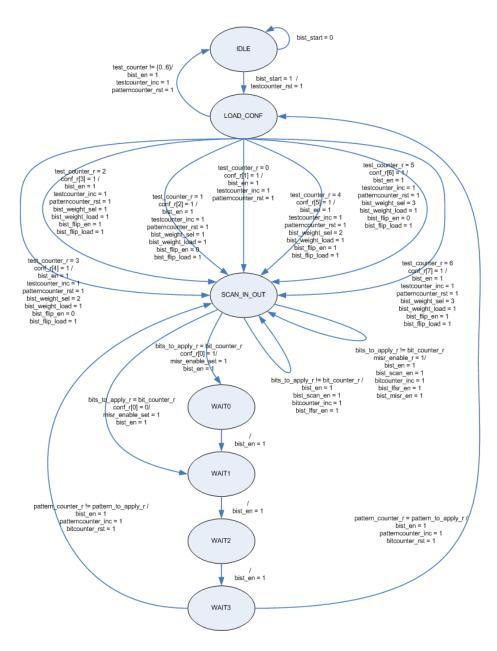

| 22 | Finite state machine of the BIST controller                                                       | 36 |

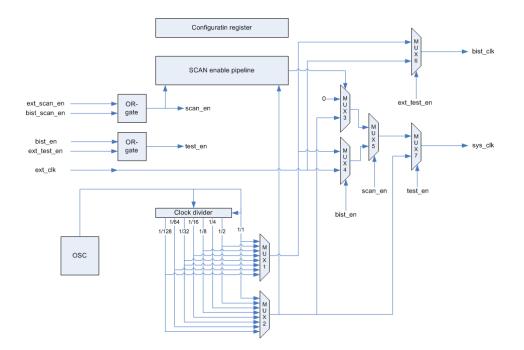

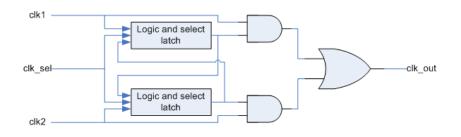

| 23 | The clock controller                                                                              | 38 |

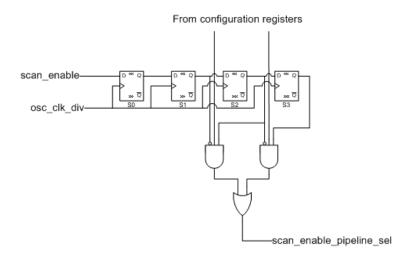

| 24 | The scan enable pipeline                                                                          | 38 |

| 25 | Clock multiplexer.                                                                                | 39 |

| 26 | Scan chain overview                                                                               | 40 |

| 27 | Waveform of SPI signals performing write, read and one ad-                                        |    |

|    | dition. $\ldots$ | 42 |

| 28 | The validation setup with Altera DE1 and Atmel STK500. $\ .$                                      | 42 |

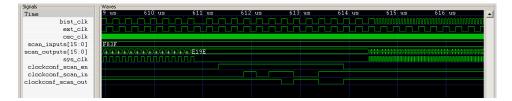

| 29 | Wavform of BIST startup and first scan pattern                                                    | 44 |

| 30 | Waveform of a launch from capture cycle                                                           | 44 |

| 31 | Wavefrom showing new configuration to the clock controller                                        |    |

|    | being applied                                                                                     | 44 |

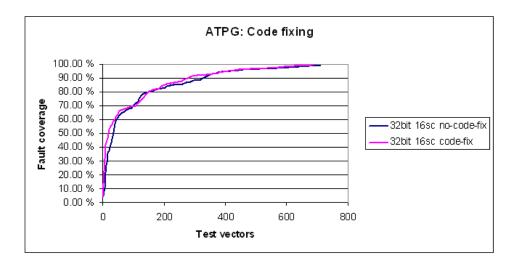

| 32 | RTL-code fixes under ATPG simulation                                                              | 50 |

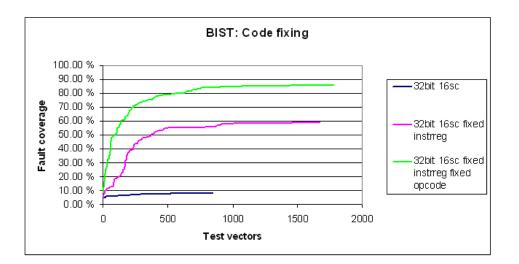

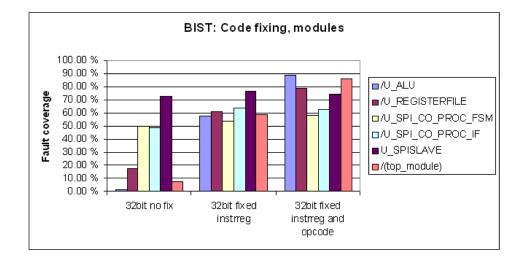

| 33 | Simulation for RTL-code fixes under BIST                                                          | 50 |

| 34 | Module overview for RTL-code fixes                                                                | 51 |

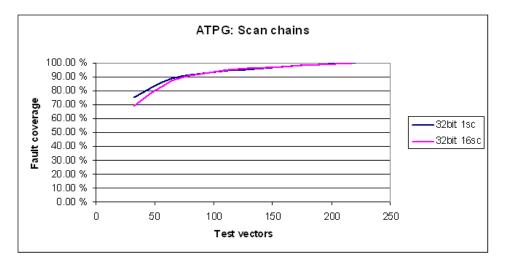

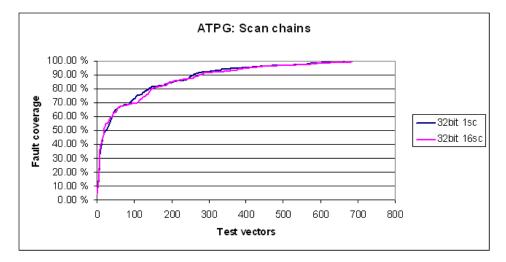

| 35 | Simulation for different number of scan chains for ATPG                                           | 52 |

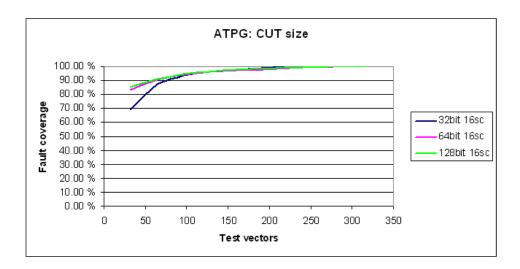

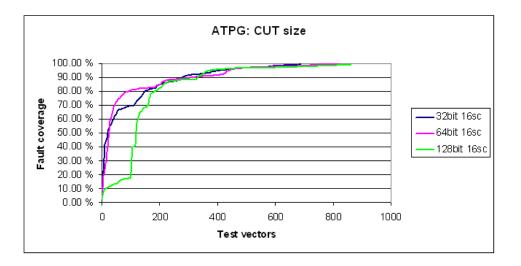

| 36 | Simulation for different CUT sizes for ATPG                                                       | 53 |

| 37 | Simulation for different CUT sizes for ATPG                                                       | 53 |

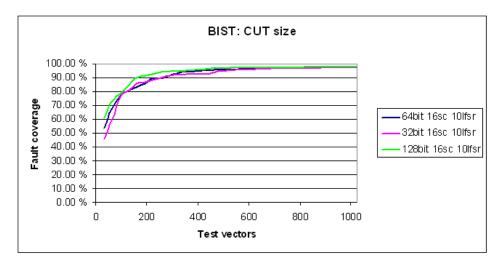

| 38 | Simulation for different CUT sizes for BIST                                                       | 54 |

| 39 | Simulation for different CUT sizes for BIST                                                       | 54 |

| 40 | Simulation for different LFSR sizes for BIST.                                                     | 55 |

| 41 | Simulation for different LFSR sizes for BIST                    | 55 |

|----|-----------------------------------------------------------------|----|

| 42 | Simulation for different number of scan chains for BIST         | 56 |

| 43 | Simulation for different number of scan chains for BIST         | 56 |

| 44 | Simulation for different number of scan chains for ATPG         | 57 |

| 45 | Simulation for different CUT sizes under ATPG                   | 58 |

| 46 | Simulation for different CUT sizes under ATPG                   | 58 |

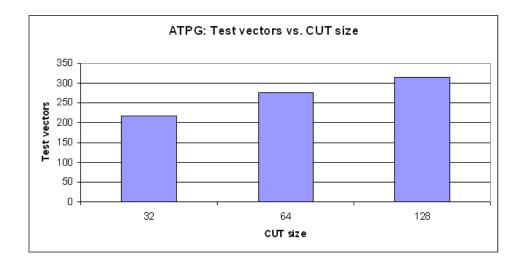

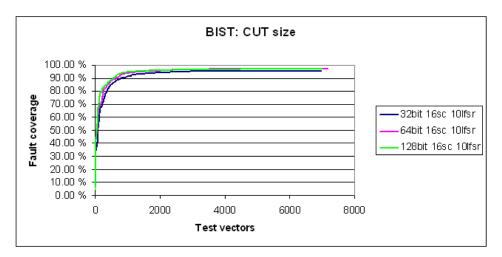

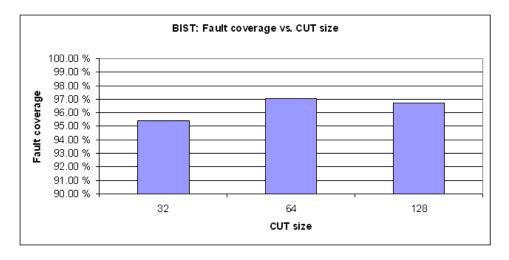

| 47 | Simulation of different CUT sizes.                              | 59 |

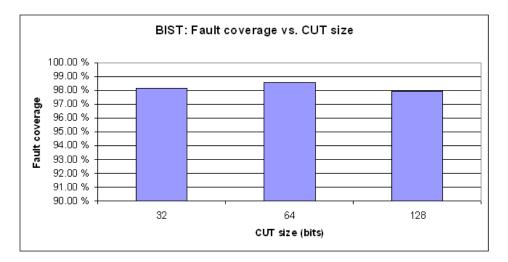

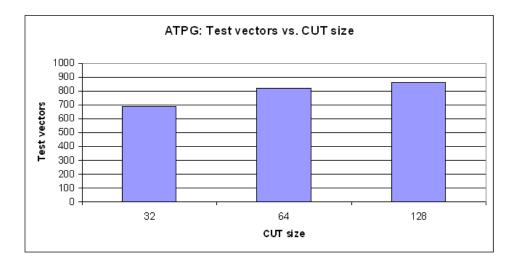

| 48 | Cut size vs fault coverage                                      | 59 |

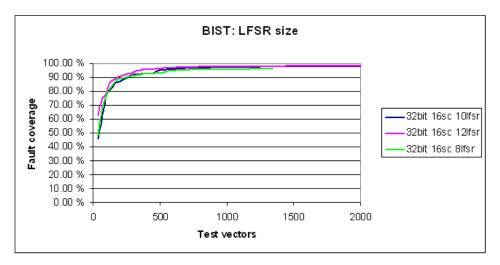

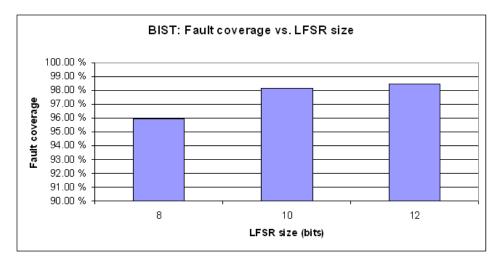

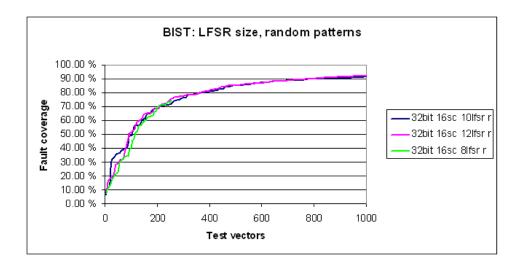

| 49 | Simulation of different LFSR size and random patterns           | 60 |

| 50 | Simulation for different LFSR sizes                             | 60 |

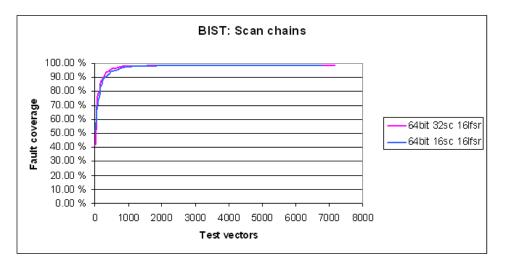

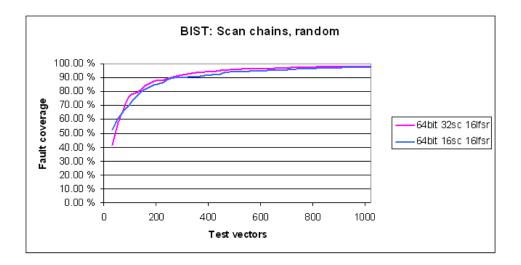

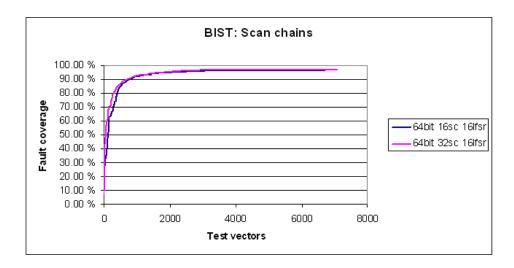

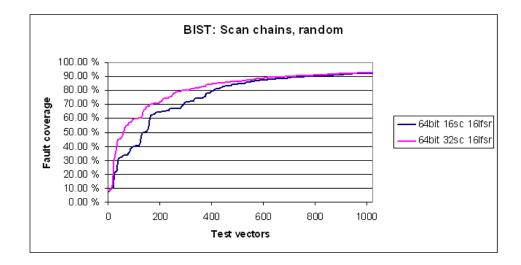

| 51 | Simulation of different scan chains                             | 61 |

| 52 | Simulation of different scan chains, random patterns            | 61 |

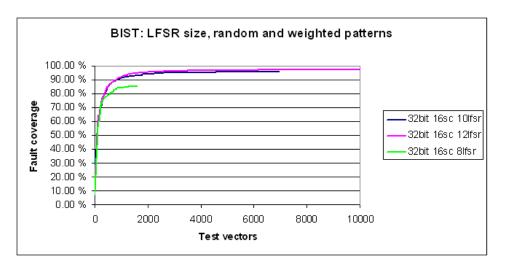

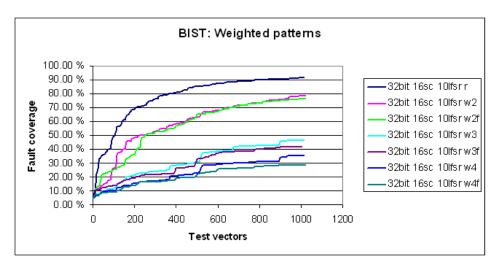

| 53 | Simulation for different weights applied                        | 62 |

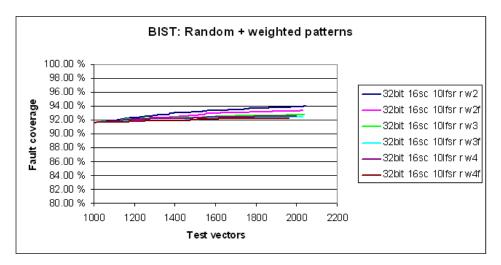

| 54 | Simulation for different weights applied after random patterns. | 62 |

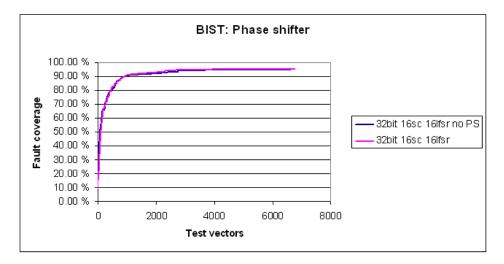

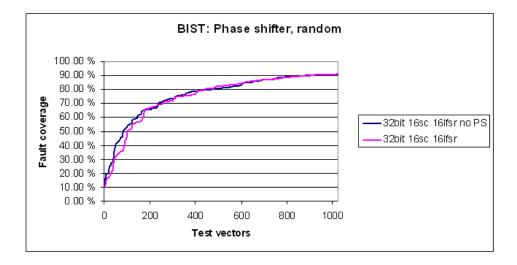

| 55 | Simulation of BIST with phase shifter and without               | 63 |

| 56 | Simulation of BIST with phase shifter and without, random       |    |

|    | patterns                                                        | 63 |

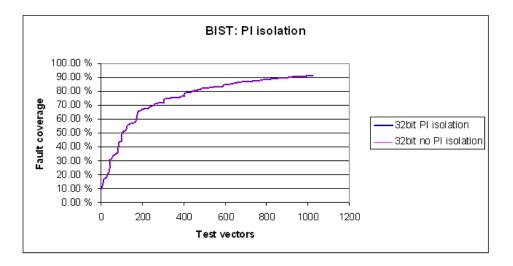

| 57 | Simulation of BIST with PI isolation and without.               | 64 |

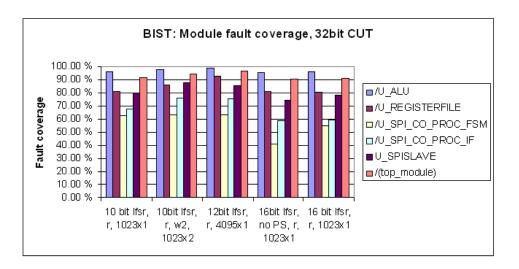

| 58 | Fault coverage for different modules                            | 64 |

| 59 | BIST test patterns and ATPG top up patterns                     | 65 |

| 60 | Test time saving for different scan speeds and number of BIST   |    |

|    | patterns                                                        | 66 |

| 61 | BIST area for different LFSR size                               | 67 |

| 62 | BIST area overhead.                                             | 67 |

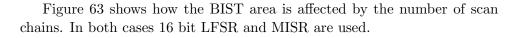

| 63 | BIST area for different scan chains                             | 68 |

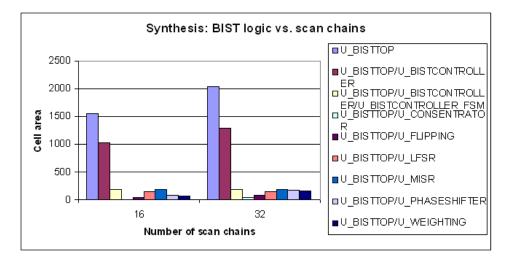

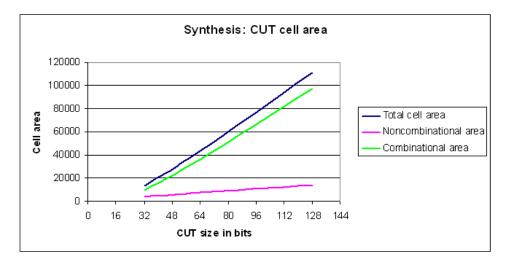

| 64 | Area for different modules of the CUT                           | 68 |

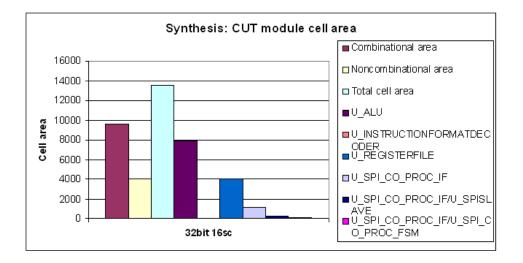

| 65 | Area for different modules of the CUT for different CUT size.   | 69 |

| 66 | Area of the CUT for different CUT size                          | 69 |

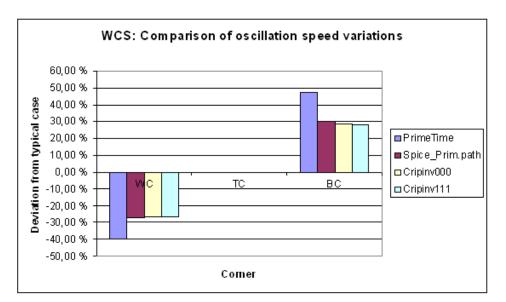

| 67 | Inverter oscillator simulations.                                | 70 |

# List of Tables

| 1 | BIST controller FSM transition table. | 37 |

|---|---------------------------------------|----|

| 2 | Instruction set summary               | 90 |

| 3 | FPGA connections                      | 91 |

# List of Abbreviation

| Abbreviation         | Meaning                                 |

|----------------------|-----------------------------------------|

| ALU                  | Arithmetic Logic Unit                   |

| ATE                  | Automated Test Equipment                |

| ATPG                 | Automatic Test Pattern Generation       |

| BIST                 | Built In Self Test                      |

| CA                   | Cellular Automata                       |

| $\operatorname{CUT}$ | Circuit Under Test                      |

| CLK                  | Clock                                   |

| $\mathbf{FC}$        | Fault Coverage                          |

| FPGA                 | Field Programmable Gate Array           |

| $\mathbf{FSM}$       | Finite State Machine                    |

| GCD                  | Greatest Common Divisor                 |

| HDL                  | Hardware Description Language           |

| LFSR                 | Linear Feedback Shift Register          |

| LOC                  | Launch Of Capture                       |

| LOS                  | Launch Of Shift                         |

| MAC                  | Multiply Accumulate                     |

| MISR                 | Multiple Input Shift Register           |

| ORA                  | Output Response Analyser                |

| PI                   | Primary Input                           |

| PO                   | Primary Output                          |

| $\mathbf{PS}$        | Phase Shifter                           |

| RTL                  | Register Transfer Level                 |

| SCLK                 | SPI Clock                               |

| SDI                  | Serial Data Input                       |

| SDO                  | Serial Data Output                      |

| SPI                  | Serial Peripheral Interface             |

| $SS_N$               | Slave Select (Negative active state)    |

| STUMPS               | Scan Test Using MISR and Parallel Shift |

| TAP                  | Test Access Port                        |

| TPG                  | Test Pattern Generator                  |

|                      |                                         |

х

# 1 Introduction

Testing of integrated circuits is a challenging task, as any NP-complete problem is. Today's integrated circuits may contain billions of transistors, several miles of narrow metal interconnections and billions of metal vias and connections. Testing for defects are necessary to obtain good product quality, and with today's integrated circuit with geometries in the nanometre range this is becoming a challenging task. For older technologies it was sufficient to use stuck-at testing and a few functional test vectors for delay testing. In newer technologies delay faults are of more concern, and for this reason functional test patterns for delay testing is no longer an option. For devices that are required to operate across a large range of voltage and temperature delay testing is very important as these parameters will affect the amount of delay.

New test approaches are necessary for delay fault testing, as functional test patterns no longer are adequate. One of the reasons for functional test patterns to be inadequate is that they are hard to develop and will not give sufficient fault coverage. Delay faults have to be tested at a structural level to achieve sufficient fault coverage. This work looks on how delay fault test can be done, and how BIST can be used to reduce the time required for test. A test chip design is developed to investigate different aspects of BIST.

Chapter 2 takes a brief look at low-level CMOS circuitry and how delay is affected by external parameters. It then looks at scan-based testing, as this is a commonly used test approach in the industry. Then it looks into BIST and how it can be used to reduce test cost. Chapter 3 describes the design of the test chip, including both the test logic and the circuit under test. Chapter 4 describes how the chip design was developed and verified. Chapter 5 explains the test approach used to gather simulation results and the test setup used. Chapter 6 presents the results as a set of graphs. Chapter 7 discusses the circuit design based on observations and the results presented in chapter 6. Finally chapter 8 concludes the report with a short summary of the discussion and suggestion for further work.

# 2 Theory

Production testing is necessary to eliminate defective circuits from reaching the customer. Each device produced must be tested, and when millions of circuits are produced each day the time required to test the circuits becomes important. The time used to test a circuit contributes to the circuits cost, and as circuits get more complex and geometries becomes smaller are in fact becoming the most dominant cost of the circuit. For this reason, design for test are becoming more important as a means to reduce test time and cost.

With new technologies, in deep sub micron geometries, the types of defects that are most likely to occur are different from those in lager geometries. Delay fault are becoming more dominant, and this requires other testing approaches than stuck-at testing. Another problem with deep sub micron technologies is that external parameters might affect delay in other ways than in lager geometries. This means that testing might have to be done under other conditions, and with other patterns to get the best fault coverage.

The following sections will take a closer look at the different aspects of submicron CMOS, fault models, testing, and how BIST can be used to reduce test cost. A large portion of the theory is taken from [Stroud, 2002], [Crouch, 1999], [Segura] and [Johns and Martin, 1997].

# 2.1 Effects of deep-sub micron technologies

The newest technology today operates on 45nm geometries. This is very deep-sub micron, and circuits made in these geometries are subject to other effects than in larger geometries (greater than 180nm).

There are two important external parameters that affect the performance of circuit after it has been made, the supply voltage and temperature. Supply voltage is probably the most important as it directly affects the speed of the circuit. This can be shown with a simple equation.

$$t = \frac{C * V}{I} \tag{1}$$

Here t is the delay in seconds, C is the load capacitance in farad, which consists of gate and trace capacitances and other parasitic capacitances connected to the driver. V is the supply voltage and I is the current delivered by the driving transistor. Replacing I by an equation for the current, [Leistad, 2007], one gets an equation for the delay that contains both voltage and temperature.

$$t = \frac{C * V_{DD}}{\mu_{n0}(\frac{T}{300})^{\beta} * \frac{C_{ox}}{2} * \frac{W}{L} * (V_{DD} - (V_{th0} - 0.002T))^{\alpha}}$$

(2)

Here  $V_{DD}$  is the supply voltage,  $\alpha$  is a constant somewhere between 1 and 2,  $\beta$  is somewhere between -1 and -2,  $V_{th0}$  is the threshold voltage of

the driving transistor at 300 Kelvin and  $\mu_{n0}$  is the mobility at 300 Kelvin. T is the absolute temperature in Kelvin, and W and L is the width and length of the driving transistor.

From this equation one can see that the delay is affected by several parameters. Transistor size, mobility, threshold voltage, supply voltage and temperature all affect the performance. In addition the resistance in the interconnect will also affect the delay, but this model does not account for this effect. One model that looks at interconnect resistance is the Elmore delay model, which considers the RC delay in different nets. Considering the routing delay is important as it can contribute to a large portion of the total delay in a circuit.

The equation for the transistor current can be used to show how delay will vary with supply voltage and temperature when not considering routing delay. Figure 1 shows a 3D graph with voltage and temperature as parameters.

Figure 1: Vdd, temperature versus Id

From this figure one can clearly see that there is a change as the supply voltage decreases. For supply voltages greater than the threshold voltage, 0.7V, the drive strength decrease with increasing temperature, which will result in a larger delay. When the supply voltage decreases and becomes close to or less than the threshold voltage this changes. Now the drive strength increases with increasing temperature and this will give lower delay. The reason for this is that both the threshold voltage and the carrier mobility are affected by temperature. They both decrease with temperature but works in opposite directions. For large supply voltages the current is mostly affected by the carrier mobility. The variation in threshold voltage is small compared to the variation in mobility, and mobility variations dominate the equation. For small supply voltages the opposite happens.

Taking into account that today's circuit are required to operate across a large voltage and temperature range one can see that delay testing is important, but also difficult. The characteristics of a circuit may vary greatly with voltage and temperature and this may result in a circuit that operating correctly under one condition but not under another. Selecting the right voltage and temperature for testing is important, and to get sufficient fault coverage several settings might be necessary depending on the technology used.

# 2.2 Fault models

Several types of defects can occur in a circuit. These defects are mapped to a set of fault models that describes how a defect will affect the circuit. These fault models are then used in fault simulations of the circuit to determine which fault coverage can be obtain. Fault coverage is a measure of how good the production test is, and if this value is to give a reliable result it is important that there is a good relationship between the defects and the faults model. For this reason there are several commonly used fault models. The next sections will take a brief look at the most common models, [Stroud, 2002], [Crouch, 1999].

### 2.2.1 Gate stuck-at 1/0 faults

The gate stuck-at model assumes that one of the inputs or outputs of a gate are tied to logic one or zero. This means that a two input gate can have six different modelled faults. Several defects can lead to this type of behaviour. For instance can a low resistance bride between one of the power supply rails and one of the nodes tie the node to the power supply rail, making the input or output to always have the same logic value.

In the example in figure 2 one of the nodes are tied to logic one. To detect that this node is tied to one, the opposite value has to be assigned to that node. This can be done by setting S to one and A to zero. Since S is one it doesn't matter what value is assigned to B in this case. In a correct functional circuit the output should now be zero, but since there is a stuck-at one fault, the output remains at one.

#### 2.2.2 Transistor stuck-on/off faults

Gate level stuck-at can accurately reflect the behaviour of transistor faults in NMOS circuitry, but the advantage of CMOS brought with it the need for transistor fault models. Transistors can be stuck-on or stuck-off due to different defects such as bridges and opens. If a transistor is stuck-on there might be a conducting path between the power supply rails for some

Figure 2: Stuck-at one fault.

input vectors. For gates with such faults the output value can be something between the two supply voltages. The input vector and the drive strength of the transistors will determine the output value of the gate.

Figure 3: Transistor representation of NAND-gate.

One problem with transistor stuck-on and stuck-off fault is that they may have memory effects, meaning that several vectors are needed to detect them. Looking at figure 3 and assuming that one of the NMOS transistors are always off, one can notice that one first has to charge the load capacitance to logic one and then apply the vector for discharging it through the NMOS transistors. If the output value stays at one it is clear that one of the NMOS transistors are always off and the defects is detected.

# 2.2.3 Delay faults

Delay fault are different from other faults. This is because they are only detected if the test is done at-speed. Some defects, such as bridges and

opens, may have characteristics that make the circuit function correctly at low speeds, but fail at high speeds. The object of delay fault testing is to test the paths between flip-flops, between primary inputs and flip-flops, and flip-flops and primary outputs. Delay fault testing requires two vectors, the first sets up the path and the second tests the path by producing a transition in the path for delay fault detection. The second vector also needs to be captured at-speed. There are two types of delay faults, transition delay and path delay fault, [Gjermundnes, 2006].

Transition delay faults, also known as slow-to-rise and slow-to-fall faults, are the type of defect that causes a single gate or transistor to be significantly slower that normal. This is also referred to as spot defects. Every gate has the possibility of having delay defects. Testing all possible faults gives long testing time, as two vectors are needed to test each possible fault location.

A path delay fault is what happens if the overall circuitry is too slow. Reasons for such faults are variation in the manufacturing process that affects all or several transistors in the circuit, such as over etching or insufficient doping. The result is that some paths through the circuitry may not meet the required performance specifications. To detect this type of fault one can apply delay tests to the longest paths through a circuit to see if they can operate at the given speed.

# 2.2.4 Bridge faults

Bridge faults occur when there is a short or resistive coupling between two or more nodes that should not be connected. There are two commonly used models for bridge faults, wired-AND and wired-OR. A wired-AND fault is also said to be zero dominant and a wired-OR is said to be one dominant. Bridge fault are complex faults. The effect of the bridge does not only depend on the bride resistance, but also one what gates are driving the different sides of the bridge and what vector is applied to these gates. Bridge faults can only be detected if opposite values are applied to the two different sides of the bridge. Since there is opposite values on the two sides there will be a conducting path between the power supply rails and in some cases the increase in current consumption can be detected.

One of the biggest problems with bridges is that one does not know which interconnections are likely to make bridges before the layout of the chip is done. To determine which wires are most likely to make a bridge one can extract the capacitive coupling between the different wires as it is likely that the wires with largest capacitive coupling is the wires that will make a bridge.

# 2.2.5 Open faults

An open fault is a break in the interconnection between to places. An open defect can be conducting or not depending on the size of the open. In the cases where it is conducting it can be modelled as a series resistance, and in cases where it doesn't conduct it can be modelled as an infinite series resistance. Delay testing is required to detect open faults, as the series resistance will increase the delay of the path by an unknown amount.

# 2.3 Scan testing

Testing of a circuit can be done in several ways. Functional testing uses the circuit without any additional logic to test it. This is not a very practical approach as a circuit can have several inputs, and if it is sequential a large amount of vectors are required to sufficiently test it. The most common approach to solve this problem is to use scan testing. If the design is a full scan design it is reduced to a combinational circuit as all sequential stages are removed. A partial scan design will have some sequential stages, but the number of them is reduced. When the circuit is reduced to a combinational circuit it reduces the number of test vectors needed, which in turn also reduces test time. It also reduces the time needed for generation of test vectors as the ATPG now only needs to consider a combinational circuit instead of a sequential one.

The reduction to a combinational circuit is obtained by connecting all registers in the circuit into a long shift register. This is done by adding a multiplexer in front of the input to each flip-flop. The multiplexers are controlled by a scan enable signal. When the scan enable signal is active the registers are connected into a shift register and the input and output are used to shift in and read out data from the circuit. When the scan enable isn't active the circuit is connected to its normal operational mode. The multiplexer adds additional area and delay, but this can be minimized by using and optimised scan cell, as seen in figure 4.

Figure 4: A muxed scan flip-flop.

To test the circuit one first sets it into scan mode by setting scan enable active. Then the scan chain is filled with known data so that the state of the circuit is known. The scan enable is then set to its inactive state, and one clock cycle is applied. The circuit is brought back to scan mode and the data is shifted out at the same time as new data is shifted in. The output from the scan chain is compared to the expected values, and if the output is different, one knows that there is a defect in the circuit. This procedure is repeated until all faults are covered.

The major problem with this approach is the time needed to shift the test vectors and the responses. One approach to reduce shifting time is to use several scan chains, but one is often limited by the amount of pins available for this purpose. The second problem is that shifting often has to be done at a slower speed than the maximum frequency of the circuit, as the testing equipment is slower than the circuit.

# 2.4 Delay testing

Delay testing is becoming more important as defects in smaller geometries are more likely to result in excessive delay. Delay testing can only be achieved by running the circuit at the maximum operational speed during test. This is not always an option. Testing equipment may be slow, and not able to run at these speeds. This leaves just two options; run the circuit at slower speed, but change to the maximum speed during the launch and capture of test data, or use some BIST logic that works independently from the external testing equipment.

Since scan testing is a widely used test method, modifying it to support delay testing would be a big advantage. This can be done in two ways, referred to as launch of shift (LOS) and launch of capture (LOC), [Xijiiang Lin; Press, Sept.-Oct. 2003], [Saxena, 2002], [Pateras, Sept.-Oct. 2003], [Vemula]. There is a big difference in these two methods. Launch of shift requires the scan enable signal to be an at-speed signal, that is, it needs to be able to operate at the maximum frequency of the circuit. This means that the scan enable signal has to be routed as a clock signal and this will result in additional area overhead. Both method has a launch and capture cycle. First the circuit is brought to a known state, and then the launch cycle applies a transition to the circuit which is captured in the capture cycle.

In launch of shift the last shift is used as the launch cycle, and the scan enable signal need to be inactive before the capture cycle. This is the reason for the need for an at-speed scan enable in this approach. The timing for a LOS cycle is shown in figure 5.

Instead of making the scan enable signal as an at-speed signal, other approaches can be used. The scan enable signal can be pipelined into several pipelines or local scan enable generators can be made, as described in [Ahmed, 1-5 May 2005]. These can then connect to a small amount of flip-flops, making the signals able to run at-speed.

The second approach, LOC, gives the ability to use a slow scan enable signal by inserting a delay before the launch cycle, as seen in figure 6.

Figure 5: Timing diagram for LOS.

Figure 6: Timing diagram for LOC.

Both methods have some limitations. Delay testing requires two test vectors, one to set up the initial condition, and one to make some transition in the circuit. In LOS the second vector is just the first vector shifted by one bit. The means that the two vectors are very alike, and this may in some cases limit the fault coverage. This can easily be seen in an example with a tree of AND-gates as in at figure 7. Assuming that you want to test for a slow-to-rise at a gate input along the longest path in the figure. The initial value has to be zero and a transition to one must be applied. If LOS is used the initial zero will just be shifted one bit to the right, and the output of the AND-tree will still be zero. This means that it is impossible it test for a slow-to-rise along some paths, and this will reduce the fault coverage.

Launch from capture also has some limitations. The second vector is the response due to the first vector. This means that not all possible combinations of inputs can be applied during the launch, but all functional ones can be. Sequential ATPG will also be necessary for LOC since the second vector is the response of the first one. Since not all possible patterns can be applied there will be a reduction in fault coverage also in this case.

Figure 7: AND-tree attached to scan chain.

# 2.5 Fault coverage

Fault coverage is a measurement of how effective a set of test vectors are in detecting possible defects in a circuit. A fault simulator takes a circuit description and test vectors as input. It generates a fault list for the circuit, or takes it as input, and simulates the test vectors against the fault list. After simulation is completed the simulator will have a list with the detected faults, possibly detectable faults, undetectable faults, and undetected faults that remains in the fault list. Using these values, the fault coverage can be calculated as described in [Stroud, 2002]:

$$FC = \frac{D + xP}{T - U} \tag{3}$$

Here D is the number of detected fault, P is the number of potentially detected faults and x is the probability of it being detected. T is the total number of faults, and U is the number of undetectable faults.

# 2.6 BIST

Build In Self Test (BIST) is a means for reducing the cost of testing. This is accomplished by adding additional logic to the circuit to be tested to ease the testing procedure. There are several approaches to BIST, but they all have certain things in common, such as test pattern generators (TPG) and output response analysers (ORA), [Stroud, 2002].

The main problem for all BIST approaches is the total number of flipflops in the circuit. The number of flip-flops can easily range in the number of hundreds of thousands, requiring large TPGs, resulting in that it is not possible to run the BIST logic for maximum length. For long test sequences higher fault coverage is obtained, but the cost of test also increases.

The goal is to test the circuit for all possible faults. ATPG will make deterministic test vectors, which is possible since the ATPG tool knows how the circuit is constructed. When BIST is used, another approach has to be used. The BIST logic has to be made so that it effectively can apply a high number of test vectors to get sufficiently high fault coverage. The straight-ahead approach is to exhaustively test the circuit. This means that all possible combinations of ones and zeros are used at the inputs to combinational logic. The number of possible combinations in today's circuits is astronomical, and it is not an option to do this. The solution is to try to make the BIST logic make pseudo exhaustive test vectors. This means that all logic cones are exhaustively tested. The result is that the entire chip is exhaustively tested, and 100% fault coverage is guarantied to stuck-at and bridging faults.

BIST can be divided into two main categories, intrusive and non-intrusive BIST. The main difference between these two are the way the TPG and ORA are implemented in the circuit. For a solution using intrusive BIST, already existing flip-flops are used in the generation of TPG and ORA. This means that there will be a performance penalty for the circuit as additional logic, which might affect the critical path, is added to the circuit. A non-intrusive BIST solution does not use existing flip-flops in the circuit to make TPG and ORA. The CUT is unaffected as TPG and ORA are added as external modules, which connect to the CUTs inputs and outputs.

Examples of intrusive BIST solutions are BILBO and circular BIST B. Koenemann and Zwiehoff [1979], [Stroud, 2002]. In BILBO all registers can be TPG and ORA. Since a register can't function as both TPG and ORA at the same time, BILBO configures some registers as TPG and some as ORA. Then the logic between them is tested. When the logic has been tested, the registers are reconfigures so that untested logic can be tested, by changing which registers operates as TPG and ORA. Several test cycles might be necessary as it is likely that more registers has to operate as TPG than ORA. This is because a logic cone can have inputs coming from different registers, which all has to be TPGs to test the logic cone. This leads to the new optimization problem of minimizing the number of test cycles needed by selecting which registers to be TPG and ORA in the different test cycles. A thing to notice is that BILBO works well for pipelined architectures. Another thing is that scan is also needed to retrieve the responses from the test cycles. Circular BIST also uses existing flip-flops for TPG and ORA. One thing that is different from BILBO is that the responses from the CUT here are used as new test patterns. This means the pseudo exhaustive testing isn't guarantied.

BIST is rarely used to test an entire chip. This is due to different types of logic and structures used within the chip, such as RAM and general sequential logic. Often several different BIST circuits exist in a circuit, some optimized for testing RAMs and other for testing generic logic. For a device containing several BIST circuits, one can save test time by running more than one at a time. One of the main problems is to determine which to run simultaneously, as one need to consider the total dissipated power during test.

One thing that makes BIST very useful is the fact that it makes it possible to test the circuit in the field. Usually circuits are tested in a test machine. This means that it can't be connected to any other logic. If a circuit has BIST and it is implemented with input and output isolation, the circuit can still be tested on a circuit board if the BIST logic supports start and stop by JTAG, software, or by any other method.

#### 2.6.1 Test pattern generation

Pattern generation can be done in several ways. Counters, accumulators, MAC-units and similar can be used as pattern generators. Their performance differs, and one will be better than another in some cases. The types of patterns made are different from the deterministic patterns made by ATPG, which target specific faults. Random patterns are of little value since one needs to know the patterns to know what signature to expect. For this reason pseudo random patterns are often used when random patterns are preferred. Counters do not generate random patterns, but still they can generate all possible patterns given enough time. For large counters this is impractical as the most significant bits switches very slow compared to the least significant bits. This result in that logic connected to the most significant bits needs very long time before they are tested.

On of the most common pattern generator used is the linear feedback shift register (LFSR). It is a pseudo random pattern generator, as its output have random characteristics. A LFSR consists of a shift register with feedbacks using XOR-gates. The location of the feedback taps is determined from primitive polynomials. The feedback can be made in two ways, internal and external. Figure 8 shows a 3 bit LFSR with external feedback and figure 9 shows a 3 bit LFSR with internal feedback.

Figure 8: LFSR with external feedback.

Figure 9: LFSR with internal feedback.

The external LFSR is just a shift register with feedback into the first register. If the LFSR is used to feed parallel scan chains, with one scan chain connected to each register output, the data in the different scan chains will be highly correlated as only one bit differ between them. The internal feedback performs better in this case as the internal XOR-gates help in randomizing the data between the scan chains. For large LFSR with several feedbacks the external feedback will also result in a LFSR with longer critical path, making it slower than the internal feedback solution. For these two reason the internal feedback register is the preferred choice when designing a LFSR.

Several other aspects also need to be considered when designing a LFSR. The most important is that it can't be initialized to the all zero state. If a LFSR is in the all zero state it will remain there, as there is no change in the feedback loop. This means that the all zero pattern can't be applied to a circuit using LFSR as TPG. To make sure that all other patterns can be applied one need to make sure that the LFSR is able to run for the maximum length. This is achieved by using a primitive polynomial to determine the construction of the feedback. The size of a LFSR is often referred to the degree of the polynomial used. Since the patterns made are determined by the initial state of the LFSR, and large LFSR makes it impractical to run it for the maximum length, it is often necessary to add additional logic to the LFSR making it possible to set the start value. This is referred to as reseeding.

As mentioned, there are some issues to be considered if a LFSR is used to feed parallel scan chains. One of them is structural dependency. If parallel output is used directly from the LFSR, parallel scan chains contains the same data just shifted by one bit. This means that not all possible vectors can be applied in an n-by-n array produced by the LFSR. Since not all possible patterns can be applied this will reduce the possible obtainable fault coverage. To reduce this problem internal feedback should be used, and using feedback with many XOR-gates is desirable.

Another problem is linear dependencies. Consider the example where a 4 bit LFSR is used to generate vectors for a 10bit scan chain. Since the all zero pattern can't be made by the LFSR, the length of the LFSR is a 15bit sequence before it starts to repeat. If exactly 10 bits are shifted into the scan chains for each test vector only 3 unique test vectors will be generated,

and of course this is not enough to test all possible faults. The solution to this problem is to avoid cases where the length of the scan chains and the length of the LFSR have a common divisor other than 1.

$$1 = GCD(N_{FF}, 2^n - 1) \tag{4}$$

If GCD is a function which calculates the greatest common divisor the equality shown in equation 4 can be used as a requirement. Here  $N_{FF}$  is the number of flip-flops in the longest scan chain and n is the number of flip-flops in the LFSR. In the case of the 4bit LFSR and 10bit scan chain, one can see that they both have the common divisor 5. If one instead of shifting exactly 10bits shifts 11bit (setting  $N_{FF}$  to 11), one will see that 11 and 15 don't have any other common divisor than 1. This means that a maximum length test is possible by shifting 11 bits into the 10 bit scan chain for each test pattern that is applied.

Other considerations to make are the size of the LFSR and the characteristic polynomial. The size, n, should be greater than the span of any logic cone in the design driven by the scan chain. The span is the number of scan elements between the two inputs to a logic cone that are farthest away from each other in the scan chain. One other requirement for the size of the LFSR is that n are chosen so that equation 5 is satisfied.

$$2^n - 1 > N_{FF} * N_{TV} \tag{5}$$

There n is the size of the LFSR,  $N_{FF}$  is the number of flip-flops in the longest scan chain, and  $N_{TV}$  is the number of test vectors to be applied. Using this requirement helps in reduce linear dependencies problems.

Regarding the characteristic polynomial, it might affect the linear dependencies, as they can be a function of the polynomial and the location of the scan flip-flop driving a logic cone. For this reasons it might in some cases be a solution to have an LFSR with programmable polynomial.

It should be stated that LFSR isn't good for all circuits, and in these cases modifying the patterns or using other TPG might be necessary.

### 2.6.2 Output response analysers

Output response analysers are used to generate a single pass or fail indication as a result of the BIST sequence. Usually it is a multiple bit value, and it is only necessary to read this value to determine if the circuit is fault free or not. Since thousands of test vector responses are compacted into a single value there is a possibility of fault masking. Fault masking occurs when a fault masks another fault by changing the signature back to the value indicating a fault free circuit. Different ORAs have different properties and different likelihood of fault masking. In many ways ORAs are similar to TPG. Accumulators, MAC-units, and counters can be used here with the response as input data.

If several identical circuits are tested at the same time a comparisonbased analyser can be used. It only requires one XOR-gate per bit and one N-input OR/NOR gate. By comparing the outputs of the different circuits one can easily find if one of the circuits has a different output than the others. The comparison-based analyser has low area overhead, but its use is restricted. Also, aliasing will occur if both circuits connected to the same XOR-gate has the same defect. Another problem with it is that it is not guarantied that the ORA is completely tested.

A counting based output response analyser counts the number of ones or zeros that reaches the output of the circuit. Here one counter is required for each output, so the area overhead can be quite large. Aliasing can occur if the number of ones and zeros at the output are unchanged for a faulty circuit, or it the counter overflows and this is not controlled. The overflow of the counter can easily be fixed by using a large counter, or by using the overflow bit as an additional input.

Parity analysers are a form of counting analyser. It is very simple, as it is a one-bit counter and only checks whether there are an even or odd number of ones in the output. It works well for serial outputs, such as scan chain outputs, but since it is only one bit, any even number of faults will result in fault masking, and for this reason it is not very attractive as a fault analyser.

Instead of counting the number of ones and zeros one can use an accumulator based ORA. In this case all outputs are used as inputs to an accumulator. The signature is the value of the accumulator after the BIST sequence. This value can then be read by ATE and compared externally or compared to a value stored in ROM. The main problem with accumulatorbased analysers is that they will overflow very fast if they are implemented as single precision accumulators (the size of the accumulator is the same as the number of outputs from the circuit). To solve this one can use double precision accumulators. In this approach the carry output from the single precision accumulator is used as input to a second adder so that no information is lost due to the carry from the first part. This approach uses more area as two adders are made. Another option is to feed the carry from the single precision accumulator to a flip-flop and then use the output from this flipflop as carry input for the accumulator. Now the carry output information remains in the circuit, but it can still be masked by other faults.

One of the most common response analysers is the multiple input shift register, MISR. It is made in the same way as an LFSR, but in addition has one XOR-gate at each flip-flop input, which is connected to a signal that is to be compacted.

MISRs are also susceptible to fault masking. One way this can happen is when a fault from one scan chain enters the MISR, making a bit flip value.

Figure 10: MISR with internal feedback.

Then in the next clock cycle another fault enters the next bit in the MISR, and as the first bit is shifted down the MISR, this bit switches back the first bit, resulting in a signature for a fault free circuit. To reduce the likelihood of fault masking one can use large MISRs, as the probably of aliasing is approximately  $2^{-n}$ , where n is the degree of the characteristic polynomial used for the MISR. Using primitive polynomials and internal feedback also helps in reducing the probability of fault masking. One last requirement for the use of MISR as fault analyser is that the signature must be non-zero if the MISR is initialized to zero. The reason for this is that, as for LFSR, the MISR has the property that it will remain in that state if all inputs are zero.

There is one other source of fault masking. Most circuits will have a large amount of outputs, and it is not desirable to make very large MISRs or accumulators. To reduce the size of the needed response analysers, concentrator logic is added between the output and the analyser. The concentrator is made of XOR-trees. This means that any even number of faults entering the same XOR cone will result in fault masking.

There is one approach that can be used to always reduce the likelihood of fault masking. By periodically monitoring the signature to check for fault detection one can detect that a fault has occurred before it is masked, and one can also abort the testing before it is finished, and save test time.

### 2.6.3 Test points

One of the main problems with testing is to control and observe internal nodes in the circuit. ATPG tools can make special test vectors that set specific values to specific nodes in the circuit. This can be done to propagate the value of a specific node to one of the outputs. For BIST this is harder as the patterns are random, and for this reason the fault coverage will be lower than for ATPG. One way to improve fault coverage, both for ATPG and BIST, is to insert test points. A test point is a point that is easily controllable, observable or both. Only a few test points can increase the fault coverage of the circuit significantly.

A control point can be made in several ways. If the node only needs to

be controlled to a specific value, zero or one, an AND or OR-gate can be used. If it needs to be controlled to different values during test a multiplexer can be used. The multiplexer will then select between the normal input and a test input, and it can be controlled by a test enable signal.

An observation point can be made of just additional wiring connecting the point to an additional output or an existing output via a multiplexer. Observation points will for this reason have less impact on the circuit, compared to control points.

For a BIST solution test points have an additional important task. The inputs of the circuit need to be controlled to prevent unknown data from reaching the response analyser. One way to achieve this is to add multiplexers in front of the inputs and supply data to these multiplexers from the TPG. The outputs are also often controlled to a known state, and at the same time the outputs are observed by connecting them to the inputs of the ORA.

The two main problems with test points are area overhead and additional delay. Test points ads additional area due to the additional logic, but also the additional routing contributes to the area overhead. If few test points are added, the additional area overhead might not be an issue, but the additional delay might be. If the test point is inserted in a critical path, the additional delay of a multiplexer or other gate will affect the circuit's performance, which might not be acceptable. Since observations points don't need additional logic to be inserted they are preferred over control points as the performance penalty are less for observation points.

### 2.6.4 Increasing the fault coverage

Due to the different problems described, it might be necessary to use large LFSR compared to the span of a logic cone. This might lead to LFSR with 20-25 bits or more, making it impossible to apply the maximum test length due to test time cost. To further increase the fault coverage one need to add some other approaches. One can be to support reseeding of the LFSR, or the support of changing the characteristic polynomial of the LFSR. Both of these can be supported by a test interface such as boundary scan.

In some cases it is not enough to use just a pattern generator and a response analyser to get sufficient fault coverage. Even if the pattern generator can make all possible patterns, the time required to do so may be excessive, and other means for applying the required patterns are necessary. There are some options to consider. The patterns can be applied from an external tester through scan or by some other method. This means that the external tester is required, and that a complete test can't be done without it. Another solution is to store the patterns internally in an ROM, but this will require additional area, and may be to costly if the required number of stored patterns is high. Another approach is to add logic that can modify the vectors generated by the pattern generator such that they will cover the hard to detect faults faster. Example of additional logic is phase-shifters, weighting logic and bit flipping logic.

### 2.6.5 Phase shifters

If a LFSR is used as TPG for a scan design, and several scan chains are connected to adjacent bits of the LFSR, neighbouring scan chains will have highly correlated data. The test data seen by the CUT will not be pseudo random; as the data in neighbouring scan chains have only one bit shift in difference. The worst case is for the LFSR with external feedback. A solution to this problem is to add logic that shifts data in neighbouring scan chains by more than one bit. The straight-ahead approach is to add shift registers with different length between all of the LFSR outputs and scan chains inputs. This approach result in large area overhead and is not a good choice. Instead one can construct a phase shifter from XOR-gates. A phase shifter is constructed by taking different outputs from the LFSR and XORing them together. This produces the same output sequence as the LFSR, but shifted by a number of clock cycles. An algorithm for calculation of which LFSR outputs to XOR together to generate a given number of shift delays is described in [Rajski and Tyszer, 26-30 Apr 1998].

A phase shifter has a number of interesting properties. It has low area overhead, only one additional XOR-gate per scan chain on average. This means that the LFSR and phase shifter has approximately the same area overhead as a TPG generated from CA-registers, but the LFSR and phase shifter performs better. The performance penalty is a delay of two XORgates between the LFSR and scan chain inputs on average. One of the most interesting properties of the phase shifter is that it allows one to generate outputs to more scan chains that there are outputs from the LFSR. This means that one can save additional area by making the LFSR smaller, but at the same time having a large amount of scan chains. The only requirement is that the size of the LFSR satisfies the equation 6.

$$2^n - 1 \ge N_{FF} * N_{SC} \tag{6}$$

Here n is the size of the LFSR,  $N_{FF}$  is the number of flop-flops in the longest scan chain, and  $N_{SC}$  is the number of scan chains.

# 2.6.6 Weighting logic

When using LFSR as TPG, and the output is random, there is an equal probability of a one or a zero entering the scan chain. Some circuits have random hard to detect faults, meaning that there is a very little chance for a random pattern to detect the faults. In these cases, additional logic might be added to the TPG to make it able to generate vectors that are more likely to detect these faults.

Weighting logic is used to change the distribution of ones and zeros in the test patterns. Weighting logic can be made up of AND-gates or ORgates. Using AND-gates will increase the likelihood of zeros and using ORgates will increase the likelihood of ones in the test vectors. To generate a set of different weights several outputs can be ANDed or ORed together. Multiplexers can then be used to select the different weights.

The area overhead of a weighting logic can be significant compared to the LFSR and phase shifter if several weights are supported. Several AND- or OR-gates are required, and large multiplexer have to be used for selection of the different weights. The fault coverage only increases with a few percents when weighting is used, and it might require a huge number of test vectors. For this reason, weighting is usually used when external test cant be used, and BIST is used for a complete onchip test [Kusko et al., 2001]

### 2.6.7 Bit flipping

Bit flipping logic is a more advanced method of changing the test vectors to increase the fault coverage. Individual bits in the test vectors are flipped, and a bit flipping function controls the flipping. The bit flipping function can uses the state of the BIST logic as inputs, for instance pattern counters, bit counters and any other counters that are available. The goal of bit flipping is to match deterministic test vectors to the ones made by the TPG by modifying the test vectors generated by the TPG [Wunderlich and Kiefer, 10-14 Nov 1996], [Gherman et al., May 2007].

To determine which bits should be flipped one need to do fault simulation. First the vectors from the BIST logic is fault simulated to determine which faults are undetected and which test vectors that don't detect faults. One then selects one of the undetected faults, and finds the one test vector, which previously didn't detect a fault, that most closely matches the test vectors that detect this fault. Logic is made to modify this test vector. This is then done for all remaining faults, and then the new BIST logic is simulated to control that all faults are detected.

This method have low area overhead, and gives high fault coverage. Since delay faults have lower random testability, this method might help significantly in increasing the fault coverage. The main problem with bit flipping is that it can take a long time to generate the bit flipping function, and if the CUT is changed in some way it all have to be redone as the test vectors might have changed.

# 2.7 Scan based BIST

Scan is one of the more common approaches to testing. ATPG are use together with ATE to performs testing on circuits. Scan based BIST moves the pattern generator inside the circuit and connects it to the scan chains. A response analyser is also connected to the scan outputs, and compacts the responses into a single value. A scan based BIST design allows several CUTs to share a common TPG and ORA. If all the CUTs have their own scan chains multiplexers can be used to connect the different scan chains to the TPG and ORA, allowing them to be tested separately. This can help in reducing the size of the ORA and TPG.

In addition to the TPG and ORA, a BIST controller is needed. The controller is used to control how many bits are shifted into the scan chains, and how many patters have been applied. A simple BIST controller can be made of an N + M bit counter, where the N least significant bits are used to count the number of bits shifted into the scan chains, an the M most significant bits are used to count the number of patterns applied. This means that the maximum length of a test using this approach is approximately  $2^{N+M}$  clock cycles.

One of the problems with scan based BIST, and other BIST solutions, is that random patterns are less effective on detecting faults than deterministic patterns. According to [Stroud, 2002] approximately ten times more patterns are needed to obtain the same fault coverage with a scan based BIST design compared to ATPG scan. This can of course vary greatly between different designs. This means that if the same scan speed and the same number of scan chains are used, as for external scan testing, the testing time can be quite large. But since a BIST design isn't restricted by the number of input and output pins on the circuit, one can have a large amount of internal scan chains connected to a TPG, and by this reducing the number of clock cycles needs to shift new test vectors into the scan chains. The shifting speed might also be increased since the speed is no longer limited by the speed of the input and output pins, or by external testing equipment. Applying these two steps can significantly reduce testing time for a scan based BIST design, and should always be considered.

One limitation that might affect the scan speed is the total power dissipation of the circuit. Scan is one of the most power demanding operations since almost the entire logic will be switching every clock cycle. Due to this, scan based BIST might not be operated at the maximum frequency of the circuit during shifting of test vectors. If this is the case it will need a clock controller to generate the appropriate clock signals, as at-speed is necessary during the capture cycle to perform delay testing.

STUMPS, or Logic BIST, is one of the most common forms for scan based BIST. It uses an LFSR for TPG, and MISR for ORA. Additional logic such as phase shifters, bit flipping and weighting are often used. STUMPS are usually not intended as the only means of testing, so it is usually followed by test data from an external tester. The main reasons for using such approach is to reduce test cost. This is achieved by shorter test time or by reducing the amount of tester memory needed, or both. Fault coverage for LBIST can vary from 65% to 80% for large industrial designs. The large variation is due to the fact that different circuits can have different amount of hard to detect faults. Inserting additional test points in the circuit can significantly increase the fault coverage by reducing the amount of hard to detect faults.

One other scan based BIST design is the hybrid design [Das and Touba, 2000]. It combines external test patterns with internal test patterns at the same time. The idea is that merging random data with deterministic data will shorten the test time, compared to the STUMPS approach, and at the same time save tester memory. One of the problems is that the test can't run faster than the external testing equipment. This means that this approach is a good choice if tester memory is the problem, and this approach is used to reduce the amount of data stored in the testers memory.

# 2.8 Cost of test

The cost of testing contributes to a large portion of the total cost of manufacturing. In state of the art circuits the test cost is close to half the cost of the device. The test cost can be modelled in several ways, depending on what type of test approach is used. The two most common parameters to model test cost on are time used and memory footprint of the test vectors. One can say that these two are almost the same, as at a given test speed the amount of memory used will correspond to a given amount of time. Still there is a small difference, as the argument often is that a cheaper tester can be used if the memory footprint of the test vectors is small. For circuits using BIST additional parameters needs to be considered. The area overhead of the BIST logic will add cost to the circuit. The development cost of the BIST logic should also be considered, as this can be large in some cases. The development cost is much harder to model as this cost can be distributed over every manufactured device, but as this number is unknown, the cost of BIST development for each device is also an unknown. Since it is an unknown, the development cost is usually left out of the equation.

Looking at the STUMPS testing approach, one can easily see that the equation for the chip cost can be quite complicated as both BIST and ATPG are used. The problem with this approach is to find the optimal number of BIST and ATPG patterns. To few BIST patterns means that to many ATPG patterns are needed, but they might require a long time to be applied, which can increase test time and cost. To many BIST patterns will also increase test cost due to longer BIST testing time. In other words, one needs to find the optimal ratio between BIST and ATPG vectors. Since the number of

ATPG top up patterns only can be determined after the BIST patterns are simulated, it can be a tedious job to fine the optimal number of BIST and ATPG patterns as several simulations are required.

If one wants to find out how much can be saved in this case, one need to calculate the total cost for both cases. Starting with the pure ATPG testing scenario with a scan design, one can easily calculate the cost of the device. Knowing the area,  $A_{CUT}$ , of the circuit, area unit cost  $C_{Area}$ , the length of the longest scan chain,  $N_{FF}$ , and the number of test vectors,  $N_{TV}$ , the tester speed  $TS_{ATPG}$ , the required time for launch and capture cycles  $T_{LC}$  and the unit time cost  $C_{Time}$ , one can find a formula for the cost,  $C_{ATPG}$ , as:

$$C_{ATPG} = A_{CUT} * C_{Area} + \left(\frac{N_{FF} * N_{TV}}{TS_{ATPG}} + N_{TV} * T_{LC}\right) * C_{Time}$$

(7)

The equation for the STUMPS approach is much the same, but additional parameters are used. The parameters have the same meaning, and the suffix ATPG and BIST are used to separate BIST parameters from ATPG parameters. For instance  $A_{BIST}$  is the area of the BIST logic.

$$C_{BIST+ATPG} = (A_{CUT} + A_{BIST}) * C_{Area} + \left(\frac{N_{FFBIST} * N_{TVBIST}}{TS_{BIST}} + \frac{N_{FFATPG} * N_{TVATPG}}{TS_{ATPG}} + (N_{TVBIST} + N_{TVATPG}) * T_{LC}\right) * C_{Time} \quad (8)$$

When subtracting the two cost functions from each other one will get the test cost saving, as in equation 9. The cost due to the area of the CUT will disappear, as it is part of both equations.

$$C_{reduction} = C_{ATPG} - C_{BIST+ATPG} \tag{9}$$

One can also easily calculate the amount of saved test time by removing the area cost from the equations and just looking at the time aspect. Doing this one get equations 10 and 12 showing the required time for each of the two cases.

$$T_{ATPG} = \frac{N_{FF} * N_{TV}}{TS_{ATPG}} + N_{TV} * T_{LC}$$

(10)

$$T_{BIST+ATPG} = \frac{N_{FFBIST} * N_{TVBIST}}{TS_{BIST}} + \frac{N_{FFATPG} * N_{TVATPG}}{TS_{ATPG}} + (11)$$

$$(N_{TVBIST} + N_{TVATPG}) * T_{LC}$$

Subtracting these two and dividing by the time for ATPG test one get the percentage of saved time. Changing the values for test speed, length of scan chains and number of test vectors one can investigate how the amount of saved time will change.

$$T_{Saved\%} = \frac{T_{ATPG} - T_{BIST + ATPG}}{T_{ATPG}} \tag{12}$$

# 2.9 Clock source for use in delay fault testing

One challenge in delay testing is to know which speed to use as the maximum speed of the circuit. Process variations are a known fact, and can significantly affect the maximum frequency of a device. One can select the worst case parameters and calculate the maximum frequency for the worst temperature and voltage corner and use this as the maximum frequency for all devices. Although this would work, it also mean that a large portion of the circuits actually are able to perform much better than the frequency they are tested at. A possible solution to this is to add an oscillator to the design and use this oscillator as clock source for the launch and capture cycles during delay testing. There is one important restriction if this is going to work. The oscillator speed must track the variations of the maximum frequency of the critical path in the circuit in different process variation corners and for different voltage and temperature corners. Another problem is that it is hard to know the maximum frequency of the device before it is finished due to the fact that routing delay contributes significantly to the total delay. For this reason such an oscillator will need some means for calibration to match the critical path after the finial layout is done.

A benefit of this approach is that one is able to measure the actual maximum frequency of the device. This again can be used to do speed binning of the manufactured devices. Speed binning can be important for several reasons. First, one can sell devices, which are able to operate at very high frequencies at a higher price, but more important, one can sell devices that work at lower speed than what the actual specification specifies at a lower price instead of scrapping them.

# 3 Test chip design

The goal is to make a design for a chip that can be used in research on delay fault testing. As scan-testing is one of the most used test approaches today, and is likely to be a part of the design flow of many companies, it can be interesting to find a solution that uses this with some modifications to achieve delay testing. In addition, BIST is becoming more and more popular as a means to reduce test cost, and for this reason a BIST solution will also be added to this design to compare BIST to regular ATPG-tools.