# Vectorized 128-bit Input FP16/FP32/ FP64 Floating-Point Multiplier

Espen Stenersen

Master of Science in ElectronicsSubmission date: June 2008Supervisor:Per Gunnar Kjeldsberg, IETCo-supervisor:Torstein Dybdal, ARM Norway AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

In 3D graphics, several floating-point formats are used in computations. The task is to make a floating-point multiplier with the current features:

- 256-bit input vector and 128-bit output.

- Supporting FP16/FP32/FP64 inputs.

- IEEE754 conforming.

- 5 step pipeline.

- Simple handshake interface.

Depending on input formats the following operations should be performed:

- Vec4 FP16 multiply uses a 128-bit input vector, and produces a 64-bit output vector.

- Vec4 FP32 multiply uses a 256-bit input vector, and produces a 128-bit output vector.

- Vec2 FP64 multiply uses a 256-bit input vector, and produces a 128-bit output vector.

The assignment is a continuation of the project task, where different floating-point multiplier architectures were proposed, analyzed and evaluated. Based on this, further analysis has to be made before an architecture is chosen. Implement the chosen architecture at register transfer level, for testing and synthesis.

Assignment given: 15. January 2008 Supervisor: Per Gunnar Kjeldsberg, IET

# Abstract

3D graphic accelerators are often limited by their floating-point performance. A Graphic Processing Unit (GPU) has several specialized floating-point units to achieve high throughput and performance. The floating-point units consume a large part of total area and power consumption, and hence architectural choices are important to evaluate when implementing the design. GPUs are specially tuned for performing a set of operations on large sets of data. The task of a 3D graphic solution is to render a image or a scene. The scene contains geometric primitives as well as descriptions of the light, the way each object reflects light and the viewer position and orientation.

This thesis evaluates four different pipelined, vectorized floating-point multipliers, supporting 16-bit, 32-bit and 64-bit floating-point numbers. The architectures are compared concerning area usage, power consumption and performance. Two of the architectures are implemented at Register Transfer Level (RTL), tested and synthesized, to see if assumptions made in the estimation methodologies are accurate enough to select the best architecture to implement given a set of architectures and constraints. The first architecture trades area for lower power consumption with a throughput of  $38.4 \ Gbit/s$  at 300MHz clock frequency, and the second architecture trades power for smaller area with equal throughput. The two architectures are synthesized at 200MHz, 300MHz and 400MHz clock frequency, in a 65nm low-power standard cell library and a 90nm general purpose library, and for different input data format distributions, to compare area and power results at different clock frequencies, input data distributions and target technology.

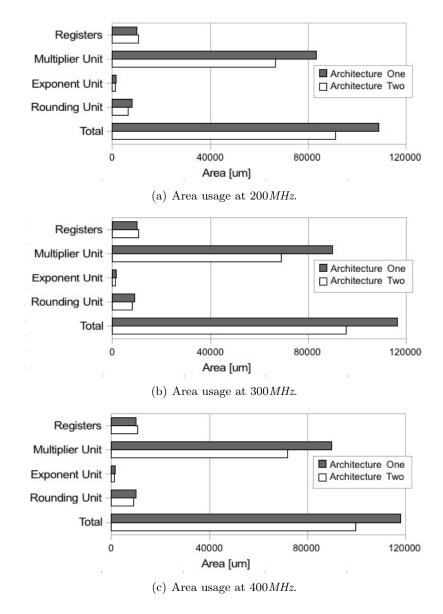

Architecture one has lower power consumption than architecture two at all clock frequencies and input data format distributions. At 300MHz, architecture one has a total power consumption of 1.9210mW at 65nm, and 15.4090mW at 90nm. Architecture two has a total power consumption of 7.3569mW at 65nm, and 17.4640mW at 90nm. Architecture two requires less area than architecture one at all clock frequencies. At 300MHz, architecture one has a total area of  $59816.4414\mu m^2$  at 65nm, and  $116362.0625\mu m^2$  at 90nm. Architecture two has a total area of  $50843.0\mu m^2$  at 65nm, and  $95242.0469\mu m^2$  at 90nm.

# Preface

This thesis concludes my Master's degree in Electrical Engineering at Norwegian University of Science and Technology (NTNU), and is a continuation of my 2007 autumn project. The assignment is given by ARM Norway, and involves research, implementation, testing and synthesis of a vectorized floating-point multiplier. The work was carried out from January 2008 to June 2008, and the topic was interesting, challenging and very instructive.

I spent a lot of time researching floating-point implementations in hardware, especially floating-point rounding, in addition to power consumption in sub-micron technologies. IEEE specifies a detailed standard for binary floating-point arithmetic, but leaves the implementation completely to the designer. Two different vectorized floating-point multipliers was implemented using the Verilog Hardware Description Language, which I had little knowledge of before starting this assignment. A significant amount of time was spent developing a sufficient testplan for the designs, and by researching and understanding the tools used for synthesis and the Tcl scripting language. Working on this thesis, I learned much about floating-point arithmetic in hardware, the synthesis and optimization process, and power consumption in different target technologies. I also gained further knowledge of digital design in general, and the Verilog Hardware Description Language.

A special thank goes to my supervisors, Associate Professor Per Gunnar Kjeldsberg (NTNU), and Torstein Hernes Dybdahl (ARM) for their guidance, feedback and interest in this assignment. I would also like to thank my fellow students for comments and constructive questions, my family and friends.

Espen Stenersen Trondheim, June 2008.

# Contents

| 1        | Inti       | roduction 1                                                                                                                            |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1        | Floating-Point Multiplication                                                                                                          |

|          | 1.2        | Power and Area Optimized Designs                                                                                                       |

|          |            | 1.2.1 Low Power Design $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$                                                     |

|          |            | 1.2.2 Area Optimized Design                                                                                                            |

|          | 1.3        | High-Speed Multiplication                                                                                                              |

|          | 1.4        | Architecture Search-space Exploration                                                                                                  |

|          |            | 1.4.1 Power Consumption $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 7$                                             |

|          |            | 1.4.2 Area Usage                                                                                                                       |

|          |            | 1.4.3 Throughput and Delay                                                                                                             |

|          | 1.5        | Proposed Architectures                                                                                                                 |

|          |            | 1.5.1 Architecture One                                                                                                                 |

|          |            | 1.5.2 Architecture Two                                                                                                                 |

|          |            | 1.5.3 Architecture Three $\ldots \ldots 10$ |

|          |            | 1.5.4 Architecture Four                                                                                                                |

|          | 1.6        | Thesis Organization and Main Contributions                                                                                             |

| <b>2</b> | Arc        | chitecture Estimations 13                                                                                                              |

|          | 2.1        | Power Estimation Methodology                                                                                                           |

|          | 2.2        | Power Estimation                                                                                                                       |

|          | 2.3        | Area Estimation                                                                                                                        |

|          | 2.4        | Performance Estimation                                                                                                                 |

|          | 2.5        | Trade-Off Considerations                                                                                                               |

| 3        | Imr        | plementation 25                                                                                                                        |

| Ŭ        | 3.1        | Choosing Architecture                                                                                                                  |

|          |            |                                                                                                                                        |

|          | 3.2        | 0                                                                                                                                      |

|          | 3.2        | Vectorized Floating-Point Multiplier                                                                                                   |

|          | 3.2        | Vectorized Floating-Point Multiplier263.2.1Inputs27                                                                                    |

|          | 3.2        | Vectorized Floating-Point Multiplier263.2.1Inputs273.2.2Outputs29                                                                      |

|          |            | Vectorized Floating-Point Multiplier263.2.1Inputs273.2.2Outputs293.2.3Architecture Description29                                       |

|          | 3.2<br>3.3 | Vectorized Floating-Point Multiplier263.2.1Inputs273.2.2Outputs29                                                                      |

| 4 | Syn          | thesis Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39  |

|---|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 4.1          | $\operatorname{Synopsys}^{\mathbb{R}}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39  |

|   |              | 4.1.1 Static Power $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40  |

|   |              | 4.1.2 Dynamic Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 40  |

|   |              | 4.1.3 Capturing Switching Activity for Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40  |

|   |              | 4.1.4 Setting Design Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41  |

|   | 4.2          | Architecture One                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41  |

|   |              | 4.2.1 Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 42  |

|   |              | 4.2.2 Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49  |

|   | 4.3          | Architecture Two                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50  |

|   |              | 4.3.1 Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50  |

|   |              | 4.3.2 Area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57  |

|   | 4.4          | Power Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59  |

|   | 4.5          | Area Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63  |

| 5 | Cor          | clusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67  |

| 0 | 5.1          | Estimation Methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68  |

|   | $5.1 \\ 5.2$ | Power Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68  |

|   | 5.2          | Area Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69  |

|   | 5.4          | Future Work   Image: Constraint of the second sec | 69  |

|   | 0.1          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 00  |

| Α | Arc          | hitecture One Verilog Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73  |

| в | Arc          | hitecture Two Verilog Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 119 |

| Ъ | 1110         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 110 |

| С | Test         | t Data Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 145 |

| D | Sim          | ulation Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 151 |

|   | D.1          | Vectorized DesignWare floating-point multiplier Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 151 |

|   | D.2          | Testbench Sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|   | D.3          | Switching Activity Simulation Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 171 |

VI

# List of Tables

| 2.1  | Normalized leakage current for logic gates [1]                  | 14 |

|------|-----------------------------------------------------------------|----|

| 2.2  | Significand multipliers static power consumption                | 16 |

| 2.3  | Significand multipliers dynamic power consumption               | 16 |

| 2.4  | Static power estimation of proposed architectures               | 17 |

| 2.5  | Total power consumption, 256-bit input vector                   | 18 |

| 2.6  | Total power consumption, 128-bit input vector                   | 19 |

| 2.7  | Architecture area comparison, FA-cells and equivalent register- |    |

|      | size                                                            | 21 |

| 3.1  | Trade-off considerations.                                       | 26 |

| 3.2  | Format encoding.                                                | 28 |

| 3.3  | Rounding modes encoding                                         | 28 |

| 3.4  | Rounding mode reduction                                         | 36 |

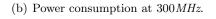

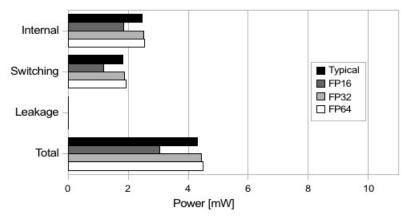

| 4.1  | Architecture one, $65nm$ CMOS total power consumption           | 42 |

| 4.2  | Architecture one, $65nm$ CMOS building blocks power con-        |    |

|      | sumption.                                                       | 43 |

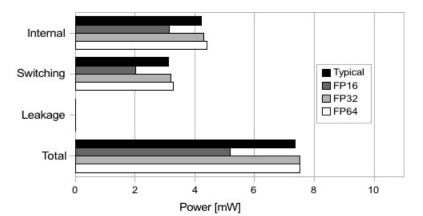

| 4.3  | Architecture one, $90nm$ CMOS total power consumption           | 44 |

| 4.4  | Architecture one, $90nm$ CMOS building blocks power con-        |    |

|      | sumption.                                                       | 44 |

| 4.5  | Architecture one, $65nm$ CMOS area usage                        | 49 |

| 4.6  | Architecture one, $90nm$ CMOS area usage                        | 50 |

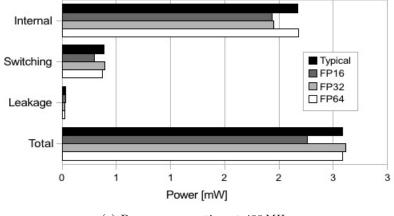

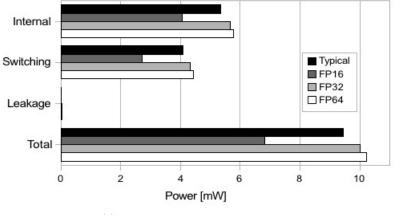

| 4.7  | Architecture two, $65nm$ CMOS total power consumption           | 51 |

| 4.8  | Architecture two, $65nm$ CMOS building blocks power con-        |    |

|      | sumption.                                                       | 51 |

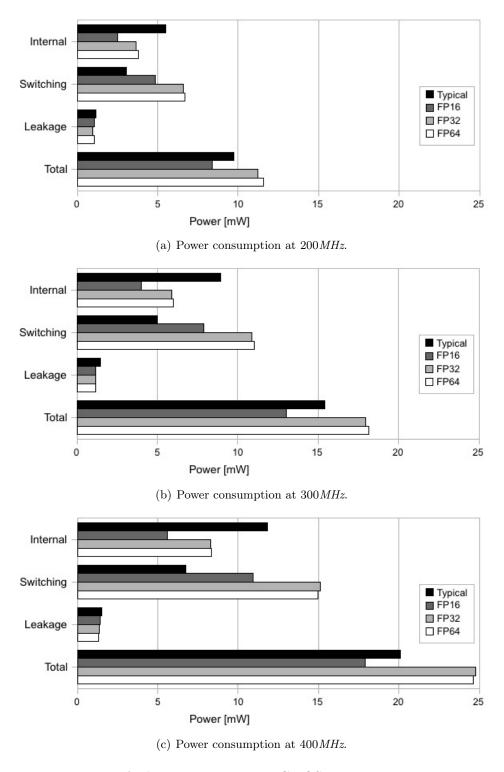

| 4.9  | Architecture two, $90nm$ CMOS total power consumption           | 52 |

| 4.10 | Architecture two, $90nm$ CMOS building blocks power con-        |    |

|      | sumption.                                                       | 52 |

|      | Architecture two, $65nm$ CMOS area usage                        | 58 |

| 4.12 | Architecture two, $90nm$ CMOS area usage                        | 58 |

|      |                                                                 |    |

# List of Figures

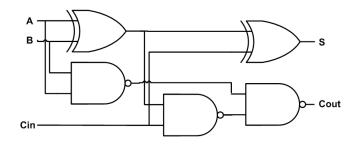

| 2.1  | Full-Adder gate-level model.                                   | 15 |

|------|----------------------------------------------------------------|----|

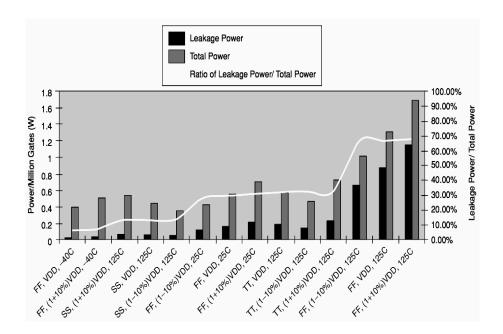

| 2.2  | Ratio of leakage power to total power in a $65nm$ CMOS library | -  |

|      | at different process corners, supply voltages and temeratures  |    |

|      | [2]                                                            | 15 |

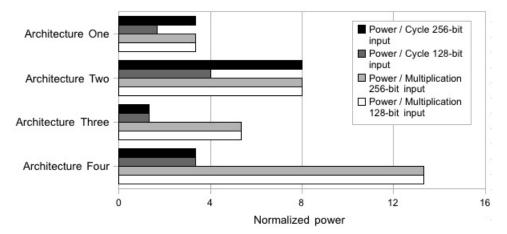

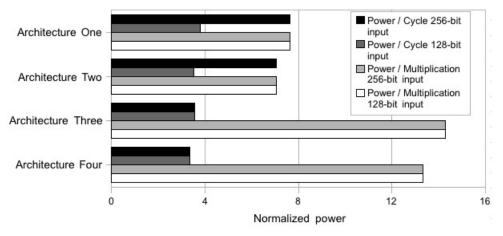

| 2.3  | Architecture power comparison                                  | 20 |

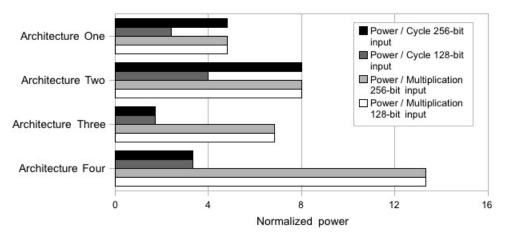

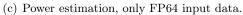

| 2.4  | Architecture area comparison                                   | 21 |

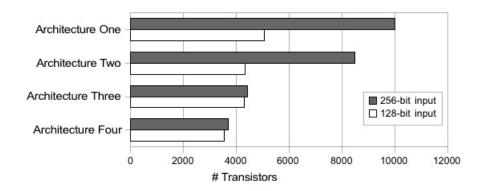

| 2.5  | Architecture latency comparison                                | 23 |

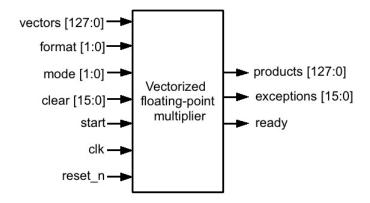

| 3.1  | Vectorized floating-point multiplier block diagram.            | 27 |

| 3.2  | First input vector layout.                                     | 27 |

| 3.3  | Second input vector layout.                                    | 27 |

| 3.4  | Clear register layout                                          | 28 |

| 3.5  | Product vector layout.                                         | 29 |

| 3.6  | Exception register layout.                                     | 29 |

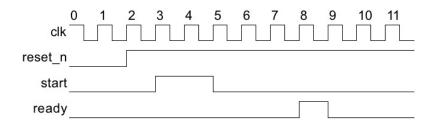

| 3.7  | Vectorized floating-point multiplier simple timing diagram     | 29 |

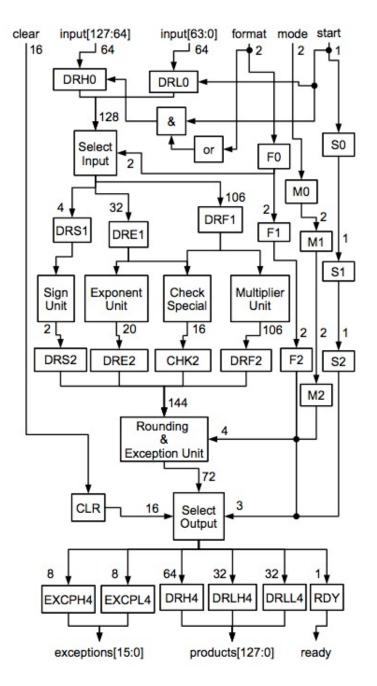

| 3.8  | Vectorized floating-point multiplier architecture drawing      | 30 |

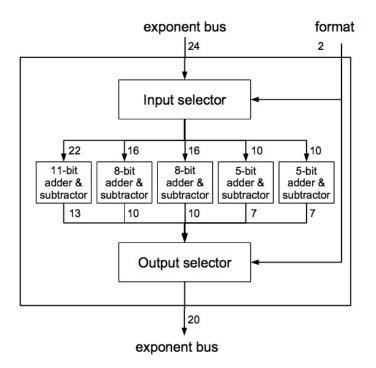

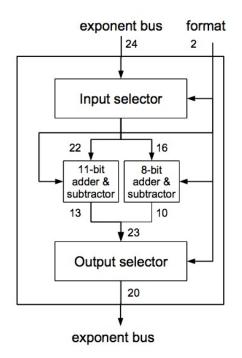

| 3.9  | Architecture one exponent unit                                 | 32 |

| 3.10 | Architecture two exponent unit                                 | 32 |

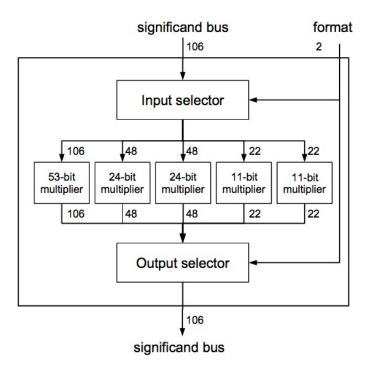

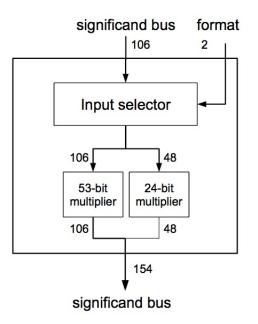

| 3.11 | Architecture one significand multiplier unit.                  | 34 |

| 3.12 | Architecture two significand multiplier unit.                  | 34 |

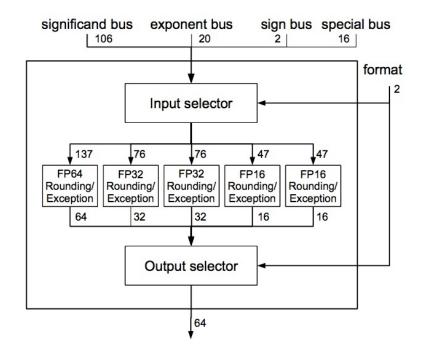

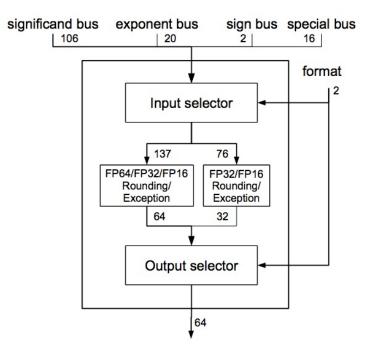

| 3.13 | Architecture one rounding and exception unit                   | 35 |

|      | Architecture two rounding and exception unit                   | 36 |

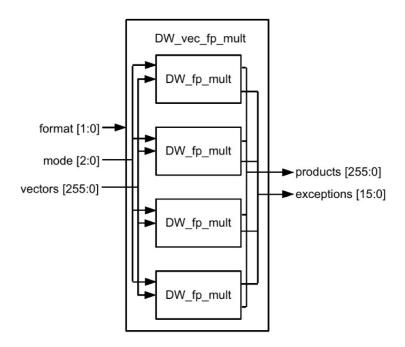

| 3.15 | DW_vec_fp_mult block diagram.                                  | 37 |

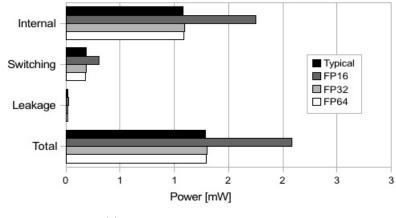

| 4.1  | Architecture one, $65nm$ CMOS power consumption                | 45 |

| 4.2  | Architecture one, $90nm$ CMOS power consumption                | 47 |

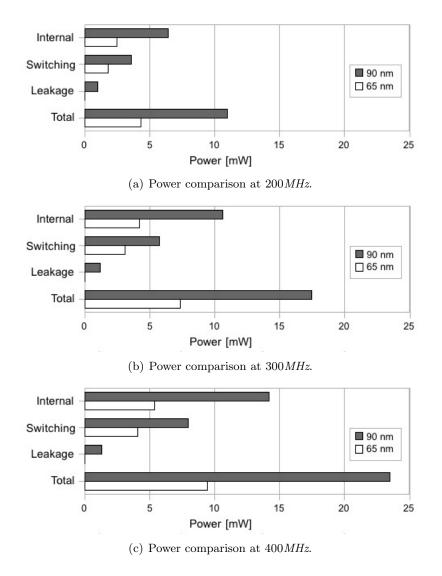

| 4.3  | Architecture one, $90nm$ and $65nm$ CMOS power comparison.     | 48 |

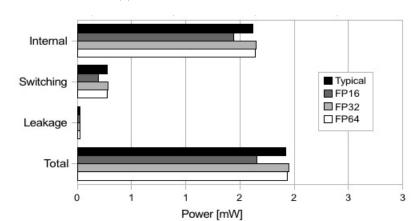

| 4.4  | Architecture two, $65nm$ CMOS power consumption                | 54 |

| 4.5  | Architecture two, $90nm$ CMOS power consumption                | 55 |

| 4.6  | Architecture two, $90nm$ and $65nm$ CMOS power comparison.     | 56 |

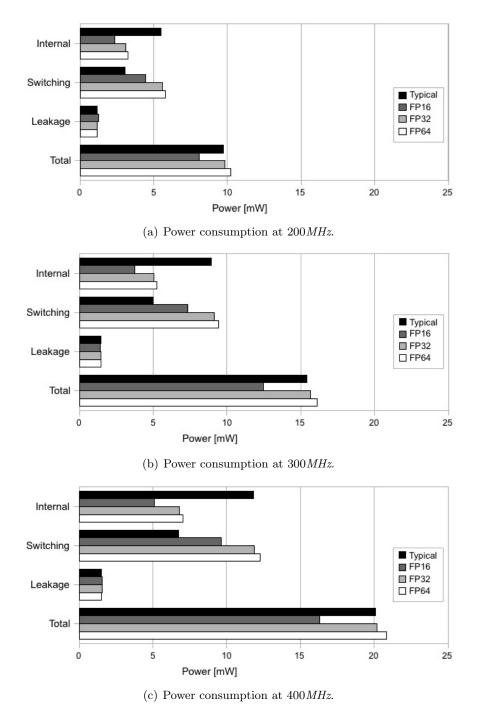

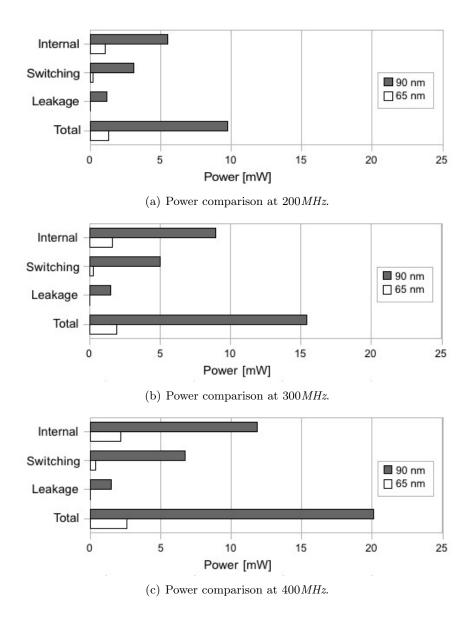

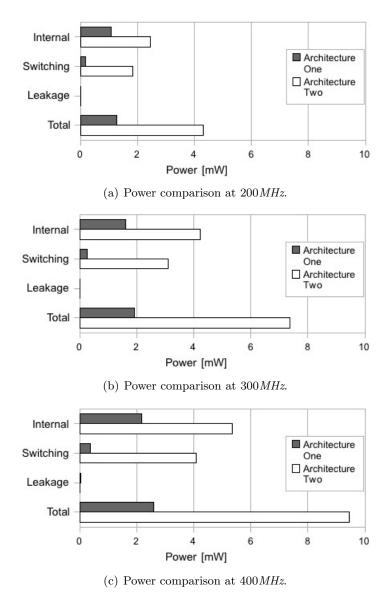

| 4.7  | 65nm architecture power comparison                             | 60 |

| 4.8  | 90nm architecture power comparison                             | 61 |

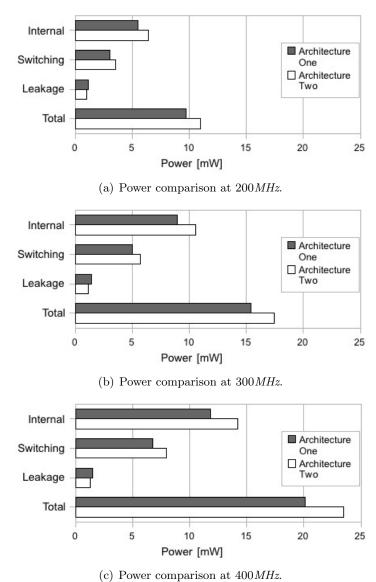

| 4.9  | Estimated vs. real power comparison.                           | 62 |

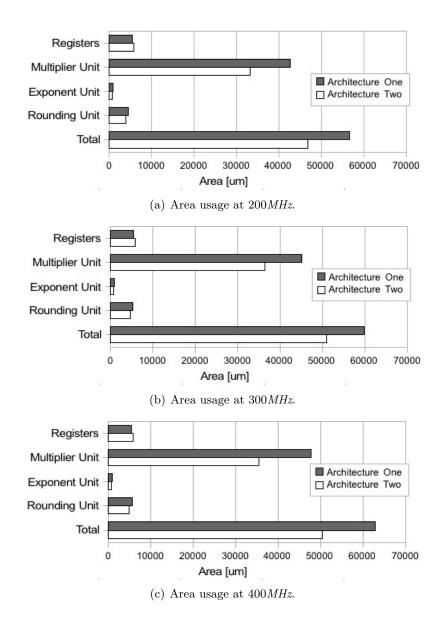

| 4.10 | 65nm | CMOS | architecture                  | area | comparison. |  |  |  |  | 65 |  |

|------|------|------|-------------------------------|------|-------------|--|--|--|--|----|--|

| 4.11 | 90nm | CMOS | $\operatorname{architecture}$ | area | comparison. |  |  |  |  | 66 |  |

# Chapter 1 Introduction

Floating-point numbers are frequently used in scientific calculations, digital signal processing applications and in 3D graphics. In 3D graphics, floating-point performance are especially demanding and several floating-point number formats are used in computations. 3D graphics accelerators have a highly parallel structure that makes them more efficient for certain algorithms than general purpose processors. The 16-bit, 32-bit and 64-bit floating-point formats FP16, FP32 and FP64 are used for high dynamic range textures, that is, where light and dark textures are spanned over a large area. All formats can be used as vertex coordinates, and the FP64 format is the minimum for graphic processing units (GPUs) to be used in scientific calculations.

ARM Norway develops hardware graphic accelerators, specifically tuned for embedded system environments, supporting the OpenGL ES and OpenVG APIs, which focus on high performance and low power consumption [3]. Mali<sup>TM</sup> 200 with GP2 fully supports OpenGL ES v2.0, v1.1 and OpenVG v1.0. Detailed information about the Mali<sup>TM</sup> 3D Graphics System Solution can be found in [4]. OpenGL ES is a royalty-free cross-platform API for full function 2D and 3D graphics on embedded systems [5], and OpenVG is a royalty-free, cross-platform API that provides a low-level hardware acceleration interface for vector graphics libraries such as Flash and SVG [6].

The purpose of this floating-point multiplier is to support three different floating-point number formats, FP16, FP32 and FP64. It is a vectorized floating-point multiplier in the sense that the input vector is a vector of operands, where three different types input vectors are supported. For the FP16 format, the input vector should be

$$[127:0] = [D1, D0, C1, C0, B1, B0, A1, A0]$$

and the output will become

$$[63:0] = [D1 \times D0, C1 \times C0, B1 \times B0, A1 \times A0]$$

For the FP32 format, the input vector should be

$$[255:0] = [D1, D0, C1, C0, B1, B0, A1, A0]$$

and the output will become

$$[127:0] = [D1 \times D0, C1 \times C0, B1 \times B0, A1 \times A0]$$

For the FP64 format, the input vector should be

$$[255:0] = [D1, D0, C1, C0]$$

and the output will become

$$[127:0] = [D1 \times D0, C1 \times C0]$$

Depending on the input vector data format, the output vector will be a 64bit or 128-bit vector of floating-point products on the IEEE 754 format.

This thesis is a continuation of my 2007 autumn project [7]. [7] presents four possible vectorized floating-point multiplier architectures with different area, power and throughput profiles. These architectures are evaluated and compared concerning area, power, throughput and latency. This thesis will further investigate power consumption of the four architectures and two architectures will be selected for RTL implementation. The implemented architectures will be tested and synthesized to see if assumptions and methodologies used to compare area and power are sufficient to select the best alternative given a set of constraints.

In a 3D graphic processing application, throughput are very important because it is operating on large data sets describing a frame or scene, where for example shading, lighting, positions and viewers perspective are considered. In any hardware implementation, area and power are usually important constraints. In a handheld, battery powered device, both area and power consumption are very important. Because of highly parallel computations, and the pipelined architecture of graphic accelerators, clock frequency is typically much lower than in a modern general purpose CPU.

This Chapter will first present the floating-point multiplication algorithm in Section 1.1. Then design strategies for low power and small area will be discussed in Section 1.2. In Section 1.3 some high-speed multiplier schemes are presented, and in Section 1.4, the vectorized floating-point multiplier architecture search-space will be explored. Section 1.5 presents the architectures evaluated in [7], and in Section 1.6, the outline and main contributions of this thesis are presented.

#### 1.1 Floating-Point Multiplication

The IEEE standard for binary floating-point arithmetic specifies a detailed standard for floating-point representation in computers [8]. Floating-point numbers are represented by a sign, an exponent and a significand, and are written as follows

$$floating - point \ number = (-1)^s \times f \times \beta^{e-bias}, \tag{1.1}$$

where s represents the sign, f the significand, e the exponent and  $\beta$  the base or radix. In IEEE 754 the base is always 2. Floating-point numbers in IEEE 754 format are biased to ensure that the exponent is always greater than zero, and thus making comparison between numbers easier. The exponent represents the range, and the significand the precision of the number.

Given to floating point numbers  $n_1 = (-1)^{s_1} \times f_1 \times 2^{e_1}$  and  $n_2 = (-1)^{s_2} \times f_2 \times 2^{e_2}$ . The floating-point product is computed as

$$n = (-1)^{s_1 + s_2} \times (f_1 \times f_2) \times 2^{e_1 + e_2 - bias}$$

This can be achieved by a simple algorithm. The floating-point multiplication algorithm is straight-forward; exponents are added and bias subtracted, significands are multiplied, and signs computed by an XOR-operation. Because the result of the significand multiplication is of width 2n, where n is the width of each significand, rounding has to be performed to obtain a final product in the IEEE specified format. The algorithm is given below.

```