# Fabrication and Electronic Investigation of GaAs nanowire/Graphene Hybrid Devices

Ambjørn Dahle Bang

Nanotechnology Submission date: August 2014 Supervisor: Helge Weman, IET Co-supervisor: Dong Chul Kim, IMTE

Norwegian University of Science and Technology Department of Electronics and Telecommunications

Master's thesis

Ambjørn Dahle Bang

Fabrication and Electronic Investigation of GaAs Nanowire/Graphene Hybrid Devices

Supervisors: Prof. Helge Weman Dr. Dong Chul Kim

Trondheim, August 9, 2014

#### Abstract

In the present study, a process for fabricating GaAs nanowire/graphene hybrid devices using electron beam lithography processing techniques is presented and demonstrated. Fabricated devices were investigated electronically by measuring I-V characteristics under a variable gate voltage.

Fabrication processes for both exfoliated and CVD-grown graphene were developed. For exfoliated graphene the outlined process is unsuccessful, as the graphene flakes were found to crumble and fall off during the first processing step following transfer. It is thus concluded that exfoliated graphene flakes are too delicate to perform any significant processing after graphene transfer.

The fabrication process was successfully demonstrated in fabrication of devices with CVD-grown graphene. However, nanowires in these devices were seen to undergo significant corrosion during the process, which is credited to the water exposure associated with graphene transfer. This was found to be an especially prominent issue for contacted nanowires, where the metal contact is believed to facilitate galvanic corrosion.

I-V characteristics and gate voltage dependence were measured for GaAs nanowire/graphene hybrid devices made with CVD-grown graphene. Large variations in the I-V behavior and gate voltage dependence was observed. This is credited to corrosion in the nanowires, which is thought to result in uncharacteristic behavior for metal-GaAs contacts. There are also indications that several devices are shortened by graphene. The electronic investigations are therefore found to be inconclusive in respect to the electronic properties of the graphene/GaAs nanowire junction. It is concluded that further developments in the fabrication process are needed to achieve GaAs nanowire/graphene hybrid devices suitable for detailed analysis.

#### Sammendrag

I den foreliggende studien blir en prosess for fremstilling av GaAs nanotråd/grafén-prøver ved hjelp av elektronstrålelitografi presentert og demonstrert. Fabrikkerte prøver ble undersøkt elektronisk ved å måle I-V karakteristikker med variabel styrespenning.

Fabrikasjonsprosesser for både eksfoliert og CVD-grodd grafén ble testet. For eksfoliert grafén var fabrikasjonsprossesen mislykket, da det viste seg at grafénflakene smuldret opp og falt av substratet i det første prosesseringstrinnet etter grafénoverføringen. Det konkluderes dermed at eksfolierte grafénflak er for sensitive til å gjøre noen signifikant prosessering etter grafénoverføringen.

Fabrikasjonsprosessen ble demonstrert til å fungere for prøver med CVD-grodd grafén. Imidlertid ble en signifikant korrosjon for nanotrådene i disse prøvene observert, noe som blir kreditert til vanneksponeringen under grafenoverføringstrinnet. Dette var et spesielt fremtredende problem for kontaktete nanotråder. I dette tilfellet mistenkes det at metallkontaktene forårsaker galvanisk korrosjon i nanotrådene.

Målinger av IV-karakteristikk og styrespenningsavhengighet ble utført på GaAs nanotråd/grafén-kontakter med CVD-grodd grafén. Store variasjoner i I-V oppførsel og styrespenningsavhengigheten ble observert, noe som blir kreditert til korrosjonen av nanotrådene, ettersom det antas at dette fører til ukarakteristisk oppførsel i GaAs-metall kontaktene. Det er også indikasjoner på at enkelte prøver er kortsluttet av grafén. De elektroniske undersøkelsene antas derfor å være for mangelfulle til å kunne trekke noen konklusjon i forhold til egenskapene ved GaAs nanotråd/grafén-kontakter. Det konkluderes derfor at videre utvikling av fabrikasjonsprosessen er nødvendig for å oppnå GaAs nanotråd/grafénprøver egnet for mer detaljert analyse.

# Acknowledgements

This project has been conducted at the Norwegian University of Science of Technology (NTNU), with the Department of Electronics and Telecommunications (IET). The work were done in Prof. Helge Weman and Prof. Bjørn Ove Fimland's group at IET, a research group working with growth and characterization of GaAs nanowires for optoelectronic applications, such as solar cells. The practical work was conducted in NTNUs cleanroom facilities, NTNU Nanolab, with the exception of the electrical characterization, which was done in the IET probing station lab.

First, I would like to thank my supervisor Helge Weman for giving me the opportunity to participate and contribute to their exciting research. By working on this project I feel that I have gained valuable insight and knowledge on the scientific research on nanowires, both in theory and practical experiments. This has been a very exciting project, and I am very motivated to continue on similar topics in the future.

I would also thank my co-supervisor Dr. Dong Chul Kim. He has been very helpful to me throughout this project, devoting countless hours to both guiding me through the practical procedures in Nanolab, and helping me understand the theory behind the processes.

Lastly I would like to thank friends and family for general support through the long and hard period of work to finish this thesis. Especially Solveig Stubmo Aamlid has been an indepensible help to me throughout this work, and this thesis would not be possible without her.

# Contents

| Acknowledgements |                |                                           |      |  |

|------------------|----------------|-------------------------------------------|------|--|

| Co               | Contents       |                                           |      |  |

| Li               | st of          | Figures                                   | viii |  |

| $\mathbf{Li}$    | List of Tables |                                           |      |  |

| 1                | Intr           | roduction                                 | 1    |  |

| <b>2</b>         | The            | eory                                      | 3    |  |

|                  | 2.1            | Semiconductor physics                     | 3    |  |

|                  |                | 2.1.1 Band Theory                         | 3    |  |

|                  |                | 2.1.2 Crystal structure and k-space       | 5    |  |

|                  |                | 2.1.3 Band structure $\ldots$             | 6    |  |

|                  |                | 2.1.4 Metal-semiconductor junctions       | 6    |  |

|                  |                | 2.1.5 Ideal rectifying behavior           | 9    |  |

|                  | 2.2            | Graphene                                  | 11   |  |

|                  |                | 2.2.1 Graphene visibility                 | 15   |  |

|                  |                | 2.2.2 Graphene fabrication                | 15   |  |

|                  | 2.3            | GaAs                                      | 17   |  |

|                  |                | 2.3.1 GaAs contacting                     | 17   |  |

|                  |                | 2.3.2 Graphene contacting                 | 19   |  |

|                  |                | 2.3.3 Graphene - semiconductor junctions  | 19   |  |

|                  | 2.4            | Chemical Vapor Deposition - CVD           | 22   |  |

|                  | 2.5            | Vapor-liquid-solid growth mechanism - VLS | 24   |  |

|                  | 2.6            | Molecular beam epitaxy - MBE              | 26   |  |

|                  | 2.7            | Scanning electron microscopy - SEM        | 26   |  |

|   | 2.8 | Electron beam lithography - EBL                                                                                                                           |

|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3 | Exp | perimental 35                                                                                                                                             |

|   | 3.1 | Overview                                                                                                                                                  |

|   | 3.2 | Sample preparation                                                                                                                                        |

|   | 0.2 | 3.2.1 Substrate fabrication                                                                                                                               |

|   |     | 3.2.2 Substrate details                                                                                                                                   |

|   |     | 3.2.3 Substrate cleaning                                                                                                                                  |

|   |     | 3.2.4 Nanowire synthesis                                                                                                                                  |

|   |     | 3.2.5 Nanowire dispersion                                                                                                                                 |

|   | 3.3 | Graphene transfer - exfoliated graphene                                                                                                                   |

|   |     | 3.3.1 Graphene dispersion                                                                                                                                 |

|   |     | 3.3.2 Surface treatment                                                                                                                                   |

|   |     | 3.3.3 Transfer                                                                                                                                            |

|   | 3.4 | Graphene transfer - CVD-grown graphene                                                                                                                    |

|   |     | 3.4.1 Graphene fabrication and preparation                                                                                                                |

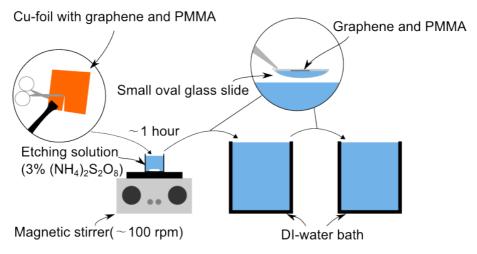

|   |     | 3.4.2 Cu etching                                                                                                                                          |

|   |     | 3.4.3 Surface treatment 44                                                                                                                                |

|   |     | 3.4.4 Transfer                                                                                                                                            |

|   |     | 3.4.5 Drying                                                                                                                                              |

|   |     | 3.4.6 PMMA removal                                                                                                                                        |

|   |     | 3.4.7 Preliminary SEM investigation                                                                                                                       |

|   | 3.5 | Contact design                                                                                                                                            |

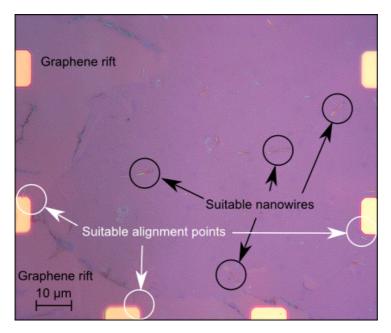

|   |     | 3.5.1 Optical microscope imaging for alignment                                                                                                            |

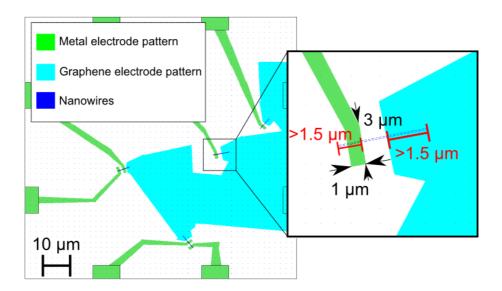

|   |     | 3.5.2 Digital mask design                                                                                                                                 |

|   | 3.6 | Graphene contacting                                                                                                                                       |

|   |     | 3.6.1 Electron beam lithography 49                                                                                                                        |

|   |     | 3.6.2 Development                                                                                                                                         |

|   |     | 3.6.3 Metallization and lift-off                                                                                                                          |

|   | 3.7 | Graphene trimming                                                                                                                                         |

|   |     | 3.7.1 Spin coating $\ldots \ldots \ldots$ |

|   |     | 3.7.2 Electron beam lithography 51                                                                                                                        |

|   |     | 3.7.3 Development                                                                                                                                         |

|   |     | 3.7.4 Plasma ashing $\ldots \ldots 52$                                |

|   | 3.8 | Nanowire contacting 53                                                                                                                                    |

|   |     | 3.8.1 Spin coating 53                                                                                                                                     |

|   |     | 3.8.2 Electron beam lithography, Development and Metallization 53                                                                                         |

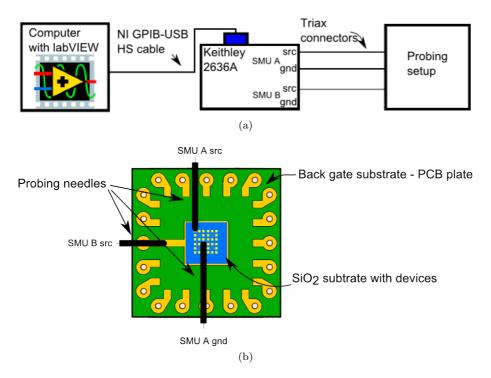

|   | 3.9 | Electrical Measurements                                                                                                                                   |

|   |     | 3.9.1 Setup                                                                                                                                               |

|   |     |                                                                                                                                                           |

|              |            | 3.9.2   | <i>I-V</i> measurements                         | 54  |

|--------------|------------|---------|-------------------------------------------------|-----|

|              |            | 3.9.3   | Gate voltage measurements                       | 56  |

|              | 3.10       | SEM i   | imaging                                         | 56  |

| 4            | Res        | ults    |                                                 | 57  |

| -            | 4.1        |         | ninary EBL procedure testing                    | 57  |

|              | 4.2        |         | nene transfer                                   | 57  |

|              |            | 4.2.1   | CVD-grown graphene - Graphene Supermarket       | 57  |

|              |            | 4.2.2   | CVD-grown graphene - Sejong University          | 58  |

|              |            | 4.2.3   | Exfoliated graphene                             | 62  |

|              | 4.3        |         | e fabrication                                   | 63  |

|              | 1.0        | 4.3.1   | Choice of resist for graphene shielding layer   | 63  |

|              |            | 4.3.2   | Choice of fabrication order                     | 64  |

|              |            | 4.3.3   | ExG-device - failure during graphene trimming   | 65  |

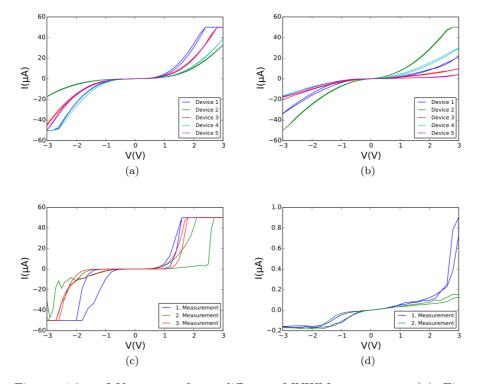

|              | 4.4        |         | ical measurements                               | 65  |

|              | 1.1        | 4.4.1   | Nanowire measurements                           | 65  |

|              |            | 4.4.2   | Graphene measurements                           | 68  |

|              |            | 4.4.3   | GP/NW-device measurements                       | 72  |

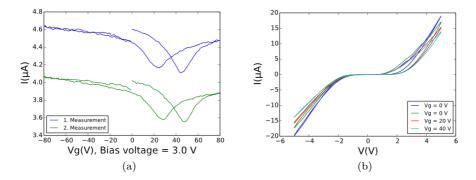

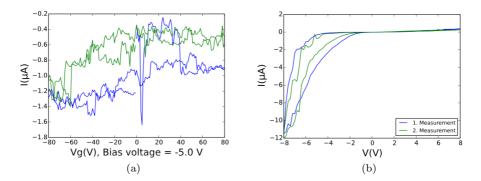

|              |            | 4.4.4   | Gate voltage measurements                       | 75  |

| 5            | Disc       | cussior | 1                                               | 79  |

| 0            | 5.1        |         | -<br>opment of EBL procedure                    | 79  |

|              | 5.2        |         | vire measurements                               | 80  |

|              | 5.3        |         | nene measurements                               | 81  |

|              | 5.4        |         | nene-nanowire device measurements               | 82  |

|              | 0.1        | 5.4.1   | Field effect in GaAs nanowire                   | 82  |

|              |            | 5.4.2   | Expectations from theory                        | 83  |

|              |            | 5.4.3   | <i>I-V</i> measurements - linear behavior       | 84  |

|              |            | 5.4.4   | <i>I-V</i> measurements - high current behavior | 84  |

|              |            | 5.4.5   | <i>I-V</i> measurements - low current behavior  | 85  |

| 6            | Con        | clusio  | n                                               | 87  |

| 7            | Fur        | ther w  | rouk                                            | 89  |

| •            |            |         |                                                 | 09  |

| Bi           | ibliog     | raphy   |                                                 | 91  |

| $\mathbf{A}$ | Appendices |         |                                                 | 99  |

| Δ            | Sub        | strate  | Dimensions                                      | 101 |

| в | EBI                                                | procedure                     | 103 |  |

|---|----------------------------------------------------|-------------------------------|-----|--|

|   | B.1                                                | Overview                      | 103 |  |

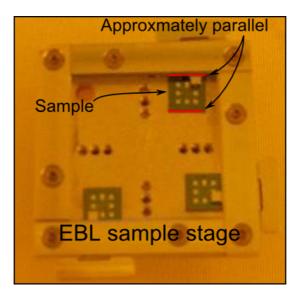

|   | B.2                                                | Sample mounting and insertion | 104 |  |

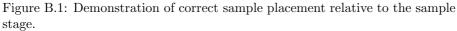

|   | B.3                                                | Beam current adjustment       | 104 |  |

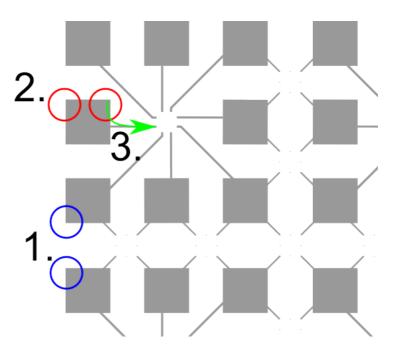

|   | B.4                                                | Beam alignment                | 105 |  |

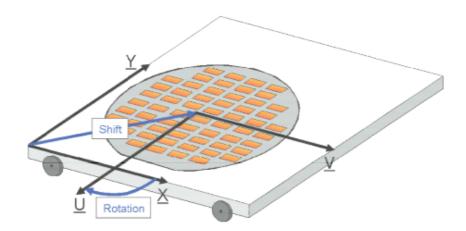

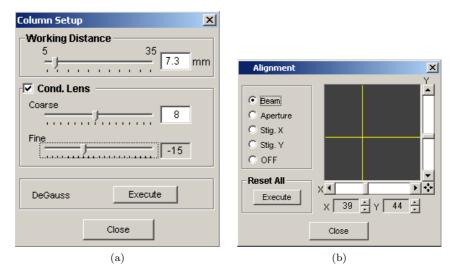

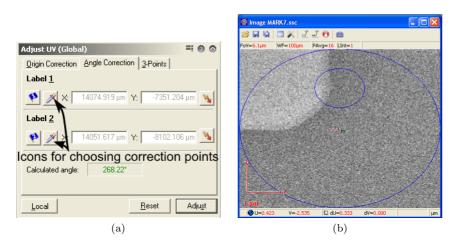

|   | B.5                                                | Rotation and angle correction | 106 |  |

|   | B.6                                                | Locating target area          | 107 |  |

|   | B.7                                                | Position correction           | 107 |  |

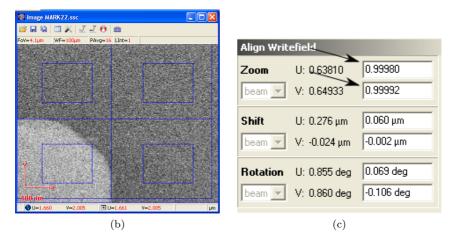

|   | B.8                                                | Stage movement alignment      | 109 |  |

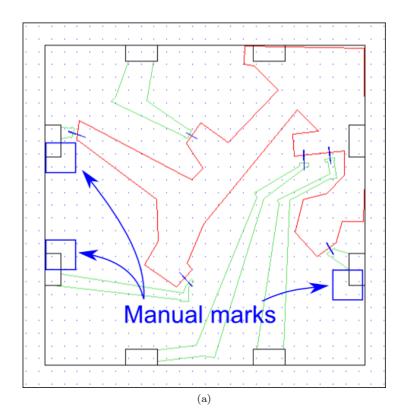

|   | B.9                                                | Write field alignment         | 111 |  |

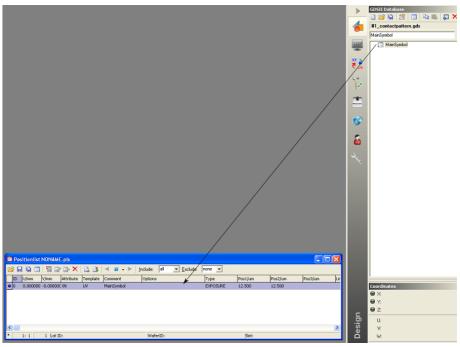

|   | B.10                                               | Exposure                      | 111 |  |

|   | B.11                                               | Sample unloading              | 114 |  |

| С | EBI                                                | procedure test                | 117 |  |

| D | O Graphene transfer results - Graphene Supermarket |                               |     |  |

# **List of Figures**

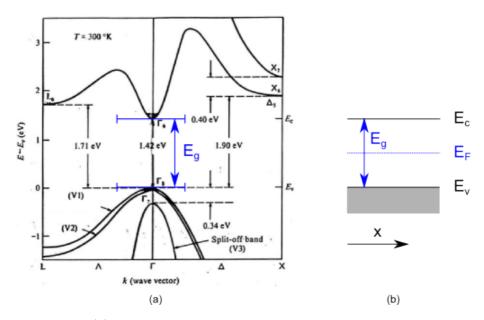

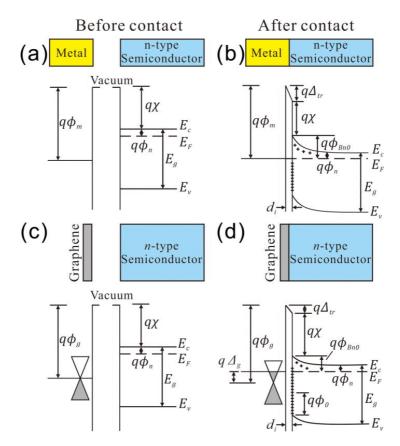

| 2.1  | Band diagrams plotted for GaAs                                                                       | 7  |

|------|------------------------------------------------------------------------------------------------------|----|

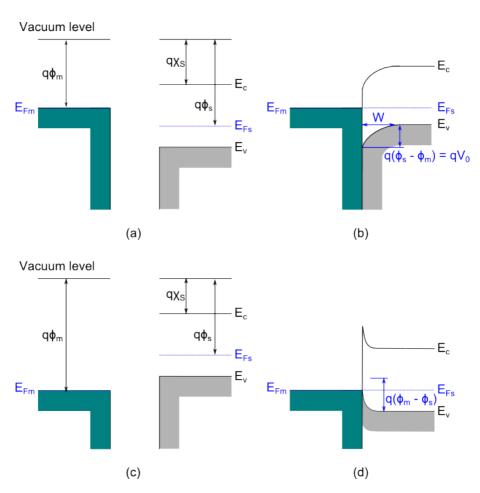

| 2.2  | Illustration of a Schottky barrier and ohmic contact                                                 | 8  |

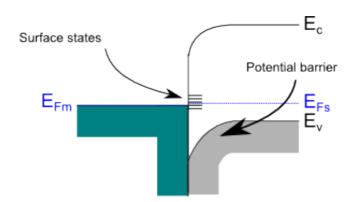

| 2.3  | Band diagram illustrating Fermi level pinning                                                        | 10 |

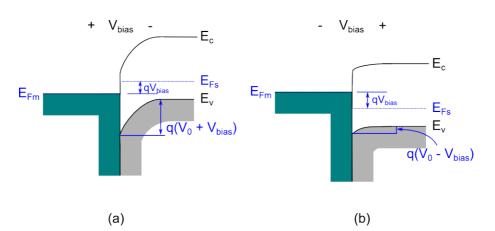

| 2.4  | Band diagrams illustrating the effect of an applied voltage to a                                     |    |

|      | metal-semiconductor junction                                                                         | 11 |

| 2.5  | Illustrations of the structure and band structure of graphene                                        | 12 |

| 2.6  | Demonstration of the ambipolar field effect in graphene                                              | 14 |

| 2.7  | Comparison of optical microscope images of single-layer graphene                                     |    |

|      | on $SiO_2$ of different thicknesses $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 16 |

| 2.8  | Band diagrams for direct and indirect band gap materials                                             | 18 |

| 2.9  | Simplified band diagrams illustrating the difference between the                                     |    |

|      | graphene-semiconductor and metal-semiconductor junction $\ldots$ .                                   | 20 |

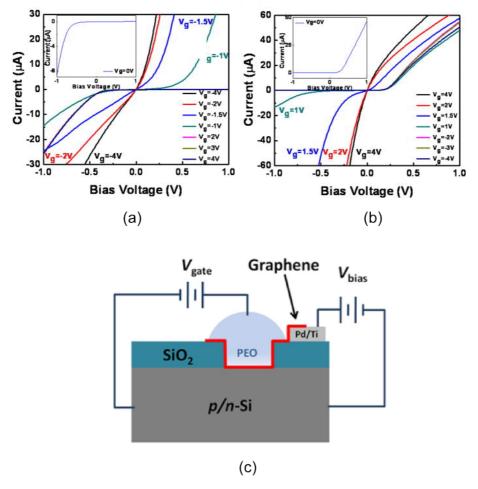

| 2.10 | I-V curves obtained from a graphene - silicon junction as different                                  |    |

|      | gate voltages induced in an electrolyte gate                                                         | 23 |

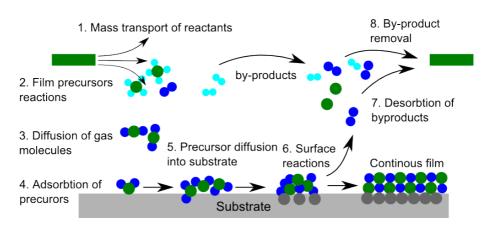

| 2.11 | Schematic overview of a CVD process                                                                  | 24 |

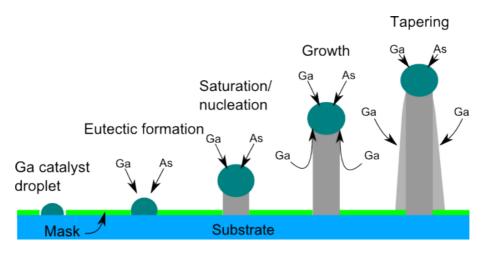

| 2.12 | Schematic overview of the VLS mechanism                                                              | 25 |

| 2.13 | MBE schematic                                                                                        | 27 |

| 2.14 | The interaction volume of in a sample observed in a SEM $\ldots$ .                                   | 28 |

| 2.15 | Schematic of beam path in a SEM                                                                      | 30 |

| 2.16 | EBL sample coordination system transformation                                                        | 32 |

| 2.17 | Examples of incorrectly aligned write fields                                                         | 33 |

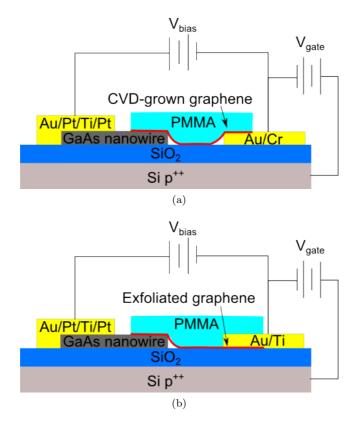

| 3.1  | Schematic diagram of the envisioned device structures                                                | 37 |

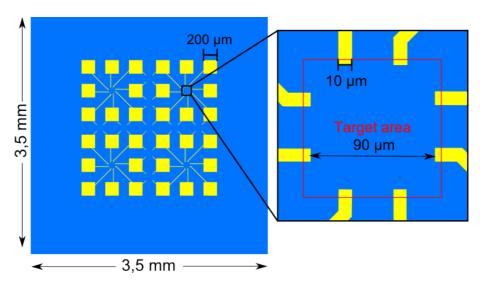

| 3.2  | The dimensions for the $SiO_2$ substrates $\ldots \ldots \ldots \ldots \ldots \ldots$                | 38 |

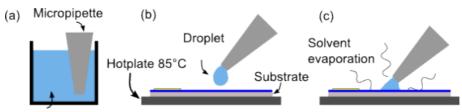

| 3.3  | Process for nanowire dispersion                                                                      | 41 |

| 3.4  | Substrate with exfoliated graphene and PMMA                                                          | 42 |

| 3.5  | Cu etching process and graphene transfer                                                             | 44 |

| 3.6  | Alignment image to locate nanowires relative to the prepatterned                |     |

|------|---------------------------------------------------------------------------------|-----|

|      | contact arms                                                                    | 47  |

| 3.7  | An EBL pattern made using CleWin                                                | 48  |

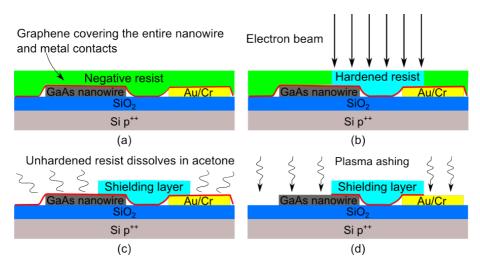

| 3.8  | Schematic overview of the graphene trimming process                             | 51  |

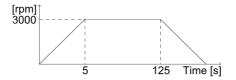

| 3.9  | The spin profile for spin coating                                               | 51  |

| 3.10 | Schematic overview of measurement and probing setup                             | 55  |

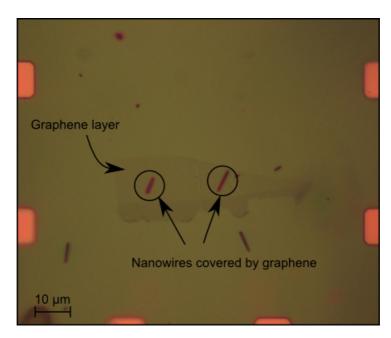

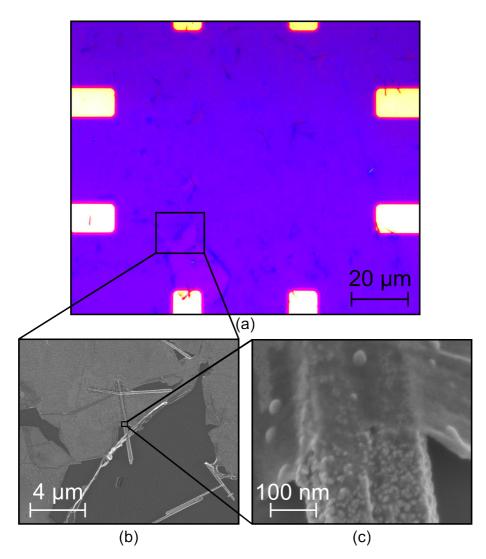

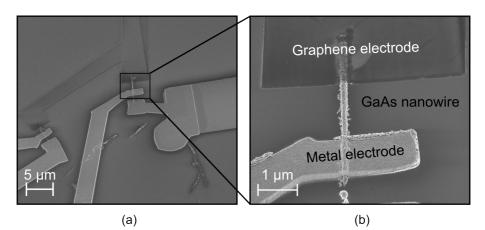

| 4.1  | Optical and SEM images after CVD-graphene transfer                              | 59  |

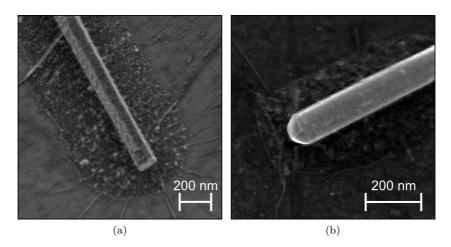

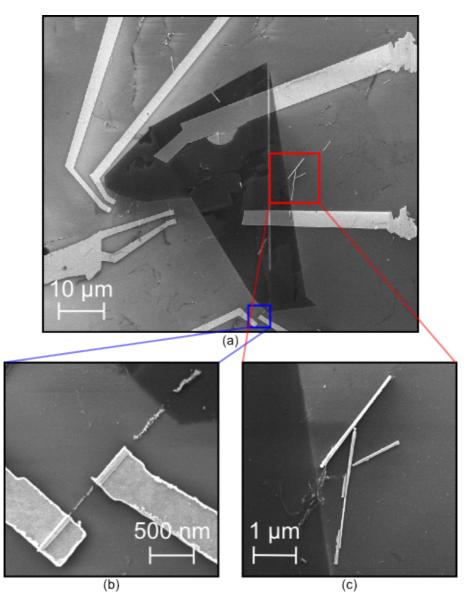

| 4.2  | SEM images of GaAs nanowires after graphene transfer                            | 60  |

| 4.4  | SEM images of nanowire before a water test                                      | 60  |

| 4.3  | SEM image demonstrating a rugged nanowire surface after transfer                | 61  |

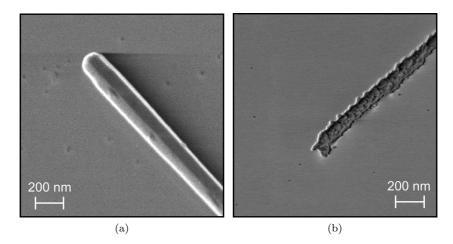

| 4.5  | SEM image demonstrating the effects of a faster drying procedure                |     |

|      | after graphene transfer                                                         | 62  |

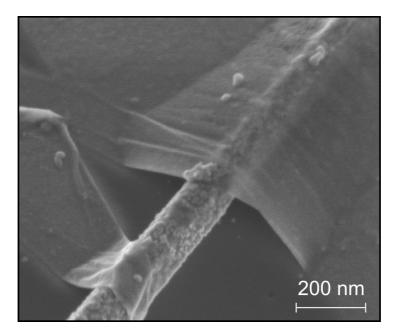

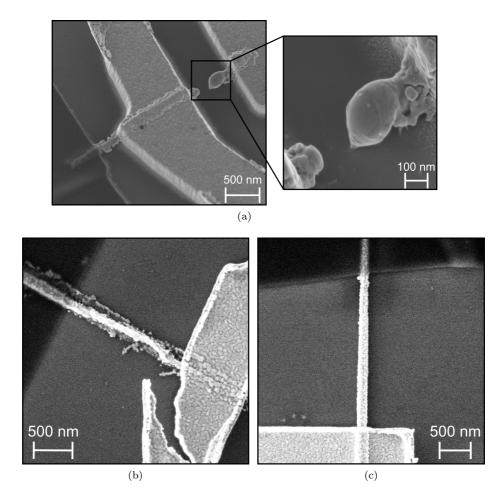

| 4.6  | SEM image demonstrating the accelerated corrosion observed in                   |     |

|      | contacted nanowires                                                             | 66  |

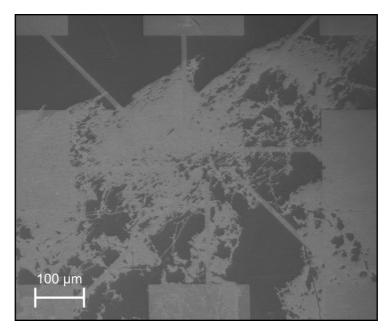

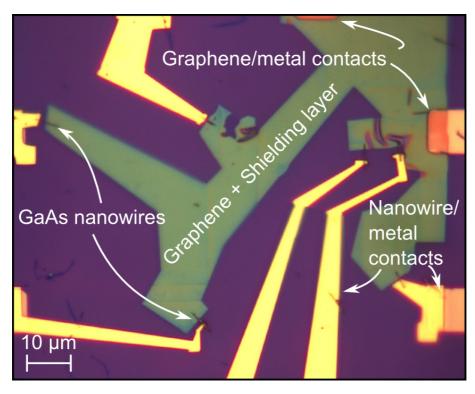

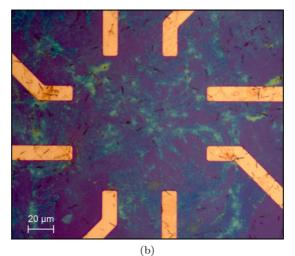

| 4.7  | Optical microscope image demonstrating six finalized graphene/GaAs              |     |

|      | nanowire hybrid devices                                                         | 67  |

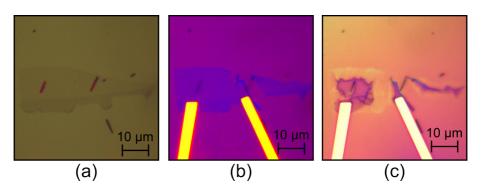

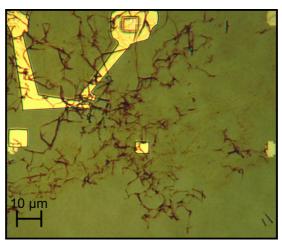

| 4.8  | Optical microscope images demonstration the destruction of exfoli-              |     |

|      | ated graphene flakes during processing                                          | 68  |

| 4.9  | <i>I-V</i> curves from different MGM-contacts                                   | 69  |

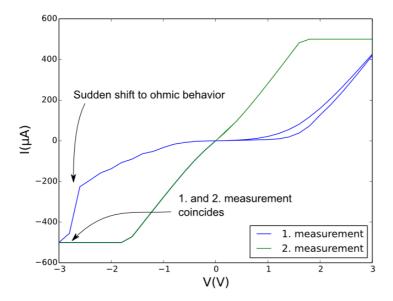

| 4.10 | <i>I-V</i> curve from a MNWM-contact demonstrating a shift from rec-            |     |

|      | tifying to ohmic behavior                                                       | 71  |

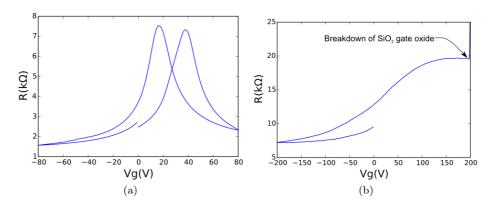

| 4.11 | Typical $R - V_{gate}$ characteristics for MGM-contacts on two different        |     |

|      | substrates                                                                      | 72  |

| 4.12 | I-V curves obtained from GP/NW-devices, displaying the two no-                  |     |

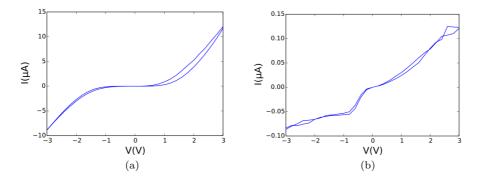

|      | table trends observed                                                           | 73  |

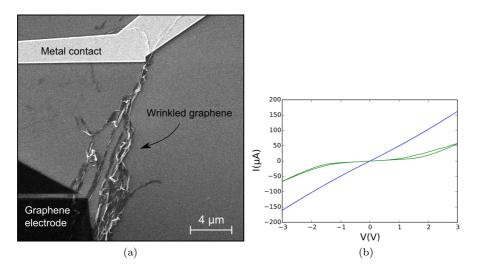

| 4.13 | SEM image and $I-V$ curve demonstrating graphene shortening $\ldots$            | 74  |

| 4.14 | SEM images showing aGP/NW-device displaying linear behavior .                   | 74  |

| 4.15 | Gate voltage measurements for devices displaying high current                   | 75  |

| 4.16 | Gate voltage measurements for devices displaying low current                    | 76  |

| 4.17 | SEM images showing various devices after electrical breakdown                   | 78  |

|      | 0 0                                                                             |     |

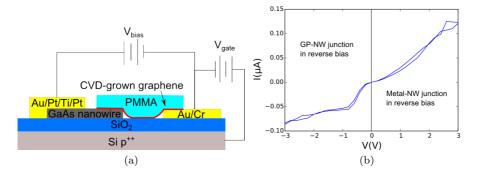

| 5.1  | Schematic of device design and $I-V$ curve example $\ldots \ldots \ldots$       | 83  |

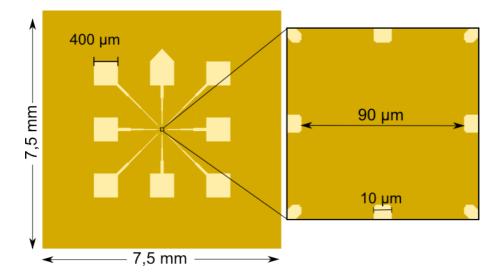

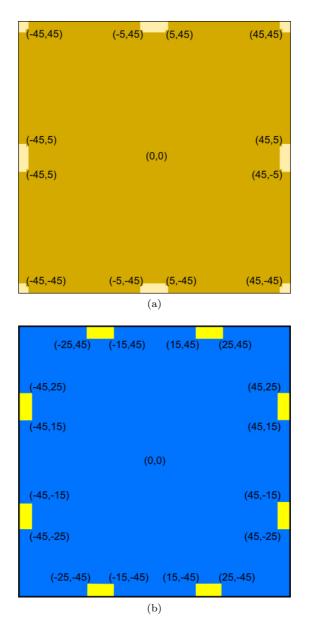

| A.1  | The dimensions of the $Si_3N_4$ -substrates                                     | 101 |

| A.2  | The coordinates given to the corners of the $Si_3N_4$ - and $SiO_2$ -substrates | 102 |

| B.1  | Correct sample placement                                                        | 105 |

| B.2  | EBL beam current and alignment menus                                            | 106 |

| B.3     | Suitable positions for rotating tilt correction, angle correction, and |     |

|---------|------------------------------------------------------------------------|-----|

|         | locating target area                                                   | 108 |

| B.4     | EBL angle correction menu and position example                         | 109 |

| B.5     | EBL fine point adjustment menus                                        | 110 |

| B.6     | EBL manual field alignment menus                                       | 112 |

| B.7     | EBL placement of manual marks in digital mask                          | 113 |

| B.8     | EBL exposure menus                                                     | 115 |

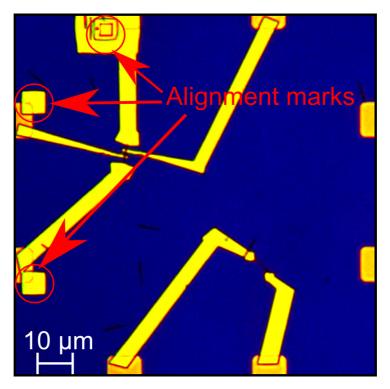

| $C_{1}$ | A finished 2- and 4-probe device with alignment marks                  | 110 |

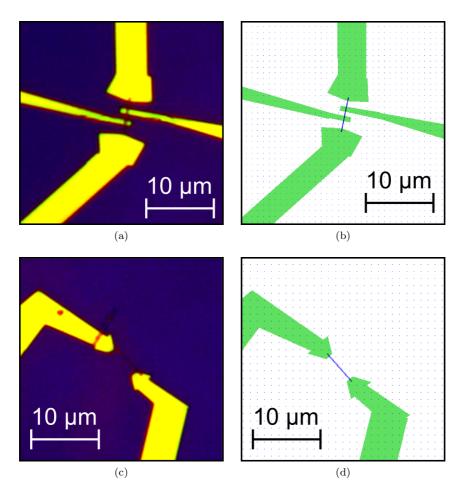

|         | · 0                                                                    |     |

| C.2     | Comparison of finished contacts and the digital mask                   | 119 |

| D.1     | Substrates with wrinkled graphene                                      | 122 |

# List of Tables

| 3.1 | Cleaning procedure parameters                               | 39 |

|-----|-------------------------------------------------------------|----|

| 3.2 | SC369 p-type GaAs nanowire growth parameters                | 40 |

| 3.3 | Surface treatment parameters.                               | 45 |

| 3.4 | Drying process parameters                                   | 46 |

| 3.5 | EBL exposure parameters                                     | 49 |

| 3.6 | Table listing parameters used in the spin coating procedure | 52 |

| 3.7 | EBL exposure parameters                                     | 52 |

| 3.8 | Metal stack used for nanowire contacts                      | 54 |

|     |                                                             |    |

| 4.1 | Resistance values obtained from five MGM-contacts           | 70 |

# Acronyms

**IPA** Isopropyl Alcohol **EBL** Electron Beam Lithography **rpm** Rounds per minute **PMMA** Polymethyl Methacrylate **CVD** Chemical Vapor Deposition **RIE** Reactive Ion Etching **SEM** Scanning Electron Microscope CVDG-device CVD-grown Graphene device **ExG-device** Exfoliated Graphene device **DI water** Deionized water MGM-contact Metal-Graphene-Metal contact **VB** Valence Band **CB** Conduction Band **MNWM-contact** Metal-Nanowire-Metal contact GP/NW-device Graphene-Nanowire device MSC-junction Metal-Semiconductor junction **GPSC-junction** Graphene-Semiconductor junction

# Chapter **]**

# Introduction

Semiconductors are today an indispensable part of modern technology. Forming the basis for the transistor, they are the fundamental building blocks of today's electronics [1]. The development in the semiconductor industry has traditionally been driven by miniaturization, following the trend of doubling the amount of transistors that can be fitted into a given area every second year, a trend commonly known as Moore's law. Ten years ago, the transistor dimensions were pushed to 100 nm, putting transistors in the nano regime [2]. In the nano scale, devices behave differently as surface effects start dominating over bulk effects, and quantum effects come into play [3]. Although the nano regime poses a great challenge to the conventional scaling of the semiconductor industry, the new regime also offers many exciting new possibilities.

A perfect example of these possibilities is graphene, a rising star within the field of nanotechnology. Graphene is a material consisting of one single layer of carbon atoms organized in a honey-comb lattice. Since its first successful isolation in 2004 [4], graphene has been subject to an explosive increase in research, which can be credited to its extraordinary properties like mechanical strength and flexibility [5], thermal conductivity [6] and impermeability to gases [7]. In terms of semiconductors, graphene is especially interesting due to its electronic properties [8]. Graphene exhibits excellent transport properties, including an exceptional electron mobility [9]. Although graphene has been suggested as a replacement of silicon in transistors [10], a complete replacement is considered unlikely [11]. Graphene is however expected to play a major role in future electronics in combination with other semiconductors.

One particular interesting combination for graphene is semiconductor nanowires,

#### 1. INTRODUCTION

which is also one of the most active research areas within the nano science community [12]. Nanowires are one-dimensional, crystalline structures with a diameter in the nano regime, and a typical length of a few micrometers. Due to their unique physical properties, semiconductor nanowires are considered as an ideal candidate for various future nanoscale devices [13, 14, 15]. Semiconductor nanowires have been demonstrated in light-emitting diodes [16], lasers [17], transistors [18] and solar cells [19].

Recently, it has been demonstrated that graphene can in fact also act as a substrate for epitaxial growth of nanowires [20]. This is an especially tantalizing concept. Not only would this represent potential substantial cost-savings in terms of replacing the costly single-crystalline semiconductor substrates normally required for epitaxial growth, but it also opens up the possibility for a wide array of unconventional electronic and optoelectronic devices, where graphene acts as a flexible, transparent electrode [21]. To realize such devices, it is however paramount to establish a good understanding of the interface formed between graphene and semiconductors, and the electronic properties of such a junction.

In terms of optoelectronic devices, a natural partner for graphene is the III-V semiconductor GaAs, which is regarded as a ideal candidate due to its directband gap and high electron mobility. Graphene-GaAs is however a relatively unexplored system, both in terms of GaAs acting as substrate for graphene [22] and the electronic properties of the GaAs-graphene junction [23]. Furthermore, to the author of this thesis's knowledge, there exists no studies that explore the electronic properties of a graphene-GaAs nanowire junction.

In the present study, an investigation of the graphene-GaAs nanowire system is conducted. A fabrication process for graphene/GaAs nanowire hybrid devices is developed and presented. Fabricated devices are investigated electronically by measuring I-V characteristics in the presence of a variable gate voltage, and the results are discussed in light of the present theory on graphene-semiconductor junctions.

# Chapter 2

# Theory

# 2.1 Semiconductor physics

To discuss the Graphene-Semiconductor junction (GPSC-junction), a brief introduction to some important concepts from semiconductor physics is needed.

## 2.1.1 Band Theory

In order to analyse the behavior of an electrical current in semiconductors, a model for describing electrons propagating through a solid is needed. An electron is a quantum particle, and should therefore be described in terms of the Schrödinger equation, which treats electrons like waves. Solving this equation for electrons affected by the coulomb potential of a positive atom core gives rise to a discrete set of allowed energy states, commonly referred to as orbitals. One of the postulates of quantum mechanics, the Pauli exclusion principle, states that two quantum particles can not occupy the same quantum state. For the case of electrons, this implies that each energy state can be occupied by two electrons, as electrons have two quantum states due to their internal spin [1, p. 49].

In the *nearly free electron* model, one assumes that the electrons occupying the outermost orbitals around an atom can be treated as free electrons in a periodic coulomb potential arising from the atom cores, and electron-electron interactions are ignored. Solving Schrödinger equation for this case gives rise to bands centered on the energy states from the single-atom case. These bands consist of N discrete energy states, where N is the number of positive ion cores

#### 2. Theory

making up the periodic potential. The gap between each discrete state in a band is narrow enough to let the bands be treated as continuous.

In a nearly free electron model at 0 K, the electrons fill the lowest available energy states. The energy of the highest occupied energy state is defined as the *Fermi energy*. When we allow the temperature to rise, there will be thermal energy available to the system, which can excite electrons to higher energy states. This will however only affect the electrons with an energy close to the Fermi energy, as only these have empty states separated by an energy comparable to the thermal energy available. The probability of an orbital being filled is described by the *Fermi-Dirac distribution*, which is given as:

$$f(E) = \frac{1}{exp[\frac{E-\mu}{kT}] + 1}$$

(2.1)

where T is temperature, k is Boltzmann's constant, and the chemical potential  $\mu$  is the quantity at which the Fermi-Dirac distribution equals 1/2. This quantity is paramount in the analysis of electron transport, as the nearly free electron model predicts that only electrons with energy close to  $\mu$  are important in determining electrical properties of solids. The quantity  $\mu$  is a function of temperature, and is often referred to as the *Fermi level* in semiconductor physics. The Fermi level should not be confused with the Fermi energy, which is only defined for 0 K.

Based on band theory, one can classify solids based on their electrical properties. In a simplified view, an electrical current can be viewed as electrons moving between states, as empty states within short interval energy interval are needed for electrons to propagate through a solid. For metals the Fermi level is situated in the middle of a band, implying that electrons near the Fermi level have empty available states nearby for all temperatures. Metals are thus good conductors at all temperatures. In the case where the Fermi level is situated between two bands, the completely filled band below the Fermi energy is normally referred to as the Valence Band (VB) and the empty band above as the Conduction Band (CB). At low temperatures, these materials are isolating, as there are no electrons in the CB and the electrons in the VB have no states to move to. However, if the energy gap is comparable to the available thermal energy, electrons can be thermally excited into the CB and contribute to a current. Such materials are either called semiconductors or isolators, based on the size of their energy gap. There is no exact definition of the value of the energy gap to differ a semiconductor from an isolator, but materials are typical called semiconductors up until  $\sim 6 \text{ eV}$ .

While all current is composed of the movement of electrons, it is necessary to distinguish between electron transport in the CB and VB for semiconductors. Electrons excited to the conduction band will experience a large amount of available states at the same energy, and can thus more or less move freely in the crystal. This excitation will however leave an empty state in the valance band, and this electron vacancy can contribute to a current in the form of an electron moving into this vacancy, leaving an empty state somewhere else. A convenient method for modelling this current mechanism is to treat this "hole" as a positive particle, which accordingly behaves opposite to an electron for an applied electric field.

## 2.1.2 Crystal structure and k-space

In a crystalline solid, the atoms are arranged in a periodic manner. An ideal crystal can be described in terms of a mathematical lattice with a basis, the smallest repetitive element in the crystal, at each lattice point [24, p. 4]. A three dimensional crystal may be defined by three translation vectors  $a_1, a_2, a_3$ , such that the crystal will look identical from any point reached from doing translation by an integer number of a's,

$$r' = r + u_1 a_1 + u_2 a_2 + u_3 a_3 \tag{2.2}$$

. This defines the *primitive translational vectors* of the lattice. Based on the internal relations of angles and lengths of these vectors, one can define 14 mathematical lattices, which can be used to present real crystals by introducing a basis of atoms at the lattice points.

The periodic nature of a crystal make them ideal for use of Fourier analysis<sup>1</sup>. By Fourier transforming the *primitive lattice vectors* one obtains the *reciprocal lattice vectors*, which defines the reciprocal space of the lattice. The reciprocal space is the representation of a crystal in terms of its periodicity in k-space. Instead of spatial coordinates, the reciprocal space coordinates are given terms of wave numbers, and is therefore often called k-space. A function viewed in reciprocal space at a specific k - value, for example  $k = \pi$  would convey information on how said function varies on a  $\pi$  periodicity.

<sup>&</sup>lt;sup>1</sup>Fourier analysis - the study of the way general functions may be represented or approximated by sums of simpler trigonometric functions. In practice Fourier analysis implies presenting a function in terms of their periodicity instead of spatial values.

#### 2. Theory

## 2.1.3 Band structure

While a simple assessment of the *nearly electron model* can justify the formation of energy bands in a solid, a more accurate model that includes the crystal structure and electron-electron interactions is needed to portray the accurate band structure in a solid. Developing such models and mapping the electronic structures is a complex task, and normally involves extensive simulations and numerical methods. These models plot the allowed energy values in terms of the wave-vectors k of the electrons, and these relations are thus often called E-k relations. As the crystal periodicity is different for various crystal directions, these relations constitute complex surfaces that should be visualized in three dimensions. It is however common to choose specific axes of interest, and plot these in a 2-dimensional manner, as seen in Figure 2.1a.

For the analysis of devices, it is however common to adopt a "simplified" band diagram. In these diagrams, one plots the bottom of the conduction band and the top of the valence band as a function of position in the device, along with the Fermi level (Figure 2.1b). Such diagrams are plotted in terms of potential energy for the negative electrons, implying that holes, being positive, gain potential energy by moving downwards in these diagrams.

## 2.1.4 Metal-semiconductor junctions

When a contact between a metal and a semiconductor is made, the ideal nature of the contact can be estimated from a band diagram assessment, and by examining the difference between the work function of metal,  $\Phi_M$ , and the workfunction of the semiconductor,  $\Phi_S$  [1, p. 227]. The work function is defined as the difference between the Fermi level and the energy level at vacuum, i.e. the energy required to remove an electron from the Fermi level and put it in vacuum. To assess the nature of the contact, one can make the thought experiment of having two separate blocks of metal and semiconductor and bringing them into contact. It can be shown that for a junction at thermal equilibrium it is necessary to have Fermi levels in both materials at the same level, as a gradient in the Fermi level would implicate a current [?, p. 109]. Bringing the metal and semiconductor together will thus result in an alignment of Fermi levels, which happens by charge transfer between the two materials. If the charge required to align the Fermi level is supplied by the minority carriers in the semiconductor, as is the case for p-type semiconductors and metals where  $\Phi_m - \Phi_s < 0$ , a depletion region<sup>2</sup> will form, creating a potential barrier for

<sup>&</sup>lt;sup>2</sup>Depletion region: A region depleted of mobile carriers, and dominated by space charge.

Figure 2.1: (a) Important axes of 3-dimensional band structure of GaAs in k-space [25]. (b) Simple band diagram as a function position, where the value of the energy gap is taken as the smallest energy gap from (a)

hole transport to the metal, as illustrated in Figures 2.2a and 2.2b. This will create a rectifying contact, implying the current is more easily conducted in one direction. Such potential barriers are referred to as *Schottky barriers*.

If the Fermi levels are aligned by accumulation of majority carriers, no depletion region is formed. There will still be a small energy difference as illustrated in Figures 2.2c and 2.2d.,but this barrier easily overcome by charge carriers by a small voltage. The current will thus flow easily in both directions. Such non-rectifying contacts is referred to as *ohmic contacts*.

### 2. Theory

Figure 2.2: Band diagrams of a metal- p-type semiconductor junction demonstrating the formation of: (a) and (b) a Schottky barrier.(c) and (d) an ohmic contact.

This ideal metal-semiconductor junction nature is based on the *Schottky-Mott* model, and makes several important assumptions. First it assumes perfect contact between the metal and semiconductor, and secondly that are no effects arising from surface states [26, p13]. At the surface of a semiconductor the covalent bonding is broken, meaning that the boundary atoms will have

unpaired electrons, so called dangling bonds. To minimize the free energy of the surface, the surface will undergo *relaxation* and *reconstruction*. In terms of band theory, this has the effect of introducing new surface and interface states in the middle of the bandgap [1].

In the *Bardeen* model the metal-semiconductor junction is modelled with a thin isolating layer between the metal and the semiconductor. By also including the charge arising from interface states and requiring electrical neutrality for zero bias, the barrier height can be described in the simplest form as [26, p. 20]

$$\Phi_B^0 = \gamma (\Phi_M - \chi_S) + (1 - \gamma)(E_g - \Phi_0)$$

(2.3)

where  $\Phi_B$  is the barrier height,  $\chi_S$  is the electron,  $E_G$  is energy gap in the semiconductor,  $\Phi_B^0$  is the barrier height attained for the case of flat bands, and

$$\gamma = \frac{\epsilon_i}{\epsilon_i + q\delta D_s} \tag{2.4}$$

where  $\epsilon_i$  is the electrical permittivity of the isolating layer,  $\delta$  is the length if the isolating layer,  $D_S$  is the density of surface states in the semiconductor. From this expression we see that if we let  $D_S \to 0$  we get  $\Phi_B^0 \to \Phi_M - \chi_S$ , which is the same result has predicted from the Schottky-Mott model. This scenario is therefore referred to as the *Schottky-Mott Limit*. If we let  $D_S \to \infty$ we get  $\Phi_B^0 \to E_g - \Phi_0$ , which is referred to as the *Bardeen limit*. In this limit the barrier height is independent of the difference in work functions between the metal and semiconductor, as illustrated in Figure 2.3. This scenario also referred to as *Fermi level pinning*, as the Fermi level is the semiconductor is said to be "pinned" by the high density of surface states.

The Bardeen model makes the assumption that the surface states of the semiconductor is not affected by being put into contact with a metal. Tung et al. argues that such an assumption is too simple to capture the true nature of the contact, as this intimate contact is bound to affect the orbitals around surface atoms, thus creating new surface states dependent on the interface chemistry[27]. They therefore argue that a more realistic model should include a quantum mechanical treatment of the surface.

## 2.1.5 Ideal rectifying behavior

The effect of applying a voltage over a metal-semiconductor junction can initially be found by assessing the simple band diagrams. By applying a negative voltage to the semiconductor relative to the metal, the electron energies in the

Figure 2.3: Band diagram illustrating Fermi level pinning in the Bardeen limit. The surface states in the middle of the band gap cause band bending at the surface, creating a potential barrier regardless of position of metal Fermi level.

semiconductor is raised as the electrostatic potential gets larger. This has the effect of raising semiconductor Fermi level relative the metal. For a p-type semiconductor this raises the potential barrier at the junction by an amount equal to the applied voltage, as illustrated in Figure 2.4a. For this case the junction is said to be in reverse bias. If the voltage is applied with the opposite sign, the potential barrier is lowered as seen in Figure 2.4b. In this case the junction is said to be forward biased.

There are various ways for a charge carrier to be transported across the potential barrier at the metal-semiconductor. The most important mechanisms are the emission over the top of the barrier and the quantum mechanical tunneling through the barrier. Recombination inside and outside the depletion regions will also contribute to the current, but these mechanisms are often neglected. Several models exist to explain these mechanisms. In the diffusion theory of Wagner, Schottky and Spenke [26, p. 92], the current is explained in terms of concentration gradients arising from the carrier accumulation at the junction. In this model the rate of transport is limited by the carrier transport from the bulk to the interface, rather than the actual transport across the junction. Another model is the thermionic-emission model proposed by Bethe [26, p. 94]. In this model the current is explained in terms of carriers gaining enough thermal energy to surpass the barrier. For this model the current is limited by the actual transport across the barrier.

Both these models in their simpler forms lead to *ideal rectifying behaviour*,

Figure 2.4: Band diagrams illustrating the effect of an applied voltage to a metal-semiconductor junction in the: (a) Reverse biased regime. (b) Forward biased regime.

which is the current-voltage relations on the form

$$I = I_0 \left( \exp\left(\frac{qV}{kT}\right) - 1 \right) \tag{2.5}$$

, where  $\Phi_B$  is the barrier height, V is applied voltage, and  $I_0$  is the saturation current. For this characteristic behavior the current increases exponentially in the forward bias, while saturating at a relatively low value for reverse bias.

# 2.2 Graphene

Graphene is an allotrope of carbon, consisting of a single layer of carbon atoms arranged in a honeycomb lattice, as seen in Figure 2.5a. Being only one atom thick, graphene is effectively a 2D-material, and electronic transport is thus constrained to two dimensions. Although the first theoretical models of graphene go as far back as 1947 [28], it was along with other 2D-crystals thought to be thermodynamically unstable and thus impossible to create physically. This was disproved when Novoselov and Geim et al. successfully isolated graphene simply by separating graphite sheets using tape [4]. The stability of graphene was initially credited to a gentle rippling of the graphene in a third

#### 2. Theory

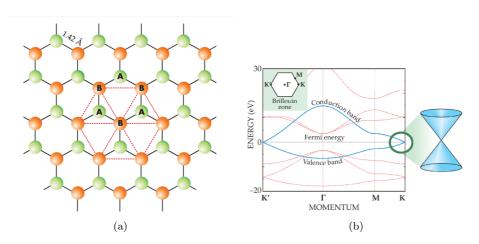

Figure 2.5: (a) Illustration of the honeycomb lattice in a graphene layer [29]. (b) Band structure of graphene. CB and VB intersect at the **K** points in reciprocal space, where the bands can be seen as two cones intersecting at one point [29].

dimension, as well as the small size of flakes. Later studies have however concluded that graphene owes its existence to the strong carbon-carbon bonds and  $\pi$  orbitals [7].

While graphene has a host of interesting properties like record stiffness and heat conductivity at room temperature [7], it is mainly the electrical properties that is of interest for this thesis. As seen in Figure 2.5a, the honeycomb lattice can be reduced to two triangular sub lattices, which give rise to the band structure depicted in Figure 2.5b. Put in simple terms, due to each carbon atom having an unpaired electron in this structure, these electrons gather in so called  $\pi$  and  $\pi$ \* orbitals which constitute the VB and CB. These orbitals are forbidden to overlap, but touch at six points in the E - K relation of graphene [29]. These points are referred to as *Dirac points* or *Neutrality points*. This implies that graphene is a zero-overlap semimetal, but it is also often referred to as zero-gap semiconductor.

An unique property of the  $\pi$  orbital is the approximate linearity as it approaches the Dirac points[8],

$$E(k) = \hbar v_F |k| \tag{2.6}$$

, where  $\hbar$  is the reduced Planck's constant,  $v_F$  is Fermi velocity<sup>3</sup>, and |k| is wave vector close to the Dirac point. Recalling that the energy of relativistic particle is given by

$$E = \sqrt{m^2 c^4 + p^2 c^2} \tag{2.7}$$

, where m is the rest mass of the particle, p its momentum, and c its velocity, we see that the linear energy dispersion in graphene actually implies that electrons behave as zero rest mass, relativistic particles described by the Dirac equation. They are therefore often referred to as Dirac fermions.

Graphene also exhibits excellent electron transport properties, in the forms of a very high electron mobility<sup>4</sup> attainable at room temperature. This is thought to be the result of Dirac fermions being more unlocalized than conventional electrons, thus behaving more like waves than particles. This allows the current to remain in the ballistic regime<sup>5</sup>. In suspended, free-hanging graphene, electron mobility can be as high as 200 000  $\frac{\text{cm}^2}{\text{Vs}}$  [9]. Being a 2D-dimensional material, graphene is however strongly influenced by its substrate, which typically limits the mobility significantly. On amorphous SiO<sub>2</sub> the mobility is reduced to around 10 000  $\frac{\text{cm}^2}{\text{Vs}}$  [8].

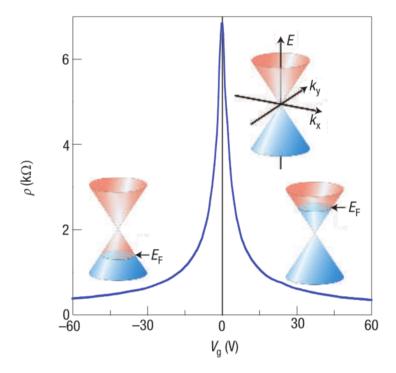

Another fascinating property of graphene is its pronounced ambipolar field effect. By applying a gate voltage to the graphene, induced concentrations of both holes and electrons have been demonstrated up to  $10^{13}$  cm<sup>-3</sup>, while still retaining a mobility in excess of  $10000 \frac{\text{cm}^2}{\text{Vs}}$  [4]. This implies that graphene in effect has a tunable Fermi level, and the conductivity (resistivity) of graphene is seen to vary significantly as a function of gate voltage, as seen in Figure 2.6. When the Fermi level is at the Dirac point, which is ideally the case for a gate voltage of zero, graphene is said to be intrinsic, and conductivity (resistivity) is very low (high) due to a very low density of states. If the Fermi level is raised via application of a gate voltage to the CB, an excess of electrons are induced, and graphene becomes capable of conducting a current characterized by electrons in the conduction band, similarly to a n-doped semiconductor. Reducing the Fermi level to the VB through applying a gate voltage of opposite sign will similar induce a concentration of holes, and the current will behave like in a

<sup>4</sup>Electron mobility: Average particle drift velocity per unit electric field,  $\mu_n = -\frac{\langle v \rangle}{E}$ .

<sup>&</sup>lt;sup>3</sup>Fermi velocity - the velocity of an electron at Fermi energy.

<sup>&</sup>lt;sup>5</sup> Ballistic transport - Current transport regime where the carriers only experience scattering by the confining walls. In this regime electron transport is dictated by wave physics, and unlike ohm's law, the resistance is independent of length of the sample.

Figure 2.6: Demonstration of the ambipolar field effect in graphene. The graph plots the resistivity of a graphene field effect device with a 300 nm  $SiO_2$  layer as dielectric, as a function of applied gate voltage. The insets indicate how the position of the Fermi level is changed with the gate voltage, making graphene behave as a p-doped (n-doped) semiconductor at negative(positive) gate voltages. [30]

p-doped semiconductor. Graphene can thus be thought of as a semiconductor with a doping concentration<sup>6</sup> tunable by a gate voltage.

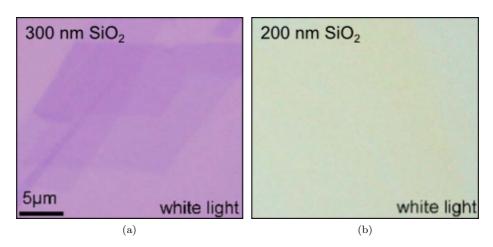

### 2.2.1 Graphene visibility

One of the reasons that graphene was not discovered until recent times is its poor visibility [30]. Although graphene is probably created every time someone uses a pencil, it is extremely difficult to identify single layer flakes amidst the substantially larger amount of thicker graphite flakes. Although graphene is visible to electron, atomic force, scanning tunneling microscopes, all of these are inefficient at finding graphene flakes due to the low throughput at the required resolution, or an absence of a clear signature of a single-layer graphene [31]. One of the key factors in graphene discovery was the usage of a 300 nm SiO<sub>2</sub>. At this thickness SiO<sub>2</sub> exhibits a combination of blue and purple contrast, where single-layer graphene becomes visible in optical microscope due to a feeble contrast difference, as seen in Figure 2.7. Only a 5 % difference in thickness of the SiO<sub>2</sub> can make single-layer graphene flakes completely invisible [30], though studies have shown that graphene can be made more visible on SiO<sub>2</sub> thicknesses by utilizing filters [31].

Another technique found to be usable in identifying graphene is the usage of Raman microscopy<sup>7</sup>, as it has been showed that the Raman spectrum of graphene clearly evolves with the number of layers [32].

## 2.2.2 Graphene fabrication

Due to its host of interesting properties and possibilities for different applications, there are numerous methods used and developed for fabrication of graphene. For graphene intended for optoelectronic applications, the two most common fabrication methods are exfoliation and Chemical Vapor Deposition (CVD) (Section 2.4).

Exfoliated graphene refers to graphene created by mechanical exfoliation or cleaving of flakes from graphite. This was the original method used in the first isolation of graphene [4], and is generally regarded as the method

$<sup>^{6}</sup>$ It should be kept in mind that doping by definition refers to tuning the carrier concentration of a semiconductor through introduction of foreign atoms, and that these foreign atoms give rise to other important effects not present in graphene.

<sup>&</sup>lt;sup>7</sup>Raman spectroscopy - Study of the inelastic scattering from illumination of a sample using a monochromatic laser with wavelengths in near infrared, visible, or near ultraviolet spectrum. This gives information on the low-frequency rotational and vibrational modes of the sample.

Figure 2.7: Comparison of optical microscope images of single-layer graphene on (a) 300 nm SiO<sub>2</sub>. (b) 200 nm SiO<sub>2</sub> [31].

that produces the best quality graphene. The highest reported mobility in graphene was reported on suspended exfoliated graphene [9]. An exfoliation normally involves the repeated peeling of small mesas of graphite, which is then transferred to a substrate, for example by rubbing a bit of tape on the surface. Single-layer or Few-layer graphene is then located by optical microscope and/or Raman spectroscopy.

The CVD fabrication of graphene has in the recent years emerged has an important method for preparation and production of graphene, which can partly be credited to its potential for industrial scale-up [33]. In a CVD process graphene is grown by surface-catalyzed reaction on a metal surface. While a variety of metals can be used, the most common include Ni and Cu, where Cu is often regarded as the most efficient catalyst. This is credited to the low carbon solubility in Cu, which allows for a greater portion of single-layer graphene. To utilize CVD-grown graphene for electronic applications, the metal must be removed and the graphene transferred to wanted surface. This is normally done by etching away the metal, and transfer the graphene using Polymethyl Methacrylate (PMMA) as a scaffold. The introduction of PMMA is however a disadvantage in terms of quality, as PMMA is known to adhere to the graphene surface and affect its electrical properties [34].

# 2.3 GaAs

GaAs is a compound semiconductor consisting of Ga from the periodic system group III and As from group IV. GaAs is therefore referred to as a III-IV semiconductor. It was originally assessed as a candidate for electronic devices with the discovery of the transistor in 1947 [35], but was surpassed by Si, because of the easier fabrication and native oxide of Si. Compared to Si, GaAs has some distinct advantages. Firstly it has higher electron mobility and electron saturated velocity, making it more efficient for switching operations, as internal charge can respond quicker to external potentials. This makes GaAs a better suited candidate for high frequency applications.

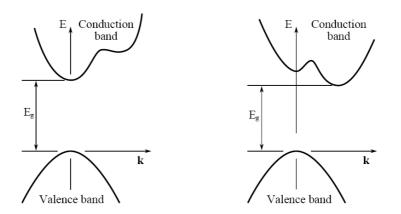

Moreover, GaAs is a direct band gap semiconductor, opposed to Si, which has an indirect band gap. A direct gap semiconductor has its conduction band minimum (CBM) located directly over the valence band maximum (VBM) in k-space, or in other words the CBM and VBM have the same k-vector, while the opposite is true for indirect gap materials [1]. Examples of the energy bands plotted for direct and indirect gap materials are shown in Figure 2.8. In practice, this means that electron excitation from valence band to conduction band in indirect gap materials is dependent on interaction with the lattice, as a change in electron k-vector, i.e. momentum is required in the transition. This is not the case for direct gap materials, making GaAs a better candidate for optoelectronic applications like solar cells and lasers.

### 2.3.1 GaAs contacting

Fermi level pinning is an especially prominent issue for GaAs, because of its high density of surface states [35]. Making ohmic contacts to GaAs is therefore notoriously difficult, as the barrier height in junction is relatively insensitive to the metal used.

To obtain good quality contacts to GaAs, a contact material also needs to have good adherence to the GaAs surface, and be stable and resistant to oxidation and corrosion. In practice, all these criteria can not be met for a single metal. It is therefore common to utilize a stack of metal layers. A typical ohmic contact scheme for p-type GaAs is Pt/Ti/Au [35, p. 200], where Pt ensures good electrical behaviour, Au optimizes the outside contact performance, and Ti acts as an adhesion and diffusion stop-layer to hinder Au atoms diffusing into the the Pt layer.

Fabrication of GaAs contacts should also include a surface treatment step, as presence of oxides on the GaAs surface will deteriorate the quality of the

Figure 2.8: Illustration of band diagram in k-space for a : (a) direct gap and (b) indirect gap semiconductor [1].

contact. Because of its high surface density, the GaAs surface is very reactive, and will form a native oxide in contact with air in the manner of minutes. To obtain ohmic contact, it is therefore paramount to minimize the time between surface treatment and metal deposition in contact fabrication process.

### Metal-nanowire junctions

One of the prominent features of ideal rectifying behavior, is the prediction of a bias independent saturation current in the reverse bias regime. In the scenario where a piece of semiconductor nanowire is contacted with a metal in both ends forming two Schottky barriers with opposite orientation, this implicates that only the low saturation current would be conductible, as one Schottky barrier will always be reverse biased. This is generally not observed in semiconductor nanowires, which typically display a non-saturating currents [36]. There are several theories proposed to deal with this in literature.

Zhang et al argues that thermionic emission model fails to explain the I-V behavior of semiconductor nanowires because of the absence of tunneling, which they claim to be the dominant component in the reverse bias current for lowdimension systems [37]. They suggest that for a reverse bias and intermediate temperature, the current can be explained in terms of the *thermionic field emission theory*. This model allows for both tunneling (field emission) and thermionic emission, and predicts a current-voltage relation [26, p. 113] as

$$I(V, \Phi_B) = -I_{sr}(V, \Phi_B) \exp\left(V\left(\frac{q}{kT} - \frac{1}{E_0}\right)\right)$$

(2.8)

, where  $I_{sr}$  is a slowly varying function of applied bias, and  $E_0$  is a parameter from tunneling theory.

On the other hand, Chiquito et al. argue that a semiconductor nanowire can be explained in terms of a modified Thermionic emission mode [38] They claim that the thermionic field emission model proposed by Zhang et al. is only applicable in heavily doped semiconductors where the tunneling probability is greatly increased.

A quantitative analysis of 2-probe devices of the same type of nanowire utilized in this thesis was attempted by another master's thesis [39]. In this thesis the I-V behavior is found to be in accordance with the behavior predicted from the thermionic field emission model.

## 2.3.2 Graphene contacting

#### 2.3.3 Graphene - semiconductor junctions

The GPSC-junction has been studied for many types of semiconductors, and the formation of a Schottky barrier at the interface is well established [23, 40, 41]. This is generally explained by graphene acting as a metal at the junction, so that the GPSC-junction can be approximated by a Metal-Semiconductor junction (MSC-junction). However, an important difference is that while the Fermi level in a metal will remain unchanged upon contacting, the Fermi level of graphene is expected to shift upon contacting due to the charge induced at the interface. This is due to the relatively low density of states for graphene around the Fermi level, as opposed to metals [23].

Zhong et al. proposes a Schottky-model modified with a floating Fermi level to describe this behavior [42], and predicts that this causes the barrier height to be lower for a GPSC-junction than for a MSC-junction. This is illustrated in Figure 2.9.

The current transport across the GPSC-junction is in most studies explained in terms of a thermionic emission model,

$$J(T,V) = A^* T^2 \exp\left(-\frac{q\Phi_B}{kT}\right) \exp\left(\frac{qV}{\eta kT} - 1\right)$$

(2.9)

19

Figure 2.9: Simplified band diagrams illustrating the difference between the graphene-semiconductor (a) and metal-semiconductor junction (c) before and after being brought into contact (b)-(d) in the presence of surface charge and a thin isolating layer. For the graphene-semiconductor junction the resulting barrier height is lower due an induced change in the graphene Fermi level [42].

, where  $A^*$  is the Richardson constant, T is temperature,  $\Phi_B$  is the zero bias barrier height. Deviation from ideal rectifying behavior is captured in the parameter,  $\eta$ , and is generally attributed to thermally assisted tunneling, generation-recombination current and bias dependent barrier height. This model is justified by the appearance of linear behavior for a logarithmic plot for the forward bias regime, which is in accordance with the prediction from thermionic emission. Using the slope in the logarithmic plot, the barrier height can be extracted. If one further assumes the Schottky-Mott limit to be valid,  $\Phi_B^0 = \Phi_M - \chi_S$ , the barrier height can be used to calculate the work function of graphene using the electron affinity of the semiconductor [41].

A trend observed for the GPSC-junction is the higher current in reverse bias than predicted from the thermionic emission model. Tongay et al. have demonstrated that while a significant reverse bias current is present in a GPSC-junction, this is not the case for a graphite junction [41]. They propose that this can be credited to the graphene Fermi level being shifted by the applied bias voltage, unlike in graphite where the Fermi level will be fixed. In response to a large reverse bias, the graphene Fermi level will therefore increase, decreasing the barrier height and thus increasing the current. This effect should also be visible for higher voltages in the forward regime in the form of a slightly decreased current, but here the effect will be difficult to distinguish from other resistance effects coming into play at a high current.

#### Graphene - Silicon

Graphene - silicon is probably the most studied graphene-semiconductor junction [40, 43, 44]. Silicon has the advantage of having a surface that is easily saturated, thus reducing interface states and Fermi-level pinning. Studies have shown while a silicon surface with dangling bonds will modify the orbitals of graphene, this is not case for a silicon surface passivated with hydrogen, where the electrical properties remain unperturbed [45]. The system is therefore well described by the Schottky-Mott limit, where the barrier height is only dependent on the difference in work function between graphene and the semiconductor. This makes the graphene-silicon junction ideal for investigating the effect of shifting the Fermi level of graphene on the GPSC-junction.

Yang et al. have demonstrated a three-terminal device they call a "barristor" [46], which is essentially a GPSC-junction with a top gate over the graphene. By modulating the gate voltage, they found that a positive gate voltage increases the current for p-type silicon and reduces the current for n-type, which they credit to the Fermi level of graphene approaching or di-

#### 2. Theory

verging from the Fermi level of Silicon. Chen et al. demonstrated a similar device, where an electrolyte gate was utilized [47]. Due to the large dielectric constant of an electrolyte gate, they were able to induce large shifts in the graphene Fermi level with relatively low gate voltages. As seen in Figure 2.10, they were able to observe a transition from almost ideal rectifying behaviour to almost ohmic behaviour, which they credit to the Fermi level of graphene being shifted almost past the Fermi level of silicon, where an ohmic contact is predicted from the Schottky-Mott model (Section 2.1.4).

#### **Graphene - GaAs junctions**

The graphene-GaAs junction is not well-studied, and to the author of this thesis's knowledge, there only exists four published studies on the electrical transport across this junction [23, 41, 48, 49].

Tongay et al. have demonstrated Schottky barriers for n-type GaAs on highly oriented pyrolytic graphite (HOGP) [41] and graphene [23]. The work function for HOGP and graphene found from the extracted barrier height using Schottky-mott theory is found to be in accordance with experimental results. But as Tongay et al. points out, the extracted barrier height is on par with the expected barrier height as a result of Fermi level pinning. It is therefore more likely that the graphene-GaAs junction is better approximated by the Bardeen limit.

# 2.4 Chemical Vapor Deposition - CVD

The CVD process is a method for a deposition of a solid film on a substrate through a chemical reaction of a gas mixture CVD has traditionally been used for depositing thin films by the semiconductor industry due to the low costs and high purity attainable [50, Ch.11], but in recent years the CVD process has been utilized in the fabrication of more exotic materials like nanowires (Section 2.5) and graphene (Section 2.2.2). The essential aspect of the CVD process is that the reactants are introduced in gas form, and these undergo chemical reactions to become film precursor. The chemically reactions should happen as close to the substrate surface as possible, and should ideally be surface catalyzed, as this produces the highest film quality [50, p. 266]. A schematic stepwise overview of the CVD process is shown in Figure 2.11.

Figure 2.10: I-V curves obtained from a graphene - silicon junction as different gate voltages induced in an electrolyte gate for (a) p-type silicon. (b) n-type silicon. (c) Schematic overview of the device structure [47].

#### 2. Theory

Figure 2.11: Schematic overview of the reaction steps taking place within a typical CVD-reactor.

# 2.5 Vapor-liquid-solid growth mechanism - VLS

The vapor-liquid-solid mechanism is a well-established growth mechanism for fabricating nanowires by a form of CVD [51, 52]. Unlike conventional CVD, where the gas reactants adsorb to the substrate surface to form a continuous film, the VLS method makes use of catalytic droplets to control growth. The droplets act as a preferred site for gas reactants, absorbing atoms both directly and via surface diffusion. This continues until the droplet becomes supersaturated, at which point epitaxial growth<sup>8</sup> commences at the boundary between the catalytic droplet and the substrate. Growth continues as more reactants absorb in the droplet, where they move to the boundary and deposit on the nanowire. The site of growth is thus confined by the area covered by the catalytic droplet, which in effect is the hole size. The nanowire will be uniform in diameter until the length becomes comparable with the surface diffusion length of the reactants, at which point tapering occurs. At this point the nanowire will become broader at the base than at the top near catalyst droplet, as most of the reactant atoms deposit before reaching top through a direct vapor solid - VS-growth. This process is illustrated in Figure 2.12.

GaAs nanowires have traditionally been grown using Au as catalyst droplet [53],

<sup>&</sup>lt;sup>8</sup>Epitaxial growth or epitaxy: crystal growth on a crystalline substrate where the new crystal maintains the structure and orientation of the substrate [1, p. 18].

Figure 2.12: Schematic overview of a Ga-assisted vapor-liquid-solid GaAs growth mechanism. Ga catalyst droplets form in the holes of the prepatterned mask, and absorb Ga and As atoms. When the droplet becomes supersaturated, Ga and As atoms go to the boundary between the droplet and the substrate and deposit as epitaxial GaAs. The growing nanowire is uniform in diameter until its length surpasses the surface diffusion length, at which point tapering is observed.

often referred to as Au-assisted VLS. In 2008 it was shown that GaAs nanowires can be grown Ga- or self-assisted, by forming Ga droplets at predefined spots using a mask [54]. This has since been the most popular method for fabricating GaAs nanowires, as extrinsic metal particles are generally not desired in nanowire devices. The presence of Au in GaAs nanowires is thought to introduce efficient non-radiative recombination centers<sup>9</sup>, making Au-assisted GaAs nanowires less desirable for optoelectronic applications [55].

Doping is conducted by introducing a gas flux of doping specimens during the growth process. The incorporation of doping atoms is currently not well understood, as the exact dopant concentrations in nanowires are generally unknown and difficult to measure. Growth parameters are therefore based on data from the growth of planar semiconductors. The system for VLS-growth utilized in this thesis, self-catalyzed GaAs doped with Be to achieve p-type,

$<sup>^{9}</sup>$ Non-radiative recombination center: An energy level in the band gap, allowing excited carriers to relax their energy without emitting a photon.

#### 2. Theory

have been studied by Casadei et al. [56]. The study concludes that the incorporation of Be atoms happens mainly through VS-growth at the nanowire sidewalls, followed by diffusion toward the core. Due to the high diffusion mobility of Be atoms in a GaAs structure, they argue that homogeneous dispersion of dopant atoms can achieved for high dopant concentrations. It will therefore be assumed the nanowires in this thesis have a uniform doping concentration.

# 2.6 Molecular beam epitaxy - MBE

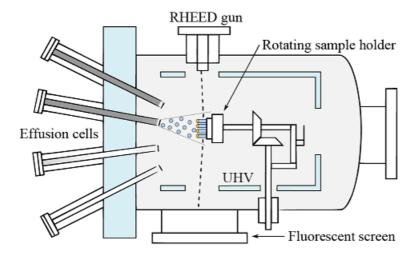

Molecular beam epitaxy is a technique for epitaxial growth by introducing the source material as molecular beams on a heated substrate in ultra-high vacuum,  $10^{-10} - 10^{-11}$  Torr [50, p. 291]. A schematic of a MBE system is shown in Figure 2.13. The source materials are separated from the main chamber in *effusion cells*, where they are heated until evaporation. The flux of each source material can then be accurately adjusted through controlling the cell temperature, and a mechanical shutter. This provides an excellent control of the ratio between the source materials, making MBE a well-suited method for deposition of compound semiconductors such as GaAs.

The vacuum level of the main chamber ensures that the mean free path of the source atoms is long enough for the atoms to reach the substrate without undergoing any chemical reactions. Upon reaching the surface, epitaxial growth occurs by atoms diffusing around until they find an empty lattice point, or attach to the side of a two-dimensional sheet. The key for achieving efficient and defect-free growth is thus to maintain a substrate temperature where the surface mobility is high, but not high enough to cause too much desorption from the surface. The reaction temperature is usually 500 to 900 °C. For compound semiconductors it is important to consider the difference in atom properties on the substrate surface. For GaAs growth, As atoms will generally experience more desorption, meaning a relatively higher As flux is required to obtain the desired ratio [35, p. 40].

To ensure epitaxial growth, a very slow growth rate must be utilized, and MBE growth rates are often given as monolayers per second, ML/s.

# 2.7 Scanning electron microscopy - SEM

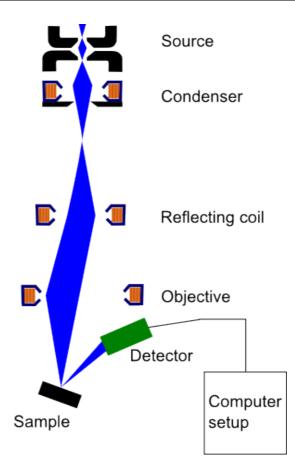

A Scanning Electron Microscope (SEM) is a type of electron microscope, an instrument that uses a focused high energy electron beam to scan the surface of a sample and produce images on the nanometer scale. SEM is a very versatile

Figure 2.13: Schematic of a typical MBE system, showing effusion cells, main chamber, and RHEED system for in-situ characterization during growth [57].

and popular instrument in material sciences, as electrons are well suited for characterization of structure and chemical characterization of surfaces due to their limited escape depth [58, p. 243]. According to the de Broglie theory electrons can be given wavelength according to

$$\lambda = \frac{h}{\sqrt{2mE}} \tag{2.10}$$

, where *h* denotes Planck constant, *m* electron mass, and *E* is the kinetic energy of an electron. At 50 keV this equals less than 0.1 Å, a value substantially lower than the wavelength of visible light at around 400 - 750 nm. Electrons can therefore be scattered by and provide information on smaller features than visible light, which is the main motivation for utilizing electrons in microscopy.

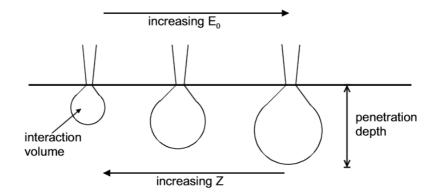

The interaction of an electron beam with matter gives rise to a multitude of different signals, which can analysed for both structural and chemical information about samples. The most important signals for a SEM is secondary electrons (SE), back-scattered electrons (BSE), and characteristic X-rays. Secondary electrons originate from the sample, and not from the electron beam itself [59, p. 60]. These are electrons that are knocked out from the valence

#### 2. Theory