# Single-Phase Bidirectional Power Factor Correction Boost Converter

Performance Evaluation of Totem-Pole PFC Converter Using Wide Band Gap Devices: GaN-HEMT and SiC

## Kalkidan Amare Gobena

Master of Science in Electric Power EngineeringSubmission date:Januar 2015Supervisor:Ole-Morten Midtgård, ELKRAFTCo-supervisor:Erik Myhre, Eltek AS

Norwegian University of Science and Technology Department of Electric Power Engineering

## Single-Phase Bidirectional Power Factor Correction Boost Converter: Performance Evaluation of Totem-Pole PFC Converter Using Wide Band Gap Devices, GaN-HEMT and SiC

# Kalkidan Amare Gobena

Master of Science in Electric Power Engineering Submission date: January 2015 Supervisor: Ole-Morten Midtgård (Professor), Elkraft Co- supervisor: Tore M. Undeland (Professor), Elkraft and Erik Myhre, Eltek AS

Norwegian University of Science and Technology Department of Electric Power Engineering

Single-Phase Bidirectional Power Factor Correction Boost Converter: Performance Evaluation of Totem-Pole PFC Converter Using Wide Band Gap Devices, GaN-HEMT and SiC

By

# Kalkidan Amare Gobena

A thesis submitted to

Department of Electric Power Engineering Norwegian University of Science and Technology

in partial fulfillment of the requirements for the degree Master of Science in Electric Power Engineering

January 2015

### **Problem Description**

Nowadays, telecom and data center industries are looking for a reliable and high performance power converter. The converter should provide high efficiency and high power density at reasonable cost. These issues can be addressed by a careful design and implementation of a converter topology that employs semiconductor devices with wide band gap material property and comprises few numbers of components. Wide band gap (WBG) devices are characterized by low on-state resistance and high thermal conductivity which in turn result in high efficiency and power density. Moreover, the design technique of the gate driver circuit also plays an important role to meet the specifications required by the industries.

The second main objective of this thesis is to utilize the stored energy in the batteries which serves as a backup source for several DC loads in data center and telecom sectors. Therefore, the proposed converter should allow bidirectional power flow between electricity mains and the backup batteries. The assignment is given for two students; single-phase AC-DC converter with PFC boost stage which is presented in this paper and DC-DC converter stage done by another fellow student.

Hence, in this master's thesis the student should:

- Assess different bidirectional PFC boost rectifier topologies and propose a topology which can give better performance: very close to unity power factor, low total harmonic distortion, high efficiency and high power density.

- Analyze and evaluate the performance of the converter topology by employing different semiconductor devices, basically Si, SiC and GaN HEMT.

- Simulate and study the performance of converter topology using LT Spice IV software.

- Produce a prototype for the converter and perform laboratory experiment at NTNU lab.

- Compare the results from computer simulation and laboratory experiment.

| Assignment given: 18 August 2014, Trondheim |                                                    |  |  |

|---------------------------------------------|----------------------------------------------------|--|--|

| Supervisor:                                 | Ole-Morten Metgård, Elkraft                        |  |  |

| Co-supervisor:                              | Tore M. Undeland, Elkraft and Erik Myhre, Eltek AS |  |  |

ii

### Preface

First and foremost, I would like to thank Almighty God for his showers of blessings throughout my life and strengthen me to complete the master thesis successfully.

I would like to express my deepest gratitude to Professor Ole-Morten Midtgård, my supervisor. I have got his helpful guidance all the way in the thesis work and recommended me some good practices in the profession. He encouraged me to write a paper for EPE 2015 conference.

I would like to extend my sincerest thanks and appreciation to Professor Tore M. Undeland for his full support, expert guidance and encouragement on my thesis work. His valuable support was not only on the thesis work but also through other academic and professional advices. He was always there when I desperately need his technical and psychological help. He was my supervisor in the specialization project in fall 2013 and co-supervisor in my thesis work.

My sincere thanks also go to Erik Myhre, Dr. Ibrahim Abuishmais and Odd Roar Schmidt for proposing the thesis idea and giving technical support. Aksel Hanssen deserves great thank you for his support regarding practical matters in producing my prototype.

I would also like to thank my parents; my elder sister, Dad and Mom. They were always supporting and encouraging me to face every challenge in life. Their prayer really helps me to be who I am today.

Kalkidan Amare Gobena Trondheim, Norway 13 January, 2015

iv

### Abstract

Several DC loads in data center and telecom industry are fed by power electronic rectifiers. The same rectifiers are used to charge a number of batteries which serve as a backup power source in case of power outage or failure of rectifiers. However, the stored energy in the backup batteries is not utilized efficiently due to reliable source of power from the mains. Therefore, the industry is demanding a highly efficient PFC converter with bidirectional power flow.

Significant improvement has been observed in the performance of power converters since the existence of wide band gap (WBG) devices in the power electronics industry. WBG devices provide high breakdown voltage and high thermal conductivity which enable to produce a more efficient and higher power density converter.

In this master thesis, a novel bidirectional PFC converter with totem-pole topology is presented for energy storage application. The totem-pole topology employs two fast WBG switches and another two slow but very low on-resistance Si MOSFET switches. Since the current is not flowing through the body diode of power MOSFETs the reverse recovery dissipation of the active switches are significantly reduced. The proposed topology provides high PF with minimum input current harmonics, high efficiency and high power density.

A literature review on wide band gap devices such as SiC and GaN has been done. The dual benefits of low on-resistance and reverse recovery charge from GaN enhance the performance of the totem–pole topology, especially in terms of efficiency. Whereas, high thermal conductivity property of SiC enable to down size the heat sink and hence increase power density.

A brief study is made on the functionality of the proposed converter for smart grid application together with battery capacities in telecom network. The research indicates that there is a huge potential of stored energy in the telecom site. Therefore, bidirectional PFC boost converter will be a power solution for efficient and cost effective use of electricity storage that also can feed power back to the grid.

The proposed topology has been studied using computer simulation and tested in laboratory experiment. Based on the specification, a prototype is produced by employing SiC MOSFETs.

vi

### Contents

| Problem Description                                                  | i    |

|----------------------------------------------------------------------|------|

| Preface                                                              | iii  |

| Abstract                                                             | v    |

| Tables                                                               | xi   |

| Figures                                                              | xiii |

| Acronyms and Symbols                                                 | xv   |

| 1 Introduction                                                       | 1    |

| 1.1 Background                                                       | 1    |

| 1.2 Motivation                                                       | 2    |

| 1.3 State - of - the art                                             | 3    |

| 1.3.1 Power Factor Correction (PFC) Converter                        | 3    |

| 1.3.2 Wide band gap materials (WBG)                                  | 5    |

| 1.4 Scope and Limitation of the thesis                               | 6    |

| 1.5 Structure of the report                                          | 6    |

| 2. Comparison and selection of switching devices                     | 9    |

| 2.1 Wide band gap materials                                          | 9    |

| 2.2 Properties of WBG Semiconductor materials                        | 9    |

| 2.2.1 Band gap                                                       | 10   |

| 2.2.2 Electric breakdown field                                       | 11   |

| 2.2.3 Higher saturation electron drift velocity                      | 12   |

| 2.2.4 High thermal conductivity                                      | 13   |

| 2.2.5 Coefficient of thermal expansion (CTE)                         | 13   |

| 2.3 Comparison of wide band gap (WBG) devices                        | 14   |

| 2.3.1 Silicon Carbide (SiC)                                          | 15   |

| 2.3.2 Gallium Nitride - High Electron Mobility Transistor (GaN-HEMT) | 17   |

| 2.3.2.1. Enhancement-mode (E-mode) GaN HEMT                          | 19   |

| 3. Single phase bidirectional PFC - boost converter topology study   | 21   |

| 3.1 Active Power Factor Converter                                    | 21   |

| 3.1.1 Review of two stage approaches                                 | 23   |

| 3.2 Synchronous Rectification (SR)                                   | 25   |

| 3.2.1 Diode Vs MOSFET                                                | 25   |

| 3.3 Bidirectional PFC boost Converter topology                       | 27 |

|----------------------------------------------------------------------|----|

| 3.3.1 GaN totem - pole PFC topology                                  | 29 |

| 3.4 Overview of smart grid functionality on bidirectional converters | 31 |

| 3.5 Battery capacity in telecom networks                             |    |

| 4. Control Circuit Design                                            | 35 |

| 4.1 Overview of gate driver circuits                                 | 35 |

| 4.2 Pulse Width Modulation (PWM)                                     | 35 |

| 4.3 MOSFET gate drive circuit design considerations                  |    |

| 4.3.1 Bipolar totem-pole driver                                      |    |

| 4.4 Gate drive control of totem-pole PFC                             |    |

| 4.5 Switching Technique                                              | 41 |

| 4.4.1 Concept of Soft Switching                                      | 41 |

| 4.4.2 Dead-time circuit                                              | 42 |

| 4.4.3 Soft- start                                                    | 43 |

| 5. Simulation-based study                                            | 47 |

| 5.1 Simulation set up                                                | 47 |

| 5.1.1 Selection of suitable simulation software                      | 47 |

| 5.1.2 Component selection                                            | 47 |

| 5.2 Converter Design                                                 | 48 |

| 5.3 A novel bidirectional AC–DC converter with PFC boost             | 49 |

| 5.4 Gate drive circuit in LTspice IV                                 | 50 |

| 6. Laboratory experiment setup and measurements'                     | 55 |

| 6.1 Component selection                                              | 55 |

| 6.2 Power loss in Power MOSFETs                                      | 55 |

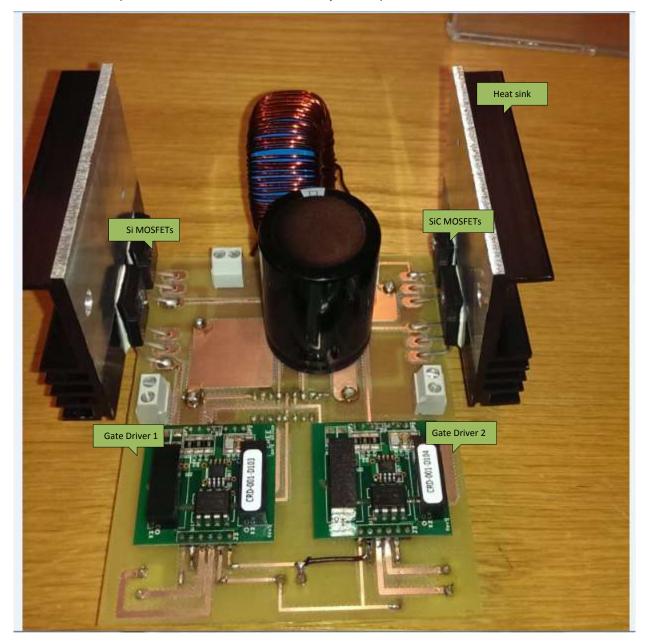

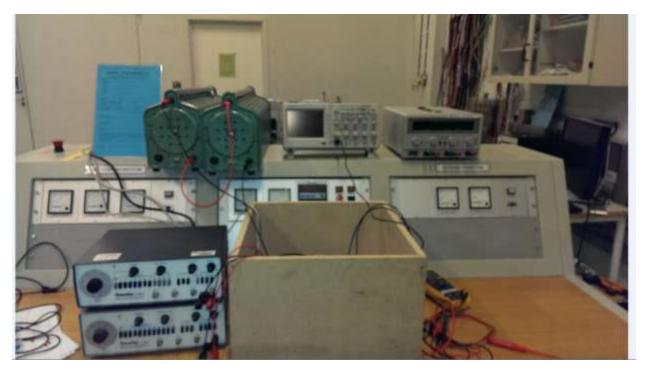

| 6.3 SiC based Laboratory setup                                       | 57 |

| 6.3.1 Totem-pole topology using «C2M0160120D» SiC MOSFET             | 57 |

| 6.3.2 «CRD-001» SiC isolated gate driver                             | 59 |

| 6.4 Prototype testing and measurements                               | 62 |

| 6.4.1 Heat sink design                                               | 64 |

| 7. Result and discussion                                             | 71 |

| 7.1 Simulation based                                                 | 71 |

| 7.2 Experiment based                                                 | 74 |

| 7.2.1 Effect of parasitic elements                                   | 74 |

| 7.2.2 Discussion on measurements                        | 74 |

|---------------------------------------------------------|----|

| 8. Conclusion and further work                          | 79 |

| 8.1 Conclusion                                          | 79 |

| 8.2 Further Work                                        | 81 |

| References                                              | 83 |

| Appendix                                                | 89 |

| Appendix A: LTspice IV Simulation circuit and waveforms | 89 |

| Appendix B: Laboratory set up                           | 93 |

| Appendix C: Additional Pictures and Graphs              | 95 |

х

## **Tables**

| TABLE 2.1 PHYSICAL PROPERTIES OF VARIOUS SEMICONDUCTORS FOR POWER DEVICES [26]       | 14 |

|--------------------------------------------------------------------------------------|----|

| TABLE 2.2 SUMMARY OF THE LATEST PROGRESS ON SIC POWER RECTIFIERS [21]                | 16 |

| TABLE 2.3 DIFFERENT APPROACHES TO REALIZE ENHANCEMENT MODE GAN HEMT DEVICE [25]      | 20 |

| TABLE 4.1 COMPARISONS OF HARD AND SOFT SWITCHING                                     | 42 |

| TABLE 7.1 SPECIFICATION OF THE PROTOTYPE SINGLE PHASE TOTEM-POLE PFC BOOST CONVERTER | 55 |

| TABLE 7.2 COMPONENT OF THE PROTOTYPE                                                 | 58 |

| TABLE 7.1 COMPARISON OF COMPONENTS FOR HIGH SPEED SWITCHING DEVICES (Q1 AND Q2)      | 72 |

xii

# Figures

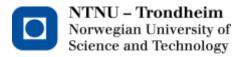

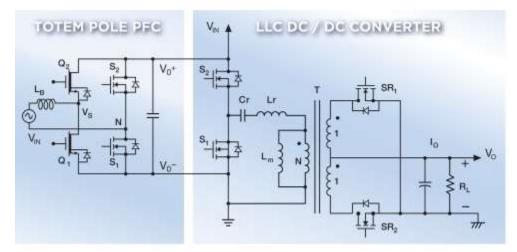

| FIGURE 1.1: TWO-STAGE AC-DC CONVERTER STRUCTURES [12]                                           | 4  |

|-------------------------------------------------------------------------------------------------|----|

| FIGURE 2.1: INTRINSIC CHARGE CARRIERS' VS TEMPERATURE GRAPH FOR SI AND SIC [21]                 |    |

| FIGURE 2.2: COMPARISON OF UNIPOLAR LIMIT OF SPECIFIC ON-RESISTANCE VERSUS BLOCKING VOLTAGE FOR  |    |

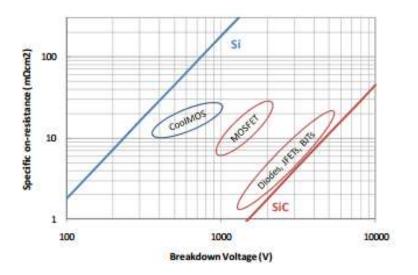

| SOME DEVICE TYPES IN SI AND SIC [22].                                                           | 12 |

| FIGURE 2.3: COMPARISON OF THREE MAJOR PHYSICAL PROPERTIES OF SEMICONDUCTOR DEVICES USING GRAI   | PH |

|                                                                                                 | 14 |

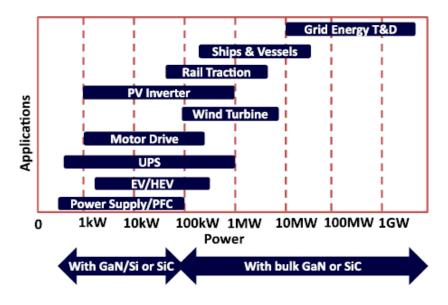

| FIGURE 2.4: ENTIRE RANGES OF POWER APPLICATIONS THAT CAN BE ADDRESSED WITH SIC AND GAN [28]     | 14 |

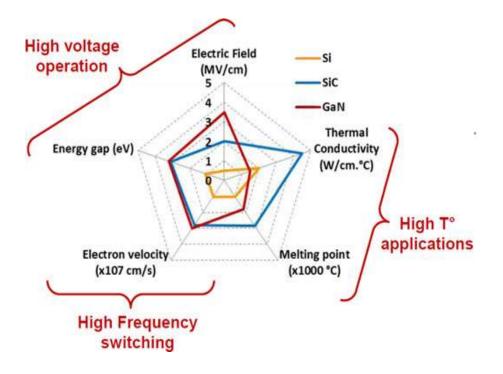

| FIGURE 2.5: SUMMARY OF SI, SIC, AND GAN RELEVANT MATERIAL PROPERTIES [19]                       | 15 |

| FIGURE 2.6: CROSS SECTION OF A NORMALLY-ON GAN HEMT [19]                                        | 18 |

| FIGURE 3.1: TRADITIONAL PFC WITH LINE RECTIFYING BRIDGE                                         | 21 |

| FIGURE 3.2: CURRENT AND VOLTAGE WAVEFORMS OF A CCM BOOST PFC CONVERTER [30]                     | 23 |

| FIGURE 3.3: CONCEPTUAL STRUCTURE OF TWO-STAGE PFC CONVERTER                                     | 24 |

| FIGURE 3.4: IDEAL WAVEFORMS OF THE TWO-STAGE PFC CONVERTER                                      |    |

| A) RECTIFIED INPUT VOLTAGE AND CURRENT                                                          |    |

| FIGURE 3.5: A BOOST CONVERTER WITH DIODE RECTIFICATION                                          | 26 |

| FIGURE 3.6: CIRCUIT SCHEMATICS OF THE BIDIRECTIONAL, ISOLATED AC-DC CONVERTER TOPOLOGY [42]     | 27 |

| FIGURE 3.7: TOTEM-POLE BOOST BRIDGELESS PFC RECTIFIER [43]                                      | 28 |

| FIGURE 3.8: REVERSE RECOVERY CHARGE TEST RESULT FOR SI MOSFET AND GAN HEMT WITH SIMILAR ON      | i- |

| RESISTANCE, SHOWING A 20X REDUCTION OF QRR FOR GAN [48]                                         | 29 |

| FIGURE 3.9: GAN TOTEM-POLE (A) SIMPLIFIED SCHEMATICS AND ILLUSTRATION (B) POSITIVE AC CYCLE (C) |    |

| NEGATIVE AC CYCLE [48]                                                                          | 30 |

| FIGURE 3.10: TYPICAL SMART GRID [50]                                                            | 32 |

| FIGURE 3.11: RECTIFIER AND BATTERY SYSTEM FOR TELECOM APPLICATION [FROM ELTEK AS]               | 34 |

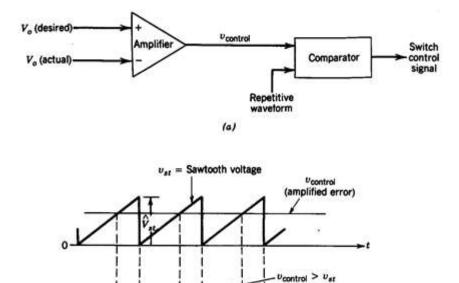

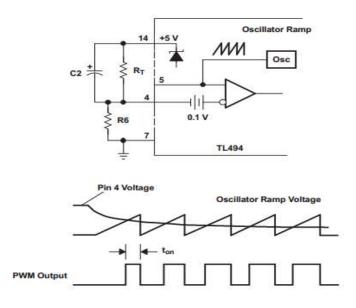

| FIGURE 4.1: PWM GENERATOR (A) BLOCK DIAGRAM (B) PWM SIGNAL [1]                                  | 36 |

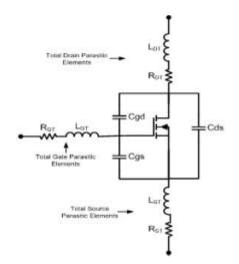

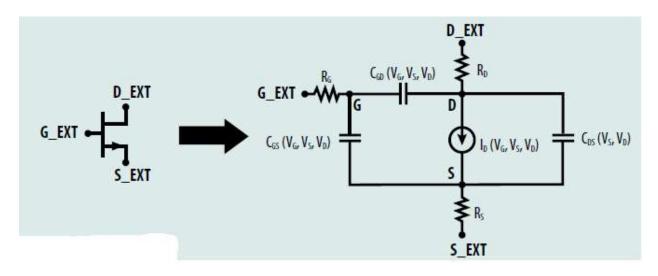

| FIGURE 4.2: MOSFET PARASITIC ELEMENTS [55]                                                      | 37 |

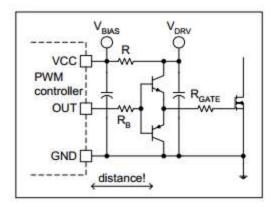

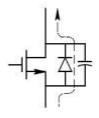

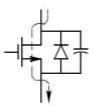

| FIGURE 4.3: BIPOLAR TOTEM-POLE MOSFET GATE DRIVER [55]                                          | 39 |

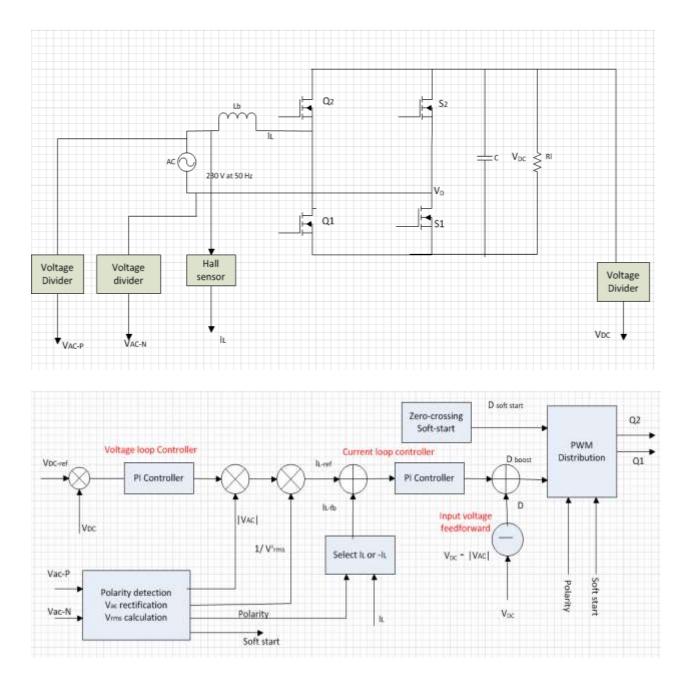

| FIGURE 4.4: TOTEM-POLE TOPOLOGY WITH CONTROL CIRCUIT BLOCK DIAGRAM                              | 40 |

| FIGURE 4.5: ZVS SCHEME                                                                          | 41 |

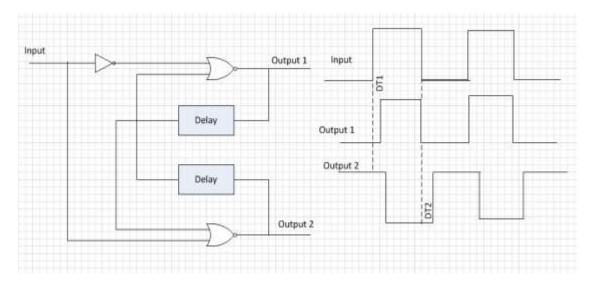

| FIGURE 4.6: DEAD-TIME GENERATION CIRCUIT                                                        | 43 |

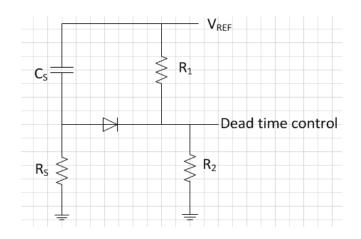

| FIGURE 4.7: SOFT-START CIRCUIT                                                                  | 44 |

| FIGURE 4.8: SOFT-START CIRCUITS WITH TL 494 – PWM CONTROL CIRCUIT [56]                          | 45 |

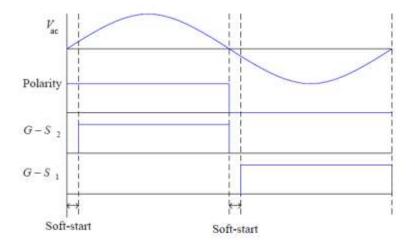

| FIGURE 4.9: TIMING OF GATE SIGNALS FOR TWO ACTIVE MOSFET SWITCHES (S1 AND S2)                   | 45 |

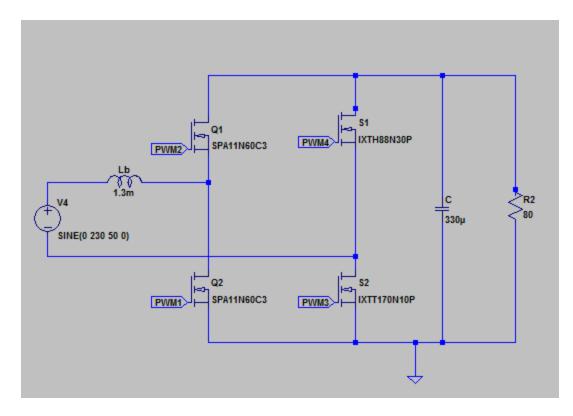

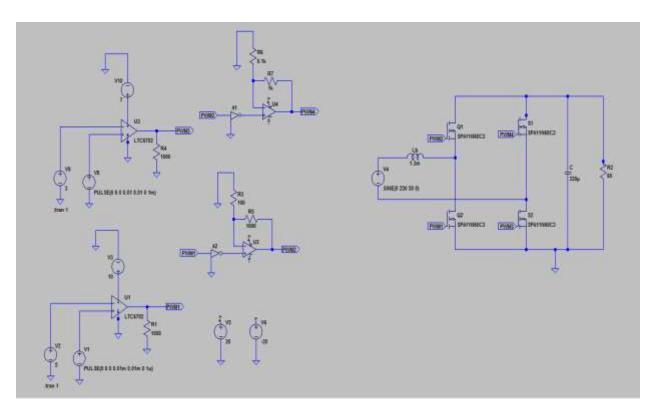

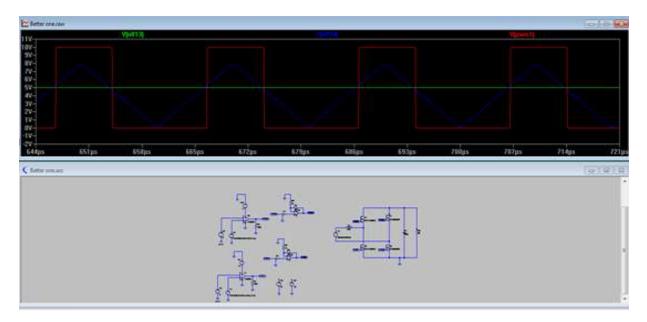

| FIGURE 5.1: LTSPICE IV MODEL FOR TOTEM-POLE PFC BOOST CONVERTER TOPOLOGY                        | 50 |

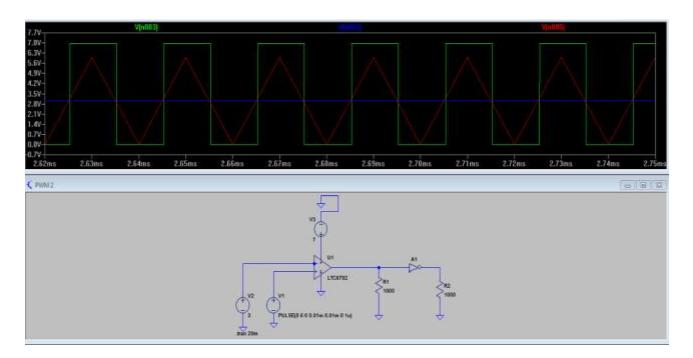

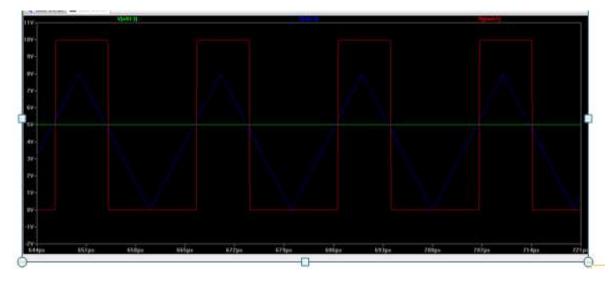

| FIGURE 5.2: PWM GENERATOR WITH ITS OUTPUT WAVE FORM ON LTSPICE IV                               | 51 |

| FIGURE 5.3: GATE DRIVER CIRCUIT                                                                 | 52 |

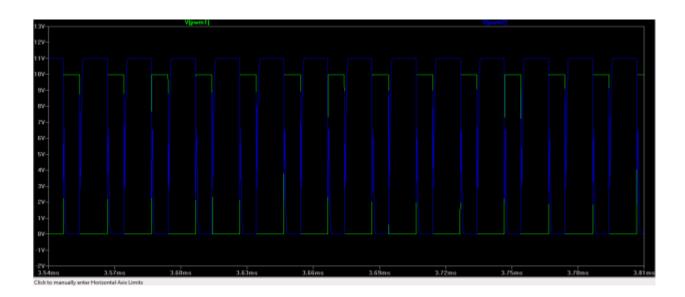

| FIGURE 5.4: GATE DRIVER SIGNALS FOR Q1 (PWM1 - GREEN) AND Q2 (PWM2 - BLUE)                      | 52 |

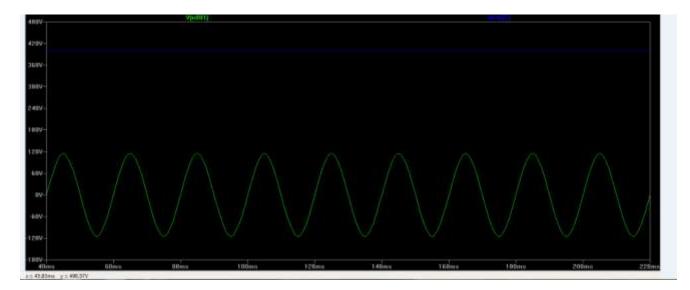

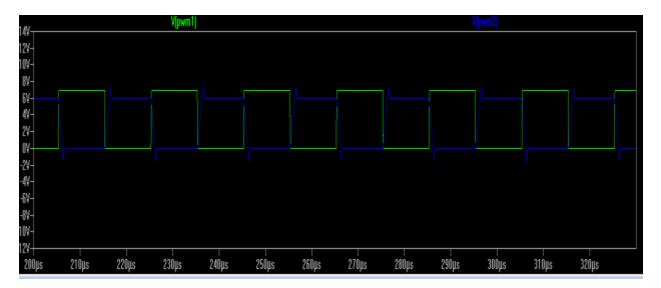

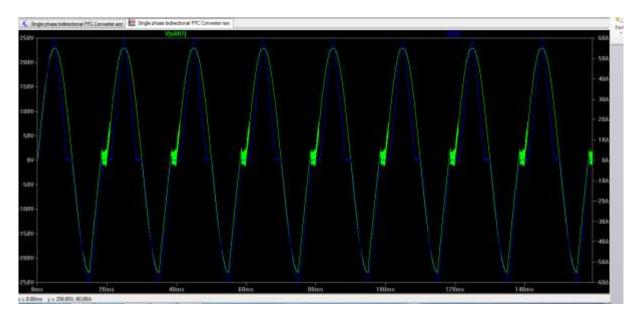

| FIGURE 5.5: WAVEFORM OF 230V AC INPUT (GREEN) AND 400V DC OUTPUT (BLUE)                         | 53 |

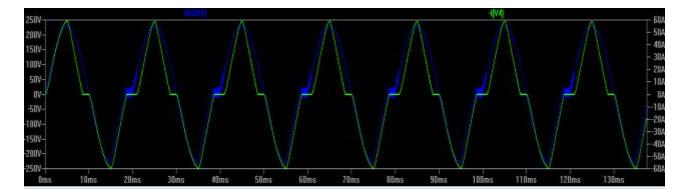

| FIGURE 5.6: EFFECT OF SOFT-START                                                                | 53 |

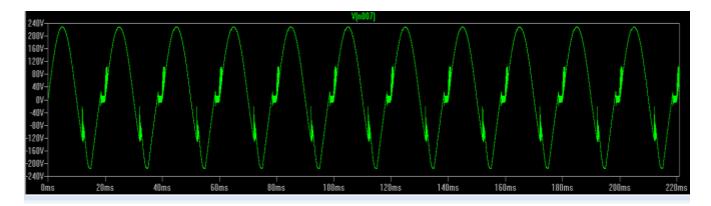

| FIGURE 5.7: WAVE FORM FOR INPUT CURRENT (GREEN) AND INPUT VOLTAGE (BLUE)                        | 54 |

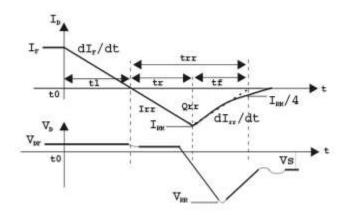

| FIGURE 6.1: TYPICAL REVERSE RECOVERY WAVEFORM FOR BODY DIODE IN POWER MOSFET [57]               | 57 |

| FFIGURE 6.2: COMMERCIAL AVAILABLE 1200V «C2M0160120D» SIC MOSFET FROM CREE                      |    |

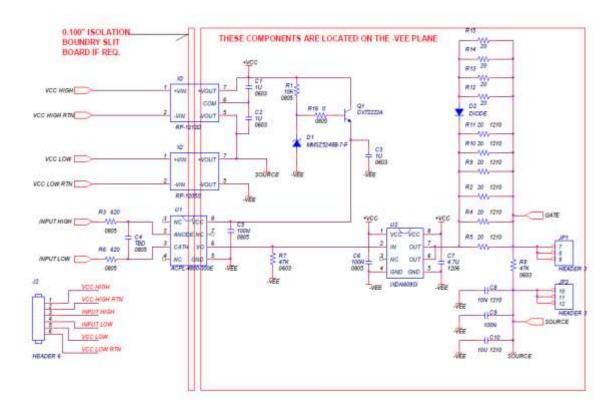

| FIGURE 6.3: SCHEMATIC DIAGRAM OF CRD-001 SIC ISOLATED GATE DRIVER [CREE]                        | 59 |

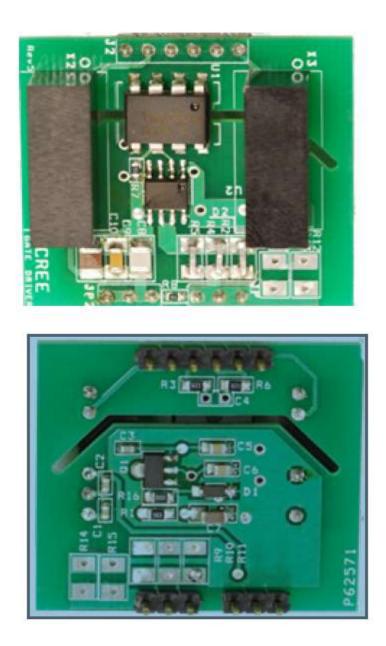

| FIGURE 6.4: CRD-001 SIC MOSFET GATE DRIVER FROM CREE, TOP VIEW (UPPER) AND BOTTOM VIEW          |    |

| (LOWER)                                                                                         | 60 |

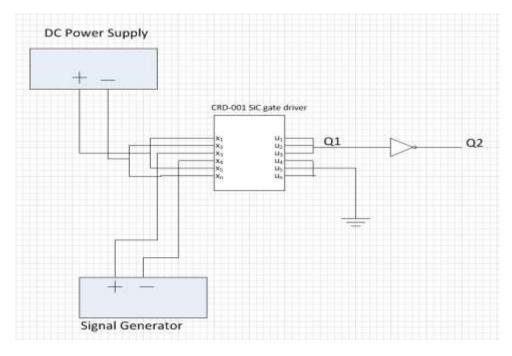

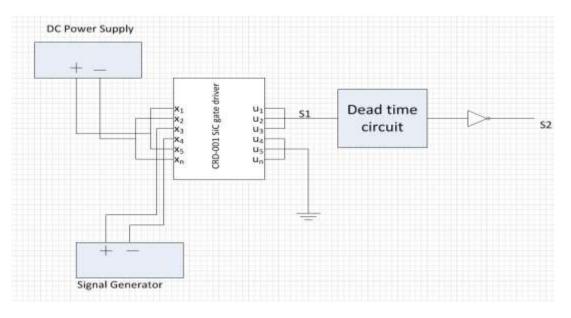

| FIGURE 6.5: CRD-001DRIVER PIN INTERCONNECTION AND PWM SIGNALS FOR Q1&Q2                         | 61 |

| FIGURE 6.6: PWM SIGNALS FOR S1 AND S26                                                             | 31 |

|----------------------------------------------------------------------------------------------------|----|

| FIGURE 6.7: DIODES USED TO BYPASS INRUSH CURRENT DURING START-UP                                   | 32 |

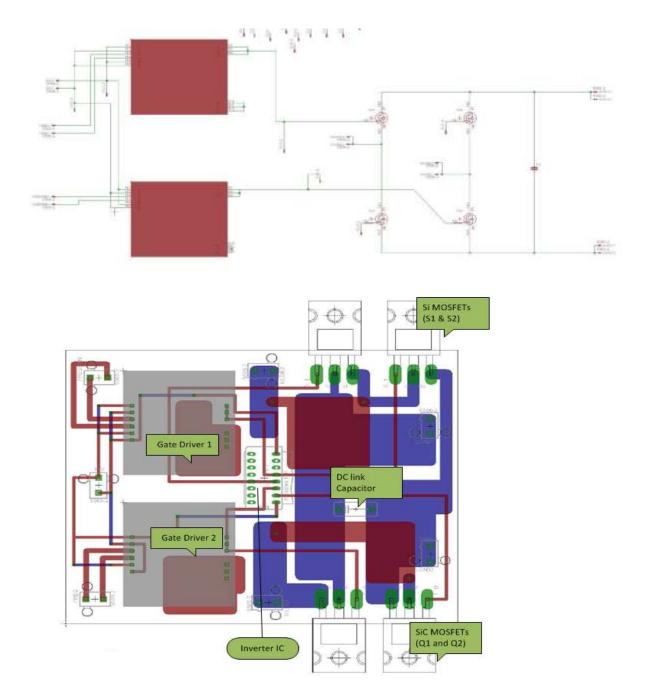

| FIGURE 6.8: PCB SCHEMATIC DIAGRAM AND BOARD LAYOUT OF THE PROTOTYPE                                | 33 |

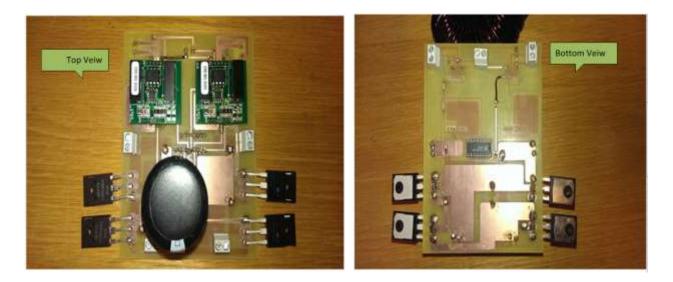

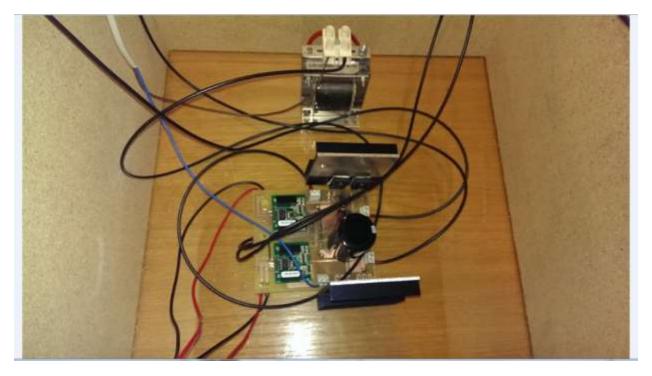

| FIGURE 6.9: TOP AND BOTTOM VIEW OF THE TOTEM-POLE PFC BOOST CONVERTER PROTOTYPE6                   | 54 |

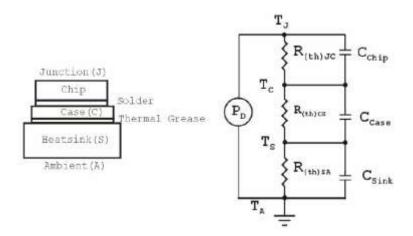

| FIGURE 6.10: POWER MOSFET CHIP THERMAL MODEL WITH SIMPLIFIED HEAT SINK SYSTEM [57]6                | 54 |

| FIGURE 6.10: PROTOTYPE FOR THE TOTEM-POLE PFC BOOST WITH HEAT SINK6                                | 66 |

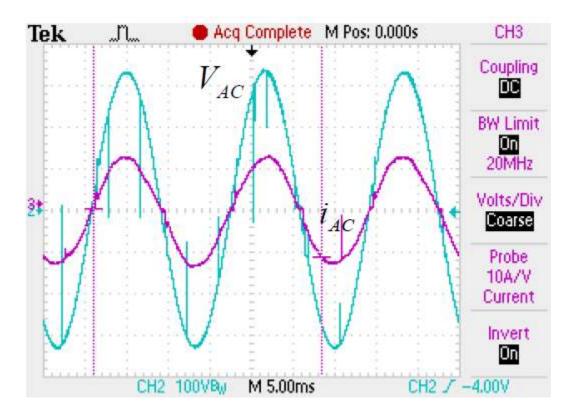

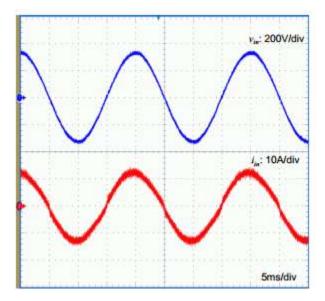

| FIGURE 6.11: WAVEFORM OF SIC BASED TOTEM-POLE BRIDGELESS PFC AT FULL LOAD 1KW. CH2: INPUT AC       |    |

| VOLTAGE(100V/DIVISION); CH3: INPUT AC CURRENT (5A/DIVISION)                                        | 37 |

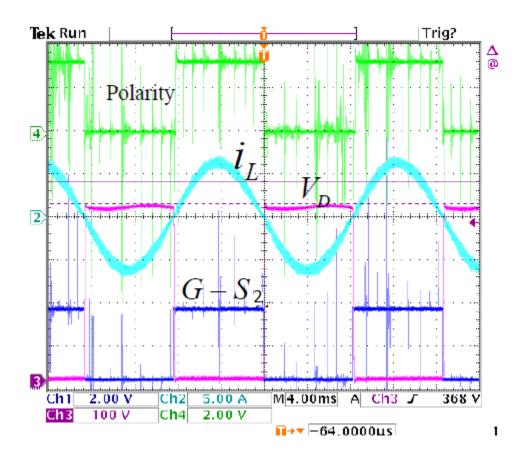

| FIGURE 6.12: (A) CH1: PWM GATE SIGNAL FOR S2; CH2: IL WAVEFORM (5A/DIVISION); CH3: VD WAVEFORM     |    |

| (100V/division); CH4: AC INPUT POLARITY SIGNAL6                                                    | 38 |

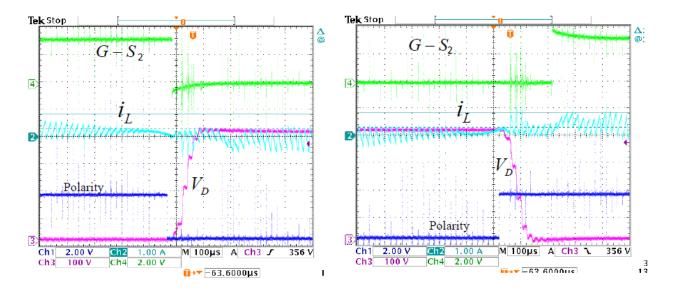

| FIGURE 6.13: ZERO-CROSSING TRANSITIONAL WAVEFORM (A) FROM POSITIVE TO NEGATIVE HALF CYCLE (B) FROM | М  |

| NEGATIVE TO POSITIVE HALF CYCLE CH1: AC INPUT POLARITY; CH2: $I_L$ WAVEFORM; CH3: $V_D$ WAVEFORM;  |    |

| CH4: PWM gate for S26                                                                              | 39 |

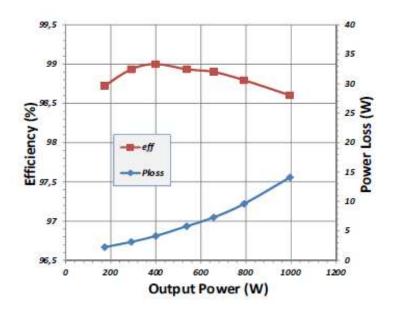

| FIGURE 7.1: MEASURED EFFICIENCY FOR GAN TOTEM – POLE TOPOLOGY                                      | 72 |

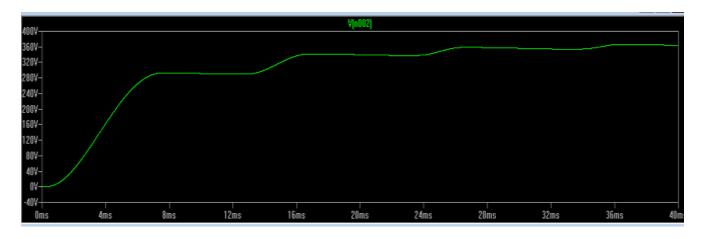

| FIGURE 7.2: OUTPUT VOLTAGE WAVEFORM DURING START-UP7                                               | 73 |

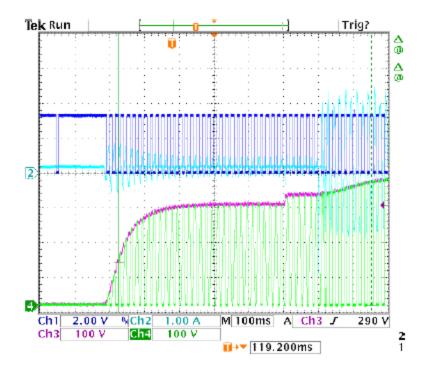

| FIGURE 7.3: START-UP OF THE TOTEM-POLE PFC PROTOTYPE (CH1: AC POLARITY, CH2: INDUCTOR CURRENT,     | ,  |

| CH3: OUTPUT VOLTAGE (VO), CH4: VD)7                                                                | 75 |

# Acronyms and Symbols

| А       | Ampere                                               |

|---------|------------------------------------------------------|

| AC      | Alternating Current                                  |

| ACMC    | Average Current Mode Control                         |

| ССМ     | Continuous Conduction Mode                           |

| СМ      | Common mode                                          |

| CSPI    | Cooling System Performance Index                     |

| DCM     | Discontinuous Conduction Mode                        |

| DC      | Direct Current                                       |

| DAB     | Dual Active Boost                                    |

| 2-DEG   | two dimensional electron gases                       |

| EMI     | Electromagnetic Interference                         |

| GaN     | Gallium Nitride                                      |

| HEMT    | High Electron Mobility Transistor                    |

| IC      | Integrated Circuit                                   |

| IEC     | International Electromechanical Commission           |

| IEEE    | Institute of Electrical and Electronics Engineers    |

| IGBT    | Insulated-Gate Bipolar Transistor                    |

| JFET    | Junction Field Effect Transistor                     |

| LTE     | Long Term Evolution                                  |

| LTSpice | Linear Technology Spice                              |

| MPP     | Magnetics Molypermalloy Powder                       |

| MOSFET  | Metallic Oxide Semiconductor Field Effect Transistor |

| Ni-Cad  | Nickel cadmium                                       |

| ORNL    | Oak Ridge National Laboratory                        |

| PF      | Power Factor                                         |

| PFC             | Power Factor Correction                            |

|-----------------|----------------------------------------------------|

| PWM             | Pulse Width Modulation                             |

| Qrr             | Reverse Recovery Charge                            |

| R&D             | Research and Development                           |

| RoHS            | Restriction of Hazardous Substances                |

| Si              | Silicon                                            |

| SiC             | Silicon Carbide                                    |

| SPICE           | Simulated Program with Integrated circuit Emphasis |

| SBD             | Schottky Barrier Diode                             |

| SMPS            | Switch Mode Power Supply                           |

| Std.            | Standard                                           |

| ТСМ             | Triangular Current Mode                            |

| THD             | Total Harmonic Distortion                          |

| ТІ              | Texas Instrument                                   |

| t <sub>rr</sub> | Reverse recovery time                              |

| UPS             | Uninterruptable Power Supplies                     |

| V               | Voltage                                            |

| W               | Watt                                               |

| WDG             | Wide Band Gap                                      |

| ZCS             | Zero Current Switching                             |

| ZVS             | Zero Voltage Switching                             |

### **1** Introduction

This master thesis is a continuation of my specialization project in fall 2013. Some part of the thesis work was carried out in specialization project phase and hence they are included in the thesis report with some alteration.

Chapter one discusses about background of AC-DC power converter with PFC boost stage. The need for a bidirectional PFC boost converter for telecom application is also the focus of this chapter. State-of-the art of wide band gap devices and PFC are also covered together with relevant literature reviews. Scope and limitation of the thesis work and the structure of the report are discussed at the end of the chapter.

#### 1.1 Background

Different electrical loads require different amount of electric power for their operation. However, most of the time the electric power supplied from utility companies is AC power. This implies that there should be some kind of power processing unit which can fill the gap between the demand of electric power required by the different DC loads and the fixed AC power. Solid state devices can be used to process and control electrical energy such as rectifiers, inverters and DC-DC converters [1]. The AC-DC converters, commonly known as rectifiers, can be realized using diodes or controlled solid state switches such as Power MOSFETs.

The input current drawn from the AC mains contain harmonics. Power electronic equipment, welding machines, transformers, motors and generators are major cause for the degradation of power quality in the mains. Current harmonics result in damage to sensitive electronic equipment, excessive overheating of capacitors and interference with neighboring electronic equipment. The input current drawn should be shaped in accordance with the input voltage waveform so that current harmonics will be reduced in the mains [2].

The quality of power in AC lines can be measured, quantitatively, by power factor (PF) and total harmonic distortion (THD). Power factor can be defined as the ratio of the amount of useful power being consumed by an electrical system to apparent power in the circuit. The current harmonics can be reduced by incorporating power factor correction (PFC) circuit in the rectifiers [3].

**1** Introduction

#### **1.2 Motivation**

The demand on solid state AC-DC power converters increases from time to time. They are employed in several application areas such as uninterruptable power supplies (UPSs), back up energy storage systems, hybrid electric vehicle chargers, power supply for telecom loads and adjustable speed drives (ASDs) [3]. However, the power converters draw pulsating input current from the utility grids which results in poor power factor. Meanwhile, the converters pollute the AC mains by injecting significant amount of harmonic current from the switching devices due to high switching frequency [4]. Improving the poor power quality becomes a great challenge for power supplying companies (utilities) as well as power converter manufacturers.

The quality of input current drawn by low power electronic devices depends on the amount of current harmonics at the mains. In order to meet harmonic regulation and standards, such as IEC 61000-3-2 and IEEE Std 519, active PFC circuit is added as a front end stage [5].

The purpose of IEEE 519 is to recommend limits on harmonic distortion according to two distinct criteria, namely:

- There is a limitation on the amount of harmonic current that a consumer can inject into a utility network.

- A limitation is placed on the level of harmonic voltage that a utility can supply to a consumer [58].

The PFC circuit can reduce a significant amount of current harmonics. Low electromagnetic interference (EMI) can be achieved by employing boost type PFC converter as compared to other types of active PFC converters in continuous conduction mode (CCM) [5]. Moreover, most of the bridgeless topologies implemented so far are boost type configuration (also referred as dual-boost PFC rectifiers) because of its low cost and its high performance in terms of efficiency, power factor and simplicity [6].

Most of the PFC converters available today are unidirectional, from the AC mains to the DC load. Power electronics rectifiers are the primary source of electric power for DC telecom loads and batteries are used as a backup power supply during failure of the rectifiers or power outage. However, most of the rectifiers employed on this sector are unidirectional and the energy stored in the batteries is not utilized properly. Hence, this master thesis project targets to design and

implement a converter which allows a bidirectional power flow between AC mains and the batteries so that the reserve energy in the batteries can be efficiently utilized.

An imminent to produce high PF rectifiers with reduced harmonic content in the input current, minimized EMI level, high efficiency, high power density, and lower cost and of course bidirectional power flow. In this paper, to meet this motivation, several single phase AC-DC boost converter topologies dedicated to PFC are studied and the best topology is selected and implemented using SiC and GaN.

Recently, many researchers and semiconductor manufacturers are attracted towards WBG materials and devices in order to use their benefits as switches in power converter application. Diodes and transistors made from SiC show a promising result in enhancing the power density and efficiency. Moreover, the newly invented GaN HEMT will be the future semiconductor material to produce the most efficient power converter.

#### 1.3 State - of - the art

In this paper, state-of-the art for bidirectional PFC boost converter is discussed by looking the PFC converter stage and the impact of wide band gap materials on the efficiency of switch mode converter.

#### **1.3.1 Power Factor Correction (PFC) Converter**

These days, there is a dramatic increase in electrical loads and hence harmonic pollution of AC grid needs a lot of attentions. AC-DC converter with power factor correction is realized in order to address this issue. In passive PFC, large capacitor bank or LC tuned filter may be required to suppress the low frequency ripple which in turn results in large volume and weight of the converter [6].

According to [7] and [8], passive PFC converters provide a lot of advantages over active PFC converters based on ease of construction, reliability, reduced noise and surge, and also it avoids the high frequency EMI. However, their application is limited to low power, mostly below 200W, due to the bulky size of the filters, lack of voltage regulation, very sensitive to line frequency. Moreover, the fundamental component of current harmonics results in a phase shift that leads to a reduction in power factor. As suggested on [5], active boost AC-DC converter

dedicated to PFC circuit can alleviate most of the problems related to passive PFC by replacing large resistors, inductors and capacitors by controlled solid state switches.

The conventional single stage AC–DC boost converter consists of a bridge diode, boost inductor and transistor switch. Even though this converter is very simple in construction, it provides low efficiency characteristics due to high switching loss in the diode bridge rectifier and high snubber loss [5], [9].

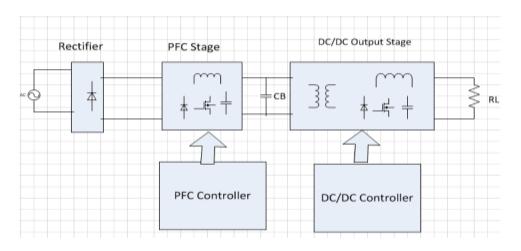

Since the two stage AC-DC converter incorporate PFC stage and DC–DC stage, the cost and size of the converter are somehow higher than single stage converter. However, the DC-DC converter stage is easy to design because the input voltage is fixed link capacitor voltage and hence the size and efficiency of DC-DC stage is improved. Moreover, size of input filters decreases due to the effect of PFC stage. High power density and high efficiency can be achieved by using two stage AC-DC boost converter with PFC topology [10], [11].

In this paper, only the bidirectional PFC - boost conversion stage will be covered. The DC-DC conversion stage is covered by a fellow student. Figure 1.1 show two-stage AC-DC converter structure.

Figure 1.1: Two-stage AC-DC converter structures [12]

The selection of a suitable converter topology for a specific application is based on several criteria such as power density, efficiency, cost, complexity, and robustness. Within this context, a lot of work has been done in the last few years in order to improve the characteristics of conventional converters used for PFC purpose, such as the reverse recovery problem of boost diode as well as an increase in the output voltage of the converter [5], [12], [13] and [14].

In another research, the performance of the PFC converter has been evaluated by using two different switching schemes; hard switched dual boost PFC rectifier and a soft switched triangular current mode PFC. According to [15], a maximum efficiency of 99.2 % at a power

#### **1** Introduction

density of 1.1kW/dm<sup>3</sup> has been achieved using the dual boost rectifier. For higher power density, the efficiency might be compromised and in dual boost rectifier the efficiency can be improved by 0.5 % with the expense of a decrease in power density by 1kW/dm<sup>3</sup>. In order to avoid the limitation imposed by the switching losses, a new topology called Triangular Current Mode (TCM) resonant-transition PFC rectifier with zero voltage switching (ZVS) is proposed. Based on the research, this approach provides a power density of 5kW/dm<sup>3</sup> at efficiency of 98.3%.

In this paper, a novel bidirectional AC-DC converter using MOSFETs for all active switches is proposed for energy storage system applications. According to [16], the reverse recovery dissipation of the power switch is greatly reduced due to absence of freewheeling current flowing through the body diode of power MOSFET. The advent of high electron mobility transistors such as gallium nitride will be a key enabler for efficient bidirectional PFC boost converters.

#### 1.3.2 Wide band gap materials (WBG)

Before the advent of wide band gap (WBG) materials, silicon was dominant semiconductor material used for switch application. WBG materials, such as silicon carbide and gallium nitride, enable the development of smaller semiconductor device that demonstrate significantly higher performance while demanding less power than more commonly used silicon semiconductor devices [17]. With the properties suitable for conducting electricity in extreme environments, they are ideal devices for applications that are subjected to high voltages and temperatures application found in electric vehicles and telecom converters which are located in harsh environment conditions.

Despite the benefits, commercial viability of wide band gap materials and devices is limited with pricing 3 to 5 times higher than silicon semiconductor devices. WBG materials contribute about 40% of the total cost device cost depending on the availability, quality and performance. Device design, fabrication and packaging are also key factors to higher cost.

According to [17], a world leader in materials research, Oak Ridge National Laboratory (ORNL), is applying vast expertise in a single crystal growth, epitaxial film decomposition and buffer development to improve the quality of WBG semiconductors by reducing internal defects and stresses.

GaN HEMTs and SiC MOSFTEs play a very important role in producing a high quality PFC converter. The devices are supposed to produce high efficiency and power density converter with almost unity power factor.

#### **1.4 Scope and Limitation of the thesis**

The scope of the project work encompasses:

- Reviewing of bidirectional converter topologies dedicated to PFC

- Over view of bidirectional PFC- boost converter for smart grid functionality

- Evaluate and analyze different bidirectional PFC boost topologies

- Design and implement the proposed topology

- Study the performance of silicon (Si), silicon carbide (SiC) and gallium nitride (GaN) in order to meet the desired requirement for the proposed converter.

- Design frequency control and voltage control

- Simulation based study on the proposed converter

- Establish experimental set up and discuss on the results

- Compare the results from simulation and laboratory

- Testing the new topology and providing a prototype

In any given research, there are always some limitations. In view of the foregoing, I hereby list some of the limitations of this thesis:

- It was unable to find GaN HEMT model in LTspice software so that Si MOSFETs with characteristics somehow similar to WBG devices are used instead.

- It was difficult to get freestanding substrate for GaN switching devices for the laboratory work.

#### **1.5 Structure of the report**

The first chapter presents the background of the PFC boost converter. Moreover, the motivation of the master thesis and state-of-the art of PFC boost converter together with wide band gap devices are also the main discussion points. Chapter 2 deals about the properties of wide band gap materials and also selection of WBG devices for the specific type of power converter. The third chapter mainly focuses on topology study. Active power factor correction converter,

synchronous rectification and bidirectional PFC with totem-pole topology are briefly discussed. Smart grid functionality and battery management system are also point of discussion in this chapter. Design and implementation phase of the proposed converter is seen on chapter 4. Different gate drive control circuits are discussed including digital control techniques. Chapter 5 presents the simulation task on the novel bidirectional PFC-boost topology. List of components and equipment together with experimental set up are dealt on chapter 6. The main findings of the study, both from simulation task and lab experiment, are briefly discussed in chapter 7. The last chapter, chapter 8, gives conclusion of the thesis project and proposes future works to be done in the topic.

### 2. Comparison and Selection of Switching Devices

The main focus of this chapter is to study the property of semiconductor materials, specifically wide band gap (WBG), in order to get better performance from a power converters.

#### 2.1 Wide band gap materials

Most power converters and wireless communication systems require switching devices having high breakdown voltage, high thermal conductivity and operate at high frequency [18]. Silicon based semiconductor technology doesn't fulfill all the above requirements due to its narrow band width. Currently, the focus of many researches is towards wide band gap devices (WDG) such as Silicon Carbide, Gallium Nitride and Diamond to address the shortcomings associated with Si based switching devices. Among those devices, diamond provides extremely large band gap and also has unique thermal characteristics but the research is at very early stage and needs more detailed study in the future. SiC and GaN show the best trade-off between theoretical characteristics, real commercial availability and maturity of their technological process [19]. SiC possess high thermal conductivity and wide band gap which makes the device a good choice for power electronics application. However, GaN offers a direct band gap and high frequency performance; because of which it finds great applications in optoelectronics and RF (radio frequency) devices [18].

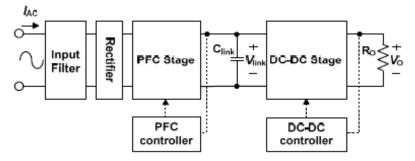

In nowadays, silicon carbide (SiC) power switching device has got a lot of attention in power electronics industry which require high power and high temperature. The concentration of intrinsic charge carrier (n<sub>i</sub>) in SiC is lower than conventional silicon based switching devices at specified temperature and this characteristic makes it better choice for high temperature application even in harsh environment. SiC MOSFETs can handle more than 700°c of junction temperature. Whereas; Si-based switching device can only work at a maximum temperature of 175°c at specified intrinsic charge carries [20].

#### 2.2 Properties of WBG Semiconductor materials

Selecting the suitable semiconductor material used for power switches is not an easy task. It is very important to look and examine the property of the material in the design of a power

converter. The main critical properties in the selection of switching device are band gap, electric breakdown field and thermal conductivity.

In addition to these, drift region width, on-resistance, saturation drift velocity and coefficient of thermal expansion also play significant role in determining the right choice of switching device for specific type of converter.

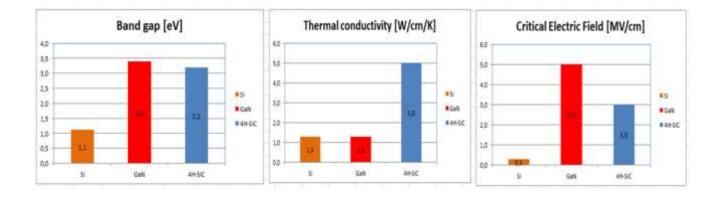

#### 2.2.1 Band gap

In semiconductor physics, the band gap refers to the minimal energy state in the conduction band and the maximal energy state in the valance band. Wide band gap device requires more energy for the intrinsic charge carriers to cross the gap this results in lower leakage current in the blocking mode. The junction temperature of the WBG device is very high so that it can be used for high temperature application. Moreover, it provides reduced heat sink size and which in turn leads to a significant decrease in weight and cost of the converter. Figure 2.1 show the intrinsic charge carrier concentration versus junction temperature graph for Si and SiC with 4H hexagonal close packing of polytypes.

$$ni^2 = C.exp \frac{q.Eg}{KT}$$

[Eq 2.1]

Where, ni =Intrinsic concentration (cm<sup>-3</sup>), C=Constant (exact value depends on material and temperature [per unit volume]), q= Electron charge (C), Eg= Band gap (eV), K= Boltzmann's constant (J/K) and T=Temperature (K).

From the relationship given in equation [2.1], the concentration of intrinsic charge carriers is directly proportional to the band gap and inversely proportional to the junction temperature of the device.

Figure 2.1: Intrinsic charge carriers' vs Temperature graph for Si and SiC [21]

As it is shown in Figure 2.1, for a large temperature range, intrinsic charge carrier concentration of 4H-SiC stays below 10<sup>15</sup> cm<sup>-3</sup>, where the intrinsic conduction of the semiconductor starts and it behaves as a bulk resistor and will not act as a semiconductor anymore. The intrinsic charge carrier concentration (n<sub>i</sub>) of 4H-SiC at 700°C is equal to that of Si at 100°C. SiC does not approach this critical intrinsic carrier concentration until temperature exceeds 1000°C. From this, we can see that SiC power semiconductor devices can operate at much higher temperature than Si made power semiconductors device [21].

#### 2.2.2 Electric breakdown field

High electric breakdown field enables the drift layer structure to be thinner and shorter which results in low specific on-state resistance, R<sub>on-sp</sub>. The key figure of merit for power switching devices is the specific on-resistance and this parameter explains directly how much resistive loss a device generates in the forward conduction mode [21]. On-resistance of SiC polytypes (3H, 6H & 4H) and GaN devices is approximately 10 times less than Si based devices and hence WBG device provide much higher efficiency [18].

As an example, SiC can handle a higher electric field, approximately 10 times, than the Si before breakdown occurs. High electric field property of SiC enables to fabricate a semiconductor device very much thinner than its Si counterpart, approximately 0.1 times thinner. In addition to this, more highly doped drift layer and lower on-resistance can be

achieved which is 10 times doping concentration and 10 times lower resistance than Si on the same blockage voltage [21].

Figure 2.2: Comparison of unipolar limit of specific on-resistance versus blocking voltage for some device types in Si and SiC [22].

The mathematically relationship between specific on resistance and electric breakdown field for unipolar device is given as:

$$R_{on,sp} = \frac{4V_B^2}{\varepsilon \mu_n V E_C^3} \qquad [Eq 2-2]$$

Where,  $V_{B}$ = Breakdown voltage (V),  $E_{c}$ =Critical electrical field (V/cm),  $\varepsilon$  = permittivity (F/cm<sup>2</sup>),  $\mu_{n}$ =Electron mobility (cm<sup>2</sup>/V/s).

#### 2.2.3 Higher saturation electron drift velocity

Saturation velocity is the maximum velocity a charge carrier in a semiconductor, generally an electron, attains in the presence of very high electric fields [23]. Charge carriers normally move at an average drift speed proportional to the electric field strength they experience temporally. The proportionality constant is known as mobility of the carrier, which is property of the material. A charge carrier cannot move any faster once its saturation velocity has reached [24].

Saturation velocity is a very important parameter in the design of a semiconductor device, especially field effect transistor. Typical values of saturation velocity might vary greatly for

different semiconductor materials, for example Si has saturation velocity about  $1 \times 10^7$  cm/s whereas; WBG devices such as GaAs and 6H-SiC have near to  $1.2 \times 10^7$  cm/s and  $2 \times 10^7$  cm/s respectively. Typical electric field strength at which carrier velocity saturate is usually on the order of 10-100 kV/cm.

High saturated drift velocity directly proportional to high switching frequency capabilities and therefore the power devices based on WBG can be switched at higher frequencies. This results in an extremely reduced in conduction and switching losses (much superior performance) thereby increasing efficiency [21].

#### 2.2.4 High thermal conductivity

Thermal conductivity can be defined as the rate of heat transfer between two materials. WBG devices have high thermal conductivity and hence they transmit heat faster than Si based semiconductor devices. Higher thermal conductivities ease heat sinking requirements for WBG devices.

#### 2.2.5 Coefficient of thermal expansion (CTE)

CTE measures the fractional change in size per unit change in temperature at a constant pressure. Semiconductor materials that have a closer CTE match to available electrically insulating ceramics (or the packing) can more easily be adapted for high power and wider temperature excursion applications. The table below summarizes some of the property of major power semiconductor materials.

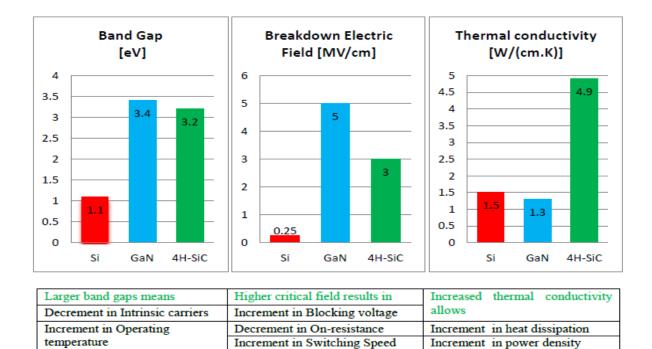

Figure 2.3: Comparison of three major physical properties of semiconductor devices using graph

| Property                                                            | Si    | GaAs | 3H-SiC | 6H-SiC | 4H-SiC | GaN       | Diamond |

|---------------------------------------------------------------------|-------|------|--------|--------|--------|-----------|---------|

| Band gap, Eg (eV @300K)                                             | 1.12  | 1.4  | 2.3    | 2.9    | 3.2    | 3.39      | 5.6     |

| Critical Electric field, Ec (x10 <sup>5</sup><br>V/cm)              | 3.0   | 4.0  | 20     | 25     | 30     | 50        | 560     |

| Thermal conductivity, λ (W/cm/K<br>@300K)                           | 1.3   | 0.54 | 5.0    | 5.0    | 5.0    | 1.3       | 20      |

| Saturation electron drift velocity,<br>Vsat (x10 <sup>7</sup> cm/s) | 1.012 | 2.0  | 2.5    | 2.0    | 2.0    | 2.0       | 3.0     |

| Electron mobility, µn (x10 <sup>3</sup> cm <sup>2</sup> /V/s)       | 1.45  | 8.5  | 1.0    | 0.415  | 0.95   | 1.0       | 2.2     |

| Hole mobility, μp (x10 <sup>3</sup> cm <sup>2</sup> /V/s)           | 0.45  | 0.4  | 0.045  | 0.09   | 0.115  | 0.03<br>5 | 1.8     |

| Dielectric constant, ɛr                                             | 11.7  | 12.9 | 9.6    | 9.7    | 10     | 8.9       | 5.7     |

Table 2.1 Physical properties of various semiconductors for power devices [26].

#### 2.3 Comparison of wide band gap (WBG) devices

Recently, most power electronics manufacturers are more attracted in fabrication of WBG devices to exploit their high power and high temperature advantages. WBG devices, especially SiC and GaN, provide the best trade-off between material properties and commercial maturity [26]. These devices can be used for wide range of power application as shown in the figure below. However, this paper only focuses on low power converter application, in few ranges of kilowatts; specifically power supply/PFC range as depicted in Figure 2.4.

Figure 2.4: Entire ranges of power applications that can be addressed with SiC and GaN [28]

#### 2. Comparison and Selection of Switching Devices

Figure 2.5 illustrate the summary of Silicon, Silicon carbide and Gallium nitride devices with respect to the properties of semiconductor materials. GaN can be used for high voltage and high switching frequency operations. Whereas, high temperature application needs a semiconductor material like SiC. Therefore, it is a trade-off to choose either of the WBG devices for desired application.

Figure 2.5: Summary of Si, SiC, and GaN relevant material properties [19]

### 2.3.1 Silicon Carbide (SiC)

Silicon carbide device technology has matured greatly over the past decades and gone from research to commercial production. The semiconductor technology greatly depends on the substrate and the epitaxial material. By definition, substrate or wafer is the crystalline material whereas epitaxy is the overlay deposition on the substrate [27]. In the last decade, a great improvement has been observed on the material quality and epitaxial processes of SiC and currently it is able to manufacture 100 mm wafers without any degradation. The material quality of 4H-SiC wafers and epitaxial is at such a high quality that many companies are offering commercial SiC wafers and epitaxial on 4H-SiC with wafer diameter 100 mm [22].

# 2.3.1.1 SiC Diodes

The market share of SiC by CREE and Infineon is substantially increased since 2009 [22]. SiC diodes are mainly used in power factor correction circuits (PFC), power supplies and recently photovoltaic (PV) inverters. The main advantage of the schottky barrier diodes (SBD) is the absence of reverse recovery current during switching; hence it is possible to increase the switching frequency considerably. Moreover, it can provide a significant decrease in volume, weight and cost for the system. For higher voltage (>3kV) either pn-diode structures or merged SBD/pn designs are considered because of the superior reverse blocking and surge current capability.

| SiC Power<br>rectifiers          | State-of-the art device                                 | Availability                                               | Features                                                                                                                                       |

|----------------------------------|---------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| PiN diode                        | CREE 10kV, 20A 2"<br>wafer                              | Commercially<br>available (CREE and<br>Infinion basically) | High voltage operation with low<br>on-state resistance and low<br>leakage current but requires<br>reverse recovery charge during<br>switching. |

| Schottky Barrier<br>Diodes (SBD) | CREE1.2kV, 50A die<br>size 5.6 mmx5.6 mm                | Commercially<br>available (CREE and<br>Infinion basically) | Free from reverse recovery<br>current, extremely high switching<br>speed but lower blocking voltage<br>and higher leakage current.             |

| Junction Barrier<br>Diode        | CREE 10kV, 20A 3"<br>wafer Chip size 10.6<br>mmx14.9 mm | Commercially<br>available (CREE and<br>Infinion basically) | Schottky like on-state and<br>switching characteristics and PiN<br>like off-state characteristics.                                             |

| Table 2.2 Summary | of the latest | progress on S | SiC power | rectifiers [21] |  |

|-------------------|---------------|---------------|-----------|-----------------|--|

|-------------------|---------------|---------------|-----------|-----------------|--|

The major SiC power device products are still rectifiers based on Schottky barrier diodes (SBD) or junction barrier diodes (JBD). Nevertheless, many companies are manufacturing active power switching devices based on MOSFETs, JFETs and BJTs.

# 2. 3.1.2 SiC MOSFETs

One of the greatest achievements in the area of Silicon carbide power semiconductor device technology was the development of high voltage power MOSFETs. One of the challenges to use SiC MOSFET in power application is stability of the oxide layer. Recently, vertical power MOSFTE becomes quite popular for power switching application. It operates in normally-off (enhancement mode) and doesn't require complex gate drive circuit. However, this device has a short coming in terms of reliability due to sensitivity of gate dielectric and also relatively poor

channel mobility under the gate dielectrics. The low mobility gives the MOSFETs a relatively high R<sub>on,sp</sub> for medium breakdown voltage (<2kV). Commercially available 1200V MOSFETs are recently released by CREE and a recent publication shows impressive performance [22].

Conventional silicon based MOSFETs are basically characterized by their high speed switching capabilities and high current carrying capacity at low blocking voltages. As the device blocking voltage increases, the on-state resistance goes higher and the current carrying capacity decreases in order to limit the on-state power dissipation. This tradeoff comes from the fact that a high blocking voltage requires a thicker drift region (epilayer). Since there is no conductivity modulation in majority carrier devices, the on-state resistance increases significantly [21].

### 2.3.1.3 SiC JFETs

A SiC JFET is typically a normally-on (depletion mode) device and conducts even though there is no gate voltage applied rather a gate voltage should be applied in order to stop conduction. A normally-on device is not recommended to use in power electronics application since it requires additional protection circuitry to prevent a DC bus short if the gate signals fail. The normally-on features demands a special gate drive design which results in complex design. However, this device looks very promising regarding reliability issues. This is because the device doesn't rely on the quality of gate control dielectrics unlike MOSFET device instead it strongly depend on the pn junction operation. Moreover, JFET exhibits a small capacitance and can thus be operated at high switching speed.

### 2.3.2 Gallium Nitride - High Electron Mobility Transistor (GaN-HEMT)

Currently, GaN-based semiconductor device are already in the market in photonics area. However, due to lack of high quality freestanding GaN substrates in the market it was unable to use the material for power application in the past few years. A well-defined global epitaxial relationship between the epitaxial GaN film and the substrate is the determining factor in order to grow high-quality, single-crystalline GaN film for power application. It was started by introducing foreign substrates such as Si, Sapphire and SiC to develop the epilayers of GaN. From the studies, substrate with Si provides GaN epilayer with lower cost compared to other substrates.

#### 2. Comparison and Selection of Switching Devices

GaN actually has a higher theoretical critical field for breakdown, and would thus seem to be better than SiC. However, the GaN devices have so far shown much lower breakdown voltages than expected, possibly from the lack of free-standing GaN substrates. High injection devices are also not possible in the direct band gap of GaN [22].

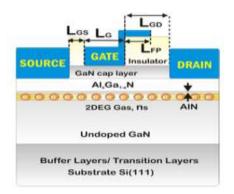

GaN power devices become dominant in the power electronics industry due to their unique and most interesting property known as a 2-dimensional electron gas (2DEG) [19]. 2DEG is a gas of electrons free to move in two dimensions, but tightly confined in the third. This tight confinement leads to quantized energy levels for motion in that direction. Among the three WBG devices, GaN is the only heterostructure material which means it has unequal band gap due to a layer formed by dissimilar crystalline semiconductors. In AlGaN/GaN heterostructures, a large conduction band discontinuity between GaN and AlGaN is formed and the presence of polarization fields allows large 2DEG concentration with high electron mobility values (1200–2000 cm<sup>2</sup>/Vs). Therefore, high breakdown voltage property of GaN-HEMT is realized by optimizing field plate technique and also by low on-state resistance.

A negative bias should be applied to the gate of GaN-HEMT in order to remove the 2DEG because they are intrinsically normally-on devices. Figure 2.6 show the cross section of normally-on GaN HEMT device. Recently, GaN-HEMT devices are getting much attention for high power application due to very low specific on-resistance and high break down properties. Moreover, they can provide high current handling capacity.

Figure 2.6: Cross section of a normally-on GaN HEMT [19]

High speed and low switching loss characteristics of GaN devices make them very attractive for switching power supplies in ultrahigh bandwidth, in megahertz range [19]. Significant changes

#### 2. Comparison and Selection of Switching Devices

have been seen since the evolvement of the first GaN based HEMT switch both in terms of output power capability and voltage capability. Recently, it is able to manufacture a GaN-HEMT switch with 40W/mm output power capability and 10kV Voltage capability [18]. These remarkable performances of GaN-HEMT are achieved by suppressing the drain current collapse and also by increasing the gate-to-drain breakdown voltage through a control of the bulk and surface trap densities.

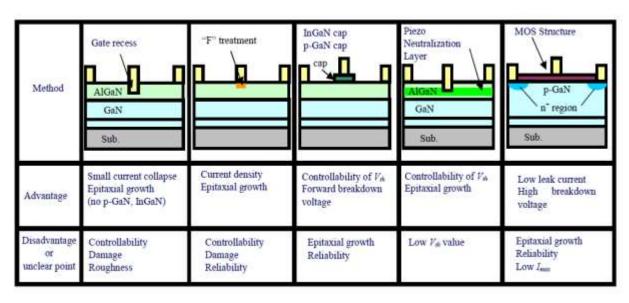

AlGaN/GaN HEMTs are generally promising candidates as switching transistors in power electronics area of application this is due to their high breakdown strength and current density in transistor channel gives a low on-state resistance, R<sub>on</sub> [23] & [24]. However, their inherent normally-on behaviour would exclude them from most power electronics applications. Several approaches have been studied in the past few years to get the best out of the GaN-HEMT to apply for power switching device. Surface-charge-controlled n-GaN-cap structure, the recessed gate and field-modulating plate structure, and the passivation of surface states via silicon nitride or other dielectric layer can be mentioned as major research points [19].

### 2.3.2.1. Enhancement-mode (E-mode) GaN HEMT

The inherent problems associated with normally-on GaN HEMTs limit their application in power converter. Normally-off (or E-mode) GaN HEMTs are preferred for safety reason and fast switching speed [22]. Recent attempts to convert GaN HEMTs into normally-off devices using gate recess or fluorine plasma treatment showed limited applicability for power electronics due to their low threshold voltages  $V_{th} < +1V$  and their voltage swings of approximately 2V. However, a Schottky-type metal on the AlGaN barrier acts as gate for normally-on HEMTs, a P-type doped semiconductor as gate is able to deplete the transistor channel when unbiased, thus yielding a normally-off device [23].

Table 2.3 Different approaches to realize enhancement mode GaN HEMT device [25]

According to [25], it has been already able to develop n-GaN cap structure, called a surfacecharge controlled structure for power amplifier application. Using n-GaN cap layer instead of AlGaN layer is able to prevent instability of frequency dispersion related surface. One good example is, n-GaN cap structure suppresses current collapse which is a key issue for the GaN based devices. Current collapse is the phenomena that on-resistance changes when transistor turns on. From the hypothesis, it has demonstrated that in off state high electric field will occur at the drain side edge of gate when high voltage is applied between source and drain. In this case, electrons are trapped on the surface of this area. These trapped electrons cannot be released easily even if gate voltage becomes turned-on, which results in the increase of onresistance.

The paper, [25], also assessed the performance of n-GaN over the conventional AlGaN cap layer structure through experiment. From the result, embedding the top surface by n-GaN cap layer provides suppression in the current collapse by reducing the concentration of electric field at the gate edge and smooths the surface.

# 3. Single-Phase Bidirectional PFC - Boost Converter Topology Study

In this chapter, the characteristics and performance of different PFC - boost converters topologies are assessed in detail. Overview of smart grid functionality in bidirectional converter is also the main discussion point.

# **3.1 Active Power Factor Converter**

Active power factor converters use power electronics active switches to change the current waveform drawn by the load in order to improve the power factor. Single phase PFC boost converter employs an input capacitor filter in order to limit the amount of switching noise propagation in to AC mains [29]. Based on this research, high power factor and low harmonic distortion can be achieved by operating the converter in CCM with average current mode control (ACMC).

PCF circuits can be broadly classified as passive and active. The basic building blocks of passive PFC are bridge diode and passive elements, such as resistor, inductor and capacitor. Whereas; active PFC uses active switch devices in conjunction with inductors [8]. Government agencies give a big attention towards active PFC circuit in order to improve grid supply capacities [3], [8]. Figure 3.1 show traditional PFC with line rectifying bridge.

Figure 3.1: Traditional PFC with line rectifying bridge

### 3. Single-Phase Bidirectional PFC - Boost Converter Topology Study

According to [3], traditional PFC boost circuit is built from bridge diode, boost inductor, a slow diode and AC active switch. Based on continuity of the input inductor current, active PFC can be further divided into discontinuous conduction mode (DCM) and continuous conduction mode (CCM). Active PFC circuits operating in DCM are simpler than their CCM counterparts and hence their cost is much cheaper. However, low efficiency due to high current stresses and a need for large input EMI filter limit the DCM PFC circuit for low power applications only [30], [31]. For medium and high power CCM PFC is preferable.

Active PFC boost converters operating in CCM can be designed and implemented by using either single stage or two stages approach [32]. The two stage converter comprises front-end PFC stage and DC–DC converter stage. According to [31] and [32], the two stage approach incurs additional PFC power stage and its control circuitry. However, it is the most widely used and cost efficient approach in high power application because of two major factors:

- ✓ PFC controller can provide a unity input power factor by sensing the input voltage waveform and shaping the input current to be in phase with the line voltage [31], [32].

- ✓ Since the voltage at the DC link is fixed, the efficiency of the DC-DC converter stage can be improved [32].

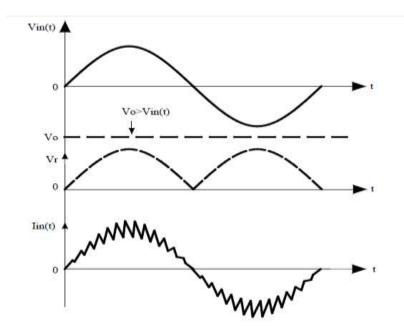

Active PFC boost converter operating in CCM produces an output voltage higher than the input voltage as shown in the figure 3.2 below. Since the converter can operate for the whole cycle of AC main, crossover distortion will not be a question for the input current. Moreover, the boost inductor is connected in series with the input that results in a continuous input current flow in the converter and even the switch cannot stop the input current to flow. Therefore, the input current contains fewer harmonic that leads to a reduced filter size and lower EMI.

Figure 3.2: Current and voltage waveforms of a CCM boost PFC converter [30]

### 3.1.1 Review of two stage approaches

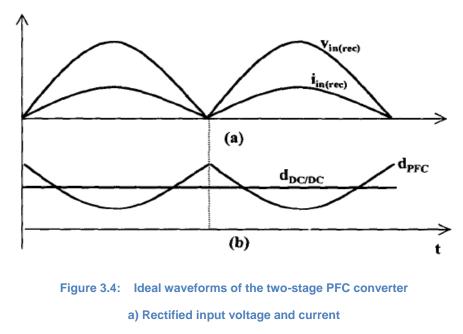

Two stage approach has two independent power stages. CCM boost PFC converter is usually employed as the front - end PFC power stage due to its high power factor, low total harmonic distortion (THD) and high efficiency characteristic [31],[32]. It consists of boost inductor, boost switch and rectifier. The rectifier can be either diode bridge for unidirectional converter or MOSFET switches if bidirectional power flow is required. The PFC controller is used to improve the input power factor. Based on [31], this can be achieved by detecting the waveform of line voltage and forcing the input current to follow the line voltage until there is no phase shift between the rectified current and voltage waveforms as shown below in Figure 3.4 (a).

The second power stage in the two stage approach is the DC-DC converter and its controller. The DC-DC output stage is the isolated output stage that is implemented with at least one switch, which is controlled by an independent controller to tightly regulate the output voltage [31]. In any PFC circuit, there should be an energy storage capacitor to store unbalanced energy. In single stage approach, the energy storage capacitor voltage varies with the load and line voltage because the controller is used to regulate the output voltage not the dc link voltage. However, in two stage approach, the PFC controller controls the dc link voltage and DC-DC controller control the DC output voltage. General structure of a two stage PFC boost converter is shown in the figure 3.3 below.

Figure 3.3: Conceptual structure of two-stage PFC converter

b) Duty cycle of PFC and DC-DC switches [33]

Figure 3.4 (a) show the PFC controller can shape the input current waveform in accordance with the input voltage waveform to enhance the power factor of the converter and to reduce the input current harmonics. On the other hand, Figure 3.4 (b) show that the duty cycle of the front- end

PFC stage varies with time. Whereas, the duty cycle of DC-DC converter stage is almost constant in time because the input and the output voltage of the converter are fixed [32].

# 3.2 Synchronous Rectification (SR)

A synchronous rectification in high performance converter design is an essential block for low voltage and high current applications since significant efficiency and power density improvements can be achieved by replacing schottky diodes with low on-resistance MOSFETs [33]. Even though using SR in switching DC-DC converter provides a lot of advantages, there are also a lot of challenges to implement it correctly especially in boost converter design.

According to [33], most manufacturers were attracted to work on the buck controller. However, the existence of automotive start-stop, together with the widespread of battery-operated devices and telecom systems creates an opportunity for the development of boost based converters with higher efficiency, higher power density and novel protection features which were not available in the previous products. The problem is addressed by using a new generation boost controller ICs which can drive SR MOSFETs.

# 3.2.1 Diode Vs MOSFET

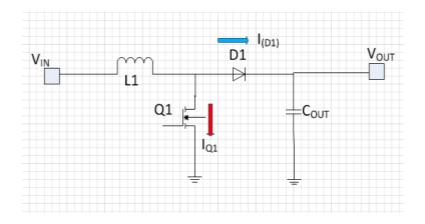

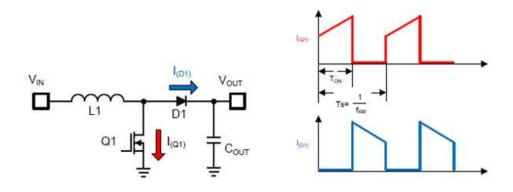

Typical boost converter diagram with diode is show in the figure below. The TI (Texas Instrument) authors show that the power dissipated in the diode D1 is considerably high and given by as:

$P_{Diode} = V_D * I_{Out} * (1 - D)$  Eq [3.1]

Where D is the duty cycle of the boost MOSFET

#### 3. Single-Phase Bidirectional PFC - Boost Converter Topology Study

Figure 3.5: A boost converter with diode rectification

Bell and Lee's stated on their article, [34], that if the magnitude of the input and output voltages are very close, the duty cycle of the boost MOSFET is small. In the meantime, the corresponding (1-D) duty cycle of the diode is large. Since the diode carry large portion of the conducting time, the power loss associated with it becomes very high. The power dissipated in the diode can be approximated as:

$$P_{Diode} = V_D * I_{In} * (1 - D)$$

Eq [3.2]

However, the loss can be significantly minimized by employing MOSFET in place of diode and the Equation 3.2 can be written as:

$$P_{MOSFET} = R_{DS(ON)} * I^2_{In} * (1 - D)$$

Eq [3.3]

As it is clearly noticed from the two Equations given above, the power dissipation on diode is determined by the forward voltage drop  $V_D$  and the input current  $I_{In}$ . However, the power dissipation on SR MOSFET is dependent on on-state resistance of the transistor  $R_{DS(ON)}$  and the input current  $I_{In}$ .

TI designers have built a MOSFET boost converter using new synchronous boost controller IC LM5122. The controller provides integrated gate drivers that directly control the low side boost MOSFET and the floating high side synchronous MOSFET. Moreover, the internal adaptive dead-time circuit avoids shoot-through between the two MOSFETs while optimizing efficiency.

## 3.3 Bidirectional PFC boost Converter topology

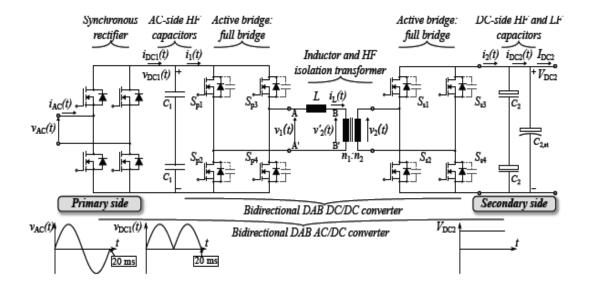

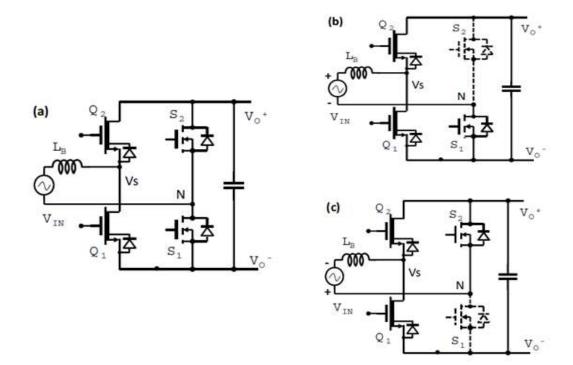

Most of the literatures regarding PFC boost converter are unidirectional [35] - [41]. However, allowing power flow in both directions has got a lot of attention these days. Bidirectional dual active boost (DAB) converter is proposed in [42]. High density bidirectional rectifier for 380V DC distribution system was tested with SiC-JFET switches in the laboratory and showed better performance than the conventional PFC rectifier [45].

According to [42], the single stage converter doesn't require front end PFC circuit and suitable for low power applications. However, the efficiency is less than two stage approach and also its application is limited to low power. Recently, more effort is exerted in order to increase the efficiency of the PFC converter at low line input for universal application using two stage approach [43]. The main objective of this paper is to study single phase bidirectional power converter for smart grid functionality. Specifically this sub chapter deals about the first stage of the two stage approach, front-end PFC boost converter, which allows bidirectional power flow between the AC mains and the DC link.

Figure 3.6: Circuit schematics of the bidirectional, isolated AC-DC converter topology [42]

The bidirectional power flow in PFC boost converter stage is controlled by the PFC controller. The control system monitors the DC link voltage and stabilizes the voltage by changing the

#### 3. Single-Phase Bidirectional PFC - Boost Converter Topology Study

source current. When the power flows from the grid to the DC side, which is in rectifier mode, the control system maintains the source current waveform and also be in phase with the grid line voltage. When the converter works in inverter mode, power flow from the DC link side to the grid, the source current is 180 degree out of phase from the line voltage. Therefore, the input power factor becomes approximately unity [44].

Since the current does not flow through the body diode of power MOSFET then the power dissipation due to reverse recovery of the active switch is greatly reduced. An interleaved totem-pole boost bridgeless rectifier is proposed with reduced reverse recovery for improved PFC [43], [46]. According to [43], the totem-pole boost bridgeless PFC rectifier eliminates common mode (CM) interference problem because the output is clamped to the input by slow diodes during each half cycle. Moreover, it has low conduction losses and hence high efficiency and low revers recovery process. In addition, totem pole topology has a potential capacity for bidirectional power conversion. However, the conduction of MOSFET intrinsic diode makes it not suitable for continuous current mode (CCM) operation. To suppress the reverse recovery of the diode, many methods have been proposed.

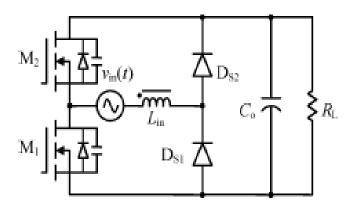

Figure 3.7: Totem-pole boost bridgeless PFC rectifier [43]

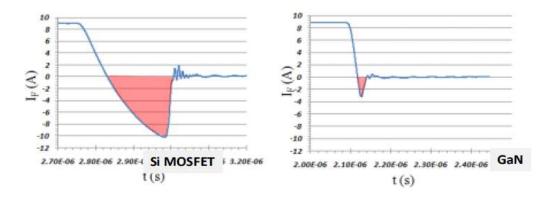

The totem- pole topology, shown in Figure 3.7, demands very low reverse recovery charge (Qrr) for the MOSFET body diodes which is not possible with high voltage silicon (Si) MOSFETs [43], [44]. The advent of gallium nitride (GaN) high electron mobility transistor (HEMT), in 1993, alleviates the problems associated with body diodes in SiC MOSFET [46]. In the future, the need for energy saving in electric conversion will be satisfied by currently emerging GaN HEMTs. The new 600V-class low Qrr transistors make this highly promising circuit a practical reality.

# 3.3.1 GaN totem - pole PFC topology

Transphorm Inc. introduced the first qualified 600V GaN HEMTs with low cost Si substrate [46], [47]. These days, the power electronics market is filled with these low on - resistance device, typically 15 milliohm, and low reverse recovery charge Qrr of 54 nC which is 20 times lower than state-of-the art Si counterpart as shown in Figure 3.8. Moreover, high power density and capacity for higher frequency operation make GaN very promising device in the power electronics industry.

Figure 3.8: Reverse recovery charge test result for Si MOSFET and GaN HEMT with similar onresistance, showing a 20x reduction of Qrr for GaN [48]

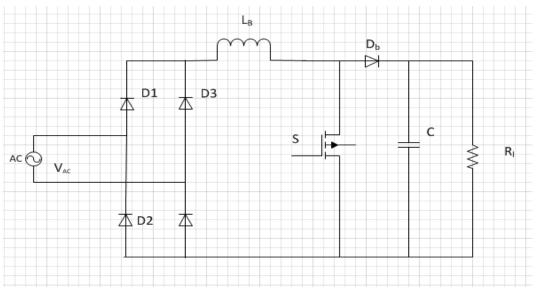

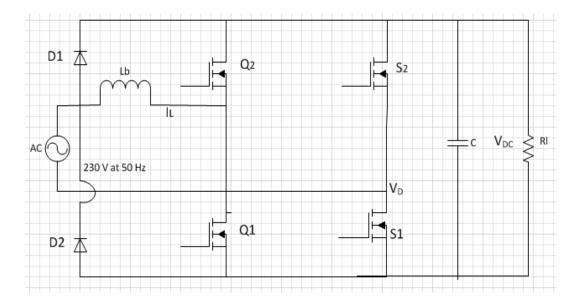

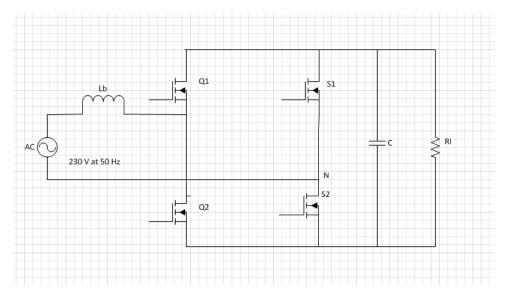

The totem - pole topology, shown in figure 3.9 (a), consists of a pair of GaN HEMT switches ( $Q_1$  and  $Q_2$ ) and another pair of MOSFET switches ( $S_1$  and  $S_2$ ). The GaN HEMT switches operate at very high pulse width modulation (PWM) frequency whereas the MOSFETs are operating at very low frequency, typically 50 Hz or 60 HZ. The switches,  $S_1$  and  $S_2$ , serve as synchrounous rectifier by replacing the power diodes in bridgeless totem pole topology so that better efficiency can be achived. This is because the MOSFET switches provide constant and very low on resistance ( $R_{DS(on)}$ ) when conducting as compared to power diodes [48].

Figure 3.9: GaN totem-pole (a) Simplified schematics and illustration (b) positive AC cycle (c) negative AC cycle [48]

The operation priniple of totem - pole PFC for two half cycles is illustarted in Figure 3.9 (b) and (c). In the positive half cycle, the current flows through  $S_1$  which connects the AC line to the output ground whereas  $S_2$  is kept in the off position. In the GaN HEMT switch pairs,  $Q_1$  is the active boost switch while  $Q_2$  freewheels the inductor current and discharges inductor energy to the output side. In the negative ac cycle,  $Q_2$  serves as active switch and  $Q_1$  freewheels the inductor current. In the meantime,  $S_1$  is in the off state and  $S_2$  forces the ac neutral line tied to the positive terminal of the dc output.

In either AC polarity, one of the GaN HEMT transistor acts as a master switch and the other as a slave switch. The master switch allows the current to charge the boost inductor whereas the slave switch releases the stored energy in the inductor to the DC output [48]. The role of the two GaN transistors interchange in every half cycle so that each transistor has got a chance to be a master in one cycle and a slave on the other half. When both MOSFET switches are either fully or partially turned on, it provides a path for current to shoot through from V<sub>in</sub> to ground. To avoid this situation, a dead-time is added in between two switching events during which both transistors are momentarily off.

### 3. Single-Phase Bidirectional PFC - Boost Converter Topology Study

During dead-time, the body diode of the slave transistor has to function as a free-wheeling diode for the inductor current to flow, therefore CCM operation can be achieved from the converter.

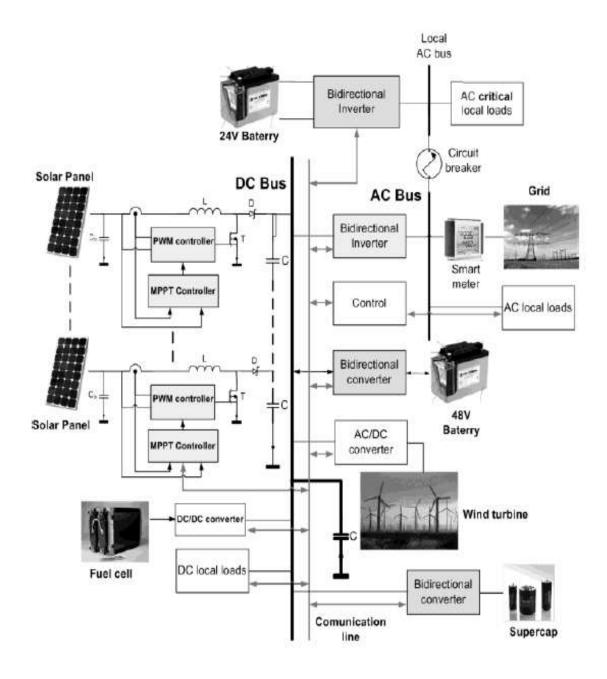

# 3.4 Overview of smart grid functionality on bidirectional converters

It is very important to study the meaning and behavior of smart grid since the modern PFC converters can be connected and work in synchronized manner with smart grid. What is smart grid? According to U.S. Department of Energy's modern green initiative, a smart grid is defined as a system that integrates advanced sensing technology, control methods and integrated communication into the current electricity grid system [49]. At the transmission level, the grid is intelligent and efficient. At the distribution and customer level, there are opportunities for automation, advanced data collection, and intelligent appliance control that provide opportunities for energy efficiency and better integration of distributed generation including renewables to reduce carbon emission.

Smart grid encompasses the distribution network with an interface to the transmission system. This includes distributed energy resources, grid interfaces, distribution circuits, customer loads and internet protocol (IP) addressable load control architecture that represent the decision support system of the smart grid. The distributed generation sources can be made by interconnecting solar cells, wind turbines, fuel cells and storage technologies.

Bidirectional power converter will be a key enabler for cost effective use of electricity storage that also can feed power back to the grid.

Figure 3.10: Typical smart grid [50]

A smart grid is a digital network that controls both distributed energy resources and interconnected load in order to operate the grid efficiently as shown in Figure 3.10. It can improve power distribution efficiency based on the design of the grid and customer usage power to flow in both directions.

#### 3. Single-Phase Bidirectional PFC - Boost Converter Topology Study