# Asynchronous Design for Low-Power

Sonal Khosla

Master of Telematics - Communication Networks and Networked Services (2 Submission date: August 2015 Supervisor: Rolv Bræk, ITEM

Norwegian University of Science and Technology Department of Telematics

Asynchronous Design for Low-Power Sonal Khosla

Problem description:

Asynchronous logic has been shown to have many theoretical advantages, ranging from lower power consumption to faster operations. However, there are many practical hazards that need to be overcome – not least of which is the lack of tool support, which has discouraged extensive use in the industry. The overall goal is for the student to investigate the usability and/or power saving potential for selected circuits and if needed, implement macros for blocks with high power saving potential.

The student would start by designing asynchronous logic for reading from FLASH memory. Some initial goals are to:

- 1. Select the correct backend tool for synthesis.

- 2. Investigate issues for an asynchronous synthesis tool to be integrated into the Nordic Semiconductor's tool-chain.

- 3. Synthesis, timing analysis, netlist simulations.

If time permits, further potential goals could be:

- 1. Power analysis.

- 2. Layout, placement, route, macro-ify.

- 3. Investigate asynchronous design for writing to FLASH.

The following skills/knowledge would be helpful (in decreasing importance):

- 1. A very good grasp of Verilog/System-Verilog and digital design principles.

- 2. An understanding of asynchronous design techniques.

- 3. Some basic understanding of the process from RTL to ASIC.

- 4. Power analysis / power simulations.

| Responsible professor: | Rolv Bræk, NTNU                                      |

|------------------------|------------------------------------------------------|

| Supervisor:            | Omer Qadir & Arne W. Venås, Nordic Semiconductor ASA |

Title: Student:

# Abstract

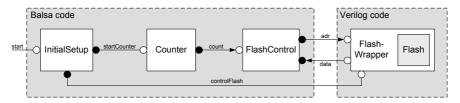

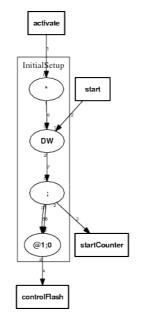

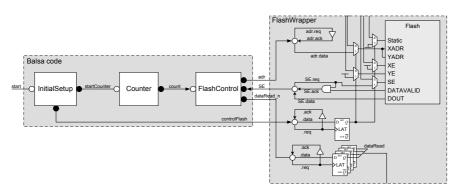

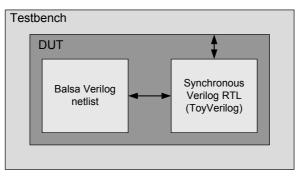

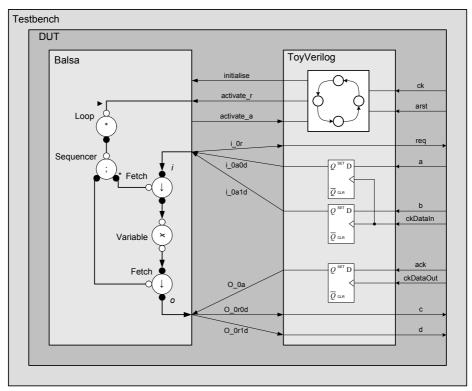

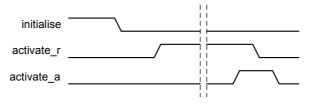

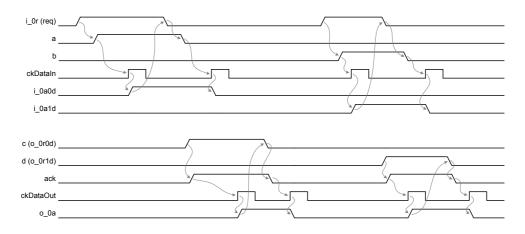

The last two decades have seen a sudden surge of renewing interest in asynchronous (or "clock-less") digital circuit design, along with its introduction into various consumer products in the industry. One major bottleneck to the further advancement of asynchronous design is the inability to integrate it with standard synchronous design. Furthermore, the ease of integration is primarily dictated by the effort spent on timing validation and analyses. It is easier to integrate an asynchronous design into a synchronous tool chain, if no or less timing analyses is required for the asynchronous part. This thesis 1) investigates several asynchronous tools to find an asynchronous tool that nullifies or minimises the timing validation to implement an asynchronous design; 2) uses "Balsa", the selected tool, to implement an asynchronous flash readout; 3) analyzes the delay insensitive nature of Balsa; and 4) integrates a simple asynchronous buffer design in Balsa together with a synchronous RTL design, and runs the combined design through Nordic Semiconductor's synchronous tool chain.

An asynchronous flash readout takes control of the flash and performs readouts from the flash. For this purpose, a Verilog netlist for both single rail and dual rail data encoding styles was generated. An analyses of the delay insensitive (DI) nature of Balsa was performed using a simple buffer design. It was found that for a Balsa generated netlist to be Delay Insensitive (DI), all the combinatorial loops must be controlled by handshaking signals and all components must be Quassi Delay Insensitive (QDI).

An attempt to integrate the Balsa Verilog netlist with Nordic Semiconductor's tool chain was made. The correct functionality of the combined design was verified before and after it was synthesized by Design Compiler (DC). One important feature is that after the synthesis of the combined design, no timing analyses is required to ensure the working of the asynchronous part. A manual inspection of the combined netlist revealed no changes in the functional behaviour for the Balsa part. Therefore, the integration of an asynchronous design written in the Balsa language is possible with Nordic Semiconductor's tool chain.

# Preface

In the last decades, the market has been flooded with high performing, power efficient devices. 'Low power devices' has been one of the chief priorities for many progressive companies including Nordic Semiconductor. Research has shown that asynchronous design practices can achieve significant power savings, thus making asynchronous design a suitable choice for low power implementations. Currently, the industry for digital circuit design is dominated by synchronous design practices which are bound to stay for many years to come. Hence, for the successful adoption of asynchronous design practices, it is essential to be able to integrate asynchronous design with a standard synchronous design. This thesis aims at doing so. It integrates a simple asynchronous design in Balsa together with a synchronous RTL design, and runs the combined design through Nordic Semiconductor's synchronous tool chain.

This thesis has been submitted for the fulfillment of Masters in Telematics being pursued at the Norwegian University of Science an Technology (NTNU). It was undertaken over a course of 21 weeks. The assignment was given by Nordic Semiconductor and was performed under the supervision of Omer Qadir and Arne Wanvik Venås. As a part of masters degree, I did a specialization project on 'Asynchronous Design through Synchronous Tool Flow' preceding this master thesis in 2014. This research provided some really interesting results. We ran into some timing issues that could not be solved by this approach. Hence, it was decided to carry forward the research into asynchronous design by using another approach i.e. by using an asynchronous tool to implement an asynchronous design and then integrate it into a synchronous tool flow.

In the end, I would like to acknowledge the efforts of all those who have contributed towards the successful completion of this thesis. I would like to express my gratitude towards my co-supervisor, Arne Wanvik Venås, who has been a perennial source of guidance and motivation. His contribution has been significant in the various phases of this thesis, such as: design implementation, library generation, integration, etc. I would also like to thank my superviser, Omer Qadir, for all his endeavours to achieve the final goal. His contribution has been significant during the initial phase of the research into various asynchronous tools to find the correct asynchronous tool, and in the delay insensitivity analysis of Balsa. Moreover, he has played an important role towards ensuring the academic perspective of this thesis. I would also like to thank Frank Burns and Danil Sokolov at the University of Newcastle, Luciano Lavango at Politecnico di Torino, and the Balsa support at the University of Manchester for their quick and enriching responses during the initial research phase. My extended thanks to the Department of Telematics at the Norwegian University of Science and Technology (NTNU) for providing me the opportunity to pursue this thesis.

# Contents

| $\mathbf{L}^{\mathrm{i}}$ | ist of | Figur   | es                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\mathbf{i}\mathbf{x}$ |

|---------------------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| $\mathbf{L}^{\mathbf{i}}$ | ist of | Table   | s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | xiii                   |

| $\mathbf{L}^{\mathbf{i}}$ | ist of | Acror   | ıyms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\mathbf{x}\mathbf{v}$ |

| 1                         | Intr   | oduct   | ion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                      |

|                           | 1.1    | Motiv   | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                      |

|                           | 1.2    | Signifi | icance of the thesis $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                      |

|                           | 1.3    | Repor   | t structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2                      |

| <b>2</b>                  | Bac    | kgrou   | nd and Theory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>5</b>               |

|                           | 2.1    | Synch   | ronous and asynchronous design $\hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots \hfill \ldots$ | 5                      |

|                           | 2.2    | Benefi  | its and challenges of asynchronous design $\hfill \ldots \hfill \ldots \hfi$      | 6                      |

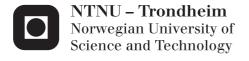

|                           | 2.3    | Fanin   | and fanout paths $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                      |

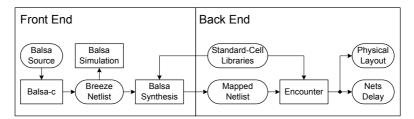

|                           | 2.4    | Fronte  | end and backend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8                      |

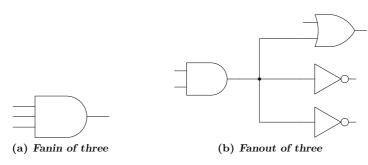

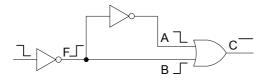

|                           | 2.5    |         | r C element $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8                      |

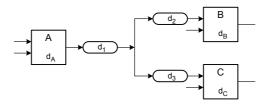

|                           | 2.6    |         | ata path and control path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9                      |

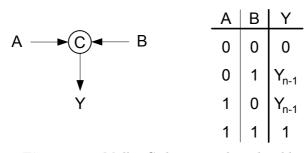

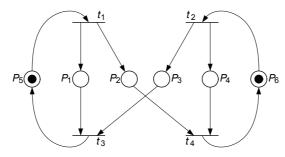

|                           | 2.7    | Hands   | shaking protocols for a<br>synchronous control communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9                      |

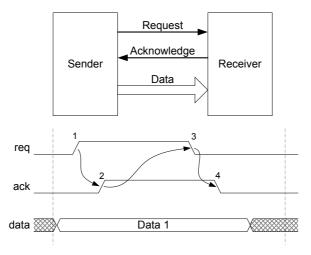

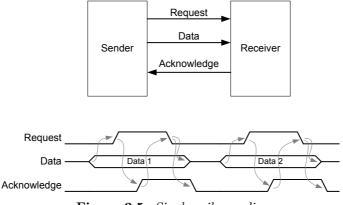

|                           |        | 2.7.1   | Two-phase handshaking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9                      |

|                           |        | 2.7.2   | Four-phase handshaking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9                      |

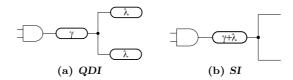

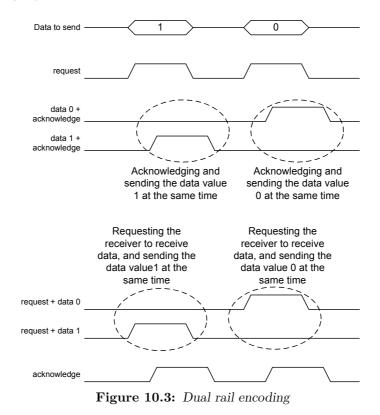

|                           | 2.8    |         | encoding protocols for asynchronous datapath                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                     |

|                           |        | 2.8.1   | Single rail encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11                     |

|                           |        | 2.8.2   | Dual rail encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12                     |

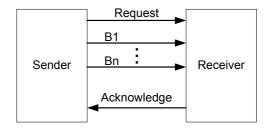

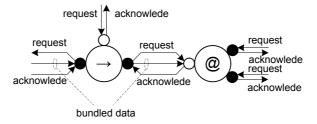

|                           |        | 2.8.3   | Bundled data encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12                     |

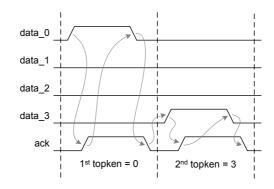

|                           |        | 2.8.4   | 1-of-N data encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13                     |

|                           | 2.9    | v       | models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 14                     |