# Challenges Adapting CUDA PIC Codes to multiple GPUs

**Olav Emil Eiksund**

Master of Science in Computer ScienceSubmission date:July 2015Supervisor:Anne Cathrine Elster, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# Challenges Adapting CUDA PIC codes to multiple GPUs

Olav Emil Eiksund

July 18, 2015

## Problem description

The Particle-In-Cell method is a particle simulation that includes a PDE solver, with applications in modelling particle acceleration and plasma waves.

This project includes adapting a naive CUDA-implementation of Particle-In-Cell codes for multiple GPUs. Previous work has shown that 3D Particle-In-Cell codes require several orders of magnitude more particles than a 2D version, for which the limited memory of a GPU is a bottleneck. The project includes investigating how additional GPUs may be used to increase possible problem size, and how this will affect performance.

#### Abstract

A Particle-In-Cell code is a common particle simulation method often used to simulate the behaviour of plasma. In this work, a parallel PIC code is developed in CUDA, with a focus on how to adapt the method for multiple GPUs. An electrostatic three dimensional PIC code is developed, with an FFT-based solver using the cuFFT library.

Several issues related to parallelizing the PIC code are discussed, along with the performance on one and two GPUs compared to the CPU version we developed based on OpenMP and FFTW as a benchmark. For most problem sizes, the application is found to be memory bound, with the speed of the memory interface playing a larger role than the double precision performance. Alternatives to some of the naive solutions are discussed, with suggestions for how the simulation could be implemented for a shared memory computer. Benchmarks were performed on several GPU platforms including Nvidia Tesla K20 and GTX 980, and the challenges of getting the implementations to simulate plasma oscillations are discussed.

#### Sammendrag

Particle-In-Cell koder er en kjent type partikkelsimulering brukt til å simulere plasmaer. I dette arbeidet utarbeides en parallell PIC kode i CUDA, som videre tilpasses kjøring på flere GPUer. PIC koden er tredimensjonal og elektrostatisk, og benytter en FFT-basert løser implementert gjennom cuFFT-biblioteket.

Ytelsen på en og to GPUer blir sammelignet med ytelsen til en CPU-variant basert på OpenMP og FFTW. Programmet viser seg å være bundet av minneaksesser, hvor hastigheten på minnet dominerer double precision regnehastighet i ytelsespåvirkning. Alternativer for noen av de mindre heldige løsningene blir diskutert, og et forslag til en shared memory-implementasjon blir nevnt. Ytelsestester ble kjørt på Nvidias Tesla K20 og GTX 980 GPU+platformer, og utfordringer rundt det å få implementasjonen til å simulare plasmasvingninger blir diskutert

### Acknowledgements

I would like to thank my advisor Anne C. Elster for providing me with this project, and for introducing me to the exciting field of GPGPU and HPC.

My advisor and I would like to thank NVIDIA for their support of the IDI/NTNU HPC-Lab through their NVIDIA GPU Research and Teaching Centers at NTNU, and NTNU for the generous equipment grants to HPC-Lab.

Many thanks to Trygve R. Sørgård for extremely valuable feedback, including proofreading and providing a deeper understading of the physics involved, and many interesting conversations.

My fellow students at the NTNU HPC-lab have provided support and new insight, and many educating experiences. I would also like to thank the students and teachers from NTNU in general, and Computer Science in particular for providing a stimulating environment and many memorable experiences throughout my time at NTNU.

I would also like to thank my family and friends who have guided me down the path that has led me here, and particularly my parents Anne Betty and Gudmund for encouraging my studies.

My time time at NTNU would not be the same without my girlfriend Kathrine, whom I would like to thank for always supporting me and keeping me motivated during difficult times.

# Contents

| 1        | Introduction                                        |                            | 1                                                         |          |

|----------|-----------------------------------------------------|----------------------------|-----------------------------------------------------------|----------|

|          | 1.1                                                 | Outlir                     | ne                                                        | 3        |

| <b>2</b> | Bac                                                 | kgrou                      | nd Theory                                                 | <b>5</b> |

|          | 2.1                                                 | 2.1 Particle-In-Cell codes |                                                           | 5        |

|          |                                                     | 2.1.1                      | Particles and Cells                                       | 6        |

|          |                                                     | 2.1.2                      | Charge density contribution from particles                | 6        |

|          |                                                     | 2.1.3                      | Solving Poisson's equation for the electric potential     | 7        |

|          |                                                     | 2.1.4                      | Deriving the electric field from the potential            | 8        |

|          |                                                     | 2.1.5                      | Updating particle positions and velocities                | 8        |

|          | 2.2                                                 | The F                      | ast Fourier Transform solver                              | 9        |

|          |                                                     | 2.2.1                      | Solving PDEs with the Fourier Transform                   | 10       |

|          |                                                     | 2.2.2                      | The FFT algorithm                                         | 11       |

|          | 2.3 Parallel computing and GPGPU                    |                            | 11                                                        |          |

|          | 2.3.1 History and motivation for parallel computing |                            | 12                                                        |          |

|          |                                                     | 2.3.2                      | General Purpose computing on Graphics Processing Units    | 13       |

|          |                                                     | 2.3.3                      | Parallel performance measures and potential speedup       | 14       |

|          |                                                     | 2.3.4                      | Architectures                                             | 15       |

|          | 2.4 CUDA - Compute Unified Device Architecture      |                            | 17                                                        |          |

|          |                                                     | 2.4.1                      | The CUDA Programming Model                                | 17       |

|          |                                                     | 2.4.2                      | Performance factors                                       | 20       |

|          |                                                     | 2.4.3                      | Alternative CUDA interfaces                               | 21       |

|          | 2.5                                                 | cuFF.                      | $\Gamma$ - the NVIDIA CUDA Fast Fourier Transform library | 22       |

|          |                                                     | 2.5.1                      | cuFFTXt - Multi-GPU support in cuFFT                      | 22       |

|          | 2.6                                                 | Relate                     | ed work                                                   | 22       |

| 3 | Imp                        | lementation                                     | <b>25</b> |  |  |  |

|---|----------------------------|-------------------------------------------------|-----------|--|--|--|

|   | 3.1                        | Goals for the implementation                    | 25        |  |  |  |

|   | 3.2                        | Simulation overview                             | 27        |  |  |  |

|   |                            | 3.2.1 Setup                                     | 27        |  |  |  |

|   |                            | 3.2.2 Simulation loop                           | 28        |  |  |  |

|   |                            | 3.2.3 Cleanup                                   | 31        |  |  |  |

|   | 3.3 Parallelization issues |                                                 |           |  |  |  |

|   |                            | 3.3.1 Atomic operations                         | 31        |  |  |  |

|   |                            | 3.3.2 Overlapping memory transfers with kernels | 31        |  |  |  |

|   |                            | 3.3.3 cuFFTXt limitations                       | 32        |  |  |  |

|   |                            | 3.3.4 Particle migration                        | 32        |  |  |  |

|   | 3.4 Particle tracing       |                                                 |           |  |  |  |

|   |                            | 3.4.1 Tracer implementation                     | 33        |  |  |  |

|   |                            | 3.4.2 Visualization script                      | 34        |  |  |  |

|   | 3.5                        | The CPU benchmark comparison                    | 34        |  |  |  |

|   |                            | 3.5.1 OpenMP                                    | 34        |  |  |  |

|   |                            | 3.5.2 FFTW                                      | 35        |  |  |  |

| 4 | Res                        | ults and discussion                             | 37        |  |  |  |

|   | 4.1                        | Hardware                                        | 37        |  |  |  |

|   | 4.2                        | Goals                                           | 38        |  |  |  |

|   | 4.3                        | Profiling                                       | 38        |  |  |  |

|   | -                          | 4.3.1 Single GPU                                | 39        |  |  |  |

|   |                            | 4.3.2 Two GPUs                                  | 40        |  |  |  |

|   |                            | 4.3.3 CPU                                       | 42        |  |  |  |

|   | 4.4                        | Simulation performance                          | 43        |  |  |  |

|   |                            | 4.4.1 Particle count                            | 43        |  |  |  |

|   |                            | 4.4.2 Grid z dimension                          | 45        |  |  |  |

|   |                            | 4.4.3 Frame count for 1000 iterations           | 46        |  |  |  |

|   | 4.5                        | Stability testing                               | 47        |  |  |  |

|   |                            | 4.5.1 Plasma oscillations                       | 47        |  |  |  |

|   |                            | 4.5.2 Two-stream instabilities                  | 50        |  |  |  |

|   | 4.6                        | Atomic operations                               | 51        |  |  |  |

|   | 4.7                        | Particle exchange                               | 52        |  |  |  |

|   | 4.8                        | Particle partitioning and load balancing        | 53        |  |  |  |

|   | 4.9                        | Variant                                         | 54        |  |  |  |

| 5 | Cor                        | clusion                                         | 57        |  |  |  |

| 9 | 5.1                        | Suggestions for future work                     | 58        |  |  |  |

|   | J.T                        |                                                 | 00        |  |  |  |

| Bibl | iograj | phy |

|------|--------|-----|

|------|--------|-----|

| Α | CUI | DA and cuFFT examples | 63 |

|---|-----|-----------------------|----|

|   | A.1 | CUDA example          | 64 |

|   | A.2 | cuFFT example         | 66 |

$\mathbf{59}$

# List of Figures

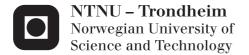

| 2.1 | Trilinear interpolation                        | 7  |

|-----|------------------------------------------------|----|

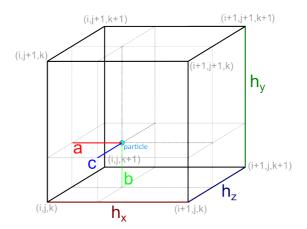

| 2.2 | Conceptual illustration of a CUDA architecture | 18 |

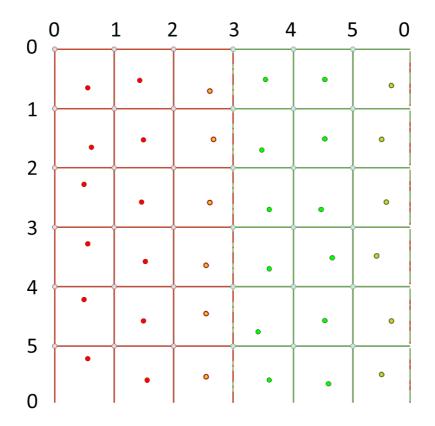

| 3.1 | Illustration of boundary storage               | 30 |

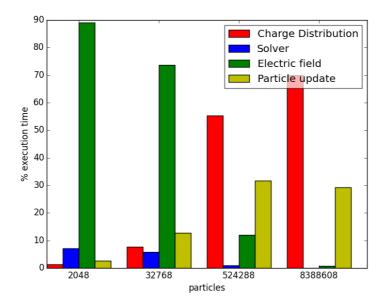

| 4.1 | Plot of profiling results, one GPU             | 39 |

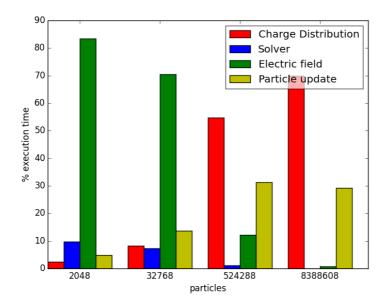

| 4.2 | Plot of profiling results, two GPUs            | 41 |

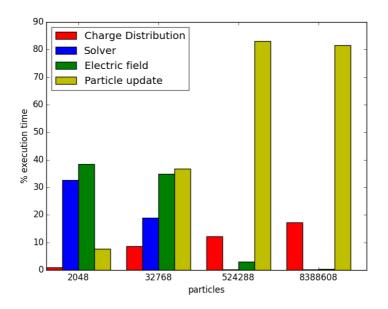

| 4.3 | Plot of profiling results, CPU                 | 42 |

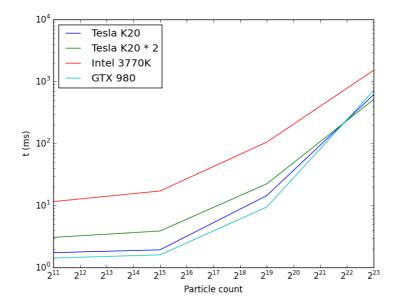

| 4.4 | Plot of performance results, particles         | 44 |

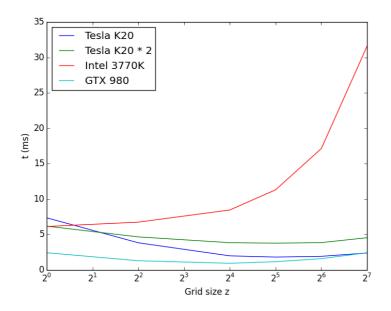

| 4.5 | Plot of performance results, grid size         | 45 |

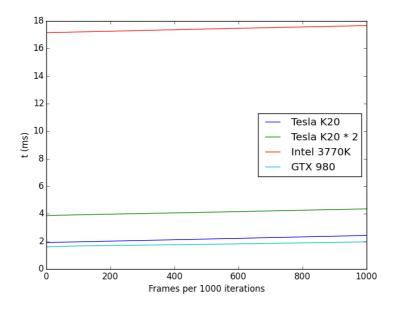

| 4.6 | Plot of performance results, frame count       | 46 |

| 4.7 | Illustration of plasma oscillation             | 47 |

| 4.8 | Illustration of oscillation breakdown          | 48 |

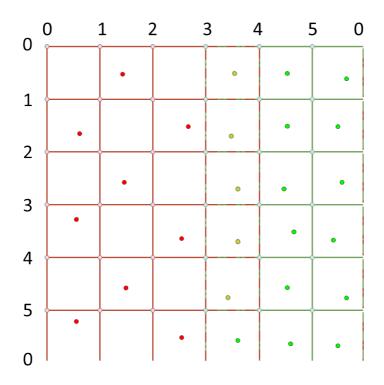

| 4.9 | Illustration of particle partitioning          | 56 |

# Chapter 1

# Introduction

Particle-in-Cell (PIC) method is a popular method that has been in use in plasma simulations since the mid 1950s. The names stems from modelling each particle (or in plasma simulations letting a "superparticle" represent a bunch of charges) in a discrete "cell". Applications include charged toner particles in a copier, charged particles in aurora borealis (assuming also an electromagnetic field is added, and simulating beam dynamics in particle accelerators. While the scope and size of the simulations have increased over the years, the algorithm is largely the same. It is considered easy to grasp, with the electrostatic version based around solving a single partial differential equation (PDE), and otherwise updating particles using classical mechanics. Advances have been made, either focusing on supporting additional physical phenomena, reducing numerical error, or increasing performance and scope[1].

In electrostatic Particle-Mesh codes, which we will cover in this thesis, the contribution of each of the particles' charges in a given cell to the cell's grid points is calculated at a given time based on the particles' location. The resulting charge density distribution is then used to calculate the electric field based on the PDE resulting from Maxwell's equations. The particles are then "pushed" by the field according to Newton's law of motion.

Until the past few decades 3D simulations were considered restricted to supercomputers, being too time- or storage intensive. As the algorithm lends itself well to parallel computing, it has seen many adaptations to various parallel architectures.

Since the early 2000s parallel processing have entered mainstream computing, with the majority of PCs using multicore processors, cell phones and tablets running on multicore processors. Among the more interesting recent advances is the use of the originally entertainment-oriented graphics processing unit (GPU) in high performance computing, and as a component of supercomputers. While they started out as graphics accelerators for 3D games and modelling, the transition from specialized hardware through programmable shader pipelines to general purpose manycore processors have led to their adoption as a parallel computing accelerator of sorts. At a relatively low cost GPUs provide access to a large number of threads with a focus on high throughput.

For this project the goal is to implement a GPU-accelerated Particle-In-Cell code, extending the algorithm and 2D codes developed by my advisor A. Elster [2] to three dimensions. Her code was later adapted for a distributed system using MPI, and for a combination of MPI and OpenMP [3, 4]. The same code has served as the backbone for this project, and although written from scratch in CUDA, the underlying algorithm is the same.

Nvidia's CUDA platform and the CUDA C/C++ language is used for development, and the cuFFT library, which is part of the CUDA Toolkit, is used to implement a PDE solver. In order to achieve a stable simulation, a certain problem size is required, with the number of particles and cells increasing by several orders of magnitude for 3D compared to 2D. Because of the limited memory size available to GPUs, containing the problem might be difficult, and a secondary goal is therefore to implement support for multiple GPUs.

Part of the work done during this project is the extension from two to three dimensions, and in line with comments made by Meyer in [3], an attempt has been made to make the code readable and modular. It is hoped this will make it easier for others to understand, extend and improve upon the work.

The real challenge of this work has been to adapt the code for execution across multiple GPUs. This includes using the cuFFTXt library when multiple GPUs are present, handling boundary conditions and particle migrations.

In order to determine bottlenecks and potential for improvements, some profiling and performance tests have been performed for different configurations. The implementation was tested on a single NVIDIA Tesla K20, an NIV-DIA GTX 980, and a system with two NVIDIA Tesla K20s. In addition, an OpenMP+FFTW variant was implemented for CPU as comparison. The major bottleneck has been found to be atomic operations, with memory performance as an important factor. Based on this, several ideas for improvement are suggested, with a focus on how to handle large numbers of particles.

Several attempts have also been made to achieve a stable plasma oscillation, with limited success. Oscillations break down after a variable number of oscillations, and further testing with parameters that satisfy constraints is encouraged. Ideas for how to do this, is also included.

# 1.1 Outline

The contents of the rest of this thesis is outlined as follows:

**Chapter two** will give a brief introduction to Particle-in-Cell codes, deriving the general algorithm from the physics equations. The FFT as a PDE solver is given a brief treatment, and the history behind parallel computing and GPGPU is summarized. Some parallel performance measures and parallel architecture classifications are described. The CUDA GPGPU environment and its FFT library cuFFT are presented, describing the programming model and some performance factors. Finally some forays into parallel PIC codes are mentioned.

**Chapter three** details the new OpenMP +FFTW and CUDA-based GPU implementations, describing the development goals, overview of the simulation, and various changes made from previous work. Some development choices regarding parallelization issues are presented. Finally the particle tracing and CPU comparison are described.

**Chapter four** presents tests and benchmarks used to evaluate the implementation, and briefly discusses the results. Potential improvements and solutions for some issues are be presented.

**Chapter six** contains our conclusions, and provides several pointers for future work.

# Chapter 2

# **Background Theory**

This chapter will provide some background information on the Particle-In-Cell method of particle simulation, including how to derive the algorithm from the physical equations. The Fast Fourier transform will also be given a brief introduction, showing how it is used as a PDE solver.

A section is devoted to the history of parallel computing, and GPGPU in particular, and different parallel architectures and ways to measure parallel speedup will be described. Nvidia's CUDA library for general purpose computing on graphics processing units (GPGPU) will be introduced, explaining the programming model and some ways to achieve good performance. The CUDA FFT library cuFFT will be given a brief introduction as well. Finally a brief recap of the history of PIC codes, and some forays into parallelizing them will be mentioned.

### 2.1 Particle-In-Cell codes

The name "Particle-In-Cell" is said to originate with a research group at Los Alamos in the 1950s, from "investigations into the fluid nature of matter at high densities and extreme temperatures" [5, p314]. Since then the term has come to refer to particle simulations involving charged particles moving within some discrete grid ("cells"). Typical applications for PIC codes have been the study of plasma, originally as a way to visualize what could not be observed, and later to predict the actual behaviour of plasma, for example in beam dynamics.

The code examined in this work is known as an electrostatic Particle-In-Cell

code. The general algorithm is based on Dr. Anne C. Elster's doctoral thesis [2], although extended to three dimensions. See section 2.6 for examples of other works published on PIC codes.

The idea behind PIC codes is that the collection of charged particles create a charge density distribution  $\rho$  that sets up an electric field. Charged particles in an electric field are affected by an electric force, causing them to move around, thereby altering the field. The PIC simulation repeats this process for some small time step  $\Delta t$  and traces the particles' movements over time as output. The physics and mathematics behind the steps will be explained in more detail below, but first the particle and field models are examined.

#### 2.1.1 Particles and Cells

The particles are represented as point charges with mass and velocity. While some PIC codes model collisions between particles(see [6]), a common approach is to assume particles with no volume, and the simulation concerned with the general behaviour of the plasma constituted by the particles rather than that of the individual particles. To achieve realistic values for the number of particles, total mass, and charge of the plasma without sacrificing performance, the particle objects of the simulation will often be a so-called "super-particle" with its charge and mass being some multiple of the particle type it models.

The cells in the name refers to the discretized field, represented in three dimensions by a grid of size  $N_x \cdot N_y \cdot N_z$ . This grid samples the charge density, electric potential and electric field at all its vertices, with greater accuracy for increasing N.

#### 2.1.2 Charge density contribution from particles

All particles contribute charge to their neighbouring grid vertices, in proportion to the distance between them. For a three dimensional simulation trilinear interpolation is used, weighting the contribution according as seen in figure 2.1. The sum of a particle's contributions thus equal the particle's charge, conserving the total charge of the system. As an example the contribution of a particle with charge  $\rho_p$  to a neighbouring vertex  $\rho_{i+1,j,k}$  is shown in equation 2.1.

$$\rho_{i+1,j,k} = \frac{\rho_p}{(h_x - a) \cdot b \cdot c} \tag{2.1}$$

h here represents the size of the cell, with  $h_x$  being its length along the x axis, found by dividing the length by the number of grid vertices. a, b and c

Figure 2.1: Trilinear interpolation. A particle (light blue) positioned at (a, b, c) within a cell. Grid vertices are indicated in grey coordinates.

describes the particle's position within the cell. a is calculated by subtracting the position of the cell wall from the particle's position.

$$h_x = L_x / N_x a \qquad \qquad = p_x - i \cdot h_x \tag{2.2}$$

#### 2.1.3 Solving Poisson's equation for the electric potential

Poisson's equation  $\nabla^2 u = f$  and the special case of Laplace's equation  $\nabla^2 u = 0$  are arguably the most important elliptic partial differential equations for practical applications [7, p910]. They appear in fluid dynamics, astronomy, electromagnetism and electrostatics, mechanical engineering, and potential fields in general.

Equation 2.3 shows Poisson's equation for electrostatics, and relates the charge density  $\rho$  of the field to the electric potential  $\Phi$ . For the derivation of the equation see [2, s3.2.1].

$$\nabla^2 \Phi_{x,y,z} = -\frac{\rho_{x,y,z}}{\epsilon_0} \tag{2.3}$$

To solve the equation for the potential  $\Phi$  some numerical solver must be chosen. Under the assumption of periodic boundary conditions, a spectral solver based on the Fourier transform is chosen. The Fourier transform is known to have efficient numeric implementations, and will give exact solutions for a periodic system.

In three dimensions the spatial derivative is  $\nabla^2 \Phi = \frac{\delta^2 \Phi}{\delta x^2} + \frac{\delta^2 \Phi}{\delta x^2} + \frac{\delta^2 \Phi}{\delta x^2}$ . The Fourier transform of a the derivative  $\frac{\delta^2 \Phi_{x,y,z}}{\delta x^2}$  is  $k_x^2 \cdot \Phi_{k_x,k_y,k_z}^2$ , which transforms equation 2.3 into 2.4, a second degree polynomial equation in place of a second order PDE.

$$(k_x^2 + k_y^2 + k_z^2) \cdot \hat{\Phi}_{k_x, k_y, k_z} = -\frac{\hat{\rho}_{k_x, k_y, k_z}}{\epsilon_0}$$

(2.4)

$$\hat{\Phi}_{k_x,k_y,k_z} = -\frac{\hat{\rho}_{k_x,k_y,k_z}}{(k_x^2 + k_y^2 + k_z^2) \cdot \epsilon_0}$$

(2.5)

This equation is then solved by dividing by  $k^2$  and scaling by  $\frac{1}{\epsilon_0}$ . After performing the inverse transform and performing any necessary normalization, the field is solved for the electric potential.

#### 2.1.4 Deriving the electric field from the potential

The electric field is related to the potential by equation 2.6, and in the discrete case can be derived using first order finite differences along each axis. The electric field at a vertex  $E_{i,j,k}$  is then as shown in equations 2.7, 2.8, and 2.9, represented as a three component vector.

$$E = -\nabla\Phi \tag{2.6}$$

$$E_x[i,j,k] = \frac{\Phi[i-1,j,k] - \Phi[i+1,j,k]}{2 \cdot h_x}$$

(2.7)

$$E_y[i,j,k] = \frac{\Phi[i,j-1,k] - \Phi[i,j+1,k]}{2 \cdot h_u}$$

(2.8)

$$E_{z}[i,j,k] = \frac{\Phi[i,j,k-1] - \Phi[i,j,k+1]}{2 \cdot h_{z}}$$

(2.9)

#### 2.1.5 Updating particle positions and velocities

When accelerating the particles only the electric forces acting on them are considered here. The gravitational forces between electrons are insignificant in  $comparison^1$ .

The electric force affecting a point charge q at position p in an electric field E is  $F_E = -q \cdot E(p)$ . Dividing by the particle's mass yields the acceleration, and the particle can then be moved using the classical mechanics equations 2.10 and 2.11:

$$v_n = v_{n-1} + a_n * \Delta t \tag{2.10}$$

$$p_n = p_{n-1} + v_n * \Delta t \tag{2.11}$$

The argument could be made that the relativistic velocity equation should be used instead, but for simplicity the Newtonian mechanics have been used. The assumption is made that most velocities will be well below a significant fraction of the speed of light.

Like [2] and many other PIC code implementations [8] a leap-frog integration scheme is used to move the particles, with the velocity update lagging half a time step behind the position update (see equations 2.12 and 2.13). The leapfrog algorithm is more accurate than the simple Euler integration of equations 2.10 and 2.11, with a limited and self-cancelling error when  $\omega \cdot \Delta t \leq 2$ , where  $\omega$ is the plasma frequency (see section 4.5.1 for more) [9].

$$v_{n+\frac{1}{2}} = v_{n-\frac{1}{2}} + a(p_{n-1}) * \Delta t \tag{2.12}$$

$$p_n = p_{n-1} + v_{n+\frac{1}{2}} * \Delta t \tag{2.13}$$

### 2.2 The Fast Fourier Transform solver

Under periodic boundary conditions a PDE can be solved using an FFT solver, which is both efficient and accurate. This section will recap the mathematics behind how the Fourier Transform can be used to solve a PDE, and give a brief introduction to the idea behind the Fast Fourier Transform Algorithm.

The Fourier Transform is shown in equation 2.14, with the inverse transform in 2.15. For a function of time f(t) its transform is considered to be a function of

<sup>&</sup>lt;sup>1</sup>The gravitational force between two electrons yields values on the scale of  $F_G = G \frac{m_e^2}{r_2} \approx \frac{5.538 \cdot 10^{-71} Nm^2}{r^2}$ , while the electric force will be  $F_E = k_e \frac{q_e^2}{r^2} \approx \frac{2.307 \cdot 10^{-28} Nm^2}{r^2}$ . This means that the electric force between two electrons will be roughly  $4.166 \cdot 10^{42}$  times stronger than the gravitational force regardless of the distance between them.

temporal frequency  $\hat{f}(\omega)$ . Similarly for a function of space f(x, y) the transform  $\hat{f}(\xi_x, \xi_y)$  represents the spatial frequency. For this reason the space described by the transformed variables  $\xi_x$  and  $\xi_y$  is often called the frequency domain.

$$\mathcal{F}(f(x)) = \frac{1}{\sqrt{2\pi}} \int_{-\infty}^{\infty} f(x) \cdot e^{-i\xi x} dx = \hat{f}(\xi)$$

(2.14)

$$\mathcal{F}^{-1}(\hat{f}(\xi)) = \frac{1}{\sqrt{2\pi}} \int_{-\infty}^{\infty} \hat{f}(\xi) \cdot e^{i\xi x} d\xi = f(x)$$

(2.15)

#### 2.2.1 Solving PDEs with the Fourier Transform

In order to find an expression for the Fourier transform of the derivative of a function f, we can derive the inverse transform from equation 2.15:

$$\frac{d}{dx}(f(x)) = \frac{d}{dx}\left(\frac{1}{\sqrt{2\pi}}\int_{-\infty}^{\infty}\hat{f}(\xi) \cdot e^{i\xi x}d\xi\right)$$

(2.16)

$$f'(x) = \frac{1}{\sqrt{2\pi}} \int_{-\infty}^{\infty} \hat{f}(\xi) \cdot \frac{d}{dx} (e^{i\xi x}) d\xi$$

(2.17)

$$= \frac{1}{\sqrt{2\pi}} \int_{-\infty}^{\infty} \hat{f}(\xi) \cdot i\xi e^{i\xi x} d\xi \qquad (2.18)$$

$$= \mathcal{F}^{-1}\left(i\xi\hat{f}(\xi)\right) \tag{2.19}$$

and by Fourier transforming both sides

$$\mathcal{F}(f'(x)) = i\xi\hat{f}(\xi) \tag{2.20}$$

The process can be repeated to show that the general rule for the transform of n'th and second order derivatives are

$$\mathcal{F}(f^{(n)}(x)) = (i\xi)^n \cdot \hat{f}(\xi) \tag{2.21}$$

$$\mathcal{F}(f''(x)) = -\xi^2 \cdot \hat{f}(\xi) \tag{2.22}$$

For a second order PDE such as Poisson's equation the result of Fourier transformation is a much more easily solvable polynomial equation, shown in equation 2.23. Solving for  $\Phi$  then consists of dividing the right hand side by  $-\xi^2$  and performing the inverse Fourier Transform.

$$\mathcal{F}(\nabla^2 \Phi) = -\xi^2 \hat{\Phi} = \frac{-\hat{\rho}}{\epsilon_0} \tag{2.23}$$

Equation 2.24 generalizes this to multiple dimensions, and for three dimensions in particular it can be seen that a division of  $\rho$  by  $\epsilon_0 \cdot (\xi_x^2 + \xi_y^2 + \xi_z^2)$  is necessary.

$$\Phi = \frac{-\hat{\rho}}{\epsilon_0 \cdot \sum_n \xi_n^2} \tag{2.24}$$

#### 2.2.2 The FFT algorithm

The Discrete Fourier Transform is a discrete analogue of the Fourier Transform from equation 2.14. The one dimensional version is seen in equation 2.25, where  $\omega$  is the Nth root of unity. The DFT will not be described in detail here, see [7] for a thorough explanation. Since for every output  $\xi_k$  each input  $x_n$  needs to be evaluated, the DFT has a computational complexity of  $O(N^2)$ .

$$\xi_k = \sum_{n=0}^{N-1} x_n \cdot \omega^{kn}, k \in 0..N - 1$$

(2.25)

The Fast Fourier Transform is the name of an optimized algorithm with a complexity of  $O(N\log N)$ . Different FFT algorithms have been invented for various purposes, but they are most commonly implemented as a recursive algorithm. The most common is the algorithm described by J.W.Cooley and John Tukey in [10], known as the Cooley-Tukey FFT algorithm.

Dividing the transform into two transforms of size  $N/_2$  is called a radix-2 FFT, while the more general case of dividing the transform by the factors of  $N \neq 2^n$  is called a mixed-radix FFT. A more detailed explanation can be found in [10] or [7], but the general idea is to split the computation to avoid recomputing the same values due to symmetry and periodicity. By exploiting these properties of the transform, the complexity  $O(N \log N)$  is achieved.

### 2.3 Parallel computing and GPGPU

Parallel computing may refer to any form of processing in which multiple operations are performed concurrently. This can range from vectorizing single instructions to running ten thousands of threads on thousands of nodes on a supercomputer. In recent years, GPGPU has become a popular form of parallelism.

#### 2.3.1 History and motivation for parallel computing

When Gordon E. Moore discussed the possibility of "Cramming More Components onto Integrated Circuits" in 1968[11], besides reasoning why and how the number of transistors on a chip would increase over time, the difficulties associated with it such as power dissipation received only a small mention. Moore expected that integrated circuits would allow for sufficient cooling, and that the shrinking size of the components would allow the circuit to run faster under the same power.

While this is true, and Moore's law regarding increasing component density on circuit boards has held true for longer than the ten year period he estimated, the increase in processing power slowed during the late 1990s and came to a halt in 2004. A visible sign of this was when the successor to Intel's previous Pentium 4 processor was cancelled in favour of a transition to a dual core architecture[12].

Important reasons for this happening were the fact that memory speeds were lagging significantly behind processor speeds already, to the point where further increase in CPU clock frequency would result in it running idle while waiting for data from memory, with the cache hierarchy no longer able to hide the latency ([13] provides a more detailed explanation, and considers whether the wall was hit when expected). Memory *bandwidth* was increasing by at least the square of the *latency*.

Memory latency had been partially hidden by increasing the instruction level parallelism, but attempting to extract further parallelism would yield diminishing returns[14].

Increasing clock frequency and transistor density both contributed to CPU power consumption increasing rapidly, to the point where traditional cooling techniques would suffice no longer[14]. Counteracting this power increase by reducing voltage would no longer be an option either, due to issues such as subthreshold leaking and electromigration becoming prominent with insufficient voltage. More transistors could be placed on the chip than could be powered on.

Rather than designing increasingly complex and massive single core CPUs the trend from the early 2000s became multicore processors, with multiple independent processing cores on a single chip. By adding additional cores the theoretical processing power of the CPU could be further increased, assuming all cores could be kept busy. Multithreading has therefore become an important aspect of modern applications programming, running independent operations in threads that execute concurrently on multiple cores. Examples of applications that commonly are multithreaded are operating systems, video and image processing applications, computer games, and other applications with heavy real time data processing requirements.

Even before consumer computers made the jump to multicore, academia and industry have made use of parallel platforms such as computer clusters and supercomputers. The different varieties of parallel architectures will be described below, but for this project a particular brand of parallel computing is of interest, GPGPU.

#### 2.3.2 General Purpose computing on Graphics Processing Units

General-purpose computing on graphics processing units (GPGPU) is a fairly recent trend in high performance and parallel computing, where programs are accelerated by running heavy computation on a graphics processing unit (GPU) rather than the more traditional CPU. Characterized by a large number of slower cheaper compute cores, modern graphics cards can deliver massive parallelism at a comparatively low cost.

The graphics pipeline on early GPUs contained specialized hardware for common graphics processing tasks. Traditionally data was passed from the CPU to the GPU where it was processed in several steps, rendered, and output to some display device. Over time the specialized hardware was replaced by a more flexible programmable pipeline, with support for programmable shaders working on common graphical primitives.

Around 2001 these programmable shaders enabled researchers to perform the first experiments with GPU computing, by defining the data and problems in terms of graphics primitives and shader programs. In order to alleviate some of the inconvenience of this convoluted programming model GPU-specific languages and libraries were written, effectively providing an abstraction over the shader language. Examples of such languages were Sh and Cg [15]. As mentioned by [16] implementing simulations using these shader languages placed severe limits on what was achievable.

As the industry as a whole began shifting its focus towards multithreading and parallel computing GPUs were also becoming more powerful and easier to program. By the late 2000s GPUs had shifted from being graphics pipelines to generic stream processors, with increasingly high parallelism and general programmability. In recent years GPGPU has been found to perform outstandingly for certain types of problems, with potentially much higher efficiency than comparable CPU implementations[17]. GPGPU is still recognized as a field with higher demands in terms of programming effort, and many problems will be better suited to the more general domain of the CPU.

#### 2.3.3 Parallel performance measures and potential speedup

When the performance of a program or system is measured the goal is often to find the improvement over a previous candidate. For parallel systems in particular, the speedup compared to the serial execution is often of interest, or the performance relative to a different parallel configuration. For parallel systems the speedup as a function of the number of processing cores is typically of interest. Two different definitions of parallel execution time has led to two well known yet different rules for parallel speedup.

In both of these the speedup of a program a with runtime  $T_a$  over a program b is defined as  $S_{a,b} = \frac{T_b}{T_a}$ , the number of times a can be executed while b is running. In addition to the number of processing cores n another important parameter is what fraction of the program is inherently serial, and which thus yields no speedup from adding additional cores. One the best known rules in this regard is Amdahl's law.

**Amdahl's law** defines the speedup as the serial execution time divided by the time it would take a parallel processor with n cores to do the same work. Assuming a serial fraction  $P_s$  and a parallel fraction  $P_p$ , with execution time for a single core  $T_1$ :

$$S_{n,1} = \frac{T_1}{T_n} = \frac{T_1}{T_1 \cdot (P_s + \frac{P_p}{n})} = \frac{1}{P_s + \frac{P_p}{n}} \left(= \frac{n}{P_s \cdot n + P_p}\right)$$

(2.26)

Letting  $n \to \infty$  it is apparent that the speedup is limited by the serial fraction, with the maximal speedup proportional to  ${}^{1}/P_{s}$ . See [18] for the original argument. What is known as Gustafson's law was proposed as an answer to Amdahl's law in [19].

**Gustafson's law** instead defines the speedup as the time it would take a single core to perform the work the parallel processor is capable of doing divided by the parallel processing time. The difference here is essentially that Gustafson

assumes the parallel part of the program can be scaled according to the number of processors rather than remaining fixed. By performing more work in a single execution the overhead from the serial fraction will no longer dominate as the number of cores increase.

$$S_n = \frac{T_1}{T_n} = \frac{P_s + P_p \cdot n}{P_s + P_p} = \frac{P_s + P_p + P_p \cdot (n-1)}{1} = 1 + P_p \cdot (n-1) \quad (2.27)$$

#### 2.3.4 Architectures

There are several options for classifying parallel computer architectures, based on programming model, hardware, communication patterns and so on. In this section the scheme known as Flynn's taxonomy will be introduced first, followed by a look at some different memory architecture classes.

#### Flynn's taxonomy

Since first proposed by Michael J. Flynn in 1972, the scheme known as Flynn's Taxonomy has been used to classify parallel architectures based on how instructions and data are shared between processors[20].

|                      | Single data | Multiple data |

|----------------------|-------------|---------------|

| Single instruction   | SISD        | SIMD          |

| Multiple instruction | MISD        | MIMD          |

**SISD** The single instruction, single data architecture represents a traditional sequential computer, any single-core CPU.

**SIMD** Single instruction, multiple data-architectures contain several processors performing the same operations on different data. Array processors are an important example here, and in particular GPUs. The same instructions are run on several processors in parallel, with each operating on its own data set. Typically consisting of an array of smaller processors that each operate on a small number of elements from a larger shared array, devices with these architectures are often called array processors.

**MISD** An uncommon architecture, the MISD does not utilize parallelism to improve performance, as it has the same throughput as a single code (SIMD)

processor. Instead of multiple cores processing more data, this case runs different instruction on the same data stream in parallel. This can be useful for systems with low fault tolerance, where processing a set of data on different systems (with different instructions) can reveal errors.

**MIMD** Both multicore CPUs and most current supercomputers fit this category, with multiple cores running instructions independently, on separate data.

**Other** Variant extensions have been proposed later, including the SPMD (single program, multiple data) and MPMD (Multiple program, multiple data). SPMD is a subcategory of MIMD where a single program is run on multiple processors in parallel. Instances of the program on different processors are not guaranteed to run concurrently however, and SPMD is therefore more flexible than SIMD.

#### Memory architectures

Parallel systems are also often categorized based on their memory architecture. As an example, while a multicore CPU and a supercomputer both fit the MIMD label, they will typically have a vastly different configuration, in particular with regard to memory spaces, and of course number of cores.

**Shared memory** Most multicore personal computers and workstations employ a shared memory architecture (SMA), where threads in programs share a memory space. This means that threads within a process can read and write the same data. Communication between threads is therefore fast.

While a shared memory may be easier to envision and program for, it becomes increasingly complex when more cores are added. Memory access arbitration will become harder, and core will have to wait longer for their request to return. Race conditions are more prevalent, but all data is available to each core.

**Distributed memory** Supercomputers and computer clusters in general often consist of a large number of nodes. Each node may consist of several cores and accelerators, and has a private memory. Nodes in a distributed system may themselves be shared-memory systems.

By distributing the memory, the number of cores competing for memory access is limited to the number of cores per node, thus improving scalability drastically. Doubling the number of nodes in the system will have no effect on the local memory latency of any core.

**Memory access types** Parallel architectures can also differ in how memory accesses are performed, notably whether they have a uniform or non-uniform memory access (NUMA) from different processors. Numerous variations exist in regard to configuration of memory and cache handling.

# 2.4 CUDA - Compute Unified Device Architecture

The Compute Unified Device Architecture (CUDA) is a proprietary GPGPU framework developed by Nvidia. While CUDA is a relatively young technology, first appearing in 2006, it has already seen widespread use in industrial and scientific computing. This section will give an introduction to the CUDA programming model, device architecture and mention some key factors affecting the performance of CUDA applications.

While CUDA applications can be developed using various languages and APIs this section will mainly concern the CUDA C/C++ language and the CUDA Runtime API. See section 2.4.3 for other ways to accelerate applications using the CUDA framework. The CUDA model is explained in detail in [21].

#### 2.4.1 The CUDA Programming Model

The CUDA architecture employs SPMD parallelism, executing the same program across multiple *Streaming Multiprocessors*(SMs), typically targeting different elements of the same data stream. Compared to a typical CPU architecture this leads to increased usage of hardware for actual computing rather than control logic and cache handling.

The multiprocessors themselves operate in a scheme called SIMT (Single Instruction, Multiple Threads), where hundreds of threads execute the same instruction concurrently. Threads are organized in blocks, and executed together on a an SM. Warps of 32 threads share control logic and therefore also execute all instructions together. See figure 2.2 for an illustration.

Figure 2.2: Conceptual illustration of the CUDA architecture, with a warp size of 8 and 4 SMs for clarity. Threads (green) in a warp share control logic (orange). All threads in a block execute on the same SM and have access to the same shared memory. All blocks on a GPU have access to global memory.

#### Device code

A CUDA C/C++ application typically consists of host code serving as a master thread which launches device code in functions called kernels. The host performs any necessary set-up such as allocating memory and transferring data to device memory, and then launches the device kernels with a specified number of threads. The kernels then process the data in some way, typically operating on one data element per thread, using relatively simple code with limited branching and looping. After the kernels have executed, the host then transfers the result back to host memory, frees resources and ends execution. See section A.1 for a simple CUDA example.

#### Threads

As mentioned, the kernels are called while specifying the number of threads. Organized as a number of threads in a block, in a grid of blocks, the thread hierarchy in CUDA somewhat reflects the hardware implementation. A relic of its origin in graphics programming CUDA organizes threads and blocks using three dimensional coordinates, allowing a natural mapping from thread index to coordinates.

Each thread has a private set of registers it operates on, while threads are executed in sets of 32 called *warps*. Each warp executes in lock-step with all threads in a warp executing all instructions (SIMD). It is thus of interest to limit divergent branching within warps, as the whole warp must execute code for all branches.

A thread block consists of up to 1024 threads, ideally a multiple of 32 since they are executes as warps of 32. Threads in a block are executed at the same time within a single SM, and can therefore synchronize with each other, and have access to the same *shared memory*.

Blocks are organized within a grid, containing all threads belonging to the same kernel launch. Blocks are distributed among SMs, execute in batches, and therefore share neither on-chip resources nor any form of synchronization other than kernel launch and end time. All blocks in a grid will execute on the same device however, and therefore have shared access to the global memory available on that device.

CUDA streams represent another level of hierarchy, allowing multiple kernel executions (grids) in separate streams. While all kernels launched in a stream are executed sequentially, kernels in separate streams may execute in any order relative to each other, or even concurrently. When using CUDA with more than one GPU, kernels will be issued to separate streams, as they are tied to a device.

#### Memory

The different levels of the memory hierarchy correspond to the thread hierarchy. Registers are the fastest memory resource available to threads. They come in a severely limited quantity, 255 per thread for current architectures, but have no latency. Registers can only be read by the owner (with some exceptions, see [22]) and share the lifetime of the thread.

Shared memory is a slower and larger memory that resides on-chip, and is shared between all threads in a block. Access latency is on the order of 10 cycles, and size on the order of 64KB per SM. Where registers are private, shared memory is typically used to communicate between threads in a block, or to store data common to several threads, reducing the load on the global memory by preventing unnecessary memory accesses. Shared memory has the lifetime of its block, so to keep any data it must be written to global memory.

The global memory is large, typically 2 to 24 GB depending on the device, but typically has a latency of several hundred cycles. All threads on a device can access global memory, and it is persistent, allowing communication between blocks and kernels. While the global memory in general is accessible by threads on the device it is contained, threads from different devices may access memory on other devices under certain conditions [21, s3.2.6.4].

Atomic operations are a common way of avoiding write conflicts when multiple threads in a shared memory context need to write to the same address. By guaranteeing only one thread can update an address at a time, no writes are lost to overwriting. While double precision atomic operations are limited to the atomic compare-and-swap, others can be implemented using the atomicCAS, as seen in the example below (based on one given in [21]).

```

--device__ double atomicAdd(double *addr, double value) {

unsigned long long int* ull_addr = (unsigned long long int*)addr;

unsigned long long int updated = *ull_addr, compare;

do {

compare = updated;

updated = atomicCAS(ull_addr, compare,

__double_as_longlong(value + __longlong_as_double(compare)));

} while (compare != updated);

return __longlong_as_double(updated);

}

```

This example also demonstrates why the atomic operations are slow; the loop runs until the value is successfully swapped. When a large number of threads attempt to write to the same address the operation can take a long time to complete. Because the CUDA architecture executes warps together, a single thread stuck in the while loop will stall the entire warp.

#### 2.4.2 Performance factors

The long latency between global memory requests and the availability of the requested data is somewhat hidden by the CUDA architecture. Whenever a warp is stalled waiting for data, the SM switches context to a warp ready to execute. The context for all executing warps are stored throughout their lifetime, so that this switching has a minimal performance impact, while serving to keep the SM busy, thus hiding the memory latency.

A big factor in this is *occupancy*. If no other warp is available while the first is waiting the SM will be idle until a warp is ready to continue. For this reason a CUDA device will have better performance if the total number of warps is higher than the number which can execute concurrently, the SMs need idle warps to switch to in order to achieve maximum throughput. The number of threads that can be stored in an SM at any time depends on the architecture, model, register usage and thread dimensionality. While many of these vary greatly from case to case, a rule of thumb is to have 128 to 512 threads per block (see table 5.1 of [23] for a comparison of utilization for various architectures).

Overlapping kernel execution with host-device memory transfers is another way to prevent downtime. Assuming the data used by the kernel and memory transfer is separate, issuing these to separate threads will allow them to execute concurrently. For this reason many CUDA API functions, especially those dealing with device memory, have synchronous and asynchronous (non-blocking) versions. Of course, this also allows the host thread to perform other tasks while the kernel and memory transfer are executing.

While the techniques above are useful to hide latency, accessing global memory correctly will yield even better results. The architecture is optimized for SIMD-style computing, where access to consecutive addresses by threads in a warp will be significantly faster than random accesses. Because memory transactions are 32-, 64- and 128-byte wide segments, memory accesses that are aligned to these sizes will yield better performance. Note that the smallest transaction is for the equivalent of eight 32-bit integers, meaning a memory access for a smaller size will waste throughput.

Structuring memory accesses so that consecutive threads access consecutive addresses is called a *coalesced* memory access. Coalesced memory accesses yield better performance, particularly for data that is aligned in memory[21, p. 5.3.2].

As mentioned above, shared memory is commonly used to reduce the number of global memory accesses. An ideal example is for image processing, where by copying the thread block's segment of an image into shared memory, all threads in the block has fast access to the whole segment.

## 2.4.3 Alternative CUDA interfaces

Support for OpenCL, an open source alternative to CUDA, is built on top of the low-level CUDA architecture on Nvidia GPUs, providing a different interface to much of the same functionality[21]. OpenACC is a compiler directive-based programming standard, aiming to provide simple parallelization of accelerators, similar to the OpenMP standard for multicore parallelization. See Nvidia's CUDA Language solutions<sup>2</sup> page for more information.

<sup>&</sup>lt;sup>2</sup>https://developer.nvidia.com/language-solutions

# 2.5 cuFFT - the NVIDIA CUDA Fast Fourier Transform library

Nvidia's Fast Fourier Transform library cuFFT is available as part of the CUDA development kit. cuFFTW is a second library which supplies similar functionality, but through an interface that mimics that of the FFTW<sup>3</sup> library to ease conversion of code.

For input sizes consisting of powers of small primes the Cooley-Tukey algorithm is used to generate efficient transforms on up to 512 million elements. Transforms of up to three dimensions are supported, for complex and real valued data. While the FFT exhibits a degree of parallelism by allowing sub-problems to be computed in parallel, cuFFT's forte is in batched transforms, where multiple data sets are transformed via a single call, minimizing overhead.

### 2.5.1 cuFFTXt - Multi-GPU support in cuFFT

Recent versions of the library have improved and extended the multi-GPU capabilities of the library as well. As of CUDA 7.0 the multi-GPU functionality (referred to as cuFFTXt) supports execution across two or four GPUs, with certain additional restrictions placed on combinations of transform and input sizes. In particular, multidimensional transforms have a minimum size of 64 along the x and y dimensions, and only support in-place complex-to-complex transforms.

Another major difference is that while the single-GPU transform can operate on any array matching the transform size, for multiple GPUs a special data structure must be allocated that contains pointers to data on the various GPUs, array sizes and information about the library. The result of a single 2D or 3D transform will also be divided along the y axis instead of along the x axis. See section A.2 for examples on use.

# 2.6 Related work

The following are examples of PIC codes being adapted to different parallel architectures.

$<sup>^{3}</sup>$  The Fastest Fourier Transform in the West

**Parallelization Issues and Particle-In-Cell Codes** [2], Dr. Anne C. Elster's Ph.d. thesis from 1994, is a detailed account of a parallel electrostatic PIC code running on a SMP architecture. Beyond giving an elaborate introduction to the physics behind the algorithm, load balancing across processors and techniques to achieve this are discussed.

*Emerging Technologies Project: Cluster Technologies* PIC codes: Eulerian data Partitioning [3] by Jan C. Meyer describes an attempt to adapt the algorithm from [2] for a message-passing architecture using MPI. The performance on a supercomputer and a PC cluster was compared.

**Parallelizing Particle-In-Cell Codes with OpenMP and MPI** [4] is Nils Magnus Larsgård's master's thesis from 2007, which also builds upon the same algorithm. The topic here is parallelization using both OpenMP and MPI on cluster computers. In particular, the goal was to find which configuration of OpenMP and MPI lead to the best performance.

A General Concurrent Algorithm for Plasma Particle-in-Cell Simulation Codes [24] is the name of a paper on a one dimensional particle in cell code written for parallelization on a distributed memory architecture, and accounts for the details on splitting the problem into subproblems in an efficient manner, and the distribution of these subproblems across the processors.

**Particle-in-Cell Charged-Particle Simulations, Plus Monte Carlo Collisions With Neutral Atoms, PIC-MCC** [6] gives a detailed review of the history of PIC codes from ca 1950 to 1990. Attempts to add particle collisions to the simulation are mentioned, and the combination of PIC code with Monte Carlo collisions is the main focus.

**Dynamic Load Balancing for a 2D Concurrent Plasma PIC Code** [25] extends [24] to 2D with a focus on load balancing. Load balancing was found to be most useful when the particle update step dominated the solver step. Since their FFT-based solver exhibited far less efficient parallelism they found that load balancing was counter productive compared to static partitioning.

Adaptable Particle-in-Cell algorithms for graphical processing units [26] implemented a simple 2D PIC code with the goal of running it on different platforms.

**Particle-in-cell plasma simulation on heterogeneous cluster systems** [1] developed a 3D PIC plasma simulation, and using OpenMP and OpenCL supports execution on either CPUs or GPUs in a cluster.

# Chapter 3

# Implementation

The Particle-In-Cell method implementation will be described in this chapter. We will also briefly discuss issues with dividing the implementation across multiple GPUs, and the implementation and possible alternatives for the particle tracer. Finally a simple OpenMP/FFTW port of the implementation issues described.

# 3.1 Goals for the implementation

The following is a summary of the goals and motivations behind some important decisions taken during implementation.

#### Particle simulation on a graphics card

The primary goal is to implement a functioning Particle-In-Cell code in CUDA, capable of simulating the expected behaviour of some system. The target simulation is plasma oscillation, as described by [2].

In addition, the implementation should support acceleration by more than one GPU, to investigate what benefits this could yield. The CUDA Fast Fourier Transform library cuFFT is used for the PDE solver, as it has support for multiple GPUs, and should integrate better with a CUDA application than most other libraries.

#### Problem size

An important question to be answered is whether the hardware and memory of a GPU is sufficient to execute and contain a PIC code of sufficient size and accuracy.

According to [1] some problems for PIC codes require a number of particles on the order of  $10^9$  and a grid of some  $10^8$  elements. A quick calculation shows that  $10^9$  3D particles using double precision data types require at least 44.7 GB of storage alone. With the largest available memory of even high-end Nvidia Tesla GPUs at around 12 or 24 GB a simulation of those sizes are still out of reach. See section 4.5.1 for more on the scale of the simulation.

For performance reasons, particles and simulation grid are all kept in GPU memory when possible. A larger number of particles could be supported by keeping the majority in host memory, transferring them to the GPU and processing them in turn. The simulation grid is still restricted to the size of the GPU memory however, unless a more low level implementation of the solver is used. To make use of the cuFFT libraries without too much overhead, and particularly because of the high cost assiciated with data transfers between host and GPU memory, the problem size will be restricted to whatever can fit in GPU memory.

To increase the available memory, and thus potentially the scale of the simulation, support for additional GPUs will be added. Whether the additional available memory can be of use is an issue that will be investigated.

#### Performance

While optimal performance is not a primary goal for this implementation, decent performance relative to a comparable multithreaded C++ implementation is expected. In addition, the performance of the multi-GPU configuration compared to the single-GPU one is of interest. Some overhead due to communication between the GPUs is expected, but whether there is enough of a benefit from splitting the FFT computation across them to outweigh this will be of interest.

#### Modularity and readability

Besides goals for increasing problem size and decent performance, a tertiary goal has been to write readable and modular code, with more loosely coupled code. Ideally this should result in a more readable code, while also being easier to extend with further functionality, such as adding other solvers, or target applications. As mentioned by [3, s6.2] the use of explicit data structures rather than arrays of primitives helps increase the modularity of the program. While data structures were used to represent both particles and grid elements in [3], the field has in this implementation been left as separate arrays for charge density and the electric field. The advantage of this is that the electric potential can be calculated in-place by the solver, reducing the memory footprint. In addition the cuFFT library does not support strided transforms across multiple GPUS as of yet.

The implementation also aims to be operating system agnostic, tested on both Windows and Ubuntu. The cuFFT library still has some restrictions on GPU configuration based on OS as of CUDA 7.0.

# 3.2 Simulation overview

The structure of the program is as follows:

- 1. Setup

- 2. Distribute charge from particles to grid

- 3. Solve charge distribution for electric potential

- 4. Calculate electric field in grid

- 5. Update particles based on electric forces

- 6. Repeat from 2 until finished

- 7. Cleanup

Each of these steps are covered below.

## 3.2.1 Setup

Setup consists of reading the simulation configuration file settings.cfg, setting up the solver, allocating and initializing particles, and opening the trace file.

The configuration file uses the INI format<sup>1</sup>, and the PropertyTree class from the Boost library<sup>2</sup> is used to read the file. Other values that depends on those read from the file are then computed and stored in a Cfg object.

The number of GPUs on the system is also read and stored in this object, but can be overridden by setting the multi option in the config file to 0, overriding the detected number of GPUs and setting it to 1. Based on this value the appropriate solver is then set up, as cuFFTXt employs a different interface than the standard cuFFT library, and requires different initialization. The FFT plan is created, and both the grid and work area for cuFFT is allocated.

**Particles are initialized** using a function and kernel particular to the application. For plasma oscillation the particles' positions should be regularly spaced in two planes. The spacing in either direction as well as the number of rows and columns in each plane is calculated, and a kernel creates a particles at each position, with no initial velocity. The distribution of particles along either axis of the plane is attempted to match the grid resolution in that direction.

A particle tracer object is also created and a trace file opened, see 3.4 for details. The tracer object uses its own set of CUDA streams to overlap its data transfers with kernel computation.

## 3.2.2 Simulation loop

The simulation loop is run a number of times specified in the config file. While previous work defined the simulation time as a parameter, the runtime is instead controlled here, with a simulation time equal to the number of iterations times the length of the time step.

An iteration of the simulation loop consists of the steps below; the charge distribution kernel, the forward cuFFT call, the solver kernel, the inverse transform, the electric field kernel, the particle update kernel, and depending on the configuration and current iteration particles might be traced.

In addition, boundary exchange and particle migration is handled for a multi-GPUs system. Because both data types and cuFFT calls are different, two different simulation loop functions have been implemented, simplifying the single-GPU version.

$<sup>{}^1 \</sup>verb"INIfileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.org/wiki/INI_fileonWikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedia.https://en.wikipedi$

<sup>&</sup>lt;sup>2</sup>http://www.boost.org/

#### Charge distribution kernel

The kernel is called for each particle and opens by finding the neighbouring grid vertices based on current position, trilinearly interpolating as shown (2.1).

Because the equations for the weights and array offsets for each neighbour are the same for this and the particle update kernel the code for finding these has been separated into a helper function.

To update each neighbour while avoiding overwriting values from other particles, atomic updates of grid values are used. This severely limits the performance of the kernel, and alternatives have been investigated.

For the multi-GPU case, particles that are positioned between vertices on two GPUs (see figure 3.1) write their contribution to a temporary boundary array. After the kernel has completed this boundary is then forwarded to each appropriate device, and the values are added to the vertices they represent.

#### Field solver

The solver step consists of a forward FFT, a solver kernel, and an inverse transform. The solver kernel divides each grid value by  $\epsilon_0 \cdot (k_x^2 \cdot k_y^2 \cdot k_z^2)$ . In addition, it normalizes the result by  $N_x \cdot N_y \cdot N_z$  as required by the transform.  $k_x$  can be calculated from the x axis coordinate i as  $k_x = i \cdot \frac{2\pi}{l_x}$  where  $l_x$  is the metric length of the simulation space in x. Since only the coordinates varies for different threads, the rest is precomputed and stored in the config object for the kernels.

#### Electric field

The electric field is derived according to the equations in section 2.1.4. For each grid element the difference between neighbours' potential divided by the distance between them is calculated along all axes.

Boundary potential values are stored in the same boundary arrays, and distributed to the other devices for multi-GPU configurations. Afterwards the boundary array is populated with the electric field values along the boundary.

#### Updating the particles

Called per particle, the electric field values of neighbour vertices are interpolated in the same way as for the charge distribution kernel. Scaling by  $\rho/m$  yields the particle's acceleration. The velocity and then position are updated accordingly. Particles that go out of bounds are "wrapped" so they re-enter the simulation

Figure 3.1: Illustration of particles in a grid split between two GPUs. Column 0 and 3 are duplicated into temporary buffers, indicated by the dotted line. The yellow particles lie on the boundaries between GPUs and need to access these buffers to write their contributions.

space on the other side, keeping with the periodicity of the simulation. As for charge distribution, particles in space between nodes from different GPUs read their electric field values from a temporary buffer.

## 3.2.3 Cleanup

After the simulation is completed the final particle traces are written to file and the trace file is closed. The FFT plan is destroyed, and other allocated memory is freed.

# 3.3 Parallelization issues

This section will mention some of the important parallelization issues faced during implementation of the algorithm. Notably, two different kinds of parallelism occur, shared memory parallelism within a GPU, and distributed memory parallelism when more GPUs are involved. Each of these have their own issues.

## 3.3.1 Atomic operations

For simplicity and readability the implementation currently uses the slow atomic operations. Their performance decreases with the number of conflicts, but require less overhead in design and maintenance during development. The issue is discussed further, with suggestions for improvements, in section 4.6.

#### 3.3.2 Overlapping memory transfers with kernels

Because of how the CUDA architecture is designed, with high throughput-high latency memory buses, it is advantageous to overlap data transfers with kernel execution when possible. By using the asynchronous variant of the memory management interface, and executing kernels in a separate CUDA stream, the host will not have to wait for either to finish before issuing new requests.

In order to benefit from this, the data dependencies within the program must allow overlapping. The data transfers involved in the simulation loop are either part of the particle tracer described below, or boundary distribution between kernels. The latter typically leaves little room for overlap, since the transferred data is written by the preceding kernel and read by the succeeding one, see table 3.1 for the lifetime of each data array.

Particle tracing however depends on data written by the particle update kernel, and must complete before the next particle update. The data transfer can therefore be overlapped with both the other kernels and also the writing of previous particle traces to file.

| functions $\setminus$ arrays | particle | $\rho, \Phi$ | Е     | boundary |

|------------------------------|----------|--------------|-------|----------|

| chargeDistribution           | read     | update       |       | write    |

| boundary, rho                | 1        | update       |       | read     |

| solverKernel                 | 1        | update       |       |          |

| boundary, phi                | ]        | read         |       | write    |

| electricfield                |          | read         | write | read     |

| boundary, E                  | ]        |              | read  | write    |

| particleUpdate               | update   |              | read  | read     |

| particleExchange             | update   |              |       |          |

| trace particles              | read     |              |       |          |

Table 3.1: Illustration of the lifetime of each data array.

The best candidate for overlapping these transfers are likely the solver, done automatically by the cuFFT library, and based on results from code profiling (see 4.3) it appears this is well utilized.

## 3.3.3 cuFFTXt limitations

While there are many options with regard to particle migration and load balancing in general, the cuFFTXt library sets restrictions. In particular, the grid is statically distributed among the GPUs involved, which limits the possibilities for dynamic load balancing.

#### 3.3.4 Particle migration

When particles on one GPU enter a part of the grid located on another, the particle must migrate from the memory of the first to that of the second in order to be able to access the correct neighbouring grid elements.

While it is easy to determine whether a migration is necessary (using a simple check of the position coordinate against the domain of the GPUs), the actual transfer of particle data is more complicated. First consider the case where all particles migrate from one GPU to another. Either the correct amount of memory must be allocated in-loop to be able to house the data, or room for all particles must be allocated on all GPUs (more advanced schemes will be mentioned in the following section). Assuming then that all GPUs have room for all particles (which yields  $1/n_{GPU}$  occupancy of the allocated memory), how should the migration occur?

The implementation currently uses a simple brute force solution, where all particles are copied to the host memory, sorted according to correct device, and copied back to the appropriate device memory. This is a simple solution, but considering that plasma oscillation along one axis, with the grid divided along another ideally has *no* particles migrating, it is wasteful to transfer all particles every iteration. Some suggestions for improving this are mentioned in section 4.7

# 3.4 Particle tracing

Without some sort of output, the simulation would serve no other purpose than as a work load to benchmark a system by. Because the output can be used to verify simulation accuracy, and because the process of writing data to file has an impact on performance itself, some support for writing particle data to file is needed. The simulation is built around plasma oscillation, with the particles' positions as the main output.

## 3.4.1 Tracer implementation

A goal for the particle tracer was that it should not distract from the algorithm, ideally handling the tracing process behind the scenes. To limit the impact particle tracing has on the general performance, the maximum number of particles traced can be specified. This allows the visualization script mentioned below to animate the movements of the particles without choking on the sheer amount of data. For the same purpose, a frame option is also given in the configuration settings, which limits how many times the tracer is called.

#### Writing data to file

Two sets of particle storage arrays plus an output array are allocated by the tracer. By using the CUDA host memory allocation function the resulting array is pinned in host memory, facilitating faster transfers between it and the GPU it is associated with. Using an asynchronous transfer of data from the GPU to one of the associated arrays, data already copied to the other can be written to file. The idea is to overlap the transfer of frame n with the writing of frame n-1 to file. By handling this in a separate thread the performance could be increased further, with the simulation running while particles are written.

An important assumption here is that the number of particles written is limited, as pinned host memory remains in RAM at all times. Since the total size of the particle array easily reach several GB in size this will be a problem. If an application needs to output *all* particles in a simulation with millions of particles, a different solution must be sought.

#### **Output** format

The output data itself has a simple structure. Position values are formatted to a precision of 12 digits and separated by commas, particles are separated by a semicolon, and frames separated by a newline. While this does not conform to a typical CSV format, it makes the process of separating the data easier.