### The Cellular Automata Research Platform: Revised, Rebuilt and Enhanced

Per Thomas Lundal

Master of Science in Computer Science Submission date: June 2015 Supervisor: Gunnar Tufte, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

### Sammendrag

Naturen har mange attraktive egenskaper som ingeniører håper på å en dag kunne gjenskape i menneskeskapt teknologi for å revolusjonere databehandling. De inkluderer blant annet reproduksjon, læring, tilpasning og massiv parallellisering. Én bioinspirert struktur er den Cellulær Automaten (CA). Den kan gjenskape flercellede organismers massive parallellitet, distribusjon og lokal samhandling.

På NTNU har tre masteroppgaver gått med til å lage en FPGA-plattform med formål om å muliggjøre forskning på CAer i kombinasjon med kunstig evolusjon og utvikling. Hovedprinsippet er at en genetisk algoritme (GA) brukes til å lage utviklingsregler, som så blir brukt til å konstruere en CA, som til slutt brukes til å beregne en fitnessverdi. Fitnessverdien blir så matet tilbake inn i GAen og prosessen gjentas til en god løsning er funnet.

I forventning om å få ny maskinvare med en større FPGA, gikk den nyligste masteroppgaven ut på å utnytte den økte ressursmengden til å bedre ytelsen og utvide CAen til 3D. Men på grunn av produksjonsproblemer kunne dessverre ikke maskinvaren leveres i tide. Derfor ble ikke en ny kommunikasjonsmodul implementert og kun grunnleggende simuleringstester kunne utføres.

I det innledende spesialiseringsprosjekt til denne masteroppgaven ble en ny kommunikasjonsmodul implementert og integrert i plattformen, som tillot skikkelig maskinvareverifisering. Den viste at designet hadde mange problemer, inkludert feilende instruksjoner, stor bruk av utdaterte elementer og separate versjoner for 2D og 3D. I denne masteroppgaven har derfor hele plattformen blitt revidert og gjenoppbygd.

Den nye plattformen løser alle store problemer med den gamle og legger til nye forbedringer som mer avansert kontrollflyt og et adaptivt programvare API. Flere og mer fininstillbare byggparametre tillater større justering av ytelse og gjør det mulig å få plass til større CAer på FPGAen.

Funksjonaliteten til alle instruksjoner er verifisert i maskinvare og demonstrert med et program som lager repliserende strukturer. Dette viser at plattformen er komplett og klar for bruk til forskning. Et klokkeproblem med kommunikasjonsmodulen fører for tiden til at hele plattformen kjører på halv hastighet, men viss det fikses vil den rå CA ytelsen bli 35% bedre i 2D og 300% bedre i 3D sammenlignet med det forrige designet. For disse ytelseskonfigurasjonene er ressursbruken vesentlig mindre i 2D og omtrent lik i 3D. ii

### Abstract

Nature has many attractive properties that engineers hope to once incorporate into man-made technology to revolutionize computing. Properties include, among other things, reproduction, learning, adaption and massive parallelism. One bio-inspired computational structure is the Cellular Automaton (CA), which can mimic the massively parallel, distributed and locally interactive nature of multi-cellular organisms.

At NTNU, three master theses have gone into creating a Field-Programmable Gate Array (FPGA) platform whose purpose is to allow research on CAs in combination with artificial evolution and development. The main principle is that a Genetic Algorithm (GA) is used to create development rules, which are then used to build a CA, which can finally be used to compute a fitness value. The fitness value is then fed back fed into the GA and the process is repeated until a good solution is found.

In expectation of new hardware with a larger FPGA, the purpose of most recent thesis was to take advantage of increased resources to improve speed and to extend the CA into 3D. However, the hardware failed to be delivered on time due to manufacturing problems. This caused the new communication module to remain unimplemented and only allowed rudimentary simulation testing.

In a specialization project leading up to this thesis, a new communication module was implemented and integrated into the platform, allowing proper hardware verification. It showed that the design had many issues, including failing instructions, extensive use of outdated features and separate versions for 2D and 3D CAs. In this thesis, the entire platform has therefore been revised and rebuilt.

The new platform solves all major issues with the previous and adds further enhancements such as more advanced control flow and an adaptive software API. More and better fine-tunable build parameters allow wider adjustment of performance and make it possible to fit larger CAs within the FPGA.

The functionality of all instructions is verified in hardware and a program that creates replicating structures is demonstrated, proving that the platform is complete and ready to be used for research. A clocking issue with the communication module is currently reducing the entire platform to half speed, but if fixed, the raw CA performance will be 35% higher in 2D and 300% higher in 3D compared to the previous design. For those performance configurations, resource usage is significantly lower in 2D and equivalent in 3D.

iv

### Preface

This master's thesis has been conducted at the Department of Computer and Information Science at the Norwegian University of Science and Technology under supervision of Associate Professor Gunnar Tufte.

The thesis counts for 30 credits and is the continuation of a 15-credit specialization project conducted autumn 2014. It concludes a 5-year master of science study in Computer Science.

I would like to personally thank Gunnar Tufte for his invaluable inspiration and support, and Odd Rune Strømmen Lykkebø who stepped in during his brief absence.

Per Thomas Lundal 2014 June 14th

## Contents

| mme        | endrag i                                                                                                                                                                                             |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Abstract   |                                                                                                                                                                                                      |  |  |  |  |

| reface     | v                                                                                                                                                                                                    |  |  |  |  |

| onten      | ts vii                                                                                                                                                                                               |  |  |  |  |

| st of      | Figures xi                                                                                                                                                                                           |  |  |  |  |

| st of      | Tables     xiii                                                                                                                                                                                      |  |  |  |  |

|            | oduction 1                                                                                                                                                                                           |  |  |  |  |

| 1.1        | Outline                                                                                                                                                                                              |  |  |  |  |

|            | kground 5<br>Evolution                                                                                                                                                                               |  |  |  |  |

|            | 2.1.1 Genetic Algorithms                                                                                                                                                                             |  |  |  |  |

| 2.2        | Development72.2.1Lindenmayer Systems7                                                                                                                                                                |  |  |  |  |

| 2.3        | Cellular Automata82.3.1Neighborhoods10                                                                                                                                                               |  |  |  |  |

|            | 2.3.2 Complexity Classes                                                                                                                                                                             |  |  |  |  |

| 2.4        | 2.3.3 Evolution and Development in CAs                                                                                                                                                               |  |  |  |  |

| 25         | 2.4.1       Sblock       12         PCI Express       13                                                                                                                                             |  |  |  |  |

| 2.5<br>2.6 | Related Work                                                                                                                                                                                         |  |  |  |  |

|            | 2.6.1       CAM-8       15         2.6.2       CAM-Brain Machine       16                                                                                                                            |  |  |  |  |

|            | 2.6.3         BioWall         16                                                                                                                                                                     |  |  |  |  |

|            | vious Work         19           Djupdal         19                                                                                                                                                   |  |  |  |  |

| 3.2<br>3.3 | Aamodt                                                                                                                                                                                               |  |  |  |  |

|            | bstrac         reface         onten         st of         Intr         1.1         Bacl         2.1         2.2         2.3         2.4         2.5         2.6         Prev         3.1         3.2 |  |  |  |  |

|          | 3.4        | Issues           |                                         | 23              |

|----------|------------|------------------|-----------------------------------------|-----------------|

| 4        | Dev        | elopme           | ent Platform                            | 25              |

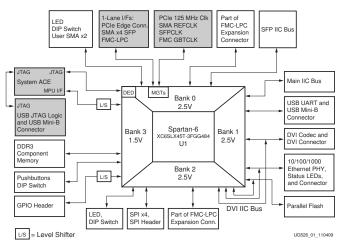

|          | 4.1        | Sparta           | n-6 SP605 Evaluation Platform           | 25              |

|          | 4.2        |                  |                                         | 26              |

|          | 4.3        | Softwa           | $\operatorname{re}\operatorname{Setup}$ | 27              |

| F        | Imp        | lomont           | ration                                  | 29              |

| <b>5</b> | 5.1        | lement<br>Conors |                                         | <b>29</b><br>31 |

|          | 0.1        | 5.1.1            | 1                                       | $\frac{31}{31}$ |

|          |            | 5.1.1<br>5.1.2   |                                         | $\frac{31}{32}$ |

|          |            | 5.1.2<br>5.1.3   | 1 0                                     | 32<br>32        |

|          | 5.2        |                  |                                         | э∠<br>33        |

|          | 0.2        | 5.2.1            |                                         | 33<br>34        |

|          |            |                  | 1 1                                     |                 |

|          |            | 5.2.2            | 1 0                                     | 34<br>25        |

|          |            | 5.2.3            | 0                                       | 35<br>25        |

|          | 50         | 5.2.4            | 1                                       | 35              |

|          | 5.3        |                  |                                         | 36              |

|          |            | 5.3.1            |                                         | 36              |

|          | <b>.</b> . | 5.3.2            |                                         | 36              |

|          | 5.4        |                  |                                         | 37              |

|          | 5.5        | Contro           |                                         | 38              |

|          |            | 5.5.1            |                                         | 39              |

|          |            | 5.5.2            |                                         | 39              |

|          |            | 5.5.3            |                                         | 39              |

|          |            | 5.5.4            |                                         | 39              |

|          |            | 5.5.5            |                                         | 40              |

|          |            | 5.5.6            | Rule Numbers Reader                     | 40              |

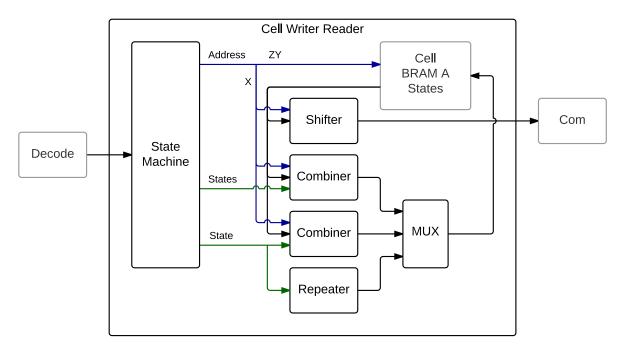

|          |            | 5.5.7            | Cell Writer Reader                      | 40              |

|          | 5.6        | Cell St          | orage                                   | 42              |

|          | 5.7        | Develo           | pment                                   | 43              |

|          |            | 5.7.1            | Cell Fetcher                            | 43              |

|          |            | 5.7.2            | Rule Fetcher                            | 45              |

|          |            | 5.7.3            | Rule Testers                            | 46              |

|          |            | 5.7.4            | Hit Processors                          | 46              |

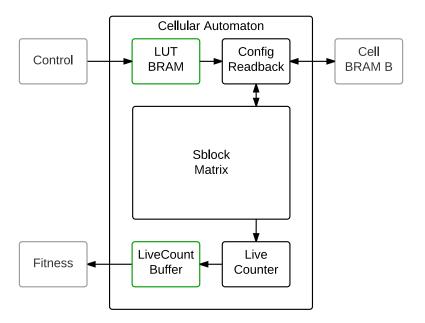

|          | 5.8        | Cellula          | r Automaton                             | 46              |

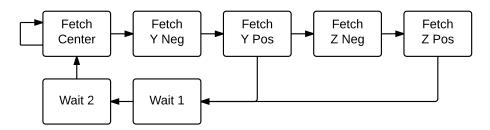

|          |            | 5.8.1            | State Machine                           | 47              |

|          |            | 5.8.2            | Sblock Matrix                           | 48              |

|          |            | 5.8.3            |                                         | 48              |

|          | 5.9        | Fitness          | 3                                       | 48              |

|          |            | 5.9.1            |                                         | 49              |

|          |            | 5.9.2            |                                         | 49              |

|          | 5.10       | Softwa           |                                         | 51              |

|          | 0.10       |                  |                                         | 51              |

|          |            |                  |                                         | 52              |

|          |            |                  | <b>T C C C C C C C C C C</b>            |                 |

|              |                  | 5.10.3         Communication         5.10.4         Compilation         5.10.4         5.10.4         Compilation         5.10.4         Compilation< |            |  |  |  |  |  |  |  |  |

|--------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|--|--|--|--|

| 6            | Ver              | ication 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5          |  |  |  |  |  |  |  |  |

|              | 6.1              | Functional Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55         |  |  |  |  |  |  |  |  |

|              | 0.1              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55         |  |  |  |  |  |  |  |  |

|              | 6.2              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 56         |  |  |  |  |  |  |  |  |

| 7            | Disc             | ussion 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59         |  |  |  |  |  |  |  |  |

|              | 7.1              | Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 59         |  |  |  |  |  |  |  |  |

|              |                  | 7.1.1 Communication $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60         |  |  |  |  |  |  |  |  |

|              |                  | 7.1.2 Cellular Automaton $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51         |  |  |  |  |  |  |  |  |

|              | 7.2              | Resource Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 52         |  |  |  |  |  |  |  |  |

|              | 7.3              | Challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53         |  |  |  |  |  |  |  |  |

|              | 7.4              | Future work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53         |  |  |  |  |  |  |  |  |

|              | 7.5              | Warnings $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64         |  |  |  |  |  |  |  |  |

| 8            | Conclusion 6     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |  |  |  |  |  |  |  |  |

| Bi           | bliog            | aphy 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57         |  |  |  |  |  |  |  |  |

| $\mathbf{A}$ | Test             | Descriptions 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | '1         |  |  |  |  |  |  |  |  |

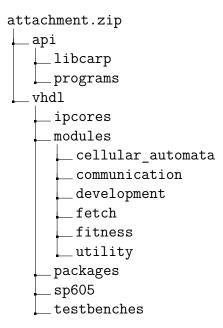

| В            | B Attached Files |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |  |  |  |  |  |  |  |  |

| С            | Inst             | uction Set Architecture 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>'</b> 9 |  |  |  |  |  |  |  |  |

| D            | Spe              | ialization Project Report 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5          |  |  |  |  |  |  |  |  |

#### CONTENTS

# List of Figures

| 2.1  | POE model                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------|

| 2.2  | Genetic algorithm                                                                                           |

| 2.3  | Development                                                                                                 |

| 2.4  | Dragon curve                                                                                                |

| 2.5  | Computing principles                                                                                        |

| 2.6  | von Neumann neighborhood                                                                                    |

| 2.7  | Complexity classes                                                                                          |

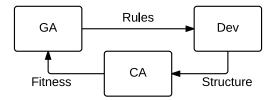

| 2.8  | CA system with evolution and development                                                                    |

| 2.9  | FPGA 13                                                                                                     |

| 2.10 | Sblock                                                                                                      |

| 2.11 | PCI Express structure                                                                                       |

| 2.12 | CAM-8 system diagram                                                                                        |

| 2.13 | BioWall                                                                                                     |

| 0.1  | Contraction 10                                                                                              |

| 3.1  | System design                                                                                               |

| 3.2  | Djupdal's hardware design                                                                                   |

| 3.3  | Aamodt's hardware design    21      Støvneng's hardware design    22                                        |

| 3.4  | Støvneng's hardware design                                                                                  |

| 4.1  | SP605                                                                                                       |

| 4.2  | Hardware setup                                                                                              |

|      | -                                                                                                           |

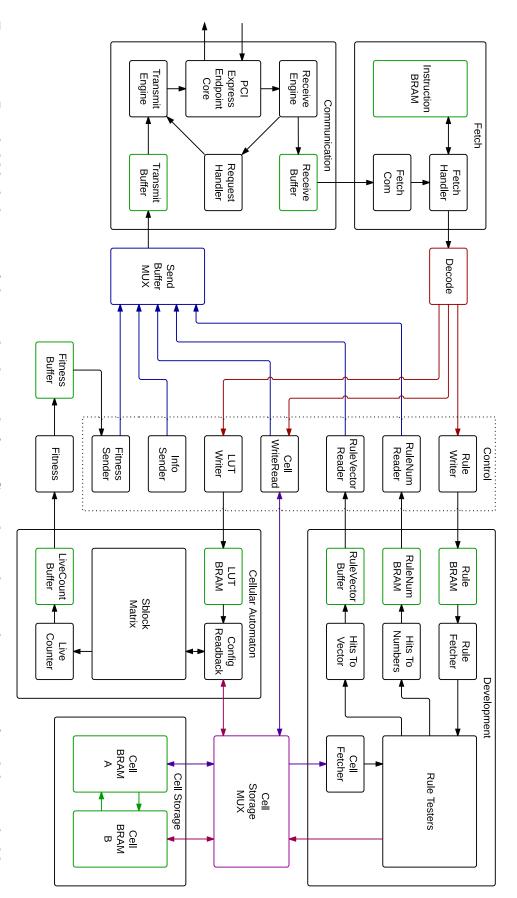

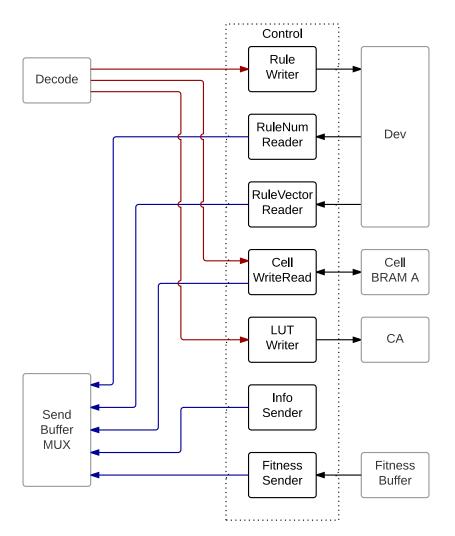

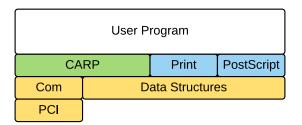

| 5.1  | High-level system diagram                                                                                   |

| 5.2  | Detailed system diagram                                                                                     |

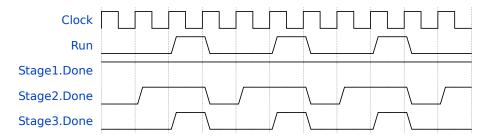

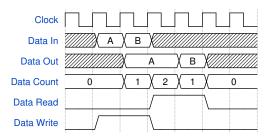

| 5.3  | Pipeline wave diagram                                                                                       |

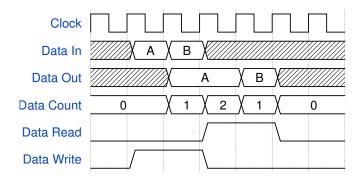

| 5.4  | FIFO buffer wave diagram                                                                                    |

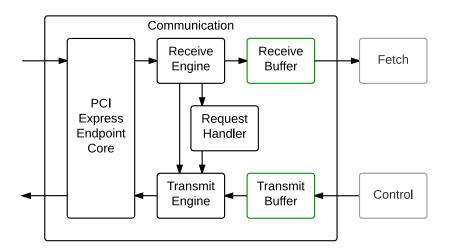

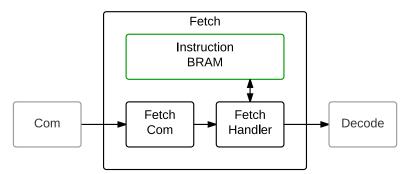

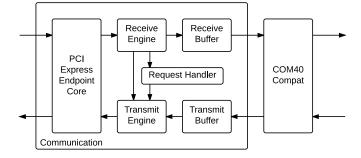

| 5.5  | Communication module                                                                                        |

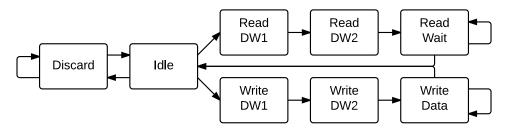

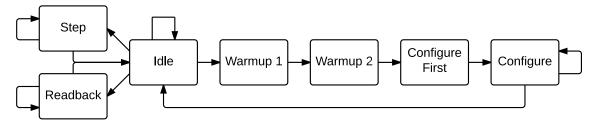

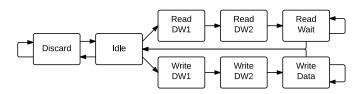

| 5.6  | Reception Engine state machine                                                                              |

| 5.7  | Transmission Engine state machine                                                                           |

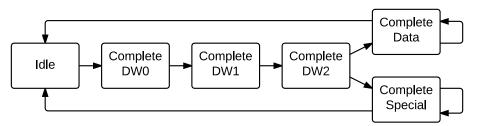

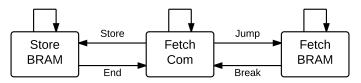

| 5.8  | Fetch module                                                                                                |

| 5.9  | Fetch Handler state machine                                                                                 |

| 5.10 | Control modules                                                                                             |

| 5.11 | Cell Writer Reader                                                                                          |

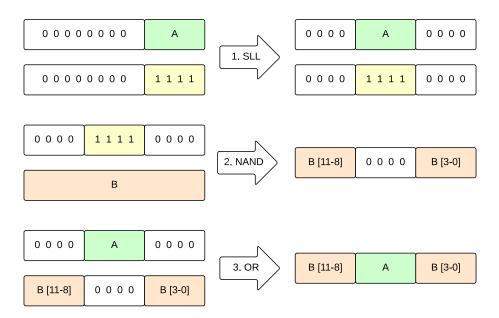

|      | Combiner operation $\ldots \ldots 41$ |

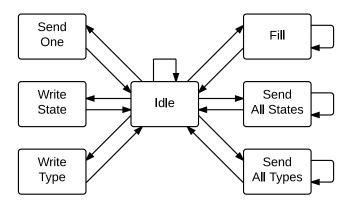

| 5.13 | Cell Writer Reader state machine                                                                            |

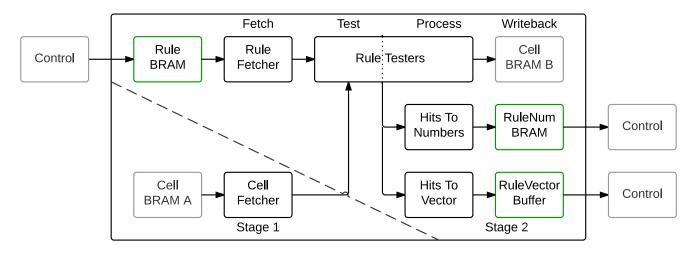

| 5.14 | Development module               |   |   |  |   |   |       |   |   |   |   |   |   |   | 43 |

|------|----------------------------------|---|---|--|---|---|-------|---|---|---|---|---|---|---|----|

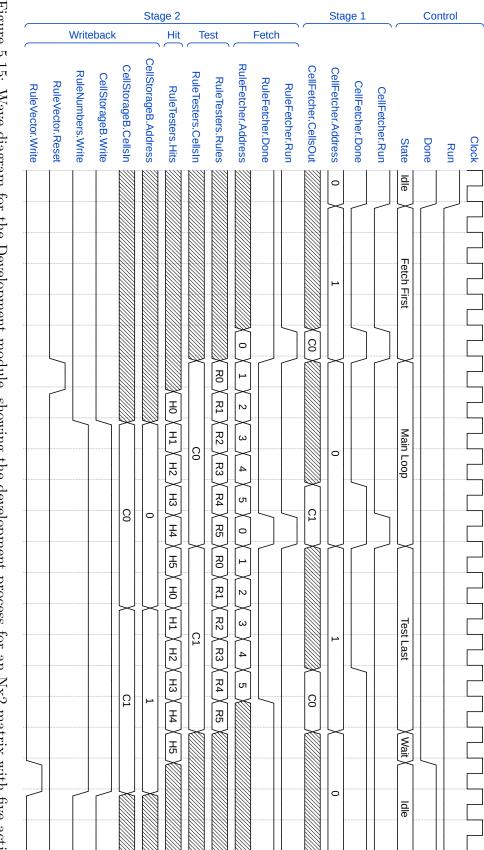

| 5.15 | Development module wave diagram  |   |   |  |   |   |       |   |   |   |   |   |   |   | 44 |

| 5.16 | Development module state machine |   |   |  |   |   |       |   |   |   |   |   |   |   | 45 |

| 5.17 | Cell Fetcher state machine       |   |   |  |   |   |       |   |   |   |   |   |   |   | 45 |

| 5.18 | CA module                        |   |   |  |   |   |       |   |   |   |   |   |   |   | 47 |

| 5.19 | CA module state machine          |   |   |  |   |   |       |   |   |   |   |   |   |   | 47 |

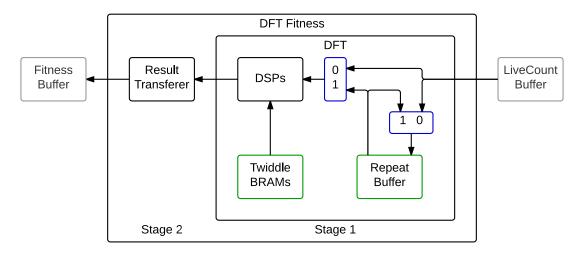

| 5.20 | DFT Fitness                      |   |   |  |   |   |       |   |   |   |   |   |   |   | 50 |

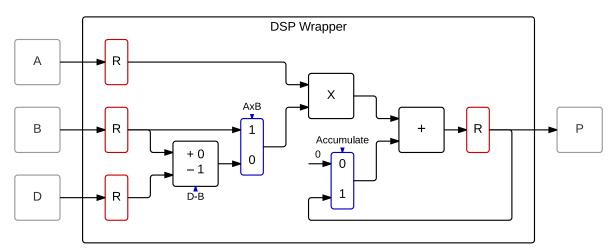

| 5.21 | DSP Wrapper                      |   |   |  |   |   |       |   |   |   |   |   |   |   | 50 |

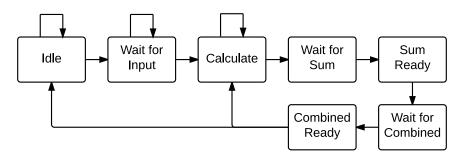

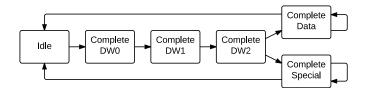

| 5.22 | DFT state machine                |   |   |  |   |   |       |   |   |   |   |   |   |   | 51 |

| 5.23 | API                              | • | • |  | • | • | <br>• | • | • | • |   | • | • | • | 51 |

| 6.1  | Replicator                       |   | • |  | • | • |       | • | • | • | • | • | • | • | 58 |

| 7.1  | Example program                  |   |   |  |   |   |       |   |   |   |   |   |   |   | 61 |

| 7.2  | Test program                     |   |   |  |   |   |       |   |   |   |   |   |   |   |    |

# List of Tables

| 3.1 | Issues                                                  | 3 |

|-----|---------------------------------------------------------|---|

|     | Parameters.    3      Special requests    3             |   |

| 6.1 | DFT error                                               | 6 |

|     | Communication performance    6      Resource usage    6 |   |

### Chapter 1

### Introduction

It is predicted that conventional CPU architectures will be unable to continue to scale in about a decade [8]. Many engineers are therefore investigating entirely different technologies in hope of finding viable alternatives. Some have looked towards nature; at biological organisms whose complexities far outweigh what humans have so far been able to engineer. Additionally, biological systems exhibit a wide range of characteristics that could possibly revolutionize computing, such as reproduction, learning, adaption, massive parallelism, graceful degradation, self-assembly and self-repair.

This has formed the field of bio-inspired computation, where the principles of nature in the form of artificial evolution, development and learning are used in the creation of computer systems. Some focus on mimicking the structure of the human brain, in the form of artificial neural networks, to create robot controllers [5]. Others focus on the emergent behaviors from thousands or millions of individual cells in Cellular Automata (CAs).

Bio-inspired computing has been an area of research at NTNU for more than a decade. In 2002, NTNU invested in dedicated FPGA hardware for the purpose of creating a platform for experimentation with CAs in combination with artificial evolution and development.

The initial work was done by Djupdal, and then extended by Aamodt shortly after. The CA was implemented as a matrix of sblocks, a form of reprogrammable CA cells, connected to a development unit capable of simulating cell growth and change. The hardware platform was connected to and controlled by a computer over a PCI connection.

A general use-case for the platform is to have the computer run a Genetic Algorithm (GA), where the genotype represents the development rules and initial CA state. Development is then used to create a phenotype in the form of a CA structure, which can be used for computation and to produce a fitness value. The fitness value is then fed back into the GA until an acceptably good solution is found.

In expectation of new hardware with a larger FPGA and faster PCI Express connection, Støvneng refurbished the design in 2014. He took advantage of the added resources to greatly improve the performance of the platform, giving a speedup of 4 or more for many operations. Additionally, he extended the CA into 3D and added a Discrete Fourier Transform (DFT). However, since the hardware did not arrive in time, the new design was only tested in simulation and the communication interface was not upgraded.

The task of the specialization project leading up to this thesis was to finish the extended platform by implementing a new PCI Express communication module, and to verify the platform's functionality in hardware. The verification process uncovered many issues, some of which made the platform unusable, and others which made debugging and fixing very difficult. This led to the decision of revising and rebuilding the entire platform from scratch in this thesis.

#### 1.1 Outline

The thesis is organized as follows:

- Chapter 2 Theoretical background, technology and related work. This chapter gives an overview of the relevant research that this thesis is based on and the technology which is used.

- Chapter 3 Previous designs and implementations. This chapter states a brief history of the platform that this thesis builds on and the main issues that needs improvement.

- Chapter 4 Development platform and setup. This chapter describes the hardware and software systems used in this thesis and their setups.

- Chapter 5 Implementation details. This chapter provides in-depth descriptions of all parts of the rebuilt and enhanced platform.

- Chapter 6 System verification. This chapter asserts the functionality of the platform through tests and an example program.

- Chapter 7 Performance, challenges and future work. This chapter analyzes the system's performance, discusses difficulties and compromises during development, and mentions possible improvements.

- Chapter 8 Concluding remarks. The final chapter concludes this paper by reviewing the new platform, its performance and its potential for future applications.

- Appendix A Functional tests. This appendix briefly describes the test programs that together provide test coverage of all instructions.

- Appendix B Attachment index. This appendix lists the attached files comprising the hardware design and software API.

- Appendix C Instruction Set Architecture. This appendix provides a complete specification of all instructions, the rule format and the LUT format.

- Appendix D Specialization project. This appendix holds the paper that led up to this thesis, in which a PCI Express-based communication module is implemented and integrated into the previous design.

CHAPTER 1. INTRODUCTION

### Chapter 2

### Background

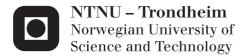

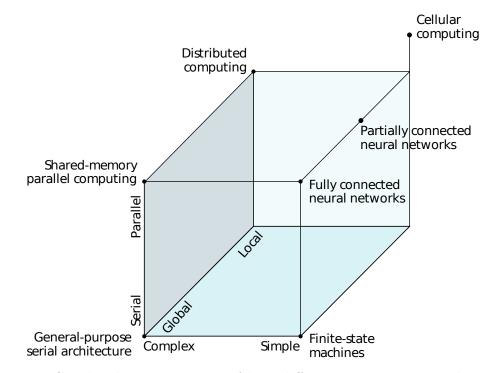

The field of bio-inspired computing encompass a wide variety of technologies that take advantage of different natural concepts. In [31], Sipper et al. partition these technologies into a space along three axes (illustrated in Figure 2.1):

- Phylogeny: Temporal adaption to the environment caused by mutation and reproduction. It is named after the evolution of the species.

- Ontogeny: Growth through cell division or equivalent methods. An example is a zygote ("mother cell") replicating to form a larger multi-cellular organism.

- Epigenesis: Adaptation through a lifetime of interactions with the environment. This can loosely be defined as learning.

Figure 2.1: The POE model for bio-inspired hardware.

This thesis focuses on the first two axes, phylogeny and ontogeny, in the form of artificial evolution and development. This chapter goes into details about the two concepts, some of the technologies that can take advantage of them and other technologies that are used in this thesis.

#### 2.1 Evolution

Evolution is the natural process that over time advances species by letting the fit survive to reproduce while the less fit perish. Essentially, each generation includes slight variations to gradually create a species that is more adapted to the environment by having the fit traits passed on to subsequent generations. In nature, this process effectively creates more fit solutions to the problem of life, which is to reproduce in a changing environment.

Similarly, artificial evolution can be used by computers to evolve solutions to computational problems instead of manually creating them, by the means of Evolutionary Algorithms (EAs) [20]. EAs can search millions of possible solutions, guided by their fitness scores, and find solutions that humans would never have imagined. In contrast to nature, where years usually pass between each generation, powerful computers can create hundreds of generations every second and find good solutions in relatively short time.

EAs have been successfully applied to many scientific tasks. For example, NASA has had great success with evolving antenna designs [21], and Floreano and Mondada have evolved robot controllers with homing navigation [9]. An interesting feature is that EAs can find ways to exploit hardware in ways that human designers cannot comprehend [34]. This can be due to complex parallel interactions, or usage of properties that are not fully understood [35].

#### 2.1.1 Genetic Algorithms

A very common type of EA is the Genetic Algorithm (GA) presented in [16]. It represents each solution as a genotype, a binary string used as a blueprint to create the solution itself, the phenotype. The genotype is comparable to nature's DNA, and it is this genetic material which is modified in the evolutionary process.

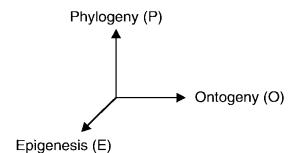

Figure 2.2: A genetic algorithm. The cycle is broken when the fitness is above a given threshold.

The GA process is shown in Figure 2.2 and works as follows: First, a base population with random genotypes is generated. Then, each phenotype is constructed and evaluated using a fitness function. If a solution has a fitness score above a set threshold, the process stops. Otherwise, a new population is created by selecting solutions with high fitness scores, crossing their genotypes, and mutating the results, before repeating the process.

#### 2.2 Development

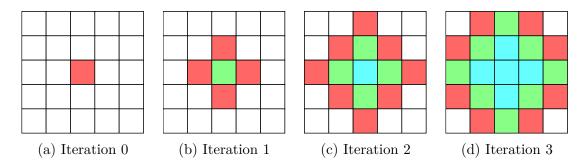

The process that transforms a genotype into a phenotype is called development, and can be regarded as a form of decompression algorithm [18]. In nature, this process is seen when a single cell transforms into a more complex multicellular organism, as visualized in Figure 2.3. Unlike with a pure decompression algorithm however, biological systems also use information about their environments to tailor themselves to them. This is known as plasticity.

Figure 2.3: Example of cells replicating and changing to develop a larger and more complex entity.

Development is needed because a complete specification of a complex organism requires much more information than practically can be stored; it is several orders of magnitude greater than that of one cell and its development rules. Plasticity and self-repairing abilities are merely bonuses, but have shown to be highly valuable properties. For the same reasons, artificial development is lucrative for building more complex computer systems that are also fault-tolerant and adaptable.

Development is never necessarily "finished"; it can continue during the entire lifespan of the system. Over time, a dynamical system tends to end up in a state of equilibrium, an attractor [19]. The attractor may be a single state, or a series of states that repeat to create a cycle. External interactions, for example suffering damage, will however likely cause the system to break from its current attractor in search for another. If the system ends up providing the same functionality, albeit possibly with a different structure, it is said to have self-repairing abilities, which is a lucrative property in the eyes of hardware engineers.

#### 2.2.1 Lindenmayer Systems

Perhaps the most known and widely used artificial development systems are Lindenmayer Systems (L-Systems). They were introduced by biologist and botanist Lindenmayer in 1968 to describe the growth of plants and fungi [24]. The L-System is a form of parallel generative grammar; starting with an axiom, a string is built by iteratively applying all the grammar rules in parallel. The string is a representation of the structure of the object; each character symbolizes a branch, twist, turn, stretch or other feature.

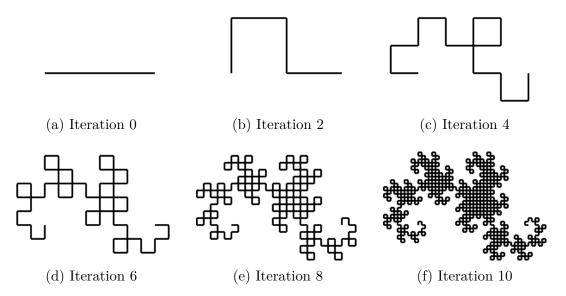

Figure 2.4: Heighway dragon curve generated with L-System using [3]. The starting string is FX and the rules are  $X \to XRYFR$  and  $Y \to LFXLY$  where F is forward, R is a right turn and L is a left turn.

In addition to plants, L-Systems are also suitable for generating other structures that grow and branch. Figure 2.4 shows how they can be used to generate fractals, specifically the dragon curve [10]. It is the pattern that emerges when a piece of paper is folded many times and then all folds opened to 90 degree angles. The corresponding L-System uses only two rules, and is a testament to how very simple development rules can create outstandingly complex shapes. L-Systems have also been applied to other tasks, such as music composition [25].

#### 2.3 Cellular Automata

A Cellular Automaton (CA) is a computational structure made up of vast numbers of very simple functional elements called cells that are arranged in a grid. Each cell contains a state and is connected to a handful of nearby cells to form neighborhoods. At given time intervals the cells then update their states based on transfer functions over the states in their neighborhoods.<sup>1</sup>

CAs are attempts to mimic the structures found in biological lifeforms, where complex results emerge from interactions between many simple cells. The key principles are massive parallelism, local interactions and simple computational units. As seen in Figure 2.5, this is the directly opposite paradigm to the general-purpose serial

<sup>&</sup>lt;sup>1</sup> CAs are specific cases of Random Boolean Networks [14].

architecture that is common in computers today. However, CAs have been shown to be Turing complete [4, 36], and can therefore perform any task.

Figure 2.5: Graphical representation of how different computing paradigms relate with regards to computing principles. (Reprinted from [30])

CAs are attractive due to their inherent robustness and scalability when paired with development. In the event of broken cells, signals can simply be rerouted, and to increase the performance, extra cells can be added and the program grown; local communication ensures that there are no bottlenecks. This greatly contrasts modern processors where a broken part normally renders the entire chip unusable, and adding more cores are of limited benefit due to the shared-memory architecture. Increasing the clock rate is no longer an option either, due to the fixed power budget.

A major challenge with CAs is programming. CAs compute by emergence using massive parallelism, while humans mostly solve problems serially [27]. This makes it near impossible for humans to construct programs, unless for very simple problems. Genetic Algorithms are therefore often used.

Other major challenges are the representation of input and parsing of output. Both arise due to the CA's distributed nature. For output, the Discrete Fourier Transform (DFT) over the number of cells with a given state appears promising however [2].

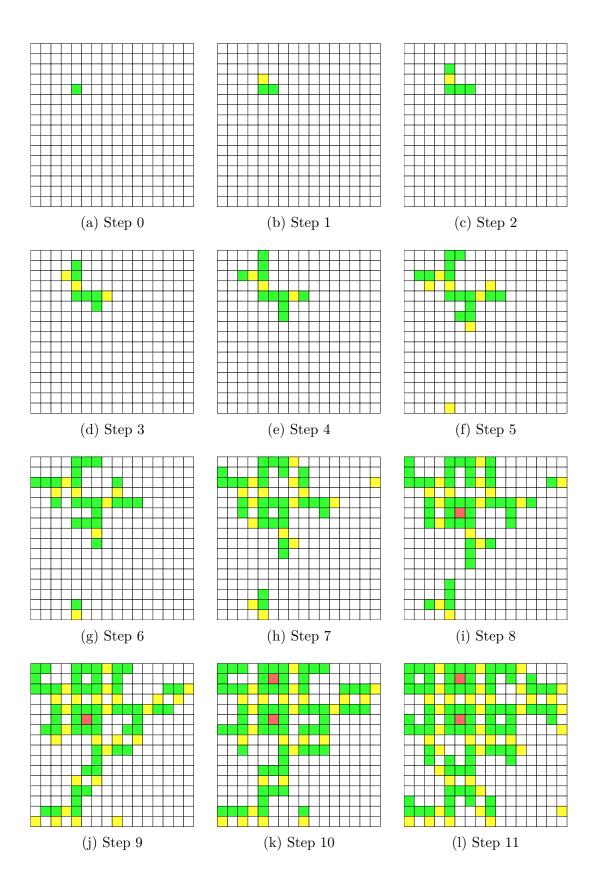

CAs have been also been used in various research. They have been environments for simulating lifeforms and creating replicating machines [36]. A very popular life simulator is Conway's Game of Life [11].

There are many variations of CAs, which are discussed in great detail in [30]. Following is a brief summary: Cell states can have discrete or continuous values. The transfer function can be represented by exhaustive enumeration or a parameterized expression. The cells may be uniform by having the same transfer function, or nonuniform. Cell updates can be synchronous or asynchronous, and in the latter case the CA can be either deterministic or nondeterministic depending on the order in which cells update. The CA may be fully specified by direct programming or adaptively evolved using a EAs. Finally, there are numerous schemes that can be used to connect cells together to form neighborhoods.

In this thesis, only a specific form of CA is used: Discrete, exhaustively enumerated, non-uniform, synchronous and deterministic. It is possible to use direct programming, but there are systems in place for adaptive evolution.

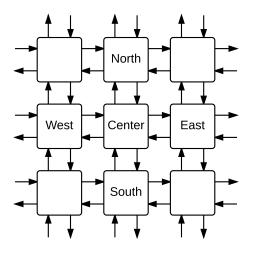

#### 2.3.1 Neighborhoods

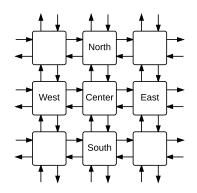

An important property of CAs is how cells are connected to form neighborhoods, as this defines what data will be available for the transfer functions and therefore changes the way data flow through the machine. It is common to connect directly adjacent cells, and sometimes those diagonally adjacent. Cells do not have to be part of their own neighborhoods, but it is common. The von Neumann neighborhood shown in Figure 2.6 is commonly used for 2D CAs, and is also used by the design in this thesis. It includes the directly adjacent cells; north, south, east and west; and the cell itself.

Figure 2.6: The von Neumann neighborhood in a 2D CA. The cell states are shared with all directly adjacent cells.

The von Neumann neighborhood is easily extendable to 3D by adding the cells directly above and below to the neighborhood. The extra dimension allow more complex signal routing since the signals can cross over or under each other, which hopefully allows more complex computation. It should however be possible to achieve the same complexity in fewer dimensions by increasing the neighborhood size, but that would likely require much more advanced transfer functions.

#### 2.3.2 Complexity Classes

Wolfram observed that some CAs developed complex pattern while others decayed into uniformity or chaos. He therefore developed a set of four classes to group them based on their emergent behavior [37]:

- Class 1 Uniform: The CA quickly results in a homogeneous state, regardless of initial condition. It lacks both the means to store data and perform computation.

- Class 2 Repetitive: The CA develops both periodic and static data structures. However, after a number of cycles the states begin to repeat. This makes complex computation impossible.

- Class 3 Chaotic: The CA is not held back by repetition as with class 2, but the patterns are so chaotic that it is unable to support data structures.

- Class 4 Complex: The CA supports complex data structures and has no discernible repetition. It should be capable of universal computation.

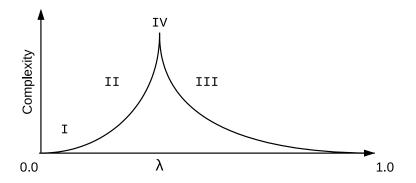

Figure 2.7: The location of Wolfram's complexity classes in  $\lambda$  space. (Adapted reprint from [23])

Langton attempted to connect Wolfram's classes to transfer function complexity [23]. For this he used a measure called  $\lambda$ , which essentially determines the inverse ratio of rules that cause a cell to transition into any given state. This means that all transitions are to a given state if  $\lambda = 0.0$ , while there are no transitions to any state if  $\lambda = 1.0$ . His findings, displayed in Figure 2.7, show that class 4 resides in a phase transition between the order of class 2 and the chaos of class 3. This is known as "The Edge of Chaos".

#### 2.3.3 Evolution and Development in CAs

The problem with using EAs to program CAs is that the search spaces are vast, even for the simplest binary CAs  $(2^{Neighborhood \cdot Cells} \text{ configurations}^2)$ . However, by

adding development to the process, the search spaces can be dramatically reduced to manageable sizes while gaining other benefits such as scalability and robustness.

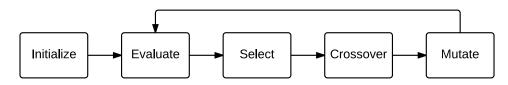

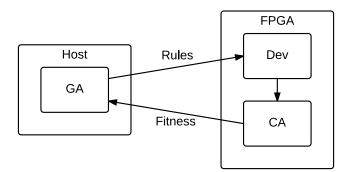

Figure 2.8: CA system with evolution and development.

The essence of the process is illustrated in Figure 2.8: The GA defines development rules. Development is then used to define a CA structure. Finally, the CA is executed to produce a fitness score that is fed back into the GA.

#### 2.4 FPGA

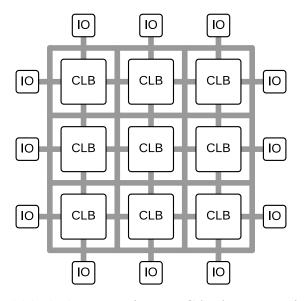

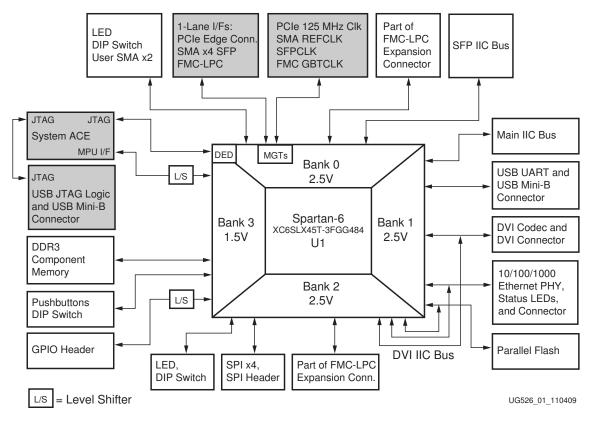

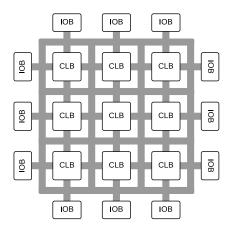

A Field Programmable Gate Array (FPGA) is a type of reconfigurable hardware. It can implement any desired logical operation by configuring and connecting a number of lookup tables (LUTs) and flip-flop registers (FFs). FPGAs can also contain dedicated blocks for addition, multiplication, storage, and other functionality. The resources are grouped into configurable logic blocks (CLBs), which through a network of interconnects can be connected to each other or input/output (I/O) pins. An example of this structure is shown in Figure 2.9. Note that modern FPGAs consists of thousands of CLBs and hundreds of I/O pins [40].

FPGAs have been the subject of bio-inspired research due to their reconfigurability, and several researchers have been successful in using EAs to evolve working electronic circuits [22, 34]. However, the resulting circuits have often ended up using intrinsic properties of the silicon and been very sensitive to environmental changes. A problem with using modern FPGAs is that some configuration bit strings can destroy the FPGA by creating short-circuits [38, 42]. This means that the bit strings can not be used directly as the genotype without complicated tests to discard those that are dangerous.

The regular structure of an FPGA makes it well suited as the basis for implementing CAs however, especially 2D ones.

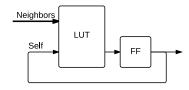

#### 2.4.1 Sblock

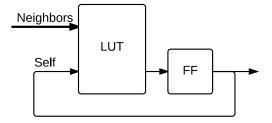

The sblock was introduced as part of a new EA-friendly FPGA architecture in [17]. The architecture is a non-uniform CA with a von Neumann neighborhood, where

$<sup>^{2}</sup>$  The number of possible configurations for a relatively small 4x4x4 CA dwarfs the estimated number of particles in the universe.

Figure 2.9: High-level block diagram of an FPGA. An array of CLBs and I/O pins are connected by a network of interconnects.

the transfer function of each cell is independently configurable at run-time. The cells, known as sblocks, are very simple structures; they consist of a configurable LUT and a FF, as shown in Figure 2.10.

Figure 2.10: Detailed block diagram of an sblock. The LUT can be reconfigured on-the-fly to implement any logical function.

The greatest benefit of using sblocks in research using EAs is that there is no risk of damage or exploitation of intrinsic properties in the silicon. Additionally, the simple structure and hardwired signal routing allows for very efficient area usage. The likelihood of a mass-produced sblock-FPGA arriving on the market in the near future is slim. However, it is possible to implement it virtually within another FPGA, as is done in this thesis.

#### 2.5 PCI Express

The PCI Express interface was designed to tackle the rising troubles with clocked parallel buses like PCI. The problem with such buses is that the clock speed can not be increased beyond a given threshold, as the slightly different lengths of the wires causes data to arrive at slightly different times. Reducing the clock period to less than the variation in arrival time means the data will become corrupted. This problem is exacerbated with larger bus sizes.

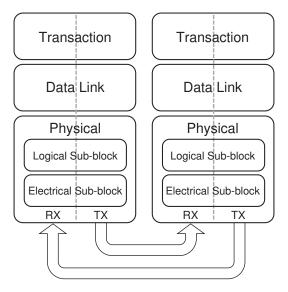

PCI Express is therefore based on serial communication over differential pairs (lanes<sup>3</sup>) without the need for a reference clock [29]. This allows an extremely fast clock speed compared to a parallel bus, and much greater bandwidth in total. PCI Express consists of three layers; the physical layer, the data link layer and the transaction layer, structured as shown in Figure 2.11.

Figure 2.11: High-level diagram showing the layered structure of PCI Express. (Reprinted from [29])

The transaction layer's primary responsibility is the creation and parsing of transaction layer packets (TLPs). TLPs are used to trigger events or start various transactions, most commonly to initiate read and write requests<sup>4</sup>. Most requests entail the return of a completion TLP containing the requested data or other information. TLPs consists of multiple 32-bit double words (DW), where the first is a common header describing the type of packet.

The data link layer ensures integrity by adding error detection codes to outgoing TLPs and performing error detection and correction on incoming TLPs. It is also responsible for retransmission if corruption occurs.

The physical layer is responsible for serialization and deserialization of the data stream. Each byte is padded with two extra bits (8b/10b encoding) to allow clock recovery.

<sup>&</sup>lt;sup>3</sup> PCI Express operates in full duplex mode, which means that each lane has an independent differential pair in each direction. 1, 2, 4, 8, 16 or 32 lanes are supported, but data is striped and thus still transmitted serially.

<sup>&</sup>lt;sup>4</sup> Read and write requests are directed at one of up to six base address registers (BARs). They represent internal memory areas that can be anywhere from a few bytes to several gigabytes in size.

#### 2.6 Related Work

This section describes work performed by others, which is related to that performed in this thesis but not directly applicable to it.

#### 2.6.1 CAM-8

The Information Mechanics Group at MIT Laboratory for Computer Science has had a focus the question "How can computation and computers best be adapted to the constraints and opportunities afforded by microscopic physics?" This has led to more than a decade of study of CAs, as their fine-grained computation with local interconnectivity are particularly good candidates for micro-physical efficiency. To this end, they have created CA Machines (CAMs) that aim to use common computer parts in smart arrangements to provide CA computation performance akin to modern supercomputers. [26] describes their eighth iteration, known as the CAM-8.

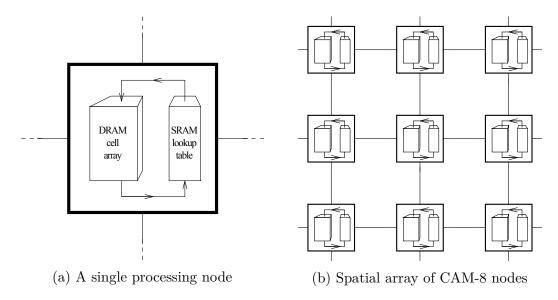

Figure 2.12: CAM-8 system diagram. (Reprinted from [26])

The CAM-8 implements a discrete, exhaustively enumerated, uniform, and synchronous 3D CA split over multiple nodes that run in parallel. Any number of nodes can be connected to form a CA of desired size, and an 8-module prototype showed to be on par with regular supercomputer simulations. As illustrated in Figure 2.12, each node contains DRAM that potentially holds millions of cells and an SRAM that holds the LUT for the current program. Within each node, cells are updated in sequence, making it a semi-parallel machine. This is a trade-off that compromises performance for the benefit of massively increased CA size and the ability to use common hardware. For 1-bit cell states, the prototype is capable of  $3 \cdot 10^9$  cell updates per second and can fit up to  $5 \cdot 10^8$  cells.

#### 2.6.2 CAM-Brain Machine

In [5], de Garis et al. introduces the CAM-Brain Machine (CBM); an FPGA-based platform that implements a CA-based neural network that is evolved using a GA. It is part of de Garis' "Artificial Brain Project", which goal is to build an artificial brain with 1 billion neurons. The CBM is a stepping stone in the right direction, and allows the formation an artificial brain with nearly 75 million neurons in a CA of 843 million cells. It consists of up to 64640 modules, each containing 24x24x24 cells split over 72 FPGAs, of which 1152 cells can be neurons. Modules are evolved separately using the Collect and Distribute based neural network model from [13], and then connected by human design.

Brain building is still mostly in the "proof of concept" phase, so to attract attention to further research they designed a cute life-sized robot kitten that would be controlled by the CBM. The work to design and evolve it's brain architecture was expected to continue well into the 2000s, but was halted when the research institution went bankrupt in 2001 [15].

#### 2.6.3 BioWall

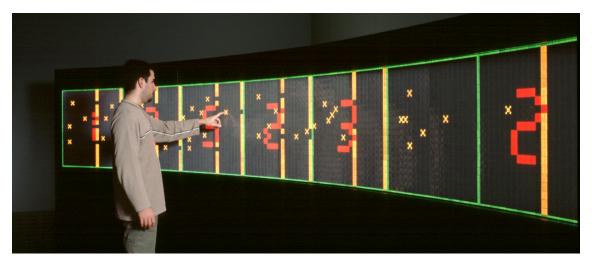

The Logic Systems Laboratory at the Swiss Federal Institute of Technology have been working on bio-inspired hardware systems for many years, mainly focusing on the ontogenetic axis through embryonics. [33] describes a machine whose purpose is to convey the principles of embryonics to the public through visual and tactile interactions. The machine, depicted in Figure 2.13, is named BioWall due to its bio-inspired nature and sheer size at 5.3x0.6x0.5 meters<sup>3</sup>.

Figure 2.13: The BioWall, running BioWatch. (Reprinted from [28])

The BioWall is made up of 3200 identical units which can be seen an artificial molecules that can be combined to form cells. Each unit consists of an FPGA, 64

LEDs and a touch sensor, allowing users to interact with the surface by touching it and receiving immediate response from the LED display.

The main application for the screen is the BioWatch, an organism capable of counting hours, minutes and seconds. It is used to demonstrate the growth and self-repair capabilities of the system. 20 x 25 molecules/units are arranged into cells, each responsible for one digit. Users can then touch molecules to disable them, forcing the cell to reroute its functionality to a neighboring molecule.

The BioWall's cellular structure is well suited for many other bio-inspired applications as well. Examples are 2D CAs such as the Game of Life [11], self-replicating structures and artificial neural networks.

CHAPTER 2. BACKGROUND

# Chapter 3 Previous Work

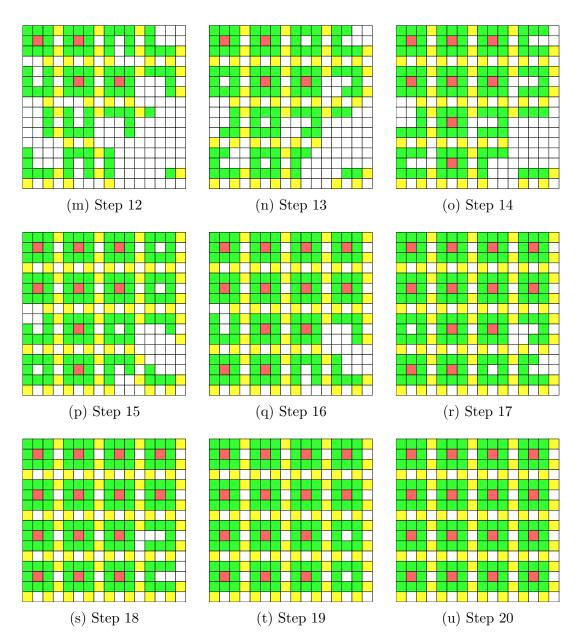

This thesis continues to build on the Cellular Automata Research Platform (CARP), which is the result of three previous master theses at NTNU. The original implementation was made by Djupdal in 2003. It was then extended with a range of various output methods by Aamodt in 2005. Finally, it was further extended and optimized in expectation of new hardware by Støvneng in 2014.

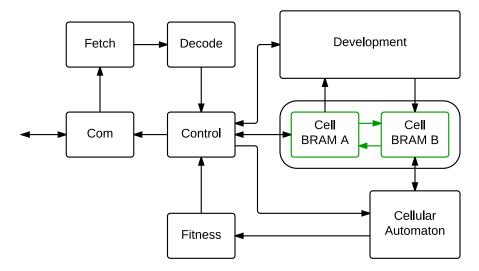

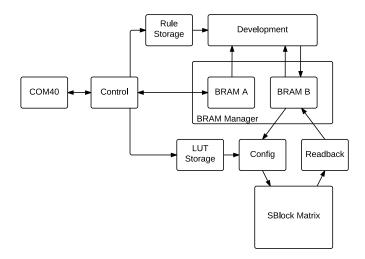

Figure 3.1: General system design.

The platform is more or less a "proof of principle" for how a CA can be combined with development and evolution to create a powerful bio-inspired system. The general system design, which is based on the setup in Section 2.3.3, is depicted in Figure 3.1: An FPGA implements the CA and development process while evolution is performed by a host computer.

#### 3.1 Djupdal

In 2002, NTNU invested in a CompactPCI computer with a NallaTech BenERA FPGA board to be used for research within the field of evolutionary hardware. The task of developing a platform for the system, based on a matrix of sblocks, fell to Djupdal [7].

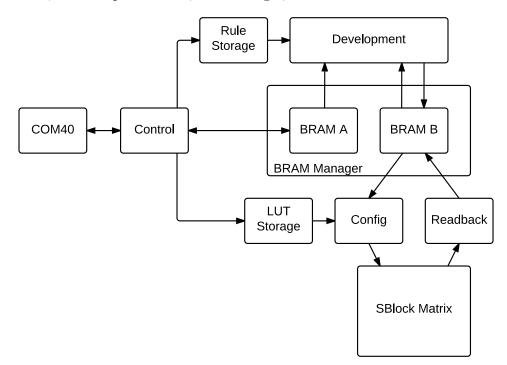

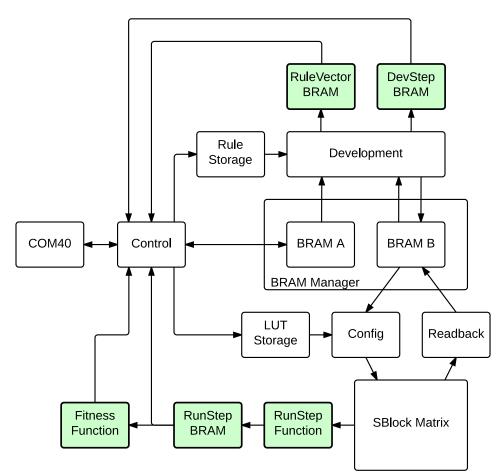

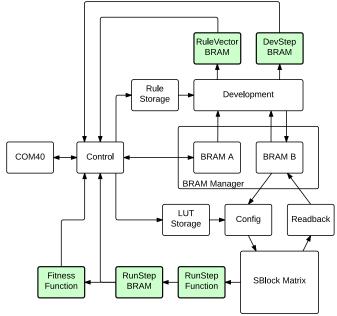

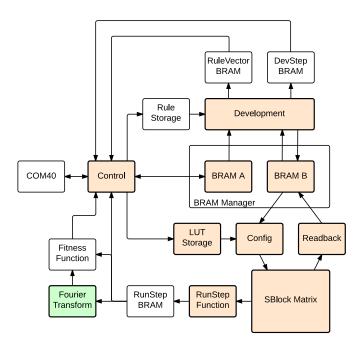

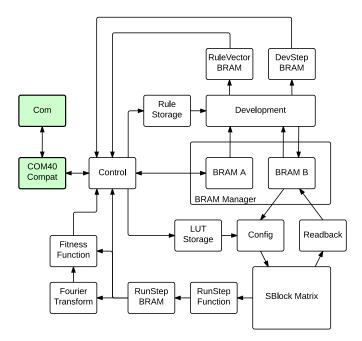

An overview of the resulting hardware platform is shown in Figure 3.2. It consists of the SBlock Matrix (SBM), Block RAM (BRAM) for storing the state and type of each cell, a development unit, control logic, and a PCI communication unit.

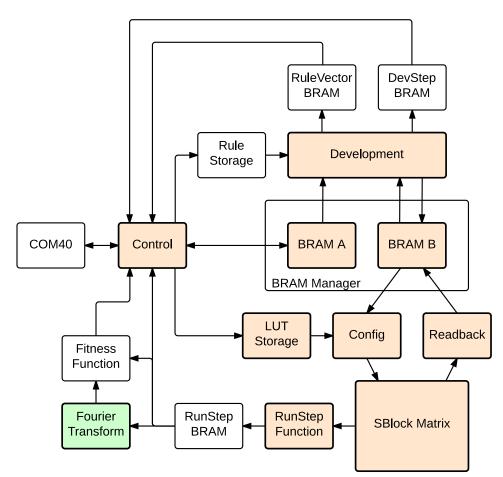

Figure 3.2: High-level block diagram of the hardware platform after Djupdal's original work.

The system is meant to be controlled by a computer running a genetic algorithm. A common flow of operation is to initialize the system with the genotype, develop it into its phenotype, step the SBM, and send the new states back to the computer. The computer then uses the newly received state data to calculate a fitness score.

The system is initialized by writing states and types to BRAM A, in addition to storing development rules and LUT conversion rules. Then development can be performed by reading cell types from BRAM A<sup>1</sup>, testing development rules, and writing the (possibly changed) types to BRAM B. The development unit tests 8 rules on 2 cells each cycle in raster order. Optionally, the BRAMs can be logically swapped and further development performed. The SBM can then be configured by translating the types in BRAM B into LUT entries according to the LUT conversion rules, before being stepped for a desired amount of cycles. Afterwards, the new states in the SBM can be read back into BRAM B, swapped into BRAM A, and sent to the computer.