# **Exploring Instruction Cache Analysis**

On Arm

# Stian Valentin Svedenborg

Master of Science in Physics and Mathematics

Submission date: September 2014

Supervisor: Harald Hanche-Olsen, MATH

Norwegian University of Science and Technology Department of Mathematical Sciences

#### Abstract

This thesis explores the challenges of implementing an instruction cache side-channel attack on an ARM platform. The information leakage through the instruction cache is formally discussed using information theoretic metrics. A successful PRIME+PROBE instruction cache side-channel attack against RSA is presented, recovering 967/1024 secret key bits by observing a single decryption using a synchronous spy process. Furthermore, an unsuccessful attempt is made at decoupling the spy from the victim. Finally, the current state of countermeasures against software based cache side-channel attacks are summarised.

# Contents

| 1 | Inti                 | roduction                               | 1               |

|---|----------------------|-----------------------------------------|-----------------|

|   | 1.1                  | Side-Channels                           | 1               |

|   |                      | 1.1.1 Micro-Architectural Side-Channels | 2               |

|   | 1.2                  | Thesis Statement                        | 5               |

|   | 1.3                  | Thesis Structure                        | 5               |

| 2 | Bac                  | ekground Material                       | 6               |

|   | 2.1                  | Cache Architecture                      | 6               |

|   | 2.2                  | The Instruction Cache                   | 8               |

|   | 2.3                  | The Spy Process                         | 11              |

|   | 2.4                  | Simultaneous Multi-Threading            | 11              |

|   | 2.5                  | Data Analysis                           | 13              |

|   |                      | 2.5.1 Vector Quantization               | 13              |

|   |                      | 2.5.2 Self-Organising Map               | 15              |

|   |                      | 2.5.3 Learning Vector Quantization      | 18              |

| 3 | The                  | eoretical Analysis of the Side-Channel  | 20              |

| J | 3.1                  | Model Assumptions and Definitions       | 20              |

|   | 3.2                  | Framework                               | $\frac{20}{22}$ |

|   | 0.2                  | 3.2.1 Attack Model                      | 22              |

|   |                      | 3.2.2 Information Theoretic Metrics     | $\frac{22}{24}$ |

|   |                      | 3.2.3 Conditional Entropy               | 25              |

|   | 3.3                  | Measuring the Information Leakage       | 26              |

|   | 3.4                  | Consequences of Theorem 1               | 28              |

|   |                      | •                                       |                 |

| 4 | $\operatorname{Pro}$ | of of Concept                           | 30              |

|   | 4.1                  | Summary of the Target Platform          | 31              |

|   |                      | 4.1.1 Timing on ARM                     | 32              |

|   | 4.2                  | Method                                  | 33              |

|   |                      | 4.2.1 Culling Dead Data                 | 34              |

|   | 43                   | Theoretical Analysis                    | 34              |

ii CONTENTS

|              | 4.4 | Practical Results                          | 42         |

|--------------|-----|--------------------------------------------|------------|

|              | 4.5 | Conclusion                                 | 42         |

| 5            | Syn | chronous Attack on RSA                     | 44         |

|              | 5.1 | Method                                     | 44         |

|              | 5.2 | Results and Discussion                     | 45         |

|              |     | 5.2.1 Formal Analysis                      | 45         |

|              |     | 5.2.2 Practical Results                    | 45         |

|              | 5.3 | Conclusion                                 | 49         |

| 6            | Att | empting an Asynchronous Attack             | 50         |

|              | 6.1 | Alterations to the Spy                     | 50         |

|              | 6.2 | Method                                     | 50         |

|              | 6.3 | Discussion of Results                      | 51         |

|              | 6.4 | Suggested Future Work                      | 52         |

|              | 6.5 | Alternate Asynchronous Attack              | 52         |

| 7            | Cou | intering I-Cache Analysis                  | <b>5</b> 3 |

|              | 7.1 | Software Transformations                   | 53         |

|              |     | 7.1.1 Avoiding Key-Dependent Control Paths | 53         |

|              |     | 7.1.2 Cache Conscious Layout               | 54         |

|              |     | 7.1.3 Cryptographic Obfuscation            | 54         |

|              |     | 7.1.4 Cache Flushing                       | 54         |

|              | 7.2 | Hardware Support                           | 55         |

|              |     | 7.2.1 Disable Caching                      | 55         |

|              |     | 7.2.2 Cache Partitioning                   | 55         |

|              |     | 7.2.3 Alternate Cache Architectures        | 56         |

| 8            | Con | nclusion                                   | 60         |

|              | 8.1 | Remaining Work                             | 60         |

|              | 8.2 | Acknowledgements                           | 61         |

| $\mathbf{A}$ | Usi | ng Performance Timing on Cortex A9         | 67         |

| В            | Ass | embly Code of The Spy                      | 69         |

| $\mathbf{C}$ | Mul | ltiply-Square Algorithm                    | 72         |

# List of Figures

| 2.1 | CPU Memory Layout                           | 7  |

|-----|---------------------------------------------|----|

| 2.2 | Example mapping of functions into I-cache   | 10 |

| 2.3 |                                             | 12 |

| 2.4 |                                             | 13 |

| 2.5 | Vector Quantization in 2-dimensions         | 14 |

| 2.6 | Illustration of a SOM training iteration    | 16 |

| 2.7 | Learning step of LVQ3                       | 18 |

| 3.1 | Key Recovery Attack                         | 23 |

| 4.1 | Illustrating Random Round Robin             | 32 |

| 4.2 | Proof of Concept: Cache set mean            | 36 |

| 4.3 | Proof of Concept: Cache set variance        | 36 |

| 4.4 | Proof of Concept: Histogram of measurements | 37 |

| 4.5 | Proof of Concept: PDF #1                    | 39 |

| 4.6 | Proof of Concept: PDF #2                    | 39 |

| 4.7 | Visualisation of timing data                | 43 |

| 5.1 | Synchronous attack: Cache set mean          | 46 |

| 5.2 | Synchronous attack: Cache set variance      | 46 |

| 5.3 |                                             | 47 |

| 5.4 | Synchronous attack: PDF $\#2$               | 47 |

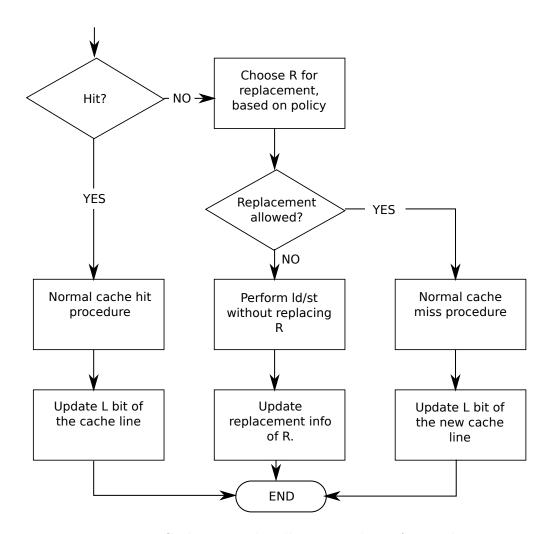

| 7.1 | Cache access handling procedure of PLcache  | 57 |

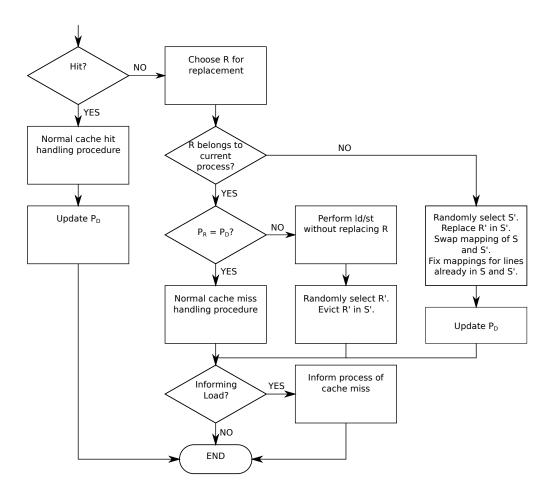

| 7.2 |                                             | 59 |

# Chapter 1

# Introduction

Information security has been a hot topic for as long as people have had secrets. Over time, techniques to share these secrets securely have evolved from simple riddles into rigorous mathematical systems with proofs and bounds on their security.

For many years there has been an unending struggle between the designers of crypto-systems and the people who want to break them. The crypto-community's goal is to always stay one step ahead of the attackers. They do so by actively breaking each others' systems, publishing the results and, most importantly, suggesting ways to defend against the attacks they find.

In more recent years, as crypto-systems become more robust against classical cryptanalysis, researchers have been looking at alternative ways to break and improve the security of crypto-systems by looking outside the pure mathematics of the system and into their actual implementation in real world usage, this is side-channel analysis.

# 1.1 Side-Channels

In cryptology, a side-channel is defined as unintentional leakage of information through a secondary channel. It is important to understand that side-channels can be completely separate from the mathematical security of the crypto-system. Even provably secure systems may be susceptible to side-channel analysis, owning to the fact that side-channel analysis usually attack the implementation of the system, and not only the mathematics upon which the system's security is based.

To give an example, most modern crypto-systems are implemented on computers. When executed on a computer, calculations take time, processors use power and memory changes state. This information may in turn be used to infer certain properties of the plain-text or even actual bits of the key of a crypto-system as it is run. Because of this, side-channels and related attacks have become a popular

topic of study over the last few decades.

One of the earlier results in side-channel analysis is the attack by Bleichenbacher in 1998 [13]. In this attack an arbitrary message of RSA Laboratories' PKCS#1 v1.5 is decrypted by the use of about 1000000 queries to a padding oracle. Bleichenbacher showed that this oracle could be created by observing how the receiver rejects a chosen cipher text. The attack works by observing the error-messages or even simply the delay of a decryption operation and uses this information to piece together the unencrypted message. Bleichenbacher's attack is a side-channel attack because it uses the details about how the decryption process is *implemented* to break the system.

Another example is a template attack on the Digital Signature Algorithm (DSA) by Howgrave and Smart [26]. In their article, they show that if it is possible to extract some bits of information about the nonce used by the DSA, it will be possible to extract the complete key within reasonable time. Howgrave's article does not show *how* one can extract such information, but more recent work has successfully implemented the attack using side-channel analysis [2].

#### 1.1.1 Micro-Architectural Side-Channels

A special class of side-channels is based on the micro-architecture of the computers on which the crypto-systems are run. These kinds of attacks analyse and exploit the way a computer's CPU, cache and other hardware work together to execute a crypto-system.

The main focus of this thesis will be on micro-architectural (MA) side-channel attacks that use the CPU's Level 1 instruction cache to gain information about the crypto-system, introduced below.

Many classes of MA side-channels are already known and this is an active field of study, see for instance [1, 2, 3, 15, 39]. The main classes of known microarchitectural side-channels are outlined below.

#### **Timing Analysis**

Pure timing attacks are among the simplest side-channels to understand. They work by measuring the time it takes to complete certain parts of a crypto-system, for which the computational time depends on the value of the secret input, usually the secret key. Kocher [27] showed how this information could be used to extract information from common implementations of RSA, the Diffie-Hellman key exchange protocol and the Digital Signature Standard, and the results may easily be adapted for other systems.

The existence of this side-channel forces implementers to ensure that the timing profiles of sensitive code are either fixed or sufficiently random.

#### **Data Cache Analysis**

Data cache attacks [9, 15] apply another strategy to infer information about the secret keys of a crypto-system, namely by observing how the CPU's data cache operates when the CPU is executing sensitive code.

Three kinds of data cache attacks exist: Trace-driven attacks rely on being able to determine whether any given memory access is a cache hit or cache miss<sup>1</sup> as the process is executing. This information may then be used to infer parts of the secret key based on, for instance, the table look-up patterns in some software implementations of AES, cf. [6].

Timing based data cache attacks rely on timing profiles instead of a cache trace. An attacker measures the total time of an operation and makes inferences as to how many cache hits or misses occur during the operation. This kind of attack is based on statistical inference and thus usually requires a much larger sample than a trace-driven attack, but it may in turn be used for remote attacks over a network. Actiquez et al. do exactly this in [9] where they use a data cache timing attack to remotely break a popular implementation of AES.

The third type of data cache attacks has been named access-driven and works by observing which cache sets (see section 2.1) the crypto-application uses, but does not care about the exact order as is done in a trace-driven attack. Armed with this knowledge, the attacker can infer which elements in the look-up tables are accessed by the cipher and from that information deduce parts of the private input.

#### **Branch Prediction Analysis**

Branch prediction analysis (BPA) [3, 4, 5] is another MA side-channel that was introduced by Aciiçmez et al. in 2006 and is based on the Branch Prediction Unit (BPU) of the processor. The BPU is a piece of hardware that tries to predict ahead of time where the execution of a program will branch off to. That is, whether a conditional statement will evaluate to true or false. This kind of prediction is needed because modern processors often use a technique called pipe-lining, which is outside the scope of this thesis. Let us suffice to say that a failure to correctly predict a branch will cause execution to stall while the pipeline recovers.

There are, as with cache attacks, several different attack strategies in BPA. The most noteworthy is Simple BPA (SBPA) [5] which attempts to discover the result of any and all branches in the attacked code. When it was introduced in late 2006, it was shown that SBPA could potentially be used to extract the complete private key from simple implementations of RSA in one iteration.

<sup>&</sup>lt;sup>1</sup>Cache architecture and terms like *cache hit* or *cache miss* are defined in section 2.1.

The attack in [5] utilises a spy process that continuously forces the BPU to expect that *no* branches will be taken. Thus, whenever a branch *is* taken the process stalls while the pipeline recovers. It is this delay that is measured and ultimately used to infer the private input.

#### **Instruction Cache Analysis**

The instruction cache (I-cache) side-channel is a natural continuation of SBPA, as both are concerned with analysing the execution flow of the crypto-application. However, whereas SBPA is concerned with the predictions of the BPU, I-cache attacks analyse how code is being loaded into the CPU's instruction cache.

Instruction cache attacks are based on a simple and powerful assumption: Any two distinct pieces of code will likely be loaded into different parts of the instruction cache. This assumption, which is often true in practice, allows us to follow the execution flow of the application as it is run.

In short, an I-cache attack utilises a spy-process that runs parallel to the attacked code on the same physical CPU core. This spy process monitors the instruction cache and notes whenever certain patterns of code are loaded into the cache. Based on this information it is possible to infer which code of the cryptoprocess was actually run. Together with a careful analysis of the crypto-process, this information may be used to piece together the secret key, or other sensitive information.

An important point to mention is that both SBPA and I-cache analysis attack code where execution flow is dependent on the input to the system. Unfortunately, this is often the case: Popular implementations of RSA, DSA and more have been known to have key-dependent flow, cf. [2, 4, 5, 8]. Any implementation of a system in which the execution flow is dependent on secret state may be vulnerable to these attacks.

#### **Shared Functional Units**

The final known micro-architectural side-channel arises due to the fact that on some systems, where two threads may run simultaneously on a single processor core<sup>2</sup>, the two threads must share the use of certain circuits. For instance, if simultaneous threads share a integer multiplier unit this may create a side-channel [7, 10]. As processor manufacturers make more optimizations in terms of area to concurrency, it is likely that we will see more side-channels of this kind.

An attack using these functional units will attempt to follow the instruction flow of the algorithm in much the same way as SBPA and I-cache analysis.

<sup>&</sup>lt;sup>2</sup>This is called Simultaneous Multi-Threading (SMT) and is discussed further in section 2.4.

# 1.2 Thesis Statement

In this master thesis we will try to build on the work by Aciçmez and others and attempt to implement an *instruction cache side-channel attack* on an ARM system. With exception to the work of Köpf et al. in [32], there has been little published research regarding micro-architectural side-channel analysis on ARM platforms, as much of the published work rely directly or indirectly on instructions and technology that is not as easily accessible on ARM platforms.

It is the intention of this thesis to explore the potency and difficulties of implementing an instruction cache side-channel on ARM platforms.

## 1.3 Thesis Structure

In chapter 2 we will cover the necessary background from previous work and give a short introduction to cache architecture.

Next, chapter 3 will cover the framework we will use to analyse the information leakage in the side-channels we will explore.

Chapters 4–6 will contain our main results, in which we delve into the practical analysis of several side-channels. Here, we present both positive results chapters 4 and 5 and a negative result in chapter 6.

Finally, in chapter 7 we recite the current state of countermeasures to protect against cache based side-channels before we summarise and conclude our results in chapter 8.

# Chapter 2

# **Background Material**

In this chapter we will explain in further detail what a cache is and how we are able to use the instruction cache (I-cache) as a side channel.

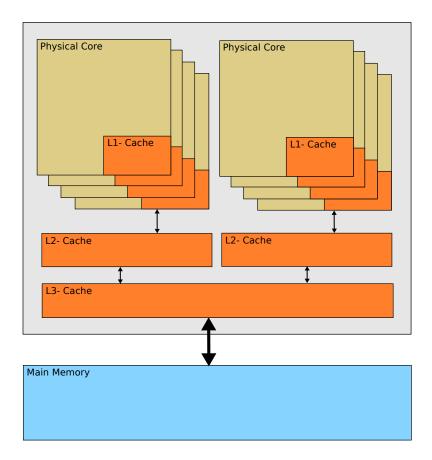

## 2.1 Cache Architecture

In computer architecture, a cache is a fast memory component that is located between the processor(s) (CPU) and the main memory (RAM). The need for a cache has arisen from an increasing inequality in the relative speed of processors and memory technology. In short, as processors have become faster and faster, memory technology has fallen behind. The solution to this problem has been to place a small portion of very fast (expensive) memory between the processor and the main memory to temporarily store frequently used data. This is the cache. A high level layout of CPU memory architecture is shown in figure 2.1.

On modern computers, there are generally 2–3 levels of cache. Level 1 (L1) is the smallest and fastest and usually split into the L1-I and L1-D cache<sup>1</sup>, one for instructions and one for data. Level 2 (L2) is slightly slower and larger and, on some platforms, Level 3 (L3) offers yet another layer that is bigger and slower.

The idea is that when the CPU needs to access the memory, it will first check if the required data is in the L1 cache, then check L2, then L3. If the data is not found on either level, it is loaded into the caches from the main memory. Thus, if the same data needs to be accessed again it will be retrieved much faster.

The exact architecture for the caches of processors are as diverse as the processor manufacturers and models themselves. There are, however, some similarities

<sup>&</sup>lt;sup>1</sup>What we are describing is often referred to as a *Harvard architecture*. It allows the CPU to access instructions and data along separate paths. In contrast, a *von Neumann architecture* has only one data path shared between instructions and data.

Figure 2.1: Typical CPU memory layout. Each physical core has its own L1 cache. A group of cores typically share an L2 cache. Multiple core groups share the L3 cache (if present).

and key terms which will be defined in this section. Most of the material in this section is adapted from [20].

**Definition 1.** The atomic amount of memory that may be loaded into the cache is called a *cache line*.

If you are to access a 32-bit integer that is not currently in the cache, the cache will load one or more cache lines such that all 4 bytes of the integer are now residing in the data cache. This is done completely analogously for the instruction cache. If you are to execute a piece of code not currently in the cache, a multiple of full cache lines will need to be loaded into the cache.

**Definition 2.** A memory access is called a *cache hit* if the memory to be loaded is already residing in the cache. An access that is not a cache hit is called a *cache miss*.

**Definition 3.** A memory object (logical data stored in memory) whose size would fit into N cache lines is called *cache unaligned* if an access to the object would cause N+1 cache lines to be loaded into the cache. A memory location that is not cache unaligned is called *cache aligned*.

Again looking at the same integer as above. If the memory location of this integer is aligned such that the first two and last two bytes reside in different cache lines, then both cache lines will need to be loaded into the cache before the CPU can access the memory.

**Definition 4.** The set associativity of the cache is a measure of how many valid cache lines any one memory location may be loaded into. This set of cache lines is called a cache set. In a fully associative cache, any memory location may be loaded into any cache line. In an N-way associative cache, a memory location may be mapped into one of exactly N fixed locations. A 1-way associative cache is called directly mapped.

**Definition 5.** When a cache line is loaded into a cache set that is full, another cache line has to be *evicted* to a higher level memory. The algorithm used to choose which cache line to evict is called the *replacement policy*. The most commonly used policy is to evict the *Least Recently Used* (LRU) cache line.

# 2.2 The Instruction Cache

In the instruction cache the memory containing the machine code to be executed is loaded. Conversely, the data to be processed is loaded into the data cache. The

Cache size: 32KB Associativity: 2-way

Cache line size: Fixed, 64 bytes

Replacement policy: Least Recently Used (LRU)

Table 2.1: Example cache features from an ARM CORTEX A15MP, L1 instruction cache.

reason for this split is the locality property of both code and data. In general, computer programs access both the instructions and the data they process such that recently used memory will probably be used again in the near future. Program code shows an even stronger locality than data due to loop structures, functions etc. Thus, caching the instructions from slower memory will, in general, result in much faster execution. Furthermore, relatively few instructions may operate on large amounts of data. In this case, the separation of the L1 caches may drastically improve performance as the instructions will not need to be fetched repeatedly from higher order memory.

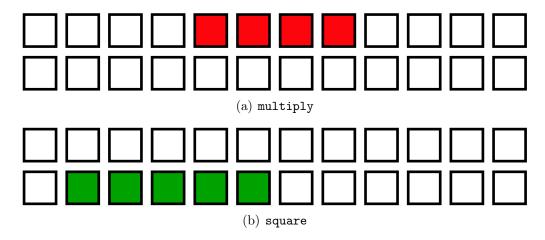

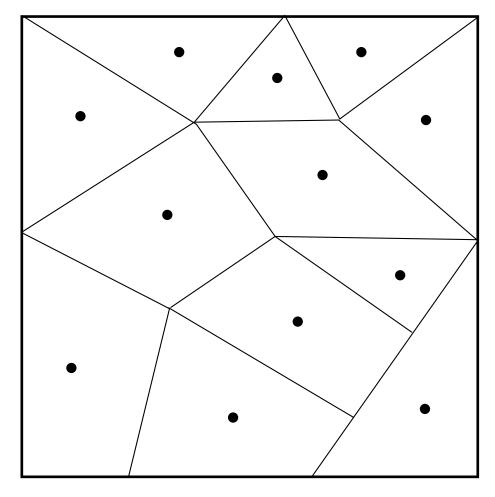

To give an example: Say we are to run the code given in listing 1. How would this code be loaded into the cache? Notice the functions multiply and square. These functions will probably be mapped into different cache sets when loaded into the cache. Now, if we assume a cache with 24 cache sets, the corresponding mapping could turn out like shown in figure 2.2 on the following page. Keep in mind that the cache sets could just as easily overlap.

```

def pow( base, exponent )

1

multiplier = base

2

result = 1

3

for bit in exponent:

4

if bit == 1:

5

result = multiply(result, multiplier)

6

multiplier = square(multiplier)

7

8

return result;

```

Listing 1: Pseudocode for a simple square and multiply exponentiation algorithm.

Figure 2.2: Example mapping of the functions multiply and square into the corresponding cache sets in an I-cache with 24 cache sets.

# 2.3 The Spy Process

The basic idea of an I-cache trace attack is that the instruction cache is shared between the different execution contexts. This is a property that can be exploited. As shown in [39] it is possible to use cache access patterns to send information across security borders, and it is a similar idea that is the basis of all cache attacks: Information about the crypto-system will leak through the cache access patterns.

The spy process in figure 2.3 on the next page is taken from [2] and shows a spy process monitoring the instruction cache. It works by first aligning the code to that of one cache set. It is then executed in such a way that it will fill one cache set with inert code and measure how long it takes to fill the entire set, using the rdtsc instruction on x86 platforms. Finally, it repeats the procedure for all cache sets. An attack utilising this kind of cache spy is referred to as a PRIME+PROBE attack in the literature.

The idea is that, if no code (other than the spy itself) has accessed a particular cache set, then the instructions stored in that set will be loaded and executed quickly. If, however, another process has accessed that particular cache set in the meantime, the spy's instructions need to be fetched from a higher level memory and the code will execute significantly slower. This difference is measurable and it is this difference that is the physical observable in the instruction cache side-channel.

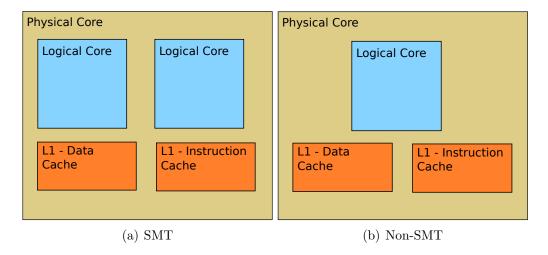

# 2.4 Simultaneous Multi-Threading

Another point that must be mentioned is the concept of Simultaneous Multi-Threading (SMT). SMT is a technique employed by some processor manufacturers<sup>2</sup> to create more logical processor cores on one physical core. They do this by replicating only some vital components of the processor and share the remaining components among these logical cores, cf. figure 2.4 on page 13.

SMT is important to instruction cache analysis because the instruction cache is amongst the components shared between the logical cores in an SMT context. Thus it is possible to run the spy-process truly concurrently to the crypto-process, and theoretically we are able to trace the execution flow as it happens.

The alternative is to execute the attack in a simulated multi-threading environment (Non-SMT) where each thread is scheduled to run in turn on one physical core. This second approach, although possible, will incur more noise from thread context switching.

Most previous work has been concerned with I-cache analysis in an SMT environment as this greatly simplifies decoupling of the spy from the victim. In this

<sup>&</sup>lt;sup>2</sup>Intel markets its SMT technology under the name Hyper-Threading.

```

xor %edi, %edi

L448:

mov <buffer addr>, %ecx

rdtsc

sub %esi, %eax

rdtsc

\mathbf{movb} \ \% \mathbf{al} \ , \ \ (\% \mathbf{ecx}, \% \mathbf{edi})

mov %eax, %esi

add %eax, %esi

jmp L0

.align 4096

inc %edi

L0:

jmp L1

jmp L64

.rept 49

.rept 59

nop

.endr

nop

.endr

L511:

L1:

jmp L65

rdtsc

sub %esi, %eax

.rept 59

\mathbf{movb} \ \% \mathbf{al} \ , \ \ (\% \mathbf{ecx}, \% \mathbf{edi})

nop

add %eax, %esi

.endr

inc %edi

. . .

L64:

cmp <buffer len >, %edi

jmp L128

jge END

.rept 59

jmp L0

nop

.endr

```

Figure 2.3: The instruction cache spy-process for x86 platforms from [2]. The same spy for ARMv7 may be inspected in appendix B.

Figure 2.4: Comparison of SMT vs. non-SMT processors. On an SMT processor, two or more logical cores share resources.

thesis we will only look at a non-SMT environment which makes the decoupling of the spy significantly harder, cf. chapter 6.

# 2.5 Data Analysis

In this section we present the necessary practical tools needed to analyse the timing measurements of the spy presented in section 2.3.

# 2.5.1 Vector Quantization

Vector quantization (VQ) [23] is the process of mapping an N-dimensional vector space down to a finite subset of vectors in the same space, preferably represented as compactly as possible. It is a very potent preliminary screening technique when looking for patterns in the presence of noise. Previous work has shown that this can be very useful when analysing the timing data from the spy-process.

**Definition 6.** A vector quantization is a mapping  $Q : \mathbb{R}^N \to \mathcal{C}$  where  $\mathcal{C}$  is a finite set of points from  $\mathbb{R}^N$ . Thus  $\mathcal{C} \subset \mathbb{R}^N$ . The set  $\mathcal{C}$  is often called a codebook.

The idea behind vector quantization is illustrated in figure 2.5 for the two dimensional case, but the same structure is valid for higher dimensions.

Figure 2.5: Example of a vector quantization of  $\mathbb{R}^2$ . The lines partition the vector space and the dots mark the representative in the codebook for each partition.

#### Nearest Neighbour Quantizers

The special class of vector quantizers we are concerned with is called *nearest neighbour quantizers* or Voronoi quantizers. What identifies a nearest neighbour quantizer is that the partitioning of  $\mathbb{R}^N$  is uniquely determined by the codebook  $\mathcal{C}$  and the use of Euclidean distance in  $\mathbb{R}^N$ :

$$d(\boldsymbol{x}, \boldsymbol{y}) = \|\boldsymbol{x} - \boldsymbol{y}\|_{2} = \sqrt{(\boldsymbol{x} - \boldsymbol{y}) \cdot (\boldsymbol{x} - \boldsymbol{y})}.$$

(2.1)

Encoding any vector  $\boldsymbol{x}$  now becomes a search through  $\mathcal C$

$$\operatorname{Enc}(\boldsymbol{x}) = \underset{\boldsymbol{y_i} \in \mathcal{C}}{\operatorname{arg \, min}} \ d(\boldsymbol{x}, \boldsymbol{y_i}). \tag{2.2}$$

If x is equidistant from two different codewords  $y_i, y_j \in \mathcal{C}$  we will simply pick the one with the smallest subscript, thereby enforcing a well defined map.

## 2.5.2 Self-Organising Map

In the previous section it was shown how to encode a vector using nearest neighbour encoding given a predetermined codebook  $\mathcal{C}$ . The next problem to address will be how to create such a VQ that best describes a set of training data.

This paper will look at a technique frequently used in signal processing and pattern recognition, namely using a Self-Organising Map<sup>3</sup> (SOM) together with use of Learning Vector Quantization (LVQ) [16, 28, 29].

The idea behind a SOM is to iteratively improve the VQ based on the training data.

Two key properties of a SOM are worth mentioning:

- 1. The algorithm is randomised, thus subsequent executions may yield different VQs.

- 2. Codewords that map domains with "similar properties" will tend to be close together in the topology of the SOM. This is of special interest in pattern recognition.

#### Training a SOM

Before the training can commence, two parameters must be chosen: The number of nodes and a topological structure describing their relationship. Typical structures include: A one dimensional string of beads (each node being a bead) or

<sup>&</sup>lt;sup>3</sup>Also known as a Kohonen Map after its creator.

various configurations of N-dimensional grids. The most common choice is a twodimensional hex-grid (also known as a honeycomb structure), as this configuration gives each node 6 equidistant neighbours whilst keeping to only two dimensions. If one is not concerned with grouping similar data together, the layout of the SOM is unimportant.

Once the topological structure is chosen, a metric  $\tilde{d}(i,j)$  measuring the distance between nodes i,j in this space is also needed. We use this to define the neighbourhood of node i.

**Definition 7.** The R-neighbourhood of a node i are all nodes j such that:

$$N_R(i) = \{ j \mid \tilde{d}(i,j) < R \}. \tag{2.3}$$

We further require that

$$R \le R' \Rightarrow N_R(i) \subseteq N_{R'}(i) \tag{2.4}$$

and

$$i \subseteq N_R(i) \quad \forall i, R.$$

(2.5)

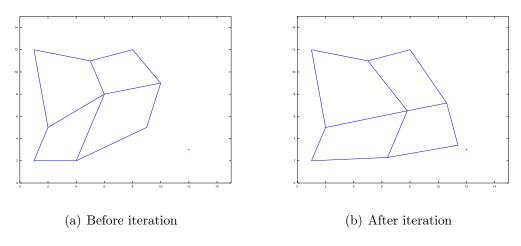

Figure 2.6: Illustration of a SOM training iteration. After the iteration, the closest codeword, along with its neighbours are pulled closer to the training vector. This iteration's training vector is shown in red, whilst the internal nodes of the SOM are shown in blue.

The algorithm starts out by assigning to each node a randomly chosen codeword  $\mu_i$ . Then for a number of iterations, a randomly drawn training vector  $\boldsymbol{x}$  is chosen, the node with the closest vector  $\mu_i$  is found and all vectors in the R-neighbourhood

of i are pulled towards x. This process is illustrated in figure 2.6 on the preceding page. During the initial phase of the training, the neighbourhood radius R is slowly decreased until  $N_R(i) = \{i\}$ . The training may still continue after this point, but only the closest node i will be affected. It is the additional pull on the neighbours of i during the initial phase that gives a SOM property 2 as stated above.

We will now introduce the algorithm for training a SOM.

### **Algorithm 1.** Training a SOM.

Given a training set  $T \in \mathbb{R}^M$ , the number of iterations N and the SOM configuration (including the number of nodes n and topological structure of the nodes expressed by  $N_R(i)$ ).

Furthermore, let  $\alpha(t)$ ,  $\beta(r)$  be two monotonically decreasing functions with range (0.0, 1.0]. Likewise, let R(t) be a monotonically decreasing function for the neighbourhood radius.

1. For all nodes j assign a random  $\mu_j$  from T.

$$\mu_i \stackrel{r}{\leftarrow} T$$

.

2. Set the time t to zero.

$$t \leftarrow 0$$

.

- 3. While t < N, repeat

- (a) Draw a random training vector.

$$x \stackrel{r}{\leftarrow} T$$

.

(b) Find the node i with  $\mu_i$  closest to x.

$$i \leftarrow \underset{j}{\operatorname{arg\,min}} \left( d(\boldsymbol{x}, \boldsymbol{\mu}_j) \right)$$

(c) For all nodes j

$$\mu_j \leftarrow \begin{cases} \boldsymbol{\mu}_j + \beta(\tilde{d}(i,j)) \cdot \alpha(t) \cdot (\boldsymbol{x} - \boldsymbol{\mu}_j) & \text{if } j \in N_{R(t)}(i) \\ \boldsymbol{\mu}_j & otherwise. \end{cases}$$

(d) Step the time.

$$t \leftarrow t + 1$$

The resulting SOM is a codebook C mapping vectors from  $\mathbb{R}^M$  to the set of integers  $\{0, 1, \ldots, n-1\}$  with a corresponding value  $\mu_i \in \mathbb{R}^M$ . For our use case we wish to label each node in the SOM according to a majority vote amongst the (labelled) training vectors.

## 2.5.3 Learning Vector Quantization

Learning vector quantization (LVQ) is a technique building on the idea of a SOM. The idea is to further increase the classification power of the vector quantizer reducing the number of "border cases".

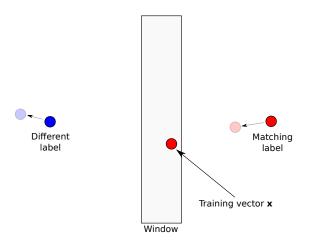

Figure 2.7: Learning step of LVQ3. Assuming the two closest codewords have different labels. The codeword with a label matching that of  $\boldsymbol{x}$  is pulled closer to  $\boldsymbol{x}$  whilst the codeword with a different label is pushed away. (If  $\boldsymbol{x}$  is in the window.)

The main idea is illustrated in figure 2.7. In short, a labelled training vector  $\boldsymbol{x}$  is randomly chosen from the training data T. Next, find the two closest labelled codewords  $\boldsymbol{\mu}_i$ ,  $\boldsymbol{\mu}_j$  in the vector quantizer  $\mathcal{C}$ . Once the two codewords are chosen we check whether the label of  $\boldsymbol{x}$  match the label of either  $\boldsymbol{\mu}_i$  or  $\boldsymbol{\mu}_j$ . If neither match, discard  $\boldsymbol{x}$  and draw a new training vector.

Otherwise, check if x is "in the window", that is, define a decision border between the codewords  $\mu_i$  and  $\mu_j$  and state that if x is in this window, it is a border case and we continue, otherwise we discard it and draw a new training vector.

Now, if exactly one of the labels match, we pull the codeword with the correct label closer to  $\boldsymbol{x}$  and push the other away. Otherwise, both labels match and we pull both closer to  $\boldsymbol{x}$ , albeit a little shorter (reduced by a factor  $\epsilon$ ).

This technique is the third iteration of LVQ as presented by Kohonen [29] and is thus called LVQ3, formally defined on the facing page.

19

#### Algorithm 2. Learning Vector Quantization 3

The input to the algorithm is a labelled codebook C, a set of labelled training vectors T, a window size  $\delta \in \langle 0.0, 1.0 \rangle$ , a fall-off factor  $\epsilon \in \langle 0.0, 1.0 \rangle$  and the number of training iterations N.

Let  $\alpha(t)$  be a monotonically decreasing function with range (0.0, 1.0].

- 1.  $t \leftarrow 0$ .

- 2. While t < N:

- (a) Increment counter:

$$t \leftarrow t + 1$$

.

(b) Choose a random training vector:

$$x \stackrel{r}{\leftarrow} T$$

.

(c) Find the two closest codewords:

$$\boldsymbol{\mu}_i, \boldsymbol{\mu}_j \leftarrow \underset{\boldsymbol{\mu}_{i'}, \boldsymbol{\mu}_{i'} \in \mathcal{C}}{\arg \min} d(\boldsymbol{\mu}_{i'}, \boldsymbol{x}) + d(\boldsymbol{\mu}_{j'}, \boldsymbol{x}) : i' \neq j'.$$

- (d) If neither labels of  $\mu_i$  and  $\mu_j$  match the label of x then repeat 2.

- (e) Check if x is "in the window":

$$\min\left(\frac{d(\boldsymbol{\mu}_i, \boldsymbol{x})}{d(\boldsymbol{\mu}_j, \boldsymbol{x})}, \frac{d(\boldsymbol{\mu}_j, \boldsymbol{x})}{d(\boldsymbol{\mu}_i, \boldsymbol{x})}\right) > \delta.$$

If not, repeat from 2.

(f) If both labels of  $\mu_i$  and  $\mu_j$  match the label of x then:

$$\mu_i \leftarrow \mu_i + \epsilon \cdot \alpha(t) \cdot [\mathbf{x} - \mu_i]$$

$$\mu_j \leftarrow \mu_j + \epsilon \cdot \alpha(t) \cdot [\mathbf{x} - \mu_j].$$

And repeat from 2.

- (g) If necessary swap  $\mu_i$  and  $\mu_j$  so that the label of x matches that of  $\mu_i$ .

- (h) Update  $\mu_i$  and  $\mu_j$ :

$$\mu_i \leftarrow \mu_i + \epsilon \cdot \alpha(t) \cdot [\mathbf{x} - \mu_i]$$

$\mu_j \leftarrow \mu_j - \epsilon \cdot \alpha(t) \cdot [\mathbf{x} - \mu_j].$

And repeat from 2.

# Chapter 3

# Theoretical Analysis of the Side-Channel

This chapter will introduce the theoretical framework for evaluating and comparing physical side-channels introduced by Standaert et al. in [42]. We start out by reciting the assumptions underlying the model behind the framework in section 3.1, followed by one of the major theorems of [42] and a brief discussion of how this may be used to compare side-channels.

# 3.1 Model Assumptions and Definitions

Firstly, the model in this chapter is based on the following informal axioms, introduced by Micali and Reyzin and here directly quoted from [34]:

- 1. Computation, and only computation, leaks information

Information may leak whenever bits of data are accessed and computed upon.

The leaking information actually depends on the particular operation performed, and, more generally, on the configuration of the currently active part of the computer. However, there is no information leakage in the absence of computation: data can be placed in some form of storage where, when not being accessed and computed upon, it is totally secure.

- 2. Same computation leaks different information on different computers

Traditionally, we think of algorithms as carrying out computation. However,

an algorithm is an abstraction: a set of general instructions, whose physical

implementation may vary. In one case, an algorithm may be executed in

a physical computer with lead shielding hiding the electromagnetic radiation correlated to the machine's internal state. In another case, the same

algorithm may be executed in a computer with a sufficiently powerful inner

configuration depends on such history.

battery hiding the power utilised at each step of the computation. As a result, the same elementary operation on 2 bits of data may leak different information: e.g., (for all we know) their XOR in one case and their AND in the other.

- 3. Information leakage depends on the chosen measurement

While much may be observable at any given time, not all of it can be observed

simultaneously (either for theoretical or practical reasons), and some may be

only observed in a probabilistic sense (due to quantum effects, noise, etc.).

The specific information leaked depends on the actual measurement made.

Different measurements can be chosen (adaptively and adversarially) at each

step of the computation.

- 4. Information leakage is local

The information that may be leaked by a physically observable device is

the same in any execution with the same input, independent of the computation that takes place before the device is invoked or after it halts. In

particular, therefore, measurable information dissipates: Though an adversary can choose what information to measure at each step of a computation,

information not measured is lost. Information leakage depends on the past

computational history only to the extent that the current computational

- 5. All leaked information is efficiently computable from the computer's internal configuration

Given an algorithm and its physical implementation, the information leakage is a polynomial-time computable function of (1) the algorithm's internal configuration, (2) the chosen measurement, and possibly (3) some randomness (outside anybody's control).

Following these axioms we will now introduce the necessary notation from [34] needed to discuss the framework by Standaert.

**Definition 8.** An abstract virtual-memory computer, or abstract computer for short, consists of a collection of special Turing machines, which invoke each other as subroutines and share a special common memory. Each element of an abstract computer is called an abstract memory Turing machine (abstract VTM).

$$\mathcal{A} = (A_1, \dots, A_n)$$

All input and output to the abstract VTM's are arbitrary binary strings. It is important to stress that abstract computers and abstract VTM's are not physical devices, they are only representations of logical computations.

**Definition 9.** A physical VTM is a tuple, P = (L, A) where A is an abstract VTM and L is a leakage function as defined below. If  $\mathcal{A} = (A_1, A_2, \dots, A_n)$  is an abstract computer and  $P_i = (L_i, A_i)$ , then  $P_i$  is a physical implementation of  $A_i$  and  $\mathcal{P} = (P_1, \dots, P_n)$  is a physical implementation of  $\mathcal{A}$ .

**Example 1.** An abstract VTM could be the calculation performed by a cryptographic primitive. Taking RSA as an example, an abstract computer would be the operation

$$c \equiv m^e \pmod{n}$$

whilst the physical VTM would be physical realisations of these operations each having a different leakage function. Example physical VTMs:

- 1. The Multiply-Square exponentiation algorithm in software.

- 2. The Montgomery Multiplication algorithm in software.

- 3. A smart card's signing hardware.

**Definition 10.** The leakage function  $L(C_A, M, R)$  models the leakage from a physical realisation of an abstract VTM. It takes three inputs:

- $-C_A$ , the internal configuration of the abstract VTM A.

- -M, the setting of the apparatus used to measure the physical observable.

- -R, a random string to model the randomness of the measurement.

## 3.2 Framework

In this section we will introduce the framework of Standaert et al. [42] for analysing the information leakage from physical side-channels. The framework is modelled around recovering well defined *parts* of the key, but, as mentioned in the original article, any secret information that can be modelled by the leakage function can be analysed using the framework.

#### 3.2.1 Attack Model

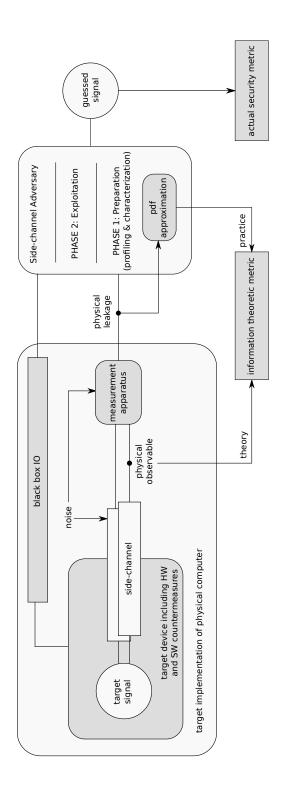

The attack model is illustrated in figure 3.1 on the next page. The attack is divided into two phases. Informally phase one is where the adversary tries to approximate the probability distribution (pdf) of the leakage function for a part of the key. In phase two, this pdf is used for exploitation.

This paper is concerned about the evaluation of the side-channel itself and not on comparing how efficient different adversaries are at extracting the information. Therefore this section will present the necessary background to compare the leakage between different implementations. [42] also covers comparing the efficiency of different adversaries, but that is outside the scope of this thesis.

Figure 3.1: Intuitive description of a side-channel key recovery attack ([42] p.6).

#### 3.2.2 Information Theoretic Metrics

As briefly mentioned, the goal of the adversary in phase one of the attack is to approximate the leakage function for a part of the key, we model this partial key information as the  $key\ class$  a key belongs to.

**Definition 11.** Let  $k \in \mathcal{K}$  be key from the key set of a cryptographic abstract computer  $E_K$ . Let  $\gamma : \mathcal{K} \to \mathcal{S}$  be a mapping from the key set to a set of *key classes*, such that  $|\mathcal{S}| \ll |\mathcal{K}|$ .

An example:  $\gamma : \mathcal{K} \to \{0, 1\}$  could partition the key set to keys starting with 0 or 1 respectively.

Next, define a key recovery adversary  $A_{E_K,L}(\tau, m, q)$  as an algorithm using at most  $\tau$  time, m memory and q queries to the target computer. The adversary's goal is to guess the correct key class  $s = \gamma(k)$ , using both the black box information (e.g. cipher-text and/or known plain-texts) and physical information leaked from the side-channel(s) of the physical computer  $(E_K, L)$ .

The adversary returns an ordered set  $\mathbf{g} = (g_1, g_2, \dots, g_{|\mathcal{S}|})$  which is a permutation of the key classes in  $\mathcal{S}$ .

**Definition 12.** The o-th order success rate of the adversary is defined as

$$\mathbf{Succ}_{\mathbf{A}_{\mathbf{E}_{\mathbf{K}},\mathbf{L}}}^{sc-kr-o,\mathcal{S}}(\tau,m,q) = \Pr[\mathbf{Exp}_{\mathbf{A}_{\mathbf{E}_{\mathbf{K}},\mathbf{L}}}^{sc-kr-o} = 1]$$

(3.1)

Where  $\text{Exp}_{A_{E_{K},L}}^{sc-kr-o}$  is successful if and only if s is in the first o elements of g.

Experiment

$$\operatorname{Exp}_{\mathtt{A}_{\mathtt{E}_{\mathtt{K}},\mathtt{L}}}^{sc-kr-o}$$

:

$$k \overset{r}{\leftarrow} \mathcal{K}$$

$$s = \gamma(k)$$

$$\boldsymbol{g} \leftarrow \mathtt{A}_{\mathtt{E}_{\mathtt{K}},\mathtt{L}}$$

$$\mathbf{if} s \in (g_1,\ldots,g_o)$$

$$\text{return 1}$$

$$\mathbf{else}$$

$$\text{return 0}$$

For the remainder of this paper we will use order o = 1.

**Definition 13.** The asymptotic success rate of an adversary  $A_{E_K,L}$  is the limit of its success rate as q goes to infinity.

$$\mathbf{Succ}^{sc-kr-o,\mathcal{S}}_{\mathtt{Ae_v,L}}(\tau,m,q\to\infty).$$

3.2. FRAMEWORK 25

## 3.2.3 Conditional Entropy

This section will introduce Shannon's conditional entropy as a metric to measure the amount of information leaked from a side-channel.

The setup is as follows, let  $L_q$  be a stochastic variable of the side-channel leakage observations and let  $l_q = (l_1, l_2, \dots, l_q)$  be a realisation of this variable.

Entropy defined by Shannon [41], is a measure of the information contained in a message, it is used as a tool in for instance data compression. Intuition yields that predictive data have low entropy, whilst completely random data have high entropy.

More formally, Shannon defines the entropy of a discrete stochastic variable X as:

$$H[X] = -\sum_{x \in X} \Pr(x) \cdot \log_2 \Pr(x)$$

(3.2)

Now, we are concerned with the entropy for the distribution of  $\Pr(S \mid \mathbf{L}_q)$  as it would help us decide on the difficulty of determining a key class s given an observation vector  $\mathbf{l}_q$ .

Shannon already defines this conditional entropy.

$$H[X \mid Y] = -\sum_{x \in X} \sum_{y \in Y} \Pr(x, y) \cdot \log_2 \Pr(x \mid y)$$

$$= -\sum_{x \in X} \sum_{y \in Y} \Pr(x) \cdot \Pr(y \mid x) \cdot \log_2 \Pr(x \mid y)$$

$$= -\sum_{x \in X} \Pr(x) \sum_{y \in Y} \Pr(y \mid x) \cdot \log_2 \Pr(x \mid y)$$

$$= -\sum_{x \in X} \Pr(y) \sum_{x \in X} \Pr(x \mid y) \cdot \log_2 \Pr(x \mid y)$$

(3.3)

$$= -\sum_{x \in X} \Pr(x) \sum_{x \in X} \Pr(x \mid y) \cdot \log_2 \Pr(x \mid y)$$

(3.5)

Now, define the conditional entropy matrix

$$\mathbf{H}_{S}^{q} = \left(h_{s,s^*}^{q}\right)_{s,s^* \in S} \tag{3.6}$$

where

$$h_{s,s^*}^q = -\sum_{\boldsymbol{l}_q} \Pr(\boldsymbol{l}_q \mid s) \cdot \log_2 \Pr(s^* \mid \boldsymbol{l}_q). \tag{3.7}$$

S is a discrete stochastic variable of the previously targeted key class S. Also, note that:

$$H[S \mid \mathbf{L}_q] = -\sum_{S} \Pr(s) \sum_{\mathbf{l}_q} \Pr(\mathbf{l}_q \mid s) \cdot \log_2 \Pr(s \mid \mathbf{l}_q) = \mathbf{E}(h_{s,s})$$

(3.8)

is exactly Shannon's conditional entropy from (3.4).

Finally, we define the mutual information as,

$$I(S, \mathbf{L}_q) = H[S] - H[S \mid \mathbf{L}_q]. \tag{3.9}$$

Mutual information is a measure of how much of the information in S is reflected in  $L_q$ .

It is important to note that in general, we do not know the probability distribution of  $\Pr(L_q \mid S)$ , but rather we estimate the probability distribution  $\Pr(\tilde{L}_q \mid S)$  using a practical number of samples.

# 3.3 Measuring the Information Leakage

Before we recite one of the theorems of [42] that will be the climax of this chapter, we must first define a few more concepts.

**Definition 14.** A first-order *Bayesian side-channel adversary* (choosing only one key class from S) is an adversary that always selects  $\arg \max_{s^*} \Pr(s^* \mid \boldsymbol{l}_q)$ .

**Definition 15.** An approximated leakage distribution  $\Pr(\tilde{L}_q \mid S)$  is considered sound if the asymptotic success rate of a first-order Bayesian side-channel adversary is one.

**Theorem 1.** Assuming independent leakages for the different queries in a sidechannel attack, an approximated leakage probability distribution  $\hat{\Pr}(\tilde{L}_q \mid S)$  is sound if and only if the conditional entropy matrix evaluated in an unbounded exploitation phase is such that the diagonal element is the smallest in every row of the approximated entropy matrix  $\hat{\mathbf{H}}_S^q$ . That is,

$$\underset{s^*}{\operatorname{arg\,min}} \ \hat{h}_{s,s^*}^q = s, \forall s \in \mathcal{S}. \tag{3.10}$$

*Proof.* Let s be the target key class, and  $(\boldsymbol{l}_q)_p = (\boldsymbol{l}_{q,1}, \boldsymbol{l}_{q,2}, \dots, \boldsymbol{l}_{q,p})$  be p realisations of a q-queries leakage vector  $\boldsymbol{L}_q$ .

Now, a Bayesian adversary using targeting s using the leakage data  $(\boldsymbol{l}_q)_p$  will be successful if and only if

$$s = \underset{s^*}{\operatorname{arg\,max}} \ \hat{\Pr}(s^* \mid (\tilde{\boldsymbol{l}_q})_p)$$

$$s = \underset{s^*}{\operatorname{arg\,max}} \ \frac{\hat{\Pr}((\tilde{\boldsymbol{l}_q})_p) \mid s^*) \cdot \Pr(s^*)}{\hat{\Pr}((\tilde{\boldsymbol{l}_q})_p)}.$$

Assume that  $\Pr(s^*)$  is uniformly distributed. Note that since  $\Pr((\tilde{l}_q)_p)$  only depends on the correct key class s it is independent of  $s^*$ . This yields,

$$s = \underset{s^*}{\arg\max} \ \hat{\Pr}((\tilde{\boldsymbol{l}_q})_p) \mid s^*).$$

Since we assume that each measurement in  $(\tilde{l}_q)_p$  is independent, we may rewrite the above as:

$$s = \underset{s^*}{\operatorname{arg\,max}} \prod_{i=1}^{p} \hat{\Pr}(\tilde{l}_{q,i} \mid s^*).$$

Now, as we are looking at an unbounded exploitation phase (asymptotic attack), the number of leakage vectors p is not bounded and the measurement vector  $(\tilde{\boldsymbol{l}}_q)_p$  is in fact a trace from the real probability distribution  $\Pr(\boldsymbol{L}_q, | s)$ . Therefore as  $p \to \infty$  each unique leakage vector in  $\boldsymbol{l}_q \in (\tilde{\boldsymbol{l}}_q)_p$  will repeat  $p \cdot \Pr(\boldsymbol{l}_q | s)$  times. Thus, an asymptotic attack is successful if and only if:

$$s = \arg \max_{s^*} \prod_{\boldsymbol{l}_q} \hat{\Pr}(\boldsymbol{l}_q \mid s^*)^{p \cdot \Pr(\boldsymbol{l}_q \mid s)}$$

$$s = \arg \max_{s^*} \prod_{\boldsymbol{l}_q} \left( \hat{\Pr}(\boldsymbol{l}_q \mid s^*)^{\Pr(\boldsymbol{l}_q \mid s)} \right)^p$$

$$s = \arg \max_{s^*} \prod_{\boldsymbol{l}_q} \hat{\Pr}(\boldsymbol{l}_q \mid s^*)^{\Pr(\boldsymbol{l}_q \mid s)}$$

$$s = \arg \max_{s^*} \prod_{\boldsymbol{l}_q} \hat{\Pr}(s^* \mid \boldsymbol{l}_q)^{\Pr(\boldsymbol{l}_q \mid s)}$$

$$s = \arg \max_{s^*} \sum_{\boldsymbol{l}_q} \Pr(\boldsymbol{l}_q \mid s) \cdot \log_2 \hat{\Pr}(s^* \mid \boldsymbol{l}_q)$$

$$s = \arg \min_{s^*} - \sum_{\boldsymbol{l}_q} \Pr(\boldsymbol{l}_q \mid s) \cdot \log_2 \hat{\Pr}(s^* \mid \boldsymbol{l}_q). \tag{3.11}$$

Now, we can observe that the sum (3.11) equals that of (3.7) save for the approximated probability in the logarithmic factor. Thus, it exactly matches how the conditional entropy is estimated in practice. Therefore, if the previous condition holds for all key classes s, the Bayesian side-channel is asymptotically successful and vice versa.

**Remark** In practice,  $Pr(s \mid l_q)$  is estimated as:

$$\hat{\Pr}(s \mid \boldsymbol{l}_q) = \frac{\hat{\Pr}(\boldsymbol{l}_q \mid s) \cdot \Pr(s)}{\sum_{s^*} \hat{\Pr}(\boldsymbol{l}_q \mid s^*) \cdot \Pr(s^*)}.$$

(3.12)

# 3.4 Consequences of Theorem 1

It turns out that under certain conditions<sup>1</sup> theorem 1 suffices to discuss the security of a side-channel. More formally the conditions are when |S| = 2, and the leakage function  $L(C_A, M, R) = L'(C_A, M) + L''(R)$  where  $L''(R) \sim N(0, \sigma)$ . That is the randomness in the leakage function is Gaussian with mean 0 and standard deviation  $\sigma$ .

This gives rise to the following two lemmas [42].

**Lemma 1.** In a key recovery side-channel attack exploiting a univariate Gaussian leakage distribution of a single query. The residual entropy of a Bayesian attack choosing between exactly two target key classes is a monotonously decreasing function of the single query (hence multi query) success rate against s.

*Proof.* Let us consider univariate Gaussian leakage and let  $|\mathcal{S}| = 2$ . Now, without loss of generality, assume the distribution of the correct key class s to have mean 0 and that of the wrong key class to have mean  $\delta$ . The standard deviation in either case is  $\sigma$ .

Now, assuming a Bayesian adversary, the success rate for the attack will be

$$\mathbf{Succ}_{\mathtt{A}_{\mathtt{E}_{\mathtt{K}},\mathtt{L}}}^{sc-kr-1,s}(\delta,\sigma) = \int_{-\infty}^{\delta/2} \mathbf{N}_{\mathbf{x}}(0,\sigma) dx$$

where

$$\mathbf{N}_{\mathbf{x}}(\mu, \sigma) = \frac{1}{\sigma \sqrt{2\pi}} \cdot \exp\left(\frac{-(x-\mu)^2}{2\sigma^2}\right).$$

The corresponding residual entropy equals

$$h_{s,s}(\delta,\sigma) = -\int_{-\infty}^{\infty} \mathbf{N}_{\mathbf{x}}(0,\sigma) \cdot \log_2 \frac{\mathbf{N}_{\mathbf{x}}(0,\sigma)}{\mathbf{N}_{\mathbf{x}}(0,\sigma) + \mathbf{N}_{\mathbf{x}}(\delta,\sigma)} dx$$

Define a change of variables first  $u = x/\sigma$  then  $z = \delta/\sigma$ :

$$\begin{aligned} \mathbf{Succ}_{\mathtt{AE}_{\mathtt{K},\mathtt{L}}}^{sc-kr-1,s}(\delta,\sigma) &= \int_{-\infty}^{\delta/2\sigma} \mathbf{N}_{\mathbf{u}}(0,1) \ du \\ h_{s,s}(\delta,\sigma) &= -\int_{-\infty}^{\infty} \mathbf{N}_{\mathbf{u}}(0,1) \cdot \log_2 \frac{\mathbf{N}_{\mathbf{u}}(0,1)}{\mathbf{N}_{\mathbf{u}}(0,1) + \mathbf{N}_{\mathbf{u}}(\delta/\sigma,1)} \ du \end{aligned}$$

$$\begin{aligned} \mathbf{Succ}_{\mathtt{A}_{\mathtt{E}_{\mathtt{K}},\mathtt{L}}}^{sc-kr-1,s}(z) &= \int_{-\infty}^{z/2} \mathbf{N}_{\mathbf{u}}(0,1) \ du \\ h_{s,s}(z) &= -\int_{-\infty}^{\infty} \mathbf{N}_{\mathbf{u}}(0,1) \cdot \log_2 \frac{\mathbf{N}_{\mathbf{u}}(0,1)}{\mathbf{N}_{\mathbf{u}}(0,1) + \mathbf{N}_{\mathbf{u}}(z,1)} \ du. \end{aligned}$$

<sup>&</sup>lt;sup>1</sup>Standaert et al. also considers more general assumptions, but this is unnecessary for our discussion.

29

Finally, observe that the success rate is a monotonously increasing function of z and that the residual entropy is a decreasing function of z, which concludes the proof.

Furthermore, in a multivariate leakage distribution the following lemma holds if each leakage component shares the same standard deviation.

**Lemma 2.** In a key recovery side-channel attack exploiting a multivariate Gaussian leakage distribution with independent leakage samples having the same standard deviation. The residual entropy of a Bayesian attack choosing between exactly two target key classes is a monotonously decreasing function of the single query (hence multi query) success rate against s.

The proof of lemma 2 is similar to that of lemma 1 and is outlined in [42].

One can therefore conclude that in the case of Gaussian noise and a key class size of 2, the higher the conditional entropy  $H[S \mid \mathbf{L}_q]$  the lower the success rate of a Bayesian adversary will be.

# Chapter 4

# **Proof of Concept**

In this section we aim to answer the following questions:

- 1. Is it possible to use the instruction cache as a side-channel on an ARM platform?

- 2. What (if any) are the added challenges of attacking an ARM platform as compared to previous work on x86?

In order to answer both questions, a prototype experiment will be performed. In short this experiment attempts to solve the problem:

```

if ( bit == 1 ) {

foo();

}

```

Observing an execution of the code above, determine whether the function foo() was called. This should be determined by observing the instruction cache exclusively.

# 4.1 Summary of the Target Platform

The platform used for all experiments in this paper is presented in the table below.

| Platform                     |                                   |

|------------------------------|-----------------------------------|

| Hardware:                    | Hardkernel Odroid X               |

| Hardware Revision:           | $0.4\ 20120808$                   |

| Operating System:            | ARM ARCH Linux                    |

| Kernel Version:              | 3.8.13.21-2-ARCH $#1$ SMP PREEMPT |

| Kernel Build Date:           | Thu Apr 24 19:25:30 MDT 2014      |

| Details                      |                                   |

| Chipset:                     | Samsung Exynos 4412               |

| Processor:                   | 4x Cortex-A9 Quad Core 1.4Ghz     |

| L1 (Data):                   | 32 KB per core                    |

| ,                            |                                   |

| L1 (Instruction):<br>L2:     | 32 KB per core<br>1 MB            |

|                              |                                   |

| Main Memory:                 | 1005 MB                           |

| Cache Line Size:             | 32 bytes                          |

| L1 Instruction Cache Details |                                   |

| Associativity                | 4                                 |

| Cache Sets                   | 256                               |

| Replacement Policy:          | Random Round Robin                |

Table 4.1: Important platform parameters.

#### Note on Random Round Robin

The fact that the L1-I cache uses a Random Round Robin<sup>1</sup> (RRR) replacement policy introduces extra noise into the measurements. As can be seen in figure 4.1 this causes cache-misses to bleed into subsequent observations in a seemingly random manner. In a Least Recently Used or First In First Out replacement pattern, we would expect the cache to be completely filled with the spy's instructions after one iteration, which is not the case for RRR.

What is actually happening is that the spy, when trying to access an instruction which is not currently in the cache, will evict a random cache line from the relevant cache set. This cache line may very well contain another part of the spy's

$<sup>^1</sup>$ Random Round Robin replacement will evict a pseudo randomly chosen cache line from a cache set.

Figure 4.1: The figure show part of a raw timing measurement on the target platform. The bleeding of cache misses into subsequent measurements is clearly visible in the excerpt. More white denote longer access time.

instructions. Thus, we could get two or even more cache misses as a result of one alien cache line in the cache set, or even subsequent measurements as shown in figure 4.1.

Luckily, the use of RRR replacement is of minor consequence for the success of the attack as its effect on the measurement is easily removed by letting the spy run for more rounds between each measurement, thus eventually evicting all alien cache lines.

## 4.1.1 Timing on ARM

One of the first challenges in implementing the instruction cache side-channel on ARM is getting access to accurate high-precision timing. How to access these timing registers differ between different versions of ARM CPUs. This paper will limit itself to discussing timing on a Cortex A9. Similar, if not identical, procedures can be followed on both older and newer cores.

On x86 the core local cycle count is easily readable through the RDTSC-instruction. On ARMv7 there is no specialised instruction to retrieve the cycle count. Instead we have to use the more general MRC-instruction to read from the performance cycle count register (CCNT). Unfortunately, access to this register is disabled by default at the lowest privilege level. It is, however, possible to enable access to this register, even to user space, from a higher privilege level.

The timing data in this paper are all measured using the MRC-instruction from user-space after enabling access to it from a loadable kernel module. Source code for enabling user-space timing is available in appendix A.

It is possible that some platforms already expose or will expose the CCNT register in the future as all that is needed to expose it is to run a small number of instructions from a higher privilege level during boot or from a driver/module running in privileged mode.

4.2. METHOD 33

Please note that restricted access to the performance timing register is not sufficient in itself to close the instruction cache side-channel. It may be possible for an attacker to get sufficiently accurate timing from other sources.

## 4.2 Method

For simplicity, the experiment in this section will simulate ideal conditions where the spy is always run immediately after the function in question. Also, in order to clear the noise introduced by the RRR replacement policy, the spy is run for 25 iterations prior to the call to foo <sup>2</sup>.

The timing data was sampled using a loop like the one shown below, where input is an arbitrary bit string.

```

for (int bit : input ) {

run_spy( 25 ); // Populate the cache, not measured

if ( bit == 1 ) {

foo();

}

run_spy( 1 ); // measured.

}

```

Throughout this section, we are considering a 2-target attack, i.e.  $|\mathcal{S}| = 2$ . We are at any given time only considering one bit of information. The measured output from the leakage function  $\tilde{L}_{256}$  is a 256 dimensional vector of timing data. Each component measures a predetermined cache set as a positive integer, with all values above 255 clamped to 255. Parts of the data in  $\tilde{L}_{256}$  will be discarded as explained below.

Now, the attack was executed as follows:

#### Preparation step

- 1. Generate training data by running the spy on known input (10 separate instances measuring 10000 iterations for each  $s \in \{0, 1\}$ ).

- 2. Cull dead cache sets, see section 4.2.1.

- 3. Create and train a SOM using the reduced training data.

- 4. Tune the resulting VQ using the LVQ3 algorithm.

#### Exploitation step

1. Run the spy on "unknown" input.

<sup>&</sup>lt;sup>2</sup>In this experiment the function foo is actually cos(·) from the standard C-library.

- 2. Reduce dimensions to the previously determined cache sets.

- 3. Encode the input using the previously trained VQ. Finally, the result is compared to the "unknown" input.

#### 4.2.1 Culling Dead Data

As we are measuring every cache set, we expect to see a lot of measurements that do not carry any information about the correct key class. Rather, we expect these dead cache sets to slow down and even hamper our analysis. Below, we present two methods to identify the live cache sets prior to building the vector quantizer.

#### Timing Mean and the Central Limit Theorem

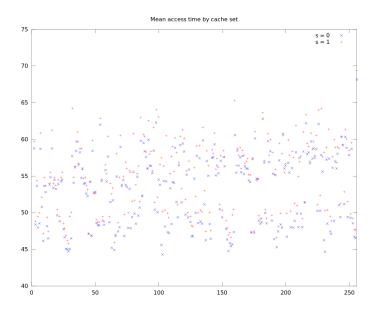

As can be seen in figure 4.2 on page 36, the mean timing value of the cache sets show a clear tendency of being a good metric to identify information bearing cache sets. However, as the variance of the timings can be quite large, relying purely on the mean could result in a too conservative culling.

Luckily, the problem could be taken directly from undergraduate textbook. By the central limit theorem: The estimated mean will follow a Gaussian distribution,  $\bar{x} \sim N(\mu, \frac{\sigma}{\sqrt{n}})$ , where n is the number of measurements. We can therefore use a simple two-sided test to check if the means are equal. If the difference is significant, we use that cache set, otherwise we discard it.

In the practical results below, we use this metric to cull dead data.

#### Mutual Information

Mutual information is another metric that can be used for this purpose. Simply by choosing the cache sets with the highest mutual information as the live. Note, however, that choosing too few cache sets could potentially hamper the analysis in cases where the target process is at an *unusual alignment*, explained in the next section.

In our experiments, we tried using only the cache sets carrying mutual information larger than 0.1. Doing so, however, yielded poorer results than using culling according to the central limit theorem. Thus, great care has to be made when using this as a culling mechanism as even a little information may help the final result.

## 4.3 Theoretical Analysis

In this section we aim to analyse the quality of the information in the side-channel proposed above. This is separate from the actual implementation of the exploita-

tion step: Here we aim to formally evaluate the side-channel according to the framework presented in chapter 3, whilst the success rate and details of the exploitation step is presented in section 4.4 on page 42. Thus this section answers the question "Can we exploit the information leaked from the side-channel?"

#### **Initial Analysis**

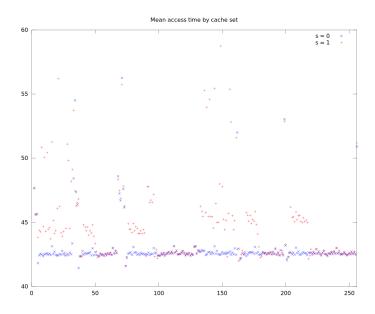

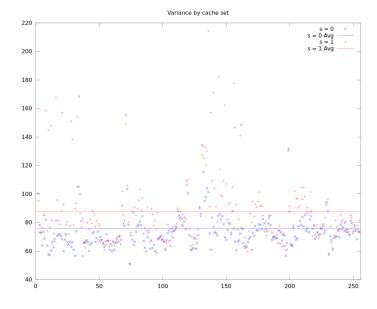

Firstly, let us consider the mean and variance for the timing of each cache set, presented in figures 4.2 and 4.3.

For small functions we do not expect much of the cache to be polluted, thus culling cache sets that do not carry information should greatly ease the later analysis. Another noteworthy point is that the mean values seen in figure 4.2 are from several independent executions of the crypto-process. Further inspection into the raw data reveals that the cache set footprint seems to vary between different executions of the program, this is due to a technique called address space layout randomisation. In short the OS will randomise where in memory it loads the executable. This is done to increase the difficulty of certain buffer overflow exploits. The rearranged data will, however, still retain alignment to memory page boundaries, which is sufficient for our analysis<sup>3</sup>.

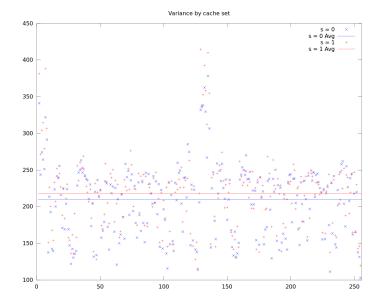

Furthermore, as can be seen in figure 4.3, there is clearly a lot of noise in the measurements. Additionally, the data set where are known cache misses seems to have a slightly higher variance than the sets without a forced cache miss.

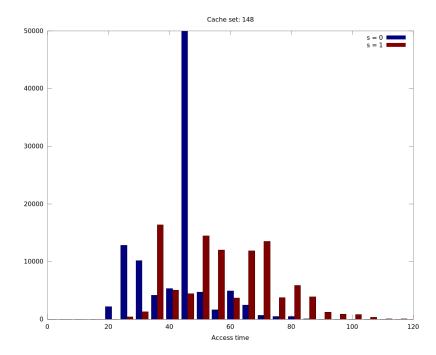

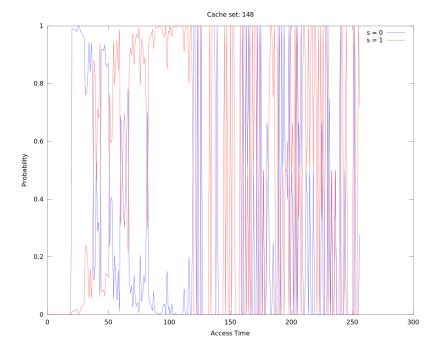

The source of this variance becomes more clear once we take a look at the distribution of the measurements in a single cache set. Below, cache set 148 was chosen as a candidate seeming to carry significant mutual information. A histogram of the data is shown in figure 4.4. There appear to be 3–4 distinct peaks where most access time measurements reside. This is most likely a product of one or more cache misses in the measurement for this cache set, or even instances where the memory system has had to access lower level memory than L2. Recall that the L1 instruction cache in this experiment has random round robin replacement, so we expect some randomness in the number of cache misses.

Another, perhaps even more interesting point is that not all measurements of s = 0 seem to result in a cache hit. This could be a result of various effects, such as OS-ticks, hardware interrupts, preemptive scheduling of other processes etc.

<sup>&</sup>lt;sup>3</sup>The cache set-alignment boundary on this platform is  $2 \cdot PageSize$ , we will therefore have only two separate footprints.

Figure 4.2: Plot shows mean value for spy measurements per cache set. Cache sets with frequent cache misses are clearly visible.

Figure 4.3: Plot shows the variance of spy measurements per cache set.

Figure 4.4: Histogram of cache access measurements for cache set 148.

#### Estimating $Pr(\boldsymbol{L}_q \mid S)$

For simplicity, we will only consider the univariate distribution of the measurement in cache set 148. The results for other cache sets are presented in table 4.2 on page 40 and we cannot assume that they are independent, but separate analysis should still yield a lot of information of the side-channel.

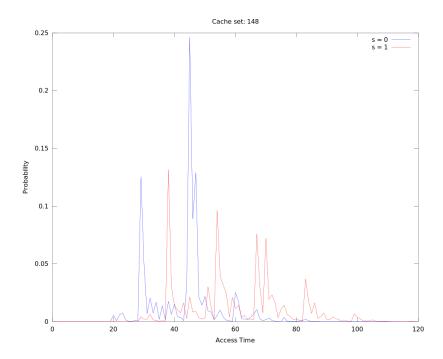

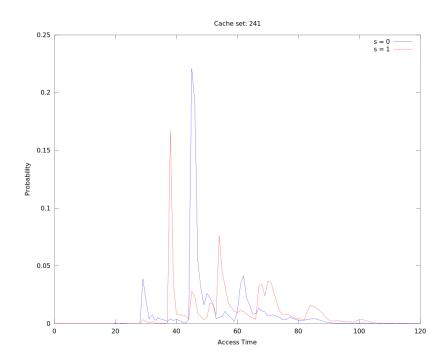

After measuring the 100000 samples for each  $s \in S$ , the estimated probability distribution  $\Pr(\tilde{L}_q \mid S)$  is easily estimated using a frequency table. The result is presented in figure 4.5. The access time axis is cropped at 120 as the the probability of access times longer than that tend towards zero.

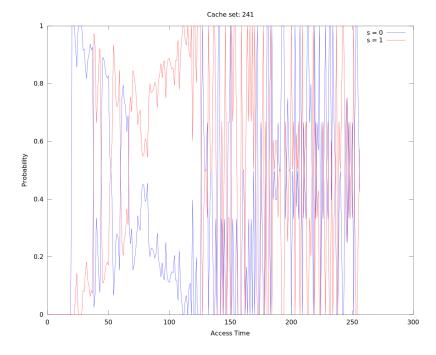

Furthermore, the distribution  $\Pr(\tilde{\boldsymbol{L}}_q \mid S)$  is used to calculate  $\Pr(S \mid \tilde{\boldsymbol{L}}_q)$  using the formula (3.12) on page 27. The results are shown in figure 4.6. For measurements between 20–120 there is a trend that may be used to determine s. As expected, measurements outside the range of commonly observed values yield unpredictable results.

#### Entropy

Shannon's conditional entropy for the measurements of cache set 148 is presented below

First, the conditional entropy matrix is calculated from (3.6):

$$\hat{\mathbf{H}}_{S,148}^1 = \begin{bmatrix} 0.44568 & 3.33847 \\ 3.41892 & 0.44405 \end{bmatrix}.$$

Thus, from theorem 1 on page 26 it is clear that the estimated probability distribution of  $\Pr(\mathbf{L}_q \mid S)$  for cache set 148 is sound.

Unfortunately, as the noise in our measurements is not Gaussian, the lemmas of chapter 3 do not apply. However, we may still calculate the mutual information of S that we have captured by our estimation of  $\Pr(\mathbf{L}_q \mid S)$ .

$$H[S \mid \tilde{\mathbf{L}}_q] = \mathbf{E}_s(\hat{h}_{s,s}) = 0.44487.$$

$H[S] = 1$

Which yields the mutual information:

$$I(S \mid \tilde{\boldsymbol{L}}_q) = 0.55513.$$

The results for the remaining cache sets are shown in table 4.2 on page 40. In this experiment all but one of the cache sets have sound approximations for  $\tilde{L}_q$ , but cache sets having mutual information less than 0.01 have been omitted for compactness.

Figure 4.5: Estimated probability distribution  $\hat{\Pr}(\tilde{\boldsymbol{L}_q} \mid S).$

Figure 4.6: Estimated probability distribution  $\hat{\Pr}(S \mid \tilde{L_q})$ .

| Cache set | $I(S, \tilde{m{L}}_q)$ | Cache set | $I(S, \tilde{m{L}}_q)$ | Cache set | $I(S, \tilde{m{L}}_q)$ |

|-----------|------------------------|-----------|------------------------|-----------|------------------------|

| 0         | Not Sound              | 78        | 0.0120                 | 153       | 0.0113                 |

| 4         | 0.0125                 | 82        | 0.0139                 | 154       | 0.0265                 |

| 5         | 0.0131                 | 84        | 0.0116                 | 155       | 0.3425                 |

| 6         | 0.0129                 | 85        | 0.0115                 | 156       | 0.3483                 |

| 7         | 0.1745                 | 86        | 0.0103                 | 157       | 0.0187                 |

| 8         | 0.0183                 | 87        | 0.0148                 | 158       | 0.0153                 |

| 9         | 0.1673                 | 88        | 0.0172                 | 159       | 0.0120                 |

| 11        | 0.1685                 | 89        | 0.0245                 | 160       | 0.3231                 |

| 12        | 0.0104                 | 90        | 0.0703                 | 161       | 0.3116                 |

| 13        | 0.0156                 | 91        | 0.0762                 | 168       | 0.0281                 |

| 15        | 0.1580                 | 92        | 0.0615                 | 169       | 0.0271                 |

| 16        | 0.0156                 | 93        | 0.0522                 | 170       | 0.0240                 |

| 18        | 0.0158                 | 94        | 0.0515                 | 171       | 0.0280                 |

| 19        | 0.0335                 | 95        | 0.0369                 | 172       | 0.0229                 |

| 20        | 0.4681                 | 132       | 0.0290                 | 173       | 0.0218                 |

| 21        | 0.0294                 | 133       | 0.0263                 | 174       | 0.0232                 |

| 22        | 0.0137                 | 134       | 0.0256                 | 175       | 0.0169                 |

| 26        | 0.0110                 | 135       | 0.3335                 | 176       | 0.0128                 |

| 27        | 0.1822                 | 136       | 0.0317                 | 203       | 0.0279                 |

| 28        | 0.1826                 | 137       | 0.3259                 | 204       | 0.0269                 |

| 29        | 0.0183                 | 138       | 0.0195                 | 205       | 0.0235                 |

| 30        | 0.0719                 | 139       | 0.3305                 | 206       | 0.0249                 |

| 31        | 0.0609                 | 140       | 0.0199                 | 207       | 0.0186                 |

| 32        | 0.1190                 | 141       | 0.0260                 | 208       | 0.0169                 |

| 33        | 0.1324                 | 142       | 0.0222                 | 209       | 0.0176                 |

| 36        | 0.0521                 | 143       | 0.3289                 | 210       | 0.0251                 |

| 40        | 0.0121                 | 144       | 0.0304                 | 211       | 0.0197                 |

| 41        | 0.0118                 | 145       | 0.0160                 | 212       | 0.0227                 |

| 42        | 0.0111                 | 146       | 0.0274                 | 213       | 0.0239                 |

| 43        | 0.0160                 | 147       | 0.0685                 | 214       | 0.0217                 |

| 45        | 0.0109                 | 148       | 0.5551                 | 215       | 0.0173                 |

| 46        | 0.0116                 | 149       | 0.0456                 | 216       | 0.0175                 |

| 75        | 0.0135                 | 150       | 0.0289                 |           |                        |

| 76        | 0.0128                 | 151       | 0.0191                 |           |                        |

| 77        | 0.0114                 | 152       | 0.0216                 |           |                        |

Table 4.2: Cache sets with mutual information  $I(S, \tilde{\boldsymbol{L}}_q) > 0.01.$

Remarks on Cache Set 0 As can be seen in table 4.2 cache set 0 seems to be a special case as the only cache set that is not sound. This is because we store the measurements in unsigned bytes and clamp all data exceeding this to 255. For cache set 0 all data seem to violate this constraint, therefore, cache set 0 has mean 255 and variance 0, regardless of the value of s. We have been unable to isolate the cause of this, but it is of no practical importance as cache set 0 is automatically culled.

#### Conclusion

After looking at the data in table 4.2 we conclude that there is exploitable information in the side-channel. As expected, there are certain cache sets that carry significantly more information about S than others and are the primary contributors to the leakage in the side-channel. Also, as will be shown in the next section, this leakage is more than enough to create an adversary with significant advantage.

## 4.4 Practical Results

As is seen in table 4.3 the success rate of this experiment was over 97%.