# Extending Amber with Virtual Memory

# Jakob Dagsland Knutsen

Master of Science in Computer ScienceSubmission date:Januar 2015Supervisor:Donn Morrison, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# Abstract

Since the birth of modern computer architecture, computer performance has witnessed an exponential growth, driven mainly by increased transistor density. In the last decade, performance advancement has become increasingly difficult as computers are limited by power budgets due to problems with heat dissipation. As transistor technology continues to advance, full utilization of the available silicon is becoming ever challenging. As a result, new avenues of design exploration have emerged to track down alternative routes for continued performance enhancement. One such research field concerns heterogeneous computer architectures, where cores that excel at different areas of computation are combined on a single chip in order to provide performance scaling and the assignment of process workloads to optimally suited hardware.

The SHMAC project applies heterogeneous research in a single ISA environment, where various hardware is deployed in a matrix of interchangeable tiles, with the only general purpose processor tile being an ARMv4T compliant Amber processor core.

While programs and operating systems have been proven to successfully run on the processor core, their practical use is limited by the available memory space as the core does not feature a memory management system.

This thesis introduces a memory management unit into the Amber processor, enabling virtual memory support at the hardware level. The final contribution is Vilma; an ARMv4T compliant core featuring a memory management unit, verified using hardware simulation and an assembly test suite.

# Sammendrag

Siden moderne dataarkitektur først ble til har ytelsen til datamaskiner overvært en eksponensiell vekst. Denne fremgangen er først og fremst drevet av en økt transistortetthet. Gjennom det siste tiåret har forbedring av ytelse jevnt blitt vanskeligere å realisere på grunn av begrensede strømbudsjetter forårsaket av problemer med varmeutslipp. Ettersom transistorteknologien fortsetter å avansere begynner det å bli enda mer utfordrende å realisere full utnyttelse av tilgjengelig silikon. Som en følge av dette trer det frem nye veier i utforskningen av systemdesign, med det målet å finne alternative løsninger for å jobbe videre med ytelsesforbedring. Ett av forsknigsområdene innen ytelse omhandler heterogen dataarkitektur hvor kjerner som utmerker seg på forskjellige områder innen databehandling er forbundet på en enkel chip. Dette skal sørge for ytelsesskalering og tildeling av prosessoppgaver til optimalt tilpasset hardware.

SHMAC-prosjektet bruker heterogen forskning i et enkelt ISA-miljø hvor ulike typer hardware er plassert i en matrise som utskiftsbare brikker hvor den eneste prosessorbrikken er en ARMv4T ettergivende Amber prosessorkjerne.

Selv om programmer og operativsystemer har vist seg å kjøre uten problemer på prosessorkjernen, så er den praktiske bruken begrenset av tilgjengelig plass på minnet siden kjernen ikke har et fungerende minnehåndteringssystem.

Denne avhandlingen introduserer en minnehåndteringsenhet inn i Amberprosessoren og muliggjør støtte for virtuelt minne på hardwarenivå. Det endelige produktet er Vilma; en ARMc4T ettergivende kjerne som inneholder en minnehåndteringsenhet. Enheten har blitt verifisert ved bruk av hardwaresimulering og et assembly testrammeverk.

### **Problem Description**

Task: Improving the AMBER-based Processor Core for the Heterogeneous SHMAC Multi-Core Prototype Current multi-core processors are constrained by energy. Consequently, it is not possible to improve performance further without increasing energy efficiency. A promising option for making increasingly energy efficient CMPs is to include processors with different capabilities. This improvement in energy efficiency can then be used to increase performance or lower energy consumption.

Currently, it is unclear how system software should be developed for heterogeneous multi-core processors. A main challenge is that little heterogeneous hardware exists. It is possible to use simulators, but their performance overhead is a significant limitation. An alternative strategy that offers to achieve the best of both worlds is to leverage reconfigurable logic to instantiate various heterogeneous computer architectures. These architectures are fast enough to be useful for investigating systems software implementation strategies. At the same time, the reconfigurable logic offers the flexibility to explore a large part of the heterogeneous processor design space.

The Single-ISA Heterogeneous MAny-core Computer (SHMAC) project aims to develop an infrastructure for instantiating diverse heterogeneous architectures on FPGAs. A prototype has already been developed. The current processor model is a 5-stage in-order pipelined AMBER processor. To ease software development and increase heterogeneity, this implementation should be extended.

The absence of virtual memory (VM) support is currently a major limitation to SHMAC software development.

The main task in this assignment is the development and implementation of virtual memory support for Amber. Specifically, the student shall design and implement a memory management unit (MMU) in hardware and ensure that the software component (e.g., operating system) manages the virtual address space and assignments to virtual memory from real memory. An important part of a virtual memory system is a mechanism for paging such that programs can make use of secondary storage. This has until now been a bottleneck in SHMAC, which has limited main memory. It is expected that the student will conduct a review on VM implementations, including in heterogeneous settings.

# Preface

This thesis is submitted to the Norwegian University of Science and Technology.

# Acknowledgements

I would like to thank my supervisor Donn Morrison, and co-supervisor Antonio Garcia Guirado, for their guidance. I would also like to give thanks to Benjamin Bjørnseth for keeping up with my questions and always striving to give thorough answers.

I would also like to give special thank Isa Agnete Halmøy Fredriksen for her support throughout this semester. I am truly grateful.

J.D.K.

# Contents

| st of<br>sting | Tables                                                       | 3                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| sting          |                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                       | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8              | s                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                       | xii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Intr           | oducti                                                       | on                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.1            | The D                                                        | ark Silicon Effect                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.2            | SHMA                                                         | AC                                                                                                                                                                                                                                                                                                                                                                                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.3            | Requir                                                       | rements                                                                                                                                                                                                                                                                                                                                                                                                               | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 1.3.1                                                        | Address translation                                                                                                                                                                                                                                                                                                                                                                                                   | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 1.3.2                                                        | Resource balanced $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                             | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 1.3.3                                                        | Portable                                                                                                                                                                                                                                                                                                                                                                                                              | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 1.3.4                                                        | Verified                                                                                                                                                                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.4            | Contri                                                       | butions                                                                                                                                                                                                                                                                                                                                                                                                               | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1.5            | Repor                                                        | t Outline                                                                                                                                                                                                                                                                                                                                                                                                             | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bac            | kgrour                                                       | nd                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.1            | Virtua                                                       | l Memory                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 2.1.1                                                        | Memory Hierarchy                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 2.1.2                                                        | Memory Management                                                                                                                                                                                                                                                                                                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 2.1.3                                                        | Introducing Virtual Memory                                                                                                                                                                                                                                                                                                                                                                                            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 2.1.4                                                        | Memory Management Unit                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | 2.1.5                                                        | Virtual Memory in Operating Systems                                                                                                                                                                                                                                                                                                                                                                                   | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2            | Fast A                                                       | ddress Translation                                                                                                                                                                                                                                                                                                                                                                                                    | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 2.2.1                                                        | Translation Lookaside Buffer                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.3            | ARM                                                          | MMU                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 2.3.1                                                        | About the MMU Architecture and System Overview                                                                                                                                                                                                                                                                                                                                                                        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 2.3.2                                                        | MMU Control                                                                                                                                                                                                                                                                                                                                                                                                           | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 2.3.3                                                        | Translation                                                                                                                                                                                                                                                                                                                                                                                                           | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 2.3.4                                                        | Page Faults and Access Control                                                                                                                                                                                                                                                                                                                                                                                        | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | 2.3.5                                                        | Walking the Page Table                                                                                                                                                                                                                                                                                                                                                                                                | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>Bac<br>2.1<br>2.2 | Introducti         1.1       The D         1.2       SHMA         1.3       Requin         1.3.1       1.3.2         1.3.3       1.3.4         1.4       Contri         1.5       Report         Background         2.1       Virtua         2.1.1       2.1.2         2.1.3       2.1.4         2.1.5       2.2         Fast A       2.2.1         2.3       ARM         2.3.1       2.3.2         2.3.3       2.3.4 | Introduction         1.1 The Dark Silicon Effect         1.2 SHMAC         1.3 Requirements         1.3.1 Address translation         1.3.2 Resource balanced         1.3.3 Portable         1.3.4 Verified         1.3.5 Report Outline         1.5 Report Outline         2.1 Virtual Memory         2.1.1 Memory Hierarchy         2.1.2 Memory Management         2.1.3 Introducing Virtual Memory         2.1.4 Memory Management Unit         2.1.5 Virtual Memory in Operating Systems         2.2 Fast Address Translation         2.3.1 About the MMU Architecture and System Overview         2.3.2 MMU Control         2.3.4 Page Faults and Access Control |

|              |                | 2.3.6 TLB and Caches                                      |

|--------------|----------------|-----------------------------------------------------------|

|              | 2.4            | Virtual Memory in Multicore Systems 17                    |

|              | 2.5            | Amber                                                     |

|              |                | 2.5.1 Wishbone Bus                                        |

| 3            | Vilr           | na 21                                                     |

|              | 3.1            | Design Decisions                                          |

|              | 3.2            | Architectural Overview                                    |

|              | 3.3            | MMU Implementation                                        |

|              |                | 3.3.1 MMU Schematic                                       |

|              | 3.4            | TLB Implementation                                        |

|              | 3.5            | Translation Table Walk Hardware                           |

|              | 3.6            | Access Control Hardware                                   |

|              | 3.7            | Coprocessor                                               |

| <b>4</b>     | Eva            | luation & Discussion 31                                   |

|              | 4.1            | FPGA Resource Usage                                       |

|              | 4.2            | Verification                                              |

|              |                | 4.2.1 MMU table walk                                      |

|              | 4.3            | Bugs in the pipeline                                      |

|              |                | 4.3.1 Load hazard                                         |

|              |                | 4.3.2 Store hazard                                        |

|              | 4.4            | Discussion                                                |

| 5            | Con            | clusions and Further Work 37                              |

|              | 5.1            | Assignment Requirements                                   |

|              |                | 5.1.1 Address translation                                 |

|              |                | 5.1.2 Resource balanced                                   |

|              |                | 5.1.3 Portable                                            |

|              |                | 5.1.4 Verified                                            |

|              | 5.2            | Further work                                              |

|              |                | 5.2.1 Investigate coprocessor bugs                        |

|              |                | 5.2.2 Increase TLB associativity                          |

|              |                | 5.2.3 Support entry invalidation                          |

|              |                | 5.2.4 Support other data structures                       |

|              |                | 5.2.5 Make Caches Virtually Indexed, Physically Tagged 39 |

| <b>-</b> -   |                |                                                           |

| Bi           | bliog          | raphy 41                                                  |

| $\mathbf{A}$ | $\mathbf{Syn}$ | thesis Report 43                                          |

|              | A.1            | Vilma Xilinx Mapping Report File 43                       |

|              | A.2            | Amber Xilinx Mapping Report File    45                    |

# List of Figures

| 1.1 | SHMAC High-level Architecture                                                                        | 2  |

|-----|------------------------------------------------------------------------------------------------------|----|

| 2.1 | Processor, main memory, and secondary memory in a computing system.                                  | 7  |

| 2.2 | Pages residing in memory and secondary storage                                                       | 9  |

| 2.3 | Address translation                                                                                  | 10 |

| 2.4 | Cached MMU memory system overview, from [6] p. B3-4                                                  | 12 |

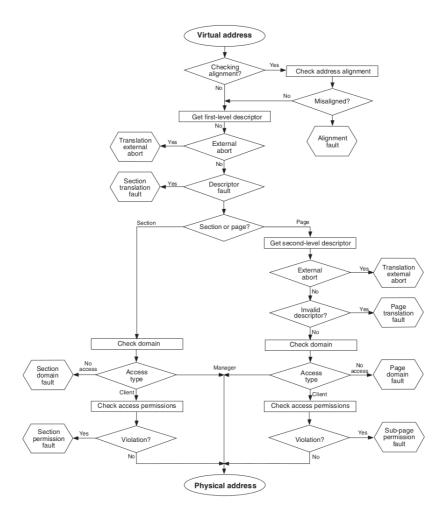

| 2.5 | Fault checking sequence, as seen in [6] p. B3-20                                                     | 15 |

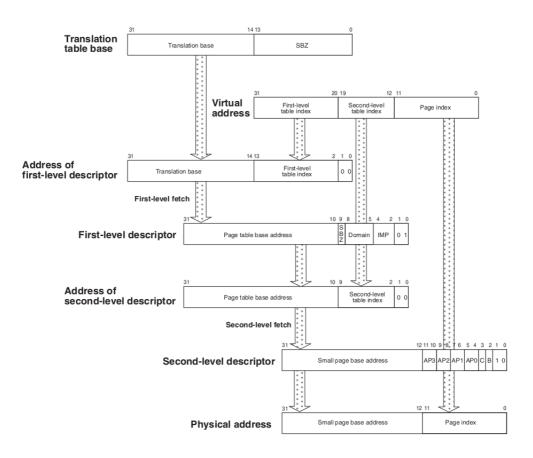

| 2.6 | Small page translation, as seen in [6] p. B3-14                                                      | 16 |

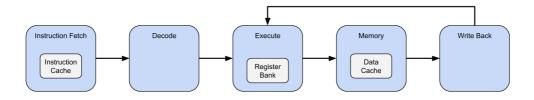

| 2.7 | The Amber core                                                                                       | 17 |

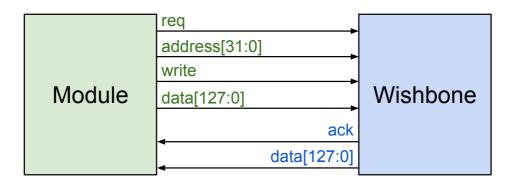

| 2.8 | Wishbone interface                                                                                   | 19 |

| 3.1 | Architectural overview of Vilma                                                                      | 22 |

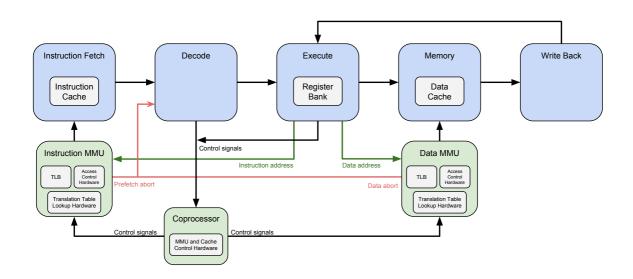

| 3.2 | Instruction address flow in Amber                                                                    | 23 |

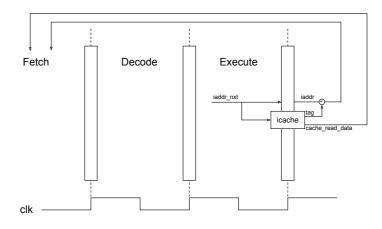

| 3.3 | Instruction address flow in Vilma                                                                    | 24 |

| 3.4 | MMU schematic                                                                                        | 26 |

| 3.5 | TLB state machine                                                                                    | 27 |

| 3.6 | Buffer registers                                                                                     | 27 |

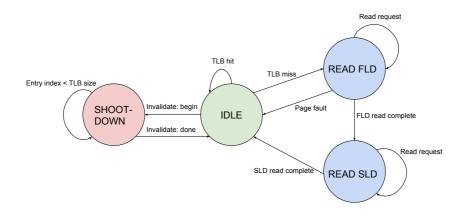

| 3.7 | TLB read process                                                                                     | 28 |

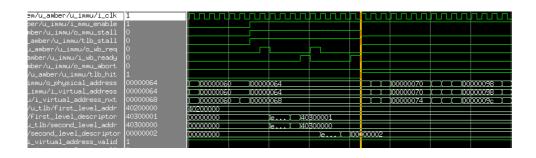

| 4.1 | Instruction MMU performing a table walk                                                              | 33 |

| 4.2 | ldr hazard                                                                                           | 34 |

| 4.3 | mcr hazard $\ldots$ | 35 |

# List of Tables

| 1.1 | Listing of the thesis requirements.                               | 3  |

|-----|-------------------------------------------------------------------|----|

| 2.1 | Listing of MMU control via system coprocessor registers           | 13 |

| 3.1 | Priority encoding of supported access control and faults in Vilma | 29 |

|     | Resource usage increase relative to Amber                         |    |

# Listings

| 3.1 | MMU abort conditional in tlb hit signal                                                           | 24 |

|-----|---------------------------------------------------------------------------------------------------|----|

| 3.2 | Cache way hit conditional in read miss signal                                                     | 25 |

| 3.3 | Cache flush control in Amber                                                                      | 29 |

| 4.1 | Address and data for fld and sld                                                                  | 33 |

| 4.2 | load r0, store r0 to coprocessor $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 34 |

| 4.3 | load r0, store r0 to coprocessor $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 35 |

# Chapter Introduction

As processor designs have undergone vast improvements in terms of performance over the last decades, the common areas exploited for this performance increase are becoming exhausted. Driven mainly by transistor technology, as predicted by Moore's law [18] and Dennard scaling [11], advancement has been achieved through increased clock frequencies and shortening of the critical path. Moore's law was predicted in 1965, and is the observation that the number of transistors that fit in a dense circuit double approximately every two years. Coupled with Dennard scaling, which states that power requirements are proportional to area, it has driven an exponential performance growth for decades. However, with the breakdown of Dennard scaling [8] in the first decade of the 21st century while Moore's law continues to hold, increased power demands challenges transistor technology, as insufficient heat dissipation is causing chips to heat up.

# 1.1 The Dark Silicon Effect

As cutting edge processor designs reached the point where it was impossible to power the whole core without damaging the chip due to the thermal increase, multicore processors allowed designers to maintain performance advancement without increasing the core clock frequency. However, the exploitable parallelism of multicore systems is reaching its limits, and with the continuation of Moore's law transistor count keeps increasing. Thus, processor design is once again faced with the problems of overheating and limitations of heat dissipation leading to wasted potential in unused transistors, otherwise known as the dark silicon effect [14].

# 1.2 SHMAC

Dark silicon is motivating the emergence of new fields of study, where different avenues of transistor utilization are explored. One such field is the area of heterogeneous processor design, where multicore processors are composed of heterogeneous cores

#### 2 1. INTRODUCTION

that have different performance and power attributes. By issuing workloads to the best suited hardware available, heterogeneous cores feature a potential to maximize performance for a given power budget. In addition, heterogeneous designs have greater potential to regulate power consumption by scaling performance according to demand, leading to a potential increase in overall energy efficiency. A use case where energy preservation is desirable in addition to periods with high performance demands, like in the mobile industry, is an applicable field for heterogeneous cores. ARMs big.LITTLE core is an example of a recent heterogeneous system that has entered the consumer market.

The EECS<sup>1</sup> group at NTNU contributes to heterogeneous research with the Single-ISA Heterogeneous MAny-core Computer (SHMAC) [4] research project. SHMAC provides an environment for heterogeneous computing research with regards to both hardware and software, and research focuses on exploring the challenges related to heterogeneous architectures.

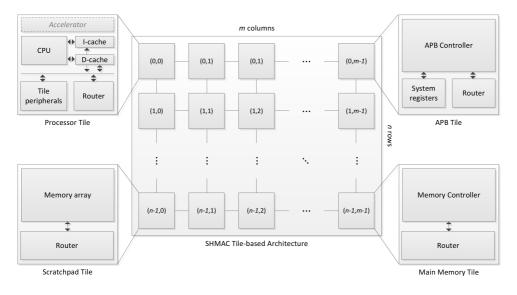

Heterogeneous research is enabled through a tiled matrix layout, where each tile can be a different processing element, and each element can talk with its nearest enighbors. Figure 1.1 shows an example of a SHMAC layout.

Figure 1.1: SHMAC High-level Architecture

The single-ISA vision in SHMAC ensures that every general purpose processing tile is able to handle any workload, regardless of differing characteristics in performance

<sup>&</sup>lt;sup>1</sup>Energy Efficient Computing Systems

and power consumption.

# 1.3 Requirements

Requirements are used to systematically evaluate the success of the thesis. In this section I present a list of requirements as I have interpreted them from the assignment text, and explain the reasoning behind each point. Some requirements are taken from the assignment text, while others have been worked out in dialog with my supervisor.

| Address translation | Vilma should be able to perform address translation in   |

|---------------------|----------------------------------------------------------|

|                     | hardware.                                                |

| Resource balanced   | FPGA resource usage of Vilma should be balanced and not  |

|                     | not greatly exceed that of Amber.                        |

| Implementable       | The mechanism for address translation in Vilma should be |

|                     | possible to implement into the original Amber core and   |

|                     | other variants of it.                                    |

| Verified            | Vilma should be extensively tested to verify the design. |

Table 1.1: Listing of the thesis requirements.

#### 1.3.1 Address translation

As specified in the assignment text, Vilma should be able to translate from virtual to physical addresses. Since the basis of Vilma, Amber, is an ARMv4T compliant processor, translation must proceed in accordance with expected behavior by software written for this architecture. This requirement is important because it determines the reusability of software that manage the virtual address space on ARM processors.

# 1.3.2 Resource balanced

As SHMAC research is performed on FPGA-chips the number of tiles in a setup is limited by the available on-chip resources. As the addition of translation hardware removes the memory bottleneck that has so far limited SHMAC software development, it would be counter productive to introduce new limitations due to resource exhaustion. FPGA-resources are measured in logic slices which inlude LUTs, and block RAM.

# 1.3.3 Portable

Introducing virtual memory to the SHMAC environment implies the use of virtual addresses across a complete tile setup. The introduced mechanism for address translation should thus be portable to Amber and variants thereof, such as the Turbo Amber core [5]. The single-ISA vision of SHMAC underlines the importance of this

#### 4 1. INTRODUCTION

point, as code that is compiled for a virtual address space must be runnable on any tile setup. This requirement demands engineering of a system with minimal implications on existing hardware.

# 1.3.4 Verified

Although not explicitly specified by the assignment text, verification of the design is implied, and is considered the most difficult part of the project. Considerable effort should be made to ensure the functional correctness of the design.

# 1.4 Contributions

This thesis contributes to the SHMAC project with the digital design of a memory management unit, written in Verilog and implemented into the Amber core. The MMU supplies the necessary hardware support to employ virtual memory as the system memory management technique, allowing main memory to be virtually extended into secondary storage. The most significant benefit of being able to use virtual memory is the elimination of the memory bottleneck that has previously limited SHMAC software research. In addition, access control hardware has been introduced to supply software with the necessary framework for applying memory protection.

# 1.5 Report Outline

The rest of the report is structured as follows:

**Chapter 2: Background** gives a historical overview of virtual memory and supplies the information necessary to understand how it works and the role it plays in a modern computer. It explains the benefits involved, and shows how performance penalties can be mitigated. It also looks closely at the literature used for development, the ARM architecture reference manual [6].

Chapter 3: Vilma details the design and implementation of the thesis contributions.

Chapter 4: Evaluation & Discussion looks at design verification and discusses the developed unit, how it turned out in terms of performance and size, and talks about problems that were encountered during development.

**Chapter 5: Conclusions and Further Work** lists the results in light of the assignment requirements, and discusses some relevant areas for further development.

The emergence of modern computer science in the 20th century gave rise to a field that has seen significant changes over the seven decades since its birth.<sup>1</sup> Technological revolutions have transformed digital computers from constructs taking up whole floors<sup>2</sup> into tiny devices of just a few grams.<sup>3</sup> Even so, the basic principle that a computer consists of a processing element and some type of memory still remains, as one has no function without the other. This inherent dependency between processing element and memory implies a limitation where not only the speed at which the processing element can process data, but also the amount of data it can process, relies on the memory's ability to serve a request.

The availability of high-speed computer memory has a direct impact on performance, and large amounts have generally always been expensive. Insufficient amounts of main memory due to program size and lack of hardware motivated programmers to introduce systems for memory management as early as in the 1940's and 1950's. Denning [12] describes how programming at that point was performed at a very basic level and required a thorough understanding of the underlaying hardware. As such, the programmer would identify the independent blocks of code in a program, and instruct which block would be in memory at different points in time during execution. This technique, called overlaying, was sufficient for the time as there was little demand for resource sharing between programs and the programmer usually had direct hardware access.

After higher level programming languages were developed in the mid 1950's, layers of abstraction supplied greater tools for development and focus began to move away from machine details and over to software. As the complexity of programs increased, so did the the development overhead involved with overlaying.

<sup>&</sup>lt;sup>1</sup>The Z3 of 1941 was the first working programmable, fully automatic digital computer [21].

<sup>&</sup>lt;sup>2</sup>The ENIAC of 1946 was roughly 2.4m by 0.9m by 30m and weighed about 27 tons [?].

$<sup>^{3}</sup>$ Microcontrollers can typically weigh just a few hundred grams and have more processor power than the ENIAC [17].

Significant performance penalties would ensue under the employment of inadequate overlaying strategies, and as development continued the burden of constructing a sufficient memory management system increased. This led to demands for systems with large amounts of main memory [2]. As demands in turn increased for resource sharing between processes, security issues became a problem due to the fact that software with direct memory access may interfere with the process state of other programs.

In 1961, research conducted at the Manchester University during the development of the Atlas computer [13][16] introduced a new technique which efficiently solved the issues related to memory management. The technique is called virtual memory, and has had profound influence on computer architecture since its invention.

In this Chapter I will provide an overview of virtual memory as a memory management technique and show how the ARM memory system is built. The Amber core is discussed in light of how the ARM Architecture Reference Manual for ARMv4T employs the memory management unit, and methods of fast address translation are also introduced.

# 2.1 Virtual Memory

In the following section I will introduce the components necessary to understand what virtual memory is and the role it plays in a computer system. The discussion will start by looking closer at the motivation behind memory management, and introduce all hardware and software systems that play a part in the enabling and execution of virtual memory as a memory management system.

# 2.1.1 Memory Hierarchy

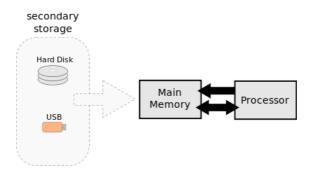

In order to explain virtual memory it is first necessary to understand the memory hierarchy as well as how the computer handles a running program. The chosen computing system model is as depicted in Figure 2.1, showing the relevant hardware as the processor, volatile main memory, e.g., RAM blocks, and non-volatile secondary storage, e.g., hard disk or flash memory. In this document, *main memory* will also be referenced as *physical memory*, or simply *memory*. The software pieces involved are the operating system and any number of running programs present in main memory.

Figure 2.1: Processor, main memory, and secondary memory in a computing system.

When power is off, all information resides on secondary storage. As the processor boots up it loads data from secondary storage into main memory, the first program being the operating system. The operating system can then initiate a running instance of another program stored on secondary storage, by moving it into main memory. A running program is called a process.

# 2.1.2 Memory Management

This subsection is introduced to provide a more detailed explanation of the motivation behind memory management, and the challenges it faces.

To run a process on a computer there are two main criteria. One, all program code must be accessible or the processor will not have instructions to execute. Two, all existing program data has to be accessible, including any new data that may be generated during runtime, or the process state will be inaccurate and cause the program to malfunction. For both code and data to be accessible, it must exist in main memory.

Now consider a 32-bit system with 2GiB of physical memory installed, with no operating system and only one running process.<sup>4</sup> Since the byte-addressable address space of  $2^{32}$  is 4GiB, the lack of physical memory is cause for an unused potential of 2GiB of the address space. Still, the program can be coded to start at address zero with an address space of 2GiB and all will be fine. Problems start to arise however, when a second process is introduced to the system. At which address should the new process start, how much space should it be given, and how is the first process notified of the newly introduced process. What if the first process generates data that enters the memory area of the second, overwriting data or instructions. And

<sup>&</sup>lt;sup>4</sup>For the purpose of the example assume that the process can load without the help of an OS.

how can a program ensure the integrity of its own process state when other software may interfere with its data.

In summation, memory management is challenges in three areas;

- 1. Unused address space

- 2. Resource sharing

- 3. Protection

#### 2.1.3 Introducing Virtual Memory

Virtual memory uses a combination of hardware and software to create an abstraction of main memory that solves the challenges with memory management. The software component is part of the operating system and manages a file structure, called a page table, for each process, containing virtual to physical address mappings. The hardware component uses the contents of the page table to perform fast address translation during runtime.

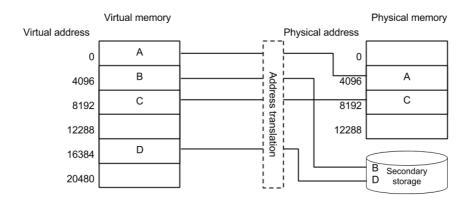

By splitting physical memory pages and adding the layer of translation, a virtual address space is created [20] where it is possible to move pages in and out of memory without breaking process execution. Figure 2.2 shows how a process may have addresses mapped to pages that reside in both memory and secondary storage. A result of this is that processes can use the whole 32-bit address space, given there is enough space on disk.<sup>5</sup> In addition, it does not matter where in memory a block is mapped to, which means a program can run from any location in main memory. This feature is called *relocation* and simplifies loading programs for execution.

To elaborate, consider again what happens when a program is instantiated on a computer. The operating system moves the executable file into memory and the processor starts executing the instructions within. Some of these instructions may be used to prepare the initial environment for the process, and once executed will not be referenced again for the duration of the process. The observation that memory may contain inactive code, and that the active part of a program differs during process execution, gives ground for a memory management system where only the active parts of a program are kept main memory. Inactive parts may then be moved to secondary storage, freeing memory space.

To employ a virtual address space a system needs to be able to perform the necessary translations, as well as manage the mappings. Address translation and management

$<sup>^{5}</sup>$ The virtual address space is generally larger than the physical address space, although it does not have to be and exceptions can occur for systems where external storage is limited.

Figure 2.2: Pages residing in memory and secondary storage

is performed automatically by the Memory Management Unit  $(MMU), {\rm described}$  below.

#### 2.1.4 Memory Management Unit

The MMU can be thought of as a unit that extends into two places, with one piece in hardware and another in software, however only the hardware is referenced as the MMU. The MMU is the logic that performs the actual address translation, while the software builds and manages page tables. The software is usually contained within the operating system. Together, these two pieces make up the system that applies the necessary translation layer required for virtual memory.

To keep track of process data, the OS keeps a data structure for every active program where it maps virtual page numbers to a physical page number or disk location. This map is called a *page table*, and the blocks of data are *pages*. A page location recorded in the page table is called a *page table entry*. When a reference occurs to a page that is not present in main memory the hardware will notify the OS. The OS is in turn responsible for bringing that page into memory, and updating the corresponding physical page number of the page table entry.

Figure 2.3 shows an example of how address translation works. The virtual page number is looked up in the page table and the corresponding physical page number is used for the memory access. The page table, indexed by the virtual page number, is sized at the number of pages in the virtual address space. With 32-bit addresses, 4KiB pages, and 4 bytes per page table entry, this adds up to  $(2^{32}/2^{12}) * 2^2 = 2^{22}$ . Consequently, the OS keeps a 4MiB table for every process.

Figure 2.3: Address translation

# 2.1.5 Virtual Memory in Operating Systems

In theory, the maximum addressable area is limited only by the processor architecture *e.g.* 4GiB for a 32-bit system. However, kernel data vital for system operation must always be present in memory, which excludes portions of the address space from paging. The exact method used to achieve this behavior may vary between OSes, but for Linux and Windows the addressable area is divided into kernel and user space. A common split is 1GiB/3GiB for 32-bit systems, but Windows will in some cases split it 2GiB/2GiB. A process may only use addresses of the user space, while the OS may access the address space in its entirety.

The OS maps the virtual address space for each process through the page table, and allocates page entries on demand. On page faults, the page fault handler is activated by the processor as it branches to a predefined address where this handler starts, and it is up to this software to determine what to do next.

#### 2.2 Fast Address Translation

A system using virtual memory may take a significant performance hit as the amount of memory accesses are effectively doubled; one access to translate, another to perform the operation. This penalty grows even larger in systems where the page table itself is paged. It can, however, be significantly reduced by adding a buffer for the translations. This buffer exploits the high spacial locality associated with address translation [20], and is called a translation lookaside buffer, or TLB.

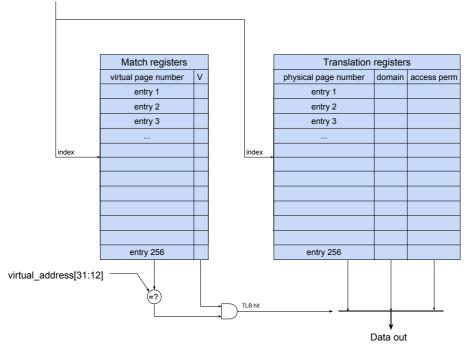

#### 2.2.1 Translation Lookaside Buffer

The TLB functions as a translation cache, tagged by the virtual address, and holds the corresponding translation in the data field. Each translation is accompanied by a reference bit, valid bit, dirty bit, and a protection field.

The reference bit is used by the replacement algorithm of the OS, while the dirty bit signals whether the corresponding page has been modified (not the TLB entry itself). The vaild bit is used to determine if an entry is active, and the protection field holds access permission bits associated with the page. The operating system manages these bits by updating the page table and invalidating the corresponding entries.

# 2.3 ARM MMU

The ARM architecture used in this thesis is ARMv4T, which is the current version of the Amber core used in SHMAC [15]. More on Amber can be found in Section 2.5. ARM DDI 0100E [6] is the ARM Architecture Reference Manual used in the development. While this manual covers versions up to ARMv5TE, the Preface on *Architecture versions and variants* states no difference in MMU architecture from v4 to v5, and is assumed safe to use.

#### 2.3.1 About the MMU Architecture and System Overview

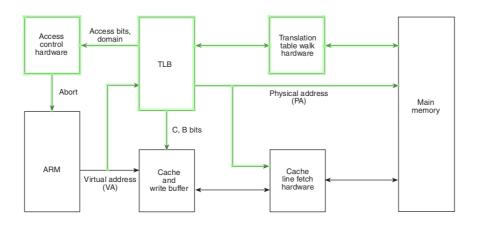

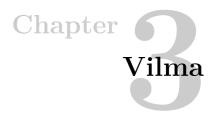

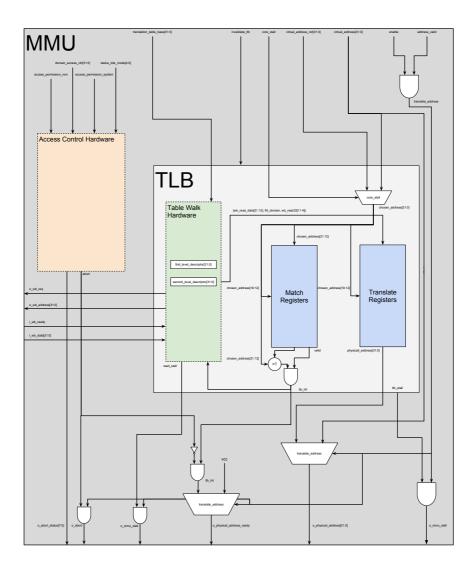

ARM is a Harvard Architecture and consequently employs separate instruction and data memory, which means there must be separate MMU and TLB for each memory interface [6]. Figure 2.4 shows how the memory system is organized. The green areas are part of the MMU design while the rest is present in the Amber core.

Figure 2.4: Cached MMU memory system overview, from [6] p. B3-4

A memory access issued by the ARM core starts with a virtual address passed from the core to both cache and TLB. If the requested data is cached we have a hit and normal operation follows the next cycle. On a miss, the TLB will walk the page table and return the physical address to the cache. Each memory access also passes through access control hardware that will raise an MMU fault for invalid accesses, invoking the OS access permission handler.

# 2.3.2 MMU Control

Control of the MMU is done via a coprocessor. The ARM core offers support for up to 16 coprocessors, using 4 bits to address them.<sup>6</sup> Some coprocessors are reserved for specific functions, like coprocessor number 15 which is the designated system control coprocessor.

The MMU is controlled by coprocessor number 15, the system coprocessor, using coprocessor instructions mrc and mcr on registers 2, 3, 4, 5, 6, 8 and 10, and some bits of register 1 [6].

Writing to a coprocessor register triggers a hardware response, but does not necessarily mean that data is written to a particular register. Only data that may be required more than once cycle is registered, like the MMU enable bit. Table 2.1 describes the different registers, the data field bits, and their functions. A complete description can be found in [6] B3.7.

$<sup>^{6}</sup>$ There are 16 coprocessors where the lowest is number 0 and the highest is number 15.

| Reg | Bits    | Function                                                  |

|-----|---------|-----------------------------------------------------------|

| c1  | [0]     | MMU enable/disable                                        |

|     |         | 0 = disabled                                              |

|     |         | 1 = enabled                                               |

|     | [1]     | Alignment fault checking enable/disable                   |

|     |         | 0 = disabled                                              |

|     |         | 1 = enabled                                               |

|     | [8]     | System protection bit, used in Access permissions         |

|     | [9]     | ROM protection bit, used in Access permissions            |

| c2  | [31:14] | Translation table base                                    |

| c3  | [31:0]  | Domain access control                                     |

| c4  | [31:0]  | Reserved                                                  |

| c5  | [3:0]   | Fault status: Indicate the type of access being attempted |

|     | [7:4]   | Fault status: Specify which domain was being accessed     |

|     | [8]     | Fault status: Returns zero                                |

| c6  | [31:0]  | Fault address                                             |

| c8  |         | TLB invalidate functions (shootdown)                      |

| c10 |         | TLB lockdown                                              |

Table 2.1: Listing of MMU control via system coprocessor registers

#### 2.3.3 Translation

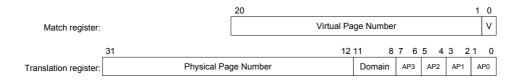

The MMU supports the use of pages and sections. Pages can be tiny, small, or large, with a block size of 1KiB, 4KiB, and 64KiB, respectively. Sections are comprised of 1MiB blocks of data. Sections and large pages are supported for mapping large regions of memory while using only a single entry in the TLB. For pages, the translation table is split into two levels that hold first- and second-level descriptors.<sup>7</sup> The translation process runs in hardware on every TLB miss occurrence, and is depicted as the *translation table walk hardware* box of Figure 2.4.

The first step retrieves the first-level descriptor by combining the contents of the translation base register (system coprocessor register 2) with the first-level table index of the virtual address. The first-level descriptor contains the base pointer to the second-level descriptor in addition to domain access control bits. The domain bits are used for setting access permission to large areas at a time in conjunction with access permission bits of the second level. The address for the second-level descriptor is formed by the page table base address of the first-level descriptor and the

<sup>&</sup>lt;sup>7</sup>The process for a small page table is presented due to its use in the Amber system.

second-level table index of the virtual address. The second-level descriptor consists of the page base address (the physical page number) and access permission bits.

# 2.3.4 Page Faults and Access Control

Access control is performed by the access control hardware depicted in Figure 2.4, which notifies the processor of errors that occur during address translation. This is done through the use of an abort signal coupled with status bits that detail the fault specifics, and are acted upon differently depending on the source of the error. For a data access, a Data Abort signal is passed to the processor and the Fault Status Register and Fault Address Register (registers 5 and 6 in Table 2.1) are updated with information detailing the exception. For instruction fetch, a Prefetch Abort signal is issued to the processor. No additional information is collected in the case of a Prefetch Abort, and the exception for an instruction that does not execute, for example, due to a branch. By not setting the Fault Status Register and Fault Address Register for a Prefetch Abort, data integrity for these registers is ensured in the case where a Prefetch Abort would corrupt the data before being branched past. On any abort, the processor will branch to a defined address where the appropriate actions.

Figure 2.5 shows the fault checking sequence of the ARM processor. The points of interest are the descriptor fault checks after each descriptor fetch, which checks bits[1:0] of the descriptor. The value 'b00 determines an invalid descriptor, where the first descriptor check will signal a section fault and the second a page fault. Domain and access permission checks verify user access rights.

External aborts are caused by errors in the memory system rather than those caught by the MMU. These are expected to be extremely rare and likely fatal to the running process.

# 2.3.5 Walking the Page Table

On a TLB miss the ARM TLB will automatically look up the missed entry in the page table. To look up a page table entry, memory accesses are placed on the memory bus twice; once to retrieve the first-level descriptor, and once again to retrieve the second-level descriptor. Due to the way page table entries are retrieved, the action is referenced as a *page table walk*. A high-level overview of the hardware is shown in Figure 2.4.

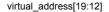

Figure 2.6 details the process of translation for a small page. Bits [31:14] of the translation table base register in the coprocessor are concatenated with bits [31:20] of the virtual address along with two zeros, forming the 32-bit address of the fld.

Figure 2.5: Fault checking sequence, as seen in [6] p. B3-20

The two zeros ensure the beginning of each word is addressed in the byte-addressable address space. The fld address is then placed on the memory bus until the fld is retrieved.

Looking closer at the fld, bits [1:0] are used to determine page presence in memory and the value 'b00 will trigger a page fault. The value 'b01 indicates a valid first-level descriptor. The address for the sld is formed by fld bits [31:10], concatenated with bits [19:12] of the virtual address, and two zeros. In reference to bits [9] and [4:2], SBZ stands for *should be zero* and the meaning of IMP is *implementation defined*. The domain bits are used by the access control hardware.

Figure 2.6: Small page translation, as seen in [6] p. B3-14

Looking at the second-level descriptor, bits[1:0] determine page validity in the same way as for the fld, where the value 'b00 will trigger a page fault. Bits [11:4] are used by the access control hardware, and the C (cacheable) and B (bufferable) control the cache and write buffer. Bits [31:12] represent the physical page number, and concatenation with the page index forms the physical address.

# 2.3.6 TLB and Caches

PIPT caches are simple and avoids problems with aliasing as described by [9][10], but suffer a performance penalty as the virtual address must be translated before it can be sent to cache.

There are two ways to solve this problem, where one is more efficient than the other at a cost of increased complexity. The simplest way is to stall the core while the TLB reads, adding a delay of one cycle for every instruction. The more advanced way is to pipeline the MMU, increasing the penalty of pipeline flushes. Once again, simplicity has been favored over performance, and the former solution was chosen.

#### 2.4 Virtual Memory in Multicore Systems

Early recognition of TLB influence on system performance steered uniprocessor designs into adapting the multilevel hierarchies used for caching in TLBs. As chip multiprocessors become more mainstream, TLBs have been exposed to coherency issues with implications on performance. Various strategies have been explored to increase performance and simplify design. A common design is to keep an MMU and the TLB hierarchy for each core, (and perform TLB shootdowns when pages are invalidated?)