# Real-time reconfigurable devices implemented in UV-light programmable floating-gate CMOS

by

Snorre Aunet

June 2002

A dissertation submitted to the Norwegian University of Science and Technology Faculty of Information Technology, Mathematics and Electrical Engineering in partial fulfillment of the requirements for the degree of Doktor Ingeniør.

#### Abstract

This dissertation describes using theory, computer simulations and laboratory measurements a new class of real time reconfigurable UV-programmable floating-gate circuits operating with current levels typically in the pA to  $\mu$ A range, implemented in a standard double-poly CMOS technology. A new design method based on using the same basic two-MOSFET circuits extensively is proposed, meant for improving the opportunities to make larger FGUVMOS circuitry than previously reported. By using the same basic circuitry extensively, instead of different circuitry for basic digital functions, the goal is to ease UV-programming and test and save circuitry on chip and I/O-pads. Matching of circuitry should also be improved by using this approach.

Compact circuitry can be made, reducing wiring and active components. Compared to earlier FGUVMOS approaches the number of transistors for implementing the CARRY' of a FULL-ADDER is reduced from 22 to 2. A complete FULL-ADDER can be implemented using only 8 transistors. 2-MOSFET circuits able to implement CARRY', NOR, NAND and INVERT functions are demonstrated by measurements on chip, working with power supply voltages ranging from 800 mV down to 93 mV. An 8-transistor FULL-ADDER might use 2500 times less energy than a FULL-ADDER implemented using standard cells in the same 0.6  $\mu$ m CMOS technology while running at 1 MHz. The circuits are also shown to be a new class of linear threshold elements, which is the basic building blocks of neural networks. Theory is developed as a help in the design of floating-gate circuits.

#### Preface

I have had the great pleasure of working with UV-programmable floatinggate ("FGUVMOS") circuits for a period. It has first and foremost been interesting and rewarding, but also hard work. Support from the surroundings has been of paramount importance:

I am very grateful to my supervisors, professors Trond Sæther, NTNU, and Yngvar Berg at the University of Oslo. They gave great support at various levels, including moral support, in seeking financial support, making various decisions, and writing and discussing technological issues.

Thanks also to associate professor Tormod Njølstad, Department of Physical Electronics, NTNU, for initiating my first meeting with FGU-VMOS circuits by arranging a trip to the Department of Informatics, University of Oslo.

I would also like to thank the Microelectronics group at the Department of Informatics (Ifi), University of Oslo, for accepting me as an occasional coworker and guest during these years.

Dag T. Wisland (Ifi) deserves thanks for SW-support and laboratory support during my visits to Ifi. Shevana Bianca Aquariux was of great help in many discussions. Associate professor Nancy Lea Eik-Nes gave help with writing of the manuscript. Thanks to professor Steinar Andresen, NTNU, for financial support for producing chips, going to conferences and more, through the Telecom 2005 programme. Thanks to Sverre Vegard Pettersen for taking the chip photos.

Thanks also to colleagues at the Department of Physical Electronics, NTNU, for nice working conditions since May 1997, and lately the Department of Computer and Information Science, NTNU. Thanks also to my family and friends for help, support and patience.

Trondheim, June 2002

Snorre Aunet

## Contents

| $\mathbf{A}$ | bstra | let                                                      | iii       |

|--------------|-------|----------------------------------------------------------|-----------|

| Pı           | refac | e                                                        | iv        |

| 1            | Intr  | oduction                                                 | 1         |

|              | 1.1   | The neuron-MOS and FGUVMOS circuit concepts              | 1         |

|              | 1.2   | New real time reconfigurable floating-gate circuits      | 5         |

|              | 1.3   | Thesis outline                                           | 9         |

| <b>2</b>     |       | ltiple-input UV-programmable MOSFETs and two-MOS         | SFET      |

|              | circ  | uits                                                     | 11        |

|              | 2.1   | MOSFETs                                                  | 11        |

|              |       | 2.1.1 MOSFETs in weak inversion                          | 11        |

|              |       | 2.1.2 Floating-gate CMOS transistors                     | 18        |

|              |       | 2.1.3 Single-input floating-gate MOSFETs                 | 21        |

|              |       | 2.1.4 Multiple-input floating-gate CMOS transistors      | 28        |

|              | 2.2   | UV-programmable inverters                                | 31        |

|              | 2.3   | A 2-MOSFET 3-input reconfigurable "single-ended" circuit | 39        |

| 3            | Floa  | ating-Gate UV-programmable MOSFETs                       | <b>45</b> |

|              | 3.1   | Implementation and layout of FGUVMOS transistors         | 45        |

|              | 3.2   | Laboratory setup and UV-programming                      | 52        |

|              | 3.3   | Measurement Results                                      | 59        |

|              | 3.4   | MOSFET discussion                                        | 72        |

| <b>4</b>     | Floa  | ating-gate UV-programmable inverters                     | 75        |

|              | 4.1   | Implementation and layout of inverter                    | 75        |

|              |       | 4.1.1 Simulation of the FGUVMOS inverter                 | 75        |

|              |       | 4.1.2 Layout of the FGUVMOS inverter                     | 81        |

|              | 4.2   | UV-programming and test setup                            | 83        |

v

|          |     | 4.2.1    | Basic information regarding UV-programming and                                 |            |

|----------|-----|----------|--------------------------------------------------------------------------------|------------|

|          |     |          | test setup                                                                     | 83         |

|          |     | 4.2.2    | UV-programming taking from tens of minutes to many hours for a few transistors | 85         |

|          |     | 4.2.3    | Additional information regarding UV-programming                                | ~          |

|          |     | _        | and test setup                                                                 | 85         |

|          | 4.3 |          | er measurement results                                                         | 89         |

|          | 4.4 |          | ation of maximum operational frequency as a function                           |            |

|          |     |          |                                                                                | 96         |

|          | 4.5 | Invert   | er discussion                                                                  | 104        |

| <b>5</b> | Mu  |          | nput floating-gate 2-MOSFET "PMNM" circuits                                    |            |

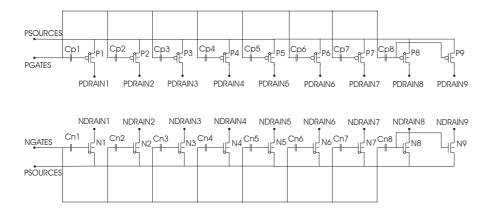

|          | 5.1 |          | mentation and layout of "PMNM" elements                                        | 109        |

|          |     | 5.1.1    | P3N3 element                                                                   | 109        |

|          |     | 5.1.2    | P5N5 element                                                                   | 112        |

|          |     | 5.1.3    | "PMNM" layout                                                                  | 117        |

|          | 5.2 | -        | cogramming and test setup of P5N5 element                                      | 120        |

|          | 5.3 | P5N5     | results                                                                        | 124        |

|          |     | 5.3.1    | Simulation results                                                             | 124        |

|          |     | 5.3.2    | Measurement results                                                            | 124        |

|          | 5.4 | PMN      | M discussion                                                                   | 131        |

| 6        | Mu  | ltiple-i | nput floating-gate 2-MOSFET "P1NM" circuits                                    | <b>133</b> |

|          | 6.1 | -        | mentation and layout of "P1NM" elements                                        | 133        |

|          |     | 6.1.1    | P1N2                                                                           | 133        |

|          |     | 6.1.2    | P1N3                                                                           | 137        |

|          | 6.2 | -        | cogramming and test setup of the P1N3 element $\ldots$                         | 137        |

|          | 6.3 | P1N3     | results                                                                        | 141        |

|          | 6.4 | P1NM     | I / PMN1 discussion                                                            | 147        |

| 7        | INV | /ERTI    | ERS, "P1NN" and "PMNM" as building blocks                                      | 149        |

|          | 7.1 | Basic    | digital functions                                                              | 149        |

|          |     | 7.1.1    | Generating Boolean functions using PMNM and P1NM                               | -          |

|          |     |          | building blocks                                                                | 149        |

|          |     | 7.1.2    | Simulation of a 4-transistor circuit able to generate                          |            |

|          |     | <b>-</b> | SUM' and CARRY'                                                                | 154        |

|          |     | 7.1.3    | Area of a Boolean function generator using minimum                             |            |

|          |     |          | transistors                                                                    | 156        |

|          |     |          |                                                                                |            |

|          |     | 7.1.4    | Discussion regarding FGUVMOS binary function gen-<br>eration                   | 157        |

|    | 7.2   | 8-tran           | sistor FULL-ADDERs                                            | 158   |

|----|-------|------------------|---------------------------------------------------------------|-------|

|    |       | 7.2.1            | Implementation and layout of FULL-ADDERs                      | 158   |

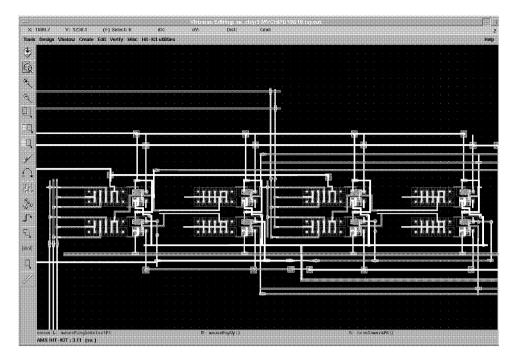

|    |       | 7.2.2            | Functionality and Power-Delay-Product simulations             |       |

|    |       |                  | of 8-transistor FULL-ADDER                                    | 161   |

|    |       | 7.2.3            | FULL-ADDER discussion                                         | 164   |

|    | 7.3   | D-Lat            | ch                                                            | 169   |

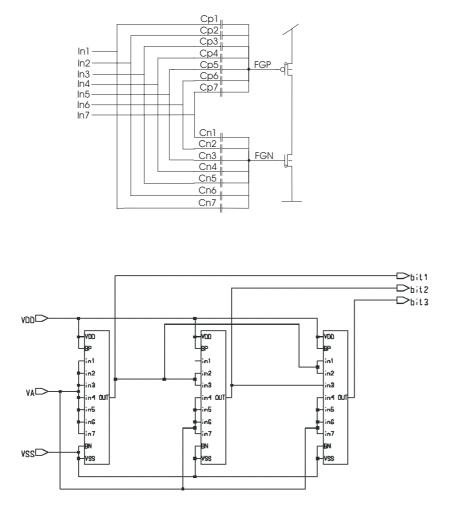

|    | 7.4   | 6-tran           | nsistor 3-bit ADC / Frequency synthesizer                     | 171   |

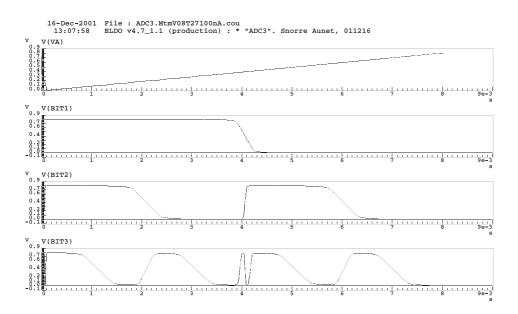

|    |       | 7.4.1            | Implementation and simulation of $ADC3$ / Frequency           |       |

|    |       |                  | Synthetisator                                                 | 171   |

|    |       | 7.4.2            | ADC / frequency synthesizer discussion $\ldots \ldots \ldots$ | 174   |

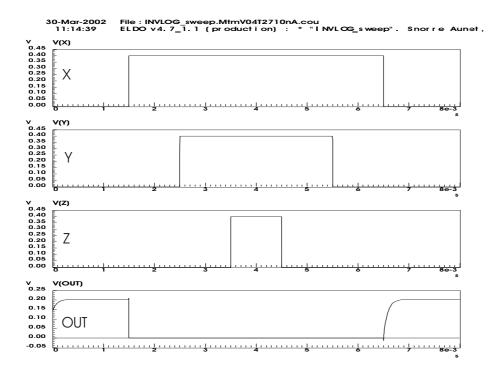

|    | 7.5   | Invert           | ter-only based logic                                          | 175   |

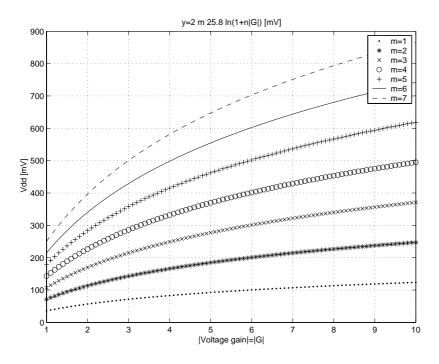

|    | 7.6   | Theor            | retical lower voltage bound and voltage gain                  | 176   |

|    | 7.7   | Imple            | menting linear threshold functions                            | 179   |

|    |       | 7.7.1            | Linear threshold elements and neural networks $\ . \ .$       | 179   |

|    |       | 7.7.2            | Mathematical definition of the FGUVMOS linear thresh          | h-    |

|    |       |                  | old gates                                                     | 180   |

|    |       | 7.7.3            | Circuit complexity and costs of linear threshold gates        | 180   |

|    |       | 7.7.4            | A new type of threshold gate                                  | 182   |

|    |       | 7.7.5            | The pFET synapse transistor - for neural networks             |       |

|    |       |                  | in hardware, or systems-on-a chip                             | 182   |

|    |       | 7.7.6            | FGUVMOS linear threshold elements                             | 184   |

|    | 7.8   |                  | taneous UV- programming of different circuit structures       | 5 186 |

|    |       | 7.8.1            | Problems connected to programming different basic             |       |

|    |       |                  | circuit structures on the same die                            | 186   |

|    |       | 7.8.2            | Possibilities towards programming different basic cir-        |       |

|    |       |                  | cuit structures on the same die                               | 189   |

| 8  | Cor   | nclusio          | ng.                                                           | 191   |

| 0  | 8.1   |                  | r Contributions                                               | 191   |

|    | 8.2   | -                | dary results                                                  | 191   |

|    | 8.3   |                  | er Work                                                       | 192   |

|    | 0.0   | 1 ul th          |                                                               | 130   |

| Bi | bliog | graphy           | 7                                                             | 194   |

| Aj | ppen  | dices            |                                                               | 207   |

| A  | Mea   | asuren           | nent setup details                                            | 207   |

|    |       |                  | ode for UV-programming and test                               | 213   |

|    |       |                  | and test                                                      |       |

| C  | Pin   | $\mathbf{lists}$ |                                                               | 221   |

#### **D** Publications

## List of Figures

| 1.1  | Programming the floating-gate.                                 | 2  |

|------|----------------------------------------------------------------|----|

| 1.2  | FGUVMOS FULL-ADDER from IEEE Transactions on Cir-              |    |

|      | cuits and Systems, 1999                                        | 3  |

| 1.3  | FGUVMOS FULL-ADDER from IEEE Transactions on Cir-              |    |

|      | cuits and Systems, 1999, detailed schematics                   | 4  |

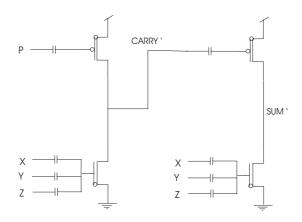

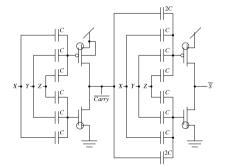

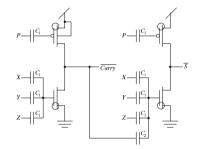

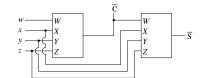

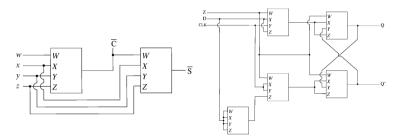

| 1.4  | Schematic for circuit generating SUM' and CARRY' using         |    |

|      | two P5N5 elements.                                             | 6  |

| 1.5  | Schematic for circuit generating SUM' and CARRY' using         |    |

|      | two P1N3 elements.                                             | 8  |

| 2.1  | Simulated NMOS drain currents for $V_{qs}$ from 0 to 2 V       | 13 |

| 2.2  | exp(ax) function simulated using Matlab.                       | 14 |

| 2.3  | Simulated NMOS drain currents for $V_{ds}$ from 0 to 2 V       | 15 |

| 2.4  | Simulated NMOS drain transconductance for $V_{ds}$ from 0 to   |    |

|      | 2 V                                                            | 16 |

| 2.5  | Simulated NMOS output resistance for $V_{gs}$ from 0 to 2 V.   | 17 |

| 2.6  | Simple model of floating-gate transistor                       | 18 |

| 2.7  | Capacitive division involving the drawn capacitance between    |    |

|      | input and floating gate and parasitics                         | 19 |

| 2.8  | $\exp(0.67 \operatorname{ax})$ function graph.                 | 20 |

| 2.9  | Schematic for subthreshold capacitances                        | 22 |

| 2.10 | Transient simulation of parasitic capacitances of inverter.    | 23 |

| 2.11 |                                                                |    |

|      | and $I_{bea}$                                                  | 24 |

| 2.12 | Transient simulation showing fractions of input voltage reach- |    |

|      | ing floating gates.                                            | 25 |

| 2.13 | Percentage of input signals reaching floating gates for two    |    |

|      | different capacitances between input and floating gates        | 26 |

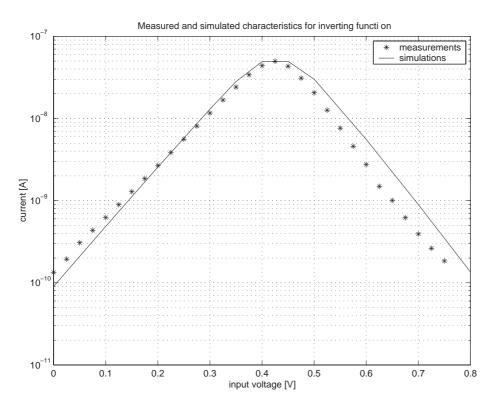

| 2.14 | Measured and simulated currents through P5N5 circuit used      |    |

|      | as an inverter.                                                | 27 |

ix

| 2.15         | Capacitive voltage divider.                                                                                          | 28         |

|--------------|----------------------------------------------------------------------------------------------------------------------|------------|

| 2.16         | Transconductance and output resistance as functions of other                                                         |            |

|              | parameters                                                                                                           | 30         |

| 2.17         | Schematic for universal FGUVMOS element.                                                                             | 34         |

| 2.18         | Simulated output voltages as a function of input voltage, for                                                        |            |

|              | two different drawn capacitances between input and floating                                                          |            |

|              | gates                                                                                                                | 35         |

| 2.19         | Truth table for FGUVMOS inverter.                                                                                    | 35         |

| 2.20         | Simulated output voltages as a function of equilibrium cur-                                                          |            |

|              | rent, $I_{beq}$ levels                                                                                               | 36         |

| 2.21         | Schematic for analog inverter                                                                                        | 37         |

| 2.22         | Simulated output voltage as a function of input voltage for                                                          |            |

|              | analog inverter                                                                                                      | 38         |

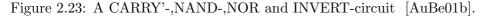

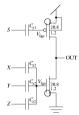

| 2.23         | A CARRY'-,NAND-,NOR and INVERT-circuit [AuBe01b].                                                                    | 39         |

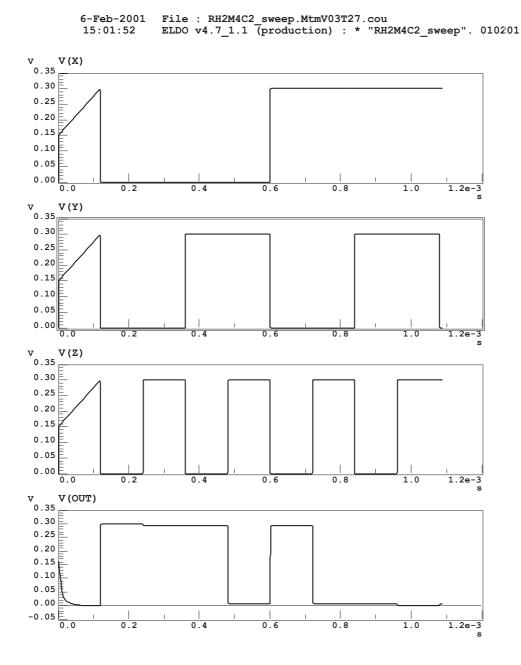

| 2.24         | Explanation of synonyms for "1" and "0" levels                                                                       | 40         |

| 2.25         | Truth table for CARRY' function of FULL-ADDER when                                                                   |            |

|              | implemented using P1N3 circuit                                                                                       | 40         |

| 2.26         | "Threshold logic-style" truth table for CARRY' function of                                                           |            |

|              | FULL-ADDER when implemented using P1N3 circuit                                                                       | 41         |

| 2.27         | Parts of exponentials for drain current equations as a func-                                                         |            |

|              | tion of 1s in the binary input                                                                                       | 42         |

| 2.28         | Table describing digital functionality of P1N3 circuit                                                               | 43         |

| 2.29         | Simulated CARRY' function implemented by P1N3 circuit.                                                               | 44         |

| 3.1          | Schematic for single PMOS and NMOS transistors on 68 pin                                                             |            |

| 0.1          |                                                                                                                      | 46         |

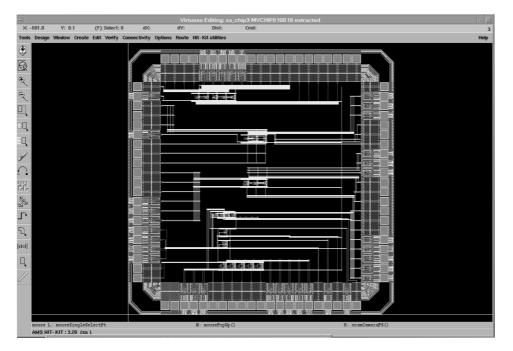

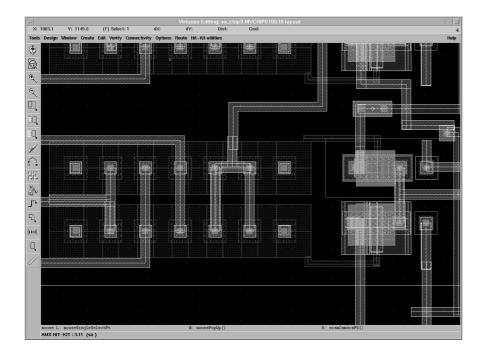

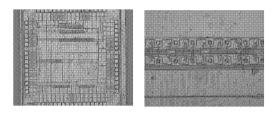

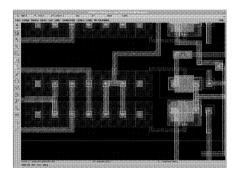

| 3.2          | chip                                                                                                                 | 40<br>46   |

| 3.2<br>3.3   | Picture of first 68 pin chip.                                                                                        | 40         |

|              |                                                                                                                      | 41         |

| 3.4          | Table for single transistors on 68 pin chip and relevant dimensions.                                                 | 48         |

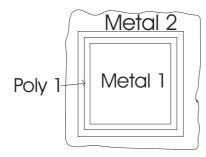

| 3.5          | Layout of $20.8\mu m/1.2\mu m$ FGUVMOS transistor.                                                                   | 48<br>49   |

| 3.6          | Drawing of metal shielding of transistors.                                                                           | 49<br>50   |

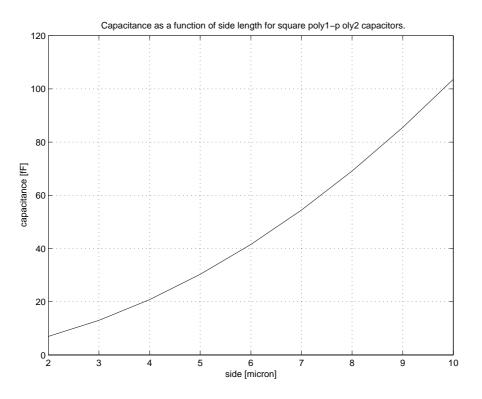

| $3.0 \\ 3.7$ | Graph showing capacitance values as a function of side lengths                                                       | 50         |

| 0.7          | for square capacitors                                                                                                | 50         |

| 3.8          | Simple sketch of laboratory setup for UV-programming of                                                              | 50         |

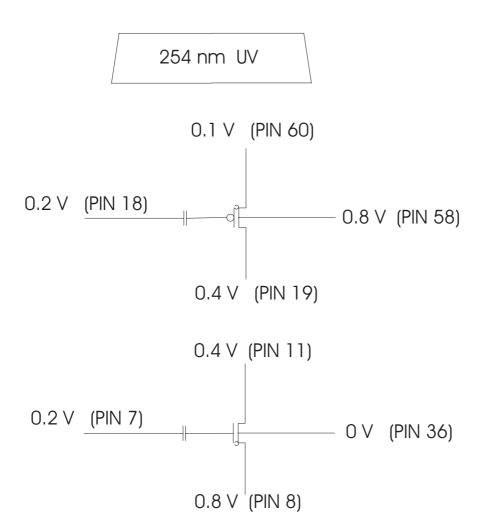

| <b>J</b> .0  | single transistors                                                                                                   | 53         |

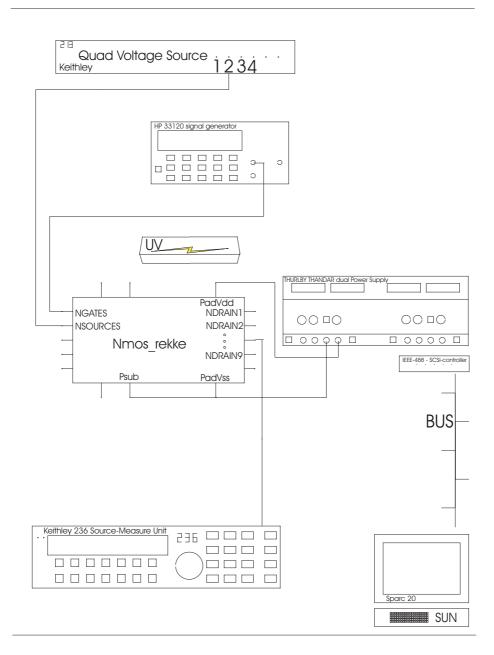

| 3.9          | Laboratory setup for UV-programming of NMOS transistors.                                                             | 53         |

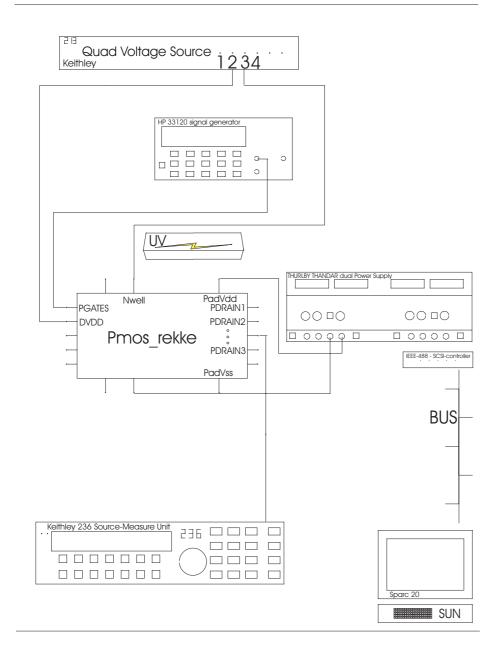

|              | Laboratory setup for UV-programming of NMOS transistors.<br>Laboratory setup for UV-programming of PMOS transistors. | $54 \\ 55$ |

| 3.10         | Photo of UV-programming and test environment at the De-                                                              | 99         |

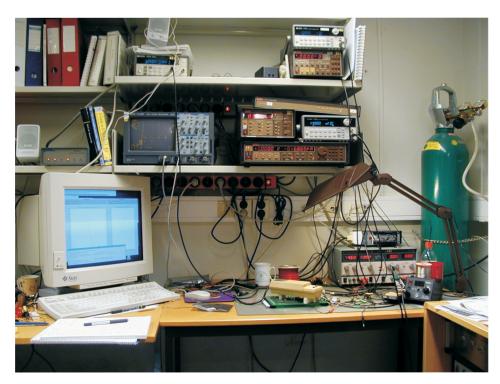

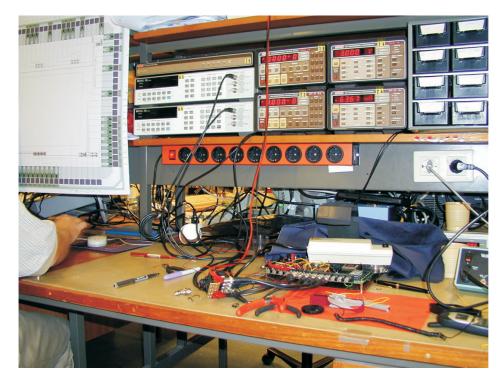

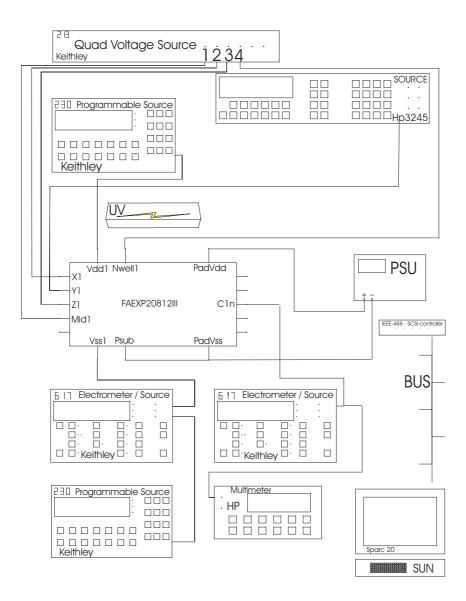

| 3.11         | partment of Informatics, University of Oslo                                                                          | 56         |

|              | parametric of informatics, University of OSIO                                                                        | 90         |

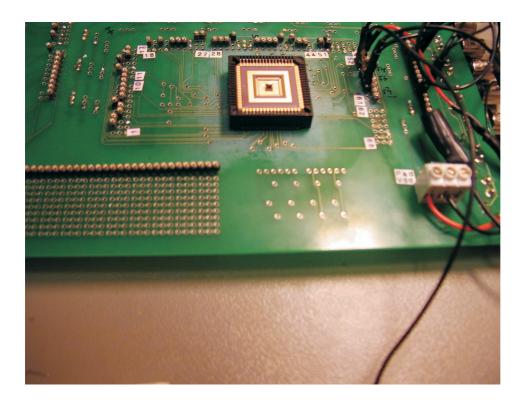

| 3.12 | Photo of first chip mounted on PCB                                                  | 57 |

|------|-------------------------------------------------------------------------------------|----|

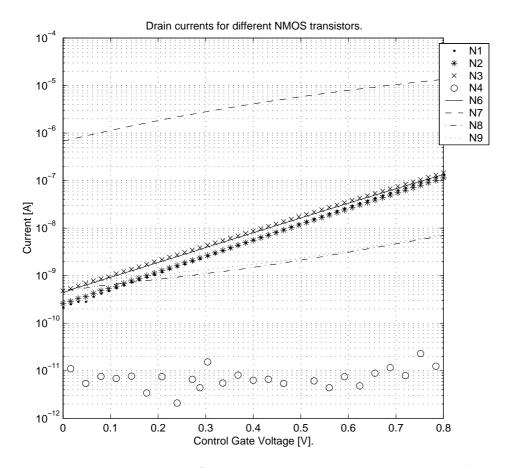

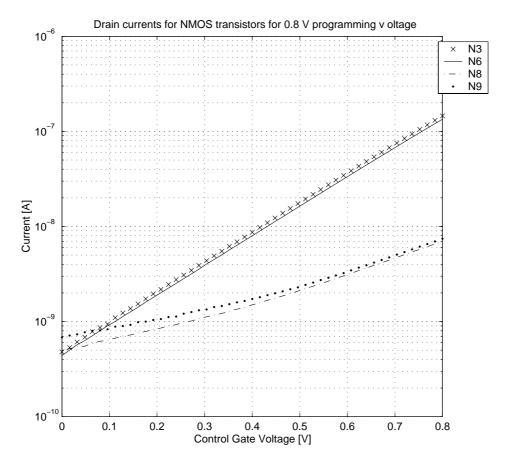

| 3.13 | Measured drain currents for different NMOS transistors, for                         |    |

|      | a programming voltage of 0.8 V                                                      | 60 |

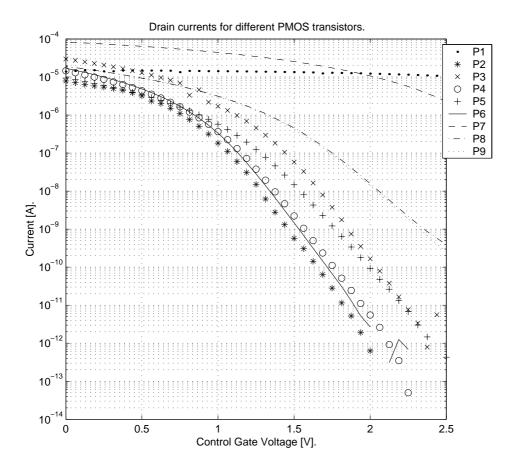

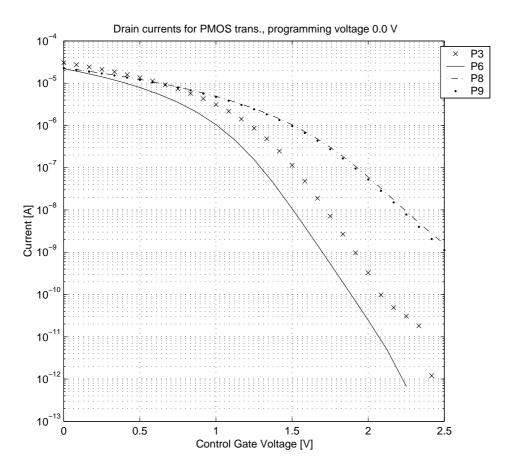

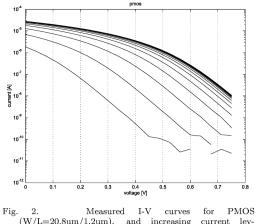

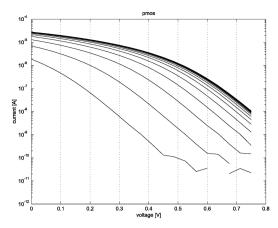

| 3.14 | Measured drain currents for different PMOS transistors, for                         |    |

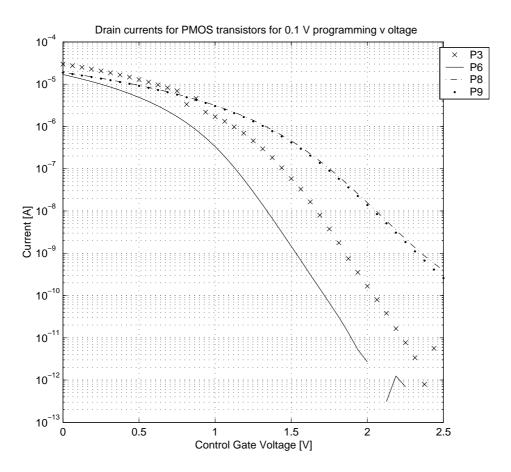

|      | a programming voltage of 0.1 V                                                      | 61 |

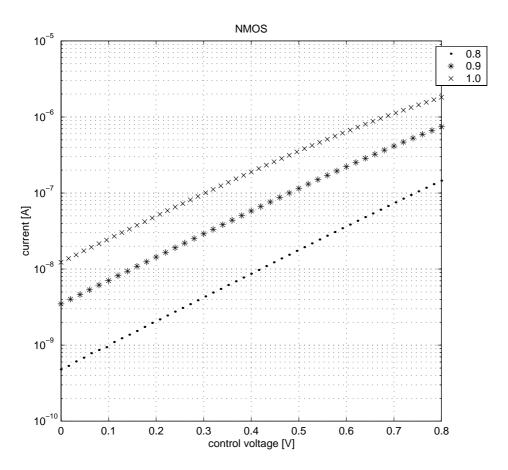

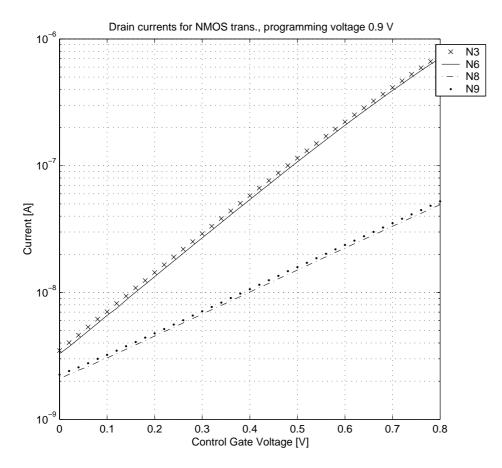

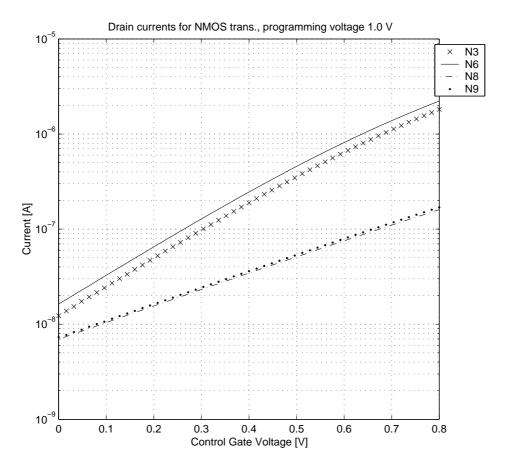

| 3.15 | Drain currents for an NMOS for programming voltages of                              |    |

|      | 0.8, 0.9 and $1.0$ V                                                                | 62 |

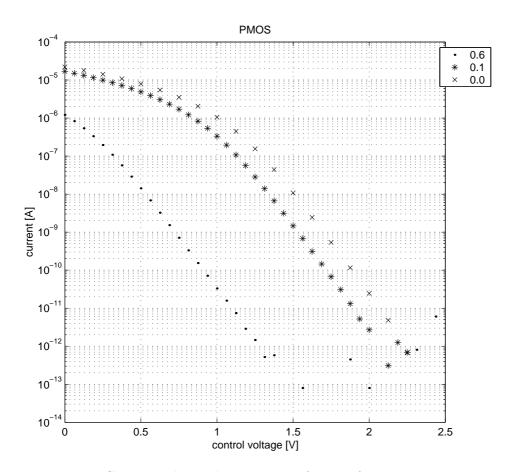

| 3.16 | Drain currents for a PMOS for programming voltages of 0.6,                          |    |

|      | 0.1  and  0.0  V                                                                    | 63 |

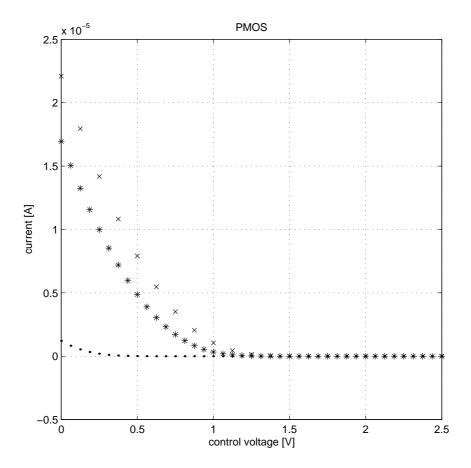

| 3.17 | Drain currents for a PMOS for programming voltages of 0.6,                          |    |

|      | 0.1 and 0.0 V on linear plot. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 64 |

| 3.18 | Programming voltages and drain current level for both PMOS                          |    |

|      | and NMOS                                                                            | 65 |

| 3.19 | Matching of NMOS drain currents for a programming voltage                           |    |

|      | of 0.8 V                                                                            | 66 |

| 3.20 | Matching of NMOS drain currents for a programming voltage                           |    |

|      | of 0.9 V                                                                            | 67 |

| 3.21 | Matching of NMOS drain currents for a programming voltage                           |    |

|      | of 1.0 V                                                                            | 68 |

| 3.22 | Matching of PMOS drain currents for a programming voltage                           |    |

|      | of 0.0 V                                                                            | 69 |

| 3.23 | Matching of PMOS drain currents for a programming voltage                           |    |

|      | of 0.1 V                                                                            | 70 |

| 3.24 | Matching of PMOS drain currents for a programming voltage                           |    |

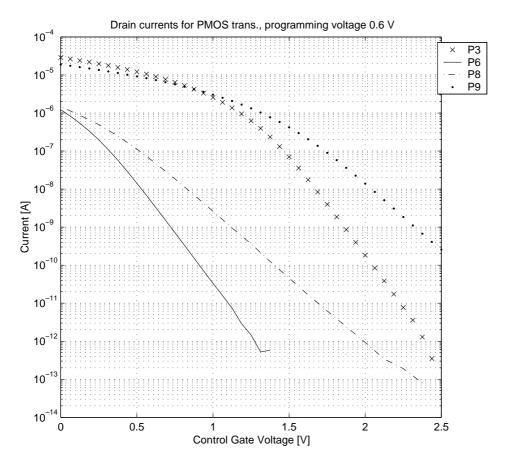

|      | of 0.6 V                                                                            | 71 |

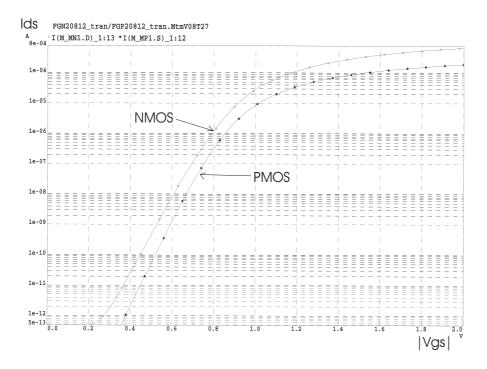

| 3.25 | Drain currents for PMOS and NMOS as a function of $ V_{gs} $ .                      | 72 |

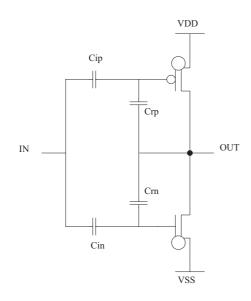

| 4.1  | Floating-gate inverter                                                              | 76 |

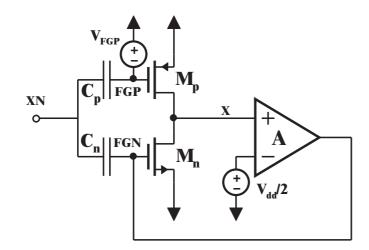

| 4.2  | Method for finding initial conditions for floating gates                            | 77 |

| 4.3  | Input to simulator for finding initial conditions                                   | 77 |

| 4.4  | Input for transient simulation                                                      | 79 |

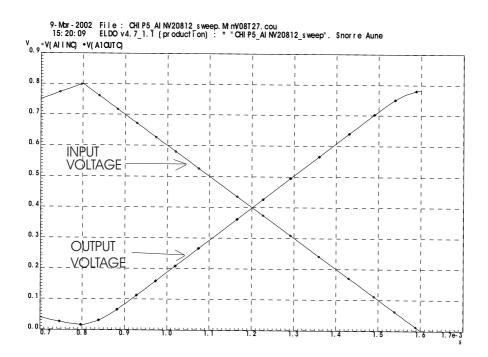

| 4.5  | Inverter transient simulation result                                                | 80 |

| 4.6  | Layout of inverter.                                                                 | 81 |

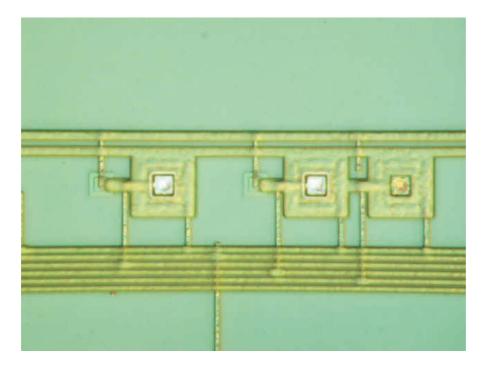

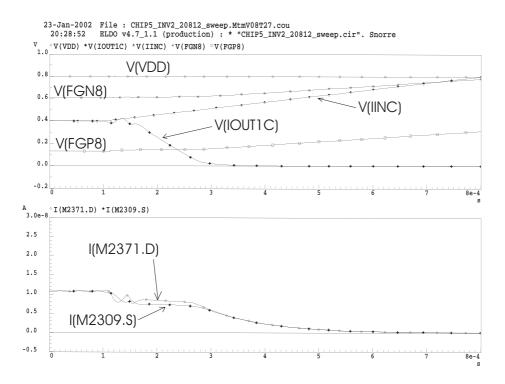

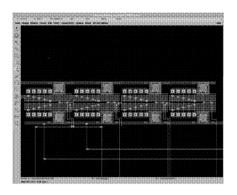

| 4.7  | Die photo of inverters.                                                             | 82 |

| 4.8  | Schematics for UV-programming mode and operative mode.                              | 84 |

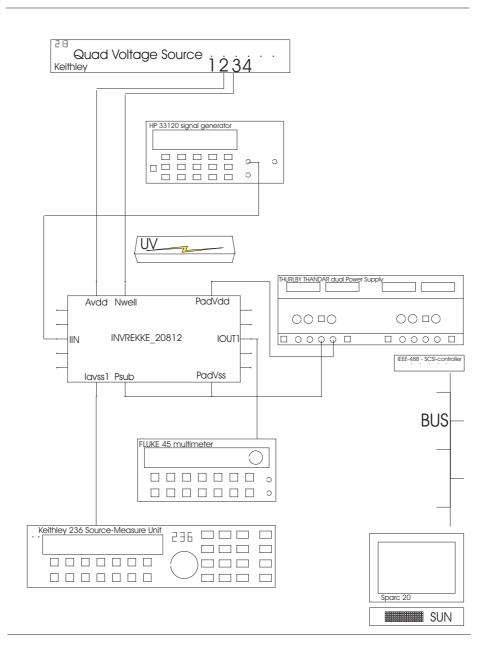

| 4.9  | Laboratory setup for inverter measurements from chip no. 1                          | 86 |

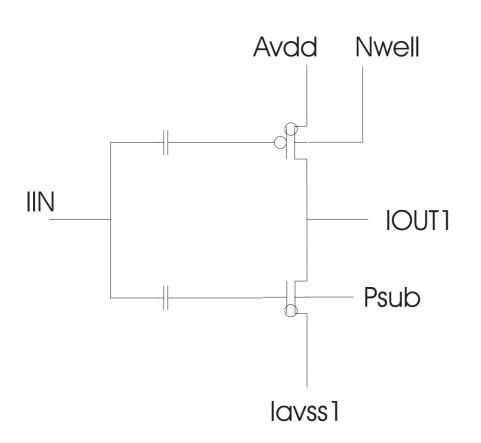

| 4.10 | Schematic for tested inverter on the 68 pin chip                                    | 87 |

| 4.11 | Measurements displayed real time on the computer screen                             | 88 |

| 4.12 | Applied voltages for testing of inverters                                           | 88 |

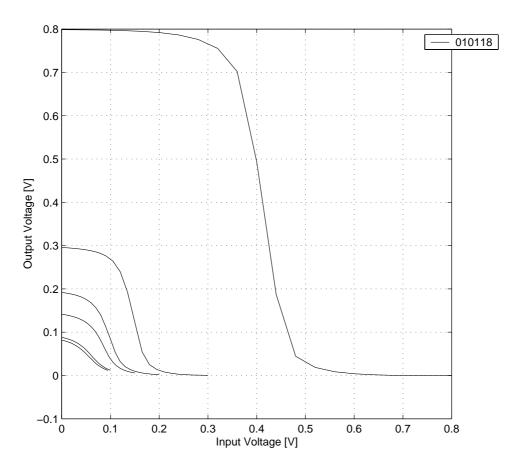

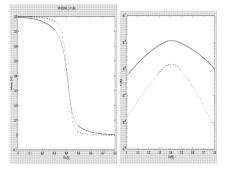

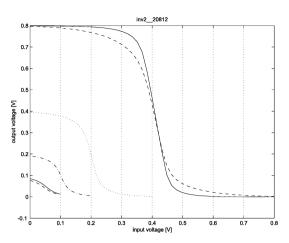

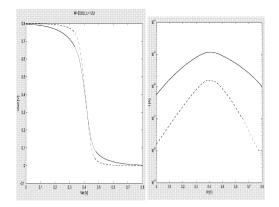

| 4.13 | Measured voltage transfer curves for power supply voltages                           |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | of 95 mV, 100 mV, 150 mV, 200 mV, 300 mV and 800 mV.                                 | 90  |

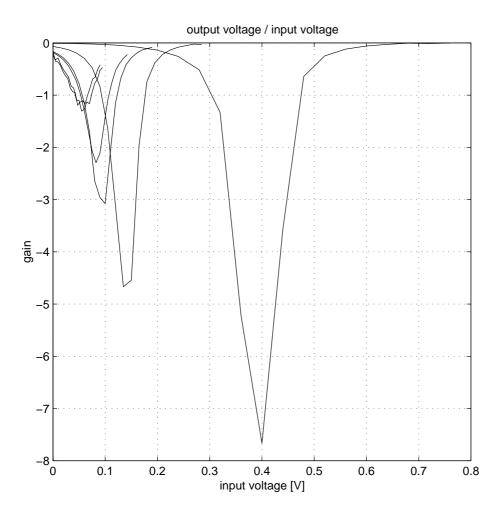

| 4.14 | Voltage gain based on measurements, for power supply volt-                           |     |

|      | ages of 95 mV, 100 mV, 150 mV, 200 mV, 300 mV and 800 $$                             |     |

|      | mV                                                                                   | 91  |

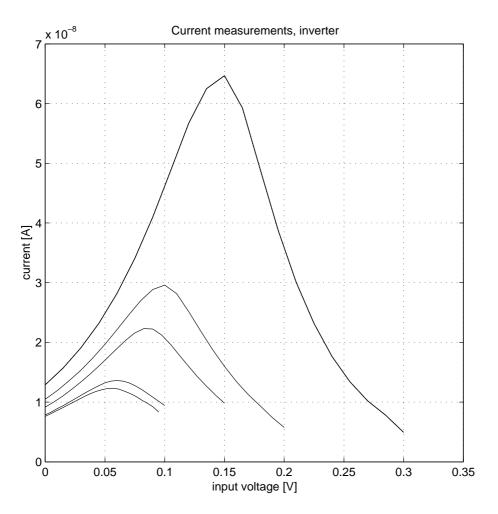

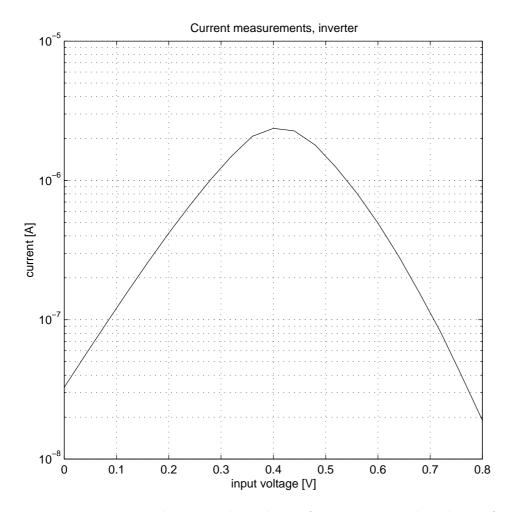

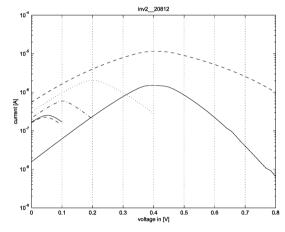

| 4.15 | Measured currents through Vss, for power supply voltages of                          |     |

|      | 95 mV, 100 mV, 150 mV, 200 mV, and 300 mV. $\ldots$ .                                | 92  |

| 4.16 | Measured current through Vss for a power supply voltage of                           |     |

|      | 800 mV                                                                               | 93  |

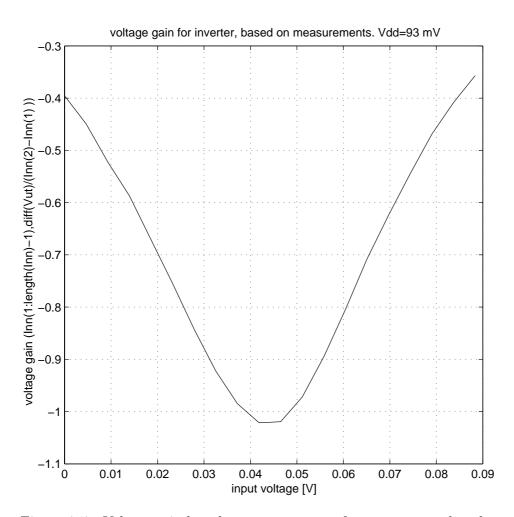

| 4.17 | Voltage gain based on measurements for a power supply volt-                          |     |

|      | age of 93 mV                                                                         | 94  |

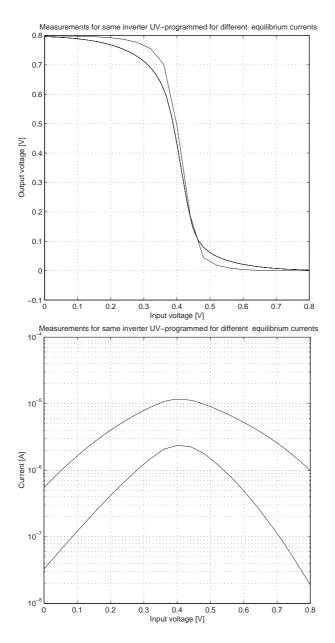

| 4.18 | Measured output voltages and currents for two different equi-                        |     |

|      | librium currents.                                                                    | 95  |

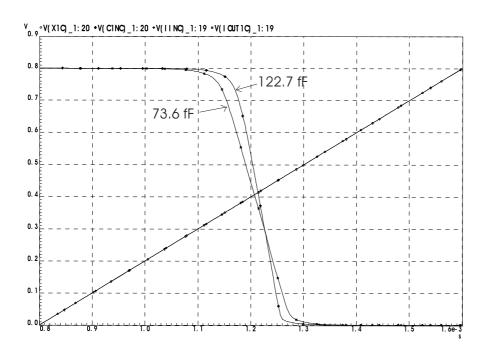

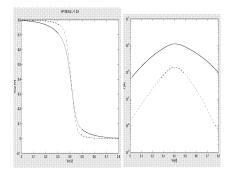

| 4.19 | Simulated operational speed as a function of $V_{dd}$ and $I_{beq}$ ,                |     |

|      | for $C_n = 73.6$ fF, based on chip layout.                                           | 96  |

| 4.20 | Simulated operational speed as a function of $V_{dd}$ and $I_{beq}$ ,                |     |

|      | for $C_n = 122.7$ fF, based on chip layout                                           | 97  |

| 4.21 | Simulated operational speed as a function of $V_{dd}$ and $I_{beq}$ ,                |     |

|      | for $C_n = 73.6$ fF, "parametrized" capacitances                                     | 97  |

| 4.22 | Table of simulated fall-times as a function of $V_{dd}$ and $I_{beq}$ ,              |     |

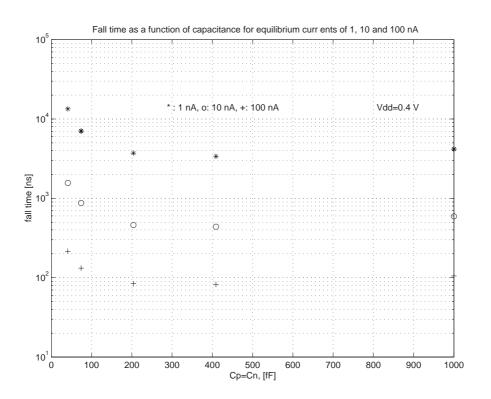

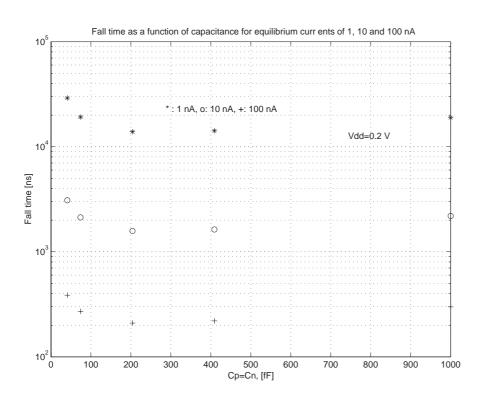

|      | $C_n=41, 74, 204, 409, 1000 \text{ (fF)}. V_{dd}=0.8, 0.4 \text{ (V)} \ldots \ldots$ | 99  |

| 4.23 |                                                                                      |     |

|      | $C_n=41, 74, 204, 409, 1000 \text{ (fF)}. V_{dd}=0.2 \text{ (V)} \dots \dots \dots$  | 100 |

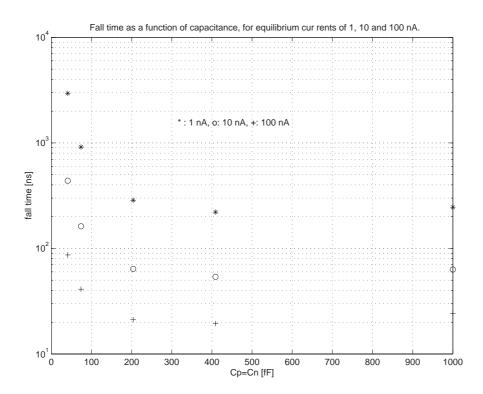

| 4.24 | Plot of fall-time as a function of $I_{beq}=1, 10, 100$ (nA) and                     |     |

|      | $C_n=41, 74, 204, 409, 1000 \text{ (fF) for } V_{dd}=0.8 \text{ V}$                  | 101 |

| 4.25 | Plot of fall-time as a function of $I_{beq}=1, 10, 100$ (nA) and                     |     |

|      | $C_n=41, 74, 204, 409, 1000 \text{ (fF) for } V_{dd}=0.4 \text{ V.} \dots$           | 102 |

| 4.26 | Plot of fall-time as a function of $I_{beq}=1, 10, 100$ (nA) and                     | 100 |

| 4.05 | $C_n = 41, 74, 204, 409, 1000 \text{ (fF) for } V_{dd} = 0.2 \text{ V.} \dots \dots$ | 103 |

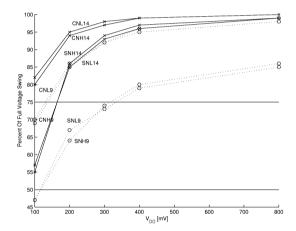

|      | Published data for floating-gate inverters                                           | 104 |

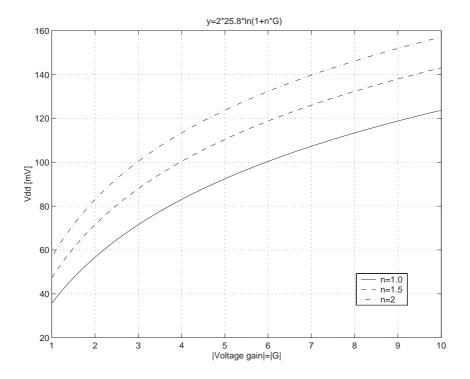

| 4.28 | Voltage gain an theoretically minimum supply voltage for                             | 100 |

|      | inverters                                                                            | 106 |

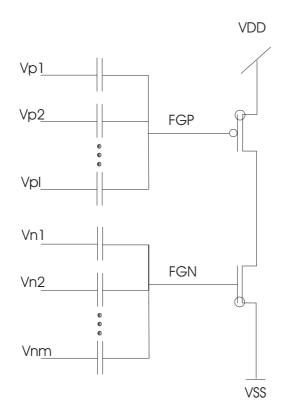

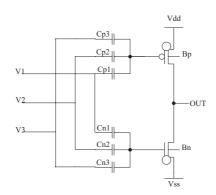

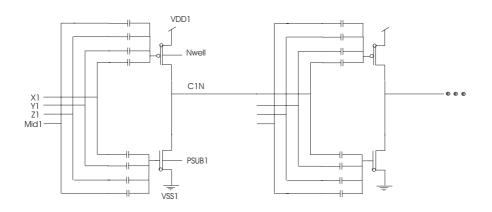

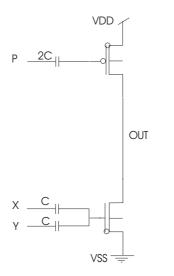

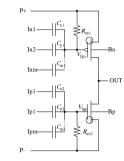

| 5.1  | Schematic for real time reconfigurable floating-gate circuit                         |     |

| 0.1  | with 3 equally weighted inputs to both PMOS and NMOS                                 |     |

|      | (P3N3).                                                                              | 110 |

| 5.2  | Truth table for CARRY' of FULL-ADDEr when implemented                                | - 5 |

|      | using a P3N3 circuit.                                                                | 111 |

| 5.3  | "Treshold logic style" truth table for CARRY' of FULL-                               |     |

|      | ADDER when implemented using a P3N3 circuit                                          | 111 |

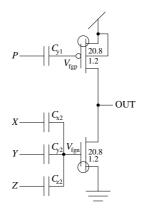

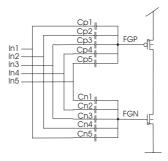

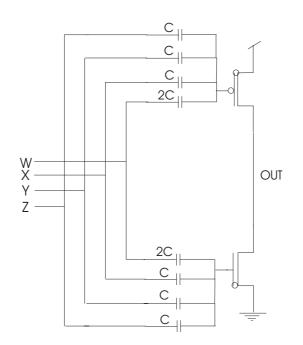

| 5.4  | Schematics for universal element P5N5                            | 112   |

|------|------------------------------------------------------------------|-------|

| 5.5  | "Treshold logic style" truth table for P5N5 circuit              | 113   |

| 5.6  | Schmematic for P5N5 variant.                                     | 114   |

| 5.7  | "Treshold logic style" truth table for P5N5 circuit, when two    |       |

|      | of the inputs are used for real time control of functionality.   | 115   |

| 5.8  | Table of functionalities for P5N5 when two of the inputs are     |       |

|      | used for real time control of functionality.                     | 115   |

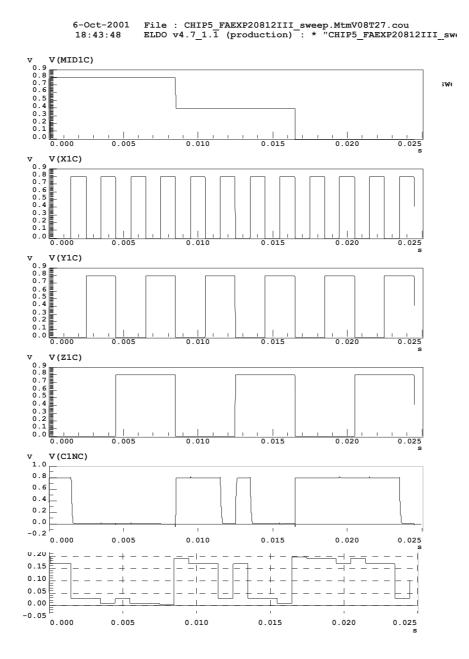

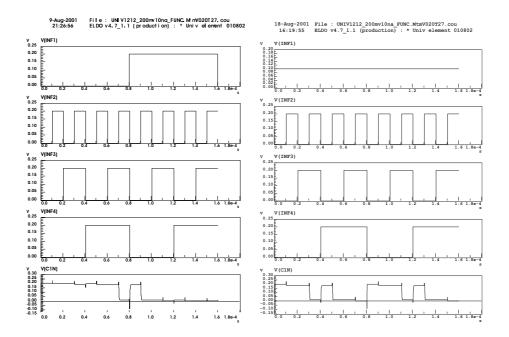

| 5.9  | Transient simulation demonstrating functionality of P5N5         |       |

|      | circuit                                                          | 116   |

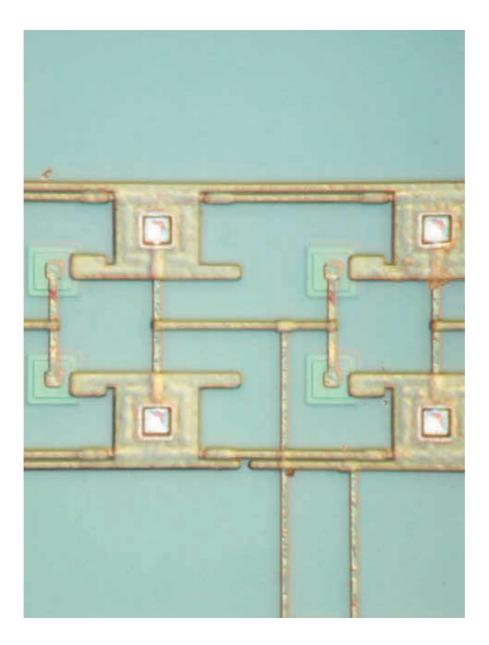

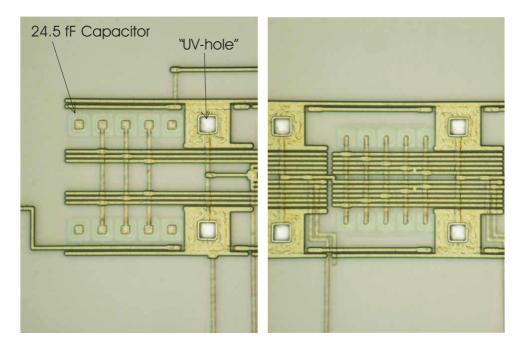

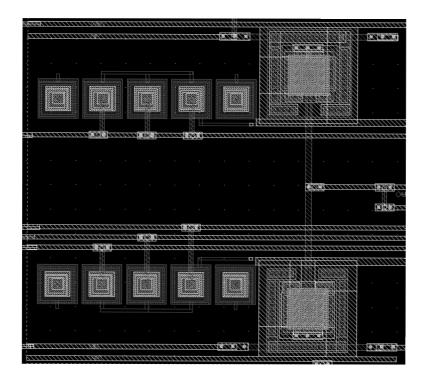

| 5.10 | Die photos of P3N3 and P5N5.                                     | 118   |

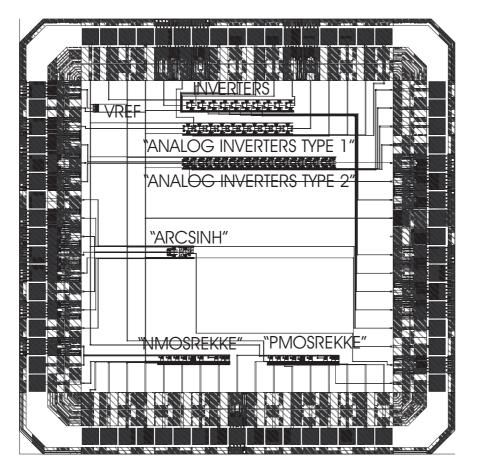

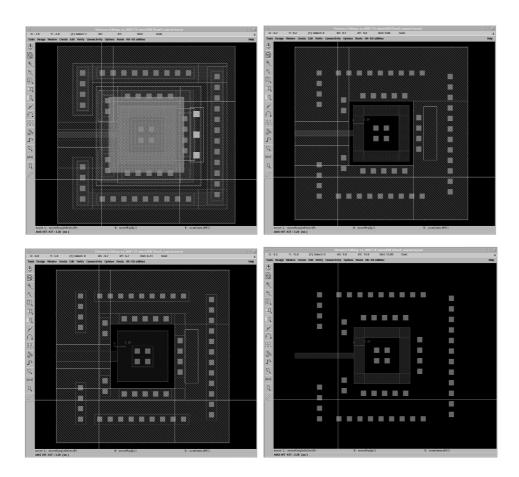

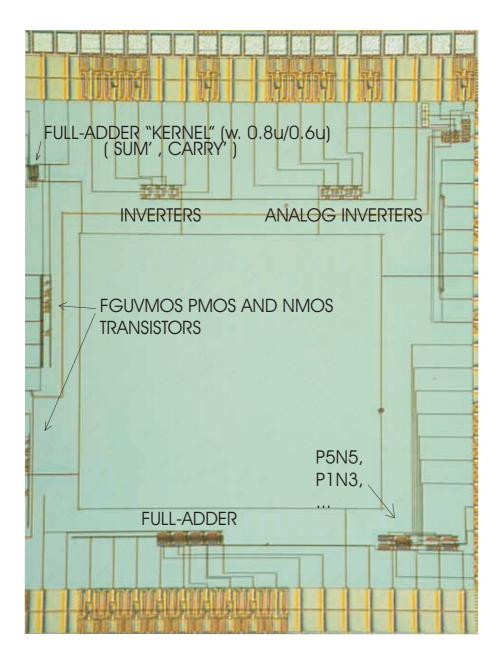

| 5.11 | Picture of 3rd chip sent for processing summer of 2001           | 118   |

|      | Layout of P5N5 using minimum transistors                         | 119   |

| 5.13 | Laboratory environment while testing P5N5 and P1N3 circuits.     | 121   |

| 5.14 | Schematics for UV-programming and test setup of P5N5.            | 122   |

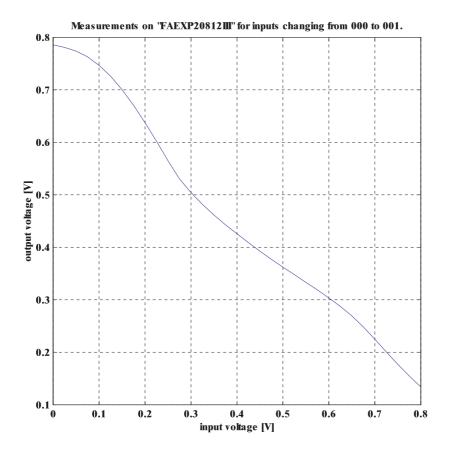

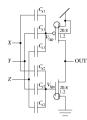

| 5.15 | Schematic of "FAEXP20812III" FULL-ADDER containing               |       |

|      | 4 P5N5 elements.                                                 | 123   |

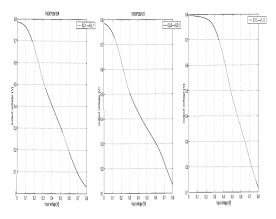

| 5.16 | Simulated NAND, NOR and CARRY' functionalities of P5N5.          | 124   |

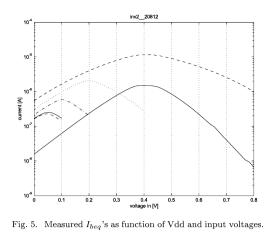

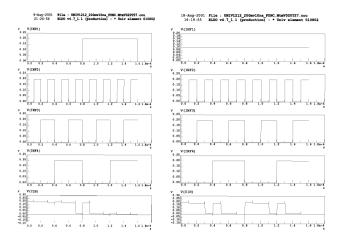

| 5.17 | Table containing UV-programming and test data for P5N5.          | 125   |

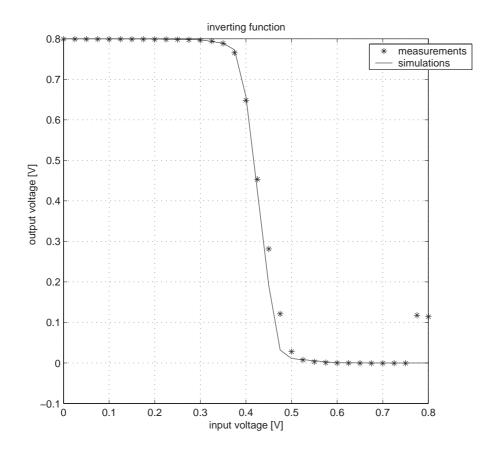

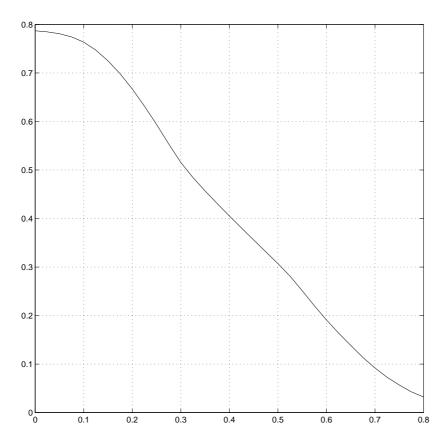

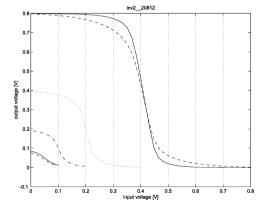

| 5.18 | Measuremed and simulated INVERTER function of P5N5.              | 126   |

| 5.19 | Measuremed 3-input NAND functionality of P5N5                    | 127   |

| 5.20 | Measuremed 3-input NOR functionality of P5N5                     | 128   |

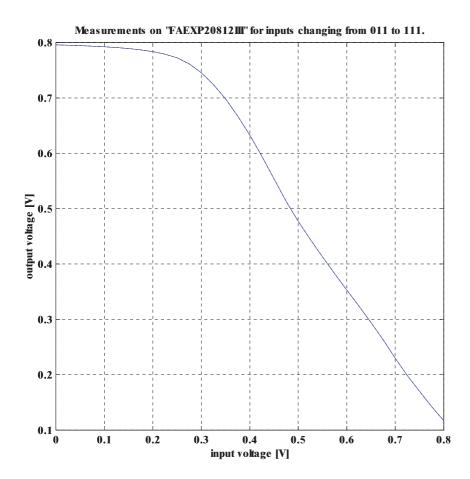

| 5.21 | Measuremed CARRY' functionality of FULL-ADDER, for               |       |

|      | P5N5                                                             | 129   |

| 5.22 | Maximum current, $I_{max}$ , at the switching point and for high |       |

|      | and low output values                                            | 131   |

|      |                                                                  |       |

| 6.1  | Schematic for real time reconfigurable circuit "P1N2"            | 134   |

| 6.2  | Output of P1N2 element as a function of binary, weighted         |       |

|      | inputs to NMOS.                                                  | 135   |

| 6.3  | Output for P1N2 element used as NAND2 and NOR2                   | 136   |

| 6.4  | Layout of P1N3 real time reconfigurable element.                 | 137   |

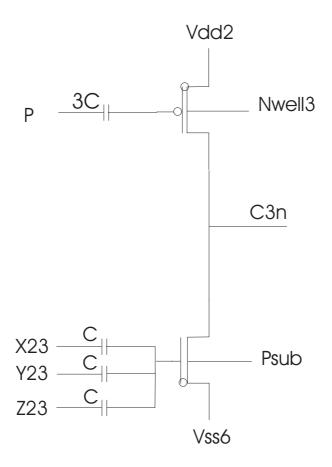

| 6.5  | P1N3 building block in "FAEXP20812" FULL-ADDER                   | 138   |

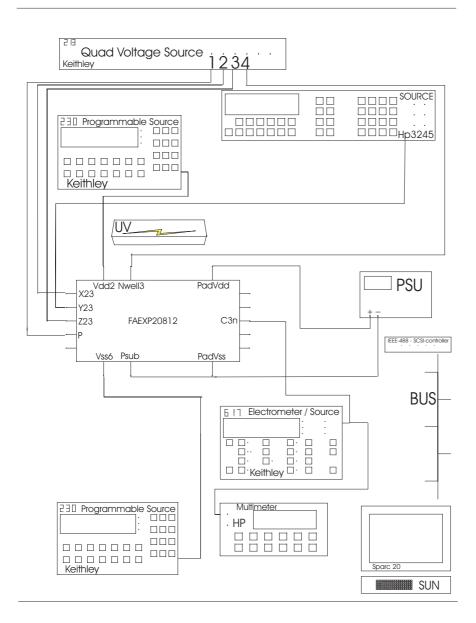

| 6.6  | Schematic for laboratory setup for UV-programming and            | 1.0.0 |

| ~ -  | test of P1N3.                                                    | 139   |

| 6.7  | Die photo from the 84 pin chip, sent for processing in spring    |       |

|      | 2001                                                             | 140   |

| 6.8  | Different applied voltages for UV-programming and testing        |       |

| 0.5  | of INVERTER functionality of P1N3.                               | 141   |

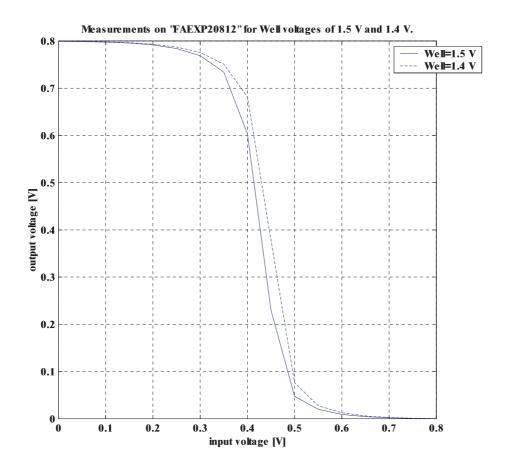

| 6.9  | Measured INVERTER functionality of P1N3, as a function           | 1.10  |

|      | of input voltage and well potential.                             | 142   |

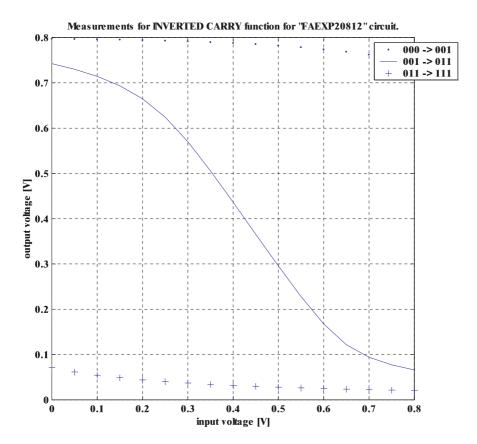

| 6.10  | Data regarding UV-programming and test of CARRY' func-                 |      |

|-------|------------------------------------------------------------------------|------|

|       | tionality of P1N3                                                      | 143  |

| 6.11  | Measured CARRY' functionality of P1N3                                  | 144  |

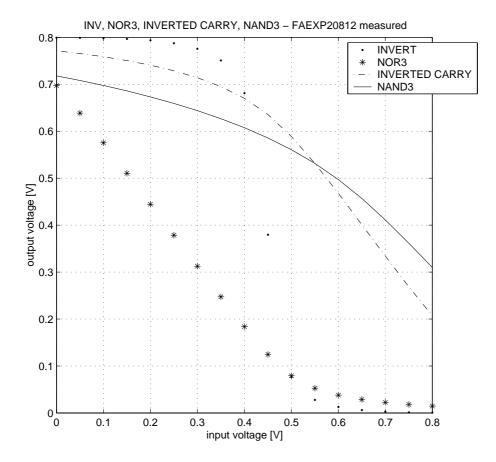

| 6.12  | Data regarding UV-programming and test of CARRY', NANDS                | 3,   |

|       | NOR3 and INVERT functionalities of P1N3                                | 145  |

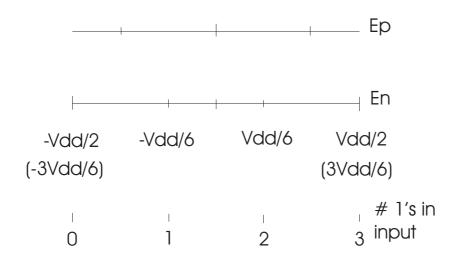

| 6.13  | Measured CARRY'-, NAND3-, NOR3- and INVERT- func-                      |      |

|       | tions of P1N3                                                          | 146  |

| 7.1   | Truth table for CARRY' function of FULL-ADDER                          | 149  |

| 7.2   | Circuit computing SUM' and CARRY' consisting of P3N3                   |      |

|       | and P5N5 elements.                                                     | 150  |

| 7.3   | Truth table for P5N5 as a function of every combination of             |      |

|       | W, X, Y, Z                                                             | 151  |

| 7.4   | Truth table for 4-transistor real time reconfigurable circuit.         | 152  |

| 7.5   | Schematic for 4-transistor real time reconfigurable element            |      |

|       | built from two P5N5 blocks                                             | 152  |

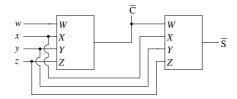

| 7.6   | Circuit computing SUM' and CARRY' consisting of P1N3                   |      |

|       | and P1N5 elements.                                                     | 154  |

| 7.7   | Transient simulation of SUM' and CARRY' functions using                |      |

|       | circuitry with capacitively weighted binary inputs to NMOS             |      |

|       | only                                                                   | 155  |

| 7.8   | Die photo of circuit consisting of two P5N5 elements using             |      |

|       | minimum transistors                                                    | 156  |

| 7.9   | Data on functionality, $V_{dd}$ and transistor count for multi-        |      |

|       | function binary circuits.                                              | 157  |

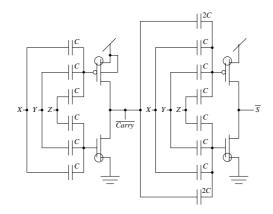

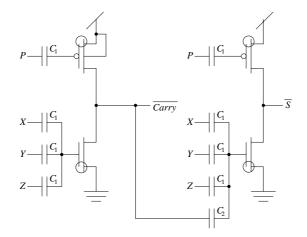

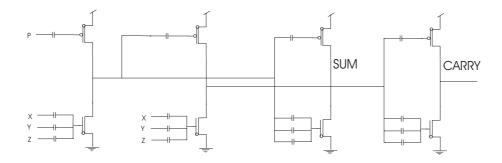

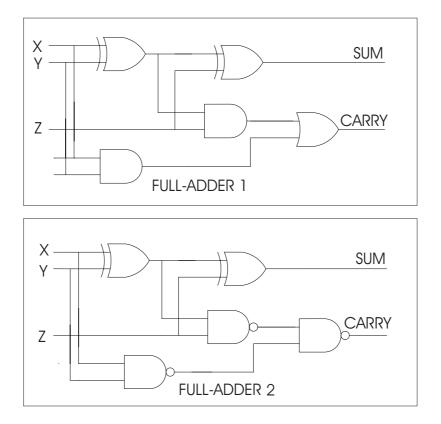

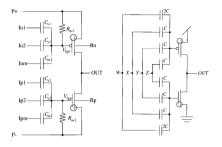

| 7.10  | Schematic for 8-transistor FULL-ADDER consisting of four               | 150  |

|       | P5N5 elements.                                                         | 158  |

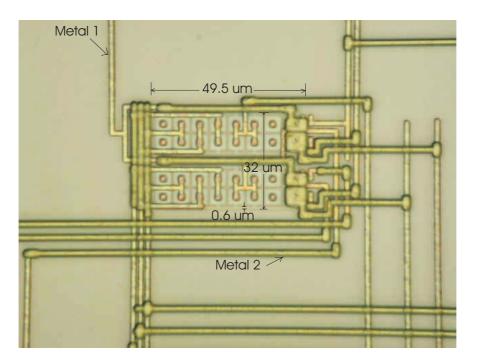

| 7.11  | Layout for 8-transistor FULL-ADDER consisting of four P5N5             | 150  |

| 7 10  | elements.                                                              | 159  |

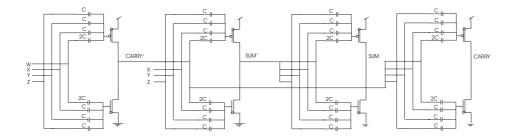

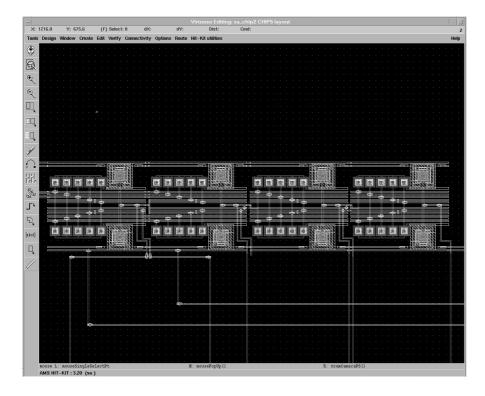

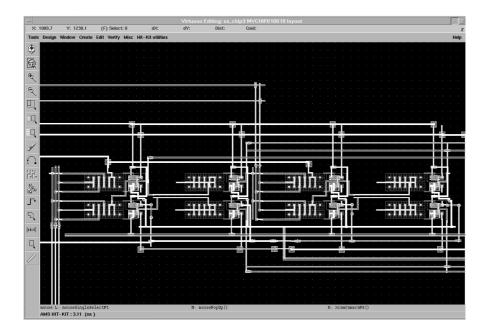

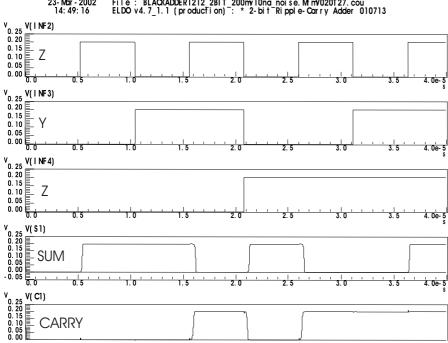

|       | Layout for 2-bit ripple-carry adder                                    | 160  |

| 7.13  | Schematic for 8-transistor FULL-ADDER consisting of four               | 1.00 |

| 714   | P1N3 elements.                                                         | 160  |

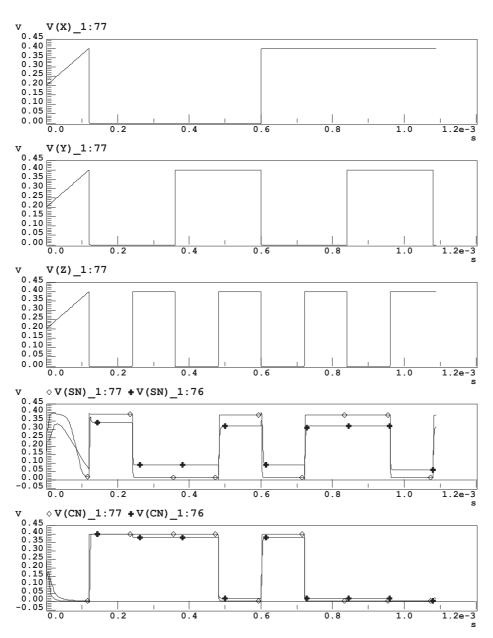

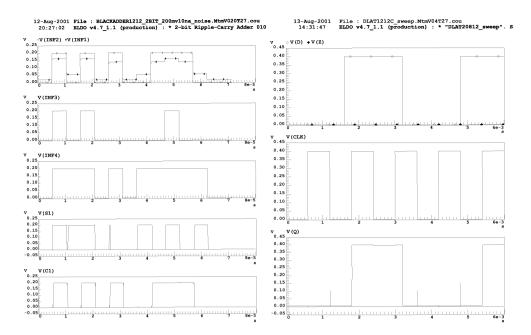

| 7.14  | Transient simulation of FULL-ADDER consisting of four                  | 1.61 |

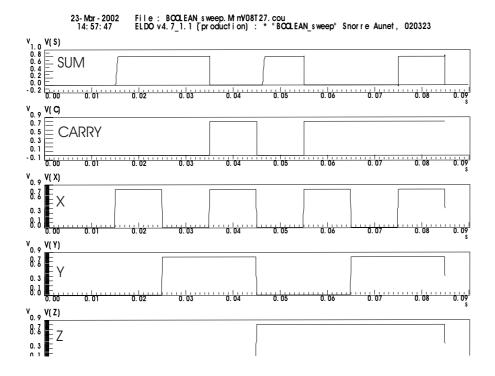

| 715   | P5N5 elements.                                                         | 161  |

|       | Simulated parameters of an 8-transistor FULL-ADDER                     | 162  |

| (.10  | Transient simulation of FULL-ADDER consisting of four<br>P1N2 elements | 169  |

| 7 1 7 | P1N3 elements.                                                         | 163  |

| (.1(  | Comparison regarding Power-Delay-Product (PDP) of FULL-                | 164  |

|       | ADDERs                                                                 | 104  |

| 7.18       | Schematics for two standard cell FULL-ADDER implemen-           |            |

|------------|-----------------------------------------------------------------|------------|

|            | tations.                                                        | 166        |

| 7.19       | Area and $\mu W/MHz$ for AMS standard digital logic cells       | 167        |

| 7.20       | Transistor count and logic depth for different FGUVMOS          |            |

|            | FULL-ADDERs.                                                    | 167        |

| 7.21       | Numbers of transistors and capacitors for a FULL-ADDER          |            |

|            | built using "transistor-as-switch-style"                        | 168        |

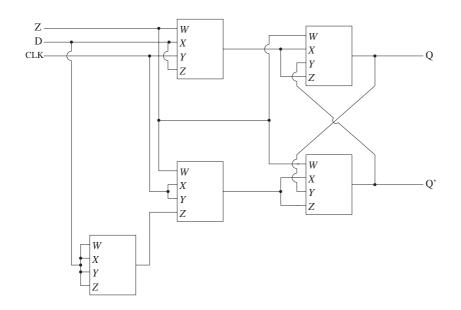

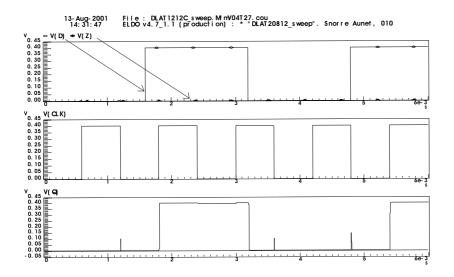

| 7.22       | Schematics for FGUVMOS D-latch.                                 | 169        |

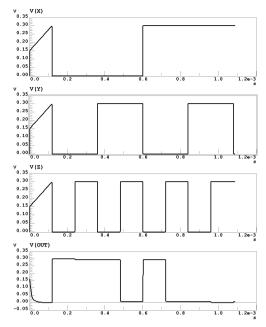

| 7.23       | FGUVMOS transient simulation trace.                             | 170        |

| 7.24       | Transient simulation for 3-bit analog-to-digital converter /    |            |

|            | frequency synthesizer based on three P7N7 elements              | 172        |

| 7.25       | Schematics for P7N7 element and 3-bit analog-to-digital con-    |            |

|            | verter / frequency synthesizer.                                 | 173        |

| 7.26       | Transient simulation of 3-input NOR using inverter-only FGU-    |            |

|            | VMOS logic.                                                     | 175        |

| 7.27       | Voltage gain and minimum theoretical $V_{dd}$ for PMNM circuits | .177       |

|            | Number of gates necessary for certain functions implemented     |            |

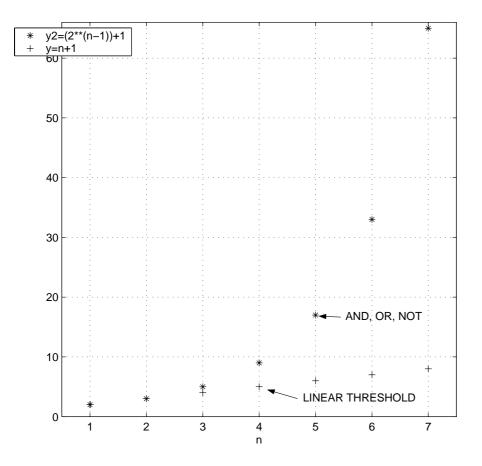

|            | by AND, OR, NOT logic vs by Linear threshold elements.          | 181        |

| 7.29       | Circuit symbol for pFET synapse transistor                      | 183        |

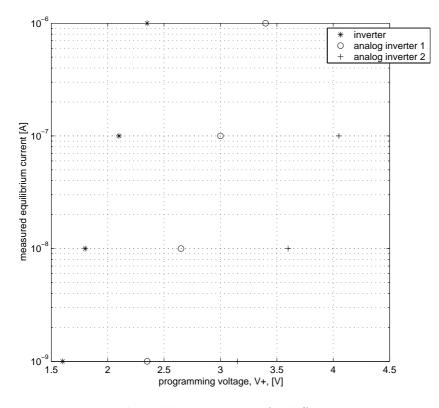

| 7.30       | Measured equilibrium currents as a function op different pro-   |            |

|            | gramming voltages, for three basic FGUVMOS circuits             | 187        |

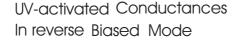

| 7.31       | Schematic for inverter with UV-activated conductances           | 188        |

| 7.32       | Measured switching voltages for circuit with logic depth after  |            |

|            | UV-programming with common voltages on rails and sub-           |            |

|            | strates                                                         | 190        |

|            |                                                                 |            |

| A.1        | Table of instrument types, laboratory numbers and serial        | 200        |

|            | numbers.                                                        | 209        |

| A.2        | List of instruments used for measurements in different chapters | .210       |

| A.3        | Names in the netlist and corresponding pin numbers on the       |            |

|            | 84 pin chip                                                     | 211        |

| B.1        | "ProgUVmin" matlab code, part one                               | 214        |

| B.2        | "ProgUVmin" matlab code, part two.                              | 215        |

| B.3        | "ProgUVmin" matlab code, part three.                            | 216        |

| В.4        | "InvSweep" matlab code                                          | 210<br>217 |

| В.4<br>В.5 | "Init" and "startup" matlab code, to the left and right, re-    | 411        |

| D.0        | spectively                                                      | 218        |

| B.6        | "NUV_prog_inv" and "skruav" matlab code                         | 210<br>219 |

| D.0        | nov_prog_mo and shraad mattab coue                              | 41 I       |

| B.7 | "Prog.m" for UV-programming and measurements on the 84 pin chip | 220 |

|-----|-----------------------------------------------------------------|-----|

| C.1 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 68 pin chip, pins 1-17                                          | 222 |

| C.2 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 68 pin chip, pins 18-34.                                        | 223 |

| C.3 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 68 pin chip, pins 35-51.                                        | 224 |

| C.4 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 68 pin chip, pins 52-68.                                        | 225 |

| C.5 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 84 pin chip, pins 1-17                                          | 226 |

| C.6 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 84 pin chip, pins 18-35.                                        | 227 |

| C.7 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 84 pin chip, pins 36-53.                                        | 228 |

| C.8 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 84 pin chip, pins 54-70.                                        | 229 |

| C.9 | Pin numbering, signal names, pad types and circuitry on the     |     |

|     | 84 pin chip, pins 71-84.                                        | 229 |

|     |                                                                 |     |

### Chapter 1

### Introduction

#### 1.1 The neuron-MOS and FGUVMOS circuit concepts

This work might be perceived as having it's startingpoint from two basic ideas, namely the multiple-input floating-gate transistor concept [ShOh91], and UV-programmable floating-gate circuits [LaWi96], [BeLa97], using the "FGUVMOS" UV-programming approach from [BeLa97].

A few important characteristics in a few words: In [ShOh91] multiple-input floating-gate circuits working in the classical above threshold regime are introduced. The device in [ShOh91] turns on when the weighted sum of all input signals exceeds a threshold. The number of transistors and interconnections can be drastically reduced by using multiple-input floating-gate devices in [ShOh91], a method that could entirely alter the way of constructing logic circuits, according to the authors of [ShOh91].

Dynamic power consumption depends linearly on the physical capacitance being switched [RaPe96]. Therefore, using fewer wires and fewer active elements for a given function may be attractive for minimizing power consumption.

FGUVMOS circuits utilize the multiple-input floating-gate transistor principle. A goal of FGUVMOS circuits has been to be able to reduce the supply voltage and adjust the effective threshold voltages of standard CMOS circuits at the same time [BeLa97], [BeWi98]. Voltage reduction offers the most direct and dramatic means of minimizing energy consumption [RaPe96]. By being able to adjust the current levels at the same time, the reduced performance following from a  $V_{dd}$  reduction can be counteracted. Supply voltages for FGUVMOS circuits have typically been in the 300 mV

1

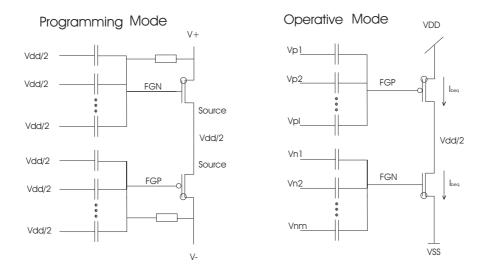

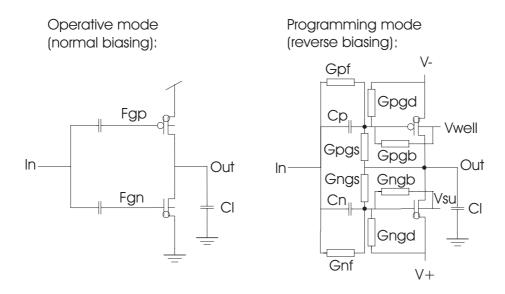

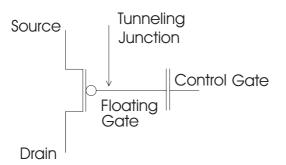

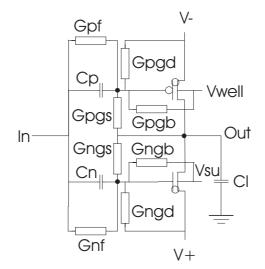

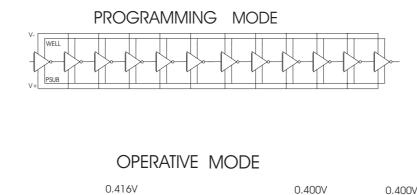

Figure 1.1: Schematic of the UV-programming mode and the normal operative mode, based on [BeLa97]. The extra circles in the MOSFET symbols indicate UV-conductances. In operative mode the equilibrium current is the drain current at the switching point, when all inputs and the output equal  $V_{dd}/2$ .

to 800 mV range. This, in combination with currents typically in the pA to  $\mu A$  range provide a significant low-power potential.

A shift in the effective threshold voltages, or current levels, is set during a UV-programming procedure. The UV-programming ensures a certain equilibrium current,  $I_{beq}$ , at the switching point of every basic FGUVMOS circuit element under normal operation. This switching point is ideal when the input voltages and output voltage are equal for all input voltages having a voltage of  $V_{dd}/2$  under normal operation, shown to the right in figure 1.1. The equilibrium current,  $I_{beq}$ , might typically be in the nA to  $\mu$ A range for circuits implemented in an AMS 0.6  $\mu$ m technology [AMS98]. UV-activated conductances between the power supply rails ( $V_{dd}$  and  $V_{ss}$ ) are used to program the desired  $I_{beq}$  levels, as illustrated in figure 1.1. In a "reverse-biased" mode [BeLa97] during UV-programming the programming voltages,  $V_+$  and  $V_-$ , on the power lines are used to control charge transport to and from the floating-gates, through the UV-activated conductances. The chosen pair of programming voltages ( $V_+, V_-$ ) determines the equilibrium current level under normal operation, after the UV-light is turned off. The shift in equilibrium currents means that a change in the effective threshold voltages, seen from the driving nodes, is done simultaneously. The circuits can be reprogrammed.

A future goal could be to program all transistors on a chip, or even a wafer, without using any additional programming circuitry [BeWi98].

Floating-gate digital circuitry like EXOR, NAND2, NOR2, INVERT,

FGUVMOS single-bit adder.

Figure 1.2: ©1999 IEEE. Reprinted, with permission, from IEEE Transactions on Circuits and Systems II, analog and digital signal processing, Vol. 46, Issue 7, July 1999.

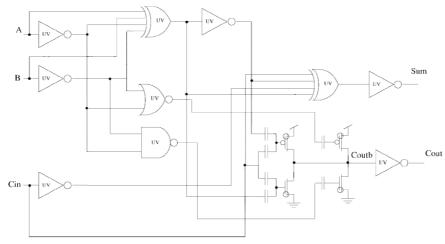

a D-flip-flop, a FULL-ADDER and a pad-driver were published in 1999 [BeWi99]. Publications describing digital FGUVMOS circuits prior to work described in this thesis can be found in [LaWi96], [BeLa97b], [BeWi97], [BeWi98], [BeWi99]. The paper [BeWi99] demonstrated the ultra-low power potential of FGUVMOS circuits working with supply voltages far below 1 V and equilibrium currents in the 4 nA to 200 nA range. A FULL-ADDER presented is shown in figure 1.2.

FGUVMOS circuits are not restricted to digital use, and some recent research results can be found in [BeLa01b], [BeLa01a]. An introduction to

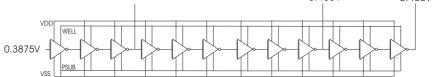

Figure 1.3: Schematics for FGUVMOS FULL-ADDER from [BeWi99] for producing SUM' and CARRY'.

the floating-gate research field can be found in a special issue of the IEEE Transactions on Circuits and Systems II, on floating gate devices, circuits and systems, from 2001 [HaLa01].

#### 1.2 New real time reconfigurable floating-gate circuits

The digital functions in [BeWi99] used different basic circuitry for different functions like NAND, NOR and INVERT, resembling the standard concept of using the transistor as a switch only.

The real time reconfigurable circuit concepts presented in this thesis have undergone some evolution. It started with the idea of using three input circuits for the CARRY' function, which has the 2-input NAND, 2-input NOR and INVERT functionality embedded [AuBe01b]. This led to an attempt to utilize a FULL-ADDER concept from [KoSh92] to make a 4-transistor circuit able to generate SUM' and CARRY' for the FULL-ADDER function. This, together with inherent capabilities of the circuit to generate Boolean functions like NAND, NOR, INVERT, XOR and XNOR were discovered [AuBe01a]. The circuits in [AuBe01a] were both composed from two different basic building blocks.

Added to this is a universal threshold circuit concept [AuBe01d], which became used for a static memory and an adder in [AuBe01e]. The idea of building FGUVMOS circuitry using only one type of basic block was used here. Later measurements from chip confirmed the function of some basic building blocks.

It has been stated earlier that "previous experience with UV-programmable floating-gates suggested the only "proof of the pudding is the eating"" [LaWi96]. Even if the techniques and experience have been developed since that, some efforts have been done towards prototyping and laboratory measurements here as well. The AMS 0.6  $\mu$ m technology have been used throughout this work, due to the experience gained from using it at the University of Oslo. Unless otherwise mentioned, the simulations are based on netlists extracted from layout. Test circuits in a 0.35  $\mu$ m technology from another producer of integrated circuits have also been produced, but no laboratory measurements have been done yet.

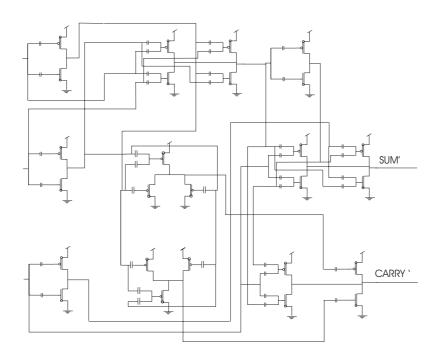

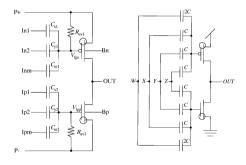

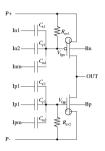

The added functionality per active device compared to earlier approaches enables a reduction in the transistor count and amount of wiring, for implementation of many digital functions. The approach from [BeWi99] used the circuitry shown in figure 1.3 to compute SUM' and CARRY'. An implementation using one of the new circuits [AuBe01d] is shown in figure 1.4. The two schematics both implement the same functions. For example is the number of transistors used for implementation of the CARRY' function reduced from 22 to 2, or more than 90% [AuBe01b] by using the new approach. Also an 8-transistor FULL-ADDER is presented, built from 4

Figure 1.4: Schematic for circuit generating SUM' and CARRY' using two P5N5 elements.

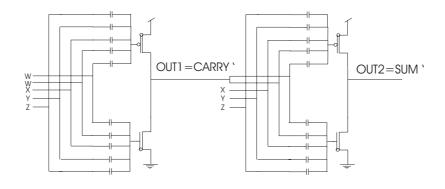

of the elements shown in figure 1.4 [AuBe01d]. This is among the lowest numbers of active elements for FULL-ADDER circuits that are known from litterature. An even simpler version is shown in figure 1.5

A widespread use of identical basic building blocks on the gate level increases matching properties when circuits are implemented in CMOS, since MOS technology is well suited for fabrication of circuits where accuracy is determined by precision of ratio between elements, while absolute tolerances are much poorer [Sæth91].

Among contributions of the work presented here is that it is based on an approach using as little diversity among building blocks as possible. It is argued that it may ease UV-programming of FGUVMOS circuits a lot, as well as reduce wiring and transistor count. This might improve the lowpower potential of digital FGUVMOS circuits.

Subthreshold circuits have been shown to consume orders of magnitude less power than the regular strong-inversion circuit at the same operating frequency [SoRo01]. FGUVMOS circuits using the standard programming scheme have always two transistors "stacked" between  $V_{ss}=0$  V, and  $V_{dd} \leq 0.8$  V. The current  $I_{beq}$  levels of the transistors can be set to the desired level, typically in the 1nA to 1 $\mu$ A range according to experience with the AMS 0.8 and 0.6  $\mu$ m CMOS processes. This means that the circuits might work entirely in subthreshold in some cases, or in weak and moderate inversion. Moderate inversion means higher  $I_{beq}$  levels than weak inversion, and can be a useful region of operation to attain a relatively high operational speed of FGUVMOS circuits. For the FULL-ADDER function running at 1 MHz operational speed, it is argued that an 8-transistor FGUVMOS FULL-ADDER uses about 2500 times less energy than a circuit based on standard library cells in the same technology.

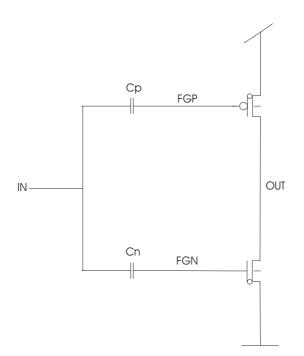

The basic building blocks proposed all consist of 2 transistors and a number of drawn capacitances between inputs and the floating gates of the PMOS and the NMOS transistors. Chosen restrictions for the capacitances have been that all drawn capacitances were of equal size and shape, and that the sum of the drawn capacitances connected to the floating gate of the PMOS transistor equals the sum of the drawn capacitances connected to the floating gate of the NMOS transistor, of a basic circuit. The number of inputs to the PMOS and NMOS, respectively, are used for naming the circuits. P1N3 means a circuit with one capacitively weighted input to the PMOS, and three capacitively weighted inputs to the NMOS.

For the inverter functionality is demonstrated by chip measurements with a  $V_{dd}$  of only 93 mV, which is amongst the lowest supply voltages reported in litterature.

Among recent work on subthreshold digital logic, work like [SvMa00] and [SoRo01] can be mentioned. Subthreshold digital logic in most cases rely on some substrate bias stabilization, as shown in [SvMa00], [SoRo01]. Subthreshold operation is common with most FGUVMOS circuits, but the multiple-input floating-gate MOSFET capabilities leading to real time reconfigurable logic functions might be unique.

As an example, the P1N3 element used twice in 1.5 may be used as a circuit producing each and every of the CARRY', NAND3, NAND2, NOR3, NOR2 and INVERT functions, depending on voltage on one or several control inputs.

A "P7N7" building block is also used in making a 3-bit analog-to-digital converter containg only 6 transistors.

In addition the new circuits were recognized as belonging to the class of circuits called linear threshold elements, the name of basic computational units in neural networks [AuBe02a].

Building blocks presented here are also currently under investigation as building blocks for systems based on evolvable hardware [Eske02] These are examples that the circuits proposed may find use in other areas than a pure digital context.

During the work on this thesis, several of the results have been published at international conferences with peer review: [AuBe01a], [AuBe01b], [AuBe01d], [AuBe01e], [AuBe02a], [AuBe01c], [BeAu01a], [BeAu01b], [BeAu01c], [BeAu01d], [BeAu01e], [YtAu02], [BeAu02], [BeNa02b], [BeNa02c], [BeNa02d]. The first five publications mentioned form the core of this thesis.

Figure 1.5: Two P1N3 elements used for implementing CARRY' and SUM'.

#### 1.3 Thesis outline

In chapter 2.1 important properties of the multiple-input floating-gate MOS-FET operating with current levels in the pA to  $\mu$ A range are explored, from an ordinary MOS transistor up to behavior in a circuit. At the end some parameters are pointed out that can provide insight in how transconductance and output resistance of these devices might be adjusted. Then some widely used equations for the universal FGUVMOS element is introduced with an inverter as example, in chapter 2.2. One of our circuit building blocks are briefly introduced in chapter 2.3.

In chapters 3, 4, 5, 6 and 7 there are descriptions regarding the function and implementation of the different circuitry in each chapter, and results and discussion following. This have been done to sum up the discussion in portions, and later add them up in a hierarchical manner.

Chapter 3 describes PMOS and NMOS transistors in the above mentioned manner.

In chapter 4 these elements are combined for inverters, with the chapter including simulations, IC layouts, UV- programming and test setup, results and discussion.

Chapter 5 deals with 2-MOSFET floating-gate elements with identically weighted inputs to both PMOS and NMOS, with a structure having much in common with chapter 4.

Chapter 6 is made basically like chapter 5, but this time the circuits have the signals used as ordinary signals, and not control inputs, connected to the NMOS floating gate only.

Chapter 7 introduces circuits made from the previously described building blocks. Another layer in the "discussion hierarchy" is added for each of them, making connections back to the basic inverter in chapter 4, and the transistors from chapter 3. FGUVMOS "Inverter-only" based logic is introduced. Linear threshold functions and implementation using FGUVMOS are discussed. New possibilities regarding UV-programming and testing are also discussed in 7.7.

Chapter 8 describes the overall results and major contributions, as well as suggestions for further work.

Introduction

### Chapter 2

## Multiple-input UV-programmable MOSFETs and two-MOSFET circuits

#### 2.1 MOSFETs

#### 2.1.1 MOSFETs in weak inversion

For an NMOS transistor operating in subthreshold, or more precisely weak inversion, the drain current,  $I_{ds}$ , is given by [AnBo91]:

$$I_{ds,n} = I_0 exp\{\frac{\kappa V_{gs}}{U_t}\} exp\{\frac{(1-\kappa)V_{bs}}{U_t}\}(1-exp\{\frac{-V_{ds}}{U_t}\}+\frac{V_{ds}}{V_0}).$$

(2.1)

For gate voltages well below the threshold voltage,  $V_t$ , of the transistor, the transistor may be said to work in subthreshold [Mead89], instead of the classical above threshold region.

Other names for operating regions of the MOSFET are "leakage-affected region", "weak inversion", "moderate inversion" and "strong inversion" [Tsiv99]. If taken in the above mentioned order they mean different nonoverlapping regions with increasing drain currents, if they were to be plotted in figure 2.1, as can be seen from in [Tsiv99] p. 45. For practical purposes  $I_{ds}$ is exponentially related to  $V_{gs}$  in weak inversion. In weak inversion, diffusion contributes to the larger part of the drain current, while drift dominates

11

in strong inversion. In moderate inversion, both drift and diffusion contribute significantly to the value of the drain current. Weak and moderate inversion are the areas used for practical implementations of FGUVMOS circuits in this thesis.

$I_0$  is the zero-bias current for the current for the given device [AnBo91], a constant where all preexponential constants have been absorbed [Mead89]. This includes W and L, the channel width and length of the MOSFET structure, respectively.  $V_{gs}$  is the gate-to-source potential,  $V_{ds}$  is the drainto-source potential and  $V_{bs}$  the substrate-to-source potential.  $V_0$  is the Early voltage, which is proportional to the channel length.  $\kappa$  measures the effectiveness for which the gate potential is controlling the channel current. It is often around 0.7 - 0.75 [Mead89], [AnBo91]. Boltzmann's constant,  $k = 1.38 \cdot 10^{-23} J/K$ , and elementary charge,  $q = 1.602 \cdot 10^{19}$  Coulomb. At room temperature T = 300 degrees Kelvin, and thus  $U_t = 25.8mV$ .

For devices in saturation within weak inversion, when  $V_{ds} \ge 4U_t$ , neglecting the early effect and the body effect [AnBo91]:

$$I_{ds,n} = I_0 exp\{\frac{\kappa V_{gs}}{U_t}\}$$

(2.2)

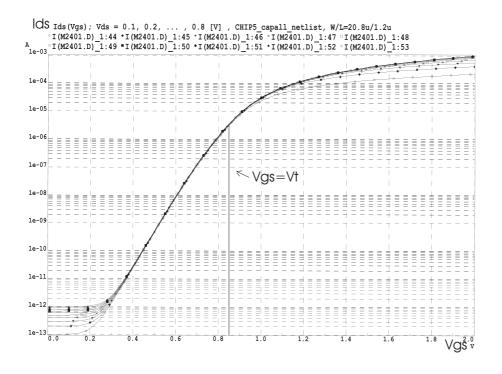

In figure 2.1 the drain current of an NMOS transistor as a function of the gate-source voltage for different drain-source voltages is simulated. For FGUVMOS circuits we have a maximum equilibrium current,  $I_{beq}$ , which often is in the microampere to nanoampere range, for the AMS 0.8 CMOS technology [BeWi99]. The voltage between drain and source,  $V_{ds}$ , adjusts the current level, but it is mainly dependent on  $V_{gs}$ . Sometimes only  $V_{gs}$  is taken into account, like in [KoGo01].

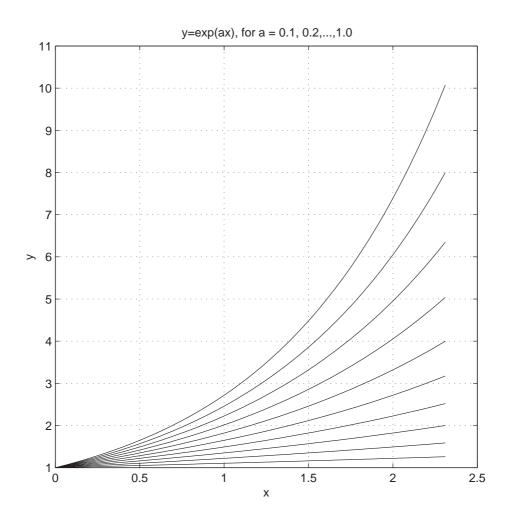

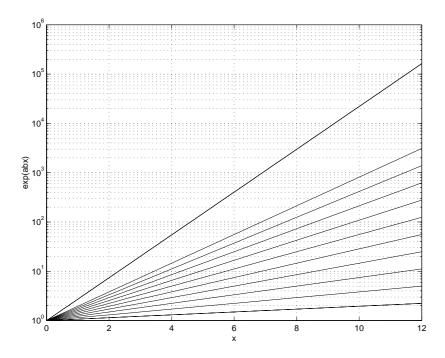

The factor  $\kappa < 1$  reduces the impact of the changing of the gate voltage. If the exponential dependence of  $V_{gs}$  on the drain current is taken into account, some of the effect of  $\kappa$  can be shown. The exponential function, exp(ax), for a = 0.1, 0.2, ..., 1.0, is shown in figure 2.2. When  $\kappa$  decreases the effect of a change in  $V_{gs}$  is reduced, analog to this figure. Simulating a transistor using for example the BSIM3V3 model displays a more complex behavior. The drain current depends on several additional parameters.

An approximated  $\kappa$  has been extracted from figure 2.1. In the case when  $I_{ds}$  varies between  $1\mu A$  and 1 nA,  $V_{gs}$  must change in average about 89 mV to change the current by a factor of 10.  $\kappa$  is relatively constant in the 10 pA to 1  $\mu$ A range. For the ideal exponential function this would only have to be 60 mV. If  $U_t = 25.8$  mV is used as unity voltage, and an 89 mV change in  $V_{qs}$  for a 10-fold change in  $I_{ds}$  is needed:

Figure 2.1:  $I_{ds}$  is shown as a function of  $V_{gs}$  for  $V_{ds} = 0.1, 0.2, ..., 1.0[V]$ . The size of the NMOS transistor is W/L=20.8 $\mu$ m/1.2 $\mu$ m. The threshold voltage is approximately 0.85 V [AMS98]. The actual W/L ratio is used for several of the circuit structures realized.

$$\kappa \frac{89}{25.8} = \ln(10) \tag{2.3}$$

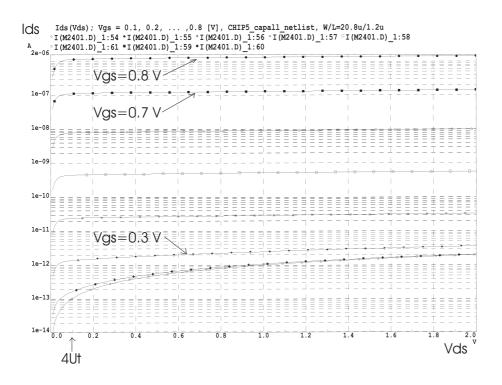

This gives  $\kappa = 0.67$ , compared to the  $\kappa$  value of 0.7 mentioned in [Mead89] p. 38. In figure 2.3 simulation results are shown where  $V_{gs}$  differs by 100 mV for each curve. When  $V_{ds}$  is above about 100 mV it is easy to see that the current level increases drastically for these increases in  $V_{gs}$ , while it is less dependent on the  $V_{ds}$  level. When  $V_{ds} > 4kT/q$  the transistor is in saturation [AnBo91]. The small-signal transconductance in saturation is [AnBo91], [IsFi94]:

$$g_m = \frac{\Delta I_{ds}}{\Delta V_{gs}} = \frac{\kappa I_{ds}}{U_t} \tag{2.4}$$

Figure 2.2: exp(ax), for a = 0.1, 0.2, ..., 1.0.  $\ln(10)=2.302$  is how much the exponent must increase in order to increase the functional value by 10 times.

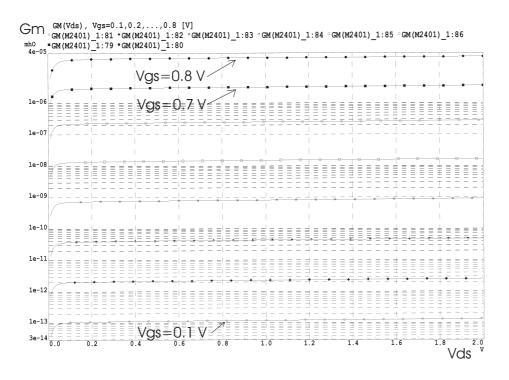

Figure 2.3:  $I_{ds}$  is shown as as a function of  $V_{ds}$ , for  $V_{gs} = 0.1, 0.2, ..., 0.8[V]$ . The current increases when  $V_{gs}$  increases. W/L =  $20.8 \mu m/1.2 \mu m$ . The NMOS netlist used for simulation is extracted from layout.

Simulated transconductances for an NMOS transistor with  $W/L = 20.8 \mu m/1.2 \mu m$  are shown in figure 2.4. The output conductance is given by [AnBo91]:

$$g_{ds} = \frac{\Delta I_{ds}}{\Delta V_{ds}} \tag{2.5}$$

For  $V_{ds}$  greater than or equal to  $4U_t$ , the output conductance may be written [AnBo91]:

$$g_{ds} = \frac{I_{ds}}{V_o} \tag{2.6}$$

The conductance is proportional to the drain current,  $I_{ds}$ , for a given transistor.

Figure 2.4: Transconductance,  $g_m$ , is simulated as a function of  $V_{ds}$  for  $V_{gs} = 0.1, 0.2, ..., 0.8[V]$ . In the saturation region,  $g_m$  increases proportionally to  $I_{ds}$ .

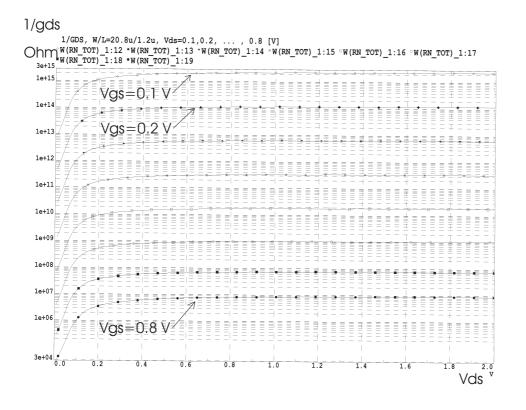

Figure 2.5: Output resistance is simulated as a function of  $V_{ds}$  for  $V_{gs} = 0.1, 0.2, ..., 0.8[V]$ . The output resistance decreases for an increase in  $V_{gs}$ .

$$r_{out} = \frac{1}{g_{ds}} \tag{2.7}$$

Output resistance is depicted in figure 2.5. The output resistance decreases proportionally with an increasing  $V_{gs}$ , which at the same time means a growing current level.

In the common-source mode the transistor can be used as an inverting amplifier with voltage gain

$$A = \frac{g_m}{g_{ds}} = \frac{\kappa V_o}{U_t} \tag{2.8}$$

which is constant for a given temperature, and for a  $V_o$  of 15 V gave a gain of 430 in [AnBo91].

#### 2.1.2 Floating-gate CMOS transistors

From practical reasons the floating-gate UV-programmable circuits are most often modeled in the weak inversion region, even if the operation might be partly in moderate and strong inversion. This is also used throughout this thesis.

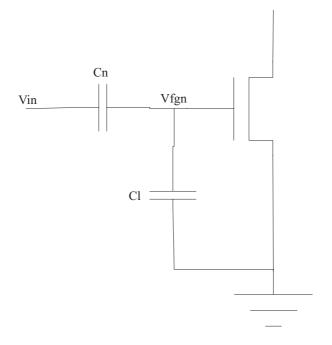

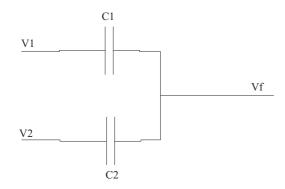

If an input signal to the gate of a MOSFET is connected via a capacitor,  $C_n$ , we have a floating-gate transistor, like in figure 2.6. For practical purposes, the gate has no DC path to ground. The charge on the floating gates, and thereby the effective threshold voltages, can be changed by Fowler-Nordheim tunneling, Hot Electron Injection or UV-light, in different ways [HaLa01], [KoGo01]. To illustrate the behavior we make the assumption that the NMOS floating gate "sees" a total load capacitance,  $C_l$ , between the floating gate and the source [LaWi96]. This  $C_l$  is not constant in reality, but is treated as such in this simple model, illustrated in figure 2.6. The poly layer forming the floating gate does contribute to  $C_l$  as well, so that increasing  $C_n$  leads to an increase in  $C_l$ .  $C_l$  also incorporates parasitic capacitances from the transistor, seen from the floating gate.

Figure 2.6: Simple model of floating-gate transistor.

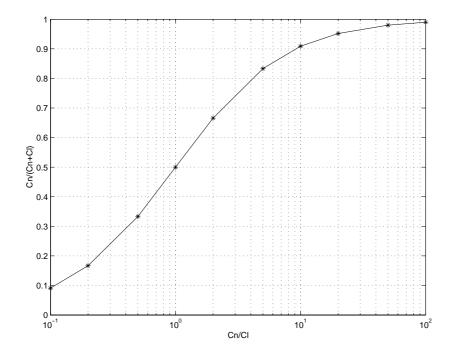

Figure 2.7:  $\frac{C_n}{C_n+C_l}$ , capacitive division involving the drawn capacitance between input and floating gate and parasitics.

$$\Delta V_{fgn} = \frac{C_n}{C_n + C_l} \Delta V_{in} \tag{2.9}$$

The amount of the signal  $V_{in}$  in figure 2.6 that slips through to the floating gate,  $V_{fgn}$ , depending on the ratio between the coupling capacitor and the load capacitor;  $C_n/(C_n+C_l)$ , is depicted in figure 2.7. In the AMS 0.8 CMOS process a coupling capacitance,  $C_n$ , of twice the size of the load capacitance,  $C_l$  was implementable without any area penalty [LaWi96]. As can be seen from figure 2.7 that case would allow approximately two thirds of the signal perturbation on the input through to the floating gate, while equally sized  $C_n$  and  $C_l$  would let 50% through.

In figure 2.8 it is demonstrated, with our  $20.8\mu m/1.2\mu$ m MOSFET and for a  $\kappa$  of 0.67, how much signal is needed on the floating gate to make the current change a certain amount, assuming that it follows a simple exponential function. The second curve from the top shows the function for  $\kappa = 0.67$ , and the uppermost curve the unrealistic case (for standard CMOS) when  $\kappa = 1.0$ . For equally sized  $C_n$  and  $C_l$ , letting 50% of the input

Figure 2.8: exp(0.67ax), for a = 0.1, 0.2, ..., 1.0, and the case exp(x)

signal perturbation through to the floating gate, and a  $\kappa$  of approximately 0.67, the relevant line in figure 2.8 is the 5th one counted from the bottom (of 11). From that curve a change of 7 units along the horizontal axis would lead to a little bit more than 10 times change in the output value. If this is translated to an NMOS transistor with  $U_t = 26$  mV as unity, this would correspond to a  $\Delta V_{gs}$  of 7 times 26 mV, or 182 mV, needed to change the magnitude of the drain-current, or output conductance of a single transistor roughly a factor of 10. In comparison an ideal MOSFET with  $\kappa = 1.0$  and  $C_n/(C_n + C_l) \approx 1$  would require a  $\Delta V_{gs}$  of 60 mV to produce the same change in the output current under the same circumstances. Taking such damping of the input into account gives the following form of the equation for the current in saturation

$$I_{ds,n} = I_0 exp\{\frac{\kappa V_{gs}(\frac{C_n}{C_n + C_l})}{U_t}\}$$

(2.10)

Using more than one capacitively coupled input signal to the floating gate of a transistor adds properties to floating-gate transistors, as will be treated later in this thesis.

#### 2.1.3 Single-input floating-gate MOSFETs

Since the sizes of the capacitances between one or several input signals relative to parasitics determines how much of the input signal that gets through to the floating gate, and thereby the transconductance and output resistance of a device, this is examined somewhat further. Firstly a very simple model is mentioned, thereafter one slightly more advanced. SPICE-based simulations using a basic floating-gate inverter are used to illustrate some of the behavior of the relevant capacitances associated with the floating gate.  $C_{ox}$  per area of a large area capacitor is calculated from [AlHo87]

$$C_{ox} = \frac{\epsilon_{ox}}{t_{ox}} \tag{2.11}$$

where  $\epsilon_{ox}=34.515 \text{ pF/m}$ , and the thickness of the gate insulator,  $t_{ox}$ , is typically 12.5 nm [AMS98]. The value of integrated circuit capacitors can be approximated by  $C = C_{ox}A$ , where A is the area of the capacitor [AlHo87]. Using a simple model for manual analysis, the gate capacitance,  $C_g$ , equals  $C_{ox}WL$ , and can be decomposed in a number of elements with different behavior, including parts solely dependent on the topological structure of the device, and other nonlinear capacitances depending on applied voltages on the MOSFET terminals [Raba96]. For a device with W=20.8 $\mu$ m and L=1.2 $\mu$ m,  $C_g$  is estimated to 68.9fF using our technology of choice.

In reality, both source and drain tend to extend somewhat below the oxide by an amount  $x_d$ , called the lateral diffusion. This means that the effective channel length of the produced transistor,  $L_{eff}$  becomes shorter than the drawn length, or the length the transistor originally was designed for, and also leads to parasitic capacitances between the gate and the source and drain terminals. These are called overlap capacitances [Raba96], and have have fixed values.

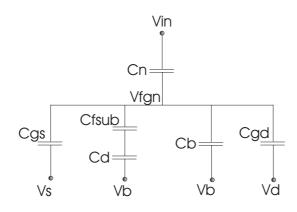

Some slightly more complex view on the parasitic capacitances are briefly mentioned here, in an attempt to provide a brief view of factors providing a little bit more realistic picture. Different models take into account different approaches or parameters influencing the floating gate, like in [WoLi92], [YaAn93], [ChKi94], [FuAr01]. Figure 2.9 is taken from [YaAn93], and it shows that the floating gate voltage,  $V_{fgn}$ , is dependent on the voltage on the input(s) as well as voltages coupled from source, substrate and drain. The subthreshold capacitance models used in [FuOm98], [YaAn93] take 4 parasitic capacitances into account. Capacitances  $C_{gs}$ ,  $C_{gd}$ , and  $C_{gb}$  are parasitic capacitances from the (floating-) gate to the source, drain and bulk, respectively.  $C_{ox}$  is the oxide capacitance. If there is one drawn capacitance,  $C_n$ , between the only input,  $V_{in}$ ,

Figure 2.9: Capacitor model of a floating-gate MOSFET [YaAn93].  $V_{cg}$ ,  $V_s$ ,  $V_b$ ,  $V_d$  denote voltages on the input, source, bulk and drain, in that order.

and the floating gate, we can denote the sum of capacitances "seen from" the floating gate as:

$$C_{sum} = C_n + C_{gs} + C_{gd} + C_{gb} + C_{ox}$$

(2.12)

The weighted sum of voltages coupled via capacitances is in many cases not the only factor determining the voltage on a particular floating gate. A charge  $Q_g$  can be left after production of the chips, or it can be set by Fowler-Nordheim tunneling, hot-electron injection or UV-illumination. UV-illumination might also be used to remove all charge from the floating gate, so that  $Q_{fg} = 0$  [FuOm98]. After production the floating gate voltages are somewhat random, even for identically drawn structures [BeWi99]. The voltage on the floating gate of the NMOS,  $V_{fgn}$ , can be written

$$V_{fgn} = \frac{C_n V_{in} + C_{gs} V_s + C_{gd} V_d + C_{gb} V_b + C_{ox} V_{sur} + Q_{fg}}{C_{sum}}$$

(2.13)

where  $V_{sur}$  is the surface potential [YaAn93], [FuOm98]. The parasitic capacitances may be nonlinearly dependent on applied voltages. Some parasitics in the subthreshold capacitance model [FuOm98], [WoLi92], [YaAn93] have been simulated using the Eldo simulator, for supply voltages of 200 mV and 800 mV, and  $I_{beq}$ -levels in the 1nA to 1000 nA range. The circuit is an inverter and the netlist extracted from layout (*CHIP5\_capall\_netlist*) [Aune02]. They are extracted from a transient simulation like the one in

Figure 2.10: Capacitances related to the  $20.8\mu m/1.2\mu m$  PMOS and NMOS are shown. "CGS(M2401)", for example, means the capacitance between gate and source for the NMOS in the inverter.

| 24Multiple-input U | V-programmable. | MOSFETs and | two-MOSFET | circuits |

|--------------------|-----------------|-------------|------------|----------|

|--------------------|-----------------|-------------|------------|----------|

| $V_{dd}[V]$ | $I_{beq}[nA]$ |                 | $C_{gdp}[\mathrm{fF}]$ | $C_{gsn}[\mathrm{fF}]$ | $C_{gdn}[\mathrm{fF}]$ | $C_{gbp}[\mathrm{fF}]$ | $C_{gbn}$       |

|-------------|---------------|-----------------|------------------------|------------------------|------------------------|------------------------|-----------------|

|             |               | $[\mathrm{fF}]$ |                        |                        |                        |                        | $[\mathrm{fF}]$ |

| 0.2         | 1             | 6.9             | 7.3                    | 4.7                    | 7.3                    | 16                     | 24.5            |

| 0.2         | 10            | 7.0             | 7.3                    | 4.7                    | 7.3                    | 15.9                   | 24              |

| 0.2         | 100           | 8.5             | 7.3                    | 5.0                    | 7.3                    | 15.1                   | 23.3            |

| 0.2         | 1000          | 27.3            | 7.7                    | 9.4                    | 7.4                    | 10.2                   | 21.4            |

| 0.8         | 1             | 6.9             | 7.3                    | 4.7                    | 7.3                    | 16.7                   | 24              |

| 0.8         | 10            | 7.0             | 7.3                    | 4.7                    | 7.3                    | 16                     | 24              |

| 0.8         | 100           | 8.4             | 8.4                    | 5.1                    | 7.3                    | 15                     | 23.4            |

| 0.8         | 1000          | 27              | 6.7                    | 9.6                    | 6.7                    | 10                     | 21              |

Figure 2.11: MOSFET average channel capacitances for different operation regions have been simulated. The "n" in  $C_{gsn}$ , for example, means the capacitance between gate and the source of an NMOS transistor. The unexpected relation  $C_{gd} > C_{gs}$  may come from a misbehaviour in the netlist extraction tool.

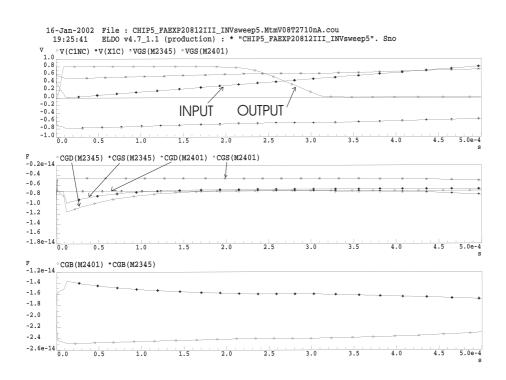

figure 2.10. The values used are taken from the time of the simulation where the output voltage, V(C1NC), changes from 0.8 V to 0 V (figure 2.10), around a time of 0.26-0.27 ms. V(X1C) means the input signal and VGS(M2345) and VGS(M2401) (figure 2.10) mean the gate-to-source voltages of the PMOS and NMOS respectively. Results can be found in figure 2.11. The parasitic capacitances are relatively constant until the  $I_{beq}$  changes from 100 nA to 1000 nA. The parasitic capacitances influence a range of important parameters such as voltage gain and transconductance. This makes them interesting to model, for example for the switching region of subcircuits, where voltage gain might be especially important.

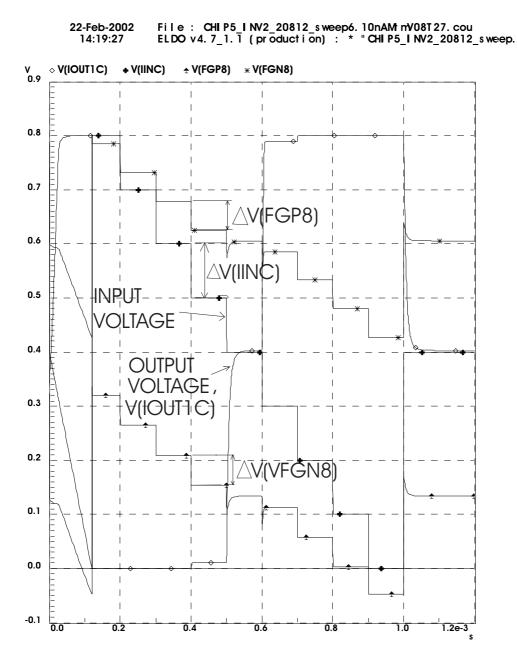

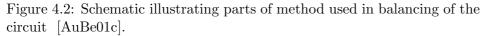

To illustrate the effect of sizing of drawn capacitances between the input and a floating gate, some simulations relevant to circuitry integrated on chip have been done. The input to an inverter were changed abruptly in steps, and the resulting steps on each of the two floating gates were measured, close to the switching point. Simulations as depicted in figure 2.12 were done, using capacitances of 74.6 and 122.7 fF, and an  $I_{beq}$  of 10 nA, measured at about 0.4 ms. Results are shown in figure 2.13, demonstrating that the bigger capacitance out of the two let more of the changing input signals through to the floating gate than the smaller one.

In figure 2.14 the inverter function of a P5N5 element is both simulated and measured on chip. The total change of the drain current of the inverting element spans between two and three decades of magnitude both for the

Figure 2.12: The input signal, V(IINC) is changed in 100 mV steps, and the floating gate voltages, V(FGN8) and V(FGP8), for NMOS and PMOS respectively, are shown. V(IOUTC) is the output voltage of the inverter.

| $C_n[fF]$ | $\Delta V_{fgp8} / \Delta V_{iinc} [\%]$ | $\Delta V_{fgn8} / \Delta V_{iinc} [\%]$ |

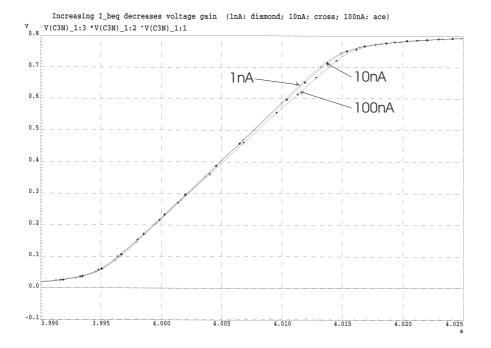

|-----------|------------------------------------------|------------------------------------------|