# Obfuscating Malware through Cache Memory Architecture Features

Çağlar SAYIN

Masteroppgave Master i Teknologi - Medieteknikk 30 ECTS Avdeling for informatikk og medieteknikk Høgskolen i Gjøvik, 2014

Avdeling for informatikk og medieteknikk Høgskolen i Gjøvik Postboks 191 2802 Gjøvik

Department of Computer Science and Media Technology Gjøvik University College Box 191 N-2802 Gjøvik Norway

# Obfuscating Malware through Cache Memory Architecture Features

Çağlar SAYIN

2014/06/01

# Abstract

There is no doubt that malicious software (malware) is one of the most important threat in computer security. With increasing of the information systems and computer network usage in the industrial and governmental infrastructures, their economy and impact over our society are increasing. According to Symantec's report in 2008[1], "The release rate of malicious code and other unwanted programs may be exceeding that of legitimate software applications." The worst of all, malware design is not as simple as how it was before. A few years ago, we saw countries who developed malware as a professorial weapon for their political benefits, and it would not be surprising if one of these weapons were seen in the corporate world soon. This malware was utilized with many camouflaging techniques (e.g. polymorphism, metamorphism, etc.) against the malware detection system.

Basically, the most of the camouflaging techniques obfuscate and hide the signatures to be stored safely in a non-volatile memory or disk, and before they started to run on the main memory, they deobfuscate the whole code to execute. Consequently, the detection systems have simply started to search the signatures in the main memory. In this thesis, we designed a way to raise the bar from "from disk to memory obfuscation" to "from disk to cache obfuscation". More specifically, we designed theoretical malware obfuscation methods for tightly coupled multi-processor systems which utilize caches as a private memory to evade main memory observer systems as well as other conventional static data analysis. In order to achieve this goal, we anticipated cache behaviours and exploited them as well as cache efficiency optimizations. With increasing deployment of multi-processor computing and other parallel processing devices, the implementation of local memories like NUMA and hierarchical caches are increasing in order to increase efficiency and performance and decrease power consumption, and this can be even the only reason which highlight our studies. Additionally, this thesis discusses implementation issues arising from interactions between cache coherence mechanisms as well as from Harvard architecture implementations

## **Keywords**

Security, Malware Design, Cache Oriented Polymorphism, Cache Coherency, Malware Evasion, Code Obfuscation

# Preface

I would like to express my gratitude to my supervisor Prof. Stephen D. Wolthusen for the useful comments, remarks and engagement through the learning process of this master thesis. I can simply say that every sentence which he built was enlightening not only during this this process, but also in his courses. Furthermore, I would like to thank Emre Tinaztepe for sharing his fabulous practical knowledge with me to the topic as well for the support on the way. Also, I like to thank the team in Stanford University who develops BookSim Simulation tool and willingly share experience. I would like to thank my family. Words cannot express how grateful I am to my mother for all of the supported me in writing, and incited me to strive towards my goal.

Finally, I would like to thank to all free software volunteers.

Çağlar Sayın 2014/06/01

# Ethical and legal considerations

The content of this document could be used for malicious purpose, but any matter or information could be misused in the life. The risky threat is not the information in this thesis, but to be ignorant about them. For this purpose, this thesis aims to enlighten security specialist and system developers against the recent methods of the possible attacks.

However, in order to act ethical responsibility, we tried to eliminate practice of tools and piece of codes which could leads malicious usage. In any case, there is no doubt that it is critical to discover and publish vulnerabilities which could cause deep impact before malicious people discover and abuse them.

"Virus don't harm, but ignorance does." - VxHeaven

# Contents

|   |      |          | ii                                                  | ii |

|---|------|----------|-----------------------------------------------------|----|

|   |      |          |                                                     | v  |

|   |      | -        | al considerations                                   |    |

|   |      |          | i                                                   |    |

|   |      | U        |                                                     | ci |

|   |      |          | xii                                                 |    |

| 1 |      |          |                                                     | 1  |

|   | 1.1  | -        | <b>J I J</b>                                        | 1  |

|   | 1.2  |          | 1                                                   | 1  |

|   | 1.3  |          | ,                                                   | 2  |

|   |      |          | 1                                                   | 2  |

|   | 1.4  |          |                                                     | 2  |

|   | 1.5  |          |                                                     | 3  |

| 2 | Rela |          |                                                     | 5  |

|   | 2.1  |          |                                                     | 5  |

|   | 2.2  |          | · · · · · · · · · · · · · · · · · · ·               | 6  |

| 3 | Back |          |                                                     | 9  |

|   | 3.1  | Caches   |                                                     | 9  |

|   |      | 3.1.1    | Motivation of Caches and Principle of Locality      | 9  |

|   |      | 3.1.2    | The basic logic of caches                           | 0  |

|   |      | 3.1.3    | Allocation, Write and Replacement Policies          | 2  |

|   |      | 3.1.4    | Miss Type and Advance Cache Optimization Methods 14 | 4  |

|   | 3.2  | Cache    | Coherence and Consistency                           | 5  |

|   |      | 3.2.1    | Snooping Coherence Protocols                        | 7  |

|   | 3.3  | Inter-c  | onnector Design                                     | 2  |

|   |      | 3.3.1    | Topology                                            | 4  |

|   |      | 3.3.2    | Topologies                                          | 6  |

|   |      | 3.3.3    | Switching                                           | 7  |

|   |      | 3.3.4    | Routing 24                                          | 8  |

|   |      | 3.3.5    | Flow Control                                        | 9  |

| 4 | Cacł | ne Orien | nted Obfuscation                                    | 1  |

|   | 4.1  | Exploit  | ting Tightly Coupled Multi-Processing Systems       | 2  |

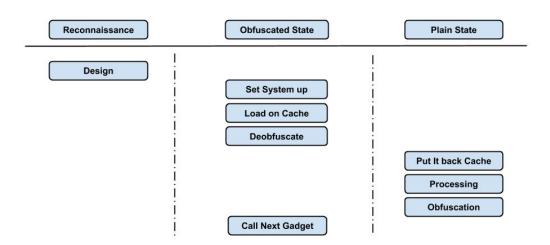

|   |      | 4.1.1    | Reconnaissance and Design 33                        | 3  |

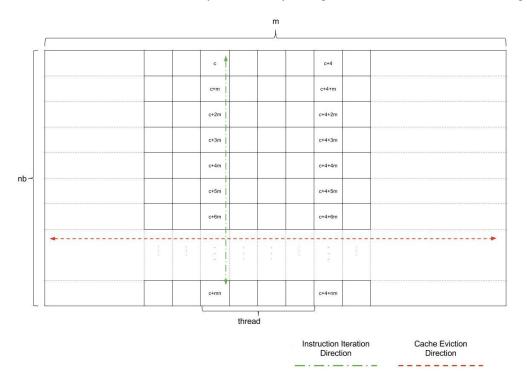

|   |      | 4.1.2    | Setting System up and Loading Cache Memory 34       | 4  |

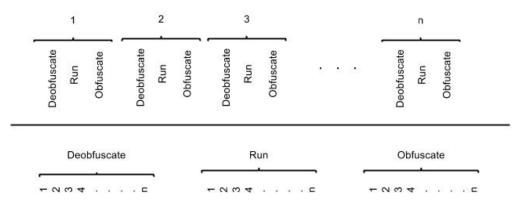

|   |      | 4.1.3    | Obfuscating, Running and Deobfuscating Gadget 30    | 6  |

|   | 4.2  | Pitfalls | , Limitations and Fallacies                         | 8  |

| 5 | Prob | abilisti | c Timing Attack against to Snoopy Cache Coherency 4 | 1  |

|   | 5.1  |          | sue                                                 | 1  |

|   | 5.2  |          | on                                                  |    |

|   |      | 5.2.1    | Horizontal Directional Cache Fetching 44            | 2  |

|    |       | 5.2.2    | Synchronization Latency of Snoopy Caches                        | 44 |

|----|-------|----------|-----------------------------------------------------------------|----|

|    |       | 5.2.3    | Overall Explanation of the Timing Attack                        | 49 |

|    | 5.3   | Pitfalls | s, Limitations and Fallacies                                    | 51 |

| 6  | Imp   | lement   | ation on Harvard Computer Architecture                          | 53 |

|    | 6.1   | The Is   | sue                                                             | 53 |

|    | 6.2   | Solutio  | on                                                              | 55 |

|    |       | 6.2.1    | Flying over Interpreter                                         | 55 |

|    |       | 6.2.2    | Forth Interpreter Language                                      | 56 |

|    | 6.3   | Pitfalls | s, Limitations and Fallacies                                    | 57 |

| 7  | Con   | clusion  | and Further Works                                               | 59 |

| Bi | bliog | raphy    |                                                                 | 63 |

| Α  | Cac   | he Men   | nory Simulation                                                 | 67 |

| В  |       | -        | ns Cache Coherency Latency Simulation Results                   | 71 |

|    | B.1   | Small    | Topology                                                        | 71 |

|    |       | B.1.1    | Small Topology Simulation with Two Percent Injection Rate Con-  |    |

|    |       |          | figuration File and Results                                     | 71 |

|    |       | B.1.2    | Small Topology Simulation with Four Percent Injection Rate Con- |    |

|    |       |          | figuration File and Results                                     | 77 |

|    | B.2   | Crowd    | led Topology                                                    | 85 |

|    |       | B.2.1    | Crowded Topology Simulation with Two Percent Injection Rate     |    |

|    |       |          | Configuration File and Results                                  | 85 |

|    |       | B.2.2    | Crowded Topology Simulation with Four Percent Injection Rate    |    |

|    |       |          | Configuration File and Results                                  | 94 |

# List of Figures

| 1  | Detection models [2]                                                      | 7  |

|----|---------------------------------------------------------------------------|----|

| 2  | Principle of Locality                                                     | 10 |

| 3  | 4 KB 4-way set associative cache with 256 cache lines                     | 11 |

| 4  | A. A Write-Through cache with No-Write Allocation B. A Write-Back cache   |    |

|    | with Write Allocation                                                     | 12 |

| 5  | Write-back Policy Cache Memory Inconsistency                              | 16 |

| 6  | Write-through Policy Cache Memory Inconsistency                           | 16 |

| 7  | MSI State Diagram for processor P1                                        | 19 |

| 8  | MESI State Diagram for processor P1                                       | 20 |

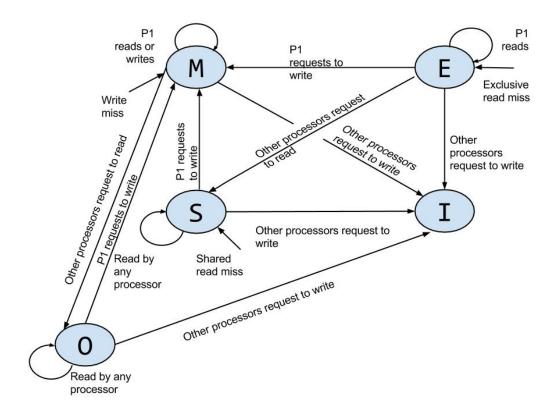

| 9  | MOESI State Diagram for processor P1                                      | 21 |

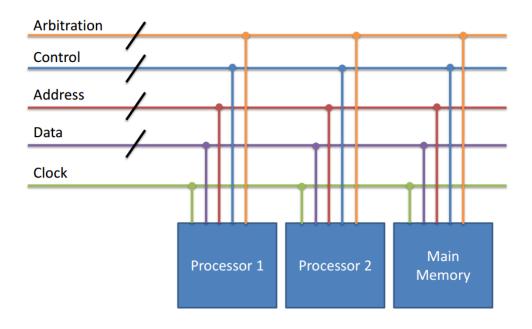

| 10 | Primitive Multi-Drop Memory Bus                                           | 22 |

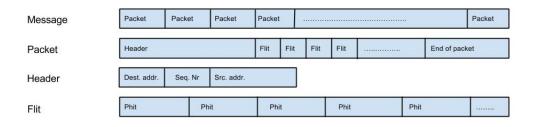

| 11 | An example of interconnector message anatomy                              | 23 |

| 12 | A) Bus topology example B) Ring topology example                          | 25 |

| 13 | A) Mesh topology example B) Torus topology example C) 3D mesh topo-       |    |

|    | logy example[3]                                                           | 25 |

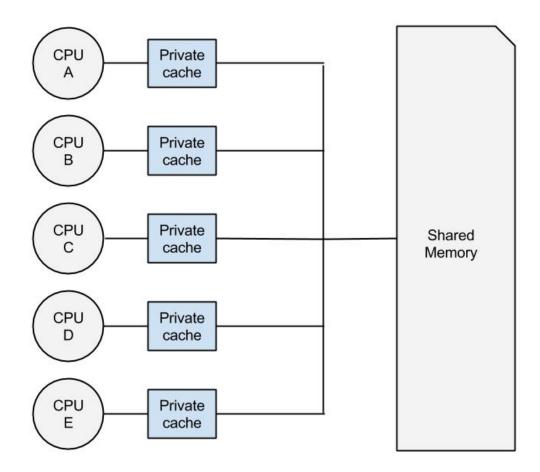

| 14 | An Example of Tightly Coupled Multi-Processing Systems                    | 32 |

| 15 | Attack vector flow chart                                                  | 33 |

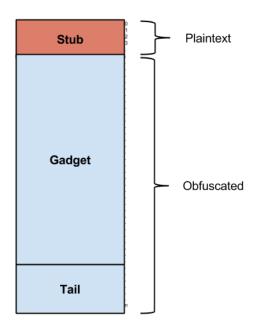

| 16 | Gadget Sections                                                           | 34 |

| 17 | Control Flow Illustration A) Stepped Control Flow B) All at Once Control  |    |

|    | Flow                                                                      | 37 |

| 18 | Directional Exploitation                                                  | 43 |

| 19 | The Time Line of the Fetching Cache Line which is Used by Another Cache   | 44 |

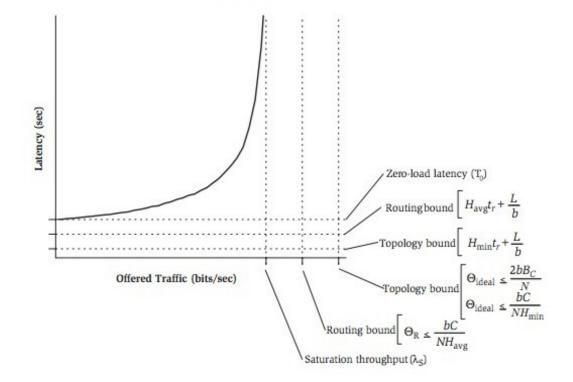

| 20 | Interconnector Latency Versus Offered Traffic [4]                         | 45 |

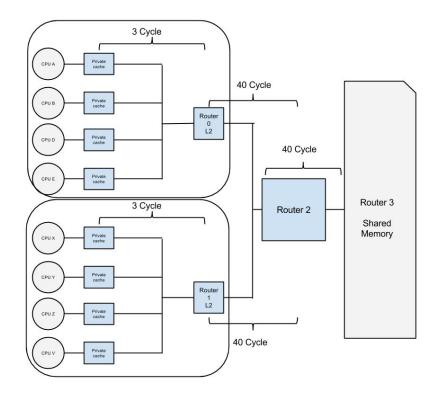

| 21 | Our Simulation Topology[4]                                                | 47 |

| 22 | The illustration of cache and time Interaction is showed with leaked por- |    |

|    | tion of obfuscated data                                                   | 49 |

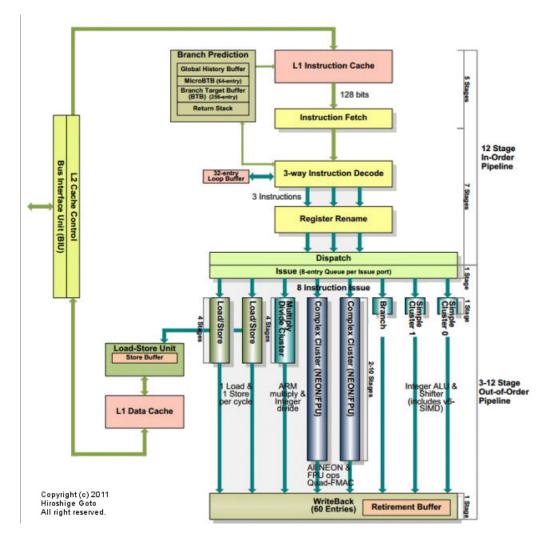

| 23 | Cortex A15 Block Diagram [5]                                              | 54 |

| 24 |                                                                           |    |

# List of Tables

| 1 | MSI states' properties        | 18 |

|---|-------------------------------|----|

| 2 | MESI states' properties       | 19 |

| 3 | MEOSI states' properties      | 21 |

| 4 | Simulation Results Comparison | 48 |

# 1 Introduction

The purpose of this chapter is to give introduction of the subject and challenge in question, as well as justification and motivation of its importance. The chapter also propose research question to guide the thesis. The purpose of this chapter is to give introduction of the subject and challenge

## 1.1 Topic covered by the project

This thesis is mainly about a novel approach to specially malware obfuscation methods although software obfuscation concept is the more broad topic. Malware is the short malicious software and can cover any program or script that is harmful to a system or its user. One of the biggest discussion is a definition of harmful on computer security. It is quite hard to define what harmful is and what malicious is. Because of the reason why we cannot classify software easily, whether malicious or not, the most efficient and suitable way to detect them is a black or white listing. Basically, there are predefined list of software which claims they are good or evil. This black lists are comprised with signatures of the software which are presumed malicious; then, we are looking for these signatures in our computers to detect malware.

Even if these lists include every possible signature, malware can evade signature detection with obfuscating itself over and over again. For each attempt, it reproduces itself, and thus, it conceals the signature. However, there are many countermeasures against them[6][7]. For example, memory dumping and scanning later is recently one of the trendy detection methods<sup>1</sup>. It is quite reasonable because while the malware is running over memory, it is naked and vulnerable.

In this thesis, we are seeking possibilities to enhance "Disk-memory level" to cache level. It is a pretty novel contribution to the computer security field because there have been a few works, so far, about what we are searching for.

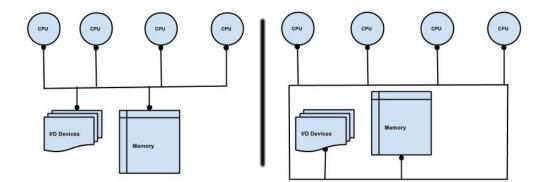

# 1.2 Problem description

The conventional PC architecture is now which security researchers, developers and malware authors familiar with. However, the density of development spreads around other architecture instead of common PC arch.. For example, mobile devices recently have much higher profile at this point comparing with our conventional desktop systems.Besides, hardware platforms especially for mobile devices are increasing in complexity and sophistication with the use of multi-processor systems becoming common place as well as the use of many layer memory architectures, such as NUMA, caches for performance and efficiency(esp. on power consumption).This opens new opportunities for obfuscation and concealment of malware.

Apart from the basic signature-based methods known to be ineffective against unknown threats, there are two mainstream techniques to detect malicious code which are called static and dynamic analysis, but indeed, the main stream method is still signature-

<sup>&</sup>lt;sup>1</sup>Especially, after boot level rootkits

based ones. Static analysis identifies malware mainly with code flow graph and data flow graph obtained from static information, while dynamic analysis is taking account dynamic execution features.

There are number of techniques for obfuscating, some relying on the precise properties of the hardware and its behaviours, that can render static analysis ineffective as well as signature analysis. Some of the key techniques deployed by malware authors for obfuscation do include race condition and exploitation of memory uses. The detection algorithms and techniques have been adequately worked so far because of the simplicity of our conventional architectures and using generic PC architecture despite these systems also started to become more heterogeneous(e.g. Intel Haswell). However, with increasing deployment of multi-processor computing and other parallel processing devices, the implementation of local memories like NUMA and caches are increasing in order to increase efficiently and performance and decrease power consumption. It is obviously clear that these features will also be exploited by malware authors at some point. The project seeks to investigate the feasibility of such malware both from a theoretical viewpoint and through the development of a proof-of-concept.

# 1.3 Justification, motivation and benefits

If malware designing is superficially considered, you could fall in the usual fallacy that it is not beneficial, and maybe it is malicious. However, if we can design it, there is always a more skillful malicious author who might already abuse this vulnerability on the black side of the moon. The duty we are actually obligated to discover these vulnerabilities and design countermeasure against them. In this way, our blessed motivation is finding possible vulnerabilities, and mitigate or eliminate their risk. Otherwise; if we are lucky, we might detect these zero time vulnerability attacks, yet it could be too late to fix and analyze them. Besides, for example, some of the most sensational and beneficial papers([6],[8],[7]) are criticizing malware with designing them as like as we do, and their values over computer security are undoubted today.

In short, we are building brakes. Sometimes they are that thing slow us down, or sometimes they even stop us in our tracks. However, they are actually there to enable us to go faster and secure.

#### 1.3.1 Research questions

- 1. How can an obfuscation method, which exploits caches to conceal information from the observers, be designed for tightly coupled and multiprocessor systems?

- 2. How can the efficiency optimisations of common cache coherency protocols found in tightly coupled multiprocessor systems be exploited for probabilistically hiding and obfuscating malware?

- 3. How can we execute deobfuscated code on the Harvard Architecture without leakage to upper memories?

## 1.4 Choice of methods

In order to solve our problems, we followed particular research methodologies for each question.

In the first question, we limited the question with tightly coupled and multi-processor systems, and we chose the design science methodology to follow during our work and we

supported it with literature review methodology. First, we started to seek cache memory architecture to understand how they work, interact with each other and affect performance. Then, we classified them in a proper way, and we noted all remarkable points in background studies chapter section 1. Besides, we try to seek practical implementation on new ARM based boards. We obtained ARM little big multi-processor based Samsung Exynos 5410 and 5420 systems on the chip boards to explore their cache memory implementation. Next, we proposed an attack vector under a constant isolated theoretical system which has the most basic tightly coupled, multiprocessor and Von Neumann architecture with write back cache policy and without cache coherency. At the end of the solution, we clearly stated possible implementation problems which we can encounter during implementation and gave references to the next questions.

In the second question, we used literature which we have already researched, and we inspected the architectural detail of modern cache coherency techniques, especially snoopy cache coherency and multi-processor interconnector design in order to describe a model to exploit the efficiency optimization of common cache coherency protocols found in multiprocessor systems. When we used design science method in this chapter, we used a quantitative approach to measure possible interconnection network latency. This approach is prepared with a simulation experiment whose simulation tools have already been acknowledged by many processor producers as accurate on its latency cycle calculation. We totally designed 4 experiments which are crowded and small topologies with congested and silent traffics and present our results in Appendix B as well as Chapter 5. At the end of the chapter, we built and designed a method to exploit the efficiency optimization of lazy cache coherency found in multiprocessor systems.

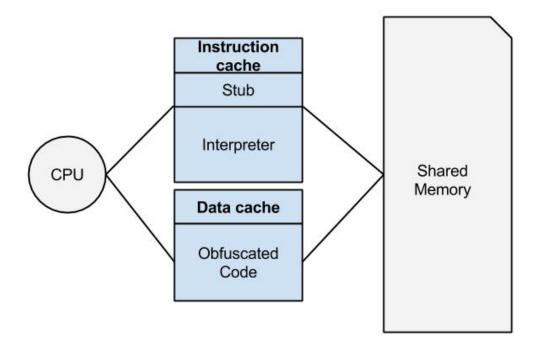

For the third question, at the end of the literature overview, we found a similar cases[9][10], which can empower our solution. The problem which we try to solve is not what they are trying to do, but it simultaneously solved our problem. We built our model and concluded interpretation approach which has been seen in previous studies with our own model. When we designed our own model, we used our attack vector which we proposed in Chapter 4 and merge it with a interpreter to execute the code in DCache, which we can access, load and store, but we cannot execute. At the end of the studies, we discussed and criticized practical issues which we can fall during the implementation of our theoretical model.

### 1.5 Thesis Outline

This section provide a brief summary listing of the content presented in this thesis. The listing is based on chapters, where each chapters and its content is described. First the related works and background studies are presented. Then, our designs is presented as well as further work and conclusion in a sequence. At the end of the thesis, we attached the simulation code which we wrote and the experiments results by Booksim v2.0 to appendix.

• Chapter 2 is related works chapter, which presents the literature related to malware, code obfuscation and countermeasures against malware. Firstly, we give the malware self defense methods' literature, and then, we conclude it with malware analysis and detection methods' literature.

- Chapter 3 is background studies chapter, which presents the background knowledge to design the cache oriented obfuscation system. Our studies are highly related to computer architecture and organization knowledges. Firstly of all, we start with cache related studies. We explain the motivation of cache, how they are working. Then, we conclude them with details about caches. Secondly, we mention about cache coherency and consistency and this section involve with an explanation of snoopy cache coherency protocols. At the end of the chapter, we describe computer interconnection network's basics. This section highly involves with their design features and their effects on the interconnector performance.

- Chapter 4 is called "Cache Oriented Obfuscation". In short, this chapter defines the basics of our thesis. In the chapter, we propose a method to exploit tightly coupled multi-processor systems and explain details and the attack vector which we propose. At the end of the studies, we discuss the pitfalls, limitations and fallacies.

- Chapter 5 is the chapter which we try to solve our second research question. We propose a probabilistic attack method to hide or obfuscate malware. We also define several formulas in this chapter to measure coherency latencies. It also includes experiment results which we designed with a interconnection simulation tool, Booksim. At the end of the studies, we discuss the pitfalls, limitations and fallacies.

- Chapter 6 includes the answer of our third research question and proposes a solution for the Harvard Computer Architecture implementation issue. It includes some elementary studies about virtual machine designing and interpretation. At the end of the studies, we discuss the pitfalls, limitations and fallacies.

- Chapter 7 concludes and summarizes the most important findings in this thesis and add presents a range of topics that should be further work to better understanding of countermeasures and to implementing the theoretical studies which we proposed.

- Appendix A is attached with the python code of simple cache simulation. We used this code to enhance our intuition over cache behaviors. It could be useful to proof our studies further.

- Appendix B includes the experiment results, which are very detailed, and configuration files to replicate it. It could be useful to proof our latency experiments and proposals further.

# 2 Related Works

## 2.1 Malware Self-Defense

This section will give an overview of researches about Malware's self-defense technique, the methods to analyze them, and their application on concurrent architecture. This section will try to give the literature about malware evasion techniques. These techniques are generally antonym solution which by malware authors, however, there are enough surveys about known technique. We classified all these methods in six categories which are code obfuscation, code reuse, anti debugging, anti emulator and visualization and covert channel over network traffic. This taxonomy is well defined by Jonathan A.P Marpaung, et al [11], yet malware authors used them to protect their own properties.

Code obfuscation was originally founded for protecting intellectual property[12], but it aims to puzzle code's binary against merely static analysis and disassembling[13]. The first known obfuscation method used encryption in order to hide its content. It was called Cascade which is seen first 1986[14]. This simple architecture of the obfuscation is called packing[15]. It involves with two parts of binary which are slub part, in order to decipher and encipher.[11]. Cascade was using simple XOR encryption and that was increasing performance.

In early of the 1990s oligomorphism and polimorphism have started to show up[14]. The main idea behind them is basically transforming their slub part in each attempt of encryption process[13]. Today, there are two types of polymorphic approach to generate different variants of slub.[16]

- Rewriting the code each time from pseudo-code so it differs code synthetically, which is actually transformation based obfuscation.

- Self-cipher itself different, order of these ciphers and using different keys.

One of the other important milestone of polymorphic malware is Mutation Engine(MtE) is written by a Bulgarian virus Author, called The Dark Avanger. It was automated obfuscation tool which actually considered impossible in those times.[17]

There are also several methods to prevent unpacking process. These methods are collected carefully by Peter Ferrie [18]. These methods are especially obstacle for automated analysis.

Compare with polymorphic methods, metamorphic approach is more complicated. It is a transformation based method instead of encryption approach.[19] Fundamentally, it produces different codes which doing same blue printed semantic. That just mitigates the detection possibility because of lack of static code.

Network traffic, by malware generally Achilles heel to detect them because they are generally adequately unique traffics to be identified[11]. They usually cover their overt malicious traffic with covert channel methods.[20]

Code reuse attacks are strong attacks because they do not inject any code in them as obfuscation methods did. They aim to use legitimate software to evade them. There are three well known applied version which are return-into-libc, return oriented programming and Frankenstein.

Return into libc attacks were demonstrated by the solar designer in 1997 as a method of bypassing non executable stack to executable libc libraries[21]. Its object is to change the "ret" infrastructure argument to the known address, possibly libc library (stdio, system, etc). However, this attack is limited with libc libraries, which we improved with return oriented programming.

Return oriented programming is a more flexiable version of retur-into-libc attack, which is introduced by Shacham in 2007[22]. Return oriented programming purpose a programming language with small gadgets(instruction bound) which involve all ability of Turing's machine[23]. Frankenstein is one of the novel application of return oriented programming by Vishwath Mohan and Kevin W. Hamlen[24].

Anti debugging and anti emulator methods are really usual for today's malware. The survey of Chen Xu et al. showed us in 2008, a majority of 6900 on-the-air malware could evade their self with exhibiting benign behavior in sandboxes, debuggers, and virtual machines.[25]. VM and debuggers are most important element of dynamic analysis techniques in autonomous sector, because it must run the file just before it touch the working environment. Yet, it is not that knotty to determine whether working environment is virtual or not. Fuzzing cpu bechmarks and comparing results entropy is a good way to determine virtual machines.[26]

Rootkits are the piece of malicious code which aims to crack integrity of the system state. The idea of the remaining invisible to the system state is traced back to one of the oldest virus "Brain"[27]. It was changing the boot process and activate the virus during booting. "Tequila" and "1689" viruses followed "Brain" in 1991 and 1993[28]. There are NTRootkit and HackerDeffender rootkits today. The proper classification of the rootkit by Adnan Abdakka[29].

On the contrary with all studies presented above, we found several directly similar cases[9][10], which can empower our Harvard implementation solution. These studies include interpreters to obfuscate malware and they use these interpreters as virtual computer over a computer. We metion about it with details in Chapter 6, section flying over interpreter.

#### 2.2 Malware analysis methods

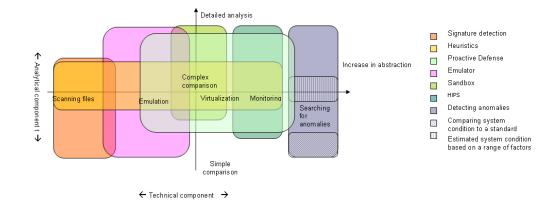

Malware analysis methods could be considered two dimensional plane which are "Anomaly" and "Signature based" detection techniques and "Statistic" and "Dynamic" and analysis methods. In addition to these two dimensional aspect, we could add also one more dimension with "Manual" and "Autonomous" methods, yet the figure 1 does not include this third dimension.

There are also several applied techniques, which combine terminology above. We tried to enumerate common techniques used by main frame detection algorithms below.

- N-gram It is a anomaly based heuristic detection method algorithm. It is a bit costly process and not practical for client side analysis. It could be fit for honey pot analysis [30] [31] [32]. They are capable against to zero time malwares and that could makes it futures malware detection system.

- Sequential approach on system and funtion call This approach is anomaly based dynamic analysis and observing and recording the flow graph of systems and function

Figure 1: Detection models [2]

calls and try to analysis anomaly behaviors.[33]

- Taint It is also called data flow analysis or data flow graph. It is basic tracking marked data values during execution.[34][34][35]

- **Control Flow Graph** They are one of the most important arm of commercial autonomous malware detection tools[36] [37] [38]. After the invention of the polymorphic and metamorphic, syntactic analysis could not bear with them. Then we moved to upper layer of information, semantic layer. Semantic can be representation of code flow, and the routes of the code are adequate to produce signature to identify malware. This methods are a member of static analysis and disassembling and source code analysis job.

- **Network Monitoring** Malware intention of the communication over network actually big clue to detect them. They generally use unique hostname, ip adress or specific protocol with particular way [11].

# **3** Background Studies

## 3.1 Caches

Solely, a cache is a small, fast, array of memory which is placed between lower level memory and higher one. It store a special block of information, in order to increase performance of computer systems. It is like a buffer area which has some logic to exploit locality features of programming logic. Today, with increasing of processing ability of computer systems, memory access is bottle neck.

The "cache" is originally french rooted with meaning "concealed place for storage."[5] We can move this definition basically to the computer science. The cache's design is definitely isolated from software layer, however; if you know your caches feature and how caches working you could program a lot more efficient codes easily.

#### 3.1.1 Motivation of Caches and Principle of Locality

The main motivation of caches is indisputably performance. As we mentioned, Performance of high-speed computers is usually limited by memory bandwidth and latency. In order to increase, and turn around that, we use an small array of memory which is located close to the processors. The location of chip is important and there are many design decision (e.g On chip, out of chip), but more crucial properties of caches are their designs (e.g. Naive Capacitor, SRAM, DRAM) and their logic complexity[39].Due to physical constrains, the size of the memory is limited which we can locate close to memory. On the other hand, these design choices are decisive factor about prices of memories. Because of all these reasons, Multi-Layer Memory Hierarchy with several caches between processor core and main memory is well-known option in order to improve performance. Nevertheless, In multilayer memory hierarchy, it is hard to know where the particular data reside in, and whether it is coherent or not. It also add many layer between memory and processor and in some cases it even decrease system performance, especially because of logical complexity of the line.

The idea all the caches logic depending on is Principle of Locality. Principle of locality is actually a concern of information theory[40]. It a conjecture of data distribution and processing order. The phenomenon assume that the the same data and related document will be accessed more frequently than other data[41]. Today, it is the one of the corner stone of computer science. It was first developed with Atlas System with purpose to develop virtual memory systems work well[42]. Then, it spread from search engines optimization to hardware caches.

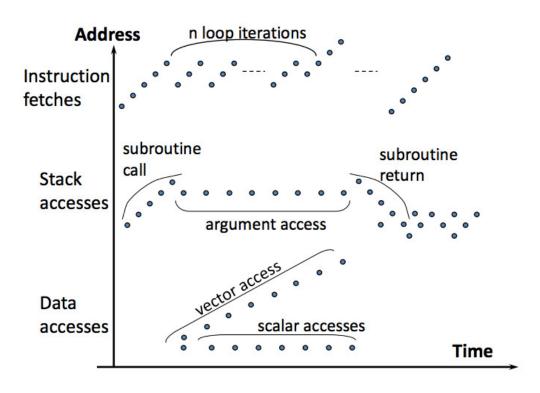

There are mainly two type of locality of reference:

**Spacial Locality** Spacial locality propose if there is a particular of memory which is accessed on memory, then it is more likely to accessing memory locations around of it in near feature. Especially arrays and instructions are exploiting this locality. Arrays, formed structure and instructions on memory are laid out lineally over memory. On figure 2, we can see spacial locality simply. For example, during instruction fetches part on the figure, n loop iterations accesses same memory loca-

Figure 2: Principle of Locality

[43]

tions for many times. There are also subclass of spacial localities like Branch Locality and Equidistant Locality. They are designed locality types of indeterministic feature of program structure. Branch prediction and Special compiler designs aims to exploits this kind of locality more efficiently.

**Temporal Locality** Temporal locality propose if there is a particular of memory location which is accessed recently, it will be accessed again more likely than any other location. Especially, variables, subroutines of stacks or other calls exploits this feature of locality. On figure 2, it is obviously seen that the values accessed once is possible to accessed again.

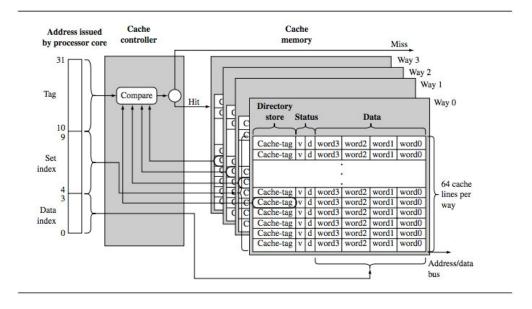

#### 3.1.2 The basic logic of caches

As we said in previous section, the basic logic behind caches is moving arranging caches with local data. In order to provide this feature as smooth as possible, we use a logic circuit called "Cache Controller". It does basic logic comparison and wiring the request and response into the right path. Thus, it intercept the write and read request from processor, replace its memory array with right scheduling method, and evict it safely and coherently. It processes with diving address of th request into three fields which are Index set field, tag field, and block field. In figure 3, these fields showed.

At the beginning of cache process after it divided address fields, It first request right cache line which is shown in figure 2. So if we have M byte memory and N byte cache line, we must have M/N = cacheline, then we can represent it with p when  $cacheline = 2^p$  Thus, cache controller just wire corresponding line with given set index.

Figure 3: 4 KB 4-way set associative cache with 256 cache lines [5]

In traditional cache convention, first field belongs to tag id. Tag id is determined depending on other field i.e. the remaining part after index field and block field calculated is tag id length. Tag id is using to verify the stored line is actually belongs to right location of memory. The cache controller has comparison circuit(XOR) and compare the requested address and the address which is in the pointed line by set index field. If they are matched with each other, then it check valid byte and hit or miss. There is a simple AND circuit between tag comparison.

Final field is called data index or block index field. It will point in the cache line the smallest addressable memory location. Therefore, when processor want to read a value, cache fetch the whole block, and that makes cache to exploit spacial locality linearly. However, it will limit the access speed remarkable, if we increase block size. The optimum block size is about 64 byte for many system. As we mention before each cache line includes cache-tag field, valid bit, dirty bit, and some coherency bits in some special systems. The length of the data index field is equal to r if wordsize =  $2^{r}$ .

When we increase the set index count it increase basically temporal locality, but not always. The cache conflict could happened when two memory location which uses same cache line could be used concurrently or twisted. Highly trashing can reduce cache performance. For this reason, associative caches are developed. Set associative caches are represented by their way number e.g 3 way associative caches or full associative caches, and there are group of cache arrays corresponding to the same set index. So that decrease the set index count but increase the performance during conflict miss in some cases. However, because of the complexity of the comparison circuit, it must be carefully chosen the number of ways. The associative caches are showed in figure 3.

The computer architecture we uses today actually first formulated by John Von Neumann [44]. On the first design of computer it was a single cycle instruction machine without any pipeline or superscalar idea. Then Hardward Mark I machine is designed with proposing two type of caches which are one for instruction, and one for data. Icache and Dcache are specified for their own purpose, because data and instruction on memories have different deterministic properties. Instruction are more tent to be linearly accessed by memory and they has branch locality which can be predict earlier. Icache also could be located more close to decode and fetch parts of processors when Dcache are instead closer to memory fetch parts. Yet, the most significant benefit of Harward design is concurrently usage both caches during pipelined architectures.

### 3.1.3 Allocation, Write and Replacement Policies

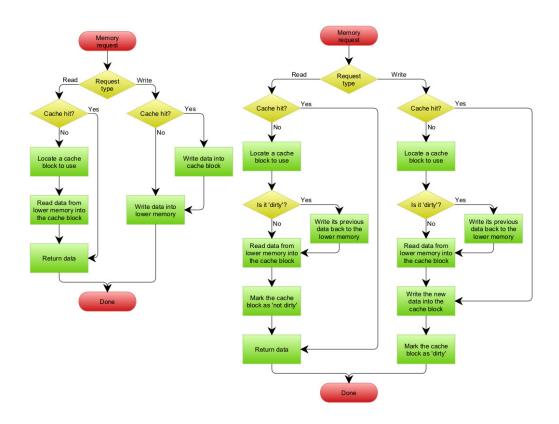

There are three policy type determine a cache behaviours. They are write policy, read policy and reallocate policy. System's performance, coherency, and designs are determined depending on these rules.

Figure 4: A. A Write-Through cache with No-Write Allocation B. A Write-Back cache with Write Allocation

[45]

#### Write Policies

**Write Through** When the cache controller designed based on writethrough policy, it write the values into the memory and caches simultaneously, when the write request is arrived from processors. It does not depend on writemiss or writehit. It will reduce write performance, because writing data on memory is a lot slower, but it stay coherent all the times. It is performance could be increased a bit with write buffer memories between memory and cache.

Write Back The systems with that policies does not have same values in memory and corresponding cache line, so the coherency between memory and caches are provided by a trashing algorithm. Cache line always store more recent data, but if there is more than one cache it is hard to decide which one is more valid or whether there is a valid coherent one. However, it effects performance quite remarkable (e.g. in ARM 15 cpu writing cycle to memory is around 200 cycle, but caches is about 4.) . The system with limited register numbers can overflow to the memory to store loop variables and that could increase write memory usage. WriteBack policy makes this kind of systems really effective. The dirty bit are stand for WriteBack policy. If you write some value on any cache line, dirty bit must be set for eviction. During trashing process, you must first move dirt block back to memory.

### **Replacement Policies**

- **Random** Random policies are designed to evict a random line in the associative caches. It is not really random on implementation, but enough random to work with it. It sounds to weak and primitive approach but actually it could be really effective on highly associative caches.

- Least Recently Used Least recently used replacement policies are actually implemented in two types. Fully most recently used and Not most recently used random. It is probably the most efficient algorithm to replace cache index sets, but it is really hard to implement on highly associative caches. You must record history of schedule and update it each attempt of access. It could be most effective and easy method on 2 way associative caches and it just need one bit to record who used last. It actually increase temporal locality, because it offers the most recently used one is more likely to be used again. The most recently used but random is a hybrid solution of least recently used and random policies. It just record who accessed last and replace one random set except most recently one.

- **First In First Out** It is also known Round robin. It is also mostly using with highly associative caches. In its implementation, it has one one tail pointer of stack and in each attempt of access it evict tail pointers set, and increment the the tail pointer to next set.

### **Allocation Policies**

- Write Allocate WriteAllocate policy is also known as ReadWriteAllocate policy. It refers that during write miss process, cache controller allocates the cache line with related address, as like as normal read miss process. It is mostly using with WriteBack policies, because it assume it is more likely to access same data which you write before.

- No-Write Allocate No WriteAllocate policy is also known ReadAllocate. It is an exotic implementation of caches. It is generally seen with WriteThough policy. This systems can be special to read privileged and they do not hope to read or write subsequent write(or even read after write.)

### 3.1.4 Miss Type and Advance Cache Optimization Methods

### Miss Type

- **Cold Misses** Cold misses are sometimes referred to as compulsory misses . If you never invoke related memory address and if you calling it first time, You will encounter with that misses. It is natural misses, and really hard to mitigate them. Spacial locality is the one of the method to avoid this misses. As we mention before, when we increase the size of block, it will increase spacial locality. Also before initializing memory, pre-fetching algorithms and branch prediction algorithms can be useful to eliminate this kind of misses. In addition to this, usage of large amount of caches will naturally reduce this misses, but it is side effect of it.

- **Conflict Misses** Those misses are the one we are able to avoid. Conflict happens in systems set with lower associativity esp. with direct map systems. To reduce this you should increase associativity. In full associative caches, it all conflict misses are avoided. The change of conflict miss is tagsize/memorysize.

- **Capacity Misses** They are also natural misses related with size of the caches. We can not store every information in memory into cache. Those misses are based by definition of caches. You can't solve it even with perfect replacement algorithm, but maybe you could decrease the rate of capacity miss with pre-fetching.

### **Advance Cache Optimization Methods**

- **Pipelined Caches** As we did in processors, we could divide cache organization in two separate stage which are decode and data. It will increase the writing efficiency because it will increase the bandwidth during subsequent requests. However the clock mechanism will decrease to hit time.

- **Write Buffers** Write buffers are small fully associated buffer memories between caches and memories. They effects cache performance because the time between writing values to memory from cache, cache memories must lock if we do not use cache memories. Thus, Cache memories store values to buffer buffer will responsible with writing it. Buffer size is important, when consecutive write operation requested. When buffers is full, it will makes cache lock to get empty.

- **Multilayer Cache** Multilayer caches are game changer optimization decisions, because when we have level 2 caches, then we could have faster level 1 caches, because it could be smaller and simpler. Namely, we are adding systems higher level caches, in order to, decrease lower level caches miss time penalty and increase the hit response time, but it will decrease lower level caches hit rate. Level 2 or higher caches could be also on-chip (i.e fast as possible) and SRAM, yet lower level caches must always be faster closer and simpler.

- **Victim Caches** Victim caches are really useful and simple idea for decreasing miss penalty time. It is a buffer memory, fully associative and mostly 4 to 16 cache line. It stores recently evicted lines in it. It means it increase the associativity of recently used lines on other small buffer with cheap and flexible design.

- **Hardware Prefetching** There are many theoretical pre-fetching method, but there are a few example implemented. The most well known is prefetch the most recently

values incremental block line. That targets to increase most recently used ones spacial locality. It is really efficient to applying it, because increasing block depth is expensive job for caches and increase hit time. If you implement one buffer memory, which prefetch next block of block you need, it automatically increase spacial locality. Also compiler based branch prediction methods are good example of instruction prefetching, however, generally, prefethers for instruction caches load all branches to decrease miss rate.

## 3.2 Cache Coherence and Consistency

Many modern computer systems with parallel processing ability have support of shared memory in hardware. Shared memory has lots of advantage over message based memory systems. Each processor could access same address space, read and write them simultaneously with using their own caches. This features has lots of benefit such as; low power consumption, higher performance and lower prices. However, without consistency between processors, parallel processing can not use many advantage of parallel programming. It could be also insecure to use a system without consistency between processors.

To provide better understanding of shared memory correctness, we defined it in two separate them in two definition, which are consistency and coherency. Consistency provide a definition of memory access rules and how they will act around computer system with store and load operations. When we compare it with coherency model, it must be more simple and easy to understand it. Therefore, it define a correct behaviours of the memory accesses of multiple threads by allowing or disallowing executions. On the other hand Coherency is a way of implementing a control protocol between memories and processors to support and provide consistency. Correct coherency provide a system which programmer or operator of the system can never determine behaviours (misbehaviours or correct behaviours) of caches[46].

As mentioned, Mention Consistency is try to define to correct shared memory behaviour between many processor in term of loads and stores. It does not have to concern specific hardware issues, such as hardware level pipelines, write buffers, caches, Outof-order processing schemes etc. However, in the market, there is no hardware provide consistency perfectly, because the reordering store and load operations is regular optimization techniques in out-of-order processors. In addition to out-of-order processors, the multi layer memory architecture makes consistency vague and subtle. Yet, most of the programmers assume memories are completely consistent. There are several level between inconsistent and sequentially consistent memory.

Memory Coherency (a.k.a. Cache Coherency) is actually to impose a protocol between caches to provide a specific consistency model on shared memory systems. Unlikely consistency, it also concern hardware uncertainness and subtle part such as write buffer, pre-fetcher. Typical consistency protocol has features which include instruction caches, multiple-level caches, virtual-physical address transaction, and coherent direct memory access. However, it is not enough to ensure consistency(depending on consistency model) by itself. It tries to makes caches synchronization in shared memory systems invisible from software developer. However there are timing techniques to analysis cache architecture and coherency model of system.

In figure 5 and 6, the consistency issues on multi layer memory systems. Assume there

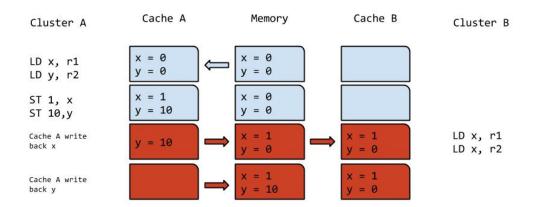

Figure 5: Write-back Policy Cache Memory Inconsistency

is two cluster which has ability to process values with given instruction codes. LD and ST instruction refer to memory load and store request. In figure 5, there is a system with two caches which belongs each cluster and one shared memory block. x and y is represents a particular memory address. Contrast with figure 6, figure 5 uses write-back policy. In step 1, cluster A loaded x and y to the processor(it could be also pre-fetcher who load them to the cache block). In second step, somehow clusters stored 1 in memory location x and 10 in memory location y. In this step, memory is not consistent with memory but it is not hazard because they are not shared with cluster B. In step 3, caches evicted the block which include address x and later address x and y were loaded into the cache B. After this moment, they will never share the values which other cluster is actually using. Y was 10 at the end in the memory but it can't be seen by cluster B, even if it try to read it a million times.

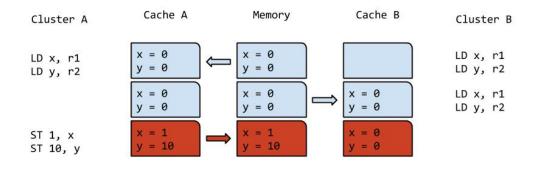

Figure 6: Write-through Policy Cache Memory Inconsistency

Write-through cache policy is intuitively perceived as solution of this problem, because it just write every values directly to the memory and it will be always synchronized with memory, yet it is not. In figure 6, write-through cache policy inconsistency showed. The problem with write-through policy, clusters use values which in their cache instead of memory, so even if memory is consistent with clusters, it is not consistent with each caches. In step 1 of figure 6, cluster A loaded x and y addresses into the its registers. Then, in step 2, cluster B loaded values of x and y addresses. In step 3, system got in inconsistent state, because cluster A write values through memory, but Cluster B uses the old values, and it will never reach never values, even if it try to load many times. For this reason, many of the large systems which has more than 64 core use this type of cache coherence.

In order to solve this problems, there are several coherency mechanisms and their protocols. Depending on the case and the number of cluster or processor in the system, system could use Snooping and Directory based mechanism. These each protocol have their own benefits and drawbacks. Snooping protocol is tent to use a lot of bandwidth, however, it is faster and more synchronous. Its logic is to broadcast each state to every node on the system. However, directory based mechanism work with request and response. There is interconnector to forward message to the right address and it makes directory based mechanism slower because of the increased latency, lighter because of the decreased bandwidth.

### 3.2.1 Snooping Coherence Protocols

Snooping coherence (a.k.a. Bus Sniffing) is a technique to have caches to watch other processors caches and provide consistency depending on specified protocol. It basically implemented with external port to the system bus. Therefore, it implemented over cache controller which has feature to watch bus. It makes cache controller bigger and waste more power, so lower layer caches could use less complex coherency protocols and vice versa. There are many snoopy cache coherency protocol also depending on consistency model, but we can categorize them in two class which are Write update and write invalidate.

In this both protocol, we try to get rid of stall data which are in different caches, but it is provided with different logics. Write-update protocol is a broadcast write protocol that in every write attempt, it will write the values into the corresponding cache block but also it broadcast the write message to the every caches on the connected bus. Thus, everyone on the bus which has the ability of interpreting the message of write-update protocol will update stall values with new ones.

Secondly, Write-invalidate is whenever you write, you invalidate other cache copies and reduce to possibility usage of stall data. Instead of sending whole data block, it just send the tag number and state of the tag. It could effectively be successful, if you have limited bandwidth and power source. Most processor with coherency is today using write-invalidate protocol. However, it is efficient if there a few writer and many reader clusters or processors. Comparing with write-update protocol, if there is many writer, it could be less efficient because of invalidation process validate-invalidateforward hops.[43]

There are many protocols for both write-invalidate and write-update to maintain coherence, such as MSI, MESI (aka Illinois), MOSI, MOESI, MESIF, write-once, and Synapse, Berkeley, Firefly and Dragon protocol. In this thesis, we will just focus on writeinvalidate protocols because of their popularity, but basic principles are same as each other.

### MSI - Basic

Basic write-invalidate snoopy cache control protocol is MSI (a.k.a Modified-Shared-Invalid protocol). In this model, each cache block has cache tag, and two status bit as same as standard caches, but instead of dirt and valid status bit, MSI cache line has state bits to

| •        | Clean/Dirtiy | Write? | Unique? | Silent Transition to |

|----------|--------------|--------|---------|----------------------|

| Invalid  | Clean        | No     | No      | -                    |

| Shared   | Clean        | No     | No      | Invalid State        |

| Modified | Dirty        | Yes    | Yes     | -                    |

Table 1: MSI states' properties

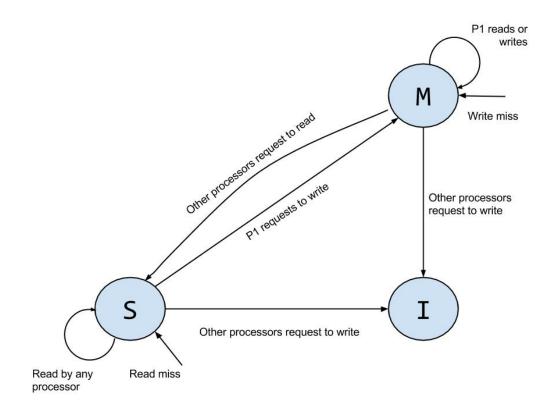

refer in which state it is. MSI has three state in state machine and they are "Modified", "Shared", "Invalid". two bits can represent four state, so definitely represent three state. The main idea behind this protocol is that one writer and many reader states provide always consistent memory sharing. Therefore, every cache in the system has different responsibilities when they read or write.

- **Invalid** Invalid state is exactly same state with standard caches' invalid state. When cache need to access a invalid block, it must act as cache miss, and be fetched this block again.

- **Shared** When there is no writer processor on this line, and if a processor request this line with purpose of read it, it will be in shared state. It is read-only cache block, and processors are not allowed write without transforming state. The processor also can evict it without writing back to the upper layer memory, because that is for sure, it is clean block.

- **Modified** It is modified and also modifiable cache block. In a memory coherent system there can be at most one modified cache and all other cache must be invalidated. It is responsible with writing back cache to the upper layer memory.

In figure 7, MSI protocol's state diagram is showed. Cache memory launch with invalid cache block, and when a read miss is comprised, cache controller will request memory block from memory. Then, the snooping control bus will broadcast the request of read. If there is a modified copy on the bus, it will abort request of memory block from memory. It will evict its line to memory, and change its state to shared state. Then, memory responds source of the request. After the fetching cache block to the source cache it, it sets the state as shared state. If there is a shared stated copies in the system, It does not matter who responds the request. In any case, It will fetch the memory block, and sets the state bits to shared.

When write miss is compromised in invalid state or shared, It will fetch the data as same as read miss cases, but the difference is it will invalidate other case's corresponding block which are shared or modified. Modified stated block must evict blocks properly. At the end, source cache block fetches the block.

Write hit can be compromise in modified state, and read hit can be compromise in shared state.

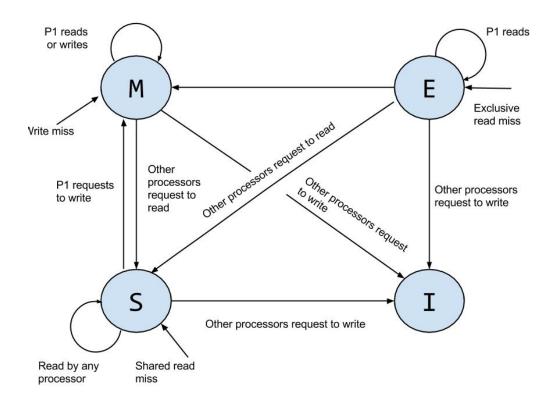

#### **MESI - Exclusive**

The MESI protocol (a.k.a Illinois protocol due to its development at the University of Illinois at Urbana-Champaign) is a widely used cache coherency protocol[47]. The idea behind the MESI is to use forth state we can use with 2 bits. In order to increase efficiency *exclusive* state is developed by JH. Patel et. al. in 1984[47]. As showed in MSI protocol, there is modified, shared and invalid states but also we have exclusive state.

Figure 7: MSI State Diagram for processor P1

| •         | Clean/Dirtiy | Write? | Unique? | Silent Transition to             |

|-----------|--------------|--------|---------|----------------------------------|

| Invalid   | Clean        | No     | No      | -                                |

| Shared    | Clean        | No     | No      | Invalid State                    |

| Excursive | Clean        | No     | Yes     | Shared Modified Exclusive States |

| Modified  | Dirty        | Yes    | Yes     | -                                |

Table 2: MESI states' properties

This exclusive states also known unmodified exclusive state, if we refer modified state as modified exclusive. This is very similar to the shared state in MSI, and in fact, Shared state is split in two different states. That is because of reducing the communication on the bus and increasing efficiency. In this case, there is exclusive cache blocks which are in read mode and they are unique i.e there is no other cache controller on the system has this cache block.

**Exclusive** The cache line is only present in current cache memory, and it has not modified yet. It is not a state to provide coherency, but it is state for increasing efficiency of bus bandwidth usage. When a cache line in exclusive state the cache controller can decide the transaction of the line without communicating with other caches. When a cache is requested with load operation, it is loaded in exclusive state, if there is no other cache controller has the cache block.

In figure 8, state transactions are showed. Bus usage is bottle neck, low performance behavior in cache coherency. Silent state transactions are transactions in cache controller without communicating with other caches. For example, there is no need to broadcast

Figure 8: MESI State Diagram for processor P1

and occupy bus for invalidating shared state in MSI protocol. If a cache controller is in shared state, the other cache controller can be shared or invalidate in MSI, so there is no dependency in the system transaction from shared to invalidate. Exclusive state is to exploit the salient transactions. When a load request arrive to cache controller from a processor, it request the line from upper level memory controller and other child caches controller. If any child controller send a shared state broadcast message, it load it in shared state. If there is a exclusive cache controller on the bus, it will degrade its state to shared and broadcast it. If there is no other shared state on the bus. It load the cache line in excluded state. Then, in case of store operation from processor, it will transact its state from exclusive to modified. It does not need to broadcast it, because we know it is unique in system. Contrast with modified state, due to be cleanness of the line, it does not need to evict line to upper memory, it can just invalidate it silently. The weakness of this protocol comparing with MSI, if there is many processor with the corresponding cache line, when it count the copies to test uniqueness, it occupy shared bus more in some cases. If there is n cache controller with corresponding cache line, it will send n broadcast message with this message, however, instead of sending whole line to upper memory it is mostly efficient to send this message.

#### **MOESI - Owned Exclusive**

Such processor producers AMD Opteron and Arm Cortex A are using MOESI protocol for cache sharing. In addition to the four states in MESI, a fifth state "Owned" appears here representing data that is both modified and shared. Using MOESI, instead of writing modified data back to main memory, it directly forward the dirty value from cache to

Figure 9: MOESI State Diagram for processor P1

| •              | Clean/Dirtiy    | Write? | Unique? | Silent Transition to             |  |  |  |

|----------------|-----------------|--------|---------|----------------------------------|--|--|--|

| Invalid        | Clean           | No     | No      | -                                |  |  |  |

| Shared         | Either No       |        | No      | Invalid State                    |  |  |  |

| Excursive      | Excursive Clean |        | Yes     | Shared Modified Exclusive States |  |  |  |

| Owned          | ed Dirty No Yes |        | Yes     | -                                |  |  |  |

| Modified Dirty |                 | Yes    | Yes     | Owned                            |  |  |  |

Table 3: MEOSI states' properties

cache before being shared, which could save bandwidth and gain much faster access to users to the cache.

**Owned** Owned state is a state if and only if a cache line can transact in it, when a read request message snooped from another processors when the cache line is in modified state. It allows dirty line sharing between caches, and reduce the latency which is arisen due to the communication between memories and processors. The line is read only by all processors, when it is owned state.

In figure 9, state transactions of MOESI protocol are showed. The relationships of states are almost same with MESI, but there is a state which supplants upper level memory with its own cache line. Hence, it is responsible with evicting lines and cleaning state. The cache line may be changed to the Modified state after invalidating all shared copies, or changed to the Shared state by writing the modifications back to main memory. If could increase efficiency sharply, if the line between upper memory and itself is long and bandwidth is limited. Mostly the L1 and L2 caches are located on-the-chip,

and memory are located somewhere outside, the buses' bandwidth between in side and outside of chips are game changer. It can be efficient to use a chip as a forwarder in many system. However, in the MOESI protocol, it is not possible to forward the cache line which is not dirty but present on the chip. If there is a shared cache line in a cache, and if any other cache controller request to load the same cache line, it fetches it from memory.

### 3.3 Inter-connector Design

Figure 10: Primitive Multi-Drop Memory Bus [43]

Computer Bus which is the primitive version of the inter-connection network was designed to transfers data between components inside a computer, or between computers. They are defined to include all computer hardware components and software, included with communication protocols, in order to communicate devices. Devices is generally called as node or end node in taxonomy. However, this definition is quite broad and it covers from today's Internet network to cloud computing network and evolved in many aspect to different direction.

In figure 10, There is an early multi-drop bus example. Multi-drop bus term is used for a bus line with many element on a line (not a ring), and there is an arbitration mechanism, so it is normal computer buses which is used in interconnection taxonomy. The multi-drop buses includes 5 separated wires which is distinguished by their purpose. Arbitration line decide actually how has right to speak, request. There is a logic devices to determine the arbitration and it is one of the most crucial research area in computer architecture and especially interconnector design[39]. Control wire is actually determine the purpose of the node. Generally, they are store and load operations. The address wire determine the requested address from corresponding place, in this case there is no cache controller so directly memory. Data wire carries the data which is stored or load, so the communication is synchronous, with consecutively request and reply. Lastly, clock wire provides a fixed, constant frequency to carry values.[39]

On recent systems the communication mechanism between nodes are quite more complicated comparing with given primitive example. The pace in the development on parallel systems makes correlation and communication between notes chaotic. Systems comprise with many nodes and requires high bandwidths to overcome and increase their bottleneck. Intercommunication is still the slowest part of mainframe and personal computers. On the other hand, with multi layer memory aspect, communication between nodes and parallel computing gets more and more complicated. It makes every cache controllers a member of interconnector and perhaps more. Today, there are some coherent interconnector which are also responsible with traffic management (i.e. QoS), barriers between devices and memories, and coherency[48].

Figure 11: An example of interconnector message anatomy

There are two main category of computer interconnectors which are host based On-Chip and System/Storage area network and remote over LAN and WAN networks interconnectors. On-Chip networks purpose to mitigate the on-flight latency and chip-crossing wire delay problems related with increased technology scaling and transistor integration. Nevertheless, there is not enough space in a single chip to fill many cores. It is a good design for interconnecting ALU, registers caches, compute tiles, and perhaps several cores and memory. System/Storage area networks are the most used interconnection systems between multi-processors, multi-computer, multi-thread systems and memory system interconnection between this cores. Because of physically constrains such as distance and density, it is usual the interconnector between systems and their I/O extensions (e.g DMA chips). LAN and WAN based systems are actually designed to connect enormous number of node together. This kind of networks distributed several locations and interconnecting PCs cluster of computers. Cloud computing is actually one of the good example to show the ability of this species. On of the other advantage of remote interconnectors is that they are generally build on well-known protocols which are tested and acknowledged protocols e.g. Ethernet, GSM, IP, TCP, UDP. All routing issues are tested for many years and solved properly.[39].

Modern interconnections with advance switching and routing mechanism are using message protocols. In figure 11, an example of simple interconnector message anatomy is shown. Alternatively, the bus anatomy we mention above, the message based protocols are packetized. However, this packetizing process has some overhead as latency[43]. Message anatomy of interconnectors comprises several layers[4].

Message The message is the unit of information which must be transmitted with a pro-

pose. If it is about cache coherency, It could be whole line of the cache to provide coherency.

- **Packet** Packets are the fixed maximum sized smallest unit of information which include routing information in its header section. It can also include sequence number for flow control protocol. Its size is depending on the arbitration mechanism on the router or switches. It comprises with data flits which actually part of information in message.

- **Flit** The small unit of link layer is called flit. Flits size are depending on the switching algorithms. In circuit switching flit size are whole packed. They are typically 4 byte to 16 byte.

- **Phit** It is the unit of the physical layer in the interconnectors design. Its size is depending on the clock cycle of the interconnector. On the primitive bus example, the clock mechanism determine the phit size when it tick. They are around 8 bit to 32 bit.

In order to characterize interconnector device we will use several feature of networks which are switching mechanism, switching mechanism, routing algorithms, topology, and flow control of networks. These feature are determine depending on application domain and defuse all character of network. Across the designs, performance with latency and bandwidth parameters and queuing theory is the valuable analysis tools to define network and its classification[39].

### 3.3.1 Topology

Topology is a mathematical study of shapes and the points and their relationships in the environment. Network topology is actually determining the path and shape of the network. The shapes which topology concerns depending on the dimension they are build on. Electronic circuit are generally build on two or tree dimensional space. The wire and nodes are the basic element of interconnector topologies, but also router is the switch element which can decide the path. The node could be grouped to regulate communication and bandwidth e.g. there could be two group as memories and processors. Also, there are two main type of network topologies, that are In-directly connected distributed and directly connected centralized. The root of "central" word in telecommunication comes from this switches, but they are too vast topics to discuss in this thesis. The basic idea of the centralizing topology is to use a central switching fabric between nodes. The switching fabrics is actually external subsystem or combination of systems, e.g omega and crossbar network topologies[4].

The general assumption of topologies is wire are faster then logical routers and transactions.-Today, there is in chip transaction devices which are faster then wires[39].-In order to design efficient topology, optimum cost and measure its quality, we have several parameters, which are diameter of tomography, routing distance, minimum bisection bandwidth and degree of a node.

Routing Distance It is any given two points distance by mean of number of links or hops

**Diameter** It is maximum routing distance between any two point of the network. In figure 12 and example A, it is from the first node of the bus to last node, so it is 5. It could be sometimes not that obvious, but it is the most far two nodes' distances.

Figure 12: A) Bus topology example B) Ring topology example

- **Average Distance** Average Distance is TotalDistance/NumberofNodes. It is one of the value which using in average latency calculation. Generally performance values are compared with each other by average latency.

- **Minimum Bisection Bandwidth** If network is segmented in two equal part, and if the bandwidth of these two segments is as minimum as possible, it is called minimum bisection bandwidth. Typically, this bisection will be the most occupied lines, and the bandwidth of bisection will effect total performance sharply. To embody it better, it is like a bridge between two island. Most of the traffic caused by the occupation on the bridge in ordinary traffic networks. The inner island bandwidth is futile to effect overall traffic.

- **Degree of a Node** It is the properties of each node to imply how many nodes it is directly connected to. The node with the highest degree is applied as degree of the network.

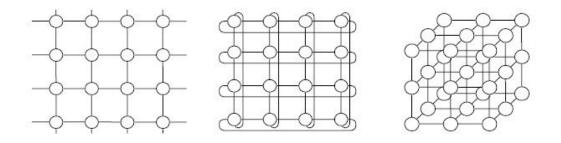

Figure 13: A) Mesh topology example B) Torus topology example C) 3D mesh topology example[3]

The number of topologies designed in literature can be too many to count, but the idea behind them has always same logic. Topology directly effect performance, but also greatly impact the cost of systems. Physical constrains such as chips' pin-out, light speed, dimension count on the board and etc. determine topologies properties. Generally chips are reducing their inner bandwidth, when they are communicating with out side of chip, due to the restriction of building pins[39].

### 3.3.2 Topologies

- **Buses and Rings** Buses and rings are the first dimensional primitive and basic type of interconnector topologies. They are both directly connected nodes in in sequence as shown in figure 12, but rings are end around buses. Namely, ring topology aims to reduce the longest link which is actually diameter of the network. If N is the total number of node, node i is directly connected to node i + 1, and node i 1 except element 0 and element N 1 in buses, and in rings, every node i is directly connected to every node i+1 and i-1 in mod N. In bus topology, diameter is N-1, in ring topology, diameter is (N-1)/2. In segmented and pipelined networks, rings are also increasing bandwidth, because when 2 closer nodes communicate with each other, other nodes can connect over all around the line. For example, When 4 and 5 is communicating, in buses, there is no way from 1, to 6 but in rings there is another links goes around the network to connect 6 and 1, so bisection bandwidth is 2 in rings and 1 in buses Rings looks more efficient and logical to use it, however, in practice it could be hard to implement because of the physical constraints, but they are vast topics to discuss in this section.

- **Two Dimensional Networks: Meshes, Tori** Meshes and Tori are the idealized structure of two dimensional interconnectors, because every best two dimensional forms to connect  $m^2$  nodes. while mesh topology is derivative of bus topology, tori are derivative of rings-as showed in figure 13, so terminologies uses meshes end around term instead of torus. The bisection bandwidths are  $2\sqrt{N}$  for meshes and  $4\sqrt{N}$  for tori. The diameters are  $2\sqrt{N} 2$  for meshes and  $\sqrt{N} 1$ . Degree of the network is 4(5 in some terminologies), and every nodes degree is same in the torus network which can be seen in figure 13.[43]

- **Multiple Dimensional Networks** They are excessive versions of the mesh and torus networks which are influenced by the chips packaging technology. Multi dimensional system over 2D space is still good to obtain higher bandwidth and balance the traffic but more complicated example are seen with Storage/System, local and wide area networks. Because they are instead of chips real 3D systems and surely, 3D networks works better in 3D systems. On an N dimensional system, if you want to build more dimensional systems such as N + 1 or N + i, it increase the wire length exponentiation when you increase i. Wire length is related with flight time of the data, and it effects directly bandwidth. One of the idealized for of the multi dimensional networks are cubes. Cubes are the three dimensional topologies which every nodes are 3Th degree and all nodes are equally close to each other. In figure 13, there is an example of three dimension mesh. CM1 and Thinking machine is the examples of their practice today in market. They actually connects thousands of computers in hyper cube topologies. They connects the mesh dimensions, which are two dimensional with each others.

- **Fully Connected Star** Fully connected stars are directly connected star topologies which actually known in some terminologies as mesh networks. This topology is the best possible topology which have been designed so far, because every nodes are directly connected with each other within 1 routing distance. If there is N number of node that means the bisection bandwidth is exactly 1024, because each node has for

every other nodes another links with an other bandwidth, it makes it bottleneckless topology.

Omega and Fat Tree Omega and fat tree topologies are examples of centralized systems. They are improvements of crossbar switches. Crossbar switches are expensive designs because its complexity increase quadratically with the number of ports. Instead of the increasing the design complexity, it increase the stages thus, permutation[39]. With N number of node and with kxk switches, log<sub>k</sub>N stages each of which contains N/k is required in omega network. However, the reduction of the implementation cost has some negative sides, which are lower bandwidth, dropped packet, more latency.

### 3.3.3 Switching