# Security Properties of a Class of True Random Number Generators in Programmable Logic

Knut Wold

Thesis submitted to Gjøvik University College for the degree of Doctor of Philosophy in Information Security

2011

Security Properties of a Class of True Random Number Generators in Programmable Logic

Faculty of Computer Science and Media Technology Gjøvik University College

Security Properties of a Class of True Random Number Generators in Programmable Logic / Knut Wold Doctoral Dissertations at Gjøvik University College 1–2011 ISBN: 978-82-91313-71-9 ISSN: 1893-1227 To my wife Mari Anne and my children Ole Petter and Per Kristian

### **Declaration of Authorship**

I, Knut Wold, hereby declare that this thesis and the work presented in it is entirely my own. Where I have consulted the work of others, this is always clearly stated.

Signed:

(Knut Wold)

Date:

## Summary

Nowadays, digital equipment such as computers with Internet and cellular phones are commonly used for communication. The users want secure communications, meaning that confidentiality, integrity and authenticity are maintained throughout the session. Confidentiality means that only the intended recipient has access to the transmitted information, integrity ensures that the information is protected against modifications, and finally, authenticity guarantees the identities of the communicating parties. All these security aspects can be achieved using cryptographic techniques and protocols. In a cryptographic system where the algorithm is public, the entire security depends on the used cryptographic key. These keys are generated by using pseudo random number generators (PRNGs) using an algorithm combined with a seed or true random number generators (TRNGs) based on a physical property generating random noise. A TRNG is preferred if the cryptographic system requires a high level of security. Traditionally, a cryptographic system is implemented in an application specific integrated circuit (ASIC), but during the recent years a field programmable gate array (FPGA) has become an attractive alternative. The advantages of using an FPGA compared to an ASIC are the flexibility regarding update of the configuration for correcting errors or adding new functionality, an easier and faster development process and availability of FPGA devices on short notice from the vendors. On the other hand, the flexibility of an FPGA with the possibility of changing the configuration makes it more vulnerable against attacks. The challenge is to design a TRNG in an FPGA with good statistical properties, a reasonable high bit rate and robustness against attacks.

In this thesis, a practical and functional enhancement of a class of TRNGs based on several equal length oscillator rings is proposed. The generation of true randomness is based on the uncertainty of where in time a transition, i.e. a change from logical zero to logical one or vice versa, of the oscillator ring outputs occur due to the presence of jitter. The enhanced TRNG was implemented in several FPGA families and the security properties were examined. The statistical properties were investigated by running the statistical test suites NIST SP 800-22 and DIEHARD, and the test results showed that this TRNG passes these tests. Due to the proposed enhancement the number of oscillator rings could be reduced and a post-processor was not needed in order to pass the statistical tests. Restart experiments from an identical reset state showed that this TRNG generates true randomness and not only pseudo randomness. A detailed spectral analysis was performed on each of the building blocks of this TRNG by investigating the frequency spectrum both in theory and by simulations showing that it approaches the frequency spectrum of an ideal random number generator. The purpose was also to optimize the design parameters in order to achieve a high bit rate. Experiments were performed and a bit rate of 300Mbit/s was achieved while generating random bits with good statistical properties. Even though the statistical properties were found to be good, understanding the noise source and quantifying the amount of entropy are important in the evaluation of an TRNG. A model based on the accumulation of jitter was proposed and simulations were carried out showing the influence of the different design parameters and technology properties on the number of hits close to a transition region defined by the standard deviation of the accumulated jitter. The simulations show that the proposed TRNG with high probability generates bits with high entropy at every sampling point. An investigation of the properties of oscillator rings implemented in three different FPGAs was performed in order to examine the interaction

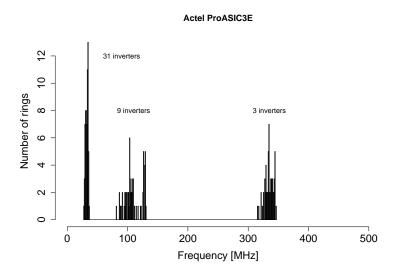

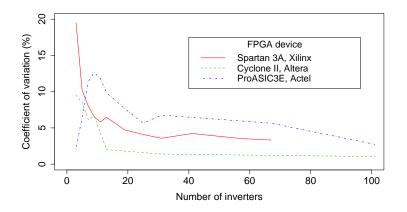

between rings located close to each other, the correlation and dependency between the rings and also the dispersion of the oscillator ring frequencies. The investigation revealed that there is interaction between some of the rings and a few of them could be regarded as correlated due to almost identical ring frequencies. The experiments showed that there are differences between the examined SRAM based FPGAs compared to a flash FPGA regarding the dispersion of the ring frequencies. The robustness of the TRNG was examined by employing an attack by superimposing a noise signal onto the power supply voltage to the FPGA. Four different TRNG designs were investigated and the two designs based on several oscillator rings were not influenced by this attack while two other reference TRNG designs were. Simulations were performed in order to explain the observed behavior on the TRNGs consisting of oscillator rings. A more exact power model of a microcontroller bus based on the influence of crosstalk due to capacitive couplings between the bus lines was proposed in order to more precisely determine the energy consumption. This model could for instance be used in a side-channel attack determining the encryption key with reduced computational effort.

A TRNG based on the proposed design was implemented in a real life cryptographic system with good results showing that this TRNG is both practical and secure. In addition, this TRNG design is easy to implement in programmable logic, the placement of the inverters inside the FPGA is not critical, it is robust against temperature and power supply variations and not influenced by effects related to aging. All this makes a TRNG based on XOR of several sampled oscillator rings a suitable component in a cryptographic system.

## Acknowledgments

The research resulting in this thesis has been carried out at Norwegian Information Security laboratory (NISlab) at Gjøvik University College (GUC) in Norway.

I wish to thank my main supervisors Chik How Tan, who unfortunately left GUC before the work was finished, and Slobodan Petrović for their contributions and constructive feedback. They have both been a source of inspiration to me and they have pushed me forward in my research. I am also very thankful to my co-supervisor and former work colleague Leif Nilsen for his useful comments on my papers and for his support when I started this project.

I am very grateful for the support from Markus Dichtl in Siemens AG in Munich in Germany. He was a very useful discussion partner on difficult technical issues and he guided me in the right direction in the process of understanding the TRNG design.

I want to thank my father Arne Wold for technical assistance especially regarding digital signal processing and Matlab, Geir Olav Dyrkolbotn for great co-operation and for assistance with measuring of high speed signals, Frode Gilberg for useful and most needed assistance in using C# and Nils Kalstad Svendsen for useful help and tips and for squash practice. I will also like to thank the rest of my colleagues at GUC for making this a pleasant and inspiring place to work in.

Finally, I want to thank my wife Mari Anne and my two boys Ole Petter and Per Kristian for inspiration and encouragement in troublesome periods when the progress of the research was not as good as expected.

# Contents

| 1 | Introduction                                                                             | 1               |

|---|------------------------------------------------------------------------------------------|-----------------|

|   | 1.1 Research Questions                                                                   | 2               |

|   | 1.2 Structure of the Dissertation                                                        | 4               |

| 2 | Background                                                                               | 5               |

|   | 2.1 RNG Properties                                                                       | 6               |

|   | 2.2 Programmable Devices                                                                 | 7               |

|   | 2.3 Noise Sources in FPGA                                                                | 9               |

|   | 2.4 TRNG Implementations in FPGA                                                         | 9               |

|   |                                                                                          | 14              |

|   | 2.6 Testing of Randomness                                                                | 15              |

|   | 2.7 Security                                                                             | 16              |

|   |                                                                                          | 17              |

|   | 2.9 Side-Channel Attacks                                                                 | 17              |

|   |                                                                                          |                 |

| 3 | Contributions and Summary                                                                | 19              |

|   | 3.1 Paper Contributions                                                                  |                 |

|   | 3.2 Summary of Thesis Contributions                                                      |                 |

|   | 3.3 Future Work                                                                          |                 |

|   | 3.4 Bibliography                                                                         | 23              |

| 4 | Analysis and Enhancement of RNG in FPGA Based on Oscillator Rings                        | 29              |

|   | 4.1 Introduction                                                                         | 29              |

|   | 4.2 Related Work                                                                         |                 |

|   | 4.3 TRNG Based on Oscillator Rings                                                       |                 |

|   |                                                                                          |                 |

|   | 4.5 Bias in TRNG                                                                         |                 |

|   | 4.6 Distribution of Ring Frequencies                                                     |                 |

|   | 4.7 TRNG Implementation                                                                  |                 |

|   | 4.8 Restart Experiment                                                                   |                 |

|   | 4.9 Conclusion                                                                           |                 |

|   | 4.10 Bibliography                                                                        |                 |

|   | 8 I J                                                                                    |                 |

| 5 | Optimizing Speed of a TRNG in FPGA by Spectral Analysis                                  | 45              |

|   | 5.1 Introduction                                                                         |                 |

|   | 5.2 Properties of a Digital Random Signal                                                |                 |

|   | 5.3 Spectral Analysis of the TRNG                                                        |                 |

|   | 5.4 TRNG Design Parameters                                                               | 52              |

|   | 5.5 Experiment                                                                           | 53              |

|   | 5.6 Conclusion                                                                           | 54              |

|   | 5.7 Bibliography                                                                         | 55              |

| ~ | Palmatrana of TRNC and not Attacks on ERCA Complex Values                                |                 |

| 6 | Robustness of TRNG against Attacks on FPGA Supply Voltage         6.1       Introduction | <b>57</b><br>57 |

|   | 0.1 Introduction                                                                         | 57              |

| 7 | 6.3<br>6.4<br>6.5<br>6.6<br>6.7<br><b>Secu</b><br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6 | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58<br>58<br>62<br>66<br>67<br>68<br>71<br>72<br>72<br>73<br>74<br>75<br>76 |

|---|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 8 | 8.1<br>8.2<br>8.3<br>8.4                                                                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77<br>77<br>78<br>80<br>83<br>84                                           |

| 9 | 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6                                                   | rity Properties of Oscillator Rings in TRNGs Introduction Interaction between Oscillator Rings Variation in Oscillator Ring Frequencies Correlation between Oscillator Rings Discussion Conclusion Interaction Conclusion Interaction Inte | 87<br>87<br>88<br>92<br>96<br>98<br>99                                     |

| A | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7<br>A.8                                     | ysis and Enhancement of RNG in FPGA Based on Oscillator Rings1Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 102<br>102<br>103<br>105<br>106<br>108                                     |

| B | B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6<br>B.7                                            | Introduction       1         Layout Dependent Phenomena       1         Theoretical Considerations       1         Security Implications       1         Simulations       1         Conclusion       1         Bibliography       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 115<br>116<br>118<br>120<br>123                                            |

| C |                                                                                          | Probabilistic Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                          |

| C.2 Bibliography |     |

|------------------|-----|

| Nomenclature     | 129 |

| Index            | 131 |

# List of Figures

| 1.1<br>1.2                                                          | Model of a symmetric cryptographic system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10 | Model of a physical TRNG.Principle of TRNG by Fisher et al.Principle of TRNG by Tkacik.Principle of TRNG by Epstein et al.Principle of TRNG by Kohlbrenner et al.Principle of TRNG by Golić.Principle of TRNG by Sunar et al.Principle of TRNG by Sunar et al.Principle of TRNG by Vasyltsov et al.Principle of TRNG by Danger et al.Post-processor based on an LFSR.                                                                                                                                                              | 10<br>10<br>11<br>11<br>12<br>12<br>13<br>13                   |

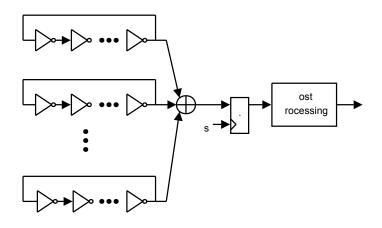

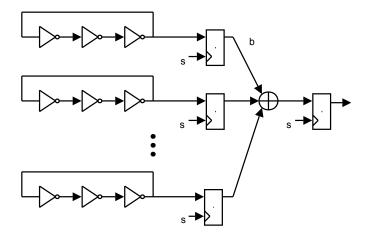

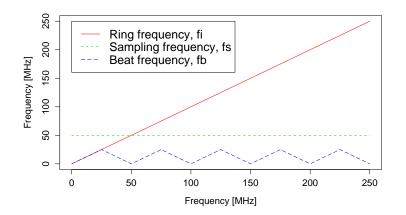

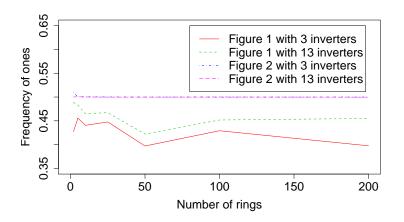

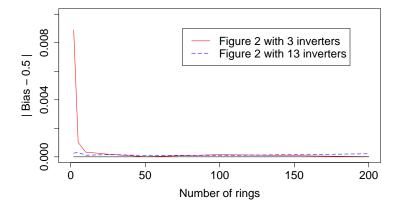

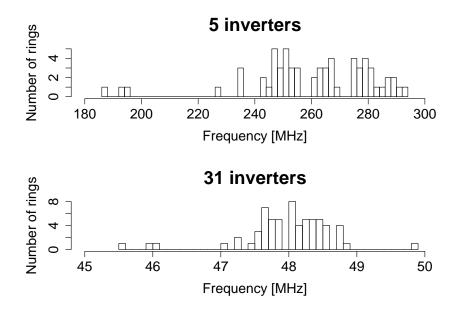

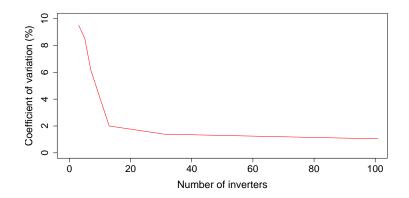

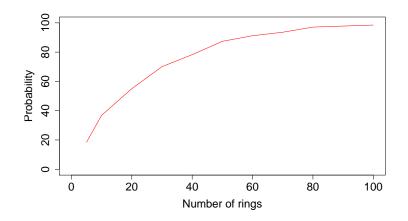

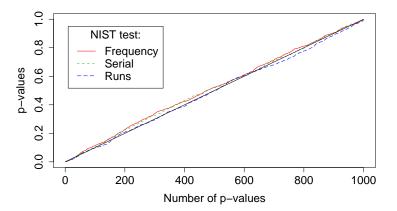

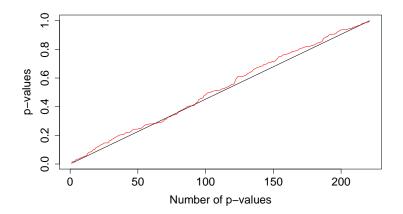

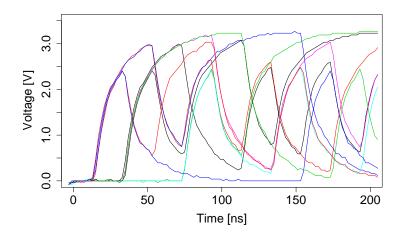

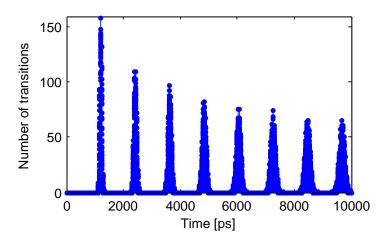

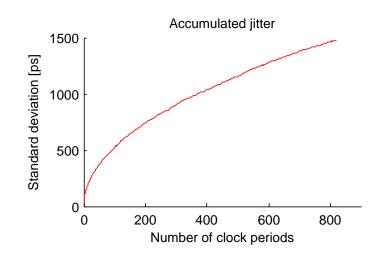

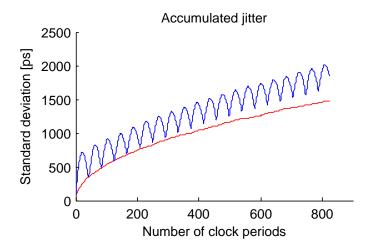

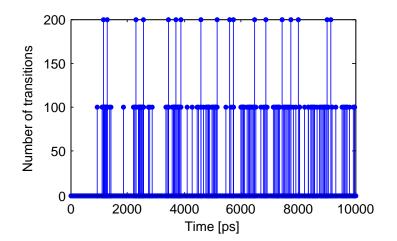

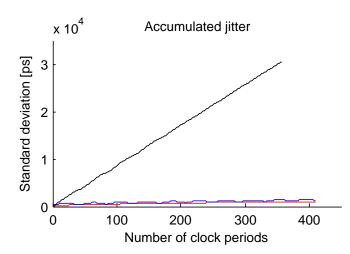

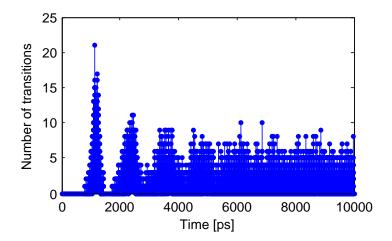

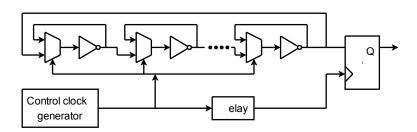

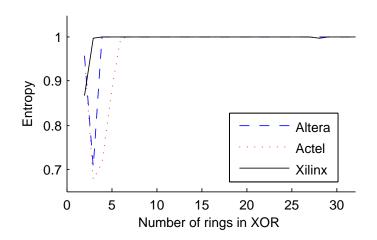

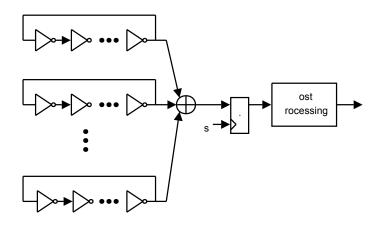

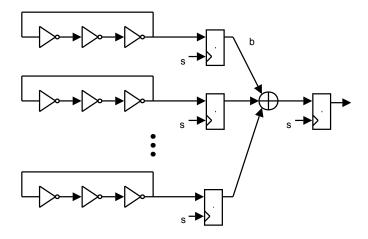

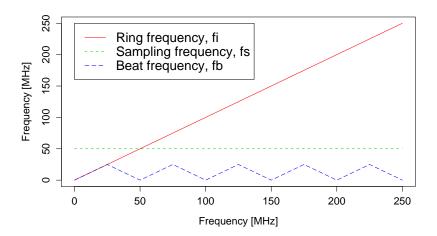

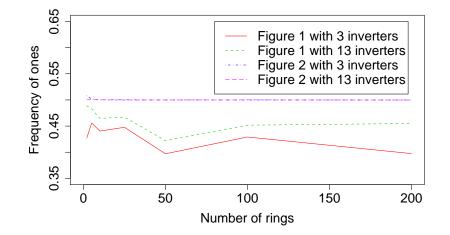

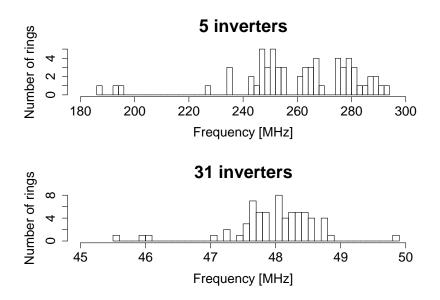

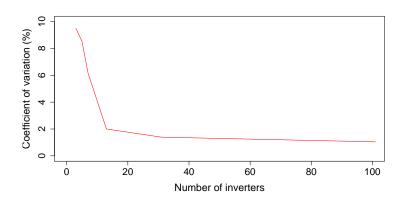

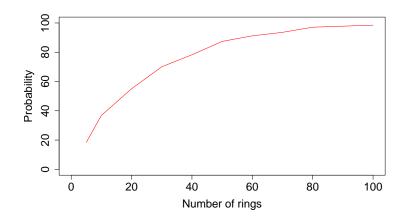

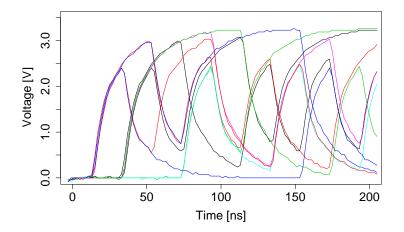

| 4.11<br>4.12                                                        | TRNG based on oscillator rings.Our proposalBeat frequencyBias of the TRNG on Figure 4.1 and 4.2Bias of the TRNG on Figure 4.1 and 4.2 $ Bias - \frac{1}{2} $ of the TRNG on Figure 4.2Histogram of ring frequenciesDispersion of frequenciesSimulated probability of hitting a transition regionSelected results from the NIST suiteResults from DIEHARD10 restarts with 25 ringsStandard deviation of 1000 traces, sampling frequency 10MHz and 25 ringsStandard deviation of 1000 traces, sampling frequency 100MHz and 25 rings | 32<br>33<br>34<br>35<br>35<br>36<br>37<br>38<br>38<br>40<br>40 |

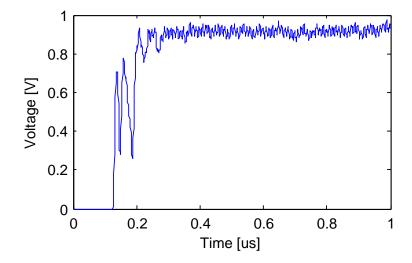

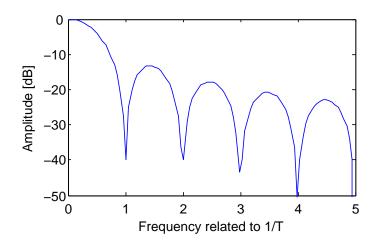

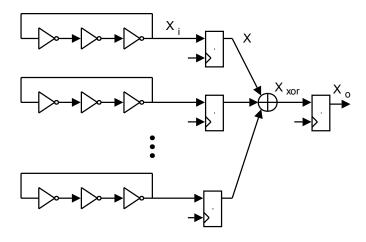

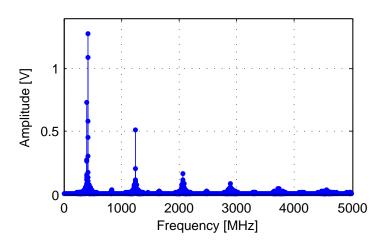

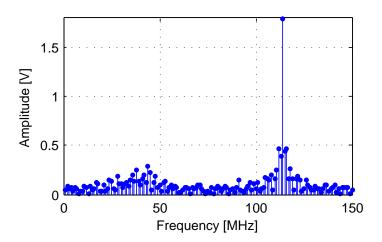

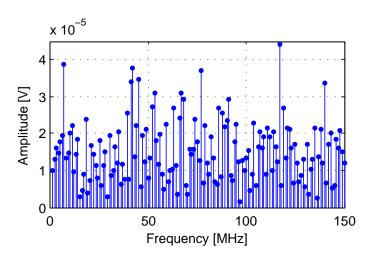

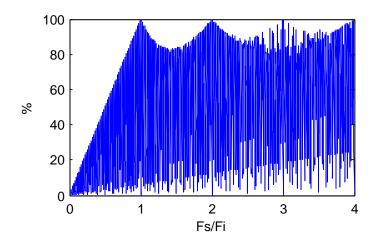

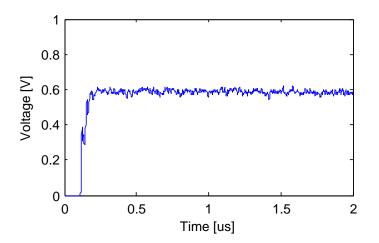

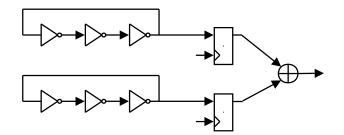

| 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10 | Shape of the power spectrum of a digital random signal.TRNG based on oscillator rings.Frequency spectrum of $X_i$ Frequency spectrum of $X_s$ Baseband spectrum of $X_s$ Frequency spectrum of $X_{xor}$ Baseband spectrum of $X_{xor}$ Frequency spectrum of $X_{xor}$ Baseband spectrum of $X_{xor}$ Amount of generated frequency components related to the sampling frequencyStandard deviation of the TRNG output in the restart experiment                                                                                   | 47<br>49<br>50<br>50<br>51<br>51<br>51<br>52<br>53             |

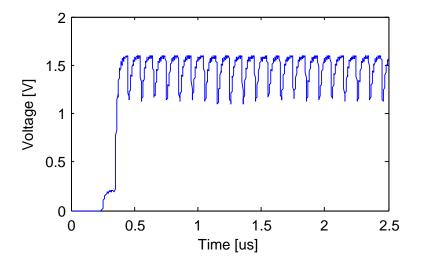

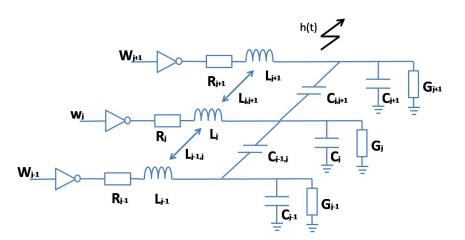

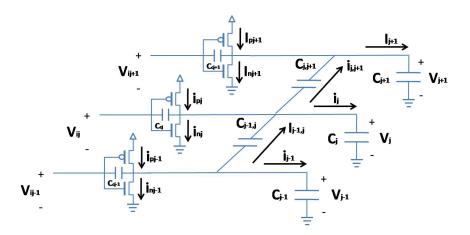

| 6.1<br>6.2<br>6.3<br>6.4                                            | TRNG based on several oscillator rings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59<br>59<br>60                                                 |

| 6.5          | Distribution of transitions after restarts of an oscillator ring with deviation in                                                  |          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

|              | frequencies.                                                                                                                        | 61       |

| 6.6          | Accumulated standard deviation after restarts of an oscillator ring with jitter, deterministic signal and deviation in frequencies. | 61       |

| 6.7          | Distribution of transitions after restarts of an oscillator ring with jitter, deter-                                                | 01       |

|              | ministic signal and deviation in frequencies.                                                                                       | 62       |

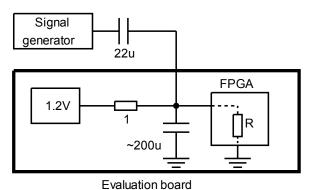

| 6.8          | Setup of the attack.                                                                                                                | 62       |

| 6.9          | 5-stage metastable TRNG.                                                                                                            |          |

|              | FIGARO TRNG.                                                                                                                        | 63       |

| 6.11         | Multi ring TRNG (Sunar).                                                                                                            | 64<br>65 |

| 6.12<br>6.13 | Bias of the TRNG designs with deterministic jitter                                                                                  | 66       |

| 0.120        |                                                                                                                                     | 00       |

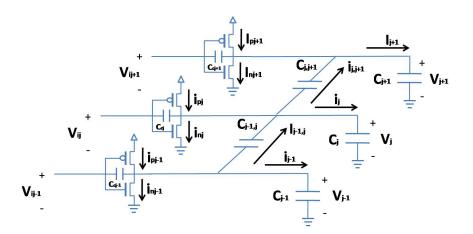

| 7.1          | Simplified model, assuming load and coupling capacitances to be dominant                                                            | 73       |

| 8.1          | TRNG design.                                                                                                                        | 78       |

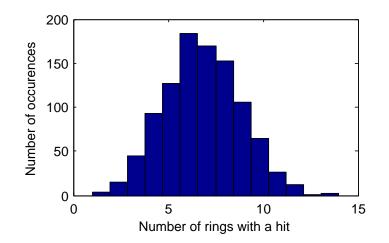

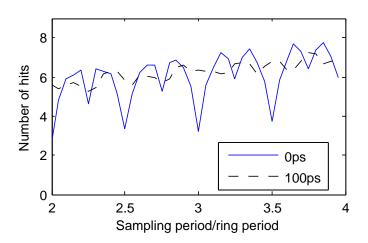

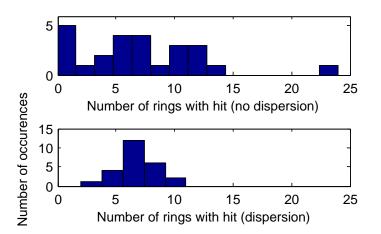

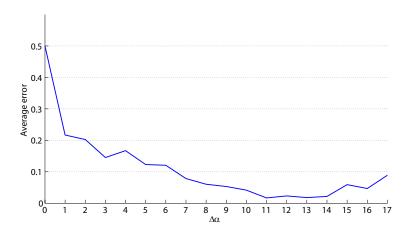

| 8.2          | Histogram of hits with the default parameters.                                                                                      |          |

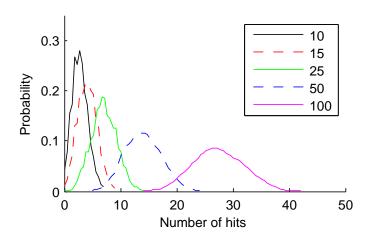

| 8.3          | Density of hits with different numbers of rings                                                                                     |          |

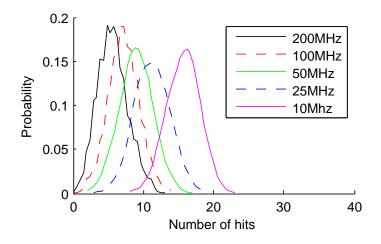

| 8.4          | Density of hits with different sampling frequencies.                                                                                | 81       |

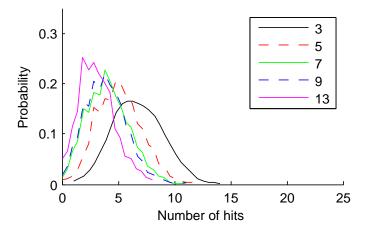

| 8.5          | Density of hits with different number of inverters.                                                                                 |          |

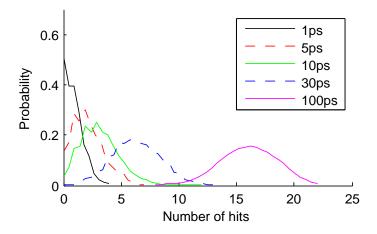

| 8.6          | Density of hits with different size of jitter.                                                                                      |          |

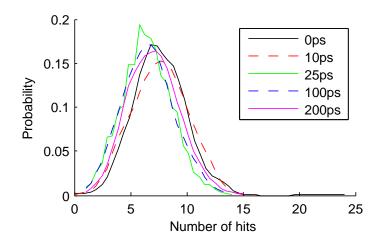

| 8.7          | Density of hits with different dispersion in ring period.                                                                           |          |

| 8.8          | Mean of hits with and without dispersion in ring periods                                                                            | 83       |

| 8.9          | Histograms of hits with and without dispersion.                                                                                     | 84       |

| 9.1          | TRNG based on several oscillator rings.                                                                                             | 88       |

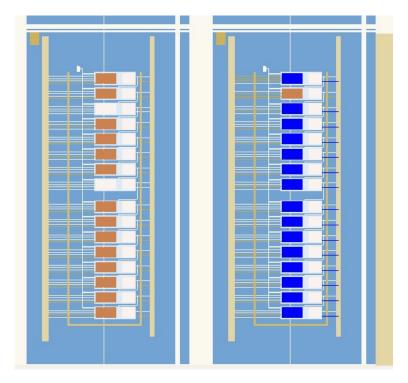

| 9.2          | Placement of two oscillator rings with 15 inverters in an Altera CycloneII FPGA.                                                    | 89       |

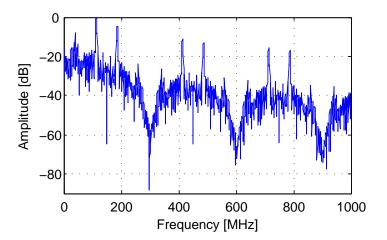

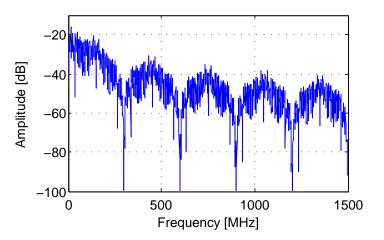

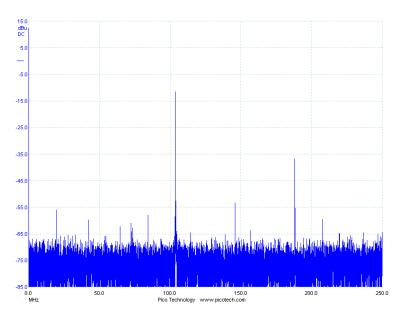

| 9.3          | Frequency spectrum of one oscillator ring                                                                                           | 90       |

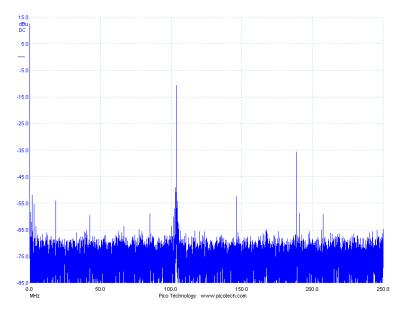

| 9.4          | Frequency spectrum of one oscillator ring with another ring enabled                                                                 | 90       |

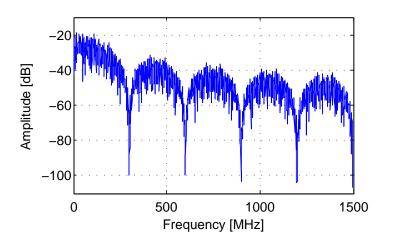

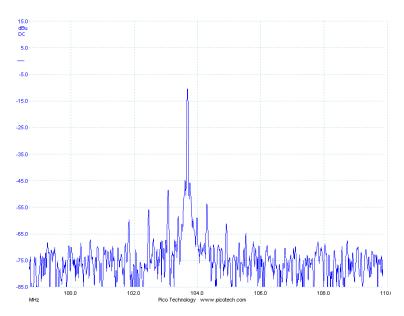

| 9.5          | Frequency spectrum of one oscillator ring around the first harmonic with an-                                                        |          |

| 0.0          | other ring enabled.                                                                                                                 | 91       |

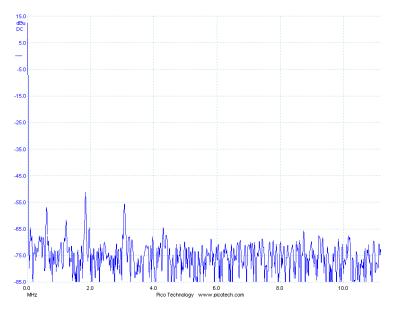

| 9.6          | Frequency spectrum of one oscillator ring around the DC component with an-<br>other ring enabled.                                   | 91       |

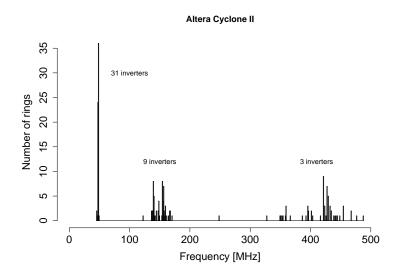

| 9.7          | Histograms of oscillator frequencies of the Altera FPGA.                                                                            |          |

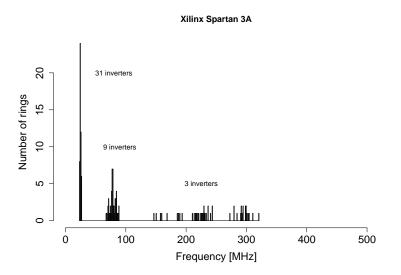

| 9.8          | Histograms of oscillator frequencies of the Xilinx FPGA.                                                                            | 93       |

| 9.9          | Histograms of oscillator frequencies of the Actel FPGA.                                                                             | 94       |

| 9.10         | с                                                                                                                                   |          |

|              | Placement of inverters in 5 oscillator rings with 3 inverters.                                                                      | 95       |

|              | Placement of inverters in 2 oscillator rings with 9 inverters                                                                       | 95       |

|              | Experimental setup for studying phase interlock                                                                                     |          |

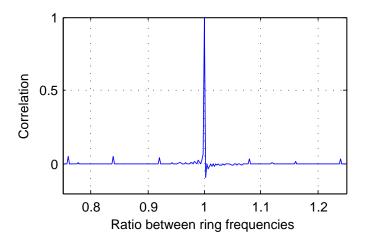

|              | Simulation of correlation of two rings with frequencies close to each other                                                         |          |

| 9.15         | Calculated entropy based on an estimator of probability.                                                                            | 98       |

| A.1          | TRNG based on oscillator rings                                                                                                      | 103      |

| A.2          | Our proposal                                                                                                                        |          |

| A.3          | Beat frequency                                                                                                                      | 104      |

| A.4          | Bias of the TRNGs on Figure A.1 and A.2                                                                                             |          |

| A.5          | Histogram of ring frequencies                                                                                                       |          |

| A.6          | Dispersion of frequencies                                                                                                           |          |

| A.7          | Simulated probability of hitting a transition region                                                                                |          |

| A.8          | 10 restarts with 25 rings                                                                                                           | 109      |

| <b>B.1</b>   | Model of layout dependent phenomena                                                                                                 |          |

| B.2          | Simplified model, assuming load and coupling capacitances to be dominant                                                            | 116      |

# List of Tables

| 2.1<br>2.2               | Possible combinations of bit values and transitions.6Resources and speed of selected TRNGs in FPGA.14 |

|--------------------------|-------------------------------------------------------------------------------------------------------|

| 4.1                      | Resources used in the Altera FPGA                                                                     |

| 6.1                      | Amount of ones of different TRNGs in FPGA                                                             |

| 7.1<br>7.2               | Analytic $(E_T)$ and simulated $(\hat{E}_T)$ dissipated energy for bus with 8 lines                   |

| 9.1                      | Correlation between oscillator rings in FPGA devices                                                  |

| A.1                      | Resources used in the Altera FPGA                                                                     |

| B.1<br>B.2<br>B.3<br>B.4 | Number of transition patters                                                                          |

#### Chapter 1

### Introduction

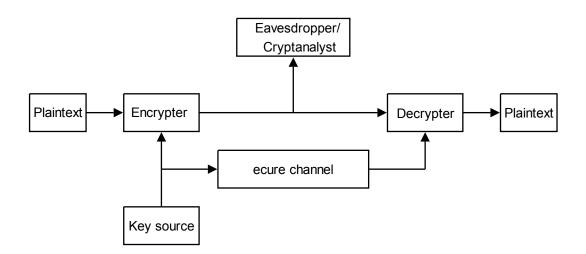

During the last decades there has been a rapid development in the technology used for digital communication. For instance, the introduction of Internet and cellular phones has revolutionized the everyday life of people, but this new technology has also made it possible for attackers to illegally get access to information that was meant to be private or secret. One possible solution to this problem is to use cryptography. This has been used for centuries in the military and especially in war situations to prevent secret information falling into the hands of the opposite side. A cryptographic system can be defined as a computer system using encryption in order to hide the information or plain text with the use of a secret key. Reconstruction or decryption of the original information should only be possible for a recipient knowing the same secret key originally used in the encryption. The objective of cryptography is to enable two entities to exchange information through an insecure channel in such a way that an attacker is unable to obtain or decode the concealed information. This could be solved by using a cryptographic system which could either be asymmetric such as a public-key system or symmetric based on for instance a block cipher such as the Advanced Encryption Standard (AES). A model of a symmetric cryptographic system is shown in Figure 1.1. It consists of an encryption block, a decryption block, a key generator and a secure channel for key management [49]. In order to achieve high security, it is important that the cryptographic algorithm is strong. However, in both symmetric and asymmetric cryptographic systems the algorithm is usually public and in this case the security depends on the secrecy of the key. Therefore it is vital that the circuit generating these keys, a random number generator (RNG), has properties that make it impossible for an attacker to predict the used key in a better way than by pure guessing. Even though the cryptographic algorithm is strong, a weak RNG could significantly reduce the security of the cryptographic system.

Figure 1.1: Model of a symmetric cryptographic system.

An implementation of an RNG used in a cryptographic system must satisfy a set of requirements. During the work with this thesis, the following requirements emerged as important for an RNG:

- The RNG shall generate output bits with good statistical properties.

- The RNG shall generate output bits with high entropy.

- The RNG shall be robust against attacks.

- The RNG shall be robust against environmental variations.

- The RNG shall have stable properties during the lifetime of a product.

- The RNG should have reasonably high throughput or bit rate.

- The RNG should have a simple implementation.

An RNG satisfying these requirements can be used in a high-grade cryptographic system.

A cryptographic system has traditionally been implemented in an application specific integrated circuit (ASIC), but the growth in the field of programmable logic devices (PLDs) has made these circuits more suitable and appealing even for use in high-grade crypto-graphic systems. Implementing an RNG inside a programmable device such as a field programmable gate array (FPGA) along with the encryption module would give a more secure design in the sense that an attack is more difficult due to limited access to the RNG and because the generated key does not need to be distributed outside the integrated circuit.

#### 1.1 **Research Questions**

Designing a circuit capable of generating random bits with good statistical properties at a high bit rate and at the same time being robust against attacks and changing environments is a challenging task. An interesting perspective is to investigate the possibility of implementing an RNG based on a physical property in a programmable device with so good properties that it could be used in a high-grade cryptographic system. This could be formulated into a research question:

• Q1: Investigate the properties of an FPGA in order to design and implement an RNG with good statistical properties, high throughput rate and independent of a special placement of the logic in the programmable device.

As an extension of this problem, two related problems can be formulated:

- Q2: What are the details of operation of such an RNG and what are its performances?

- Q3: Is this RNG implementation robust against attacks?

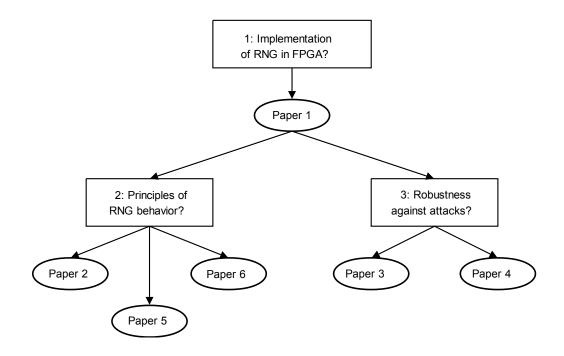

These three research questions are answered by the following papers included in this thesis:

- Knut Wold and Chik How Tan, Analysis and Enhancement of Random Number Generator in FPGA Based on Oscillator Rings, in International Journal of Reconfigurable Computing, pp. 1–8, 2009.

- 2. Knut Wold and Slobodan Petrović, **Optimizing Speed of a True Random Number Generator in FPGA by Spectral Analysis**, in *Proceedings of the 4th IEEE International Conference of Computer Sciences and Convergence Information Technology (ICCIT'09)*, pp. 1105–1110, 2009.

- Knut Wold and Slobodan Petrović, Robustness of TRNG against Attacks that Employ Superimposing Signal on FPGA Supply Voltage, in Proceedings of the Norwegian Information Security Conference (NISK'10), pp. 81–92, 2010, Tapir Akademisk Forlag.

- Geir Olav Dyrkolbotn, Knut Wold and Einar Snekkenes, Security Implications of Crosstalk in Switching CMOS Gates, in *Proceedings of the 13th Information Security Conference (ISC'10)*, Lecture Notes in Computer Science, vol. 6531, pp. 269–275, 2011, Springer.

- Knut Wold and Slobodan Petrović, Behavioral Model of TRNG Based on Oscillator Rings Implemented in FPGA, in Proceedings of the 14th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS'11), pp. 163–166, 2011.

- 6. Knut Wold and Slobodan Petrović, Security Properties of Oscillator Rings in True Random Number Generators, *Submitted*.

In addition, the following paper (see Appendix A) is overlapping with one of the papers listed above:

Knut Wold and Chik How Tan, Analysis and Enhancement of Random Number Generator in FPGA Based on Oscillator Rings, in Proceedings of the 4th IEEE International Conference on Reconfigurable Computing and FPGAs (ReConFig'08), pp. 385–390, 2008.

In Appendix B, the full version of paper 4 as it was presented at the conference is given, and in Appendix C, an additional theoretical model of an RNG based on oscillator rings is presented, in which the guaranteed randomness rate is computed.

The relationship between the research questions and the included papers is shown in Figure 1.2.

Figure 1.2: Relationship between the included papers and the research questions.

Paper 1 [64] answers the research question Q1. In that paper, an RNG based on XOR of several sampled equal length oscillator rings is proposed. This RNG is an enhancement of the proposal of Sunar et al. [51]. The RNG is implemented in an Altera Cyclone II FPGA and the experiments show that the properties of this generator are good.

However, even though the design is quite simple, the exact principles behind its behavior is not obvious. Paper 2 [60] investigates the frequency spectrum of the different modules in this RNG explaining its behavior. At the same time, the RNG is optimized in order to achieve a high throughput rate. Paper 5 [62] investigates the amount of entropy in the RNG by defining a model based on the number of hits in the transition region determined by the size of the standard deviation of the accumulated jitter. The simulations performed in Matlab verify the observations from the experiments performed in [64] that the proposed RNG design generates entropy at every sampling point or bit. Paper 6 [59] investigates the low-level properties of the oscillator rings implemented in an FPGA and their implication on the security of this RNG. The covered topics are interaction between oscillator rings implemented physically close to each other, correlation and dependency between the sampled output of the oscillator rings and the dispersion between oscillator ring frequencies. All the experiments are carried out using three different types of FPGAs from different vendors.

The robustness of the RNG is investigated in paper 3 [61] answering Q3. Four different RNG designs are implemented and tested for robustness against an attack that employs superimposing signal on the FPGA power supply voltage. The experiments show that RNGs based on several oscillator rings are not influenced by this attack while the two other designs are. In paper 4 [17], an improved power model based on layout dependent phenomena such as capacitive couplings between bus lines is proposed. This power model can be used to improve the performance of a side-channel attack by reducing the computing workload, but also to reveal the random data transfered on a data bus between the key source and the encryption module in an RNG.

#### **1.2** Structure of the Dissertation

The rest of the thesis is organized as follows: In Chapter 2 an overview of random number generators in programmable devices is given describing the state of the art and different aspects related to the topic. In Chapter 3 a summary of the contributions of the included papers and the thesis is given. In Chapters 4-9 the six research papers included in this thesis are presented. In Appendix A the overlapping paper is given, in Appendix B the full version of paper 4 is included and in Appendix C an additional theoretical model of an RNG based on oscillator rings is presented.

### Background

An RNG is a device or a circuit generating a stream of bits with a property that the value of each bit is unpredictable, but in the long run the bits follow a certain distribution. Based on the knowledge of the previous bits it shall be impossible to calculate or predict the next bit in a better way than by pure guessing. These random bit sequences could for instance be used for generation of session keys, initial vectors (IVs) or cryptographic challenges/responses in a cryptographic system.

Implementations of binary sequence generators used in cryptography can be divided into two different categories [42]:

- Pseudo random number generator (PRNG): an algorithm with a property that it is computationally infeasible to predict the value of the next bit even when all the previous bits are given. The output bit is unpredictable, but it is reproducible since sequences generated from the same seed or initial state in the PRNG will be identical, i.e. the generator is deterministic.

- True random number generator (TRNG): a device where the generation of an output bit is based on a physical random process (for example a radioactive device, thermal noise from a diode, jitter of a clock or metastability on a signal, etc.), or on non-deterministic events (for example system time in a computer, seek time of a hard disk, user interaction like mouse movements or keyboard typing, etc.). The output bit is both unpredictable and irreproducible.

In addition, it is possible to implement RNGs, which are combinations or hybrids with design elements from both the PRNG and the TRNG. In the rest of this thesis the focus will be on physical TRNG.

TRNGs based on logic devices can be implemented in for instance an ASIC, in a secure micro controller on a smart card or in a programmable device such as an FPGA. In this thesis, only implementations of TRNGs in FPGA are considered.

The main challenge in designing a TRNG is to find a suitable noise source and a method of extracting the randomness from this source. For instance, the stochastic process of radioactive decay has been used for generation of random bits. The disadvantages of RNGs based on a radioactive device are low bit rate, large physical size and potential environmental and medical challenges. An often used alternative is to amplify the noise of a diode [26]. Problems related to this solution are the sensitivity to variations in temperature and power supply voltage and the changes in component properties due to aging. In addition, the bit rate is not very high and the implementation uses external components, which makes manipulation by an attacker easier. A better solution is to implement the whole TRNG inside an integrated circuit such as a micro controller or a programmable device such as an FPGA or a PLD. The advantages are that the design is digital and therefore more robust against aging and variations in temperature and power supply voltage and the implementation is more secure because of limited physical access by an attacker.

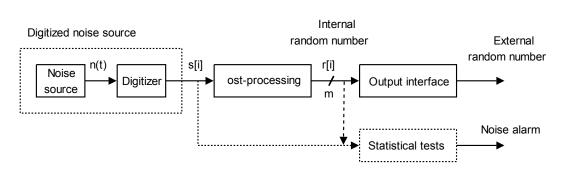

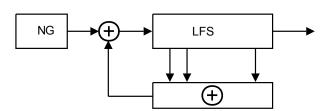

A model of the physical TRNG [10, 44] is shown in Figure 2.1. The noise source is the physical property creating the true randomness or entropy in the generator. The noise signal n(t) is typically an analog signal and it is digitized creating a binary digital signal s[i].

Figure 2.1: Model of a physical TRNG.

The random number can then be fed into a post-processor creating the *m*-bit internal random number r[i]. The post-processor may be skipped if the noise source has good properties, but in most real TRNG implementations in cryptographic systems a post-processor is recommended. The output interface could be storage of random bits in some sort of memory before distributing the bits to for instance the encryption module. In addition, there should be a surveillance circuit monitoring the bit sequences in order to detect statistical weaknesses or a breakdown in the generated random bit stream.

For an RNG implementation, the power consumption per generated output bit should be reasonably low. For logic devices, the power consumption could be measured by counting the number of logic gate transitions per bit. In this thesis, the power consumption of the programmable logic devices is not considered.

#### 2.1 RNG Properties

An ideal random sequence  $x_n \in \{0,1\}$ , n = 1, 2, ... can be generated by flipping a fair coin, observing the outcome of a toss and allocating for instance a zero for head and a one for tail. Each throw can be regarded as independent of the previous ones and each outcome occurs with a probability of  $\frac{1}{2}$ . Table 2.1 shows the possible combinations of the outcomes and what combinations that result in a transition, i.e.  $0 \rightarrow 1$  or  $1 \rightarrow 0$ , in such a scheme.

The following properties are achieved based on an ideal random sequence:

- 1.  $Prob(x_n = 0) = Prob(x_n = 1) = \frac{1}{2}$

- 2.  $Prob(Transition) = \frac{1}{2}$

Property 1 states that there should be an equal amount of zeros and ones in the sequence, i.e. no bias. Property 2 states that on average there should be a transition or change in the bit value for every second bit. If a bit sequence diverges much from these properties, the sequence will not be regarded as random because it is possible to predict the next bit in a better way than guessing.

Some similar requirements are reflected in Golomb's postulates for a PRNG [23]:

| Present bit | Next bit | Transition |

|-------------|----------|------------|

| 0           | 0        | No         |

| 0           | 1        | Yes        |

| 1           | 0        | Yes        |

| 1           | 1        | No         |

Table 2.1: Possible combinations of bit values and transitions.

- The number of zeros and ones shall be approximately equal over a period.

- The number of blocks (runs of ones) over a period shall be as follows: <sup>1</sup>/<sub>2</sub> of all blocks shall have length 1, <sup>1</sup>/<sub>4</sub> of all blocks shall have length 2, <sup>1</sup>/<sub>8</sub> of all blocks shall have length 3, etc. The similar distribution applies for gaps (runs of zeros).

- The value of the autocorrelation function shall be constant except for multiples of the period where it has a peak

The entropy in information theory is a measure of uncertainty of the value of the next generated bit. The entropy H of a binary signal is defined as [45]:

$$H = -\sum_{i=0}^{1} p_i \cdot \log_2(p_i)$$

(2.1)

where  $p_i$  is the probability of generating a zero or a one. Ideally, the probabilities  $p_0$  and  $p_1$  are equal to  $\frac{1}{2}$  resulting in an entropy of 1.0, which is the maximum value of the entropy function in Equation (2.1).

For practical implementations of a TRNG the following general requirements can be given [42]:

- The statistical properties of the random sequence should be good.

- It shall not be possible to compute either previous or future bits based on the knowledge of subsequences of bits generated by the RNG with a higher probability than by pure guessing.

An RNG satisfying these requirements can be regarded as suitable for use in a high-grade cryptographic system treating sensitive information. The first requirement is usually experimentally verified by using statistical test suites such as NIST SP 800-22 [35] or DIEHARD [32]. The generated bit sequences used as input to these tests must be long (several Mbit) in order to verify that the bit sequences have the expected properties. Verifying the second requirement is more challenging, but it can be achieved by finding a lower bound of the entropy per random bit based on a stochastic model of the noise source [43, 44]. This stochastic model is simplified if the generated bits can be regarded as independent. A method achieving this independence is to implement a stateless or memoryless RNG by for instance resetting all the states inside both the digitized noise source and the post-processor after each generated bit [10].

#### 2.2 **Programmable Devices**

Programmable devices are integrated circuits with a regular architecture and the ability of being configured by the customer in the field and not restricted to the facilities of the manufacturer. A programmable device can be classified based on how the configuration is stored in the device:

- SRAM four transistors forming two cross-coupled inverters storing 1 bit.

- Flash EPROM a floating-gate MOSFET transistor with two gates storing 1 bit.

- Antifuse a permanent electrical connection created by applying a current exceeding a specified limit.

The programmable device is said to be volatile if the configuration is lost when the power is switched off meaning that the configuration needs to be loaded at every power-up. A device based on SRAM is volatile while flash EPROM and antifuse FPGAs are non-volatile.

The configuration of the SRAM and the flash EPROM devices are re-programmable while the antifuse devices are one-time-programmable (OTP).

An alternative classification of programmable devices can be made by the size and the complexity of the programmable device:

- SPLD Simple Programmable Logic Device.

- CPLD Complex Programmable Logic Device.

- FPGA Field Programmable Logic Device.

SPLDs are small devices only capable of implementing simple digital logic, while the largest FPGAs can implement complex digital systems. The complexity of a CPLD is somewhere in between the SPLD and the FPGA. In the rest of this section the focus will be on FPGA only.

An FPGA consists of an array of several small blocks or logic elements. Typically, each logic element consists of a look-up table (LUT) and/or a register element. A LUT can implement any digital function only limited by the number of inputs to the LUT, typically between 3 and 6 depending on the vendor and the FPGA family. The LUT consists basically of a configured memory location and a multiplexer selecting the correct memory bit based on the bit combination on the input signals to the LUT. The register element can implement a flip-flop or a latch capable of storing 1 bit. The number of these blocks or logic elements in an FPGA can vary from some thousands in the smallest devices to more than a million in the largest.

The basic building block of an FPGA varies both in name and functionality depending on both the vendor and the specific FPGA family. For instance, the Cyclone II FPGA from Altera [3] uses the name *logic element* containing a 4 input LUT and a 1 bit register element. The Virtex II FPGA from Xilinx [66] uses the name *slice* containing two 4 bit LUTs and two 1 bit register elements. The ProASIC FPGA family from Actel [1] uses the name *VersaTile* configured either as a 3 input LUT or a 1 bit register. All these different definitions complicate the work of the designer regarding comparison of the size of the FPGA devices from different vendors.

All these small elements are placed in a regular structure connected together with different routing resources. The blocks located close to each other are grouped into a larger unit or cluster by short routing. These clusters are again connected together by longer routing resources. The global nets used for clock and reset signals need special attention because it is important that these nets have equal timing delay to all the logic elements in the FPGA. If a clock edge arrives to the logic elements at different point in time, there is a risk that the digital design will not work properly.

In addition, other special resources are found in an FPGA. Usually, an FPGA contains a number of SRAM blocks. A typical size of a SRAM block is 4Kbit, but the read and write bus widths are configurable and several RAM blocks can be put together constructing larger memories. Other components found in an FPGA are phase-lock loop (PLL) for generating additional clock signals, multipliers for performing digital signal processor (DSP) functions, CPU cores and communication interface modules.

The digital design is described in a hardware description language (HDL) where VHDL and Verilog are the two most commonly used. The HDL files are input to the software tools running synthesis and place and route (P&R). The synthesis is a process of verifying, optimizing and translating the hardware description into a netlist defining the hardware primitives needed in the digital design and the connections between these primitives. The P&R is an iterative process searching for an optimal placement of the primitives defined in the netlist into physical LUTs and registers in the FPGA and creating the routing between these elements. The P&R process can be done automatically by the SW tools based on the settings done by the operator, but it is also possible to do the P&R operation more manually. In this thesis, only automatic P&R are used based on the default settings of the SW-tools. The final output is a binary file or bit-file containing the configuration of the FPGA. Typically, this bit-file is loaded into the FPGA through the JTAG interface. When the configuration is stored inside the FPGA, it will implement the digital design according to the hardware description the user has made.

#### 2.3 Noise Sources in FPGA

The two most used physical noise sources in an FPGA generating true randomness are jitter of clocks and metastability on signals. Usually, both jitter and metastability are unwanted properties in an electronic design, but in a TRNG they contribute with the unpredictable behavior necessary for generating the true randomness.

Jitter can be looked upon as short-term variations of a digital signal's significant instants from their ideal positions in time [52]. The randomness arises because the exact position in time when a transition occurs is unpredictable. The jitter typically follows a Gaussian distribution characterized by a zero mean and a standard deviation  $\sigma$  [25, 33, 55]. The size of the jitter is related to the technology used in the integrated circuit.

A flip-flop in a digital system has two stable states: logical zero (ground (GND) or 0V) and logical one ( $V_{cc}$  typically 3.3V). If the flip-flop samples a signal during the setup or hold times of a transition, the result could be that the voltage level at the output of the flip-flop is neither GND nor  $V_{cc}$ , but at an intermediate undefined level (metastability). After a short period of time the voltage level will return to one of the two stable states, but to which state it stabilizes is unpredictable. This phenomenon can be described by dropping a ball on a hill and observing to which side of the hill (represented by the two stable logic levels) the ball lands [4]. The duration of the metastable state depends on where the ball is dropped. If it falls right on the top it takes longer time before it rolls down to one of the sides than if the ball is dropped on the slope of the hill.

Care must be taken when implementing these noise source circuits in HDL because they typically consist of combinational loops. These structures can be removed during the synthesis process if the tools are not instructed to preserve them. The actual implementation needs to be examined and tested in order to verify that the circuit is correctly implemented. Both jitter and metastability are unwanted properties in ordinary digital designs. The manufacturers will always design their integrated circuits in such a way that the size of the jitter is minimized and that the probability of getting metastable states in the device is as low as possible.

#### 2.4 TRNG Implementations in FPGA

As seen in Figure 2.1, a typical implementation of a TRNG consists of three parts. Firstly, a physical random noise source, which in the case of an FPGA is typically jitter or metastability. Secondly, a digitizer, which collects the randomness from the entropy source and generates a binary bit sequence. Thirdly, a post-processor, which improves the statistical properties of the random bit sequence by performing whitening and data compression.

Several implementations of TRNG in FPGA have been proposed [50], and in the rest of this section some of them are presented with the focus on the used noise source and the digitizer circuit.

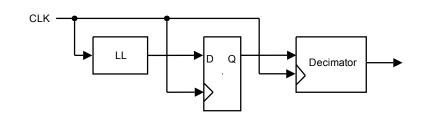

In 2002, Fisher et al. [20] used an analog PLL in Altera FPGAs as entropy source in a TRNG, see Figure 2.2. The generated signal from the PLL has jitter and it is sampled in a D flip-flop clocked with a master clock. The frequencies of the master clock and the PLL output are chosen to be relatively prime. The decimator circuit is used for removing the deterministic part of the random signal. In order to increase the bit rate, this TRNG can be extended by XORing the sampled outputs from a delay chain of the PLL output clock signal [19]. This TRNG design is restricted to FPGAs containing an analog PLL excluding

Figure 2.2: Principle of TRNG by Fisher et al. [20].

for instance FPGA devices from Xilinx containing a digital PLL. The achieved bit rate of this TRNG was less than 1Mbit/s.

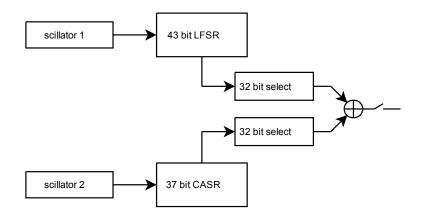

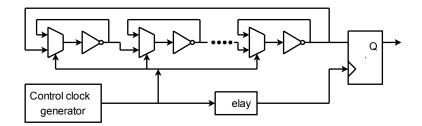

In 2002, Tkacik [53] proposed a TRNG using a linear feedback shift register (LFSR) and a cellular automata shift register (CASR) clocked by two independent free running oscillator rings, see Figure 2.3. Selected outputs from the LFSR and the CASR are combined by an XOR generating the final random signal. Since the LFSR/CASR structures contain memory elements, the output bits are correlated. There must therefore be a delay of more than twice the length of the LFSR register between the sampling of each output bit to achieve independent random bits. An attack on this TRNG design was presented by Dichtl [13] under the assumption that the feedback polynomials of the LFSR and the CASR and the permutation before the XOR are known. Schindler [41] presented a stochastic model and a lower limit of the entropy per bit of this TRNG scheme.

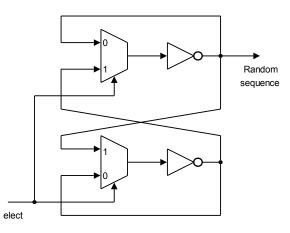

In 2003, Epstein et al. [18] proposed a TRNG based on a bi-stable memory element consisting of two multiplexers and two inverters, see Figure 2.4. When the select signal is at logic zero, the circuit reduces to two single inverter oscillator rings which are put into a metastable state. When the select signal is logic high, the circuit resolves the output of the two oscillator rings and stabilizes either to logic zero or logic one and thereby creating randomness. The outputs of several of these memory elements are then connected together by the use of XOR to generated the final output bit sequence.

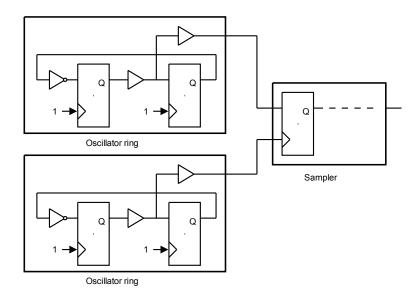

In 2004, Kohlbrenner et al. [29] used two oscillator rings where each ring consisted of two transparent latches, a buffer and an inverter, see Figure 2.5. The generated clock signal from the oscillator ring contains jitter and acts as an entropy source. The sampler circuit was a D flip-flop where the output of one of the oscillator rings was connected to the data input while the other ring output was connected to the clock input. In addition, the sampler circuit decides when a new random bit is ready on the output. The frequencies of the two

Figure 2.3: Principle of TRNG by Tkacik [53].

Figure 2.4: Principle of TRNG by Epstein et al. [18].

oscillator rings have to be almost identical or correctly matched if this implementation is going to work properly. The design achieved a bit rate of less than 1Mbit/s.

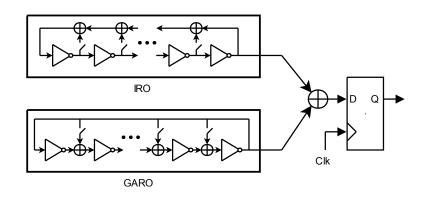

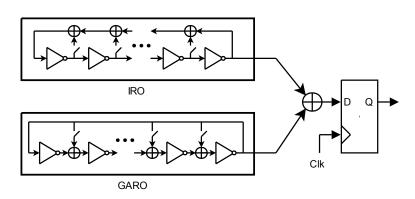

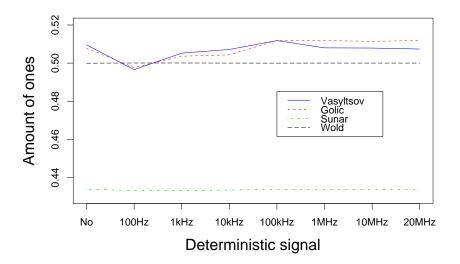

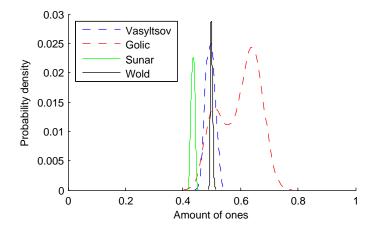

In 2006, Golić [22] proposed a TRNG using a Galois ring oscillator (GARO) and a Fibonacci ring oscillator (FIRO), see Figure 2.6. These LFSR like structures use inverters as delay elements instead of register elements, and the switches are either open or closed implementing the feedback polynomial. Continuous oscillations in these structures are achieved if the feedback polynomials satisfy certain requirements [22]. The outputs from the GARO and the FIRO are combined with an XOR and the random sequence is generated by sampling the XOR output with a D flip-flop. This design was further investigated and implemented by Dichtl et al. [15]. The FIRO/GARO structures behave in an analog manner creating an output signal similar to a noise signal, and they may therefore be susceptible to crosstalk from other signals inside the FPGA. The achieved bit rate of this TRNG was reported to be 12.5Mbit/s.

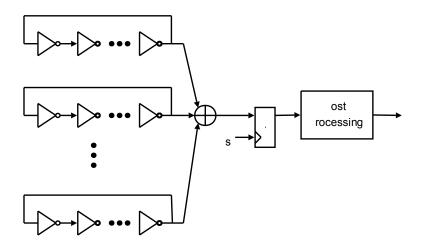

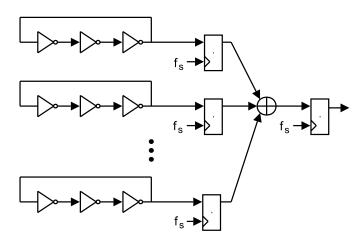

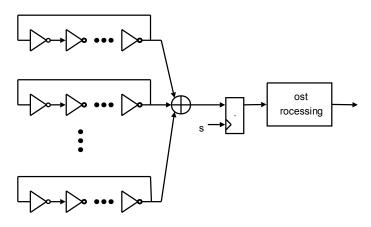

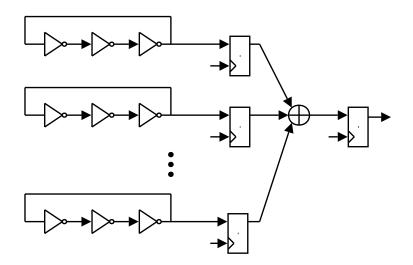

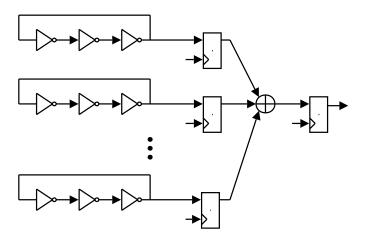

In 2007, Sunar et al. [51] gave a theoretical proposal of a TRNG based on several equal

Figure 2.5: Principle of TRNG by Kohlbrenner et al. [29].

#### 2. BACKGROUND

Figure 2.6: Principle of TRNG by Golić [22].

length oscillator rings made up of an odd number of inverters (114 oscillator rings where each ring consists of 13 inverters), see Figure 2.7. The main idea is to use a relatively large number of oscillator rings combined by the XOR operation in order to ensure that at each time at least one of the oscillator ring is sampled near a transition point with a sufficient high probability. The observation that an output bit obtained by sampling an oscillator ring signal is more random if the sampling occurs near a transition edge, was pointed out by Bock et al. [8]. The underlying assumption for the calculations based on this TRNG design, is that jitter of the individual ring oscillators are statistically independent. Imbalances between zeros and ones in the random signal are corrected by using a post-processor based on a resilient function. An implementation of this design was carried out by Schellenkens et al. [40] with only three inverters in each oscillator ring. The reported achieved bit rate of this TRNG included the post-processor was 2.5Mbit/s. This design was criticized by Dichtl et al. [15] mainly because the current CMOS technology is not capable of handling the high number of transitions per time unit generated by all the oscillator rings at the input of the XOR-tree. In addition, the assumption that jitter in individual oscillator ring signals is independent is not realistic due to interactions between these signals in practical implementations, and that the urn model introduced in [51] does not include the fact that the standard deviation of jitter accumulates in time. In 2008, Wold et al. [63] proposed an enhancement of the design of Sunar by adding a D flip-flop between each oscillator ring

Figure 2.7: Principle of TRNG by Sunar et al. [51].

Figure 2.8: Principle of TRNG by Vasyltsov et al. [57].

output and the XOR tree correcting the speed problem pointed out in [15]. Experiments performed on the enhanced TRNG showed that the statistical tests passed with the use of only 25 oscillator rings. The reported bit rate of this TRNG was 100Mbit/s.

In 2008, Vasyltsov et al. [57] proposed a TRNG based on a 5-stage metastable ring oscillator where each stage contains only a multiplexer and an inverter, see Figure 2.8. The multiplexers are controlled such that in the first phase each of the five inverters is connected in a loop (output to input) so that they are put into a metastable state. In the second phase, the five inverters are connected as an oscillator ring with initial values depending on the metastable states. The idea of switching between metastable circuit configurations and oscillating configurations is based on the work by Epstein et al. [18]. A random bit is sampled at the output of the ring at the end of the second phase. The result is a fast and small implementation of a TRNG in an FPGA or ASIC, but optimization in the synthesis process causes difficulties in an FPGA is critical. This implementation uses very little of the resources in the FPGA and the reported bit rate was 140Mbit/s.

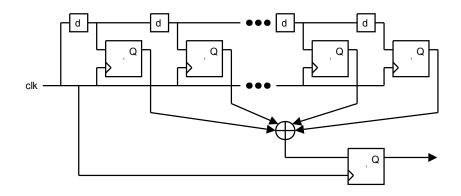

In 2009, Danger et al. [12] proposed a TRNG based on metastability with open loop structures in FPGA. The principle of this design is a delay chain where sampled signals from several tap points in the chain are XORed together and then sampled to create the random signal, see Figure 2.9. The delay between the elements is crucial and special care must be taken in the routing of the delay chain. The reported bit rate of this TRNG was 20Mbit/s.

In 2009, Gyorfi et al. [24] proposed a TRNG using the block RAM in a Xilinx FPGA as entropy source. The method is based on writing a logic one and a logic zero simultaneously to the same memory location in a block RAM configured as a dual port. The resulting value of the written bit is unpredictable due to the attempt to write different values at the same

Figure 2.9: Principle of TRNG by Danger et al. [12].

| TRNG                                              | Speed [Mbit/s] | # LEs       |

|---------------------------------------------------|----------------|-------------|

| Analogue PLL (Fisher et al. [20])                 | <1             | $\sim 50$   |

| LFSR/CASR (Tkacik [53])                           | <1             | $\sim 150$  |

| Two oscillator rings (Kohlbrenner et al. [29])    | <1             | $\sim 50$   |

| FIGARO (Golic [22])                               | 12.5           | $\sim 50$   |

| Multi oscillator rings (Sunar et al. [51])        | 2.5            | $\sim 1800$ |

| Multi oscillator rings (Schellenkens et al. [40]) | 2.5            | $\sim 650$  |

| Multi oscillator rings (Wold et al. [63])         | 100            | $\sim 100$  |

| 5-stage oscillator ring (Vasyltsov et al. [57])   | 140            | $\sim 5$    |

| Open loops (Danger et al. [12])                   | 20             | $\sim 140$  |

Table 2.2: Resources and speed of selected TRNGs in FPGA.

time. The problem of this method is finding a memory location in the RAM giving an unbiased result. Their proposal is to use a circuit seeking for this optimal location at a regular basis. A disadvantage with this design is that it is not portable to other FPGAs than devices from Xilinx. A post-processor is needed in order to improve the statistical properties of this TRNG.

Recently, Varchola et al. [56] proposed a new high entropy digital element based on a bi-stable circuit named transition effect ring oscillator (TERO) implemented in an FPGA. The randomness is extracted on oscillatory trajectory when the TERO resolves a metastable event.

In addition, other TRNG designs have been proposed such as [5, 8, 36, 54].

The number of logic elements occupied in an FPGA for most of these presented TRNGs is low, approximately 50-150 which is less than 1% of the available resources in a medium sized FPGA. An exception is the original proposal of Sunar et al. [51] which uses about 1800 logic elements due to the large number of oscillator rings and many inverters in each ring.

Table 2.2 gives a summary of different TRNGs with a comparison regarding output bit rate and usage of logic elements (LEs) in an FPGA.

#### 2.5 Post-processing

A post-processor is a circuit or algorithm used for improving the quality of the generated random bit sequence. The post-processor has two purposes: Firstly, it should adjust for statistical weaknesses in the generated bit sequence from the noise source. Secondly, it should increase the entropy of the random number by performing data compression at the cost of a reduced bit rate of the generator.