## **Reverse Engineering Microprocessor Content Using Electromagnetic Radiation**

Geir Olav Dyrkolbotn

Thesis submitted to Gjøvik University College for the degree of Doctor of Philosophy in Information Security

2011

Reverse Engineering Microprocessor Content Using Electromagnetic Radiation

Faculty of Computer Science and Media Technology Gjøvik University College

Reverse Engineering Microprocessor Content Using Electromagnetic Radiation / Geir Olav Dyrkolbotn Doctoral Dissertations at Gjøvik University College 2–2011 ISBN: 978-82-91313-73-3 ISSN: 1893-1227 This thesis is dedicated to my wife, Susan and my two children, Guiliana and Bryan. Without your support and sacrifices this work would not have been possible.

### **Declaration of Authorship**

I, Geir Olav Dyrkolbotn, hereby declare that this thesis and the work presented in it is entirely my own. Where I have consulted the work of others, this is always clearly stated.

Signed:

(Geir Olav Dyrkolbotn)

Date:

### Summary

Moore's law has, for almost half a century, described a trend in which the number of transistors in integrated circuits have been doubled every year. Properties, such as processing speed, memory capacity and physical size of circuits, are strongly linked to Moore's prediction. Integrated circuits, such as microprocessors, therefore get smaller yet more and more powerful. The combination of smaller size and larger capacity allow more and more functionality to be included in small microprocessor devices, such as smart phones and smart cards. This includes security related functions, such as confidentiality, integrity, availability and non-repudiation. The use of microprocessor devices is said to make fraud more difficult, however, research has found them susceptible to side-channel attacks. Sensitive information can escape via side-channels such as power consumption or electromagnetic radiation (EMR). When a microprocessor executes its program, power consumption (or resulting EMR) can be used to reveal the content of program and/or data memory of the microprocessor. The correlation between power consumption and microprocessor activity has found many uses: to recover cryptographic keys, to reveal hidden hardware faults, to create a covert channel or to reverse engineer the code executed. This is concerning, considering the increasing demand for and dependability upon microprocessors in secure applications.

This thesis contributes by building a more realistic model of the arsenal available to an adversary engaged in reverse engineering microprocessor content through the electromagnetic side-channel. This includes; (i) presenting a new attack, resembling wireless skimming, (ii) a method for in-depth analysis of EMR and better understanding of what and how much EMR is necessary to launch an attack, (iii) a new power model that better explains the underlying phenomena and (iv) a non-invasive method for reverse engineering physical properties based on EMR.

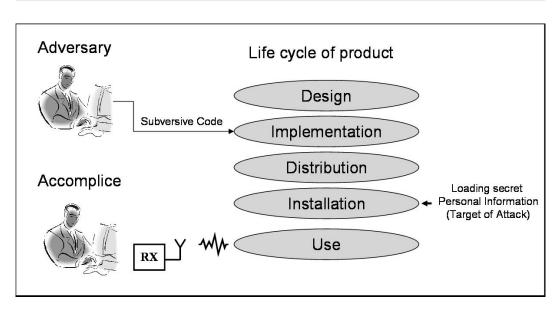

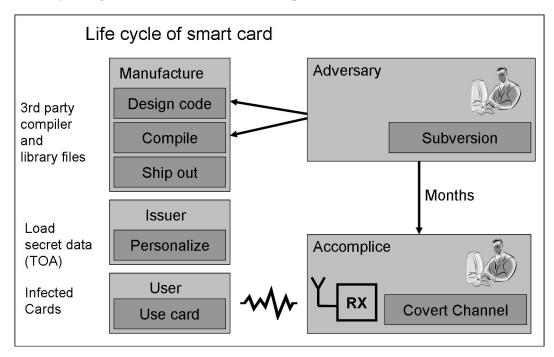

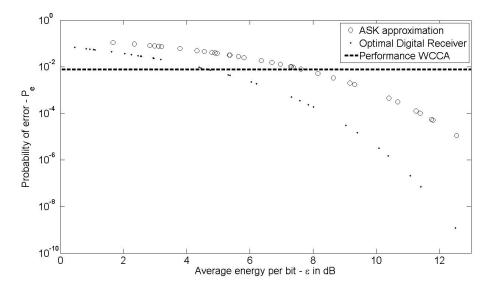

The Wireless Covert Channel Attack (WCCA) contributes towards exploiting the electromagnetic side-channel in a new attack and attack scenario for microprocessor smart cards. The attack brings together knowledge from different fields; electromagnetic sidechannels, covert channels and subversion. The scenario assumes that a highly skilled insider is able to hide a small program (subversive code) on a microprocessor smart card in an early stage of the products life cycle. During normal use of the smart card, the subversive code intentionally manipulates the electromagnetic side-channel, creating a covert channel that can potentially broadcast the cards internal secrets to a nearby receiver. The attack is launched without possession of the card and is, therefore, unlikely to be detected by the user. The feasibility of the attack has been demonstrated on modern, high-security cards with all available security features activated, which demonstrates that attacks resembling wireless skimming are feasible. This contribution highlights the importance of life-cycle security focus for products used in secure applications.

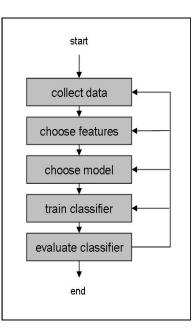

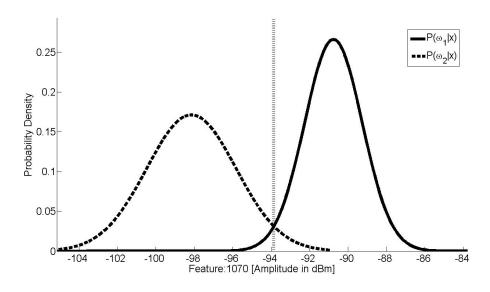

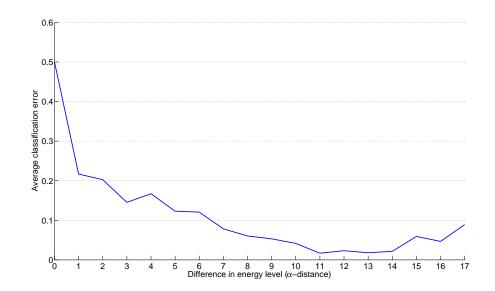

Challenges faced by WCCA and other side-channel attacks are: What and how much of the available EMR is necessary to launch an attack, and how do choices affect the efficiency of the attack? This thesis recognizes reverse engineering microprocessor content as a pattern recognition problem, and can therefore address these challenges as a feature selection problem. A comparison of several multi-class feature selection methods by their performance in a WCCA application is provided. Combining these results with the template attack provides a method for in-depth analysis of the electromagnetic side-channel. This method was applied to data transfer on the microprocessor's internal buses, which gave new insight as to the underlying phenomena and revealed that commonly used power models are not suitable to explain the level of detail achieved by Bayesian classification (e.g. template attack).

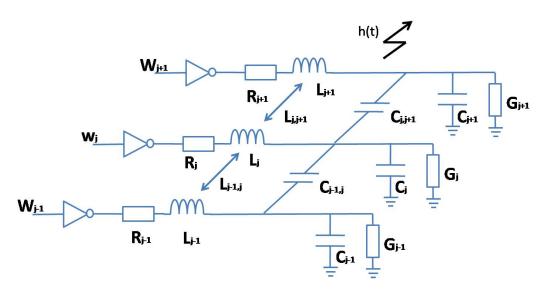

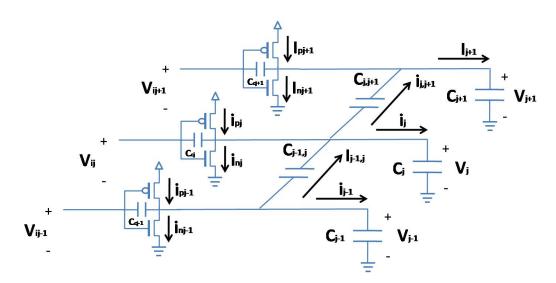

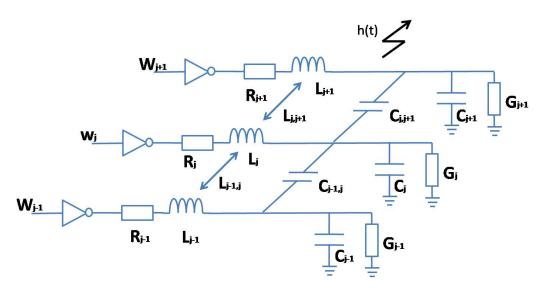

This thesis provides the hypothesis that the classification results can be explained by layout dependent phenomena (LDP). LDP include; (i) inductance and capacitance of conductors, (ii) inductance and capacitance between conductors, (iii) wireless transmission characteristics (i.e. antenna properties) of conductors and other circuit elements and (iv) complex combinations of these phenomena. Simulations and experiments are provided that give new insight as to how capacitance between bus-wires (capacitive crosstalk) influence the energy dissipation and the resulting radiated electromagnetic field in any physical implementation of a digital circuit (e.g. microprocessor). A new power model, based on capacitive crosstalk, is proposed, which better explains the classification results achieved. This can improved side-channel exploitation capabilities.

The new power model shows that energy dissipation (i.e. EMR) is a function of internal physical structures of the microprocessor. It can therefore improve the performance of sidechannel attacks that rely upon a good power model to be successful (e.g. power analysis attacks). A spinoff of this result is that if the microprocessor activity is known, it should be possible to reverse engineer physical structures of the microprocessor. This thesis provides a non-invasive method for determining the relative position of internal bus wires based on known transition pattern and the influence of capacitive crosstalk on EMR. By including other LDP it should be possible to reverse engineer other physical structures of the microprocessor. This is, to the best of our knowledge, a new application area for electromagnetic side-channel information and holds potential for future work.

## Acknowledgments

This work was carried out at the Norwegian Information Security laboratory (NISlab) at Gjøvik University College (GUC) in Norway. From 2003 until 2010 I was formally a PhD student at the University of Oslo. In 2010 I transferred to GUC.

First, I would like to express my thanks and appreciation to my advisor, Professor Einar Snekkenes. Thank you for all your support, contributions, guidance and especially for motivating me when I was struggling and for holding me back when I tried to do too much. A journey that was supposed to last 4 years has now endured for 8 years. Thank you for your patience and understanding.

During the completion of this thesis I have been employed by the Norwegian Armed Forces. I am much in debt to LtCol Roger Johnsen who saw the military's need for PhD work in information security and who, with the support of Brigadier Bakke, allowed me to take on the task. Thank you Roger for your friendship, unconditional support and encouragements. Without our understanding, "work when I can, stay home when I need to", this work would never have been completed. I wish to thank Ivar Kjærem and Bjarte Malmedal for continuing to honor this agreement and for your unconditional support. I would also like to thank all my colleagues in the Armed Forces for your support and patience in waiting for me to finish.

Even though you all finished before me, I want to thank my fellow PhD students; Nils Kalstad Svendsen, Kirsi Helkala, Davrondzhon Gafurov, Hanno Langweg, Knut Wold and Lasse Øverlier for discussions, feedbacks and many inspiring coffee breaks. In particular I would like to thank Nils and Kirsi for being my math experts and Knut for his help with simulations in PSpice as well as the article we wrote together.

I am grateful to Patrick Bours, Slobodan Petrovic and Katrin Franke for their guidance and support, particularly regarding pattern recognition. Thanks to Stephen Wolthusen for his motivating remarks as well as his help regarding LaTex and the formatting of this thesis. Thank you Erik Hjelmås for both administrative and technical help and all the extra trouble you spared me. I am also indebted to Arne Wold who always had the correct answer to any of my signal processing and Matlab questions and to Are Strandli for help with cumbersome statistics. I would also like to thank Jan Audestad for being a source of inspiration both inside and outside the classroom.

Unfortunately, my biggest inspiration for choosing to focus on side-channel attacks and smart cards, never got the chance to see the end result. I enjoyed many inspiring discussions with the late Torgeir Husum, Norway's Mr. Tempest.

Finally, I want to thank my family and friends, in particular my wife, Susan, for the unconditional support and encouragement during these years. Thank you for not giving up on me and for proof reading all my "interesting" papers. The completion of this work is just as much to your credit as to mine. I wish to thank my children, Guiliana and Bryan, for constantly reminding me of what is important in life.

## Contents

| 1 | Introduction11.1Problem Description/Motivation11.2Research Questions21.3Ethical and Legal Considerations31.4Structure of the Thesis31.5Bibliography3                                                      |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 | Background72.1Microprocessors82.2Electromagnetic Radiation132.3Capturing Electromagnetic Radiation: Measurement Setups172.4Analysis/Application - Side-Channel Attacks262.5Bibliography31                 |

| 3 | Summary of Work353.1Main Research Question363.2Survey and Feasibility Study363.3A New Attack373.4Feature Selection383.5Understanding the Phenomena393.6New Application403.7Future Work413.8Bibliography42 |

| 4 | Summary of Contributions454.1Wireless Covert Channel Attack454.2Feature Selection464.3A New Power Model474.4Reverse Engineering Physical Properties474.5Bibliography47                                    |

| 5 | A Wireless Covert Channel on Smart Cards495.1Introduction495.2Previous Work505.3Wireless Covert Channel Attack515.4Experiment535.5Analysis555.6Conclusion and Future Work565.7Bibliography57              |

| 6 | Analysis of the Wireless Covert Channel Attack596.1Introduction596.2The Wireless Covert Channel Attack606.3Pattern Recognition Approach63                                                                 |

|    | 6.4<br>6.5<br>6.6                                                                                                                                              | Results       Conclusion and Future Work       Bibliography                                                                                                         | . 69                                                                                                                                                                                            |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | AC                                                                                                                                                             | omparison of Multi-class Feature Selection Methods                                                                                                                  | 71                                                                                                                                                                                              |

|    | 7.1                                                                                                                                                            | Introduction                                                                                                                                                        | . 71                                                                                                                                                                                            |

|    | 7.2                                                                                                                                                            | The Phenomenon                                                                                                                                                      | . 72                                                                                                                                                                                            |

|    | 7.3                                                                                                                                                            | Feature Selection Methods                                                                                                                                           | . 75                                                                                                                                                                                            |

|    | 7.4                                                                                                                                                            | Comparison and Discussion                                                                                                                                           | . 78                                                                                                                                                                                            |

|    | 7.5                                                                                                                                                            | Conclusion and Future Work                                                                                                                                          |                                                                                                                                                                                                 |

|    | 7.6                                                                                                                                                            | Acknowledgement                                                                                                                                                     |                                                                                                                                                                                                 |

|    | 7.7                                                                                                                                                            | Bibliography                                                                                                                                                        |                                                                                                                                                                                                 |

|    |                                                                                                                                                                |                                                                                                                                                                     | ~ -                                                                                                                                                                                             |

| 8  |                                                                                                                                                                | dified Template Attack                                                                                                                                              | 85                                                                                                                                                                                              |

|    | 8.1                                                                                                                                                            | Introduction                                                                                                                                                        |                                                                                                                                                                                                 |

|    | 8.2                                                                                                                                                            | Microprocessors                                                                                                                                                     |                                                                                                                                                                                                 |

|    | 8.3                                                                                                                                                            | The Experiment                                                                                                                                                      |                                                                                                                                                                                                 |

|    | 8.4                                                                                                                                                            | Analysis                                                                                                                                                            |                                                                                                                                                                                                 |

|    | 8.5                                                                                                                                                            | Conclusion and Future work                                                                                                                                          |                                                                                                                                                                                                 |

|    | 8.6                                                                                                                                                            | Bibliography                                                                                                                                                        | . 96                                                                                                                                                                                            |

| 9  | Secu                                                                                                                                                           | urity Implications of Crosstalk in Switching CMOS Gates                                                                                                             | 99                                                                                                                                                                                              |

| 2  | 9.1                                                                                                                                                            |                                                                                                                                                                     |                                                                                                                                                                                                 |

|    | 9.2                                                                                                                                                            | Layout Dependent Phenomena                                                                                                                                          |                                                                                                                                                                                                 |

|    | 9.3                                                                                                                                                            | Theoretical Considerations                                                                                                                                          |                                                                                                                                                                                                 |

|    | 9.4                                                                                                                                                            | Security Implications                                                                                                                                               |                                                                                                                                                                                                 |

|    | 9.5                                                                                                                                                            | Simulations                                                                                                                                                         |                                                                                                                                                                                                 |

|    | 9.6                                                                                                                                                            | Conclusion                                                                                                                                                          |                                                                                                                                                                                                 |

|    |                                                                                                                                                                |                                                                                                                                                                     | . 105                                                                                                                                                                                           |

|    | 9.7                                                                                                                                                            | Bibliography                                                                                                                                                        |                                                                                                                                                                                                 |

| 10 |                                                                                                                                                                | Bibliography                                                                                                                                                        | . 104                                                                                                                                                                                           |

| 10 | Non                                                                                                                                                            | Bibliography                                                                                                                                                        | . 104<br><b>107</b>                                                                                                                                                                             |

| 10 | <b>Non</b><br>10.1                                                                                                                                             | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107                                                                                                                                                                    |

| 10 | <b>Non</b><br>10.1<br>10.2                                                                                                                                     | Bibliography       Bibliography         Introduction       Introduction         Crosstalk in Switching CMOS gates       Introduction                                | . 104<br><b>107</b><br>. 107<br>. 108                                                                                                                                                           |

| 10 | <b>Non</b><br>10.1<br>10.2<br>10.3                                                                                                                             | Bibliography       Bibliography         Introduction       Crosstalk in Switching CMOS gates         Non-Invasive Black Box Reverse Engineering Method       Method | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108                                                                                                                                                  |

| 10 | Non<br>10.1<br>10.2<br>10.3<br>10.4                                                                                                                            | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111                                                                                                                                         |

| 10 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5                                                                                                                    | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111                                                                                                                                |

| 10 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5                                                                                                                    | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111                                                                                                                                |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6                                                                                                            | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111                                                                                                                                |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo                                                                                                    | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 108<br>. 111<br>. 111<br>. 111<br><b>113</b>                                                                                                |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1                                                                                            | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113                                                                                                |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2                                                                                    | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 115                                                                                                |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3                                                                            | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 115<br>. 117                                                                              |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4                                                                    | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 115<br>. 117<br>. 118                                                                     |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5                                                            | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 115<br>. 117<br>. 118<br>. 121                                                                     |

|    | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6                                                    | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 115<br>. 117<br>. 118<br>. 121<br>. 125                                                            |

| 11 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7                                            | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 113<br>. 115<br>. 117<br>. 118<br>. 121<br>. 125<br>. 125                                          |

| 11 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>Prep                                    | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 113<br>. 115<br>. 117<br>. 118<br>. 125<br>. 125<br><b>127</b>                                     |

| 11 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>Prep<br>A.1                             | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 115<br>. 117<br>. 118<br>. 125<br>. 125<br><b>127</b><br>. 127                                     |

| 11 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>Prep<br>A.1<br>A.2                      | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 113<br>. 115<br>. 117<br>. 118<br>. 125<br>. 125<br><b>127</b><br>. 129                            |

| 11 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>Prep<br>A.1<br>A.2<br>A.3               | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 113<br>. 115<br>. 117<br>. 118<br>. 121<br>. 125<br>. 125<br><b>127</b><br>. 129<br>. 130          |

| 11 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>Prep<br>A.1<br>A.2<br>A.3<br>A.4        | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 113<br>. 115<br>. 117<br>. 118<br>. 121<br>. 125<br>. 125<br><b>127</b><br>. 129<br>. 130<br>. 132 |

| 11 | Non<br>10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>Layo<br>11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>Prep<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5 | Bibliography                                                                                                                                                        | . 104<br><b>107</b><br>. 107<br>. 108<br>. 108<br>. 111<br>. 111<br><b>113</b><br>. 113<br>. 113<br>. 115<br>. 117<br>. 118<br>. 125<br>. 125<br><b>127</b><br>. 129<br>. 130<br>. 132<br>. 134 |

|    | A.7                | Bibliography                        | <br> | <br> |  | ••• | <br> | <br> | ••• | <br> | <br>. 138               |

|----|--------------------|-------------------------------------|------|------|--|-----|------|------|-----|------|-------------------------|

| B  | <b>Majo</b><br>B.1 | <b>ority Voting</b><br>Bibliography | <br> | <br> |  |     | <br> | <br> |     | <br> | <br><b>141</b><br>. 142 |

| No | omeno              | clature                             |      |      |  |     |      |      |     |      | 143                     |

| In | dex                |                                     |      |      |  |     |      |      |     |      | 145                     |

# List of Figures

| 2.1  | Electromagnetic side-channel leakage from a microprocessor                      | 7  |

|------|---------------------------------------------------------------------------------|----|

| 2.2  | Smart card - a complete computer                                                | 9  |

| 2.3  | Simplified block diagram of Microchip PIC 16F84A.                               | 10 |

| 2.4  | Execution sequence and pipelining of microprocessor PIC 16F84A.                 | 11 |

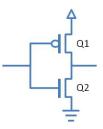

| 2.5  | CMOS inverter.                                                                  | 12 |

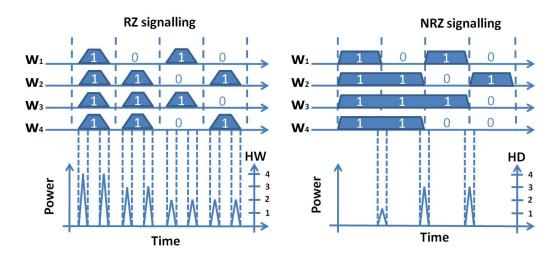

| 2.6  | Power consumption of RZ/NRZ signals related to HW/HD                            | 13 |

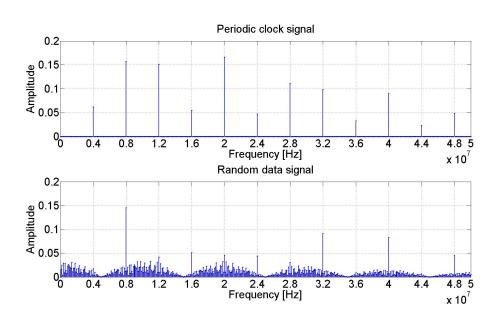

| 2.7  | Estimated electromagnetic spectrum of a periodic and a random signal            | 16 |

| 2.8  | Schematics of the measurement setup                                             | 18 |

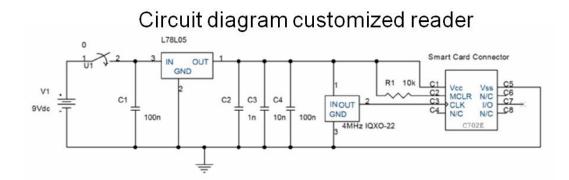

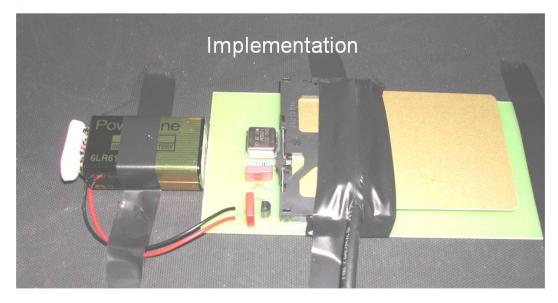

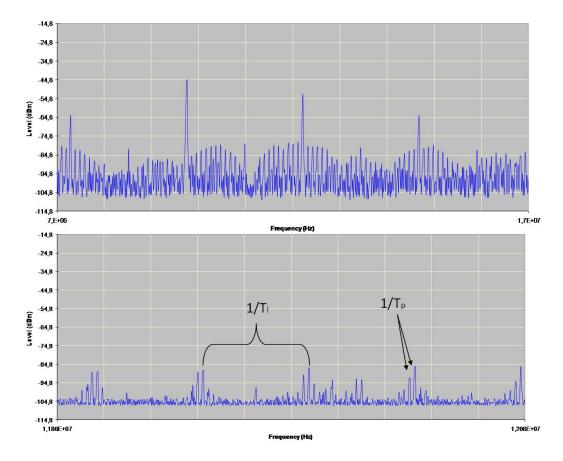

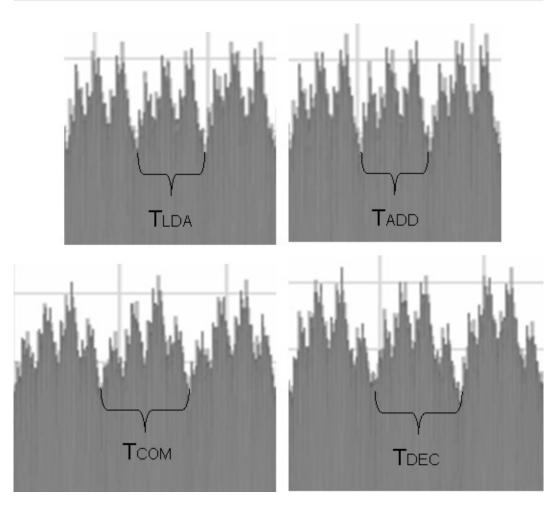

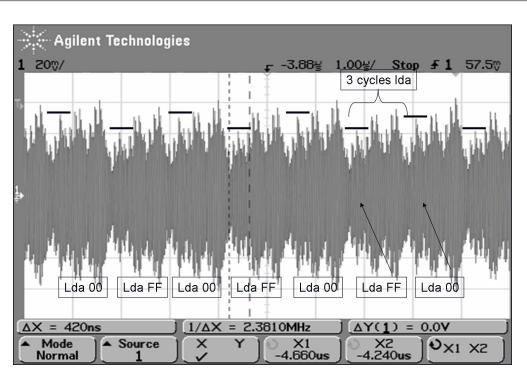

| 2.9  | Customized smart card reader, circuit diagram and implementation                | 19 |

| 2.10 | Solenoid probe.                                                                 | 21 |

|      | Near and far field antennas                                                     |    |

|      | Frequency domain measurements with spectrum analyzer                            |    |

|      | Time domain measurements of repetitive program                                  |    |

|      | Comparison of LDA, DEC, ADD and COM instruction.                                |    |

| 2.15 | SPA trace: argument dependent power consumption                                 | 26 |

| 0.1  |                                                                                 | •  |

| 3.1  | Relationship between research questions and published papers                    | 36 |

| 5.1  | WCCA scenario                                                                   | 52 |

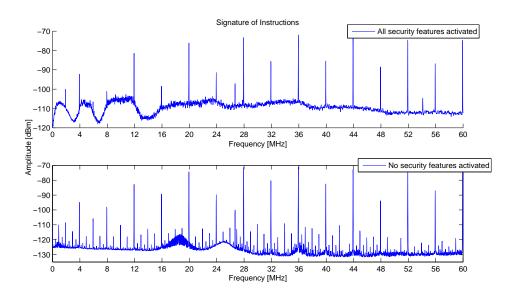

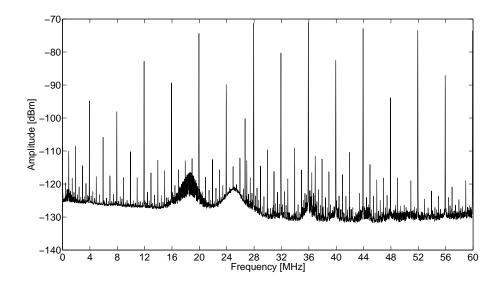

| 5.2  | Average power spectrum density as signatures of instructions                    |    |

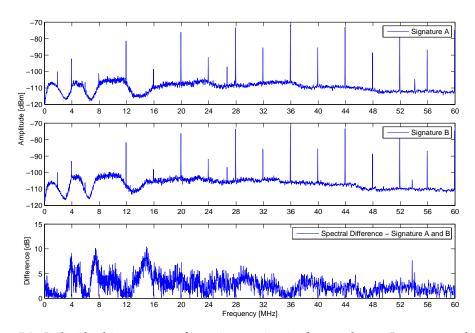

| 5.3  | Individual signatures of two instructions and spectral differences              |    |

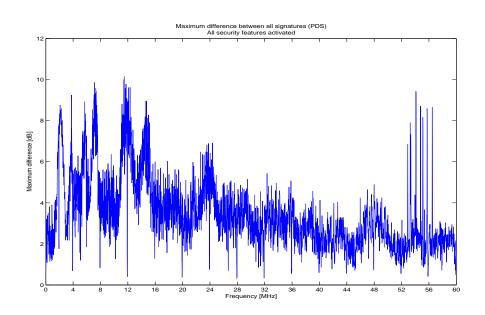

| 5.4  | The largest spectral difference for all combinations of instructions            |    |

|      |                                                                                 | 60 |

| 6.1  | WCCA scenario                                                                   |    |

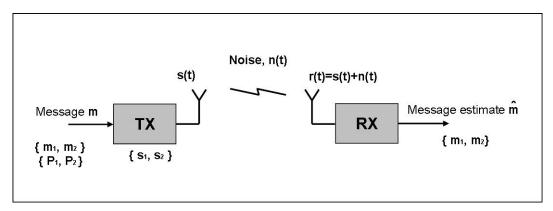

| 6.2  | Basic Binary System                                                             |    |

| 6.3  | 0 0                                                                             |    |

| 6.4  | The design cycle of a pattern recognition system                                |    |

| 6.5  |                                                                                 | 65 |

| 6.6  |                                                                                 |    |

| 6.7  |                                                                                 |    |

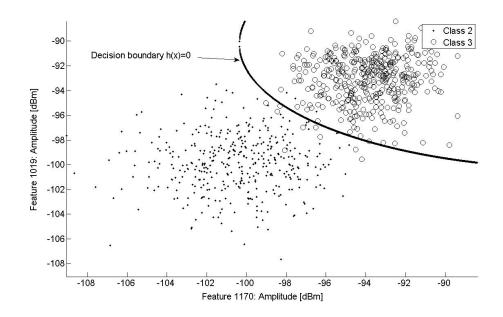

| 6.8  | Two dimensional classification performs better if features are carefully chosen | 68 |

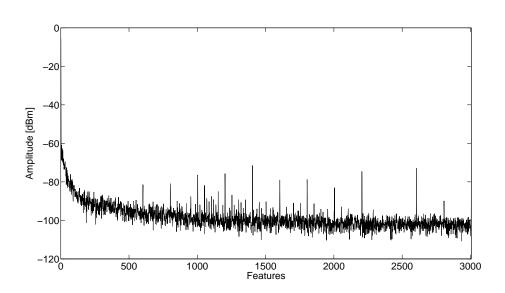

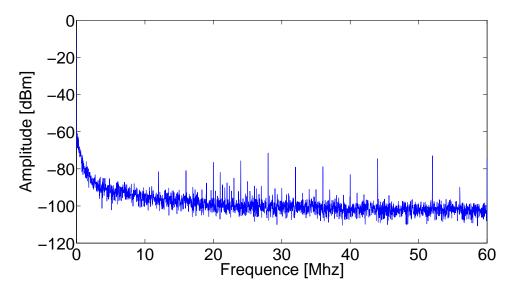

| 7.1  | Unprocessed data: One measurement of instruction BCF                            | 74 |

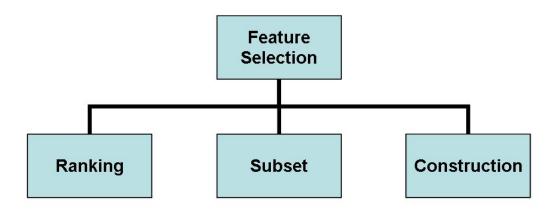

| 7.2  | Feature selection techniques can be divided into three groups                   |    |

| 7.3  |                                                                                 |    |

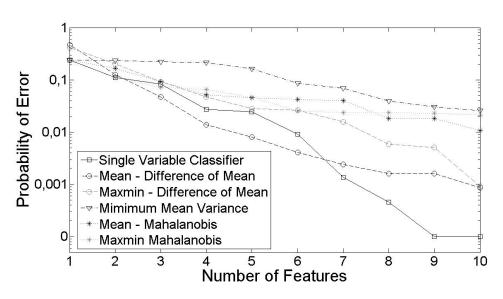

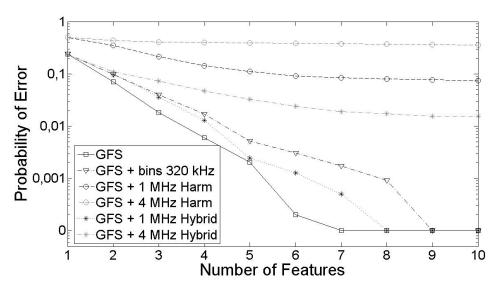

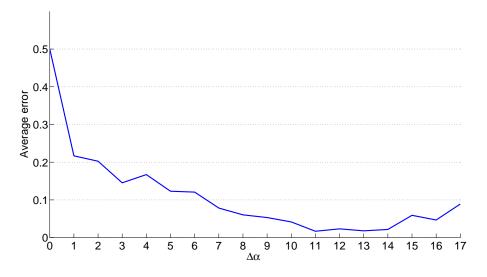

| 7.4  | Error performance of subset based feature selection methods                     |    |

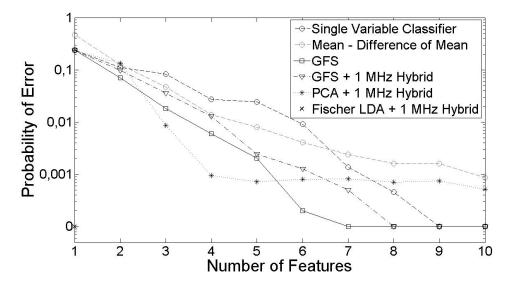

| 7.5  | Comparing the error performance                                                 |    |

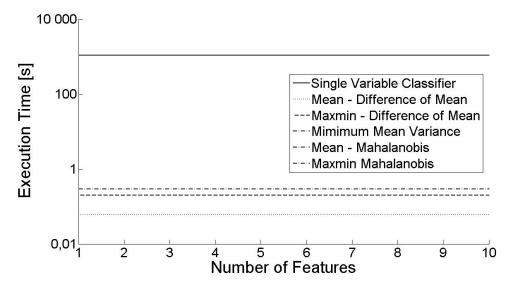

| 7.6  | Execution time of ranking based feature selection methods                       |    |

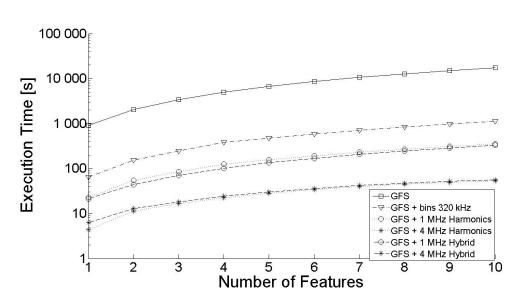

| 7.7  | Execution time of subset based feature selection methods                        |    |

| 0.1  |                                                                                 | 07 |

| 8.1  | Expected emanation from a parallel bus                                          | 86 |

| 8.2  | Execution cycles and pipelining of microprocessor PIC 16F84A.                   | 87 |

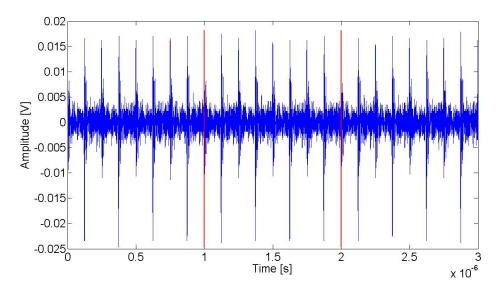

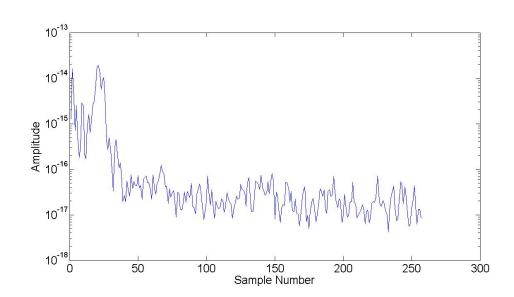

| 8.3  | Signature of three consecutive NOP's                                            | 91 |

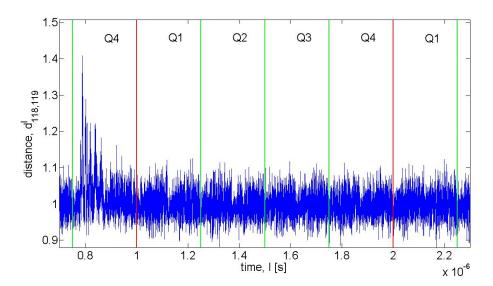

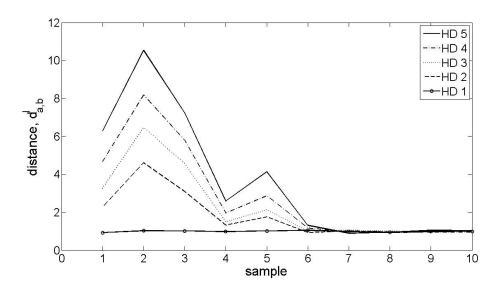

| 8.4  | The distance between NOP number 118 (HW=7) and NOP number 119 (HW=1).           | 92 |

| 8.5  | Frequency domain representation of Q4 (i.e. first half)                         | 93 |

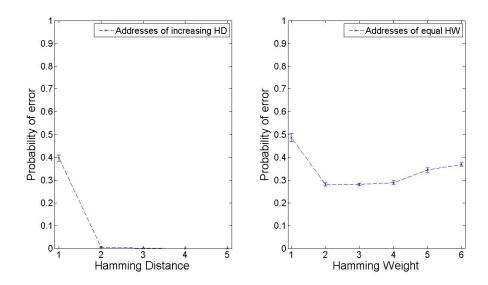

| 8.6<br>8.7 | Probability of error of increasing HD (left) and equal HW (right)                    |

|------------|--------------------------------------------------------------------------------------|

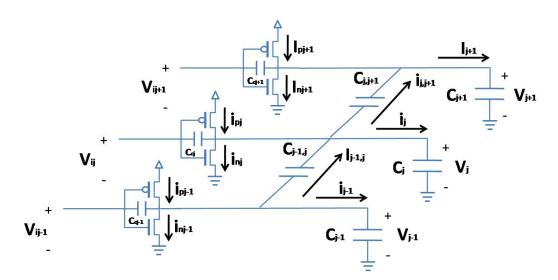

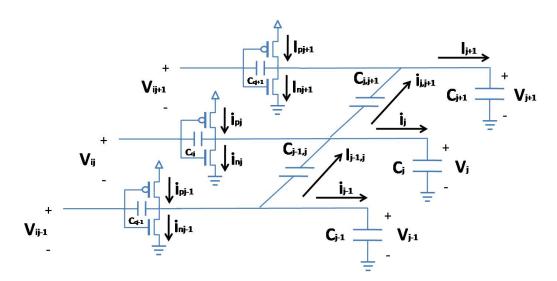

| 9.1        | Simplified model, assuming load and coupling capacitances to be dominant 101         |

| 11.2       | Model of layout dependent phenomena                                                  |

| A.2        | Model of layout dependent phenomena                                                  |

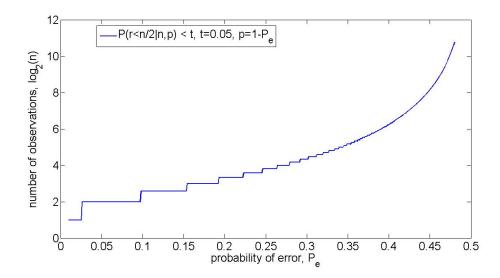

| B.1        | The smallest number of observations as a function of the probability of error 142 $$ |

# List of Tables

| 2.1<br>2.2<br>2.3            | Relationship between power consumption and transitions for a CMOS inverter12Relationship between frequency, wavelength and near/far field border15Example of test code for PIC 16F84A.20                                                                                              |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.1                          | Classifying 5 instructions based on an increasing number of features 69                                                                                                                                                                                                               |

| 7.1<br>7.2<br>7.3            | HD of true and estimated operation sequences73A sample of the instruction executed by the microprocessor75The table shows what frequency [MHz81                                                                                                                                       |

| 9.1<br>9.2                   | Analytic and simulated dissipated energy when considering crosstalk 103<br>Comparing the ability to extract information of different detectors                                                                                                                                        |

| 10.2<br>10.3                 | Transition patterns using the least amount of energy                                                                                                                                                                                                                                  |

| 11.2<br>11.3<br>11.4<br>11.5 | Classes of crosstalk                                                                                                                                                                                                                                                                  |

| A.3                          | Table of transition patterns, energy levels, HD and crosstalk index133Dissipated energy when considering crosstalk for 2 adjacent wires135Analytic and simulated dissipated energy when considering crosstalk136Comparing the performance of different detectors for an 8 wire bus136 |

Chapter 1

### Introduction

Is it secret, is it safe?

GANDALF

#### 1.1 **Problem Description/Motivation**

An increasing number of systems rely upon tamper resistant microprocessor devices, such as smart cards, for security related applications. It is well known that microprocessor devices leak information about their activity through side-channels [14]. Side-channel attacks exploit correlations between the internal sensitive information and unintentionally externally available information such as time [9] and power consumption [10], optical [12], acoustic [5] or electromagnetic radiation (EMR) [15]. These attacks can be invasive or non-invasive such that no traces are left behind.

Side-channel attacks are not new, military and government organizations have supposedly used them for a long time. In 1956, MI5s operation ENGULF used telephone taps to record the sound from Hagelin cipher machines. The sound was used to calculate the settings on the Hagelin machines [23]. The electromagnetic side-channel, when EMR is correlated to sensitive information about a system itself or data handled by the system, has even been given its own codeword; TEMPEST. Side-channel attacks were brought to the public interest in 1985 when Van Eck [22] showed how to eavesdrop on video display units from a considerable distance via EMR. In 1996, Anderson and Kuh published, "Tamper Resistance: A Cautionary Note" [3], which showed that trusting tamper resistant devices can be problematic. That same year, Kocher [9] published his work on exploiting differences in execution time (Timing Attacks). In 1999 Kocher et al. [10] published their ground-breaking power analysis attacks. Simple Power Analysis (SPA) and Differential Power Analysis (DPA) received some attention from, among others, the banking industry, and countermeasures were publicly announced. Power analysis has since then received a lot of attention, with many improved attacks and countermeasures. In 2007 S. Mangard et al. gave out the book, Power Analysis Attack - Revealing the Secret of Smart Cards [14] which is an excellent introduction to the topic, but also summarized development within the field.

In 2000, Quisquater and Samyde [15, 16] applied analysis techniques from SPA and DPA to electromagnetic side-channels, thus introducing electromagnetic analysis (EMA). Gandolfi et al. [8] showed, in 2001, that EMA was not only a theoretical possibility, as cryptographic keys from DES, RSA and the alleged comp128 were successfully retrieved using EMA. In recent years several papers have been published in an ongoing effort to systematically investigate electromagnetic side-channel attacks [1, 2, 6, 8, 11, 13, 15, 16, 17, 18]. The experiments have been extended to some distance from the target, implying that physical access to the target may not be necessary. It has been shown that EMA is at least as powerful as power analysis, and that EMA could circumvent power analysis countermeasures [1, 18]. In 2002, Chari et al. [6], presented the *Template Attacks*, which claims to be close to the theoretical limits of information extraction. There are also papers that further developed these ideas [1, 2, 4, 19]. At USENIX 2002 [17], Quisquater and Samyde described an automatic method to classify instructions, carried out by a simple CISC processor. A neu-

ral network (Kohonen's self organizing maps) was trained to automatically recognize, and thus reverse engineer, executed code based on stored electromagnetic and power signatures. In 2010, Rechberger et al. [7] presented a methodology to reverse engineer executed code on a microprocessor, based on side-channel information only.

Due to the continuing reduction in transistor size (Moore's law), microprocessor technology continues to shrink in size yet increase in power. This development has made possible devices such as smart phones and smart cards. However, as we become more dependent upon these devices and use them increasingly for sensitive information, protecting the device and the information it contains becomes ever more important. The importance of understanding side-channel attacks is therefore higher then ever, as no perfect protection exists. The number of problems are many and side-channel attacks are highly application dependent. Each practical case needs to be studied as the results obtained two years ago might be obsolete today. An ongoing effort to understand what is deducible from sidechannel information is desirable as vulnerabilities, previously found infeasible to exploit, may be within the adversaries reach today.

#### 1.2 **Research Questions**

Any acceleration of electric charges is accompanied by an electromagnetic field [20]. When a microprocessor executes its program, EMR is therefore generated as a consequence of accelerating electric charges associated with transistor transitions (i.e. the power consumption). This work is concerned with the vulnerabilities in which the correlation between EMR and sensitive information presents to a potential adversary. Better risk assessment and security measures can be achieved when the arsenal available to an adversary is better understood. This thesis is concerned with obtaining a better understanding of the origin of EMR, how to capture and represent EMR as well as how EMR can be exploited from a reverse engineering point of view. The overall goal can be stated as:

#### How can electromagnetic radiation be used to reverse engineer microprocessor content?

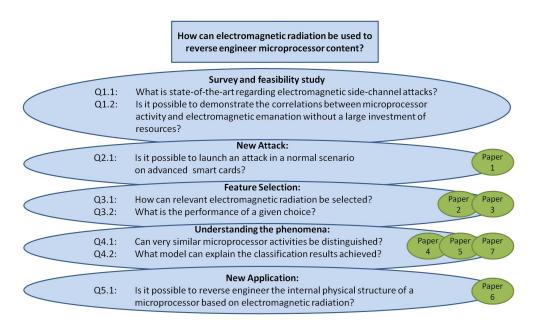

During research the main research question was divided into the following problems, which are explained in further detail in chapter 3:

- Q1.1: What is state-of-the-art regarding electromagnetic side-channel attacks?

- **Q1.2:** Is it possible to demonstrate the correlations between microprocessor activity and electromagnetic radiation without a large investment of resources?

- **Q2.1:** Is it possible to launch an attack in a normal scenario on advanced smart cards?

- **Q3.1:** How can relevant electromagnetic radiation be selected?

- **Q3.2:** What is the performance of a given choice?

- **Q4.1:** Can very similar microprocessor activities be distinguished?

- Q4.2: What model can explain the classification results achieved?

- **Q5.1:** Is it possible to reverse engineer the internal physical structure of a microprocessor based on electromagnetic radiation?

#### **1.3 Ethical and Legal Considerations**

A non-disclosure agreement was signed to get access to modern smart cards with state-ofthe-art security measures. Therefore, special consideration has been taken to ensure that business-confidential information and the identity of vendors are not revealed. In addition, a special focus has been devoted to making sure that classified TEMPEST information, available through the Norwegian Armed Forces and NATO, has not been revealed. All resources used for this thesis are unclassified research papers or textbooks.

Each time somebody publishes an article that reveals security vulnerabilities or introduces a new attack, the following question pops up: "are you not giving the recipe on how to steal information to the wrong guys?". The naive answer is yes, but in my opinion that would be security through obscurity. To pretend there are no vulnerabilities, thus claiming the system is secure is unethical. As an example, T. Tjøstheim wrote that [21]: *Norwegian online banks have supported secrecy, fearing that the discovery of vulnerabilities could have economic consequences or cause a loss of reputation*. The Norwegian online banks are not unique. In light of this a better question is: "Are we now obligated to publish findings that bring vulnerabilities out in the open?" This will facilitate, and in some cases force, more secure systems, and is far better than sticking ones head in the sand, hoping nobody discovers any security vulnerabilities. The chances are, the bad guys know about the vulnerabilities already.

#### **1.4** Structure of the Thesis

The rest of the thesis is organized as follows: Chapter 2 presents necessary theory to understand the contributions of this thesis. This includes, basic knowledge of microprocessor technology, the origin and nature of EMR, practical laboratory knowledge and analysis techniques. Chapter 3 presents a summary of the work done for this thesis and shows the relationship between research questions and published papers. Future work is also found in chapter 3. Chapter 4 gives a summary of the contributions of this thesis. In chapter 5-11 the 7 research papers, constituting the main body of this thesis, are found. State-of-the-art is not included, as this is found in each contributing paper.

#### 1.5 Bibliography

- [1] AGRAWAL, D., ARCHAMBEAULT, B., RAO, J., AND ROHATGI, P. The em sidechannel(s). In *Cryptographic Hardware and Embedded Systems - CHES* (2003), vol. 2523 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 29–45. Available from: http://dx.doi.org/10.1007/3-540-36400-5\_4. 1, 15, 17, 19, 23, 37, 50, 71, 85, 88, 113, 127

- [2] AGRAWAL, D., RAO, J., AND ROHATGI, P. Multi-channel attacks. In *Cryptographic Hardware and Embedded Systems CHES* (2003), C. Walter, e. Ko, and C. Paar, Eds., vol. 2779 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 2–16. Available from: http://dx.doi.org/10.1007/978-3-540-45238-6\_2. 1, 17, 37, 50, 88

- [3] ANDERSON, R., AND KUHN, M. Tamper resistance: A cautionary note. In *In Proceed*ings of the 2nd USENIX Workshop on Electronic Commerce (WOEC 96 (1996). 1, 50

- [4] ARCHAMBEAU, C., PEETERS, E., STANDAERT, F. X., AND QUISQUATER. Template attacks in principal subspaces. In *Cryptographic Hardware and Embedded Systems - CHES* (2006), vol. 4249 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 1–14. 1, 30, 39, 72, 91

- [5] ASONOV, D., AND AGRAWAL, R. Keyboard acoustic emanations. In *IEEE Symposium* on Security and Privacy (may 2004), pp. 3 – 11. 1

- [6] CHARI, S., RAO, J., AND ROHATGI, P. Template attacks. In *Cryptographic Hardware and Embedded Systems CHES* (2003), vol. 2523 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 51–62. Available from: http://dx.doi.org/10.1007/3-540-36400-5\_3. 1, 8, 28, 29, 30, 37, 39, 40, 45, 46, 50, 71, 72, 85, 86, 88, 89, 91, 94, 95, 96, 99, 113, 127, 132

- [7] EISENBARTH, T., PAAR, C., AND WEGHENKEL, B. Building a side channel based disassembler. In *Transactions on Computational Science X* (2010), vol. 6340 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 78–99. Available from: http://dx.doi.org/10.1007/978-3-642-17499-5\_4.2

- [8] GANDOLFI, K., MOURTEL, C., AND OLIVIER, F. Electromagnetic analysis: Concrete results. In *Cryptographic Hardware and Embedded Systems - CHES* (2001), vol. 2162 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 251–261. Available from: http://dx.doi.org/10.1007/3-540-44709-1\_21. 1, 7, 15, 17, 21, 26, 37, 85, 113, 127

- [9] KOCHER, P. Timing attacks on implementations of diffie-hellman, rsa, dss, and other systems. In Advances in Cryptology (1996), vol. 1109 of Lecture Notes in Computer Science, Springer Berlin / Heidelberg, pp. 104–113. Available from: http://dx.doi.org/ 10.1007/3-540-68697-5\_9. 1, 26, 50, 71, 88

- [10] KOCHER, P., JAFFE, J., AND JUN, B. Differential power analysis. In *Advances in Cryptology* (1999), vol. 1666 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 388–397. Available from: http://dx.doi.org/10.1007/3-540-48405-1\_25. 1, 7, 8, 26, 27, 45, 47, 50, 71, 76, 85, 88, 99, 107, 113, 127

- [11] KUHN, M., AND ANDERSON, R. Soft tempest: Hidden data transmission using electromagnetic emanations. In *Information Hiding* (1998), vol. 1525 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 124–142. Available from: http://dx.doi.org/10.1007/3-540-49380-8\_10. 1,7,37,46,51

- [12] KUHN, M. G. Optical time-domain eavesdropping risks of crt displays. In IEEE Symposium on Security and Privacy (2002), pp. 3 18. 1

- [13] KUHN, M. G. Compromising Emanations: Eavesdropping Risks of Computer Displays. Technical report, University of Cambridge, 2003. UCAM-CL-TR-577. 1, 25, 37

- [14] MANGARD, S., OSWALD, E., AND POPP, T. Power Analysis Attack Revealing the Secret of Smart Cards. Springer, 2007. 1, 7, 11, 12, 13, 16, 22, 26, 27, 30, 40, 47, 85, 87, 99, 107, 108, 113, 114, 127

- [15] QUISQUATER, J.-J., AND SAMYDE, D. A new tool for non-intrusive analysis of smart cards based on electromagnetic emissions: the sema and dema methods. *Eurocrypt rump session* (2000). 1, 37, 50, 88

- [16] QUISQUATER, J.-J., AND SAMYDE, D. Electromagnetic analysis (ema): Measures and counter-measures for smart cards. In *Smart Card Programming and Security* (2001), vol. 2140 of *Lecture Notes in Computer Science*, Springer Berlin / Heidelberg, pp. 200–210. Available from: http://dx.doi.org/10.1007/3-540-45418-7\_17. 1, 7, 15, 16, 17, 21, 26, 37, 50, 88

- [17] QUISQUATER, J.-J., AND SAMYDE, D. Automatic code recognition for smart cards using a kohonen neural network. In *Conference on Smart Card Research and Advanced Application Conference* (Berkeley, CA, USA, 2002), USENIX Association. Available from:

http://portal.acm.org/citation.cfm?id=1250988.1250994. 1, 8, 37, 39, 45, 50, 85, 86, 88, 94, 96, 99, 113, 127

- [18] RAO, J., ROHATGI, AND PANKAJ. Empowering side-channel attacks. Tech. rep., IBM T.J. Watson Research Center, 2001. 1, 7, 16, 17, 37, 50, 88

- [19] RECHBERGER, C., AND OSWALD, E. Practical template attacks. In Information Security Applications (2005), vol. 3325 of Lecture Notes in Computer Science, Springer Berlin / Heidelberg, pp. 440–456. Available from: http://dx.doi.org/10.1007/ 978-3-540-31815-6\_35. 1, 30, 91, 93

- [20] SKITEK, G., AND MARSHALL, S. *Electromagnetic Concepts and Applications*. Prentice Hall, 1987. 2, 14

- [21] TJØSTHEIM, T. Security analysis of electronic voting and online banking systems. Ph.D. thesis, The University of Bergen, Department of Informatics, 2007. 3

- [22] VAN ECK, W. Electromagnetic radiation from video display units: An eavesdropping risk? Computers & Security 4, 4 (1985), 269 – 286. Available from: http://www. sciencedirect.com/science/article/pii/016740488590046X. 1, 50

- [23] WRIGHT, D. Spycatcher. Viking Penguin Inc, 1987. 1

Chapter 2

### Background

If we knew what it was we were doing, it would not be called research, would it?

ALBERT EINSTEIN

A microprocessor has a functional activity which is to transform a set of input bits to a set of output bits. It is well known that the functional activity also generates electromagnetic radiation (EMR) as a function of the power consumption of the microprocessor [13, 18, 29, 32]. This is concerning, from an information security point of view, if the EMR is correlated to sensitive information about, or handled by the microprocessor. Compromise of sensitive information is then at risk if an adversary is able to capture and analyze the EMR, known as the electromagnetic side-channel.

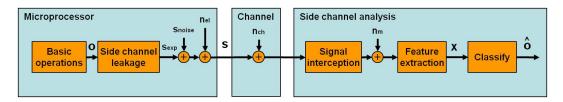

Electromagnetic side-channel attacks can be modeled as seen in Figure 2.1. The microprocessor executes it program using as set of basic operations (e.g. transfer, arithmetic, logic and shift), usually controlled by a "square wave" clock. A sequence of basic operations necessary to execute a program is called an execution sequence, o. The majority of the power consumption, and associated EMR, during an execution sequence is related to the number of gates that change state [20]. This is determined by what bit values are processed and moved by the microprocessor. The EMR from each basic operation is, therefore, a function of the instruction (opcode and operand), the data, the address in memory and the prior state (upstate) of the microprocessor. This relationship can be exploited by an adversary to deduce the content of program or data memory, otherwise kept secret. The adversary may have knowledge of, or even be able to, choose part of the execution sequence in order to reveal specific details (e.g. run a known cryptographic algorithm for an unknown value of the cryptographic key [17] or alternate the execution of two different instructions [10]). The emitted electromagnetic signal, s, in Figure 2.1 will have a signal part and a noise part. The signal part,  $s_{exp}$ , is due to power consumption during gate transitions related to handling sensitive information. The noise part  $s_{noise}$  is due to power consumption during gate transitions irrelevant to handling the sensitive information. Any electronic device will also be subject to electronic noise,  $n_{el}$  [20].

Side-channel analysis requires interception of EMR subject to channel noise,  $n_{ch}$ , and measurement noise,  $n_m$ . Properties (features), x, of the intercepted signal are then extracted

Figure 2.1: Electromagnetic side-channel leakage from a microprocessor.

and used to compute an estimate of the execution sequence,  $\hat{o}$ . The estimated execution sequence, together with known or chosen memory content, can then be used to reveal sensitive information, e.g. the content of program or data memory. This process can be viewed as a pattern classification problem [9]. Based on properties, x, of the intercepted EMR, predict the execution sequence which took place. Side-channel attacks have adapted a range of different classification approaches, such as visual inspection [17], difference of means or correlation coefficient [17], Bayesian classifier [8] or neural networks [30].

EMR only pose a security risk if sensitive information is correlated to EMR and the adversary can intercept and extract the information. In order to understand how EMR can reveal sensitive information, it is necessary to understand how basic microprocessor operations and execution sequences are correlated to the power consumption. This is the topic of section 2.1. Section 2.2 talks about how EMR is generated and how it is related to power consumption. The measurement setup necessary to intercept EMR is introduced in section 2.3 and section 2.4 introduce relevant analysis techniques.

#### 2.1 Microprocessors

The purpose of this chapter is to get an understanding of how a microprocessor executes its program and how this is related to the power consumption. This will help understand how sensitive information handled by a microprocessor can be compromised through measurements of the power consumption.

It is difficult and resource-demanding for an adversary to capture and analyze the power consumption of the microprocessor every waking moment. In addition, it is likely to be unnecessary as correlations between sensitive information and power consumption probably are found at specific time instances. Detailed knowledge of the program and how it is executed by the microprocessor, i.e. the execution sequence, is then important to identify the time instance of relevant activity. The basic principles of a general microprocessor are covered first, followed by a detailed explanation of how a microprocessor smart card works. This introduction is based on the architecture of the Goldcard smart card, containing Microchips PIC 16F84A microcontroller, as it is easily available without a non-disclosure agreement and principles are easily generalized to more advanced cards used in security sensitive applications (e.g. mobile phones, travel documents, electronic wallets, credit cards and pay TV). Finally, an introduction to power consumption associated with bit-level microprocessor activity is given.

#### 2.1.1 General microprocessor

A microprocessor typically includes memory (program memory, data memory), Central Processing Unit (CPU), I/O and buses (data, program, control). The CPU is responsible for controlling the operation of the device by fetching, decoding and executing instructions, one by one. A set of instructions is called a program and is stored in program memory. Each instruction consist of opcode and operand. The opcode specifies the instruction type and the operands the operation of the instruction, e.g. memory location of data and where to store the result. The CPU use a set of basic operations such as: Transfer, arithmetic, logic and shift. Transfer is used to move data on buses between memory locations. Arithmetic, logic and shift operations are done by the Arithmetic Logical Unit (ALU) of the CPU. The ALU can perform arithmetic and boolean function between a working register and memory locations. The execution of basic operations (i.e. execution sequence) is usually controlled by a square wave clock. How fast the microprocessor can perform the tasks instructed by the instructions, depend on the clock and if parallel activities can take place. In traditional von Neumann architecture [23] data and program are fetched over the same bus. In Harvard architecture [23] separate buses are used, allowing data and instructions to be fetched simultaneously, thus increasing the speed of the microprocessor. This also makes

#### 2.1 MICROPROCESSORS

Figure 2.2: Smart card - a complete computer.

it possible to have data and instructions of different lengths, allowing for more efficient use of the program memory. This is important in resource limited devices, such as smart cards.

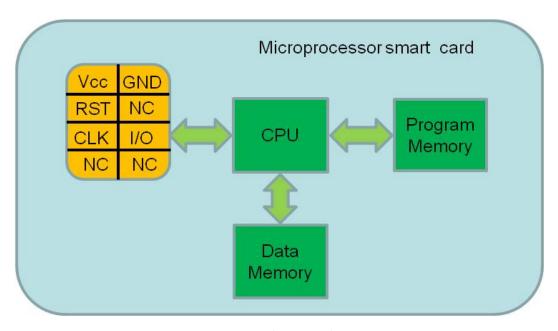

#### 2.1.2 Smart Cards: Specific processor

Microprocessor smart cards are complete computers embedded in a small chip (Figure 2.2), and typically contain CPU, program and data memory (RAM, ROM, EEPROM), I/O interface and buses. They are typically used in security sensitive applications and sometimes have sensors, security logic and specialized coprocessors for handling cryptographic algorithms [31]. The electrical connections are also shown in Figure 2.2. A smart card usually have 8 contacts. ISO 7816-2 specifies the designation and function of the contacts [31]. Two connectors are reserved for auxiliary contacts and one has gone out of use (NC). The other connectors are I/O for serial communication,  $V_{cc}$  for power supply, CLK for clock input, GND for ground and RST for reset input.

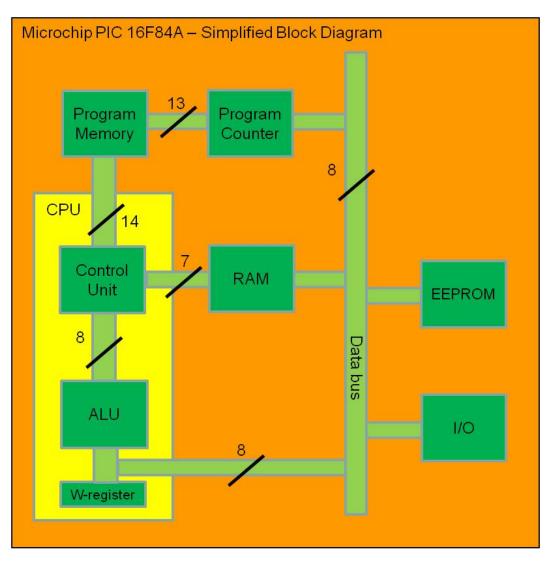

The Goldcard is a microprocessor smart card which contains an 8 bit Microchip PIC 16F84A special-purpose microprocessor (i.e. microcontroller), which handles clock speeds up to 20 MHz. A simplified block diagram of PIC 16F84A is seen in Figure 2.3. The CPU consists of a Control Unit (CU), ALU and a working register (w-register). The program memory can hold 1024 14bits instructions. 68 bytes of RAM and 64 bytes of EEPROM is also available. A Harvard architecture with separate 8 bit data and 14 bit program bus allows some parallel activities to take place. There are 35 instructions available grouped into three basic categories: byte-oriented operations, bit-oriented operations and literal and control operations. For details, see Microchips Reference Manual [22].

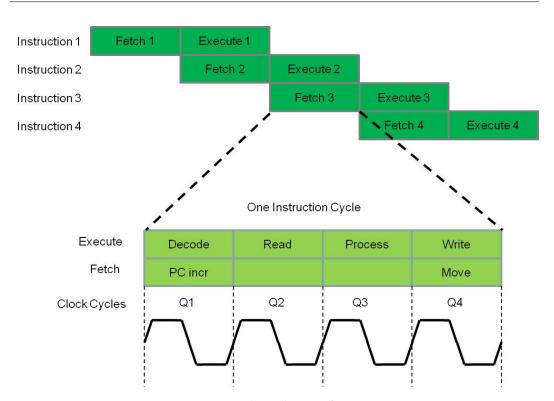

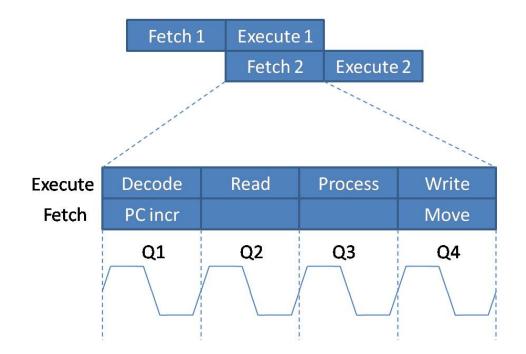

Microchip PIC 16F84A executes one instruction in four quadrature clock cycles (Q cycles), which have a period equal to the clock provided through the CLK connection (Figure 2.2). A two-stage pipeline is used to fetch the next instruction while the current instruction is executed (Figure 2.4). The microprocessor executes one instruction in each instruction cycle, except for program branches that require two cycles. Clock cycle 1 (Q1) is used to decode the current instruction in CU's instruction register. This may involve setting an address on the 7 bit address bus to RAM, setting an 8 bit literal to the ALU or setting up

#### 2. BACKGROUND

Figure 2.3: Simplified block diagram of Microchip PIC 16F84A.

control lines to ensure correct processing as specified by the opcode. Q1 is also used to increment the program counter, which points to the next instruction in program memory. Clock cycle 2 (Q2) is the operand read cycle where data memory is read, e.g. transfer data from RAM at the address provided by CU, to the ALU via the 8 bit data bus. Clock cycle 3 (Q3) is used to process data in the ALU as specified by the opcode (i.e. control signals set by CU). This could be addition, subtraction, shift or logic operations. Finally, clock cycle 4 (Q4) is used as the destination write cycle. Results of ALU operations in Q3 are either written to the working register or back to the memory location used in Q2. Q4 is also used to move the next instruction from program memory to the CU's instruction register. One instruction cycle is then complete and the next cycle can start.

Such detailed knowledge of the execution sequence can be used to identify time instances of basic microprocessor operations (e.g. transfer) of interest. An adversary interested in the opcode or memory location of instructions should focus on Q1. Correlation between power consumption and one particular byte of data, may be strongest during the read cycle (Q2) or the write cycle (Q4). Notice that in Q4 the parallel activities of moving

Figure 2.4: Execution sequence and pipelining of microprocessor PIC 16F84A.

the next instruction into the CU will add to the noise  $s_{noise}$  (Figure 2.1) and make analysis harder. Correlations between power consumption and processing data (e.g. XOR of cryptographic key) in ALU is expected to be strongest in Q3. This information should only be used to initiate the analysis. There may well be correlations that do not follow these simple guidelines. For other microprocessor technologies, the execution cycle itself can provide information, e.g. a Motorola microcontroller has 3 or 4 clock cycles in the instructions cycle, depending on the opcode.

#### 2.1.3 Power Consumption

The purpose of this chapter is to get an understanding of the power consumption associated with basic microprocessor operation, in particular, bit-level transfer operations on internal buses. This introduction is largely based on the book, Power Analysis Attacks [20] in which further detail can be found.

Digital circuits, such as ASIC's, FPGA's and microprocessors, are built using logic cells. Logic cells can be implementations of boolean function like inversion, NAND and XOR and are referred to as combinational cells as their outputs are logical combination of the inputs. Other types of logic cells are flip-flops and registers. These are called sequential cells, and the output depend on the input, preceding inputs or on their initial state. Combinational cells and sequential cells are used to build functionality of higher complexity, such as adders, counters and state machines. These building blocks are then used to build systems (e.g. microprocessor). All logic cells are implemented using transistors. There are many different types of transistors, however, the majority of cells use complementary metal-oxide semiconductor (CMOS) technology [27].

A precise simulation of the power consumption of digital circuits can be obtained using analog circuit simulators like PSpice [7]. This requires a netlist of all transistors, the con-

Figure 2.5: CMOS inverter.

nections between them and parasitic elements. The precision of the simulation depends on how accurate the parasitic elements are modeled. Simplifications are usually done to reduce the complexity. The lumped-C model is common, where all parasitic elements are lumped together as single capacitance at the output of a cell [20].

It is also possible to simulate the power consumption at a logic level. A netlist of logic cells and the connection between them allows simulation of the transitions taking place in the circuit. This can then be mapped to the power consumption by the circuit. Both these methods require detailed knowledge to make the netlits, that may not be available to an attacker. However, devices such as the microprocessor have components (buses, ALU, memory) that behave in a predictable way (e.g. execution sequences and basic operations). For an attacker it may be enough to map the power consumption to bit-level activities of the device, and the absolute power consumption may not be relevant.

The CMOS inverter is often used to explain the power consumption in CMOS logic cell. It is representative for other logic cells, because they are all based on the same principle of pull-up and pull-down networks. The CMOS inverter uses two transistors; one p-channel (Q1) and one n-channel (Q2) MOSFET [27] as seen in Figure 2.5.

There are 4 cases to consider. When the input is high (logic 1), Q1 is off and Q2 is on. This connects the output to ground. If the output was previously high a current pulse occurs as the output is discharged through Q2, resulting in a power consumption  $P_{10}$ . If the output was already low there is no discharge, but only a small static power consumption,  $P_{00}$ . When the input is low, Q1 is on and Q2 is off. This connects the output to the power supply. If the output was previously low a current pulse occurs as the output charges up through Q1, resulting in a power consumption  $P_{01}$ . If the output was already high there is a small static power consumption,  $P_{11}$ . In the case of a transition on the output of the inverter, the power consumption will be much larger as a result of the added power associated with charging up or discharging the output. This is called dynamic power consumption [20]. The results are summarized in table 2.1.

Notice that the static power consumption is very small and usually neglected, such that  $P_{00} = P_{11} \approx 0$ . According to [20], the leakage current is in the range of 1pA. Since the majority of the power consumption occurs when there is a transition between logic one

Table 2.1: Relationship between power consumption and transitions for a CMOS inverter [20].

| Transition        | Power Consumption | Туре               |

|-------------------|-------------------|--------------------|

| $0 \rightarrow 0$ | $P_{00}$          | static             |

| $0 \rightarrow 1$ | $P_{01}$          | static and dynamic |

| $1 \rightarrow 0$ | $P_{10}$          | static and dynamic |

| $1 \rightarrow 1$ | $P_{11}$          | static             |

and zero, it can be argued that it is the number of changes in logic value that determines the power consumption. It is also common to assume the dynamic power for discharge and charging the output is equal, such that  $P_{01} = P_{10}$ . This is the background for two common power models: The Hamming Weight (HW) and Hamming Distance (HD) model.

HW is simply the number of bits set to one, and HD is the number of bits that are different. For two binary values X and Y, both with length l, Hamming distance is given by  $HD(X,Y) = \sum_{i=1}^{l} X_i \oplus Y_i$ . The HD model can be used to describe the power consumption when consecutive data are known. This is often the case for buses and registers of a microprocessor. The HW model is used if no consecutive data is available and is therefore, in general, not very well suited for CMOS circuits. However, in [20] it is stated that "..., in practice the HW of a data value is usually not completely unrelated to the power consumption that is caused by the processing of this value."

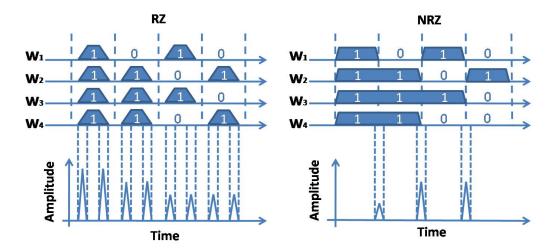

Another explanation can be illustrated by considering a parallel bus (e.g. the data bus of a microprocessor), with 4 wires ( $w_1, \dots, w_4$ ) transmitting data simultaneously. Current is drawn by each bus wire during the rising and falling edge of each logic "1". The dynamic power consumption will be proportional to how many wires conduct current, as illustrated in Figure 2.6. On the right side of Figure 2.6 the "square wave" signal has equal duration to the bit interval (non-return to zero - NRZ). The power consumption is then proportional to the HD of the data. On the left side, the duration of the "square wave" signal is shorter than the bit interval (return to zero - RZ). The power consumption is then proportional to the HW of the data. Pre-charge bus is one type of RZ.

To summarize: The power consumed by basic microprocessor (CMOS based) operation is proportional to bit values handled by the device, which is a function of the instruction (opcode and operand), the data, the address in memory and the prior state (upstate) of the microprocessor.

#### 2.2 Electromagnetic Radiation

Electromagnetic radiation (EMR) is energy propagating through space. This energy has both a wave-like and a particle-like behavior that depends on the wavelength. EMR of different wavelengths are known by their more familiar names: radio waves, microwaves,

Figure 2.6: The power consumption of RZ signal types (left) is proportional to the HW of the data. The power consumption of NRZ signal types (right) is proportional to the HD of the data.