# GPU Accelerated NIDS Search

Kristian Nordhaug

Master's Thesis

Master of Science in Information Security

30 ECTS

Department of Computer Science and Media Technology

Gjøvik University College, 2012

Avdeling for informatikk og medieteknikk Høgskolen i Gjøvik Postboks 191 2802 Gjøvik

Department of Computer Science and Media Technology Gjøvik University College Box 191 N-2802 Gjøvik Norway

# GPU Accelerated NIDS Search

Kristian Nordhaug

2012/07/01

# **Abstract**

Network Intrusion Detection System (NIDS) analyzes network traffic for malicious activities and report's findings from events that intend to compromise the security of the computers and other equipment. NIDS looks into both headers and payloads of the network packets to identify possible intrusions.

NIDS models that only use Central Processing Units (CPU) such as the IDS Snort, have in the last decade struggled with the CPU as the bottleneck of the system. Network traffic has been increasing more rapidly than the clock-speed of CPUs. The CPUs have gained more cores, but lack implementation for utilizing multi-core CPUs and are unable to cope with the bandwidth throughput we are starting to see in high-tech network infrastructure that they are set to protect. The massive flows of data packets overload the NIDS and lead to packet loss which makes them pass by unchecked for malware and intrusion attempts, increasing the false-negative rate. The main cause of this is the *network packet inspection* module in the detection engine of the NIDS. The detection engine consists of numerous functions and ultimately contains an algorithm for *string searching*. This thesis will focus on accelerating the NIDS by parallelizing this algorithm.

In the recent years modern GPUs have evolved from being a tool that only displays highend graphics for games, to be used for general-purpose scientific and engineering computing across a range of platforms [35]. GPU computing is the short term used when ordering the GPU to take over and accelerate the computationally-intensive calculations normally done by the CPU, and instead let the CPU take care of the more sequential parts of the application. They then work together solving tasks in a heterogeneous co-processing computing model. Using Graphics Processing Units (GPU) for general-purpose scientific and engineering computing has grown exponentially the last few years. This has happened mostly from the work Nvidia has put into their CUDA platform and programming model. Some of the most common areas for use of GPU is fluid dynamics, seismic processing, molecular dynamics, computational chemistry, finance and supercomputing. Programs need to be specifically designed to run optimized on a GPU, and special programming APIs have been designed explicitly for GPU computing. The most well known ones are CUDA and OpenCL. In the recent year's modern GPUs have evolved from being the tool that displays high-end graphics for games, to be the tool used in general-purpose scientific and engineering computing across a range of platforms.

The goal of this project was to harness the power within GPUs and use it to accelerate NIDS such as Snort, by using CUDA technology. Several papers have been published on the topic of GPU acceleration, however only a handful of them targeted NIDS with varying results. We believe this can be improved dramatically by further research in how different hardware components interact and how to exploit the components and their APIs in new ways for creating high-performance algorithm solutions.

We present our implementations of known string search algorithms programmed in C++ and CUDA, with analysis of these algorithms and conclude with contributions from our experiments

and theoretical analysis.

# Sammendrag

NIDS analyserer nettverkstrafikk for ondsinnede aktiviteter og rapporterer funn fra hendelser som har til hensikt å kompromittere sikkerheten til datamaskiner og annet utstyr. En NIDS ser inn både header og payload av nettverkspakker og identifiserer mulige inntrengere i systemer.

NIDS modeller som kun benytter hovedprosessoren (CPU) som produktet Snort, har i det siste tiåret kjempet med CPU som flaskehalsen i systemet. Nettverks trafikken har økt raskere enn klokke-hastigheten til CPU. Selv om CPU har fått flere kjerner, mangler det implementering for å utnytte multi-core prosessorer i NIDS De klarer ikke lenger å takle mengden av trafikk gjennomstrømming vi ser i high-tech nettverksinfrastruktur der de er satt for å beskytte. De massive strømmene av datapakker overbelaster NIDS, som gjør at de krysser forbi uten å bli sjekket for malware og innbruddsforsøk. Den viktigste årsaken til dette er modulen for *inspeksjon av nettverk pakker* i deteksjon motoren på NIDS. Deteksjons motoren består av mange funksjoner og inneholder en algoritme for *streng søk*. Denne oppgaven vil fokusere på å aksellerere NIDS ved å parallelisere denne algoritmen.

GPU databehandling er slang uttrykket for å bruke GPU til å overta og aksellerere intensive beregninger, normalt gjort av CPU. CPU vil istedet få frihet til å ta seg av den mer sekvensielle delen av søknaden. De arbeider deretter sammen for å løse oppgavene i en heterogen coprosessor databehandlings modell. Bruken av Graphical Processing Units (GPU) for generell vitenskapelig og teknisk databehandling har vokst eksponentielt de siste årene. Dette har skjedd hovedsakelig på grunn av arbeidet Nvidia har lagt inn i sin CUDA plattform og programmerings modell. Noen av de vanligste områdene for bruk av GPU er veskedynamikk, seismisk prosessering, molekylær dynamikk, beregningsorientert kjemi, økonomi og supercomputing. Programmer må være spesielt designet for å kjøre optimalisert på en GPU, og spesielle programmerings APIer har blitt designet eksplisitt for GPU databehandling. De mest kjente er CUDA og OpenCL. I de siste årene har moderne GPUer utviklet seg fra å være verktøyet som viser high-end grafikk for spill, til å være et verktøy som brukes i generell vitenskapelig og teknisk databehandling på en rekke plattformer.

Målet med dette prosjektet er å utnytte kraften i GPU og bruke den til å akselerere NIDS som Snort, ved hjelp av CUDA-teknologi. Flere artikler er publisert om temaet GPU-akselerasjon, men bare en håndfull målrettet mot NIDS, med varierende resultater. Vi tror dette kan forbedres dramatisk ved videre forskning på hvordan ulike maskinvarekomponenter samhandler, og hvordan man best utnytter komponentene og deres APIer på nye måter for å skape nye høyder for ytelse i algoritmiske løsninger.

Vi presenterer våre implementasjoner av kjente streng søk algoritmer, programmert i C++ og CUDA, samt analyse av disse algoritmene og konluderer med bidrag fra våre eksperimenter og teroretiske analyse.

# **Contents**

| Ab  | strac   | tii                                                                            |

|-----|---------|--------------------------------------------------------------------------------|

| Sa  | mme     | ndrag                                                                          |

| Co  | nten    | ts                                                                             |

| Lis | st of I | Figures                                                                        |

| Lis | st of T | Tables                                                                         |

| Pr  | eface   | xii                                                                            |

| 1   | Intro   | oduction                                                                       |

|     | 1.1     | Problem Statement                                                              |

|     | 1.2     | Contributions                                                                  |

|     | 1.3     | Choice of Methods                                                              |

|     | 1.4     | Outline                                                                        |

| 2   | State   | e of the Art                                                                   |

|     | 2.1     | Related work                                                                   |

|     |         | 2.1.1 Summary                                                                  |

|     | 2.2     | Technical Background                                                           |

|     |         | 2.2.1 Graphical Processing Units                                               |

|     |         | 2.2.2 CUDA                                                                     |

|     |         | 2.2.3 NIDS                                                                     |

|     |         | 2.2.4 Algorithms                                                               |

| 3   | Imp     | lementations & Results                                                         |

|     | 3.1     | Scope                                                                          |

|     | 3.2     | Limitations                                                                    |

|     | 3.3     | Lab Environment                                                                |

|     | 3.4     | Experiment #1                                                                  |

|     |         | 3.4.1 Execution                                                                |

|     |         | 3.4.2 Analysis                                                                 |

|     | 3.5     | Experiment #2                                                                  |

|     |         | 3.5.1 Knuth-Morris-Pratt (KMP)                                                 |

|     |         | 3.5.2 Aho-Corasick (AC)                                                        |

| 4   | Con     | clusions                                                                       |

|     | 4.1     | Research Questions                                                             |

|     |         | 4.1.1 To what extent can NIDS performance be increased by using GPU? 5         |

|     |         | 4.1.2 What parts of the NIDS can be optimized?                                 |

|     |         | 4.1.3 Which program specific factors give the increase, or decrease in perfor- |

|     |         | mance?                                                                         |

|     | 4.2     | Summary of Contributions                                                       |

|     | 4.3   | Future  | Research                            | 3 |

|-----|-------|---------|-------------------------------------|---|

| Bil | bliog | raphy . |                                     | 5 |

| A   | App   | endix . |                                     | 1 |

|     | A.1   | Experi  | ment #1:Naïve String Search 6       | 1 |

|     |       | A.1.1   | Naïve Search Engine 6               | 1 |

|     |       | A.1.2   | Naïve Search Kernel 6               | 4 |

|     |       | A.1.3   | Naïve Search CPU Implementation 6   | 6 |

|     | A.2   | Experi  | ment #2: Knuth-Morris-Phatt (KMP) 6 | 8 |

|     |       | A.2.1   | KMP Engine                          | 8 |

|     |       | A.2.2   | KMP Preprocessing                   | 1 |

|     |       | A.2.3   | KMP Kernel                          | 2 |

|     | A.3   | Experi  | ment #2: Aho-Corasick (AC)          | 5 |

|     |       | A.3.1   | Aho-Corasick Engine                 | 5 |

|     |       | A.3.2   | Aho-Corasick Kernel                 | 8 |

|     |       | A.3.3   | Aho-Corasick Tree Structure         | 0 |

|     |       | A.3.4   | Aho-Corasick CPU Implementation     | 5 |

|     | A.4   | Experi  | ment - Common Functions             | 9 |

|     |       | A.4.1   | Dictionary Structure                | 9 |

|     |       | A.4.2   | Output Handler                      | 2 |

|     |       | A.4.3   | Packet Handler                      | 4 |

|     |       | A.4.4   | Monitoring                          | 5 |

|     |       |         |                                     |   |

# List of Figures

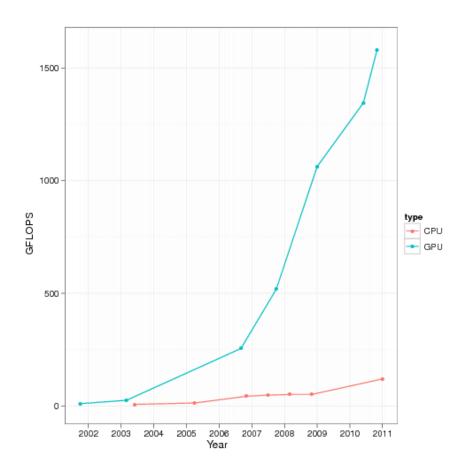

| 1  | GPU vs CPU - Floating point operations (FLOPs) [13]                               | 2  |

|----|-----------------------------------------------------------------------------------|----|

| 2  | Gainward GeForce GTX 580 1536MB GDDR5 Memory ([18])                               | 8  |

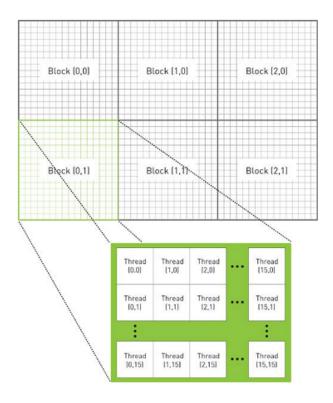

| 3  | 2D layout of threads and blocks on a GPU [46]                                     | 10 |

| 4  | Multiple Nvidia GPUs                                                              | 14 |

| 5  | Basic data flow of a Snort NIDS                                                   | 17 |

| 6  | Runmode for a pcap device in Suricata [43]                                        | 18 |

| 7  | Knuth-Morris-Pratt - Algorithm Walkthrough [7]                                    | 21 |

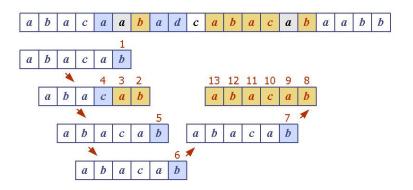

| 8  | Knuth-Morris-Pratt - Example Execution [7]                                        | 22 |

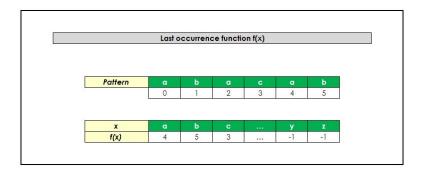

| 9  | Boyer-Moore - Last Function [6]                                                   | 23 |

| 10 | Boyer-Moore - Example Execution [6]                                               | 23 |

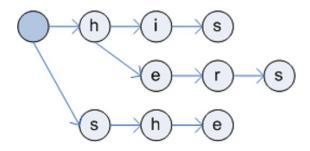

| 11 | Aho-Corasick - goto function [44]                                                 | 25 |

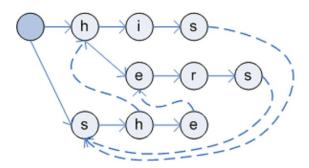

| 12 | Aho-Corasick - failure function [44]                                              | 25 |

| 13 | Aho-Corasick - Output of Next Move Function $\delta$                              | 27 |

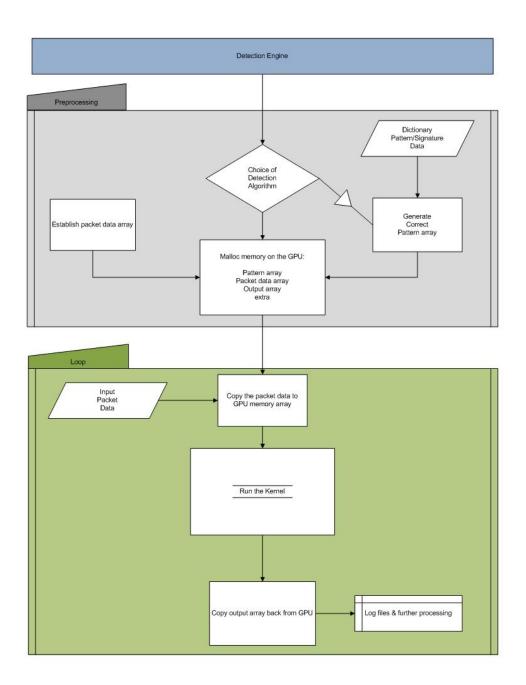

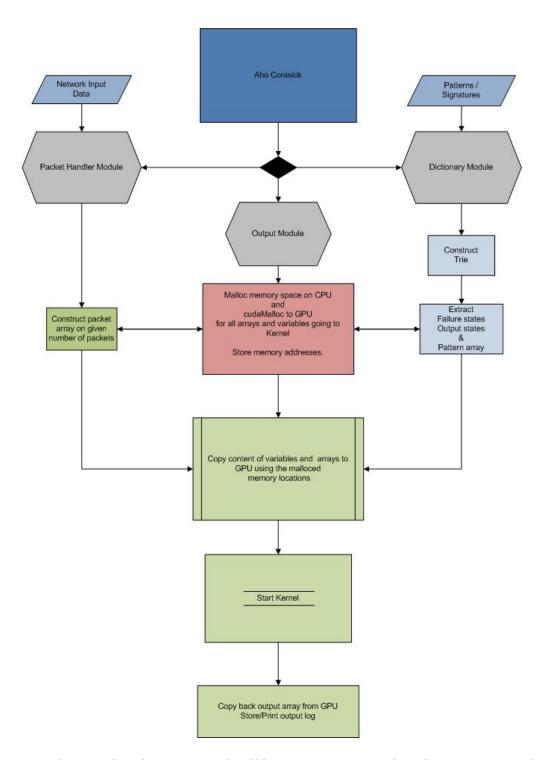

| 14 | Detection Engine using GPU                                                        | 33 |

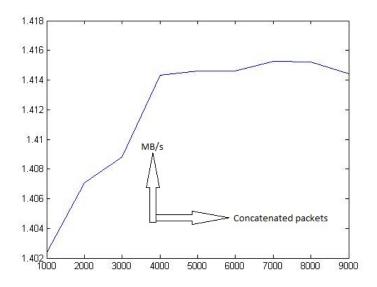

| 15 | Naïve GPU Execution, 456 patterns checked vs. packets with length of 40 chars     | 38 |

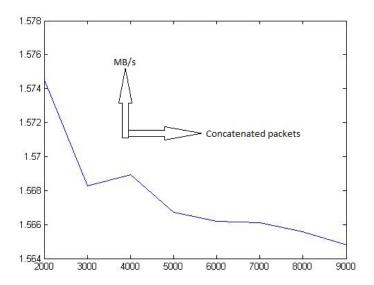

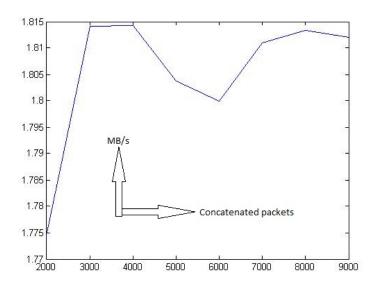

| 16 | KMP GPU execution, 456 patterns checked vs. packets with length of 40 chars       | 41 |

| 17 | KMP CPU Implementation, 456 patterns checked vs. packets with length of 40 chars. | 42 |

| 18 | Aho Corasick Implementation. Red and blue areas are run once to limit the         |    |

|    | computation needed, green is looping over new packets placed into the malloced    |    |

|    | memory space on the GPU for each new collection of packets                        | 44 |

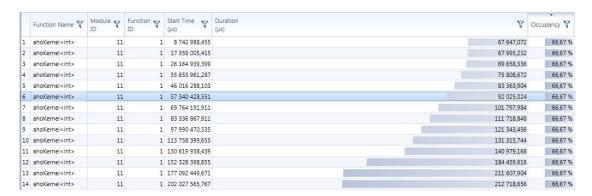

| 19 | Occupancy at 1024 kernels per block                                               | 45 |

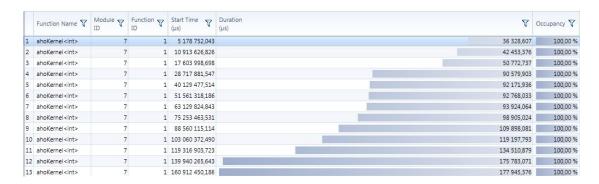

| 20 | Occupancy at 512 kernels per block                                                | 46 |

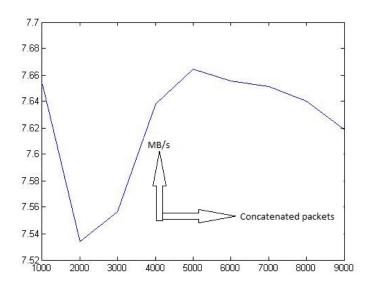

| 21 | Aho-Corasick CPU Execution, 456 patterns checked vs. packet length of 80chars     | 47 |

| 22 | Aho-Corasick GPU Execution, 35500 patterns checked vs. packet length of 80chars.  | 48 |

# List of Tables

| 1  | Benchmark results of a Nvidia GF100 chip [16]                                   | 11 |

|----|---------------------------------------------------------------------------------|----|

| 2  | Bandwidth results between the Main Memory(host), GeForce 580 GTX and            |    |

|    | GeForce 280GTX, (Bandwidth tester [38])                                         | 11 |

| 3  | Naïve string search                                                             | 20 |

| 4  | Knuth-Morris-Pratt - Failure Function                                           | 21 |

| 5  | Lab Environment Hardware                                                        | 32 |

| 6  | Required software for programming                                               | 34 |

| 7  | Hardware Details: GeForce GTX 580                                               | 34 |

| 8  | Hardware Details: GeForce GTX 460                                               | 35 |

| 9  | Average execution runtime of the Naïve string search on GPU                     | 37 |

| 10 | KMP execution, 456 patterns checked vs. packets with length of 40 chars         | 40 |

| 11 | GPU Aho Corasick. 456 signatures checked vs. packets with length of 80 chars    | 46 |

| 12 | GPU Aho Corasick. 35500 signatures checked vs. packets with length of 80 chars. | 46 |

| 13 | GPU Aho Corasick. Multiple runs of 35500 patterns checked vs. packet length of  |    |

|    | 40chars                                                                         | 48 |

# **Preface**

This master's thesis report conclude the end of my Master of Science in Information Security program at Høgskolen i Gjøvik (HIG) 2012. I would first like to thank my supervisor Prof. Slobodan Petrović for all help during the thesis and overall time here at Gjøvik. Petrović's lecture in Intrusion Detection and Prevention was what inspired me to write this thesis. Moreover, i would like to thank the student opponent; David Ormbakken Henriksen for feedback on the report. Finally i would like to thank Svein Engen, Benjamin Adolphi and Andreas Tellefsen for valuable feedback throughout this process.

# 1 Introduction

Network Intrusion Detection System models that only use Central Processing Units (CPU) such as Snort, have in the last decade struggled with the CPU as the bottleneck of the system. Network traffic has been increasing more rapidly than the clock-speed of CPUs. The CPUs have gained more cores, but lack implementation for utilizing multi-core CPUs and are unable to cope with the bandwidth throughput we are starting to see in high-tech network infrastructure that they are set to protect. The massive flows of data packets overload the NIDS and lead to packet loss which makes them pass by unchecked for malware and intrusion attempts, increasing the false-negative rate. The main cause of this is the *network packet inspection* module in the detection engine of the NIDS. The detection engine consists of numerous functions and ultimately contains an algorithm for *string searching*. This thesis will focus on accelerating the NIDS by parallelizing this algorithm.

Using Graphics Processing Units (GPU) for general-purpose scientific and engineering computing has grown exponentially the last few years. Ordering the GPU to take over and accelerate the computationally-intensive calculations normally done by the CPU, the two work together solving tasks in a heterogeneous co-processing computing model. Some of the most common areas for use of GPU is fluid dynamics, seismic processing, molecular dynamics, computational chemistry, finance and supercomputing. Programs need to be specifically designed to run optimized on a GPU, and special programming APIs have been designed explicitly for GPU computing. The most well known ones are CUDA and OpenCL. In the recent year's modern GPUs have evolved from being the tool that displays high-end graphics for games, to be the tool used in general-purpose scientific and engineering computing across a range of platforms.

# 1.1 Problem Statement

NIDS models that use Central Processing Units (CPU) for computation have in the last decade struggled more and more with the CPU becoming the bottleneck of the system. Network traffic has been increasing more rapidly than the clock-speed of CPUs making it harder and harder to keep up inspection of all network traffic that they are set to protect. The CPUs have gained more cores, but NIDS such as Snort [52] lack implementation for utilizing multi-core CPUs and are unable to cope with the bandwidth throughput. The massive flow of data packets overloads the NIDS and forces the NIDS to drop packets to keep up the real-time surveillance, letting them pass by unchecked for malware and intrusion attempts further increasing the total false-negative rate. A good GPU implementation can dramatically increase the amount of calculations that can be performed at the same time and boost performance of the NIDS, reducing false-negative rate caused by dropping packets. When gaining more computational power the system can handle more traffic without affecting performance of the NIDS, and the cost of the NIDS can be reduced by many factors as the hardware requirement is less to perform equally to the standard CPU based model. Figure 1 show a graph displaying the evolution of GPU and CPU the last decade in

Figure 1: GPU vs CPU - Floating point operations (FLOPs) [13]

the case of floating point operations (FLOPs) per second possible.

There are two main types of NIDS, signature-based, and anomaly-based. This thesis focus on signature-based systems that monitor network traffic using known attack patterns. NIDS analyze network traffic for malicious activities and reports findings from events that intend to compromise the security of the computers and other equipment. A NIDS looks into both headers and payloads of the network packets to identify possible intrusion. This is known as deep packet inspection (DPI). Most Signature based NIDS consist of different modules; from Network Traffic, Packet Capture, Packet Decoding, Preprocessors, Detection Engine, to Output-Logging and Alerting, all highly customizable to the user's needs [34]. In most of these modules there are components consuming huge amounts of computational power, especially Preprocessors and the Detection Engine. Cabrera et al. (2004) [9] reported that signature matching in Snort accounts for over 60% of the total processing time alone. Since then the ammount of signatures active in Snort has quadrupled, making it an even more demanding process.

# 1.2 Contributions

In this master thesis, we examine the viability of using Graphical Processing Units (GPU) in a Network Intrusion Detection System (NIDS) to accelerate the detection engine process with CUDA parallelization technology from Nvidia. We will show that utilizing GPUs for taking over the signature matching we can theoretically increase the overall performance of NIDS, reducing the chance of dropping packets, increasing false negative rate, from too high packet throughput on the network.

The thesis contribute with answers to the following research questions:

- 1. To what extent can NIDS performance be increased by using GPU?

- 2. What parts of the NIDS can be optimized?

- 3. Which program specific factors give the increase, or decrease in performance?

# 1.3 Choice of Methods

In addition to theoretical analysis, the experimental part of this thesis is of decisive importance, thus the refinements of the experimental model will show how efficient the GPU implementation of the NIDS search algorithm is compared to its original implementation. For this, a qualitative and experimental methodology [27] will be used to answer the research questions. Learning the tools and programming languages to work with GPUs and CUDA, and technologies that are found in NIDS will take a large portion of time spent on the master thesis. A deep dive into the core of NIDS is needed to find the best abilities and weaknesses.

Addressing the first research question, *Can NIDS performance be increased by using GPU?* a careful review of literature and documentation of current NIDS systems and GPU technology is necessary, to understand exactly which parts of the pipeline is suited for parallelization. We believe that the best way to gain this knowledge is to experiment with the technologies involved and find more optimal solutions to problems encountered in a normal NIDS. Understanding how it everything fit together, the technologies behind and the architectural weaknesses in NIDS will be needed to start the experimental creation of a GPU based implementation to answer the

research questions.

The answer to the second research question *What parts of the NIDS can be optimized?* will be based on the gathered knowledge and be subject of even deeper analysis while conducting experiments to determine to the full extent of which factors that play a part in performance, both positive and negative directions. Experiments will be performed in a lab environment, set up with the latest technology possible to take advantage of all the enhancements made from previous versions of CUDA and compute power to get as accurate results as possible.

Finally, the third research question *Which program specific factors give the increase, or decrease in performance?* will be highlights from our experimentation and programming and be a valuable collection of tips and tricks as to how we found the different systems to work in synergy gaining performance boosts, and performance loss from different methods and techniques used to archive a certain function in our code. These experiences will be part of our contribution to whomever would continue the work for implementing GPU acceleration into an NIDS.

By offloading the work from the CPU to the GPU, the systems can perform massive amounts of parallel calculations and gain high performance boosts to reduce or completely eliminate packet loss. To be able to create algorithms for the GPU, experiments need to be performed to determine what data should be processed on the GPU rather then CPU as the GPU will only give performance boots at tasks that can be done in parallel. Sequential processing would still be done far better by the CPU.

Theoretical problems of the project will be to look at algorithms, how these will need to be rewritten to fit GPU architectures, optimization techniques for the GPU and look for direct access methods towards other hardware, especially the main memory and the network interface itself.

Technical side of the project will be to implement a prototype / proof-of-concept software with the GPU accelerated IDS algorithms utilizing the researched optimization methods.

Finally, methods for benchmarking the performance of NIDS will be applied and a comparison carried out between the results of the project and the state-of-the-art open source systems.

# 1.4 Outline

In Chapter 2 we give details of related work in regards to signature-based NIDS that utilize content or regular expressions. Next we provide a technical background to the Graphical Processing Units, CUDA technology and NIDS architectures. Chapter 3 shows our design and implementation of string matching algorithms using CUDA and evaluates the results from our prototype implementation compared to related work. Chapter 4 concludes our findings and work.

# 2 State of the Art

This chapter presents the most related work from the perspective of this thesis, then continues with a background overview of the technologies used; Graphical Processing Units, the CUDA architecture, and Network Intrusion Detection Systems.

# 2.1 Related work

In normal signature-based NIDS systems the most crucial operation performed is the pattern matching. Pattern matching is the technique of searching through a string to find a specific pattern given as binary data or a set of characters. It is used in all fields of study and technologies, from indexing libraries, search engines on the Internet such as Google, or locating a word in a text file. These search tools can often let the user customize the criteria of the search in different ways, from searching for a particular character, one word or many, titles or content, or based on a given length. This flexibility of search dates back to the 1950's with S.T. Kleene's [45] formalism of regular sets, known in computing as *regular expressions*.

In the art of pattern matching two main classifications exist, single- and multi pattern algorithms. Single pattern matching algorithms will search through a text for each known pattern individually, which means it will loop through the whole text as many times as the total number of patterns. Original examples of single pattern algorithms are the Knuth-Morris-Pratt(MKP) [26] and Boyer-Moore(BM) [8]. Multi-pattern string algorithms operate quite differently, searching through the known text only once, looking for all patterns at the same time. This is done by preprocessing the patterns into a Final State Machine(FSM) or finite automata, that is further used to conduct the actual matching with the text. For multi-pattern algorithms we use two main types of automata, Non-Deterministic Finite Automaton (NFA) and Deterministic Finite Automaton (DFA) (DFA and regular expressions can be found in [50]). An NFA will generate a state for each possible input symbol, leading to many possible next states. The DFA on the other hand will only have one possible next state for each symbol, following the path of transition. It will jump deterministically from one state to another. Downside with DFA is the huge amount of memory needed to generate a next state for all symbols used. Examples of multi-pattern string matching algorithms include Aho-Corasick [1], Wu-Manber [61] and Commentz-Walter [11] (all algorithms can also be found in [33]). Most NIDS that are signature-based use a type of finite automata combined with regular expressions as described for their pattern matching.

Many approaches have attempted to take parts of NIDS and split them into elements for basic multi-threading parallelism realized by normal CPU multi-core processors [20, 21, 47, 48, 54]. Attempts at accelerating NIDS through special hardware other then the CPU have also been made for years. Commercial NIDS systems have for example been using technologies like Application-Specific Integrated Circuits (ASIC) or Field-Programmable Gate Arrays(FPGA), chips designed

and programmed solely to run a single algorithm or a small system. The use of Ternary Content-addressable Memory (TCAM) have also been done by Yu et al. [62] and Meiners et al. [30]. Both where quite fast, but in hardware extremely expensive. Chip circuits (FPGAs) also have the downside that when changing a rule or adding a new rule set, one must program a whole new circuit and then recompile the whole automaton, a very time consuming and difficult task. Improved approaches to FPGAs include Sidhu and Prasannas implementation of regular expressions on FPGAs (2001) [49], Baker et al. with a signature based method (2004) [4], and later Dharmapurikar et al. with bloom filters(2004) [14] and Kennedy et al. on a Statix 3 FPGA (2010) [23]. Attig et al. also proposed improvement to FPGAs with payload content scanning and header processing (2005) [2].

Several research efforts have been attempted at developing adoptions of *string matching algorithms* for Graphical Processing Units (GPU):

Huang et al.(2008) [19] attempted intrusion detection on a GPU based on the Wu-Manber algorithm [61]. Smith et al.(2009) [50] created an extended DFA with regular expressions on a GPU for intrusion detection and evaluated GPUs for network packet signature matching. Marziale et al.(2007) [29] use GPU for accelerating in-place file carving tools. Zha et al.(2011) [63] implemented a CUDA algorithm based on Aho-Corasick [1] with a Tesla GT200 card.

Jacob and Broadly attempted to accelerate Snort on a GPU with their *PixelSnort* (2006) [22]. They focused on offloading the string matching algorithm from the CPU to the GPU with a simplified single-pattern KMP algorithm [26]. This was at an early stage, not using new technology such as CUDA or OpenCL. They programmed the basic fragment shader in OpenGL to perform the calculations like normal visual graphics programming. Pixelsnort did not achieve any speed-up under normal conditions.

Related work combining CUDA and NIDS has been done by Vasiliadis et al. in multiple research papers: [55] was an attempt to gain high performance in NIDS (Snort) using Graphics Processors. They observed that single pattern matching algorithms like KMP were not suited for GPU computing, and rather tried using multi-pattern matching algorithms. The authors chose to port the algorithm Aho-Corasick [1] (Snort's standard detection engine algorithm), and concluded that it could boost performance of Snort at the time by a factor of two. The single-threaded architecture of Snort restricted the scalability of their work, not managing to utilize the power of multi-core CPU. The authors tried different approaches to start kernels on the GPU; assigning a single packet to each multiprocessor, assigning a single packet to each stream processor, and splitting up the packet into chunks to utilize the warp with size of their current GPU.

In [56] the team created a regular expression matching engine tailored to IDS use, and combined it with the work from Gnort. This experiment claimed a 60% increase in the overall packet processing throughput in Snort. However, the solution used only one GPU. The team realized the problems within Snort's single-thread architecture and wanted to further research Snort's performance when running multiple executions at the same time, one on each core.

In [58] the authors presented a pattern matching library for GPU. The library supports both

string searching and regular expression matching on the CUDA architecture. In addition the paper discussed the performance impact of different types of memory hierarchies and presented possible solutions for memory congestion problems.

Later Vasiliadis and Ioannidis published [51] modified the open source antivirus ClamAV from Sourcefire with their own GPU accelerated engine. They used the same methods and ideas from prior work [55, 56, 58].

The latest published contribution from the team combining all previous work [57] the authors propose a new framework model for NIDS, combining commodity hardware, general purpose hardware components, in a single-node design for high-performance network traffic analysis. The main idea is that no component needs to be synchronized, or wait for other executions to gain access to resources.

Chen-Hsiung Liu et al. created the PFAC Library [10]; string matching on the GPU using the Aho-Corasick algorithm. The program is written such that for every input byte a thread on the GPU is started, and the instance of the algorithm will run from that location until no match is found against a pattern. The PFAC library does not support multi-GPU but the authors claim it can easily be combined with other threading libraries to perform string matching on multiple GPUs at once.

# 2.1.1 Summary

The thesis will most importantly focus on [55] by Vasiliadis et al. titled Gnort: High Performance Network Intrusion Detection Using Graphics Processors. Results presented in Chapter 3 will be discussed and analyzed against this paper.

# 2.2 Technical Background

This section will give overview of technology used throughout the thesis. This includes Graphics Processing Units (GPUs), CUDA programming, Network Intrusion Detection Systems (NIDS) and well known algorithms for use in pattern matching.

# 2.2.1 Graphical Processing Units

The constant global demand for high-definition graphics in 3D games and realtime visualization for applications have lead to massive investments in developing Graphic Processing Units (GPU) for harnessing computational power in an extremely efficient parallel processing computational model. The GPUs have grown almost exponentially in processing power and memory bandwidth.

In this thesis we have chosen to work with the CUDA architecture. CUDA is Nvidia's standard parallel architecture and is exclusively integrated into nearly every Nvidia graphics card today. API and compiler support is available for C, C++, Fortran, Matlab and more. It gives direct access to the hardware without the need of other APIs [41]. CUDA offers the most optimal platform for GPU computation with fast calls as it is tailored specifically for the hardware, also giving fast Direct Memory Access (DMA) and other functions that would be needed for a real-time NIDS system. We believe CUDA is the most promising framework for further research and development due to the quality of the API, development kit, documentation, free on-line education and training, books and example programs.

The first GPUs were produced by Nvidia in 1999, designed as graphics accelerators to

handle all visuals that are to be seen on the screen of the computer and only supporting some specific functions [35]. Using these GPUs for scientific work was at this time hard, as the only programming language available was OpenGL [25]. Scientists had to take the calculations they wanted to perform and map them to problems with triangles and polygons that could be represented visually on the screen [41]. Newer cards have gained more processors with higher frequency, higher number of CUDA cores, increased memory and API support. Figure: 2, shows an image of a high-end Nvidia GeForce graphics card (GTX 580), also used during the experiments in this thesis.

Figure 2: Gainward GeForce GTX 580 1536MB GDDR5 Memory ([18])

# 2.2.2 CUDA

Nvidia supplies CUDA developers with an up to date programming guide [37] with the release of each CUDA revision as well as a best practice guide for CUDA C development[36]. We strongly recommend anyone who wish to gain more insight in CUDA to read these documents found in the CUDA-Toolkit documentation: [38]. Books with best practices examples for CUDA has also been released.

Nvidia provides three types of cards that all support CUDA: Tesla, Quadro and GeForce, respectively [39].

Tesla is the scientific GPU card, designed for data centers and workstation computing applications. It is based on the "Fermi" GPU computing architecture, and can deliver massive application performance. Tesla have full double precision on floating numbers, faster PCIe communication and large data set support. It also has Nvidia GPUDirect with InfiniBand, used by the major "supercomputers" around the world. It also has two DMA engines for dual access to main memory. Special drivers for Windows also exist for Tesla, reducing CUDA kernel overhead. Tesla also supports Error Correcting Code (ECC) Memory, for critical applications with uncompromised computing accuracy and reliability, where it protects register files, L1/L2 caches, shared memory and DRAM.

Quadro is the professional graphics solution and is created to process the max possible triangles per second possible. Quadro is also based on the Fermi architecture and has two DMA

engines, but not the other functions that are unique to Tesla. Quadro is often used by digital content creators such as in the movie industry, design engineers, geo-scientists and more.

*GeForce* is the normal consumer version, much cheaper than the other two, though almost the same graphics power as the Quadro and Tesla, but only one built in DMA engine and none of the other features. This is the type that is referred to as a "gamer" card, found in laptops and normal desktop workstations.

# **Interface**

CUDA consists of a set of extensions to the normal C language and a runtime library. Source files containing CUDA-code must therefore be compiled with Nvidia's own compiler: **nvcc**. The runtime is built from the CUDA driver API which is also accessible to developers. A program can use the runtime library or driver API, or both at once without problems. *nvcc* is accessable from command line and is supported in all newer versions of the biggest operating systems, namely Windows(7,Vista and XP), Mac OS X, and Linux. Linux has supported Toolkit versions for Fedora, Ubuntu, RedHat, OpenSuse and SUSE Enterprise Server, but other distributions such as Arch Linux work as well.

New revisions of CUDA have a *compute capability* flag within a given GPU, and is defined by a major and a minor revision number. Compute capability describes which features are supported by the CUDA hardware. At this moment of writing, the newest cards are based on the Fermi architecture and has compute capability 2.x. Current features are detailed in [38].

Compute capability is set as an option flag. Example: arch=compute\_20, -code=sm\_20 will set the compiler to compute capability 2.0. Nvidia has also added macros to be used within code to switch between different code-paths based on compute capabilities by calling for example: \_CUDA \_ARCH \_.

# **Parallelization**

The GPU core is organized in a "Single Instruction Multiple Data-architecture(SIMD). The idea is to execute multiple copies of a program in parallel with only one single call to the GPU. In CUDA, the executed code sent to the GPU is called a *kernel*. An example is provided where we add two vectors A and B and store the result in C: Listing 2.1. The code looks and feels like normal C-code. However, there are identifiers that separate host-code from device-code, here represented with \_\_global \_\_. The second important part of this example is how the function VecAdd is called from within main(). The difference from a normal C function call is "«<B, T»>" which is an execution configuration syntax that tells the GPU to launch B-number of *blocks*, containing T-number of *threads*. In the documentation of CUDA the word *warp* can often be seen. This describes the minimum group size of threads that can be processed in SIMD fashion for maximum performance. However, we do not work with warps directly, this is rather the purpose of blocks. A block is a collection of these threads and can share memory and work together. Blocks are again clustered in a *grid* pattern, making it relatively easy to access any specific thread within the program.

```

// Kernel definition

\_\_global\_\_ void VecAdd(float* A, float* B, float* C)

```

```

{

3

int i = threadIdx.x;

4

5

C[i] = A[i] + B[i];

}

6

7

8

int main()

9

{

10

// Kernel invocation of BB blocks with TT threads.

11

VecAdd << BB, TT>>> (A, B, C);

12

}

13

```

Listing 2.1: Example of launching a kernel in CUDA with C code [38]

Figure 3: 2D layout of threads and blocks on a GPU [46].

# **Memory Access**

A basic assumption within the CUDA programming model is that the threads are executed on a separate device from the host application running on the CPU. These devices hold their own separate memory spaces, accessible for the programmer. Note some General-Purpose computing on Graphical Processing Units (GPGPU devices) such as laptops have an integrated graphics chip on the motherboard, in addition to a second more powerful GPU chip. These share the main memory of the laptop seamlessly, but this does not change the programming model.

On CUDA GPUs contain two main types of memory storage, on-chip and on-board. The onchip memory is by far the fastest, however limited in size, merely some kilobytes(KB) storage. These memory spaces are known as the register, shared memory and texture memory. They are used effectively when the programmer wants to reuse data multiple times very quickly. The on-board memory is the largest memory storage on the GPU card, measured in gigabytes(GB), known as global memory. Compared to on-chip, global memory is rather slow, and is used for storing data over time while executing programs. Table 1 contains benchmark results of Nvidia's GF100 chip memory access speed, found in cards such as GTX 470 and 480.

| Memory          | Speed                        | Location | Cached | Access     | Scope                  |

|-----------------|------------------------------|----------|--------|------------|------------------------|

| Register memory | $\approx 8000 \mathrm{GB/s}$ | on-chip  | No     | Read/Write | One thread             |

| Shared memory   | ≈ 1600GB/s                   | on-chip  | N/A    | Read/Write | All threads in a block |

| Global memory   | $\approx 177 \text{GB/s}$    | on-board | Yes    | Read/Write | All threads + host     |

| Mapped memory   | $\approx 8GB/s$              | host     | Yes    | Read/Write | All thread + host      |

Table 1: Benchmark results of a Nvidia GF100 chip [16].

| Device            | Memory transfer | Speed         |

|-------------------|-----------------|---------------|

| 580 GTX           | Host 	o Device  | 3889.6 MB/s   |

| 580 GTX           | Device → Host   | 4323.7 MB/s   |

| 580 GTX to 280GTX | Device → Device | 163636.7 MB/s |

Table 2: Bandwidth results between the Main Memory(host), GeForce 580 GTX and GeForce 280GTX, (Bandwidth tester [38])

# **Memory Space**

Experienced programmers like to call these memory spaces for variable type qualifiers. These qualifiers specify in which device memory a variable will be stored. CUDA supports automatic variable declaration without the use of qualifiers, and will generally be placed in the register. However, the compiler may choose to place it somewhere else as it feels fit. To force a location of a variable we therefore declare where we want it located. This is done by calling for example: \_\_shared \_\_, \_\_constant \_\_or \_\_global \_ \_.

### Device

qualifiers will declare that the variable will be sent to the GPU device. \_\_device \_\_can be used together with any of the other memory target qualifiers to further declare where the variable should be stored. Using this qualifier alone, the variable will be stored in global memory by default and has a lifetime for the whole execution of the program or until it is released. Each of the qualifiers have performance and usability consequences that will greatly affect the running program if not used correctly:

memory (\_ global \_ qualifier) is located on-board also known as DRAM and is the biggest memory storage on the GPU card. The performance related to global memory resides in the fact that all global memory accesses have to be performed perfectly coalesced. This means that all memory requests sent from all threads needs to be combined into a single memory transaction. Efficient use of global memory is essential in a program by avoiding memory bandwidth limitations through data reuse. (Details regarding performance of global memory see [36]).

### Shared

memory (\_\_shared \_\_qualifier) is located on-chip, a copy for each block launched on the GPU. A running thread has only access to the copy within its own block, and cannot change or read from other blocks. The lifetime of shared memory is the same as the lifetime of the block it is created for. This makes it ideal for programs that need cooperation between some threads, without the need of synchronizing every thread on the GPU. This memory is much faster then global memory, and should by all means be used whenever possible where many threads need access to the same memory.

# Constant

memory (\_\_constant \_\_qualifier) has a size of 64KB that also holds an 8KB cache. This memory is used to hold constant variables that will and cannot change during the execution of the kernel, and can only be set from the host, before kernel is launched. All threads on the GPU have access to constant memory.

### Registers

are the fastest cache memory on the GPU. To achieve peak performance in a program, registers are the best choice with the lowest latency and highest bandwidth.

### **Texture**

is a wrapper around the global memory already mentioned. Texture memory is read only on the device and can only be set from the host. It is however relatively small, only an 8KB cache. Texture memory is a hardware interpolation of the block, and will be used most effectively if it can read clustered blocks on the global memory. This memory is mostly used for graphics, when utilizing multi-sampling techniques and more.

# Page-Locked Host

memory, also called *pinned* memory is located on the host memory and not on the device. The allocated memory will not be swapped to disk by the OS, but remains at the same location, with the same address space for the whole duration of the program.

### **Performance Metrics**

Measuring performance accurately is important when we want to optimize CUDA. [36] lists the most optimal methods:

The *runtime of kernels* can be measured using timers from either CPU or the GPU. There are however many pitfalls and advantages to using either one. The GPU operates asynchronously when calling kernels and memory operations also work asynchronously when set. The CPU has to be synchronized through the CUDA API to be able to measure correctly. This blocks the calling CPU thread until all kernels are completed. This approach is therefore only usable when measuring the overall performance, and not on a particular kernel or stream [36].

Using GPU timers is carried out by recording timestamps of events on the GPU itself, and is therefore OS independent. This is fully supported by the CUDA API and is quite intuitive to use. All parts of the code can be measured by calling <code>cudaEventRecord()</code> and give a <code>start</code> or <code>stop</code> parameter. The <code>cudaEventElapsedTime()</code> will then give the duration of the event. The GPU timer is measured in milliseconds, and has around half a millisecond resolution [36].

The most important part to measure is the bandwidth of data transfers. This can be done either as theoretical or as effective bandwidth calculation. The structure of the data itself and GPU memory used will have the largest impact on performance. Theoretical max bandwidth is hardware dependent and found in the product specifications. The GPU used for this thesis was a GeForce 580 GTX, with DDR5 RAM, with a clock rate of 2.01GHz and 384-bit bus width. Theoretical max performance is therefore 192.096 GB/sec:  $(2001 * 10^6 * (384/8) * 2)/10^9 = 192.096$ GB/sec

Effective bandwidth is found after timing the events and activities and calculating the data accesses of the program. This can be done for each array, matrix or whatever is needed. The math behind effective bandwidth is straightforward: basically, the *total amount of data bits read per time unit*, here in seconds.

Bandwidth can also be analyzed in the CUDA Visual Profiler *cudaprof*. The tool can display useful statistics such as how well the code is performing compared to the hardware limit of the system.

# Multi-GPU programming

Using multiple GPUs in programming does not automatically require much extra effort from the programmer. CUDA itself is built to support it. The part left for the programmer is to select the correct GPU for the upcoming work which can become quite messy if not done correctly. When a CPU program will send work to the GPU, it establishes a context(view of a GPU) between the calling CPU thread and the GPU. The context contains all states for that GPU, from the virtual address space, streams, events, allocated blocks of memory, and more. The important part is that only one context can be active at a GPU at any given time. Even though a GPU can only be working with one context at a time, it can be used by many contexts. The CPU is in charge of swapping between the contexts, and uses the CUDA driver to do so. This can be done in such a way that each CPU thread switches contexts itself, or one thread handle context switching for all, when the GPU goes idle. Note that any memory allocated by one context cannot be accessed by other contexts, as the allocations are in different virtual address spaces [36]. The problem left for gaining high performance is building the functions to handle the switching and delegating workloads to the different GPUs, including in the calculation estimates of how long the work will take for each GPU, and taking into account their different specifications if they are not of the same type. Figure 4 displays an installation using two Nvidia graphics cards.

# **Calculation Correctness**

There are standards set for calculations such as binary floating-point representations in the *IEEE* 754. CUDA devices follow these with only some exceptions. They come from the same problem as any other calculation performed in parallel, where doing two operations simultaneously can change the answer if either one is done before the other. In CUDA the programmer must be

Figure 4: Multiple Nvidia GPUs

extremely careful to make sure threads reading the same memory do so in an atomic fashion to prevent faulty answers.

Nvidia provides a debugger for all systems, such as CUDA-GDB for Linux, and Parallel Nsight for Windows. The debugging tools are created for extensive control over everything that happens on and with the GPU, from what threads, blocks and warps that are active, to memory consumption and variables, and also how much of the total bandwidth of the card is being used by the program or kernel-wise for further optimization of the code. More details of the debuggers can be found at [40].

# 2.2.3 NIDS

Snort and Suricata methodology is based on *misuse detection*. These are signature-based systems where it looks for difference between abnormal and normal traffic that comes through the network using known attack patterns. Abnormal traffic detection bases itself on previous encounters, turned into attack signatures from observations and traces of malware. Both Snort and Suricata support a variety of accelerators; this includes *pfring*, and spesific network hardware such as *endace capture-cards*, *napatech capture-cards*, *Intel X10 capture-cards*, and *myricom capture-cards*.

# **Rules and Signatures**

Rules and Signatures are created to counter vulnerabilities. Microsoft's definition of a vulnerability, by Scott Culp [52]: "A vulnerability is any flaw that makes it infeasible, even when implemented or used properly, to prevent an attacker from; usurping privileges, regulating

internal protected operations, compromising data, or assuming trust that was not explicitly granted." Exploits are the practical term for the techniques or methodologies that take advantage of the actual vulnerabilities.

*Signatures* as used in Snort and Suricata are defined as any detection method that use a piece of data, content, marks or characteristics to uniquely identify a known exploits entering the network. The signatures have limited protection capabilities, since the exploit first has to be detected before a signature can be written to detect it. Any zero-day exploit would pass through signature detection easily.

Rules are based on detecting the process of how a vulnerability would run on the system. This detection method is designed to work against zero-day exploits, where the signatures may have been changed to be undetectable, but where the overall process of the vulnerability remain the same and still can be detectable. A rule often uses a signature that it will look for; in Snort Rule Language (SRL) this is named *content* and can consist of plain text or be combined with *regular expressions* 2.1.

All rules used in Snort and Suricata are based on the SRL. The *Sourcefire VRT Certified Rules* are the official rules explicitly for Snort and are created, tested and approved by the Sourcefire Vulnerability Research Team (VRT). The Snort community also has their own internally shared rules; *Community Rules* referring to all rules that are created and tested by the community and are freely available to everyone using Snort.

Another type, Shared Object (SO) rules, are loadable modules that can extend detection capabilities of the NIDS. The rules were first made with Snort version 2.6.0 with its new API. The rules written in C code, allow for detection of vulnerabilities that would be impossible to detect by a mere text based rule from the normal Snort rule language. This functionality is also used by the VRT to release binary modules without publishing the actual vulnerability. This is used in cooperation with vendors such as Microsoft, who through joint programs like MAPP [31] can share vulnerability information with NIDS and antivirus companies who create patches and detection methods before they are known to the public [24].

The largest open source community *Emerging Threats* specialize in creating rule-sets for both Snort and Suricata and other firewalls. The community has been at work since early 2003, though under different names, originally as *Bleeding Snort*. Emerging Threats is also funded by the US Army Research Office and the National Science Foundation. The rulesets are updated daily and are free to use for any organizations, commercial and private.

A typical SRL rule usually consist of an action, header, rule-options (content signatures), ID, and revision number. An example of a rule from Emerging Threats for both Snort and Suricata is provided in Listing 2.2:

```

1

alert tcp HOME_NET any -> EXTERNAL_NET HTTP_PORTS

2

(msg:"ET TROJAN Dapato/Cleaman Checkin";

3

flow:established,to_server;

4

5

content:".php?rnd="; http_uri;

fast_pattern; content:"GET";

[http_method; pcre:"/?rnd=\d{5,7}\x20HTTP1\/1\.[01]\x0d\x0aHost\]

x3a \x20/";

content:!"User-Agent | 3a | "; http_header;

8

content:!"Accept | 3a | "; http_header;

9

10

reference: md5,1d26f4c1cfedd3d34b5067726a0460b0d;

reference: md5,45b3b6fcb666c93e305dba35832e1d42;

11

reference: url, www.microsoft.com/security/portal/Threat/

12

Encyclopedia/Entry.aspx?Name=Trojan%3AWin32%2FCleaman.G;

classtype: trojan-activity;

sid:2014200;

13

14

rev:3;)

```

Listing 2.2: An example of a rule [15]

### Snort

Snort (developed and maintained by Sourcefire) has for over a decade been de facto standard when it comes to open source NIDS with millions of downloads and over 400,000 registered users world wide. It has become the most known and used open source IDS/IPS in the world, capable of performing real-time traffic analysis and packet logging, protocol analysis, content string matching, and attack vectors such as buffer overflows, port scans, and much more. The downside to Snort is that there is no standard support for multi-core CPUs or GPU acceleration. Additionally, the official development of the new version Snort 3.0 has been put on hold since around 2008. However, the community is still developing plugins and minor upgrades. The possibilities an administrator has in regard to configuration in Snort are quite massive. The system can be put into three main modes; run as a mere IP logger like tcpdump on specific IPs, a packet-logger of network traffic, or as full NIDS (default). Together with a configured firewall, Snort can also act as an Intrusion Prevention System (IPS) (snort in-line mode). This however is not much used and is not encouraged, as it requires huge amount of testing and configuration of rules for allowing/blocking the correct traffic. As mentioned, Snort is not multi-threaded, which is its most significant weakness. It is however possible, with great effort to set up snort to run with multi-processes, assigning one snort execution to each CPU core and have them cooperate. It requires lots of configuration but is the way most large companies and organizations have managed to keep up in speed and is well tested.

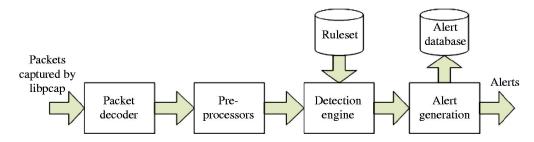

Snort as a whole has grown fairly large, and consist of many major modules, each addressing its own important part of the NIDS. As it is open source it takes advantage of other projects, and uses the *libpcap* library [53] for *packet capturing*. The packet is then handled by a *packet decoder* and delivered to the module with *pre-processors*. Next in the pipeline is the *detection engine* where *string matching* is done. If the module detects abnormal traffic, the event is reported to the *alert-module*, which will generate a packet alert and send it to screen or a custom database. Figure 5

show the basic data flow of Snort NIDS, which is based on the pcap runmode.

Figure 5: Basic data flow of a Snort NIDS

The problem with Snort lies in the fact that the code base has started to become quite old and outdated for today's hardware. It does not support multi-core processors, and is only run as a single thread, as mentioned before. Snort does not have any actual support for GPU acceleration. It has such a large code base that it has proven a gigantic task to rewrite the system for multi-threading. The Snort 3.0 project, which was supposed to address this issue has been put on ice and has not been in development for the last years. NIDS administrators have however found a workaround for managing the problem. They build the system and configure snort in such a way that they can run one instance of Snort on each core, combining the power and splitting the workload between multiple processes. This has been done for quite some time, but it is hard to set up, and maintain.

A good thing about Snort is that it has been well documented over the decade it has been in development and there are countless sub-projects that have been built to support and enhance the power of snort, releasing the main thread of snort of some of the workload. Most of the projects develop for the alerting module, making better ways of controlling the visual display of alerts and events for the administrators. Some also make it possible to control many Snort sensors at once, such as those used in massive organizations and business infrastructures, over many locations around the world. This makes it possible to have one control center for traffic analysis. Barnyard2 [17] enables parsing of the open source log file standard unified2, and lets Snort save computational power by saving data efficiently by only saving to the disk and taking no further actions. Oinkmaster is another project that handles updating and managing the rule sets in Snort. It can handle all the major types of rules, such as VRT rules, community rules, Emerging Threat rules and other 3rd party such as those released for Suricata. The full list of additional improvements to Snort can be found in [12].

# Suricata

Suricata (developed and maintained by the non-profit organization Open Information Security Foundation (OSIF)) is basically a "clone" or "fork" of Snort in the way that it uses the same solution for creating rules and signatures. In this way, the community behind Snort can continue using their expertise without much effort for developing code, rules and signatures for Suricata instead. Suricata's main mission is to continue open IDS development where the Snort team has failed, without being blocked by the licenses governing Snort. The solution is to have a scaled, enterprise-ready IDS for government as well as private sector. The program code is written in C,

and is mainly designed for scalability. It utilizes multi-threading on CPU which allows the IDS to easily take advantage of all hardware power given. Suricata is also the only open source system that has started implementing GPU acceleration support [42], though still at an experimental stage. Worth mentioning is that Nvidia is one of the technology partners of OSIF to help develop CUDA GPU acceleration. Currently, Suricata uses a Wu-Manber algorithm implementation in their GPU detection engine, but the future plan is to implement Aho-Corasick to get rid of extra post processing and pattern chopping, as well as the issue with using byte blocks (see section 2.2.4 for more details on Wu-Manber). It neither takes advantage of the texture, shared memory and mapped memory, which in the latest releases of CUDA has been improved in speed and bandwidth by a great amount [36]. As of now, the speed of the GPU implementation is still not faster then an equal CPU version.

Suricata has also managed to get Ivan Ristić to join their development team, one of the lead developers from ModSecurity. Ristic created the library *libhtp* a security-aware parser for the HTTP protocol, which has been included into the Suricata project, providing very advanced processing of network streams within Suricata [42].

A mentionable problem with Suricata, compared to Snort, is the lack of documentation. There are hardly any resources on the net, by the community or the developers, such as guides for installation and maintenance, or details about the implementation itself. The documentation available on the OSIF WIKI is disappointingly short and barely enough to get the system running [43].

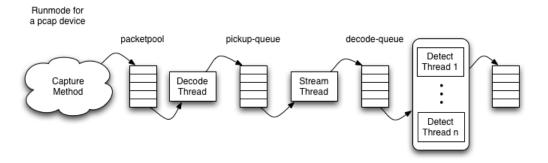

Suricata is also based on the pcap run-mode like Snort, module based implementation for; capturing, decoding, stream processing, and detection module. Figure 6 show the Suricata run-mode. Most of the same 3rd party tools used for Snort, also work for Suricata. OSIF recommend the use of the open source software tools BASE [5] and Squil [59] for managing events in Suricata.

Figure 6: Runmode for a pcap device in Suricata [43]

# 2.2.4 Algorithms

In a NIDS detection engine, the main component is the string matching algorithm. The objective of the algorithm is to search for a string (also called a pattern), or multiple strings (multipattern). Single pattern matching algorithms will search through a text for each known pattern individually, which means they will loop through the whole text as many times as the total number of patterns. Original examples of single pattern algorithms are the Knuth-Morris-Pratt(KMP) [26] and Boyer-Moore(BM) [8]. Multi-pattern string algorithms operate quite differently, searching through the known text only once, looking for all patterns at the same time. Aho-Corasick [1] and the Wu-Manber [61] are the most original and used multi-string algorithms. String algorithm requires one or many search string inputs, and a text or datafile to compare against. Over the last 50 years there have been many algorithms developed for searching strings and patterns. They are optimized for different types of work, and vary in complexity.

Within string matching there are two different problems for algorithms, *exact* string matching and *approximate* string matching. Exact is the classical approach, and what is mostly used by NIDS, as it sets out to find the perfect match to a given pattern or string. Approximate string matching takes error into account, and can find strings even though some characters are wrong, or missing. An example of approximate search is *Google search*, which give a "Did you mean this word?" if the user spelled wrong compared to what is indexed the most.

String algorithms follow three different approaches in general, *prefix searching, suffix searching* and *factor searching*. This is based on which direction the search window is shifted. For prefix search we try to find the longest prefix of the window that is also a *prefix* of the strings or patterns searched after. In suffix search the window shifts backwards, and the algorithm tries to find the longest *suffix* of all strings and patterns. Suffix is best used when the strings are actual words where the endings are the same on many words such as "ion" or "ing". Factor search also work backwards, looking at the suffix of the window, but also takes into account that it is a *factor* of the string or pattern.

# Complexity

When we are to analyze an algorithm we concentrate on the order of growth of the algorithm's operation count to perform a given task, meaning the amount of resources such as memory usage and time consumption that are needed for execution. This will give us a indicator of the algorithm's efficiency. Scientists like to talk about this as *algorithm complexity*, the difference in matching time, quantified based on the input to the algorithm. Complexity in this thesis is represented with the O-notation, pronounced "big oh". A formal definition is given in many books, for example in [28]: "A function f(x) is said to be in O(g(x)), denoted  $f(x) \in O(g(x))$ , if f(x) is bounded above by some constant multiple of g(x) for all large x, i.e., if there exist some positive constant c and some nonnegative integer  $x_0$  such that  $f(x) \le cg(x)$  for all  $x \ge n_0$ ".

Basically, time complexity is calculated by counting all the elementary operations the algorithm has to perform on the computer. We estimate that all elementary operations take the same fixed amount of time, leaving us with a constant factor that will provide us with an overall impression of the algorithm. Typically we want to know two complexity scenarios, *average* and

worst-case. For instance, an algorithm could have a complexity of  $O(2^n)$  which would be an exponential growth, often seen in worst-case scenarios, or O(n) meaning it would take linear time to the input of the algorithm, often seen in average time. Note, *exponential growth* is really bad and not wanted in any algorithm.

# Naïve string search

The naïve string search is the most basic form of string search algorithms. It performs no techniques for optimizing memory or increase of speed. The algorithm will start at the first text symbol in n, and try to match it against the first symbol in s, the search string / pattern. If this is matched as positive, the algorithm increment its counters, and compares the next string symbol s+1 to the next symbol in the text n+1. The process will continue until the whole string is found, or the algorithm reach a mismatch. It will then either report a success, or fail back to the first string symbol s, and restart the matching process against the next symbol in the text (doing n=n+1). The average complexity of naïve string search is O(s+n), and has a worst-case scenario at O(s+n). Example of naïve string matching; see Table 3.

| String Pattern: | a | b | Ъ | а |   |   |   |   |

|-----------------|---|---|---|---|---|---|---|---|

| Text:           | a | b | a | ь | a | b | b | a |

| Iteration 1:    | a | b | b |   |   |   |   |   |

| Iteration 2:    |   | a |   |   |   |   |   |   |

| Iteration 3:    |   |   | a | b | a |   |   |   |

| Iteration 4:    |   |   |   | a |   |   |   |   |

| Iteration 5:    |   |   |   |   | a | b | b | a |

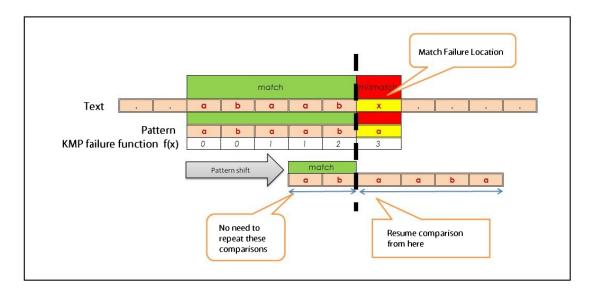

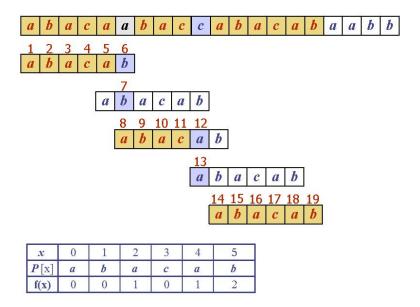

# **Knuth-Morris-Pratt (KMP)**

There are of course smarter ways of searching for a string in a given text in less worst-case time then (O(s\*n)), one is the Knuth-Morris-Pratt (KMP) algorithm invented in 1974 by Donald Knuth, Vaughan Pratt and James H. Morris. The optimization performed in this algorithm is that when a mismatch occurs, one can skip the next or several following characters to avoid doing a re-comparison of the same symbol which is a waste of time and computational power. This is because KMP keeps the information unlike the naïve approach that does nothing further with the data found during the scans of the text. To achieve this, the algorithm needs to precompute a failure function(Table 4. The function indicate the largest possible shift for the skipping of characters. In detail, the failure function  $\int$  for pattern s, store the length of the longest prefix of s inside j that is a suffix of  $s[1,\ldots,j]$ . The true objective is to map the repeated substrings inside the pattern itself. When the failure function is complete the main algorithm can start, and will run like the naïve function until it meets a mismatch. When it does it will look up the failure function table, and seek out the location of the closest suffix that matches the prefix of the pattern. This leads to a worst-case of O(s+n), and a required memory usage with size of (s) for the failure table.

The algorithm generates an automaton from the text, using O(s) time (Figure 7).

Table 4: Knuth-Morris-Pratt - Failure Function

| X    | 0 | 1 | 2 | 3 | 4 | 5 |  |

|------|---|---|---|---|---|---|--|

| P[x] | a | b | a | a | b | a |  |

| f(x) | 0 | 0 | 1 | 1 | 2 | 3 |  |

Figure 7: Knuth-Morris-Pratt - Algorithm Walkthrough [7]

When the algorithm then runs the search against this automata, the worst-case scenario matching time has been reduced to O(s+n). This algorithm is still limited by the fact that it is a single pattern matching algorithm, meaning this process has to be repeated for every string or pattern that wants to be searched. The algorithm is great if one only need to look for a low number of strings, but rapidly becomes too demanding when reaching higher numbers such as in NIDS with thousands of rules and signatures. Example execution of KMP see Figure 2.2.4.

Figure 8: Knuth-Morris-Pratt - Example Execution [7]

#### **Boyer-Moore (BM)**

The string search algorithm Boyer-Moore was developed in 1977 by Bob Boyer and J Strother Moore. BM is like KMP, a single-pattern search algorithm, the main difference of the two is that BM starts its search with the last character of the pattern, rather then the first as most other algorithms - it works backwards. The idea behind it is that if the last character does not match, there is no reason to go through all the characters from the beginning. BM also uses "failure function" like the KMP algorithm although it is called bad character shift rule and another good suffix shift rule. Improved versions of Boyer-More have been even better, further increasing the logic where where to look for match in fewest iterations possible. The Turbo-Boyer-More requires some extra memory space, storing the factor of the text from the previous iteration where a suffix shift was successful (did not mismatch). Turbo-BM has O(2n) as worst-case scenario, and an average of O(n). Another derivative of BM is Boyer-Moore-Horspool. It uses less space, but require an even better suffix table. The inner loop of the algorithm makes it perform less overhead for each iteration of the loop. While the average complexity of BM-Horspool is O(n), the worst-case scenario O(s \* n) is higher then the real BM algorithm, but theoretical worstcase is hard to achieve in practice. All Boyer-Moore algorithms works better with longer pattern strings, longer will make it possible to skip characters faster while shifting the pattern string.

Figure 9: Boyer-Moore - Last Function [6]

Figure 10: Boyer-Moore - Example Execution [6]

#### **Aho-Corasick (AC)**

Aho-Corasick (AC) was published in 1975 by Alfred V. Aho and Margaret J. Corasick [1], and is the most known multi-pattern search algorithm. The main objective is to construct a Final State Machine (FSM) for pattern matching from known keywords (or given as a dictionary), then process input strings against the FSM with *exact-set* matching. When AC was developed the fastest algorithm to perform bibliographic searches was KMP, which was not very effective on large datasets. This leed to the idea of creating a linear-time method by preconstructing a search pattern from all the known keywords, a generalization of KMP for multiple strings. The algorithm itself can be broken into four different parts; construction of a *goto function* (Algorithm 2.2.1 and Figure 11), construction of a *failure function*(Algorithm 2.2.2 and Figure 12) establishing a *pattern matching machine*(Algorithm: 2.2.3), and finally construction of the *next move function*(Algorithm 2.2.4). The last part is only used in the Deterministic Finite Automaton (DFA) version of the algorithm.

```

Algorithm 2.2.1: AHO-CORASICK - GOTO FUNCTION(K)

Input: Set of keywords K = \{y_1, y_2, ... y_k\}

Output: Goto function g and a partially computed output function

Comment: We assume output(s) is empty when state s is first created and

g(s,a) = fail if a is undefined or if g(s,a) has not yet been defined.

The procedure enter(y) insert into the goto graph a path

that spells out y.

newstate \leftarrow 0

for i \leftarrow 1 to k

do enter(y<sub>i</sub>)

for each a such that g(0, a) = fail

do g(0, a) \leftarrow 0

procedure: enter(a_1 a_2 .... a_m):

state \leftarrow 0

j \leftarrow 1

while g(state, a_i) \neq fail

\int state \leftarrow g(\text{state}, a_j)

j \leftarrow j + 1

for p \leftarrow j to m

(newstate \leftarrow newstate + 1

g(state, \alpha_{\mathfrak{p}}) \leftarrow newstate

do

state \leftarrow newstate

output(state) \leftarrow \{a_1 a_2 ... a_m\}

```

Figure 11: Aho-Corasick - goto function [44]

```

Algorithm 2.2.2: AHO-CORASICK - FAILURE FUNCTION(g, output)

Input: Goto function g, and output function output

Output: Failure function f and output function output

queue ← empty

for each \alpha such that g(0, \alpha) = s \neq 0

queue \leftarrow queue \bigcup \{s\}

f(s) \leftarrow 0

while queue ≠ empty

Comment: let r be the next state queue

queue \leftarrow queue - \{r\}

for each a such that g(r, a) = s \neq fail

queue \leftarrow queue \bigcup \{s\}

do

state \leftarrow f(r)

while g(state, a) = fail

do

state \leftarrow f(state)

f(s) \leftarrow g(state, a)

output(s) \leftarrow output(s) \bigcup output(f(s))

```

Figure 12: Aho-Corasick - failure function [44]

AC has been used in numerous different projects since its creating. In NIDS the first was written in 2002 by Marc Norton and released with Snort in version 2.0 with support only for Non-Deterministic Finite Automaton (NFA). This early version was not very effective, and in

2003 Daniel Roelker joined the development team. The new version included a massive speed optimization and improved memory usage. The update added sought after state transitions abilities to formats such as full-matrix, sparse-matrix, banded-matrix, and sparse-banded-matrix. The overall biggest update was support for both NFA and DFA. Even today AC is still the fastest algorithm and default in the Snort detection engine. The research team of Zha et al.(2011) [63] attempted to make CUDA implementation of Aho-Corasick and claimed good results, speedups between 8.5-9.5 times more then against a single-thread CPU, and 2.4-3.2 times more then a multi-threaded CPU. Suricata, the NIDS with GPU acceleration has the Aho-Corasick algorithm on their todo-list for future implementation.

```

Algorithm 2.2.4: AHO-CORASICK - NEXT MOVE FUNCTION(q, f)

Input: Goto function g, falure function f

Output: Next move function \delta

queue ← empty

for each symbol a

\delta(0, a) \leftarrow g(0, a)

if g(0, a) \neq 0

then queue \leftarrow queue \bigcup g(0,a)

while queue \neq empty

Comment: let r be the next state in queue

queue \leftarrow queue -\{r\}

do

for each symbol a

if g(r, a) = s \neq fail

\textbf{do} \ \big\{ \texttt{queue} \leftarrow \texttt{queue} \bigcup \{s\} \delta(r,\alpha) \leftarrow s

else \delta(\mathbf{r}, \mathbf{a}) \leftarrow \delta(f(\mathbf{r}), \mathbf{a})

```

| Input symbol              |    | N ext state |

|---------------------------|----|-------------|

| State 0:                  | h  | 1           |

|                           | 5  | 3           |

|                           | ¥  | 0           |

| state 1:                  | e  | 2           |

|                           | ì  | 6           |

|                           | h  | 1           |

|                           | 5  | 3           |

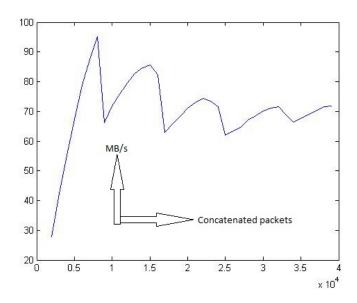

|                           | 1  | 0           |