Andreas Bjørsvik Sevat Mestvedthagen

## Optimization of CBADC Digital Estimation Filter for RISC-V Implementations

Master's thesis in Electronic Systems Design Supervisor: Trond Ytterdal Co-supervisor: Fredrik Esp Feyling June 2023

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Master's thesis

Andreas Bjørsvik Sevat Mestvedthagen

## Optimization of CBADC Digital Estimation Filter for RISC-V Implementations

Master's thesis in Electronic Systems Design Supervisor: Trond Ytterdal Co-supervisor: Fredrik Esp Feyling June 2023

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

## Abstract

Control-bounded analog-to-digital (A/D) conversion has emerged as a promising conversion method allowing less constrained analog and digital circuit architectures. However, a digital post-processing step is needed. In this thesis, we investigate how the digital estimation filter of the control-bounded A/D converter (CBADC) can be implemented as an accelerator complementing a 32-bit RISC-V Central Processing Unit (CPU). The implementation is a fixed-point unit made for a single input system.

As the digital estimation filter for the CBADC is not thoroughly investigated, we find what configurations of filter length, the number of fixed-point bits, and oversampling ratio are needed for each number of analog states to reach the desired signal-to-noise ratio (SNR) of 70 dB.

The developed accelerator employs a finite impulse response (FIR) filter algorithm with lookback and lookahead recursion to calculate the estimates. The accelerator parallelizes and pipelines the task to achieve the target sampling frequency of 20 MHz. The most energy-efficient configurations are the ones with the lowest number of analog states, as they also have the shortest filter lengths. This compensates for the higher oversampling ratio they need.

To reduce power consumption, multiple variations of the accelerator, aiming to optimize the circuitry, is implemented. The area and power consumption of the reference version of the accelerator with four analog states is estimated to be 170 255  $\mu$ m<sup>2</sup> and 11.70 mW. By reducing bit widths of coefficient registers and corresponding logic units where larger bit widths are unnecessary, the power consumption can be reduced by up to 27.4%, and area reduced up to 30.7%, to 125 300  $\mu$ m<sup>2</sup> and 9.17 mW. The implementation of lookup tables (LUTs) enables a power reduction of up to 40.1% at the expense of an area increase of up to 61.9%, thus 279 102  $\mu$ m<sup>2</sup> and 7.44 mW. Among the variations of LUT implementations, the two-input LUT proves to be the most power efficient. A commercially available 28 nm CMOS technology is used for all the simulations.

## Sammendrag

Kontrollbegrenset analog-til-digital (A/D) omforming har vokst frem som en lovende omformingsmetode som tillater færre begrensninger på de analoge og digital kretsarkitekturene. Derimot er et digitalt etterprossesseringssteg nødvendig. I denne avhandlingen vil vi undersøke hvordan det digitale estimeringsfilteret til en kontrollbegrenset A/D omformer (CBADC) kan bli implementert som en aksellerator tilkoblet en 32-bit RISC-V prosessor (CPU). Implementasjonen er en fasttallsenhet laget for et system med et enkeltinngangssignal.

Ettersom det digitale esimeringsfilteret for CBADCen ikke er grundig undersøkt, har vi funnet konfigurasjonene av filterlengde, antall fasttallbits, oversamplingsrate som er nødvendig for hvert antall analoge tilstander for å nå ønsket signal-støy forhold (SNR) på 70 dB.

Den utviklede akselleratoren benytter en avgrenset impulsrespons (FIR) filter algoritme med rekursjoner fremover og bakover for å regne ut estimatene. Akselleratoren paralelliserer oppgaven for å nå målet om en samplingfrekvens på 20 MHz. De mest energieffektive konfigurasjonene viser seg å være de med lavest antall analoge tilstander siden disse også har de korteste filterlengdene. Dette kompenserer for de høye oversamplingsratene de trenger.

For å redusere effektforbruket har flere variasjoner av akselleratoren, med mål om å optimalisere kretsen, blitt implementert. Arealet og effektforbruket til referanseversjonen av akselleratoren med fire analoge tilstander er estimert til å være 170 255  $\mu$ m<sup>2</sup> og 11.70 mW. Ved å redusere bitbredden for koeffisientregistre og samsvarende logiske enhter der større bitbredde er unødvendig, kan effektforbruket reduseres med opptil 27.4% og arealet reduseres med opptil 30.7%, til 125 300  $\mu$ m<sup>2</sup> og 9.17 mW. Ved å implementere oppslagstabeller (LUTer) muliggjør en reduksjon av effektforbruket på opptil 40.1% på bekostning av en økning av areal på opptil 61.9%, til 279 102  $\mu$ m<sup>2</sup> og 7.44 mW. Blant variasjonene av LUT-implementasjoner, ble en to-inngangs LUT funnet mest effektsparende. En kommersielt tilgjengelig 28 nm CMOS teknologi er brukt i simuleringene.

# Acknowledgements

Firstly, we would like to thank our supervisors, Professor Trond Ytterdal and Fredrik Esp Feyling, for their guidance over the past year. The meetings we have had throughout the year have been inspiring and enlightening.

We would also like to thank Leon Mayrhofer for our conversations regarding the implementation of the digital estimation filter and the comparison of results.

# Table of Contents

| Li            | List of Figures vii |                                                   |    |  |  |  |

|---------------|---------------------|---------------------------------------------------|----|--|--|--|

| $\mathbf{Li}$ | st of               | Tables                                            | ix |  |  |  |

| 1             | Intr                | oduction                                          | 1  |  |  |  |

|               | 1.1                 | Control-Bounded Conversion                        | 1  |  |  |  |

|               | 1.2                 | Related Work                                      | 1  |  |  |  |

|               | 1.3                 | Scope                                             | 2  |  |  |  |

|               | 1.4                 | Main Contributions                                | 2  |  |  |  |

|               | 1.5                 | Specifications                                    | 3  |  |  |  |

|               | 1.6                 | Outline                                           | 3  |  |  |  |

| 2             | Bac                 | kground                                           | 4  |  |  |  |

|               | 2.1                 | Number Representation                             | 4  |  |  |  |

|               | 2.2                 | Oversampling and Subsampling                      | 5  |  |  |  |

|               | 2.3                 | Power Consumption in a Digital Circuit            | 5  |  |  |  |

|               | 2.4                 | Supply Voltage Level and Device Threshold Voltage | 6  |  |  |  |

|               | 2.5                 | Power Gating and Clock Gating                     | 6  |  |  |  |

|               | 2.6                 | Pipelining                                        | 7  |  |  |  |

|               | 2.7                 | Parallelism                                       | 7  |  |  |  |

|               | 2.8                 | Accelerators and Coprocessors                     | 8  |  |  |  |

|               | 2.9                 | RISC-V                                            | 8  |  |  |  |

|               | 2.10                | CBADC                                             | 9  |  |  |  |

|               |                     | 2.10.1 Analog System                              | 9  |  |  |  |

|               |                     | 2.10.2 Digital Control                            | 9  |  |  |  |

|               |                     | 2.10.3 Digital Estimator                          | 9  |  |  |  |

|               |                     | 2.10.4 FIR Filter                                 | 10 |  |  |  |

|               | 2.11                | Software Tools                                    | 10 |  |  |  |

|   |                      | 2.11.1 CBADC Python Library                            |    |  |  |  |  |  |

|---|----------------------|--------------------------------------------------------|----|--|--|--|--|--|

|   |                      | 2.11.2 RISC-V Toolchain                                | 11 |  |  |  |  |  |

|   |                      | 2.11.3 Cadence Xcelium                                 | 11 |  |  |  |  |  |

|   |                      | 2.11.4 Cadence SimVision                               | 11 |  |  |  |  |  |

|   |                      | 2.11.5 Synopsys Design Compiler                        | 11 |  |  |  |  |  |

|   |                      | 2.11.6 Synopsys PrimeTime                              | 12 |  |  |  |  |  |

| 3 | Imp                  | blementation                                           | 13 |  |  |  |  |  |

|   | 3.1                  | FIR Filter                                             | 13 |  |  |  |  |  |

|   | 3.2                  | CPU Core                                               | 13 |  |  |  |  |  |

|   | 3.3                  | Accelerator                                            | 14 |  |  |  |  |  |

|   | 3.4                  | SystemVerilog Modules                                  | 15 |  |  |  |  |  |

|   |                      | 3.4.1 Accelerator Top-Level Module                     | 16 |  |  |  |  |  |

|   |                      | 3.4.2 Single Analog State Calculation                  | 17 |  |  |  |  |  |

|   |                      | 3.4.3 Multi-Cycle Adder                                | 17 |  |  |  |  |  |

|   | 3.5                  | Core Optimizations                                     | 18 |  |  |  |  |  |

|   |                      | 3.5.1 Reduced Signal Widths                            | 18 |  |  |  |  |  |

|   |                      | 3.5.2 Lookup Tables                                    | 20 |  |  |  |  |  |

|   |                      | 3.5.3 Post-Synthesis Parameterizability                | 20 |  |  |  |  |  |

|   |                      | 3.5.4 Remove Low-Pass Filtering from Digital Estimator | 21 |  |  |  |  |  |

|   | 3.6                  | Memory                                                 | 22 |  |  |  |  |  |

| 4 | $\operatorname{Res}$ | sults and Discussion                                   | 23 |  |  |  |  |  |

|   | 4.1                  | Choosing Filter Parameters                             | 23 |  |  |  |  |  |

|   | 4.2                  | Frequency                                              | 26 |  |  |  |  |  |

|   | 4.3                  | Limitation of the Cell Library                         | 27 |  |  |  |  |  |

|   | 4.4                  | Reference Version                                      | 27 |  |  |  |  |  |

|   | 4.5                  | Lookup Tables                                          | 29 |  |  |  |  |  |

|   | 4.6                  | Reduced Signal Widths                                  | 31 |  |  |  |  |  |

|   | 4.7                  | Post-Synthesis Parameterizability                      | 32 |  |  |  |  |  |

|   | 4.8                  | Combination of Optimizations                           | 34 |  |  |  |  |  |

|   | 4.9                  | Remove Low-Pass Filtering from Digital Estimator       | 34 |  |  |  |  |  |

| 5 | Fut                  | ure Work                                               | 37 |  |  |  |  |  |

|   | 5.1                  | Reduction of Area and Power Consumption                | 37 |  |  |  |  |  |

|   | 5.2                  | Sampling Frequency and Bandwith                        | 38 |  |  |  |  |  |

| 6            | Conclusion                                     | 39 |

|--------------|------------------------------------------------|----|

| Bi           | bliography                                     | 41 |

| A            | Custom Instructions                            | 43 |

| в            | Finding Filter Length                          | 44 |

| $\mathbf{C}$ | Finding FPB                                    | 48 |

| D            | Filter Coefficients Without Low-Pass Filtering | 52 |

| $\mathbf{E}$ | Result Table                                   | 56 |

# List of Figures

| 2.1  | Clock gating circuit [1].                                                                                     | 7  |

|------|---------------------------------------------------------------------------------------------------------------|----|

| 2.2  | The parts of the control-bounded A/D converter [2]                                                            | 9  |

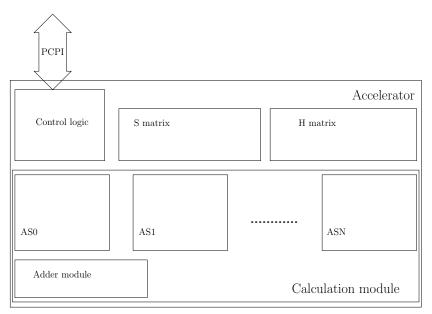

| 3.1  | A block diagram of the top-level module connecting the Picorv32 CPU with the accelerator.                     | 16 |

| 3.2  | Overview of the accelerator module.                                                                           | 16 |

| 3.3  | Two of the adder modules implemented                                                                          | 17 |

| 3.4  | Absolute value of the filter coefficients when $N = 4$                                                        | 18 |

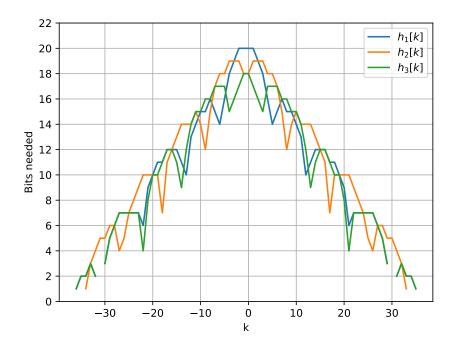

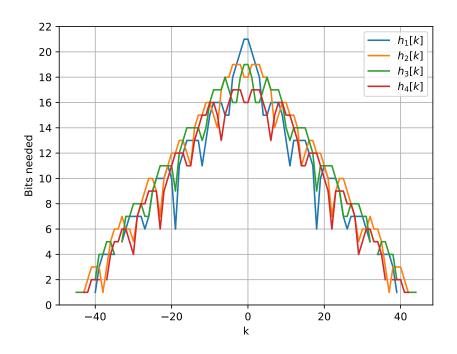

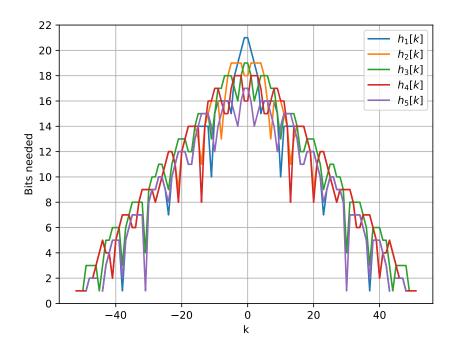

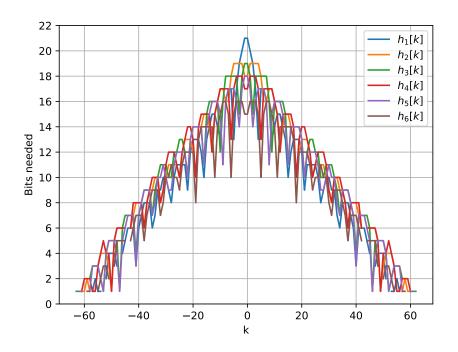

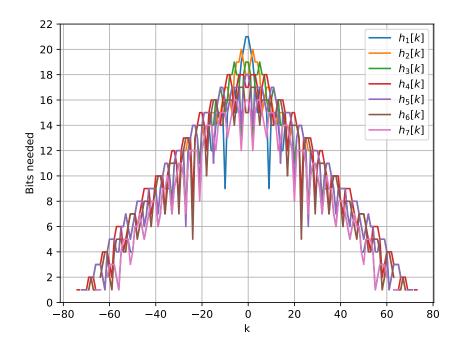

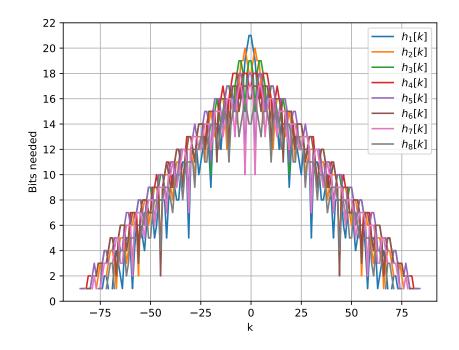

| 3.5  | The number of bits needed to store each coefficient of $H$                                                    | 19 |

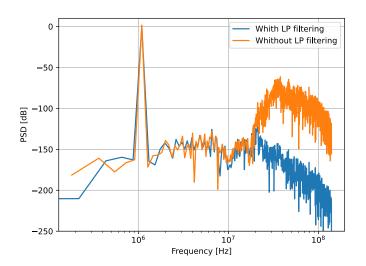

| 3.6  | PSD for $N=5~\mathrm{OSR}=7$ with and without LP filtering in the digital estimator                           | 21 |

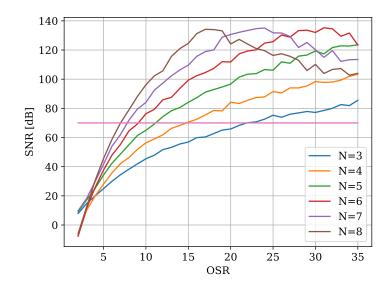

| 4.1  | SNR vs. OSR for different numbers of analog states with $K1 = 1024$                                           | 24 |

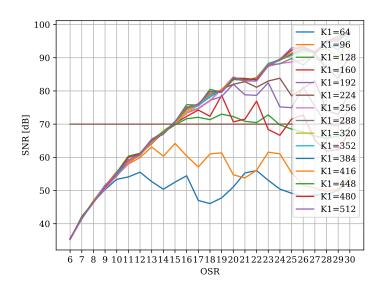

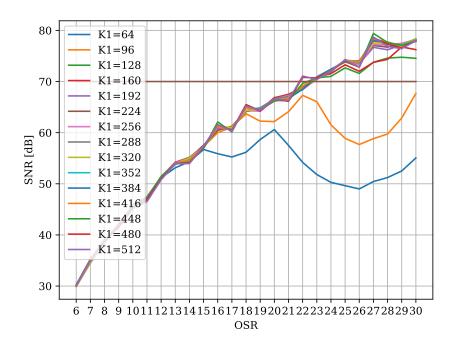

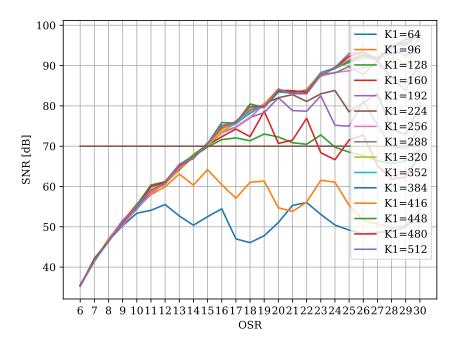

| 4.2  | SNR with different values of $K1$ and OSR for $N = 4$                                                         | 24 |

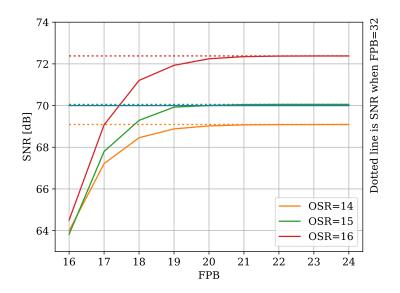

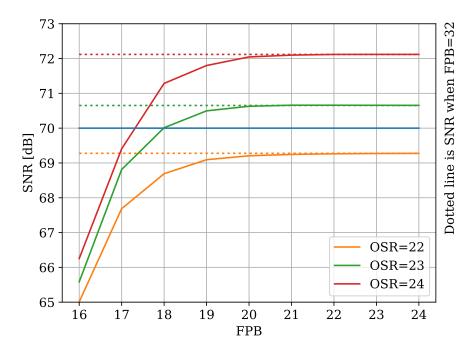

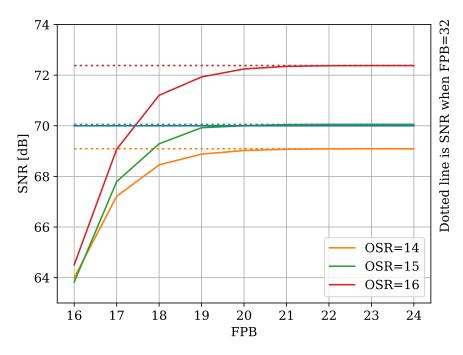

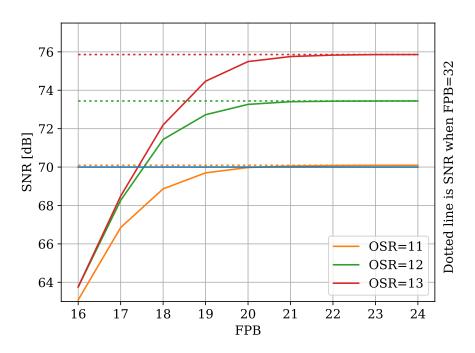

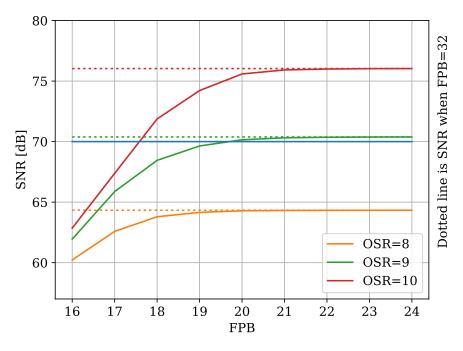

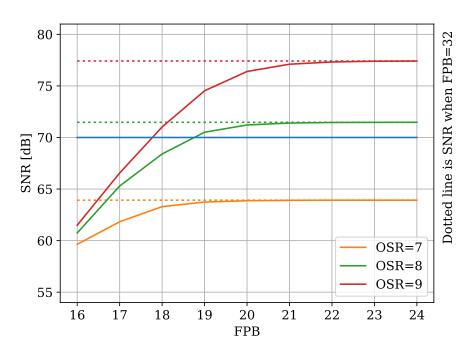

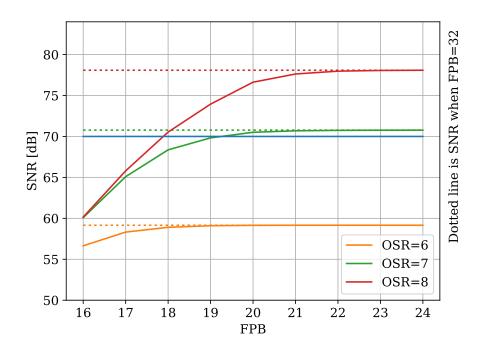

| 4.3  | SNR for different numbers of bits used for $N = 4$                                                            | 25 |

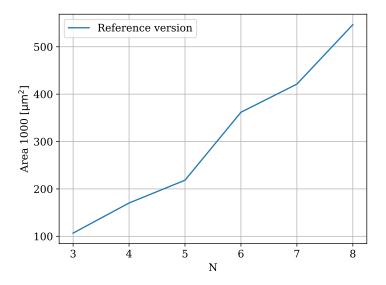

| 4.4  | The total cell area of the reference versions of the digital estimation filter                                | 27 |

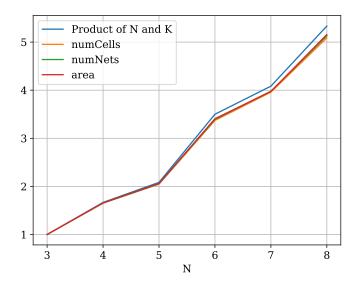

| 4.5  | The normalized area, cell count, and number of nets of the circuit compared with the normalized $N \cdot K$ . | 28 |

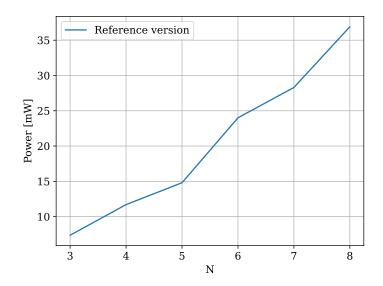

| 4.6  | Power consumption of the reference version                                                                    | 29 |

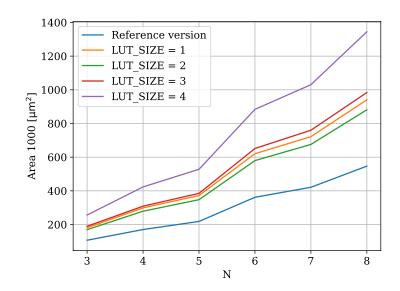

| 4.7  | Total cell area of all DE filters with LUTs                                                                   | 30 |

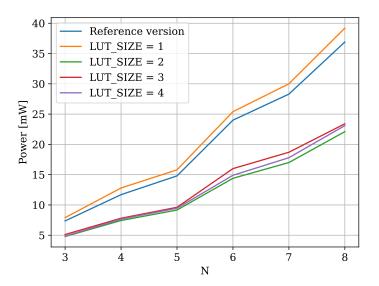

| 4.8  | Power consumption of all DE filters with LUTs                                                                 | 30 |

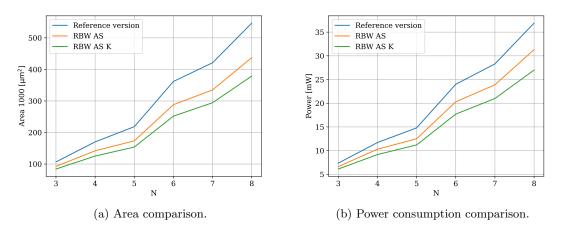

| 4.9  | Optimization with reduced bit width (RBW) compared to the reference                                           | 31 |

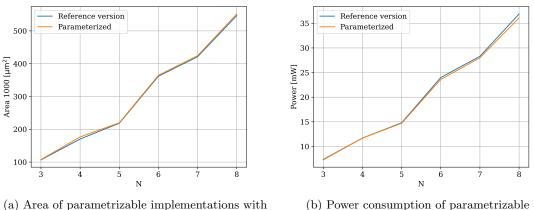

| 4.10 | Comparison between reference version and parametrizable version. $\ldots$                                     | 33 |

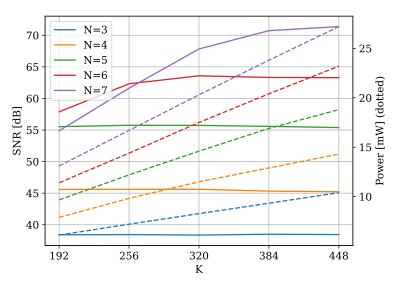

| 4.11 | Power and SNR of $N_MAX = 7$ and $K_max = 448. \dots \dots \dots \dots \dots \dots$                           | 33 |

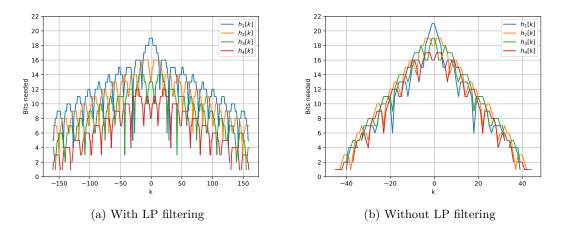

| 4.12 | Number of FPBs needed to store the filter coefficients with and without LP filtering.                         | 35 |

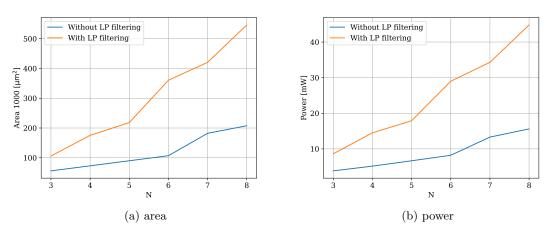

| 4.13 | Area and power with and without LP filtering in DE                                                            | 36 |

| A.1  | The format of the RISC-V R instructions [3]                                                                   | 43 |

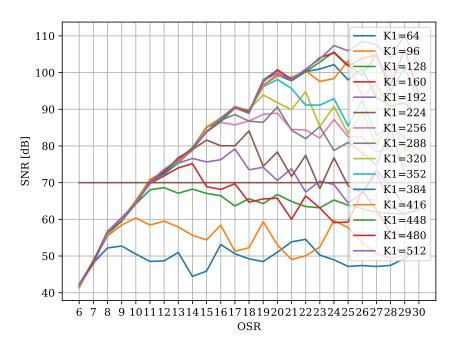

| B.1  | SNR VS OSR to find $K1$ for $N=3$                                                                             | 44 |

| B.2  | SNR VS OSR to find $K1$ for $N=4$                                                                             | 45 |

|      |                                                                                                               |    |

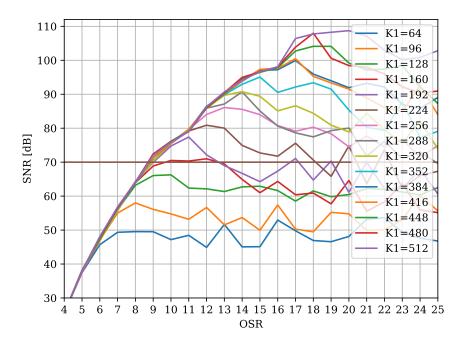

| B.3 | SNR VS OSR to find K1 for $N=5$          | 45 |

|-----|------------------------------------------|----|

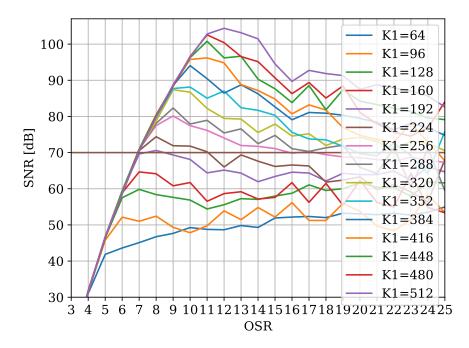

| B.4 | SNR VS OSR to find $K1$ for $N=6$        | 46 |

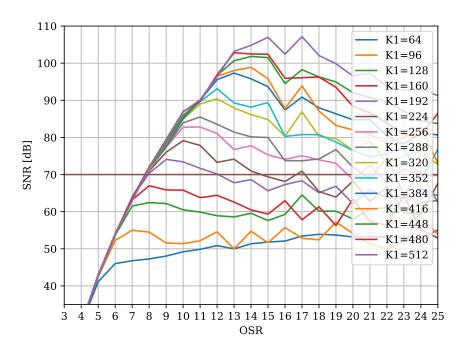

| B.5 | SNR VS OSR to find $K1$ for $N=7$        | 46 |

| B.6 | SNR VS OSR to find $K1$ for $N=8$        | 47 |

| C.1 | SNR VS OSR to find FPB for N=3           | 48 |

| C.2 | SNR VS OSR to find FPB for N=4. $\ldots$ | 49 |

| C.3 | SNR VS OSR to find FPB for N=5           | 49 |

| C.4 | SNR VS OSR to find FPB for N=6           | 50 |

| C.5 | SNR VS OSR to find FPB for N=7           | 50 |

| C.6 | SNR VS OSR to find FPB for N=8           | 51 |

| D.1 | No filtering N3                          | 52 |

| D.2 | No filtering N4                          | 53 |

| D.3 | No filtering N5                          | 53 |

| D.4 | No filtering N6                          | 54 |

| D.5 | No filtering N7                          | 54 |

| D.6 | No filtering N8                          | 55 |

# List of Tables

| 1.1 | Target specifications                                                                      | 3  |

|-----|--------------------------------------------------------------------------------------------|----|

| 2.1 | Organization of bits with fixed-point representation.                                      | 4  |

| 3.1 | The PCPI interface signals [4].                                                            | 14 |

| 3.2 | Number of bits used to store the filter coefficients with different optimizations. $\ .$ . | 19 |

| 3.3 | Implementation of LUT combining 2 samples                                                  | 20 |

| 4.1 | Requrements for the system to get 70 dB                                                    | 25 |

| A.1 | Decoding patterns for the instructions                                                     | 43 |

| E.1 | Results from all simulations                                                               | 56 |

## Chapter 1

## Introduction

As the world we live in is analog, all digital systems collecting data from the physical world need to convert those analog signals into digital representations. The conversion is achieved using an analog-to-digital converter (ADC).

The analog signals are often weak, and the translation to the digital world consumes energy. By utilizing a vast amount of resources on an ADC, the results can be precise. The power consumption, however, will also be high. In many applications, this energy consumption is critical and should be minimized.

There exist ADCs in a variety of versions, but all ADCs perform both analog signal processing and digital signal processing. The amount of each of these steps can vary, but if either the analog or the digital signal processing is inaccurate, the ADC will not be precise. Finding the optimal weighting of resources between analog and digital processing is important to reduce power consumption. Research shows that by combining a complex analog system with multiple simple digital controls, precise analog-to-digital (A/D) conversion can be accomplished [2]. This converter is called a control-bounded analog-to-digital converter (CBADC). The digital control signal is analyzed by a digital estimator to find and compute the digital representation of the analog signal.

#### 1.1 Control-Bounded Conversion

The CBADC is a new and innovative method for A/D conversion first proposed by Loeliger et al. in [5]. Later these ideas have been further developed [2, 6, 7]. The main difference between CBADC and A/D converters based on sampling theory is that CBADC separates the analog and digital parts, whereas the digital control is used to stabilize the analog system. The separation of these two parts also makes room for new innovations in both the analog and digital parts.

One problem the CBADC has a solution for is the loss of performance from imperfect components and the impact of real-world environments. A calibration based on the transfer function of the analog system will synchronize the digital estimator with the analog system. The calibration will maintain the performance of the system even if the characteristics of the analog system are changed by real-world impact.

#### 1.2 Related Work

In [5] Loeliger et al. introduced a new type of ADCs called unstable-filter ADC. This concept was developed further in [6]. The first time the control bounded A/D converter was mentioned was in the dissertation of [2]. At the date of writing, the material made by Malmberg is the main source on this topic. How the analog part of the system can be realized has been discussed by Esp Feyling

in [8].

The work presented in this thesis is based on a previous project by the authors exploring design implementations of two different digital estimation filters for the CBADC [9] on a RISC-V processor. These implementations were a single-core finite impulse response (FIR) filter and a multi-core batch filter. Both filters performed poorly, but the FIR filter showed more promising qualities in terms of potential speedup. The batch filter is thus deserted, but the goal of this project is somewhat similar. In addition to this, another study of digital estimation filter architectures has been conducted, where a hybrid estimation filter also was implemented [10].

### 1.3 Scope

The thesis aims to give insight into how power consumption and the area of the digital estimation filter of a control-bounded A/D converter are affected by design choices. The thesis discusses how the implemented filter using a RISC-V CPU and an accelerator performs with variations in hardcoded parameters and post-synthesis parameterizability. The thesis explains how parameters can be changed to optimize power consumption while maintaining a high signal-to-noise ratio (SNR). The digital implementation filter is made for a single-input A/D converter.

The digital estimation filter is implemented in multiple different versions, some with optimizations, to find how optimization techniques can reduce area or power. The thesis discusses how power consumption and area are affected by enabling post-synthesis parameterization, reduction of bit widths, and change of filter algorithm.

The designs will be synthesized on a 28 nm FDSOI technology, with a supply voltage of 0.80 V. Power estimates are generated using Synopsys PrimeTime. PrimeTime uses the design's synthesized netlist and switching activity from simulation and information from the cell library. The CPU core is an open-source CPU core, the Picorv32 [4], configured with the extension RV32E. The accelerator is designed using SystemVerilog.

The focus will be on the accelerator and the CPU. In terms of power consumption, hierarchy, or delay, the memory system is not considered. The analog system of the CBADC, its calibration, and how it interacts with the memory are not considered.

## 1.4 Main Contributions

The main contribution of this thesis is the insight into how the digital estimator part of the CBADC can be implemented and optimized when using a CPU and a connected accelerator. Some other contributions are:

- The area and power of the digital estimator are highly correlated with the number of analog states used and the filter depth. The digital estimator will be smaller and consume less power if fewer analog states are used. The area will also be reduced when the filter length is lowered.

- By pre-calculating some filter coefficients of the digital estimator and saving them as lookup tables, power can be reduced at the cost of a larger area

- Both power and area can be reduced by reducing the bit width of registers for the smaller coefficients and the size of modules computing using these coefficients.

- By making the circuit for the digital estimator configurable after synthesis, the area and power consumption are unnoticeably higher.

### 1.5 Specifications

The target bandwidth of the system is set to be 10 MHz. The Nyquist frequency is thus 20 MHz, and the minimum sampling frequency is 20 MHz. The system should have at least 70 dB SNR, and the digital estimation filter shall not be the limiting factor. The design should be parameterizable and should be implemented to work for designs with three to eight analog states. The specifications are displayed in Table 1.1.

| Table 1.1: | Target specificatio | ons. |

|------------|---------------------|------|

|------------|---------------------|------|

| Sampling frequency | $\geq 20 \text{ MHz}$ |

|--------------------|-----------------------|

| Bandwidth          | 10 MHz                |

| Analog states      | 3 - 8                 |

| SNR                | > 70  dB              |

### 1.6 Outline

The thesis starts by presenting the theory needed to understand the rest of the thesis. Chapter 2 explains different principles on how to optimize circuits for power, like clock gating, changing supply voltage, and pipelinging. In the end, details about how the control-bounded A/D converter work and details on the digital estimator are presented.

Chapter 3 explains how the digital estimation filter is implemented by first describing the CPU core and accelerator module. Then different optimizations implemented in variations of the accelerator are explained. At the end of the section, the software tools used are mentioned, and a description of how they work is provided.

The next part of the thesis presents the results from the simulations and discusses how different oversampling ratio (OSR), number of analog states N, and filter length K will impact the performance. Chapter 4 starts by presenting how the system is configured to get the target SNR and frequency and what limitations this gives. The rest of the section is looking at the performance of the different versions of the accelerator and how their optimizations reduce the power consumption of the circuitry.

In Chapter 5, a discussion of possible optimizations to reduce the size, power consumption, or increase sampling frequency is provided. The section presents possible solutions that are generally known principles on how to optimize the power of the circuit and, more specifically, how the DE of the CBADC can be optimized.

Chapter 6 concludes the thesis.

## Chapter 2

## Background

#### 2.1 Number Representation

The most common ways to represent decimal numbers in computer systems are floating-point and fixed-point representation. The main difference is that in fixed-point representation, a fixed number of bits are used to represent the integer and fraction part of the number. Whereas floating point numbers vary the precision depending on the use. Because floating-point numbers use variable numbers of bits to represent the number, they have a higher dynamic range and precision than the fixed-point representation. A drawback of floating-point representation is increased complexity, resulting in larger and often slower arithmetic logic units to do floating-point operations [11]. Recent studies have shown that utilizing fixed-point representation instead of floating-point in the MPEG-2 video compression algorithm results in a significant decrease in cycle count (75%) and an increase in energy efficiency (76%) [12].

The bits in a fixed-point number are divided into three parts: the sign bit, the integer part, and the fraction part. The organization of the bits can be seen in Table 2.1. The sign bit's value determines whether the number is negative or positive. The integer part is represented by bits that decide the integer value of the number, with the largest value it can represent being  $(2^n - 1)$ , where n is the number of bits used in the integer part. For negative numbers, the lowest number that the integer part can represent is  $-2^n$ . The remaining bits after the integer part are called the fractional bits, representing the decimal value of the number. The smallest interval between two adjacent values is determined by  $2^{-f}$ , where f represents the number of bits allocated to the fractional part. This determines the resolution limit for numerical representation and indicates the minimum step size between representable numbers. Therefore, the numerical range that can be represented is limited by  $(2^n - 2^{-f})$  and  $-2^n$ , with the step size between adjacent numbers being  $2^{-f}$ .

|                                            | ()rconizotion | of hite | with five  | d_noint | ronrocontetion  |

|--------------------------------------------|---------------|---------|------------|---------|-----------------|

| $\perp a \cup i \cup \perp i \cup \perp i$ | Organization  | OI DIUS | WIUII IIAU | u-Domu  | representation. |

|                                            |               |         |            |         |                 |

| Sign bit | Interger part | Fraction part |

|----------|---------------|---------------|

| 1-bit    | n-bits        | f-bits        |

When changing how many bits are used to store a number, sign extending needs to be done to not change the value. This means copying the most significant bit to all the newly added bits. For example, if you have a 4-bit number and want to store it in an 8-bit register, you can store the number 0110 (6) as 00000110. However, if it is a negative number, such as 1101 (-3), it is stored as 1111101. If sign extension is not done, the information that indicates whether the number is negative or positive will be lost since the leftmost bit is used to determine that.

#### 2.2 Oversampling and Subsampling

Oversampling is a technique commonly used in ADCs to improve the SNR of the resulting digital signal. The method involves sampling the analog input signal at a frequency that exceeds the Nyquist frequency. The degree of oversampling is measured by the oversampling ratio (OSR) and is calculated as

$$OSR = \frac{F_s}{F_N} = \frac{F_s}{2BW}$$

(2.1)

where  $F_s$  is the sampling frequency,  $F_N$  is the Nyquist frequency and BW is the bandwidth of the signal. By increasing the sampling frequency above the Nyquist rate, oversampling provides additional information about the analog signal, thereby reducing the effects of noise and increasing the SNR of the ADC[13].

To mitigate this computational burden, downsampling can be applied to the oversampled signal. Downsampling reduces the number of calculated samples to 1/DSR of the original signal. If the oversampling ratio is equal to the downsampling ratio DSR = OSR, the resulting sampling frequency of the ADC would be equal to the Nyquist frequency  $F_n$ . However, if DSR is greater than OSR, aliasing and information loss can occur, leading to degraded signal quality and lower SNR. The maximum DSR can be without aliasing can be given by

$$DSR = \frac{F_s}{F_N}.$$

(2.2)

#### 2.3 Power Consumption in a Digital Circuit

The power P in an electrical circuit is given by

$$P(t) = I(t)V(t), \qquad (2.3)$$

where I(t) and V(t) are the total current and voltage in the circuit at time t. The energy consumed by the circuit can be found by integrating the power over a time period T:

$$E = \int_{t=t_0}^{t_0+T} P(t)dt.$$

(2.4)

In an ideal circuit, only the charging of the capacitances in the circuit would consume power. The energy to charge one capacitor can be found using Equation 2.4. By charging a capacitor with capacitance C to the voltage  $V_C$  the energy,  $E_C$ , consumed is

$$E_C = \int_0^\infty I(t)V(t)dt = \int_0^\infty C\frac{dV}{dt}V(t)dt = C\int_0^{V_{DD}} V(t)dv = \frac{1}{2}CV_{_{DD}}^2.$$

(2.5)

In a digital circuit, the two contributors to power consumption can be divided into static power and dynamic power. The total power consumed by the circuit is then

$$P_{tot} = P_{dynamic} + P_{static}.$$

(2.6)

The static power of the circuit is leakage power that is dissipated from the circuit when a voltage is applied [1]. The static power is primarily dependent on the voltage  $V_{DD}$ , technology node, and area of the circuit. When measuring leakage, the currents can be divided into several sources of leakage currents, denoted as Isub, Igate, Ijunct, and Icont. These sources respectively represent the subthreshold current that flows through turned-off transistors, the current that leaks through the thin gate dielectric, the current that arises from diffusions between the source and drain, and the current due to contention in ratioed circuits.

The total static power consumed by the circuit is given by the product of the supply voltage VDD and the sum of these individual current components, as shown here

$$P_{static} = (I_{sub} + I_{gate} + I_{junct} + I_{cont}) \cdot V_{\scriptscriptstyle DD}.$$

(2.7)

Therefore, minimizing the individual components of static power is crucial in designing low-power digital circuits that optimize power consumption and performance.

Dynamic power, however, is the power consumed by the circuit due to the transistors switching between states. Some dynamic power is needed to charge load capacitances, but some currents are unwanted. Short-circuit currents are not wanted and are caused when a complementary pMOS and nMOS transistor are both partially turned on during switching, leading to a current flow from  $V_{DD}$  to  $V_{SS}$ .

Modern complementary metal-oxide-semiconductors (CMOS) chips consist of large amounts of transistors. The number of transistor transitions in the circuit each clock period can be described by the activity factor  $\alpha$ . The activity factor is the probability of a circuit node transitioning from 0 to 1, as this is the only time a node consumes active power. The power consumed can then be written as

$$P_{switching} = \alpha C V_{\scriptscriptstyle DD}^2 f, \qquad (2.8)$$

where f is the clock frequency. To reduce the power consumption of the circuit, either of these coefficients must be reduced. Because the voltage is squared, a change in this coefficient would have the largest impact on the power.

### 2.4 Supply Voltage Level and Device Threshold Voltage

The power consumed by the circuit is highly dependent on the supply voltage  $V_{DD}$ , as seen in Equation 2.7 and Equation 2.8. A reduction would profoundly affect the total power consumption of the circuit, as the relation is linear for the static power dissipation and quadratic for the dynamic power dissipation, even when considering modifications to the microarchitecture to maintain the performance of the circuitry.

Although having a low supply voltage is a crucial part of a low-power system, the supply voltage has limitations on how low it can be adjusted. As the supply voltage is reduced, the circuit's performance is also reduced. When the supply voltage approaches the device threshold voltage, the delay of signals through logic gates increases immensely [14]. The device threshold voltage thus limits the lowering of the supply voltage. However, reducing the threshold voltage simultaneously can maintain performance when reducing the supply voltage. This would drastically decrease the switching power of Equation 2.8. Sadly, the subthreshold leakage current will increase exponentially, leading to a higher static power consumption [14].

### 2.5 Power Gating and Clock Gating

One method of reducing the circuit's power consumption is by power gating unused parts of the chip. By cutting off power to a logic block that is not used, both the leakage power and the switching power will be removed. From Equation 2.3 and either a voltage or current is needed to draw power, and both of them will be very close to 0 if the voltage source is cut off.

When power gating, the logic block uses a virtual  $V_{DD}$  rail called  $V_{DDV}$ . Between  $V_{DD}$  and  $V_{DDV}$ , a set of header switch transistors can be turned on to raise  $V_{DDV}$  to  $V_{DD}$ . If the transistors are turned off, the connection between  $V_{DD}$  and  $V_{DDV}$  disappears, and  $V_{DD}$  will gradually fall towards ground.

The time to change between *active* and *sleep*-mode takes time and energy. In addition, some logic must be added to the chip to control the header switches. Because power gating requires extra logic, which consumes power during transitions, the size of the gated part of the logic should be significant and not be turned on and off often. When power gating, all volatile memory components of the power gated logic will lose their information. To store information needed later, state retention registers can be used at a low power cost, or the states can be stored in the memory to power gate the entire logic block. If the output from the block needs to be valid while the block is powered

down, an output isolation gate can be used.

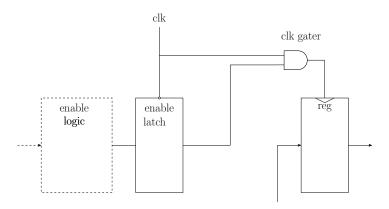

Another effective way to reduce power consumption is clock gating. The coefficient will not reduce the static power but aims to reduce the activity factor,  $\alpha$ , of Equation 2.8. Clock gating can be implemented by ANDing the clock signal with an enable signal to stop the propagation of the clock in idle logic blocks. This is shown in Figure 2.1. The enable latch is added to make the clock stable when the clock is active. The clock signal significantly impacts a circuit's power consumption, leaving clock gating as an effective method to reduce power consumption. As well as reducing power consumption of the clock tree, clock gating the input register to a logic block will prevent switching inside the block. The clock enable signal can be implemented with simple logic but can often be part of some of the most critical paths on the chip. The clock signal must remain stable while the clock is active to ensure that the datapath is not being corrupted. The clock gating can be fine-tuned, but turning off the clock for larger blocks can reduce the power consumption even more because the clock is cut off higher in the clock tree.

Figure 2.1: Clock gating circuit [1].

### 2.6 Pipelining

Replacing one large functional unit with several simpler units placed in a pipeline with registers in between reduces the critical path of the system. The result of each pipeline stage is fed into the next stage at the following clock cycle. This could allow an increase in frequency and higher computational speeds. Another possibility is to keep the low frequency and lower the voltage to reduce the power consumption. The cost of adding pipeline stages is an increase in registers and higher latencies. The pipeline stages can be hard to balance correctly, as each step should take approximately the same time to compute. With an unbalanced pipeline, the faster stages are not appropriately exploited, as the clock frequency must be low enough for the slowest stages to finish [1].

### 2.7 Parallelism

Instead of or in addition to pipelining, parallelism can be implemented to reduce power or increase the performance of a task. As with pipelining, parallelism computes several tasks at the same time. However, with parallelism, the computational blocks are identical. If one task is repeatedly performed, parallelism can be used to perform multiple of these tasks simultaneously. This could either be used to increase performance or, by lowering the clock frequency and supply voltage, reduce the power consumption. Some disadvantage of parallelizing a task is a significant increase in area, as well as more complex control logic. Using a parallelized structure will only provide a significant speedup if the data being processed is not highly dependent on intermediate answers from other calculations. If data is highly dependent, some processing units must wait for others before starting their own calculation. A method of implementing a parallel architecture is multiprocessing, either by using a SIMD (Single Input Multiple Data) processor or MIMD (Multiple Input Multiple Data) processor. The SIMD processor performs the same instruction on multiple data elements using multiple PEs (Processing Elements), requiring only a single instruction fetch and instruction decode unit. A MIMD processor, on the other hand, has multiple PEs, each having its own instruction fetch and instruction fetch and instruction fetch and thus consumes more power.

### 2.8 Accelerators and Coprocessors

An accelerator is a special-purpose function unit that can offload the processor on frequently used and compute-intensive tasks. A CPU is very flexible and easy to program. However, for some tasks, they can not provide the performance, latency, or power efficiency that is required. An accelerator can not replace the CPU, but by offloading some tasks from the CPU to the accelerator, the requirements for the CPU can be relaxed [15]. Increasing the performance of a CPU might be very costly, both in terms of area and development cost, and using an accelerator might be more cost-effective. An accelerator is designed to do a specific or small set of tasks to meet system requirements at high performance, lower cost, and reduced power consumption. A single chip can consist of multiple accelerators that increase the performance. The accelerator works independently of the CPU and has its own memory.

A coprocessor has some similarities to an accelerator, as it is a specialized hardware unit designed to improve the performance of a computer system. The main difference is that while an accelerator works independently of a CPU, the coprocessor works in conjunction with the CPU. The coprocessor works alongside the CPU and shares the same workload. The coprocessor will share the same memory as the CPU and will often be used for multiple different tasks.

In [16], the power of RISC instructions in a CPU is measured. They found that for a 32-bit addition in a 90 nm RISC processor that consumes 125 pJ, only seven pJ is the ALU operation. This means that the vast majority of the power consumption comes from overhead, like fetching the instructions, decoding, and scheduling them. Using an accelerator or a coprocessor on some tasks can drastically reduce the amount of overhead and increase performance, as well as lower power consumption.

Hardware accelerators take advantage of not being constrained by the design rules that apply to general-purpose hardware, as they only will be used for one or a small set of tasks. Design considerations not improving the general case might speed up the accelerated task considerably [15]. Accelerators can take advantage of the concepts of pipelining and parallelism described in Section 2.6 and Section 2.7. By utilizing both parallelism and pipelining, performance can be significantly increased without increasing power consumption for some tasks.

## 2.9 RISC-V

RISC-V is an open-source instruction set architecture (ISA) first introduced in 2010 [17]. It was introduced as an alternative to the other main ISAs, such as the ARM ISA and x86 used by Intel. RISC-V uses the same principles as the ARM ISA architecture, which is also a reduced instruction set architecture (RISC) and therefore has few and simple instructions, compared to a complex instruction set architecture (CISC) such as Intels x86.

RISC-V is an ISA that tries to fit in all kinds of applications. The way that is solved is by modularity. The base ISA is simple, and if the system needs more complex instructions, they can be added with extensions. The ISA is also supported on 32, 64, and 128-bit processors. The flexibility makes it suitable for small embedded systems that need to be efficient. Another advantage of the RISC-V instruction set is its large number of "free" opcodes reserved for adding custom instructions. Using an open-source ISA like RISC-V gives the opportunity of designing a new core, buying one from one of the several companies selling RISC-V IP blocks, or downloading a free core [18].

To make a power optimized system, the E extension can be used. It will reduce the number of CPU registers used from 32 to 16. This would reduce the area of the processor, but it could reduce the performance of the system. Some other normal extensions are the F extension for floating-point operations and the M extension for multiplication and division.

### 2.10 CBADC

Control-bounded analog-to-digital (A/D) conversion defines a new interface between the analog and digital worlds that utilize the strengths of both parts. This is achieved by having an unstable analog system controlled by a single or multiple digital control loops. The main contributor to the research on this topic is Malmberg in [2], which will be the primary source for this subchapter.

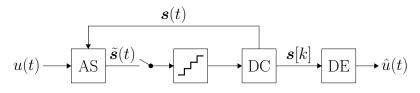

The control-bounded analog-to-digital converter (CBADC) breaks down the conversion task into three parts: analog system (AS), digital control (DC), and digital estimator (DE). The interaction between these steps is shown in Figure 2.2, where the input signal u(t) and estimate  $\hat{u}(t)$ are assumed to be scalar values. The other signals,  $\tilde{s}(t)$ , s[k] and s(t), are vector-valued. The CBADC can be implemented as an A/D converter with multiple input channels to increase overall performance [2].

Figure 2.2: The parts of the control-bounded A/D converter [2].

#### 2.10.1 Analog System

The AS is an analog continuous-time filter that enhances specific signal attributes while suppressing unwanted ones, typically by amplifying certain frequency bands and suppressing others. The complexity of the AS depends on the degree of amplification and sharpness of transitions needed. The performance of the control-bounded converter is closely linked to the AS's ability to amplify desired signal characteristics. The AS operates as an open-loop system controlled by the DC loop, meaning that stability of the AS is not necessary as it is enforced via the DC loop.

#### 2.10.2 Digital Control

The DC's task is to maintain bounded AS states by observing a sampled and quantized version of the control signal s[k] and producing a control contribution in response. The DC uses both analog-to-digital converters (ADCs) and digital-to-analog converters to create a continuous-time analog signal. In order to be deemed effective, the DC must maintain a bounded AS state for an input signal that is also bounded.

#### 2.10.3 Digital Estimator

The main task of the DE is to compute an estimate  $\hat{u}(t)$  of u(t). It uses the control signal s[k] created by the DC and its knowledge of the AS and control contribution, s(t), to generate the estimate. In [2] Malmberg uses a non-standard Kalman smoothing algorithm to calculate the samples in the DE. The algorithm is based on factor graphs, but it can be applied without extensive

knowledge of this topic, as it can be reduced to a linear filter. The estimation algorithm is reduced to three steps. The first is forward recursion

$$\vec{\boldsymbol{m}}_{k+1} \triangleq \boldsymbol{A}_f \vec{\boldsymbol{m}}_k + \boldsymbol{B}_f \boldsymbol{s}[k], \qquad (2.9)$$

then backward recursion

$$\overleftarrow{\boldsymbol{m}}_{k-1} \triangleq \boldsymbol{A}_b \overleftarrow{\boldsymbol{m}}_k + \boldsymbol{B}_b \boldsymbol{s}[k-1], \qquad (2.10)$$

and finally, the calculation of the estimates

$$\hat{u}(t_k) \triangleq \boldsymbol{W}^{\mathsf{T}}(\overleftarrow{\boldsymbol{m}}_k - \overrightarrow{\boldsymbol{m}}_k).$$

(2.11)

#### 2.10.4 FIR Filter

The digital estimator part of the CBADC can be implemented using an FIR filter. When calculating the FIR estimate, Equation 2.9, 2.10, and 2.11 are used to derive the formula. The FIR filter estimate is calculated as

$$\hat{u}(t_k) = \sum_{l_1=0}^{K_1} \overleftarrow{\boldsymbol{h}}_{l_1} \boldsymbol{s}[k+l_1] + \sum_{l_2=1}^{K_2} \overrightarrow{\boldsymbol{h}}_{l_2} \boldsymbol{s}[k-l_2]$$

(2.12)

when the samples are uniformly spaced. In Equation 2.12 the first part is calculating the backward recursion with K1 samples and the last summation is calculating the forward recursion with K2 samples. To simplify further, the forward and backward recursion can be combined. This is shown in

$$\hat{u}(t_k) = \sum_{l=-K_1}^{K_2-1} h_l s[k+l]$$

(2.13)

where all filter coefficients are given by

$$\boldsymbol{h}_{l} \triangleq \begin{cases} \boldsymbol{W}^{\mathsf{T}} \boldsymbol{A}_{b}^{l} \boldsymbol{B}_{b} & \text{if } l \geq 0, \\ -\boldsymbol{W}^{\mathsf{T}} \boldsymbol{A}_{f}^{-l+1} \boldsymbol{B}_{f} & \text{else.} \end{cases}$$

(2.14)

When the FIR filter is downsampled, the difference is that window of s that is used moves with the value of DSR instead of just 1. That leads to the estimate given by

$$\hat{u}(t_k) = \sum_{l=-K_1}^{K_2 - 1} h_l s[Rk + l]$$

(2.15)

where R is the downsampling ratio. This shows that downsampling is an effective way of calculating fewer samples without losing information.

#### 2.11 Software Tools

#### 2.11.1 CBADC Python Library

The focus of the thesis is on the digital estimator of the CBADC. To get useful input to the DE the analog system and digital control need to be simulated. To do that the python toolbox made by Malmberg is used [19]. It is used to determine the system's parameters needed to reach the target SNR and calculate the coefficients for the digital estimation filter. The tool can generate the filter coefficients the digital estimation filter uses to calculate the samples. The control signal sequence samples can be generated from a theoretical input signal. The tool provides an estimate of the input signal that can be used to verify the SystemVerilog module.

The analog frontend must be initialized when simulating the system with the Python tool. The function  $get\_leap\_frog$  with parameters OSR, N, and bandwidth is used for this. This version is

not available in the main branch of the CBADC library at the time of writing this thesis. Thus the version contained from the *veriloga\_v2* branch is used. To get the filter coefficients, the digital estimator is initialized as an FIR filter with the analog system, digital control, and filter length as inputs. The analog system and the digital control need to be simulated to get the control signal sequence. That is done by creating a simulator with the *get\_simulator* function and running it sample by sample with *next* function. When running simulations on the system an input signal must be used. The standard input when testing oversampling converters is a sinusoidal signal [2]. With the Python toolbox, this can be done by using the function *Sinusoidal* to initialize the analog signal.

#### 2.11.2 RISC-V Toolchain

The RISC-V toolchain is a C and C++ cross-compiler [20]. The toolchain can compile C or C++ files with gcc into assembly code or machine instructions. The compiled assembly code can also be converted to different memory formats depending on the use case. When this is done together with a linker script, the memory file can be used directly on a CPU. Before compiling the C code the toolchain needs to be set up to target the same parameters as the CPU the code should be run on i.e., what extensions that can be used.

#### 2.11.3 Cadence Xcelium

The simulation tool Xcelium (Cadence Xcelium Logic simulator) is used to simulate the digital system. The RTL (Register Transfer Level) simulations and the GLS (Gate Level Simulation) simulations are performed using Xcelium. The simulator tool receives SystemVerilog files as input and parameter values. The SystemVerilog files are compiled with the parameter values set to the corresponding parameter input. One of the SystemVerilog files is the top-level module, a testbench. The testbench reads the hex file (memory), which is compiled C code as explained in Section 2.11.2. When running GLS, the SystemVerilog design file is replaced with a single file, a Verilog gate level representation of the circuit [21].

Xcelium prints messages during simulation to be used for debugging. Another debugging method is by probing signals and showing the waveforms of the signals; see Section 2.11.4. The memory can be dumped after the simulation. From the dumped memory, all calculated samples can be extracted. Correct execution of the filter is checked by comparing these samples with the reference calculations provided by the Python tool [19].

All signal transitions can be written to a VCD (Value Change Dump) file. This file is used for timebased analysis in the power estimation tool. Alternatively, a SAIF (Switching Activity Interchange Format) file can be dumped to perform an average power estimation by the power estimation tool.

#### 2.11.4 Cadence SimVision

Cadence SimVision is used for debugging. SimVision is a graphical tool that can show waveforms of signals in the circuit. By storing the switching activity of some signals while running Xcelium, the waveform can be studied to find errors or verify the correct behavior of the circuit at all points in the simulation. Specific signals or all signals in a block can be shown. In SimVision, bus signals can be displayed as hexadecimal, decimal, or binary numbers to ease the reading of signal values [22].

#### 2.11.5 Synopsys Design Compiler

The synthesis tool used is Synopsys DC (Design Compiler). DC compiles the SystemVerilog RTL code into a Verilog gate level file. While compiling, DC optimizes the design by leaving out unused registers and blocks of code. If the design does not meet the timing requirements, DC alters the

circuit to provide the necessary delay optimization, if this is possible. This can lead to a higher area, and thus, the circuit will probably consume more power [23].

It compiles the RTL files using the library files for a 28nm FDSOI technology. The library files contain physical implementation details on all the logic cells that can be used. This information gives the synthesis tool enough knowledge to estimate the area of the circuit, the power consumption, and the timing of the circuit. These estimates, however, are not precise estimation results. The design must be placed and routed for the synthesis tool to find the correct area. The synthesis tool lacks the switching activity of the circuit. Thus, it cannot calculate a precise result, as it uses default switching activity for all the nets in the circuit.

#### 2.11.6 Synopsys PrimeTime

Synopsys PT (PrimeTime Static Timing Analysis) is used for power estimation. The tool receives the synthesized design, switching activity as a VCD file, and information about the specific library from the library files to estimate how much power the circuit consumes. The cell library used can be used in a low voltage threshold configuration and a regular threshold configuration. The supply voltage's lowest configuration is 0.80 V. The library is only used in the regular threshold mode, with a supply voltage of 0.80 V, as the design meets the timing requirements for all configurations.

Because the switching activity of the circuit is analyzed, the calculated results are more accurate than the results provided by the synthesis tool. The power consumed by the circuit can be estimated for individual scenarios, like if the circuit can run in various modes [24].

## Chapter 3

## Implementation

#### 3.1 FIR Filter

In Equation 2.13 s is the control signal given from the digital control, and the individual values of s can only be -1 or 1. Due to the nature of the control signal, no multiplications are needed to calculate the estimate  $\hat{u}$ . The estimate can be calculated by checking if the s-values are -1 or 1 and do subtraction or addition, respectively. Since a digital bit only can have the values 0 and 1, the value -1 will be represented by a 0, i.e., if there is a 0, a subtraction should be performed, and if there is a 1, an addition should be performed.

Each of the samples  $\hat{u}(t_k)$  is calculated independently of each other but with the same  $h_l$ . The difference between the samples is that s is updated (a new set of bits are shifted in) for each calculation of a new sample. With no dependence between the samples, the task can easily be parallelized. The number of additions done per sample is dependent on the size of the backward recursion (K1) and forward recursion (K2). The total recursion size, denoted as K, represents the sum of K1 and K2. Throughout this thesis, K1 and K2 are always equal, and only K1 will be used.

The filter coefficients, denoted as  $h_l$ , are constrained to the range between -1 to 1, rendering them highly suitable for fixed point representation. The benefit of the most common alternative, floating point, is flexibility, but when no flexibility is needed, fixed-point will yield higher performance at a lower cost. The calculations performed are only additions and subtraction of the values in  $h_l$ , and the result of these additions will never reach values higher than 1 or lower than -1, meaning no integer bits are needed. In the context of a 32-bit CPU, 32-bit fixed point numbers are the most natural choice, with 1 bit reserved for the sign, 0 for the integer part, and the remaining 31 bits allocated to the fractional part.

To reduce the size of the accelerator, fewer bits than 32 are used. Section 4.1 shows that 22 bits are the fewest bits needed for calculation without reducing the SNR substantially. If it is set lower, the SNR will be affected. Using one sign bit and none for the integer part of the number will result in the smallest possible increment between adjacent values being  $2^{-21} = 4.768 \cdot 10^{-7}$ . Using fewer bits for the numbers will reduce the size of the registers and the width of the adders, which means a significant reduction of area compared to a 32-bit implementation.

#### 3.2 CPU Core

When choosing which CPU core should be used for an application, what operations the CPU should perform is crucial to know. For the digital estimation filter of the CBADC, only a few instructions are used, but they must be performed several times per calculated sample. Only add, load, store, and branch instructions are used in the filter calculations. Consequently, when using

a RISC-V core, no extension is needed to run efficiently, and the E extension can be used without slowing down anything. For a system that only should perform a specific task, benchmark tests of cores might not be very helpful as cores perform some tasks faster than others. It is more helpful to look at how fast it can do the specific tasks it is meant to do.

The chosen CPU core for this project is Picorv32. This RISC-V core is selected for its simplicity, low area, and power usage. The reason for using RISC-V compared to other ISAs is that the standard is open source. In [25], Picorv32 is the core using the least resources and has the lowest power consumption of the tested CPU cores. The Picorv32 core is also suitable for simple operations as it can be implemented using only the E extension. It is implemented with the simplest configurations to reduce the area and power consumption. The measured cell area of the CPU is 4519  $\mu$ m<sup>2</sup> with 3972 logic cells.

Another benefit of the core is its built-in functionality for adding external logic via Pico Co-Processor Interface (PCPI) [4]. The signals of the interface can be seen in Table 3.1. The PCPI is made such that every time the core gets an instruction that it does not recognize the *pcpi\_valid* signal is asserted. The instruction is written to the *pcpi\_insn* signal, and all data the external logic needs must be at the *pcpi\_rs1* and *pcpi\_rs2* signals. Once the external logic completes the instruction, the result is written to the *pcpi\_rd* signal, and *pcpi\_ready* is activated, allowing the CPU to proceed with the following instruction. If no module has signaled it will complete the instruction, the CPU will continue with the next instruction.

| Table | 3.1: | The | PCPI | interface  | signals   | [4].    |

|-------|------|-----|------|------------|-----------|---------|

| 10010 | 0.1. |     |      | 1110011000 | Signation | 1 - 1 - |

| Name          | I/O | Width | Explanation                                                                           |

|---------------|-----|-------|---------------------------------------------------------------------------------------|

| $pcpi_valid$  | 0   | 1     | When the CPU receives an unsupported instruction, pcpi_valid is asserted.             |

| $pcpi\_insn$  | Ο   | 32    | When pcpi_valid is asserted, the unsupported instruction is broadcasted on pcpi_insn. |

| $pcpi\_rs1$   | Ο   | 32    | Contains CPU-register $rs1$ value.                                                    |

| $pcpi\_rs2$   | 0   | 32    | Contains CPU-register $rs2$ value.                                                    |

| $pcpi\_wr$    | Ι   | 1     | If the coprocessor is returning a value, pcpi_wr must be asserted.                    |

| $pcpi_rd$     | Ι   | 32    | The return value is written to pcpi_rd.                                               |

| $pcpi\_wait$  | Ι   | 1     | Is asserted if a PCPI module needs more than 16 cycles to complete the instruction.   |

| $pcpi\_ready$ | Ι   | 1     | Asserted when the coprocessor is finished executing its instruction.                  |

### 3.3 Accelerator

The Picorv32 CPU core cannot calculate samples with a frequency of 20 MHz alone. One possible solution to this problem is to use multiple CPU cores in parallel, and another solution is to connect one CPU core to a custom-made hardware component to help speed up the calculations. The benefit of using multiple CPU cores in parallel is its flexibility after synthesis. A disadvantage is that it requires more complex memory management if multiple cores access the same memories. In addition: a CPU is not specialized, and some unnecessary logic is added per extra core.

In this thesis, the proposed solution to the CPU core's lack of speed is to use a custom accelerator connected to the Picorv32 core. An accelerator design can exploit the knowledge of the system to utilize features such as parallelism and pipelining, as explained in Section 2.6 and 2.7. Multiple copies of the same module can be placed in parallel to process multiple data elements at the same time. This would enhance performance significantly if the clock frequency is the same. If power is of primary concern, instead of using one unit, five units with clock frequency  $\frac{1}{5}$  of the original unit could perform the same task with a significantly lower voltage source. Pipelining can be utilized in combination with parallelism. By having i.e. five pipeline stages, each stage only needs to compute 20% of the original computation. This could allow an increase in frequency and higher computational speeds. Another possibility is to keep the low frequency and lower the voltage to reduce the power consumption.

The digital estimation will, for each sample, add or subtract  $N \cdot K$  coefficients together. For a configuration N = 3 and K1 = 128, 768 coefficients must be summed together. Computing sums of 16 coefficients in a module, 48 modules can calculate sums of all coefficients. The 48 sums can be summed by another three modules, and the sum of the three final intermediate results can be

summed together to the estimate. Three pipeline stages are thus implemented. The first stage uses 48 parallelized blocks, and the second uses three. The final stage is not utilizing any parallelization.

Even though the Picorv32 has lower performance than the other cores it is compared to in [26], it could perform well enough when the main calculation is outsourced to an accelerator. The accelerator is connected to the Picorv32 CPU, which is used as an interface to the memory, instruction fetch unit, and control unit. The CPU decodes some of the instructions and executes them as well. To connect the custom circuit to the CPU, the PCPI is used together with some custom-made instructions. Since the implemented module is used alongside the CPU and gets data from the CPU when used, it could be considered a coprocessor to the Picorv32. However, as the module uses its own optimized memory and is designed to perform a specific task, it is referred to as an accelerator.

Typically, a Picorv32 coprocessor will assert the signal  $pcpi\_ready$  when it has completed its calculations. The CPU will wait for the assertion of  $pcpi\_ready$  before it continues its following instruction. As we want the CPU and the accelerator to work in parallel, the  $pcpi\_ready$  signal is asserted whenever the accelerator recognizes the instruction. The returned result of the calculation is thus the calculation of a delayed sample. The accelerator adds additional delay as the calculation is separated into stages, calculating intermediate results each time *start* is asserted. As long as the accelerator finishes its intermediate calculations sooner than the next custom instruction is issued, the samples will be calculated correctly. If not, the intermediate results will not be correct before passing them on to the following submodules. As the Picorv32 is a simple core executing the instructions in order, using a fixed number of cycles on each instruction, calculating the number of cycles between each issued instruction is straightforward. The number of cycles the accelerator module uses to compute the estimates can be tailored to the CPU core.

The integration of an accelerator with a CPU necessitates the establishment of a mechanism for the CPU to determine when to engage the accelerator. To achieve this, custom instructions are devised, then integrated into the toolchain to enable the compiler to recognize these instructions. The format of the custom instructions is the standard RISC-V instruction format using some unused masks. The instructions implemented are one for issuing the calculation and three different ones to load in data. All of them will, for simplicity, use two registers as input and one as output. To use these instructions together with the C-code, the assembler is modified to understand the instructions, and inline assembly in C is used to write them. Then the compiler chooses which registers to use for the operations in the custom instructions. A comprehensive breakdown of the custom instructions can be found in Appendix A.

### 3.4 SystemVerilog Modules

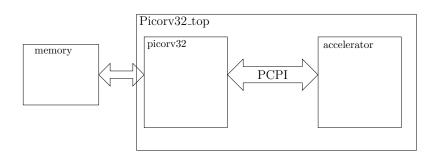

At the top level, a module connecting the Picorv32 to the accelerator can be found. While the Picorv32 is an open-source CPU, the accelerator is made by the authors of this thesis. The module consists of several submodules that together calculate the samples of the ADC. A block diagram of the top-level module is shown in Figure 3.1. The figure shows that the Picorv32 core is connected to the accelerator through the PCPI interface. It can also be seen that the memory is connected to the memory interface of the Picorv32. The memory is only simulated in the testbench and is thus outside the top-level module. Hence it will not be synthesized. All modules are implemented using the hardware description language SystemVerilog.

The different versions of the accelerators all consist of modules and submodules. The submodule lowest in the hierarchy is the adder module. This module adds together  $NUM\_ADD$  number of values. The result is computed in  $NUM\_ADD+1$  cycles. One step higher in the hierarchy, multiple of these adder modules are combined to add the results from all submodules together. Highest in the hierarchy, the matrices h and s are read in, stored in the registers S and H, and distributed to the lower levels. The top-level accelerator module controls the lower levels. The code for all the modules can be found in [27].

Figure 3.1: A block diagram of the top-level module connecting the Picorv32 CPU with the accelerator.

#### 3.4.1 Accelerator Top-Level Module

The top level of the accelerator is in charge of controlling the accelerator module, as well as storing h and shifting in s when the CPU sends the coefficients and control sequence samples. When the *pcpi\_valid* signal is set high, the module checks if the instruction is recognized as one of the custom instructions. If the instruction issued is to push a coefficient to the H matrix, the CPU will assign rs1 and rs2 (registers 1 and 2 of the CPU) to values of s. The coefficient value will be found at rs1, while the analog state the coefficient belongs to is at rs2. The coefficient will be shifted into H, which is a shift register. In Figure 3.2, a block diagram of the accelerator module is shown.

Figure 3.2: Overview of the accelerator module.

When the CPU provides new values of s, both registers are used for control sequence samples. For all configurations of the accelerator, DSR is equal to OSR. This means that DSR sets of N control sequence bits are shifted into the shift register for each calculation of a new sample. All these bits are shifted into S in one clock cycle. At the same time, the signal *start* is asserted, signaling to the submodules to start calculating the value of a sample. The delay before the next time *start* is asserted must be at least as long as it takes for the addition submodules to sum all its operands. This will be the case for the filter as long as the implemented CPU fetches new instructions and control sequence values from memory before sending it to the accelerator, and this requires enough time.

At the same time as the calculation of another sample is issued, the accelerator will write the value of the previously calculated sample to the *pcpi\_rd* for the CPU to read. The *pcpi\_ready* signal will be set to 1 to let the CPU continue the program it is executing.

In the accelerator module, a calculation module is instantiated. This module separates the calculations into separate ones for each analog state, parallelizing the calculation of each analog state. The filter coefficients and control sequence signals are routed into the corresponding module, and an adder module adds the result of each state before it is transferred to the CPU using the PCPI interface.

#### 3.4.2 Single Analog State Calculation

This module adds together all coefficients of an analog state. First, the operands and the control signal for that analog state are passed to an array of modules adding together weighted sums of the coefficients, as explained in Section 3.4.3. This is the first step of a pipeline in the single analog state calculation. Each submodule calculates the result of  $NUM\_ADD$  of the weighted coefficients and returns the sum, as explained in Section 3.4.3. The number of weighted summation submodules must be at least  $(N \cdot K)/NUM\_ADD$  to calculate all weighted additions, utilizing parallelism in the accelerator. Since the total number of coefficients is much larger than the number of additions in a single weighted summation module, at least one more pipeline stage of adder modules needs to be implemented. The adders used in this step are non-weighted adders. They add together the results from the previous stage.

#### 3.4.3 Multi-Cycle Adder

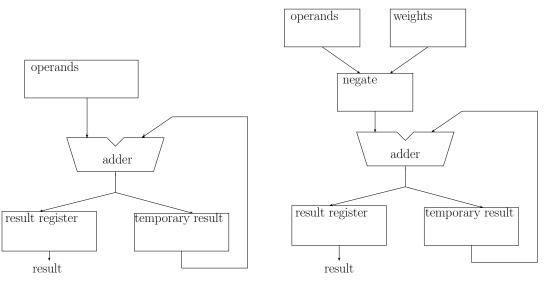

The multi-cycle adder is made in multiple versions. A simple adder that only adds numbers together, a weighted adder receiving the s-values corresponding to the h-values and calculates the weighted sum, and multiple versions using LUTs.

The first version shown in Figure 3.3a receives the operands as input. When the signal, *start*, rises, the module will start calculating the sum. One of the operands will each clock cycle be added to a register containing the temporary result. When all additions are performed, the output *res* is assigned the sum of all the operands. The module receives inputs *clk*, *resetn*, and *enable* as well. When *resetn* is 0, the module will be reset, setting *res* and the temporary result register to 0. The enable signal will stop all calculations in the module if deasserted.

(a) Simple adder module that adds operands (b) Adder module that adds weighted operands together.

Figure 3.3: Two of the adder modules implemented.

The second version shown in Figure 3.3b receives the S-values corresponding to the H-coefficients. These S-values are used as a weight for the addition. As in the first version, one coefficient is added each clock cycle. But the coefficient is weighted, where the weight 1 means use the coefficient as it is, and 0 means multiply with -1 before adding (same as subtraction). This will add some extra logic to the module.

### 3.5 Core Optimizations

#### 3.5.1 Reduced Signal Widths

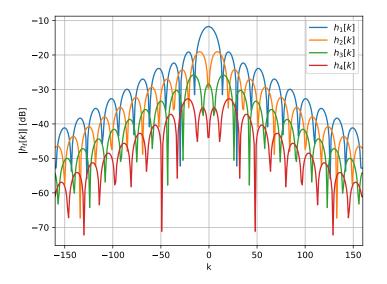

When creating filter coefficients, some observable patterns concerning the size of the numbers are found. These patterns depend on which analog state they represent and the coefficient's proximity to the filter's center. These patterns are illustrated in Figure 3.4. When introducing more analog states in a CBADC, the coefficients of new analog states are mostly lower than the corresponding coefficients in the lower analog states, where  $h_1$  are the coefficients corresponding to the lowest analog state. Therefore, a smaller number of bits can be used to represent the coefficients. When the bit-width of the coefficients is reduced, the sizes of signals and adder modules can also be reduced. By sign extending the signals when they are being added together with wider signals, the results will be the same as if all signals had the same wide bit-width, to begin with. This means that the SNR will be identical.

Figure 3.4: Absolute value of the filter coefficients when N = 4.

By reducing the size of the coefficients, the removal of the most significant bits is meant. A number that is small enough not to alter the coefficient value or intermediate results must be chosen to preserve the precision of the CBADC. Because the numbers are signed fixed-point numbers only 0s are removed from the most significant bits of positive numbers and 1s from the negative numbers. The potential decrease in area and power consumption could be significant.

From Figure 3.4 we see that for the lowest analog state,  $h_1$ , the peak coefficient values are larger than for  $h_2$ , which in turn has a larger peak than  $h_3$ . Because of this, the number of bits representing the coefficients and bit-width of calculations can be made smaller. The higher the analog state is, the fewer bits need to be used. This implementation will save both area and power by instantiating smaller H registers in the accelerator and smaller single analog state calculation modules.

As mentioned, there is likewise a trend in coefficient magnitude based on how close to the center of the filter they are. Coefficients near the center tend to be larger than those near the edges. Additional area and power can be saved by reducing the coefficients' bit-width closer to the filter's edges.

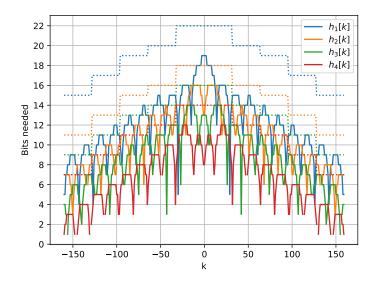

How many bits can be removed is individual for the different numbers of analog states. This means each configuration needs to have different numbers of bits removed for each analog state. To find how many are required, a plot of how many bits are used for each of the coefficients is made, and an example of the coefficients when N = 4 can be seen in Figure 3.5. Since the optimization is done both to the coefficient registers and in the adder modules, there must be some headroom to store the results of the additions, which will be larger than a single coefficient. For this reason, the dotted line is 4 bits higher than the minimum needed for only the registers.

Figure 3.5: The number of bits needed to store each coefficient of H.

How many extra bits are needed on the specific system is found through trial and error. The system with the highest number of bits removed, which does not give any changes in the calculations compared to the reference version, is used. First, the optimization for each analog state is implemented. This removes a number of bits for all coefficients and adders in a single analog state. The number of bits in the state would be set to the value at k = 0 of the dotted line in Figure 3.5. This exploits that the coefficients for the higher analog states are smaller than those for the lower states. Table 3.2 displays how many bits can be used in the modules with reduced coefficient sizes compared to the reference version without optimizations. The number of bits in the table is the total number used in the registers to represent the coefficients. The number of bits in the **H** matrix register without optimization is calculated by  $N \cdot K \cdot \text{FPB}$ , i.e.,  $3 \cdot 256 \cdot 22 = 16896$  for N = 3.

| Table 3.2: Number of bits used | to store the filter | coefficients with diffe | rent optimizations. |

|--------------------------------|---------------------|-------------------------|---------------------|

|--------------------------------|---------------------|-------------------------|---------------------|

| N  | <i>K</i> 1 | FPB | Bits with no | Bits with optimization | Bits with both | Decrease with both |

|----|------------|-----|--------------|------------------------|----------------|--------------------|

| 11 |            | ГРВ | optimization | per analog state       | optimizations  | optimizations      |

| 3  | 128        | 22  | 16896        | 14592                  | 12288          | 27.3%              |

| 4  | 160        | 22  | 28160        | 22400                  | 18048          | 35.9%              |

| 5  | 160        | 22  | 35200        | 27520                  | 22400          | 36.4%              |

| 6  | 224        | 22  | 59136        | 44800                  | 35584          | 39.8%              |

| 7  | 224        | 22  | 68992        | 54208                  | 43456          | 37.0%              |

| 8  | 256        | 22  | 90112        | 71168                  | 55808          | 38.1%              |

The calculations in the accelerator are done in blocks of 32 values. Each of these blocks are optimized to use fewer bits the farther away from the center of the filter the coefficients are. There is no optimization for the coefficients of H from -32 to 31. From the following 32 coefficients on each side of them, the number of bits is reduced, and the size of the reduction is more significant

at the edges of the filter. The number of bits used for each block is chosen by an offset to the number of bits in the largest coefficient. The reduction at the filter's edges can be more significant with a larger K or steeper decline of the absolute value of h.

#### 3.5.2 Lookup Tables