Kåre-Benjamin Hammervold Rørvik

# Next Generation Compression Algorithm

July 2022

# Next Generation Compression Algorithm

Kåre-Benjamin Hammervold Rørvik

Electronic Systems Design Submission date: July 2022 Supervisor: Milica Orlandic Co-supervisor: Lars Erik Songe Paulsen

Norwegian University of Science and Technology Department of Electronic Systems

# Preface

This master thesis is my work for the spring of 2022. It was written at the Department of Electrical Engineering at the Norwegian University of Science and Technology. The thesis is credited 30 points and is part of course TFE4930. Councillors for this master thesis were Milicia Orlandic and Lars Erik Songe Paulsen.

This thesis's objective has been to create a synthesizable hardware implementation of the compression algorithm Asymmetric Numeral Systems (ANS), specifically the uniform binary variant (uABS) of the algorithm, and verify the design. Therefore a software model should also be made and used for prototyping purposes, and as a reference. My preparational project thesis introduced the concept of compression, which will be briefly summarized in this master thesis. Furthermore, I have created two new and improved software models based on the experiences gained from the project thesis. While the software models are new and improved, they are based on the software model of the project thesis. The UVM testbench was based on strategies and methodology proposed by Cadence in their course "SystemVerilog Accelerated Verification with UVM" [1] (completed while working with ARM).

My motivation for making a hardware implementation of the uniform binary variant is twofold:

- I want to learn more about hardware implementation, design, and verification processes. My ambition is to take an arbitrary algorithm and be able to work out a fully synthesizable design, thoroughly verify it, and implement it on an FPGA.

- This uniform binary variant (uABS) of ANS does not have any online open-source hardware implementation. This lack of available open-source implementations makes the work even more exciting. My work could be a meaningful contribution to the world of hardware compressors (e.g., an accelerator in an embedded system).

# Acknowledgement

I would like to extend my deepest gratitude to my councillors Lars-Erik and Milica for being very helpful and accessible during the work of this master thesis. I am also grateful for the support and experience I received at ARM. Furthermore, I would like to thank my loving family, friends and colleagues for helping with proofreading and support.

Trondheim, 14.7.2022

Kåre-Benjamin Hammervold Rørvik

# Abstract

Compression serves an instrumental role in today's computer systems. Next generation compressors seek to bring modern innovation to the field of compression and answer today's demand for transmitting more data between devices. Although rapid development is happening with software-based compression algorithms, hardware implementations may also bear significant gains. Such gains are improved computational speed, cheaper circuitry and decreased power consumption.

Historically, entropy-based compression techniques offer compression ratios close to the theoretical limits. However, the emergence of the Asymmetric Numeral Systems (ANS) algorithm in 2014 by Jarosław Duda provides a new and innovative take on the family of compressors [2]. Contrary to numerous other entropy-based compressors, the algorithm offers highly competitive compression ratios while still boasting low computation times.

The thesis's main objective is to create a high-quality synthesizable hardware implementation of the Uniform Binary Variant (uABS) of ANS. This is done in hardware descriptive language using industry-standard tools. The final hardware implementation was achieved through an iterative process, first by implementing a higher level software model and a lower level software model, before implementing the hardware model. An iterative approach was needed due to the increased complexity of implementing a hardware design and the lack of software implementation.

The hardware implementation was later optimized to achieve higher performance and to ensure lightweight circuitry. A balance between high performance and resource usage (Power, Performance and Area) had to be found. This balance was struck without sacrificing precision and robustness, thus not adversely affecting compression ratios.

Lastly, the hardware designs were verified with UVM and non-UVM testbenches. The hardware implementation was tested for correctness, accuracy, and performance(compression ratios), among other metrics. It revealed that both timing and results satisfy the conditions of a full-fledged ANS compressor, where the hardware implementation yielded compression ratios converging the theoretical limit while maintaining low processing times. The verification process also revealed how the compressor was suited to handle a considerable amount of inaccuracy in the probability modelling.

The implementation reports revealed peak encoding and decoding speeds in the mega-bit range. Being able to handle sizeable bitstreams of data situates the implementation as useful for modern world applications, especially given its low resource requirements. Therefore, based on the implementation and verification reports results, one may conclude that the hardware implementation is successful.

# Sammendrag

Kompresjon har en viktig rolle i dagens datasystemer. Neste generasjons kompressorer forsøker å tilfredsstille dagens økende krav om å kunne håndtere stadig økende datamengder. På tross av rask utvikling innen programvarebaserte komprimeringsalgoritmer, kan maskinvareimplementasjoner gi betydelige gevinster. Eksempler på slike gevinster er forbedret beregningshastighet, rimeligere elektronikk og redusert strømforbruk.

Historisk sett tilbyr entropibaserte kompresjonsteknikker kompresjonsforhold nær de teoretiske grensene. Da Asymmetric Numeral Systems (ANS)-algoritmen av Jarosław Duda kom i 2014 fikk verden tilgang til et nytt og innovativt medlem av kompressorfamilien [2]. Sammenlignet med andre entropibaserte kompressorer tilbyr algoritmen meget konkurransedyktige kompresjonsforhold, samtidig som den kan skilte med hurtig beregning.

Avhandlingens hovedmål er å lage en syntetiserbar maskinvareimplementasjon av høy kvalitet basert på Uniform Binary Variant (uABS) av ANS. Dette gjøres ved hjelp av maskinvare-beskrivende språk og industristandardverktøy. Den endelige maskinvareimplementasjonen ble oppnådd gjennom en iterativ prosess, først ved å implementere en programvaremodell på høynivå og så en programvaremodell på lavnivå, før maskinvaremodellen ble implementert. En iterativ tilnærming ble brukt for å håndtere maskinvaredesignkompleksiteten og en grunnleggende mangel på liknende programvareimplementasjoner. Maskinvareimplementasjonen ble senere optimalisert for å oppnå høyere ytelse og for å sikre et enkelt kretsdesign samt en skalerbar arkitektur. Det måtte samtidig oppnås en god balanse mellom forbruk, ytelse og elektronikkareal (PPA). Denne balansen ble oppnådd uten å måtte ofre presisjon og robusthet, og uten negative påvirkning på kompresjonsforholdet. Til slutt ble maskinvaredesignene verifisert gjennom bruk av både UVM og ikke-UVM testbenker. Maskinvareimplementasjonen ble blant annet undersøkt med tanke på korrekthet, nøyaktighet og ytelse (kompresjonsforhold). Verifikasjonen viste at både timing og kompresjonsresultater tilfredsstiller kravene til en fullverdig ANS-kompressor. Den endelige maskinvareimplementasjonen ga kompresjonsforhold som konvergerte mot den teoretiske grensen, samtidig som lave behandlingstider ble beholdt. Verifikasjonsprosessen viste også at kompressoren kunne håndtere en betydelig økning i unøyaktighet i sannsynlighetsmodelleringen.

Implementasjonsrapportene viste encodings- og dekodingshastigheter i megabitområdet. Selv uten ytterligere optimaliseringer vil den dermed kunne håndtere betraktelige bitstrømmer med data, og gjøre implementasjonen nyttig for moderne anvendelser, spesielt gitt det lave ressursbehovet. Ut fra resultatene av implementasjons- og verifikasjonsrapportene kan det derfor konkluderes med en vellykket maskinvareimplementasjon.

# Contents

| 1 | Intr | roduction 1                                        |                                                 |    |  |  |  |  |  |  |

|---|------|----------------------------------------------------|-------------------------------------------------|----|--|--|--|--|--|--|

|   | 1.1  | Backg                                              | round                                           | 1  |  |  |  |  |  |  |

|   | 1.2  | .2 Compression uses cases with room for innovation |                                                 |    |  |  |  |  |  |  |

|   | 1.3  | New a                                              | and innovative compression candidates           | 2  |  |  |  |  |  |  |

|   | 1.4  | Reseau                                             | rch questions and contributions                 | 2  |  |  |  |  |  |  |

| 2 | The  | oretica                                            | al background                                   | 3  |  |  |  |  |  |  |

|   | 2.1  | Comp                                               | ression theory                                  | 3  |  |  |  |  |  |  |

|   |      | 2.1.1                                              | Data compression                                | 3  |  |  |  |  |  |  |

|   |      | 2.1.2                                              | Shannon's source coding theorem                 | 4  |  |  |  |  |  |  |

|   |      | 2.1.3                                              | Lossless compression                            | 4  |  |  |  |  |  |  |

|   |      | 2.1.4                                              | Lossy compression                               | 4  |  |  |  |  |  |  |

|   | 2.2  | Asymi                                              | metric Numeral Systems                          | 5  |  |  |  |  |  |  |

|   |      | 2.2.1                                              | Solving issues of basic ANS                     | 6  |  |  |  |  |  |  |

|   |      | 2.2.2                                              | uABS                                            | 6  |  |  |  |  |  |  |

|   | 2.3  | Genera                                             | al HW implementation                            | 8  |  |  |  |  |  |  |

|   |      | 2.3.1                                              | FPGA                                            | 8  |  |  |  |  |  |  |

|   |      | 2.3.2                                              | Xilinx target FPGAs                             | 9  |  |  |  |  |  |  |

|   |      | 2.3.3                                              | Briefly about thermal considerations            | 11 |  |  |  |  |  |  |

|   |      | 2.3.4                                              | Timing: Setup and hold slack                    | 12 |  |  |  |  |  |  |

|   |      | 2.3.5                                              | The Ready-Valid data interfacing design pattern | 12 |  |  |  |  |  |  |

|   |      | 2.3.6                                              | FPGA divide library                             | 14 |  |  |  |  |  |  |

|   |      | 2.3.7                                              | FPGAs and fixed point numbers                   | 15 |  |  |  |  |  |  |

|   | 2.4  | Using                                              | SystemVerilog for synthesis                     | 16 |  |  |  |  |  |  |

|   | 2.5  | State                                              | machines                                        | 17 |  |  |  |  |  |  |

|   | 2.6  | 2.6 UVM                                            |                                                 |    |  |  |  |  |  |  |

|   |      | 2.6.1                                              | Standard UVM testbench architecture             | 18 |  |  |  |  |  |  |

|   |      | 2.6.2                                              | UVM testbench                                   | 18 |  |  |  |  |  |  |

|   |      | 2.6.3                                              | UVM test                                        | 19 |  |  |  |  |  |  |

|   |      | 2.6.4                                              | UVM environment                                 | 19 |  |  |  |  |  |  |

|   |      | 2.6.5                                              | UVM scoreboard                                  | 19 |  |  |  |  |  |  |

|   |      | 2.6.6                                              | UVM agent                                       | 19 |  |  |  |  |  |  |

|   |      | 2.6.7                                              | UVM sequencer                                   | 20 |  |  |  |  |  |  |

|   |      | 2.6.8                                              | UVM sequence                                    | 20 |  |  |  |  |  |  |

|   |                | 2.6.9  | UVM di     | river                                                                                                                                               | 20        |

|---|----------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|   |                | 2.6.10 | UVM m      | onitor                                                                                                                                              | 20        |

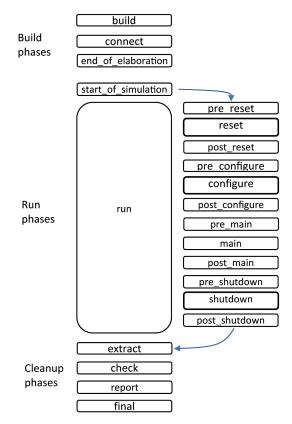

|   |                | 2.6.11 | UVM pl     | hases                                                                                                                                               | 20        |

| 3 | Imp            | lemen  | tation     |                                                                                                                                                     | <b>21</b> |

|   | 3.1            | Introd | uction to  | implementation                                                                                                                                      | 21        |

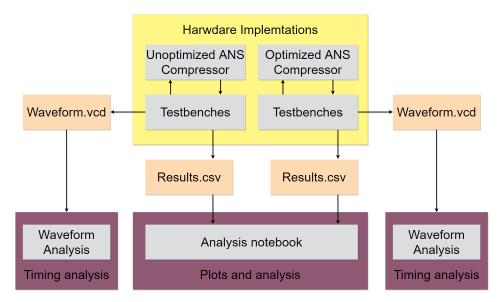

|   | 3.2            | System | ns overvie | 2w                                                                                                                                                  | 23        |

|   | 3.3            | Softwa | re model   | 8                                                                                                                                                   | 25        |

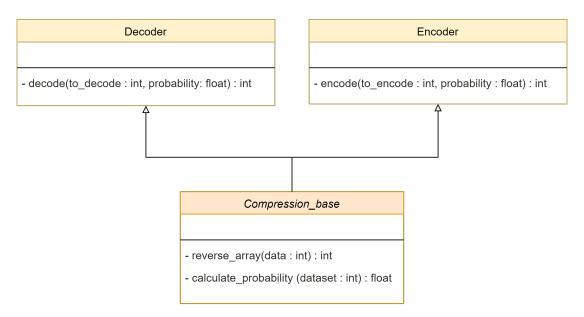

|   |                | 3.3.1  | ANS C-     | $\vdash + \text{ software Model} \dots \dots$ | 25        |

|   |                |        | 3.3.1.1    | Creating the ANS C++ software Model                                                                                                                 | 25        |

|   |                |        | 3.3.1.2    | ANS C++ software model testbench                                                                                                                    | 28        |

|   |                | 3.3.2  | ANS Sy     | stemVerilog software Model                                                                                                                          | 28        |

|   |                |        | 3.3.2.1    | Creating the ANS SystemVerilog software model                                                                                                       | 29        |

|   |                |        | 3.3.2.2    | ANS SV model testbench                                                                                                                              | 29        |

|   | 3.4            | Hardw  | are imple  | ementations                                                                                                                                         | 30        |

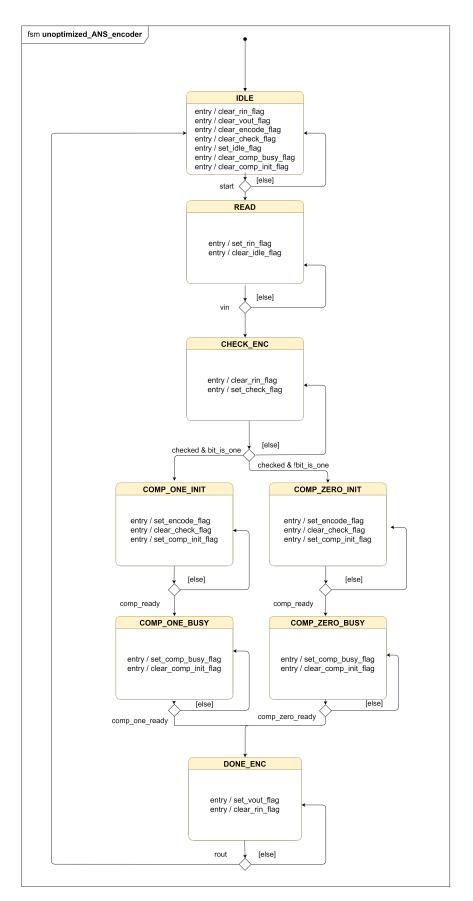

|   |                | 3.4.1  | Unoptin    | nized ANS compressor                                                                                                                                | 30        |

|   |                |        | 3.4.1.1    | Overview                                                                                                                                            | 30        |

|   |                |        | 3.4.1.2    | Interface                                                                                                                                           | 31        |

|   |                |        | 3.4.1.3    | Finite State Machine                                                                                                                                | 31        |

|   |                |        | 3.4.1.4    | Arithmetic                                                                                                                                          | 35        |

|   |                |        | 3.4.1.5    | Preparations for Synthesis and Implementations                                                                                                      | 35        |

|   |                | 3.4.2  | Optimiz    | ed ANS compressor                                                                                                                                   | 36        |

|   |                |        | 3.4.2.1    | Overview                                                                                                                                            | 36        |

|   |                |        | 3.4.2.2    | Interface                                                                                                                                           | 36        |

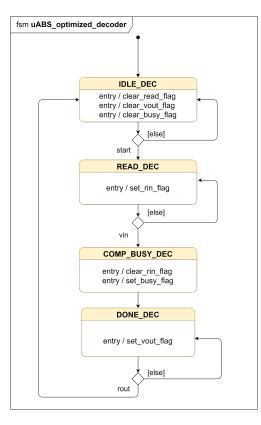

|   |                |        | 3.4.2.3    | Decoder                                                                                                                                             | 37        |

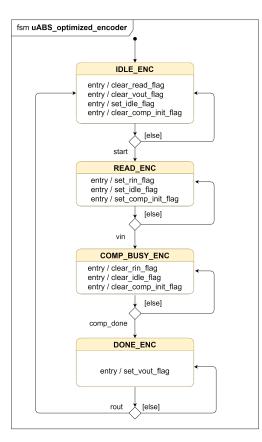

|   |                |        | 3.4.2.4    | Encoder                                                                                                                                             | 37        |

|   |                |        | 3.4.2.5    | FSM                                                                                                                                                 | 37        |

|   |                |        | 3.4.2.6    | Arithmetic                                                                                                                                          | 39        |

|   |                |        | 3.4.2.7    | Preparations for synthesis and implementations $\ldots \ldots \ldots \ldots$                                                                        | 39        |

|   |                | 3.4.3  | Verificat  | ion of Hardware Implementations                                                                                                                     | 39        |

|   |                |        | 3.4.3.1    | Master testbench                                                                                                                                    | 40        |

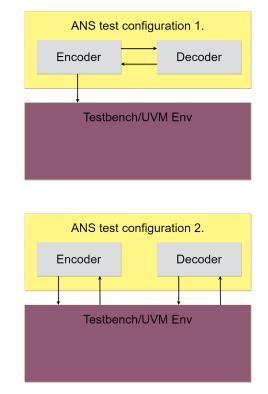

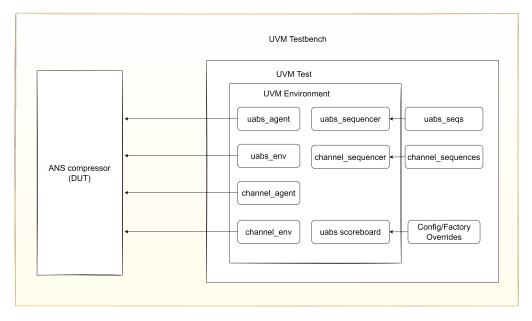

|   |                |        | 3.4.3.2    | UVM testbench                                                                                                                                       | 40        |

| 4 | $\mathbf{Res}$ | ults   |            |                                                                                                                                                     | 44        |

|   | 4.1            | Introd | uction to  | results                                                                                                                                             | 44        |

|   | 4.2            | Param  | eters      |                                                                                                                                                     | 45        |

|   |                |        |            |                                                                                                                                                     |           |

| 4.3 | Optim                    | Optimized ANS compressor hardware implementation 4        |          |  |  |  |  |  |  |  |  |

|-----|--------------------------|-----------------------------------------------------------|----------|--|--|--|--|--|--|--|--|

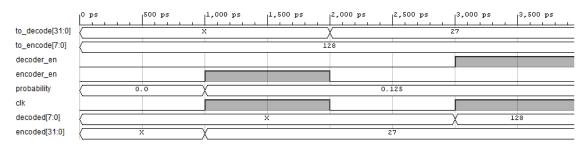

|     | 4.3.1                    | Waveforms and verification                                |          |  |  |  |  |  |  |  |  |

|     |                          | 4.3.1.1 UVM environment reports                           | 46       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.1.2 Master testbench reports                          | 47       |  |  |  |  |  |  |  |  |

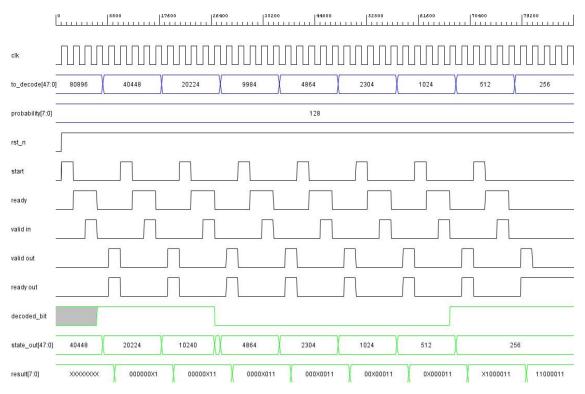

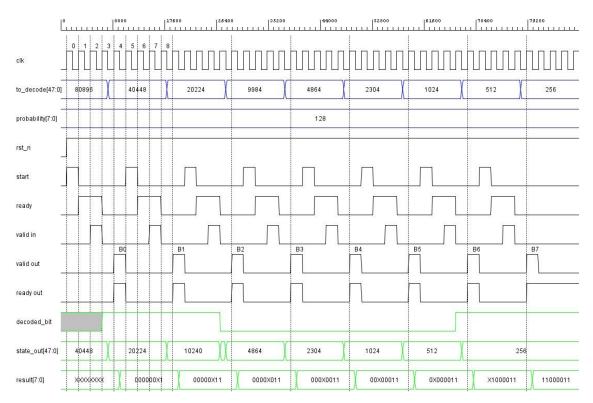

|     |                          | 4.3.1.3 Decoder waveforms                                 | 48       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.1.4 Encoder waveforms                                 | 49       |  |  |  |  |  |  |  |  |

|     | 4.3.2                    | Synthesis and implementation reports                      | 51       |  |  |  |  |  |  |  |  |

|     | 4.3.3                    | FPGA Zynq UltraScale+ ZCU106                              | 51       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.3.1 Decoder                                           | 52       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.3.2 Encoder                                           | 53       |  |  |  |  |  |  |  |  |

|     | 4.3.4                    | Porting the solution to the FPGA Devboard Spartan-7-SP701 | 54       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.4.1 Decoder                                           | 54       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.4.2 Encoder                                           | 55       |  |  |  |  |  |  |  |  |

|     | 4.3.5                    | Performance analysis                                      | 57       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.5.1 Encoding and decoding speeds                      | 57       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.5.2 Compression behavior                              | 58       |  |  |  |  |  |  |  |  |

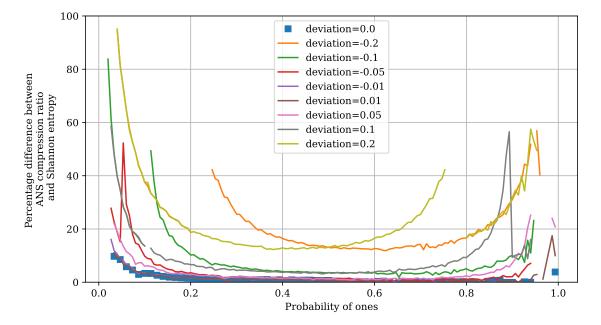

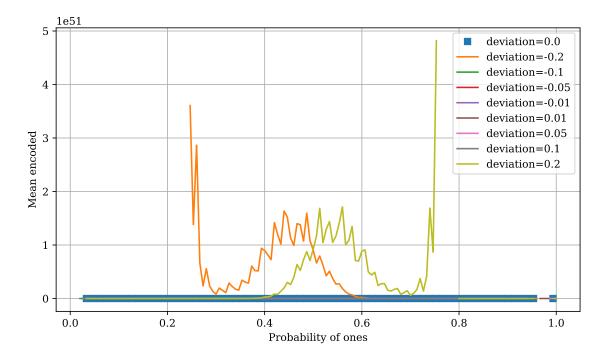

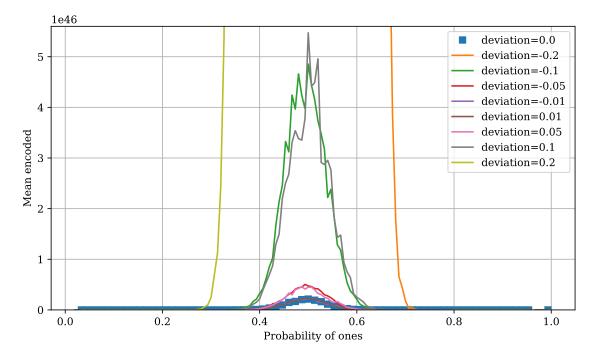

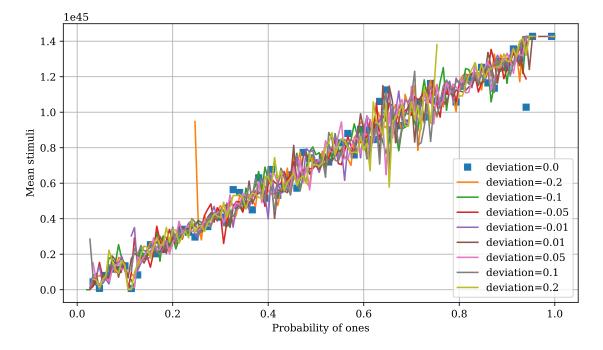

|     |                          | 4.3.5.3 Compression behavior with probability deviations  | 61       |  |  |  |  |  |  |  |  |

|     | 4.3.6                    | RTL analysis schematics                                   | 69       |  |  |  |  |  |  |  |  |

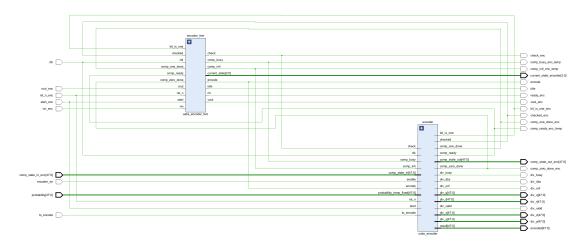

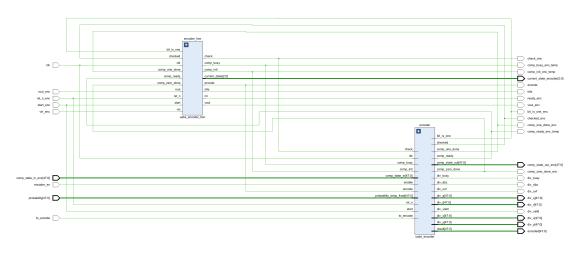

|     |                          | 4.3.6.1 Decoder                                           | 69       |  |  |  |  |  |  |  |  |

|     |                          | 4.3.6.2 Encoder                                           | 69       |  |  |  |  |  |  |  |  |

| 4.4 | Unopt                    | otimized ANS compressor hardware implementation           | 72       |  |  |  |  |  |  |  |  |

|     | 4.4.1                    | RTL Analysis schematics                                   | 72       |  |  |  |  |  |  |  |  |

|     |                          | 4.4.1.1 Decoder                                           | 72       |  |  |  |  |  |  |  |  |

|     |                          | 4.4.1.2 Encoder                                           | 72       |  |  |  |  |  |  |  |  |

| 4.5 | Softwa                   | vare models                                               | 73       |  |  |  |  |  |  |  |  |

|     | 4.5.1                    | C++ software model                                        | 73       |  |  |  |  |  |  |  |  |

|     | 4.5.2                    | SystemVerilog software model                              | 73       |  |  |  |  |  |  |  |  |

| Die | cussior                  | 5P                                                        | 74       |  |  |  |  |  |  |  |  |

| 5.1 |                          | all evaluation                                            | 74       |  |  |  |  |  |  |  |  |

| 5.2 |                          | ation of the compression behavior                         | 75       |  |  |  |  |  |  |  |  |

| 5.2 |                          |                                                           |          |  |  |  |  |  |  |  |  |

| 5.3 |                          | s of errors in compression                                | 75<br>75 |  |  |  |  |  |  |  |  |

| 5.4 |                          | t of BIT_WIDTH and FBITS                                  | 75<br>76 |  |  |  |  |  |  |  |  |

| 5.6 |                          |                                                           |          |  |  |  |  |  |  |  |  |

| 0.0 | Evaluation of FSMs    76 |                                                           |          |  |  |  |  |  |  |  |  |

$\mathbf{5}$

|    | 5.7 Interface                                                            | . 76  |

|----|--------------------------------------------------------------------------|-------|

|    | 5.8 Evaluation of the Ready/Valid interface                              | . 77  |

|    | 5.9 Clock gating and further power saving                                | . 77  |

|    | 5.10 Effect of chosen FPGA on performance, utilization and power results | . 78  |

|    | 5.11 Evaluation of testbench                                             | . 78  |

|    | 5.12 Issues during simulation                                            | . 79  |

|    | 5.13 Analysis of RTL views                                               | . 79  |

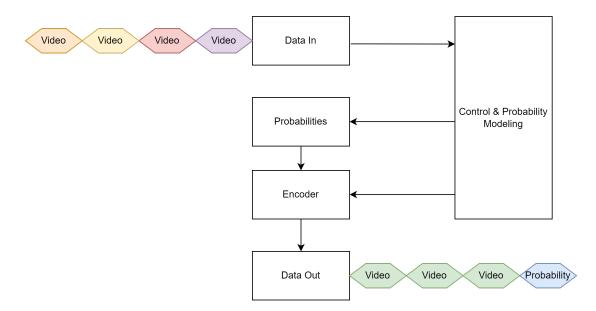

|    | 5.14 The ANS compressor as part of a larger system.                      | . 79  |

|    | 5.15 Experimental software Models                                        | . 81  |

| 6  | Further work                                                             | 81    |

| 7  | Conclusion                                                               | 82    |

| Re | eferences                                                                | 84    |

| Aj | ppendix A Optimized ANS compressor - decoder                             | 87    |

| Aj | ppendix B Optimized ANS compressor - encoder                             | 92    |

| Aj | ppendix C Master testbench                                               | 99    |

| A  | ppendix D UVM testbench                                                  | 105   |

|    | D.1 UVM uABS                                                             | . 105 |

|    | D.2 UVM testbench                                                        | . 122 |

| Aj | ppendix E SystemVerilog software model, both encoder and decoder         | 127   |

| Aj | ppendix F $C++$ software model, both encoder and decoder                 | 130   |

| A  | ppendix G Unoptimized ANS compressor                                     | 137   |

# 1 Introduction

# 1.1 Background

Data storage and communication capacity are always limited and associated with a cost. A wide range of computing devices uses compression, ranging from powerful supercomputers to Internet of Things (IoT) microcontrollers and nodes. With the desire of transmitting more data between devices, compression of data becomes even more relevant. Compression can be implemented in software (SW) or hardware (HW), with compression innovation taking occurring more rapidly in software.

Software compression utilizes the most expensive computing resources on devices, such as the central processing units (CPUs, computing cores) and the graphical processing units (GPUs). These resources must also serve other tasks, such as the user applications (apps) and the operating system (OS).

Even though software compression may offer real savings in terms of storage and data transfer if used extensively, it does take a heavy toll on both processing capacity and associated power consumption.

User perception is also a practical side of it, especially noticeable for portable equipment where higher power consumption translates into shorter runs per charge and where a sluggish response may be at least partly due to background processes such as data compression when employed there.

The environmental footprint of software compression is also significant, both in terms of the power consumption (and associated  $CO_2$  emissions) and for the manufacture of both new equipment and the recycling of old. Moreover, it appears fair to assume that the upgrade frequency of computing devices is somewhat higher in the lack of hardware compression, with compression as an extra burden on top of running apps and OS.

Implementing compression in hardware therefore potentially offers tangible relief on all those accounts. Moreover, hardware compression ultimately places electronics designers, design houses, and chipmakers in a very privileged position, being able to implement and market well-designed hardware-based compression solutions that will benefit users, enterprises, manufacturers, and the environment.

## 1.2 Compression uses cases with room for innovation

There are two categories of compression algorithms: The lossless and the lossy. The lossy ones might optimize away some of the original data, preserving just as much as is necessary to be of practical use when decompressed. Many hardware compressor designs exist, supporting compression standards such as AV1, VP9, AVS2, H.264, and H.265, which are a vital integral part of today's photographic equipment, video cameras, and smartphones [3]. No one would even suggest reverting to using general computing cores for such compression operations today, with increased cost, size, and power consumption.

Lossless compression is a strong contender for general hardware-based compression implementations. As there are also many use cases where lossy compression is undesirable. Lossless compression algorithms alleviate transfer and storage bottlenecks while unambiguously reproducing the original data's exact representation.

Some of the lossless compression algorithms are limited in terms of performance or unfit for random binary data. One reason is that many well-known techniques from lossless compression perform best on higher-level data with specific characteristics and use cases, such as text compression. However, they will not compress well in other settings and are typically demanding in terms of processing requirements and memory usage. They play an important role in the compression ecosystem, however, does not cover all use cases. In particular, the lowest level of data, where there might be typically relatively random binary datasets, with large companies keeping much of their accelerators proprietary. This use case has room for innovation and improvement and is an especially important use case for hardware compressors as naturally find themselves handling binary data.

## 1.3 New and innovative compression candidates

Entropy-based compression techniques are known to offer compression close to theoretical limits with relatively lightweight computations. The Asymmetric Numeral Systems (ANS) algorithm by Jarosław Duda (2014) offers highly competitive compression ratios while still boasting efficient computation. Whereas there are a handful of variants, such as uABS and rANS with different features and advantages. It is a family of compressors being praised highly as being next generation and seeing many new design additions in the past years.

The ANS entropy coding principles have also influenced previously existing compression algorithms and have influenced many of the most proliferated compression standards, such as JPEG XL, Facebook/Zstandard, Google pik, Apple/LZFSE, as well as the lowest layers of compression found in iOS and macOS [4]. Whereas macOS squarely points toward the benefits of a hardware compressor implementation as well, operating at the bottom layer of the OS's themselves to the benefit of all applications running on them.

ANS performs well with relatively random data, even those featuring an uneven distribution of 1s and 0s. The so-called uniform binary variant (uABS) of ANS works well for the compression of binary data (interpreted as natural numbers) as long as the probability of the number of 1s and 0s is known. The probability can easily be computed, making a software implementation relatively straightforward to model. Whereas the algorithm itself consists dominantly of arithmetic operations and conditional statements, which are convenient to model in software.

Overall, uABS appears to be well-posed for successful low-power hardware implementation. However, no hardware implementations appear to be published or readily available for reuse as of now. This is illustrated by worldwide web searches and using database queries of reusable electronic designs such as [5].

Narrowing the research to uABS appears to therefore be a good choice, focusing on the implementation challenges since possible alternative compressors have been well covered in the preceding project thesis [6].

## 1.4 Research questions and contributions

The thesis's main objective is to create a high-quality synthesizable hardware implementation of the compression algorithm Asymmetric Numeral Systems (ANS) using hardware descriptive language. Specifically the uniform binary variant of the algorithm, and to verify the design. Based on this following research questions were posed:

- Is it possible to design a modular hardware implementation of the uABS algorithm using industry-standard tools which are:

- Configurable,

- performs close to the theoretical limits of entropy-based compression

- and are easily implementable on commercial FPGA?

- Is it possible to design a hardware decoder performant enough to be useful to decode large streams of data at a sufficient speed for real use cases?

- Will the hardware compressor be robust enough to compress datasets with inaccurate probability modelling?

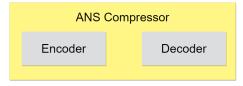

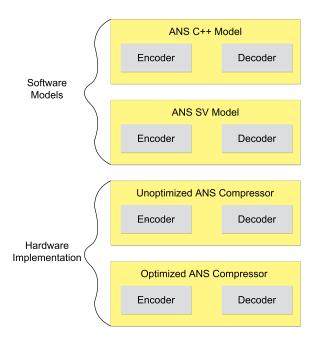

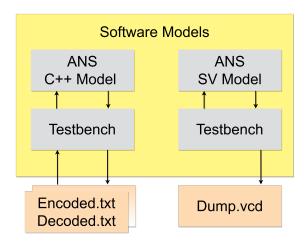

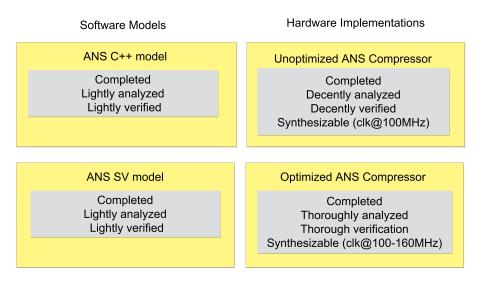

The workflow of this thesis was to first implement higher-level models, before moving to the low level of abstraction with the hardware implementations. This led to four iterations: High-level software model (C++ model), low-level software model (SV model), unoptimized ANS hardware compressor and optimized ANS hardware compressor. Each preceding step was based on the previous one, and between each step, comparisons were made to ensure the robustness and accuracy of the solution. This led to the following contributions:

- An iterative approach towards implementing an optimized hardware design, basing it on high-level and low-level software implementations, and their performance.

- A high-performance open source modular plug-and-play hardware implementation of the uABS algorithm using industry-standard tools, which was fully synthesized in an EDA. It is also easily implementable on commercial FPGA, with a configurable encoder/decoder module. The final hardware implementation was optimised in order to achieve higher performance and make the circuitry lightweight, compared to an unoptimized implementation. In order to achieve this, a trade-off analysis was performed. The analysis balances high performance and low resource usage while keeping the compressor high in efficiency and accuracy.

- The optimized and unoptimized implementations were verified through a testbench. The top testbench was simulated using a reliable verification methodology (UVM). The simulations verified that:

- Both timing and behavior act according to the requirements of a full-fledged ANS compressor. With performance approaching the theoretical limits of entropy-based compression.

- Peak encoding and decoding speeds were measured to be in the mega-bit range, making them useful for modern world applications. The decoder in particular is expected to perform well enough to decode streams of video.

- It was also proven that the ANS compressor achieves accurate compression behaviour even with inaccurate probability modelling (up to  $\pm 10\%$  deviation in probability).

- Implementation of two easily configurable software reference models, one high and low level, in a well-designed software simulation environment. Both software models were verified through similar testbenches as the hardware model, where the testbench tested for correct compression behaviour.

# 2 Theoretical background

## 2.1 Compression theory

Some key aspects of compression theory are presented to provide the reader with a background for understanding the compression algorithms, which will be briefly presented thereafter. In addition to those presented below, the preparatory project thesis [6] delves into more detail on other compression algorithms.

#### 2.1.1 Data compression

The hunger for storage and communication bandwidth is high and ever increasing, due to a broad range of data intensive applications ranging from high-power supercomputer scientific applications to ultra-low-power Internet of things (IoT) applications.

Reducing the number of bits stored or transferred, and still being able to retrieve or receive them exactly as they were originally (lossless) or sufficiently recognizable (lossy) is the goal of all compression/decompression techniques [7]. There are several ways to achieve data compression, with differences in areas such as implementation complexity and suitability for different types of data [8]. The following is a brief summary of notable compression algorithms. Special emphasis is given to the Asymmetric Numeral System (ANS) and uABS (uniform binary variant) [2], the latter being the main focus of the hardware implementation of this thesis.

Compression algorithms are implemented in ways that take advantage of characteristics of the input data, such as the type of data and how the different symbols of the data type occur in the input data. Data may exhibit repeating sequences of data and statistical properties of data, such as uniformly or non-uniformly distributed symbols.

In all cases, the capabilities of compression techniques are expressed using a few important metrics. One of them is the compression ratio, which is the ratio of uncompressed data versus compressed data size [9], given by equation (1):

$$Compression ratio = \frac{UncompressedSize}{CompressedSize}$$

(1)

Alternatively, in order to compare the compression ratio to the Shannon source coding theorem[10] directly, the compression ratio may be expressed as, as shown in equation (2):

$$Compression ratio = \frac{CompressedSize}{UncompressedSize}$$

(2)

Within the field of data communication, compression will be relative to the data rate [11, 12] of the data passing by as shown in equation (3):

$$CompressionRatio = \frac{UncompressedDataRate}{CompressedDataRate}$$

(3)

#### 2.1.2 Shannon's source coding theorem

Shannon's source coding theorem [10] states that the smallest possible code that can express a given piece of information (such as string of symbols) with sufficient precision and reliably is limited, thus defining a theoretical limit of data compression. The average number of bits per symbol must be equal to or larger than this limit [13], as shown in equation (4) below, with the index "i" representing a given symbol to get coded with a given probability p, which, in summation provides the entropy H over all possible symbols X:

$$H(X) = -\sum_{i=1}^{n} p_i \log_2(p_i)$$

(4)

#### 2.1.3 Lossless compression

Shannon's discussion on entropy provides a solid groundwork for how much we can compress original data composed of discrete data, yet reproduce them exactly and losslessly. Examples of discrete data are human readable texts, CAD drawings, computer software and control signals.

#### 2.1.4 Lossy compression

Lossy compression allows for and assumes that a certain degree of information will be lost during the compression/decompression cycle, yet with a decompressed variant of the original data sufficiently similar to be of practical use [14]. The compression task thus relies on eliminating the least necessary information, in essence reducing the entropy of the data. Lossy compression is therefore used where absolute accuracy is not required and/or feasible. One example is in the use of digital

audio, where the level of compression can increase while still maintaining a sufficient degree of entropy to afford a good reproduction of the original [15].

#### 2.2 Asymmetric Numeral Systems

The Asymmetric Numeral Systems (ANS) lossless entropy based encoding method [16] describes the conversion of sequences of symbols (messages) originating from a given alphabet, to natural numbers. This is done using statistical compression schemes, where the most frequent symbols are mapped in an optimal fashion onto shorter (i.e. small) natural numbers, and less frequent symbols onto longer natural numbers, thus providing high compression ratios if the implementation works properly[13].

As an introduction to elements of the ANS scheme, a simple but still fully working encoder, assuming a binary string with equal probability of the two symbols '0' and '1' can be demonstrated. The corresponding natural number of the string can be coded, one bit at a time based upon the input string of bits  $b_1b_2b_3...b_i$  where  $b_i$  is MSB. In this simple coder, new bits  $b_{i+1}$  can be inserted after multiplying the already coded number by two and adding the new bit. Encoding is presented in equation (5). Decoding follows in a similar simple fashion with equation (6), as given by [13].

$$C(x_i, b_{i+1}) = 2x_i + b_{i+1} \tag{5}$$

$$(x_i, b_{i+1}) = D(x_{i+1}) := (\lfloor \frac{x_{i+1}}{2} \rfloor, x_{i+1} \bmod 2)$$

(6)

It is however important to note that in this case, the equations (5) and (6) provides optimal compression according to Shannon's source coding theorem only when the probabilities of "0" and "1" are equal, i.e. there is a uniform distribution of these two symbols. In this particular case entropy is given as  $H(x) = -(2 \cdot \frac{1}{2} \log_2(\frac{1}{2})) = 1$ , since  $p_0 = p_1 = \frac{1}{2}$ .

This indicates that there is 1 bit per binary digit in the coded natural number, excluding a starting bit for the natural number  $x_0 = 1$ , and therefore no real gain in terms of compression of the encoder.

This can be illustrated by recalculating the resulting entropy for a slightly skewed distribution using t his coder, with  $p_0 = \frac{3}{8}$  and  $p_1 = \frac{5}{8}$ . The resulting entropy is  $H(x) = -(\cdot \frac{3}{8} \log_2(\frac{3}{8}) + \cdot \frac{5}{8} \log_2(\frac{5}{8})) \approx 0.954$ . The simple ANS implementation of (5) and (6) sorely lacks statistical coding that could take advantage of the skew in distribution, taking into advantage the overrepresentation of '1' versus '0' in this example.

Coding perfectly the  $(q_s)$  symbol distribution onto a  $(p_s)$  symbol sequence, this would produce an average of  $\sum_s p_s lg(\frac{1}{q_s})$  bits per symbol. The difference between this value and the optimal one is called the Kullback - Leiber distance[2], in shorthand notation given as:

$$\Delta H = \sum_{s} p_{s} lg(\frac{p_{s}}{q_{s}}) \tag{7}$$

This can be simplified as follows, using a second order Taylor's expansion of the logarithm, around 1:

$$\Delta H = \sum_{s} \frac{-p_s}{\ln(2)} \left( \left(1 - \frac{q_s}{p_s}\right) - \frac{1}{2} \left(1 - \frac{q_s}{p_s}\right)^2 \right) \approx 0.72 \sum_{s} \frac{(p_s - q_s)^2}{p_s}$$

(8)

Note that in the case of true entropy coding,  $q_s = p_s$ , and hence the difference (and distance) will be zero. It can also be seen that if not, the Kullback-Leiber distance for non-entropic coding grows for each encoded symbol contributing to deviations from the ideal of  $p_s - q_s = 0$ . Utilizing the statistical properties of a data set with ANS will be further discussed in subsection 2.2.1.

The natural number (also known as state) must always be given an initial value. In other systems this value is often referred to as check sum. This initial value could theoretically be initialized to '0', however will lead to potential loss of data. This means that the case where the natural number is initialized as  $x_0 = 0$ , is not guaranteed to result in the indented compression behavior. Common practice is to initialize the natural number  $x_0 = 1$  [6].

Note that one important feature of ANS is that it has been shown to be suited for hardware implementation, in an adaptation known as Low Complexity ANS (LOCO ANS) [17].

#### 2.2.1 Solving issues of basic ANS

While the simple ANS algorithm discussed previously only works optimally with uniform distribution, most data deviate more or less from this assumption, that is for  $p_0 \neq p_1$ , such as  $p_1 = p < 1 - p = p_0$ .

Looking at equation (5) for encoding, each bit should contribute with as little entropy as possible. Optimal encoding  $C_{opt}$  may be expressed using (9) according to [13]:

$$H(C_{\text{opt}}(x_{i}, b_{i+1})) = H(x_{i+1}) = H(x_{i}) + H(b_{i+1})$$

=  $\log_{2}(x_{i}) - \log_{2}(p_{b_{i+1}})$

$\implies C_{\text{opt}}(x_{i}, b_{i+1}) \approx \frac{x_{i}}{p_{b_{i+1}}}$  (9)

Using this result, a coder true to the criterium of minimizing entropy can be implemented [13], mapping odd and even binary numbers according to probabilities (p, 1-p) using the coding function in equation (10). Decoding would then be using equation (11), using the result of (9):

$$x_{i+1} = C(x_i, b_{i+1}) \tag{10}$$

$$(x_i, b_{i+1}) = D(x_{i+1}) \tag{11}$$

The three first variants of ANS (chronologically) according to the distributions of the source symbols and methods of realization are [4]:

- 1. Uniform Asymmetric Binary System (uABS): Only for the processing of binary symbols

- 2. Range Asymmetric Numeral System (rANS): Is not only '0' and '1', but with sub-cycles (ranges) as well.

- 3. Table Asymmetric Numeral System (tANS): Tabularizing the ANS's encoding/decoding process

These will be explained very briefly in the following sections, with special emphasis on uABS, which is the basis of the hardware implementation of this paper.

#### 2.2.2 uABS

uABS (uniform binary variant of ANS) can compress/decompress binary messages of finite size, providing an optimal entropy coding/decoding process covering all distributions; including non-even.

Assuming a binary alphabet, and focusing on the odds,  $N \cdot p$  odd numbers can be mapped in the first N natural numbers with probability  $p=\Pr(1)$ , so that for any given N and N+1 [13]:

$$\lceil (N+1) \cdot p \rceil - \lceil N \cdot p \rceil = \begin{cases} 1 & \text{, if } N \text{ has an odd mapped} \\ 0 & \text{, otherwise} \end{cases}$$

(12)

Note that this may be interpreted as N satisfying the outcome of [N \* p] in respect of odd numbers with no odd numbers expected at N + 1.

The encoding function is presented in equation (13), and satisfies the requirements for distribution as set forth by (12) [13].

$$C(x_i, b_{i+1}) = \begin{cases} \left\lceil \frac{x_i+1}{1-p} \right\rceil - 1 & \text{, if } b_{i+1} = 0 \\ \left\lfloor \frac{x_i}{p} \right\rfloor & \text{, otherwise} \end{cases}$$

(13)

The decoding function presented in equation (14) is the reverse calculation, and returns the original binary sequence [13].

$$(x_{i}, b_{i+1}) = D(x_{i+1})$$

$$b_{i+1} = \lceil (x_{i+1} + 1) \cdot p \rceil - \lceil x_{i+1} \cdot p \rceil$$

$$x_{i} = \begin{cases} x_{i+1} - \lceil x_{i+1} \cdot p \rceil & \text{, if } b_{i+1} = 0 \\ \lceil x_{i+1} \cdot p \rceil & \text{, otherwise} \end{cases}$$

(14)

Knowing the probability is vital to make uABS work correctly. Obviously readily available on the coding side, but must be made available to the decoding process work. In practice, p has to be stored or transferred along the compressed data, hence requiring space and thereby reducing the effective compression ratio.

An encoding example is shown in equations (15) of the 8-bit binary sequence 10011000 to a natural number, using the uABS variant adapted from [13]. Note that p of odds (counting 1s) is  $p = \frac{3}{8}$  (and hence  $p = \frac{5}{8}$  for evens), and initial value (also known as state) is  $x_0 = 1$ .

$$x_{1} = C(x_{0}, b_{1}) = \lfloor \frac{x_{0}}{p} \rfloor = \lfloor 1 \cdot \frac{8}{3} \rfloor = 2$$

$$x_{2} = C(x_{1}, b_{2}) = \lceil \frac{x_{1} + 1}{1 - p} \rceil - 1 = \lceil (2 + 1) \frac{8}{5} \rceil - 1 = 4$$

$$x_{3} = C(x_{2}, b_{3}) = \lceil \frac{x_{2} + 1}{1 - p} \rceil - 1 = \lceil (4 + 1) \frac{8}{5} \rceil - 1 = 7$$

$$x_{4} = C(x_{3}, b_{4}) = \lfloor \frac{x_{3}}{p} \rfloor = \lfloor 7 \cdot \frac{8}{3} \rfloor = 18$$

$$x_{5} = C(x_{4}, b_{5}) = \lfloor \frac{x_{4}}{p} \rfloor = \lfloor 19 \cdot \frac{8}{3} \rfloor = 48$$

$$x_{6} = C(x_{5}, b_{6}) = \lceil \frac{x_{5} + 1}{1 - p} \rceil - 1 = \lceil (48 + 1) \frac{8}{5} \rceil - 1 = 78$$

$$x_{7} = C(x_{6}, b_{7}) = \lceil \frac{x_{6} + 1}{1 - p} \rceil - 1 = \lceil (78 + 1) \frac{8}{5} \rceil - 1 = 126$$

$$x_{8} = C(x_{7}, b_{8}) = \lceil \frac{x_{7} + 1}{1 - p} \rceil - 1 = \lceil (126 + 1) \frac{8}{5} \rceil - 1 = 203$$

The corresponding decoding of the natural number 203 of uABS variant is shown in (16) [13]. Note that it is generated in reversed order.

$$b_{8} = \lceil (x_{8}+1) \cdot p \rceil - \lceil x_{8} \cdot p \rceil = \lceil (203+1) \cdot \frac{3}{8} \rceil - \lceil 203 \cdot \frac{3}{8} \rceil = 0$$

$$x_{7} = x_{8} - \lceil x_{8} \cdot p \rceil = 203 - \lceil 203 \cdot \frac{3}{8} \rceil = 126$$

$$b_{7} = \lceil (x_{7}+1) \cdot p \rceil - \lceil x_{7} \cdot p \rceil = \lceil (126+1) \cdot \frac{3}{8} \rceil - \lceil 126 \cdot \frac{3}{8} \rceil = 0$$

$$x_{6} = x_{7} - \lceil x_{7} \cdot p \rceil = 126 - \lceil 126 \cdot \frac{3}{8} \rceil = 78$$

$$b_{6} = \lceil (x_{6}+1) \cdot p \rceil - \lceil x_{6} \cdot p \rceil = \lceil (78+1) \cdot \frac{3}{8} \rceil - \lceil 78 \cdot \frac{3}{8} \rceil = 0$$

$$x_{5} = x_{6} - \lceil x_{6} \cdot p \rceil = 78 - \lceil 78 \cdot \frac{3}{8} \rceil = 48$$

$$b_{5} = \lceil (x_{5}+1) \cdot p \rceil - \lceil x_{5} \cdot p \rceil = \lceil (48+1) \cdot \frac{3}{8} \rceil - \lceil 48 \cdot \frac{3}{8} \rceil = 1$$

$$x_{4} = \lceil x_{5} \cdot p \rceil = \lceil 48 \cdot \frac{3}{8} \rceil = 18$$

$$b_{4} = \lceil (x_{4}+1) \cdot p \rceil - \lceil x_{4} \cdot p \rceil = \lceil (18+1) \cdot \frac{3}{8} \rceil - \lceil 18 \cdot \frac{3}{8} \rceil = 1$$

$$x_{3} = \lceil x_{4} \cdot p \rceil = \lceil 18 \cdot \frac{3}{8} \rceil = 7$$

$$b_{3} = \lceil (x_{3}+1) \cdot p \rceil - \lceil x_{2} \cdot p \rceil = \lceil (4+1) \cdot \frac{3}{8} \rceil - \lceil 7 \cdot \frac{3}{8} \rceil = 0$$

$$x_{2} = x_{3} - \lceil x_{3} \cdot p \rceil = 7 - \lceil 7 \cdot \frac{3}{8} \rceil = 4$$

$$b_{2} = \lceil (x_{1}+1) \cdot p \rceil - \lceil x_{1} \cdot p \rceil = \lceil (2+1) \cdot \frac{3}{8} \rceil - \lceil 4 \cdot \frac{3}{8} \rceil = 0$$

$$x_{1} = x_{2} - \lceil x_{2} \cdot p \rceil = 4 - \lceil 4 \cdot \frac{3}{8} \rceil = 2$$

$$b_{1} = \lceil (x_{1}+1) \cdot p \rceil - \lceil x_{1} \cdot p \rceil = \lceil (2+1) \cdot \frac{3}{8} \rceil - \lceil 2 \cdot \frac{3}{8} \rceil = 1$$

$$x_{0} = \lceil x_{1} \cdot p \rceil = \lceil 2 \cdot \frac{3}{8} \rceil = 1$$

#### 2.3 General HW implementation

#### 2.3.1 FPGA

A wide scale of standalone field programmable gate array (FPGA) chips, as well as embedded FPGA functionality on multi-function chips are manufactured. Several are well posed as possible targets for a hardware implementation of the compressor in this project.

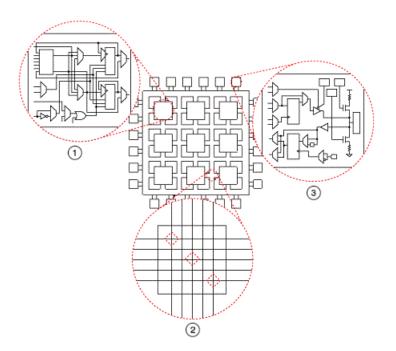

As an introduction to this section of theory on FPGAs, one may illustrate the core functionality with figure 1, courtesy National Semiconductors [18]. This shows the three basic FPGA functionalities of logic, routing and I/O.

Logic, as embedded in so-called Configurable Logic Blocks (CLBs) typically contains a number of slices, each with flip/flops, look-up-tables (LUTs), registers, multiplexers, wiring, carry logic, arithmetic logic and storage logic and similar. Some CLB slices also include distributed RAM and 32-bit shift registers [19].

Block memory, DRAM, registers and FIFO queues are commonplace in FPGAs today, providing easy access to different types of storage, with different strengths and weaknesses.

I/O is organised in Input/Output Blocks (IOBs) where each of these handles a certain type of I/O [20]. Assigning IOBs to physical ports, they become bonded IOBs. IOBS is connected to an actual physical wire going out of the chip. Physical connect can be such as PXI backplanes or Real-Time System Integration (RTSI) connectors. Note that non-bondable IOBs encompass (among others)

Figure 1: Configurable Logic Blocks, routing and I/O on FPGAs. Illustration taken from [18]

internal lines that provide I/O between configurable and non-configurable parts within the FPGA [20].

Routing allows for the transport of data to and from the different parts of the FPGA.

For small-scale system design, manually wiring components on an FPGA provides tight optimization but requires an intimate understanding of the FPGA components and their uses. To be productive at scale, high-level tools converting statement-based designs expressed in either VHDL or Verilog/SystemVerilog offers good results as well, given a performant EDA for synthesis.

The FPGAs range from traditional standalone chips such as the 7-series of Xilinx (starting with the Spartan-7) to a variety of FPGA functionality on multiprocessor on a chip (MPSoC) systems.

#### 2.3.2 Xilinx target FPGAs

A possible standalone-FPGA target for a hardware implementation of the compressor in this project is the Xilinx XC7S100 Spartan-7, the 7-series entry-point low-power FPGA.

Figure 2: Xilinx Spartan-7 FPGA, illustration taken from [21]

The best quipped Spartan-7 has 1100KB DRAM and 1 analog to digital converter (XADC), based on a 28 nm process [21]. The 7 Series families is summarized in table 1 and 2 for supplemental info.

Xilinx offers the SP701 Evaluation Kit for prototyping and development using the top-of-the Spartan-7 variant Xilinx XC7S100. Third-party vendors are marketing other more or less elaborate development kits and hobby kits based on the Spartan-7, such as a small-factor board IAM

#### Table 1: Xilinx 7-series overview, illustration taken from [21]

#### 7 Series Families Comparison

| Max. Capability                | Spartan-7           | Artix-7                                    | Kintex-7                                              | Virtex-7                         |

|--------------------------------|---------------------|--------------------------------------------|-------------------------------------------------------|----------------------------------|

| Logic Cells                    | 102K                | 215K                                       | 478K                                                  | 1,955K                           |

| Block RAM <sup>(1)</sup>       | 4.2 Mb              | 13 Mb                                      | 34 Mb                                                 | 68 Mb                            |

| DSP Slices                     | 160                 | 740                                        | 1,920                                                 | 3,600                            |

| DSP Performance <sup>(2)</sup> | 176 GMAC/s          | 929 GMAC/s                                 | 2,845 GMAC/s                                          | 5,335 GMAC/s                     |

| MicroBlaze CPU <sup>(3)</sup>  | 260 DMIPs           | 303 DMIPs                                  | 438 DMIPs                                             | 441 DMIPs                        |

| Transceivers                   | -                   | 16                                         | 32                                                    | 96                               |

| Transceiver Speed              | -                   | 6.6 Gb/s                                   | 12.5 Gb/s                                             | 28.05 Gb/s                       |

| Serial Bandwidth               | -                   | 211 Gb/s                                   | 800 Gb/s                                              | 2,784 Gb/s                       |

| PCIe Interface                 | -                   | x4 Gen2                                    | x8 Gen2                                               | x8 Gen3                          |

| Memory Interface               | 800 Mb/s            | 1,066 Mb/s                                 | 1,866 Mb/s                                            | 1,866 Mb/s                       |

| I/O Pins                       | 400                 | 500                                        | 500                                                   | 1,200                            |

| I/O Voltage                    | 1.2V-3.3V           | 1.2V–3.3V                                  | 1.2V-3.3V                                             | 1.2V-3.3V                        |

| Package Options                | Low-Cost, Wire-Bond | Low-Cost, Wire-Bond,<br>Bare-Die Flip-Chip | Bare-Die Flip-Chip and High-<br>Performance Flip-Chip | Highest Performance<br>Flip-Chip |

Notes:

Additional memory available in the form of distributed RAM. Peak DSP performance numbers are based on symmetrical filter implementation. Peak MicroBlaze CPU performance numbers based on microcontroller preset. 1. 2. 3.

Table 2: Spartan-7 FPGA Feature Summary by Device, illustration taken from [21]

#### Spartan-7 FPGA Feature Summary by Device

|         |                | CLB                   |                                | Block RAM Blocks             |       |       | cks <sup>(3)</sup> |                     |      |    |                |                                   |                 |

|---------|----------------|-----------------------|--------------------------------|------------------------------|-------|-------|--------------------|---------------------|------|----|----------------|-----------------------------------|-----------------|

| Device  | Logic<br>Cells | Slices <sup>(1)</sup> | Max<br>Distributed<br>RAM (Kb) | DSP<br>Slices <sup>(2)</sup> | 18 Kb | 36 Kb | Max<br>(Kb)        | CMTs <sup>(4)</sup> | PCle | GT | XADC<br>Blocks | Total I/O<br>Banks <sup>(5)</sup> | Max User<br>I/O |

| XC7S6   | 6,000          | 938                   | 70                             | 10                           | 10    | 5     | 180                | 2                   | 0    | 0  | 0              | 2                                 | 100             |

| XC7S15  | 12,800         | 2,000                 | 150                            | 20                           | 20    | 10    | 360                | 2                   | 0    | 0  | 0              | 2                                 | 100             |

| XC7S25  | 23,360         | 3,650                 | 313                            | 80                           | 90    | 45    | 1,620              | 3                   | 0    | 0  | 1              | 3                                 | 150             |

| XC7S50  | 52,160         | 8,150                 | 600                            | 120                          | 150   | 75    | 2,700              | 5                   | 0    | 0  | 1              | 5                                 | 250             |

| XC7S75  | 76,800         | 12,000                | 832                            | 140                          | 180   | 90    | 3,240              | 8                   | 0    | 0  | 1              | 8                                 | 400             |

| XC7S100 | 102,400        | 16,000                | 1,100                          | 160                          | 240   | 120   | 4,320              | 8                   | 0    | 0  | 1              | 8                                 | 400             |

#### Notes:

Each 7 series FPGA slice contains four LUTs and eight flip-flops; only some slices can use their LUTs as distributed RAM or SRLs. Each DSP slice contains a pre-adder, a 25 x 18 multiplier, an adder, and an accumulator. Block RAMs are fundamentally 36 Kb in size; each block can also be used as two independent 18 Kb blocks. Each CMT contains one MMCM and one PLL.

2. 3. 4. 5.

Does not include configuration Bank 0.

#### Electronics [22] kit for under USD100.

The Xilinx Zynq UltraScale+ series MPSoC, which is based on a 16 nm-process [23], was chosen as the primary FPGA target in this project. It provides a host of applications and real-time Arm core processors as well as several memory and connectivity options.

Figure 3: Xilinx Zynq UltraScale+, illustration taken from [23]

Table 3, Zync UltraScale+ MPSoC: CG Device Feature Summary for a presentation of the capabilities of the series, comparable to those of 7-Series in table 1 and of Spartan-7 in table 2.

Xilinx offers development kits based on Zynq UltraScale+ as well, such as the Zcu106 [24].

It may be worthwhile to note that the UltraScale+ series fans out at 600K system logic cells; while the 7-series goes on to 1955K.

#### Table 3: Xilinx Zynq UltraScale+ series overview, illustration taken from [23]

|                                         | ZU1CG                                                                                                           | ZU2CG                                                                                                                              | ZU3CG         | ZU4CG                 | ZU5CG                    | ZU6CG        | ZU7CG       | ZU9CG        |  |  |  |

|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|--------------------------|--------------|-------------|--------------|--|--|--|

| Application Processing Unit             | Dual-core                                                                                                       | Dual-core Arm Cortex-A53 MPCore with CoreSight; NEON & Single/Double Precision Floating Point;<br>32KB/32KB L1 Cache, 1MB L2 Cache |               |                       |                          |              |             |              |  |  |  |

| Real-Time Processing Unit               | Dual-core Arm Cortex-R5F with CoreSight; Single/Double Precision Floating Point; 32KB/32KB L1<br>Cache, and TCM |                                                                                                                                    |               |                       |                          |              |             |              |  |  |  |

| Embedded and External<br>Memory         | 256KB On-Chip Memory w/ECC; External DDR4; DDR3; DDR3L; LPDDR4; LPDDR3;<br>External Quad-SPI; NAND; eMMC        |                                                                                                                                    |               |                       |                          |              |             |              |  |  |  |

| General Connectivity                    | 214 PS I/0                                                                                                      | ); UART; CAI                                                                                                                       | N; USB 2.0; 1 | 2C; SPI; 32t<br>Timer | o GPIO; Real<br>Counters | Time Clock;  | WatchDog Ti | mers; Triple |  |  |  |

| High-Speed Connectivity                 |                                                                                                                 | 4 PS-GTR;                                                                                                                          | PCIe Gen1/2   | ; Serial ATA          | 3.1; DisplayP            | ort 1.2a; US | B 3.0; SGMI | Ι            |  |  |  |

| System Logic Cells                      | 81,900                                                                                                          | 103,320                                                                                                                            | 154,350       | 192,150               | 256,200                  | 469,446      | 504,000     | 599,550      |  |  |  |

| CLB Flip-Flops                          | 74,880                                                                                                          | 94,464                                                                                                                             | 141,120       | 175,680               | 234,240                  | 429,208      | 460,800     | 548,160      |  |  |  |

| CLB LUTs                                | 37,440                                                                                                          | 47,232                                                                                                                             | 70,560        | 87,840                | 117,120                  | 214,604      | 230,400     | 274,080      |  |  |  |

| Distributed RAM (Mb)                    | 1.0                                                                                                             | 1.2                                                                                                                                | 1.8           | 2.6                   | 3.5                      | 6.9          | 6.2         | 8.8          |  |  |  |

| Block RAM Blocks                        | 108                                                                                                             | 150                                                                                                                                | 216           | 128                   | 144                      | 714          | 312         | 912          |  |  |  |

| Block RAM (Mb)                          | 3.8                                                                                                             | 5.3                                                                                                                                | 7.6           | 4.5                   | 5.1                      | 25.1         | 11.0        | 32.1         |  |  |  |

| UltraRAM Blocks                         | 0                                                                                                               | 0                                                                                                                                  | 0             | 48                    | 64                       | 0            | 96          | 0            |  |  |  |

| UltraRAM (Mb)                           | 0                                                                                                               | 0                                                                                                                                  | 0             | 13.5                  | 18.0                     | 0            | 27.0        | 0            |  |  |  |

| DSP Slices                              | 216                                                                                                             | 240                                                                                                                                | 360           | 728                   | 1,248                    | 1,973        | 1,728       | 2,520        |  |  |  |

| CMTs                                    | 3                                                                                                               | 3                                                                                                                                  | 3             | 4                     | 4                        | 4            | 8           | 4            |  |  |  |

| Max. HP I/O <sup>(1)</sup>              | 156                                                                                                             | 156                                                                                                                                | 156           | 156                   | 156                      | 208          | 416         | 208          |  |  |  |

| Max. HD I/O <sup>(2)</sup>              | 24                                                                                                              | 96                                                                                                                                 | 96            | 96                    | 96                       | 120          | 48          | 120          |  |  |  |

| System Monitor                          | 1                                                                                                               | 2                                                                                                                                  | 2             | 2                     | 2                        | 2            | 2           | 2            |  |  |  |

| GTH Transceiver 16.3Gb/s <sup>(3)</sup> | 0                                                                                                               | 0                                                                                                                                  | 0             | 16                    | 16                       | 24           | 24          | 24           |  |  |  |

| GTY Transceivers 32.75Gb/s              | 0                                                                                                               | 0                                                                                                                                  | 0             | 0                     | 0                        | 0            | 0           | 0            |  |  |  |

| Transceiver Fractional PLLs             | 0                                                                                                               | 0                                                                                                                                  | 0             | 8                     | 8                        | 12           | 12          | 12           |  |  |  |

| PCIe Gen3 x16                           | 0                                                                                                               | 0                                                                                                                                  | 0             | 2                     | 2                        | 0            | 2           | 0            |  |  |  |

| 150G Interlaken                         | 0                                                                                                               | 0                                                                                                                                  | 0             | 0                     | 0                        | 0            | 0           | 0            |  |  |  |

| 100G Ethernet w/ RS-FEC                 | 0                                                                                                               | 0                                                                                                                                  | 0             | 0                     | 0                        | 0            | 0           | 0            |  |  |  |

| Zumm Hiltun Conto I | MDCoC: CC Douise Footune Cum  |      |

|---------------------|-------------------------------|------|

|                     | MPSoC: CG Device Feature Sumn | пагу |

|                     |                               |      |

Notes:

. HP = High-performance I/O with support for I/O voltage from 1.0V to 1.8V. HD = High-density I/O with support for I/O voltage from 1.2V to 3.3V.

HD = High-density I/O with support for I/O voltage from 1.2V to 3.3V.

GTH transceivers in the SFVC784 package support data rates up to 12.5Gb/s. See Table 2.

#### 2.3.3 Briefly about thermal considerations

FPGA-related thermal design issues have not been taken into consideration in this project, due to time and project constraints. This can however be an important issue when designing applications for FPGAs. Agne & al [25] present an interesting discussion on the impact of different FPGA elements on power consumption, demonstrated by using the Xilinx S7 and other FPGAs. Certain uses can easily overheat the chip and/or create challenges for the power budget.

Apart from design changes to avoid some of the most notorious power guzzlers in the FPGA port logic design, some relief can be found by using processes with smaller feature sizes, such as 20 nm, 16 nm or below. One example is the Zynq Ultrascale+ [23] series based on 16 nm, providing 2–5X greater system-level performance/watt over 28nm devices [26].

In addition to smaller feature size, other design choices can lower the power consumption in the logic gate functions, with enhanced logic blocks for a target of 90% utilization for the UltraScale+ [26]. If on-chip elements such as processing cores can be used in a sensible manner, reducing the use of off-chip (MPSoC) functions, further power savings can be achieved. Note that this will not necessarily lower related chip heating issues per se since even more power consumption is crammed into a small space by using other functions on the MPSoC. But if for instance the CPU cores of the UltraScale+ can be used together with the logic gates on-chip, real power savings can be achieved compared to the total power consumption of a system forced to intensive I/O activity for intermediate result data transport passed via the power-wise expensive external lines of the chips involved.

#### 2.3.4 Timing: Setup and hold slack

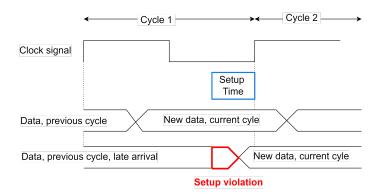

Signal propagation through high speed/high-frequency circuitry such as FPGA or ASIC does pose some challenges. Looking into a propagation path, one will either experience that signal propagation is well timed with data in place before being clocked (and locked) in place, or that it fails to do so.

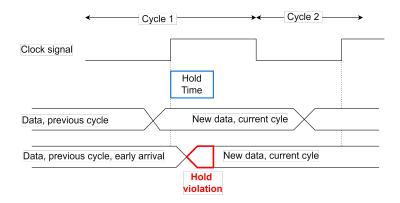

There are two variants of setup and hold slack: Setup slack, and hold slack.

The difference between desired time (clock propagation) and achieved time (data propagation) for a timing path is called the setup slack. It may either be: positive, zero or negative. Negative simply means that the signals fail to propagate within the given time frame, while zero means that it does succeed but without any margin. Zero or positive means that the data has propagated successfully, and in time [27]. Please refer to figure 4 of [28] for an example of setup timing.

Figure 4: Signal setup timing

The difference between the achieved and desired time for locking the data is called hold slack. It simply means that if data are in place too early, and not stable during the hold, locking will fail. Please refer to figure 5 of [28] for an example of hold timing.

Figure 5: Signal hold timing

The libraries of the synthesis and verification tools know the different signal propagation data of the elements used. Proper design will minimize the probability of zero and negative setup and hold slack, and verification will minimize the chance of not finding any timing errors that might slip through.

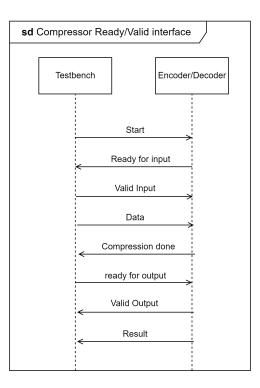

#### 2.3.5 The Ready-Valid data interfacing design pattern

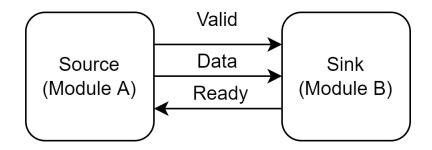

One of the challenges of electronic design is proper handshaking when transferring data from a source to a sink. The handshake is used for the sink to signal that it is ready for data, and the

source to signal that it will transmit data.

Simple solution patterns such as the ReadyValid data interfacing design patterns, have been with us for a while as exemplified by [29] and illustrated in figure 6.

Figure 6: Ready/Valid interfacing design pattern principle with one source and one sink

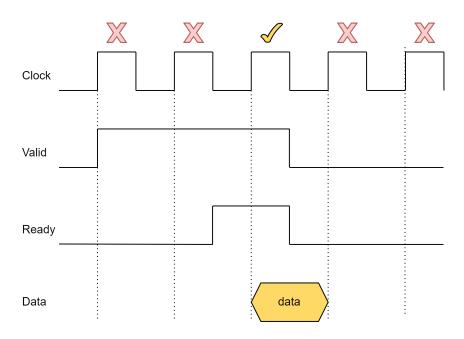

This pattern relies on two handshake signals: Valid from source to sink, signalling that the data presented are to be consumed, and ready from sink to the source, signalling that the sink is indeed ready to consume. Both will have to be true in order to facilitate a successful data transfer, locking in (and holding) data on the sink. Note that the original design pattern relies on the rising edge of the clock to hold (lock) the data on the sink as the receiving end, as illustrated in figure 7.

Figure 7: Ready/Valid signals vs. transfer on rising edge, one clock cycle data transfer

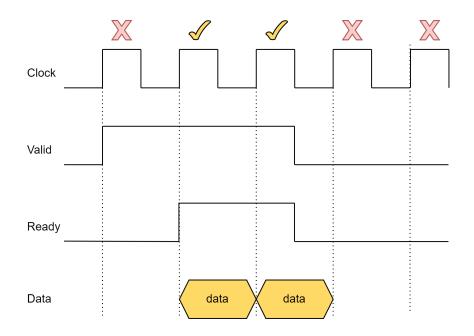

This pattern is not limited to the simple stop-and-go timing as shown here; but can string a number of transfers, as long as both Valid and Ready er true, as shown in figure 8.

Referring to the discussion of section 2.3.4, special caution must be exercised to avoid negative setup and hold slack.

Figure 8: Ready/Valid signals vs. transfer on rising edge, two clock cycle data transfer

#### 2.3.6 FPGA divide library

The different FPGAs are delivered with a wide array of functionalities as defined by the FPGA itself, and the standard libraries of synthesizable functions of the different vendors and third parties.

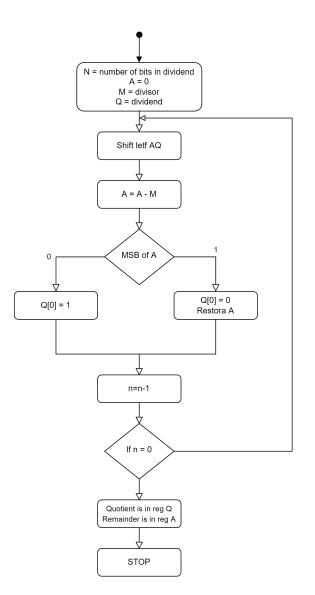

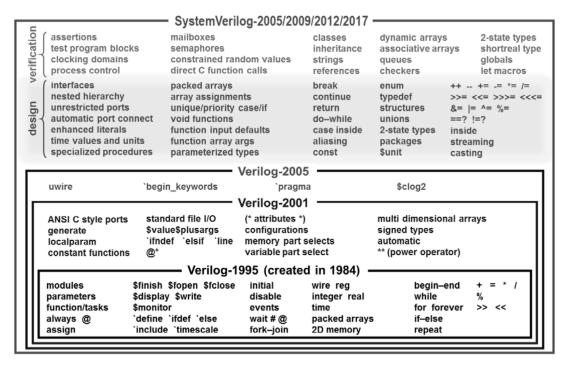

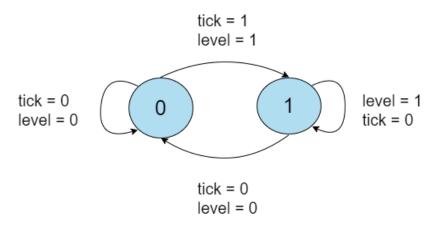

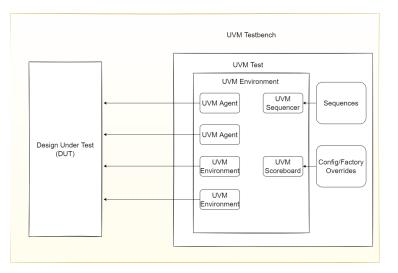

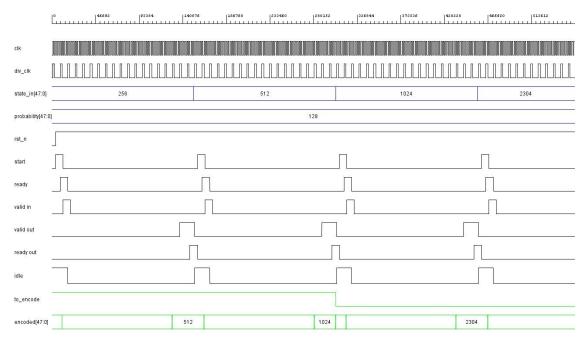

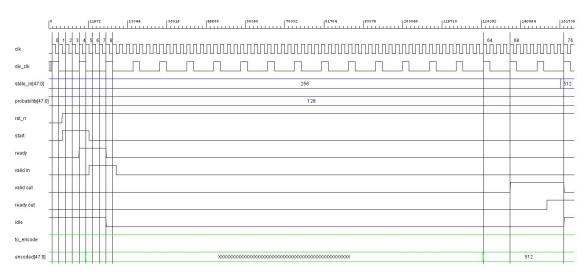

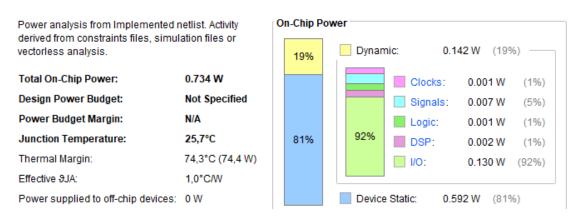

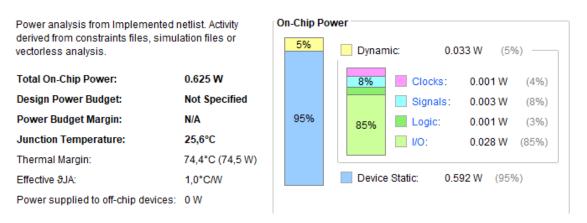

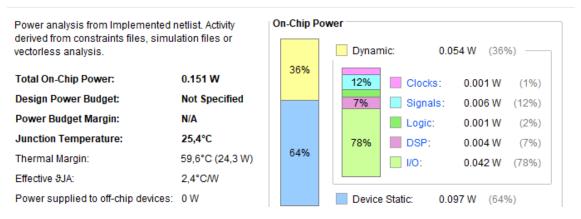

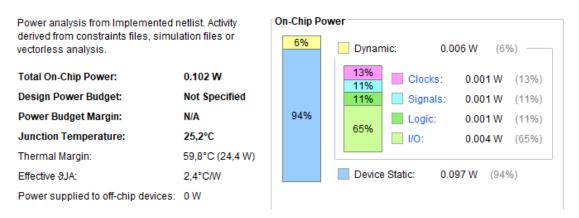

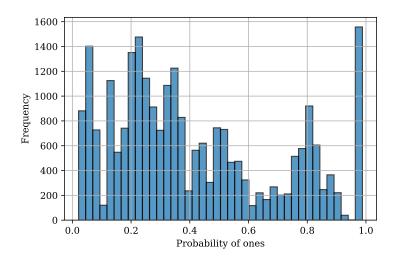

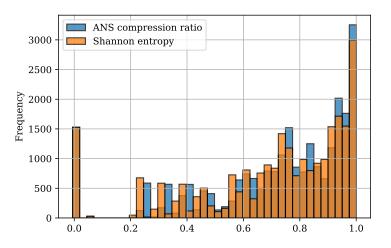

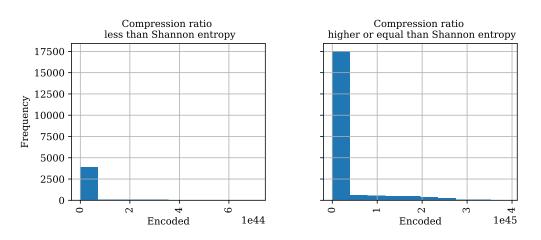

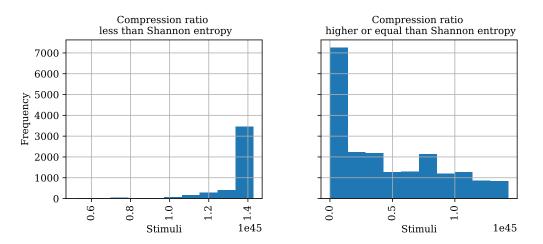

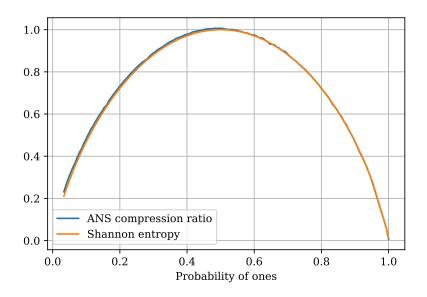

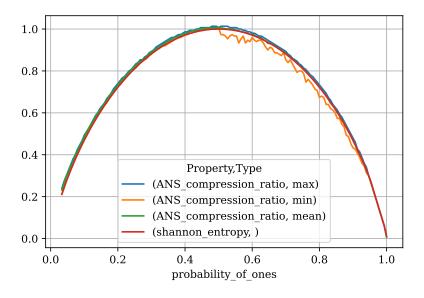

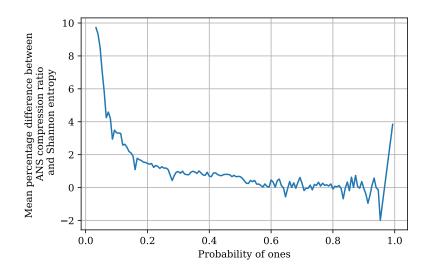

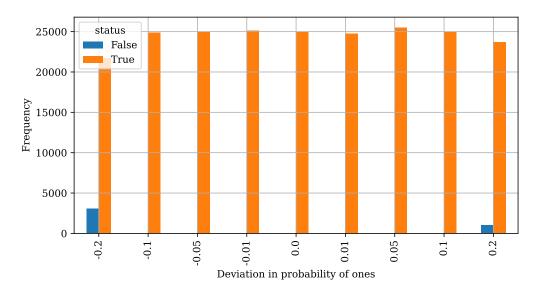

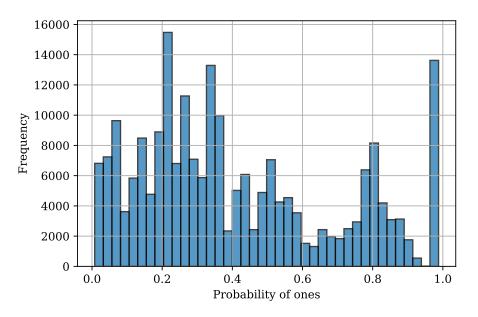

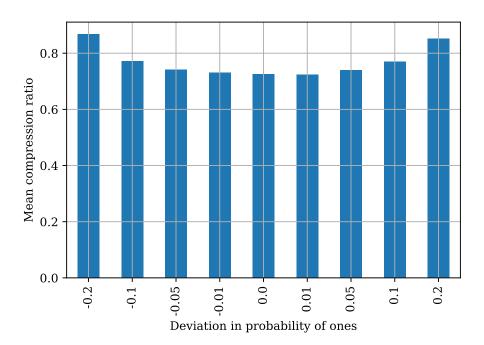

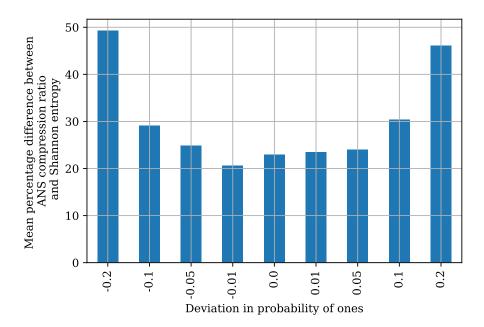

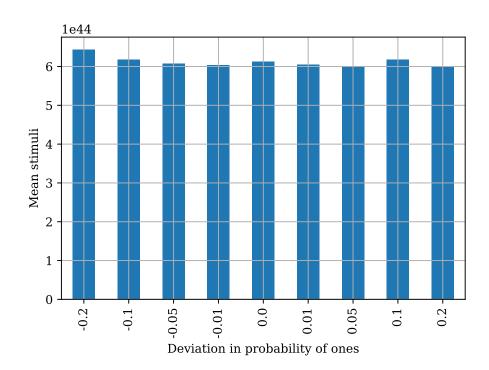

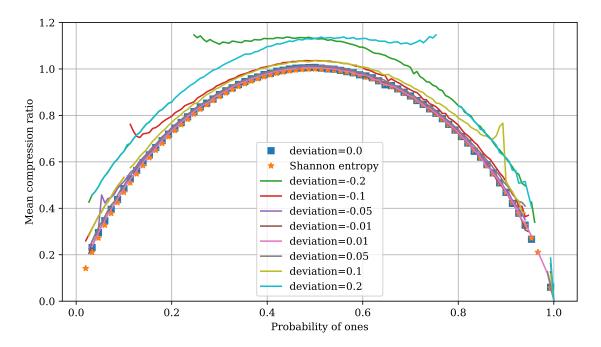

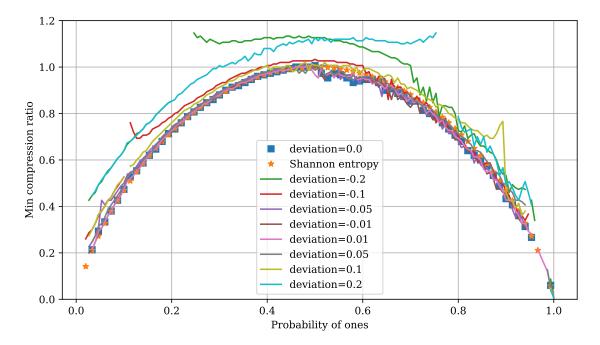

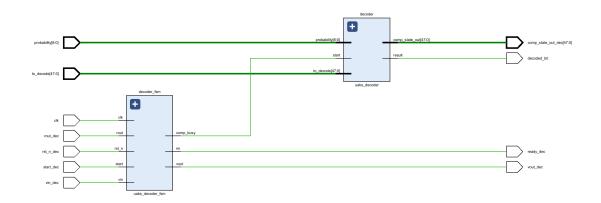

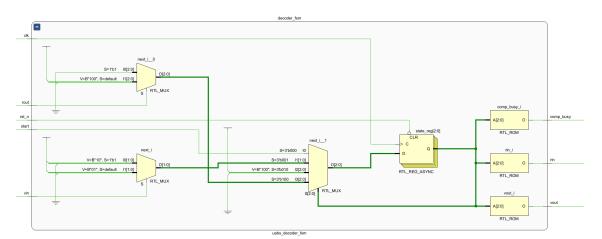

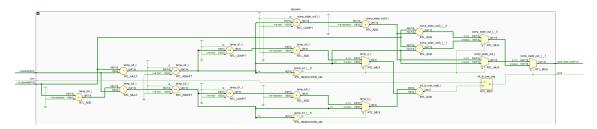

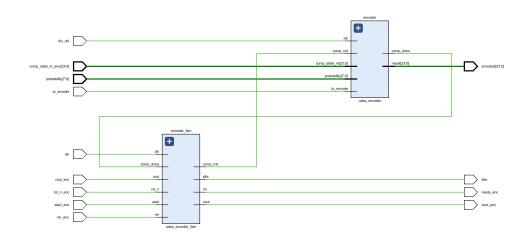

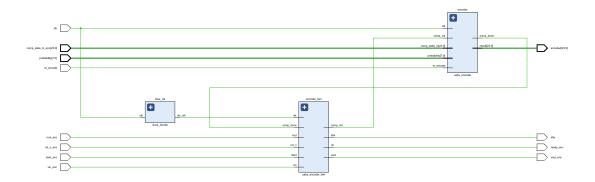

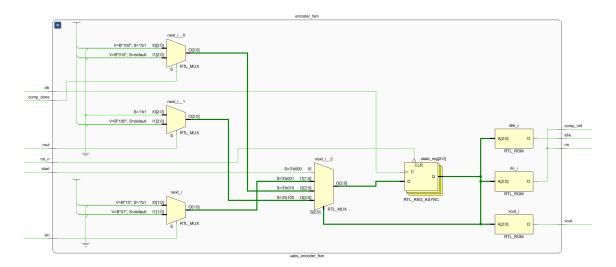

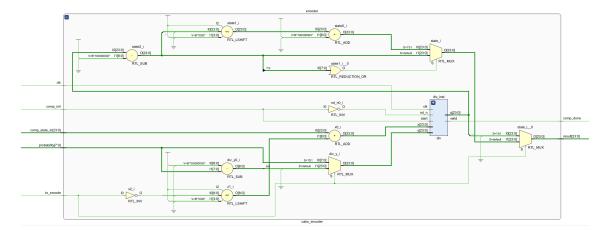

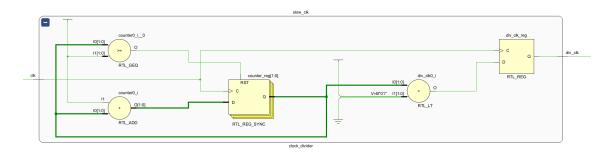

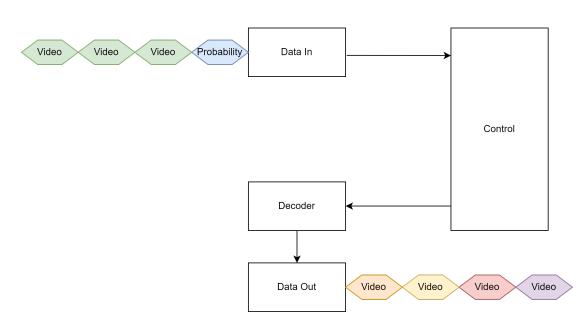

The fixed-point division is not available out-of-the-box with Verilog with FPGAs. ANS type compression requires division; and luckily, additional libraries are available.