Doctoral theses at NTNU, 2022:59

## Andreas Giannakis

# Design of High-Performance Solid-State Circuit Breakers for LVDC and MVDC Applications

# NTNU

NTNU Norwegian University of Science and Technology Thesis for the Degree of Philosophiae Doctor Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Norwegian University of Science and Technology

Andreas Giannakis

# Design of High-Performance Solid-State Circuit Breakers for LVDC and MVDC Applications

Thesis for the Degree of Philosophiae Doctor

Trondheim, February 2022

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Norwegian University of Science and Technology

#### NTNU

Norwegian University of Science and Technology

Thesis for the Degree of Philosophiae Doctor

Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

© Andreas Giannakis

ISBN 978-82-326-5896-1 (printed ver.) ISBN 2978-82-326-6016-2 (electronic ver.) ISSN 1503-8181 (printed ver.) ISSN 2703-8084 (online ver.)

Doctoral theses at NTNU, 2022:59

Printed by NTNU Grafisk senter

## Abstract

Today, the emerging technology of LVDC and MVDC grids is under extensive research. These grids ease the integration of distributed electricity generation systems and offer several advantages over the AC counterparts, such as lower transmission losses at the same voltage level. However, the lack of a high-performance protection scheme against DC short-circuits is currently the main showstopper for their further development. Three main circuit breaker topologies have been proposed for the fault clearance in DC grids. Among them, the solid-state breaker exhibits the highest speed of breaking operations at a cost of high conduction losses caused in power semiconductor devices. This PhD thesis investigates primarily the design of solid-state DC breakers with the aim of minimizing their conduction losses. For this purpose, the conducting performance of several commercial Silicon and SiC semiconductor technologies with blocking voltage in the range of 1200 - 1700V have been extensively evaluated. Experimental results revealed that the normally-ON SiC JFETs achieved the lowest conduction losses for mediumpower LVDC and MVDC solid-state breakers. On the other hand, at high-power MVDC applications, three high-voltage power semiconductor devices are identified. It has been shown that the IGCT-based breakers exhibit the lowest conduction losses. However, to avoid complicated gate driver designs utilized in IGCTs, the use of the gate voltage-controlled IGBTs for high-power solid-state breakers is imposed.

Additionally, this PhD thesis proposes the concept of applying the maximum gate voltage (overdrive) to the active power semiconductor devices used in solid-state breakers in order to minimize the conduction power losses. Especially in SiC MOSFETs and in normally-ON SiC JFETs, the forward voltage drop is reduced significantly compared to IGBT-based semiconductor technologies. In particular, experimental results showed that the normally-ON SiC JFET achieves a conduction loss reduction up to 33% at 55% of normalized current when overdriving.

Three overvoltage suppression configurations used in solid-state breakers for  $700-1800V_{DC}$  applications have been experimentally evaluated in terms of electrothermal performance and passive components requirements. The feasibility and the application-oriented usability of MOVs as an overvoltage suppression configuration for medium-power solid-state LVDC and MVDC breakers has been demonstrated. In addition, the applicability of using both RCD snubber circuits and MOVs as an overvoltage suppression configuration for high-power MVDC solid-state breakers is also revealed.

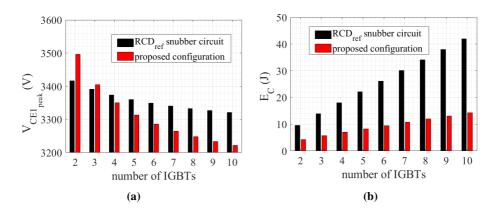

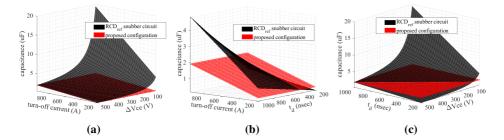

The voltage level of an MVDC grid can be significantly higher than the blocking voltage of a high-voltage semiconductor device. This imposes the need for series-connecting a high number of devices for the breaker design. However, this practice introduces design challenges, such as uneven voltage distribution among the devices during the breaking operation. A hybrid method for designing a solid-state MVDC breaker employing series-connected IGBTs with minimum snubber capacitances requirements is proposed. This method is based on the combination of RCD snubber circuits and a gate coupled transformer. The proposed method minimizes the snubber capacitances by 60% compared to a reference configuration which only consists of RCD snubber circuits, when a gate signal propagation delay of  $1\mu s$  between two series-connected IGBTs is introduced. Finally, in a  $3kV_{DC}$  study, experimental results showed that by keeping the same snubber capacitance, the voltage difference between two IGBTs was measured to be 380V without the use of the gate coupled transformer. On the other hand, in the proposed scheme, the corresponding voltage difference was reduced to 60V.

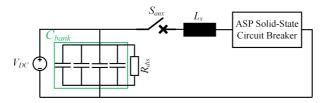

Finally, the design of an automatic and self-powered solid-state breaker using normally-ON SiC JFETs suitable for a  $700V_{DC}$  grid is proposed. This breaker exhibits low conduction losses and it also eliminates the need for external auxiliary circuits used for fault sensing and gate-driver supply. The effectiveness of the breaker has been experimentally validated by interrupting a fault current of 33A within  $330\mu s$ .

## Acknowledgements

First and foremost, I have to thank my parents, Evangelos and Anna and my brother, Konstantinos for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. My thoughts also go to my beloved grandmother, Tasoula, who passed away recently, and who had always been supportive to me and to my personal goals. This accomplishment would not have been possible without them.

I must also express my very profound gratitude to my main supervisor, professor Dimosthenis Peftitsis. Without his assistance and dedicated involvement in every step throughout the PhD process, this thesis would have never been accomplished. Our technical and social discussions as well as his lab guidance have made me a more mature and complete person and a more experienced engineer. Dimos has been not only a great supervisor, but also a mentor and a great friend to me.

I have spent all my PhD time at NTNU, in Trondheim, Norway. During these four years, I have been part of a friendly and warm atmosphere in the Electric Power Engineering department. I also had the pleasure to meet and spend time with many colleagues. Funny stories, jokes, "teasing" each other, as well as technical and philosophical discussions during the coffee breaks have made my PhD journey not only more entertaining, but also more productive. For this, I need to thank many of my colleagues that I can now call them friends. It is, Aravinda, Atousa, Augusto, Babak, Dan El, Daniel, Erick, Gard, Gilbert, Ole-Christian, Rahgbendra, Reza, Santiago, Spyros, Subhadra, Tobias and Yoga. I also wish to show appreciation to the technical and administrative staff at the department who have been very helpful to me throughout the PhD duration.

The football practices have always been the best "therapy" to recover and forget sad and frustrating moments that normally happen during the PhD time. I therefore need to thank all members of the football team at the department, called "Power Challengers" for providing me many enjoyable moments.

Finally, I wish to extend my special thanks to a few more friends. It is their company which made my stay in Trondheim during the PhD time more pleasant. To Michalis V., Doc, George, Spyros, Lina, Stefanos, Artemis, Michalis S., Thomais, and Panos. Thank you all for the great memories. And to Hanne who supported my PhD journey to reach the final destination with her love, her company and her encouragement. Tusen takk.

## Abbreviations

| ASP      | Automatic and Self-Powered                                |

|----------|-----------------------------------------------------------|

| BIGT     | Bi-mode Insulated Gate Transistor                         |

| BiMOSFET | Bipolar Metal-Oxide Semiconductor Field Effect Transistor |

| DUT      | Device Under Test                                         |

| FS       | Field-Stop                                                |

| GDU      | Gate Drive Unit                                           |

| GTO      | Gate Turn-OFF                                             |

| HVAC     | High-Voltage Alternating Current                          |

| HVDC     | High-Voltage Direct Current                               |

| IEC      | International Electrotechnical Commission                 |

| IEEE     | Institute of Electrical and Electronics Engineers         |

| IGBT     | Insulated Gate Bipolar Transistor                         |

| IGCT     | Integrated Gate Commutated Thyristor                      |

| JFET     | Junction Field Effect Transistor                          |

| LVDC     | Low-Voltage Direct Current                                |

| MMC      | Modular Multilevel Converter                              |

| MMC-FB   | Modular Multilevel Converter with full bridge sub-modules |

| ММС-НВ   | Modular Multilevel Converter with half bridge sub-modules |

| MOSFET   | Metal-Oxide Semiconductor Field Effect Transistor         |

| MOV      | Metal-Oxide Varistor                                      |

| MVAC     | Medium-Voltage Alternating Current                        |

| MVDC     | Medium-Voltage Direct Current                             |

| NPC      | Neutral-Point Clamped                                     |

### NPT Non-Punch-Through

- PT Punch-Through

- **RCD** Resistor-Capacitor-Diode

- SiC Silicon Carbide

- SM Sub-modules

- VSC Voltage Source Converter

# Contents

| 1 | Intr | oductio   | n                                                     | 1  |

|---|------|-----------|-------------------------------------------------------|----|

|   | 1.1  | Backg     | round                                                 | 1  |

|   | 1.2  | Object    | tives and scope of the thesis                         | 2  |

|   |      | 1.2.1     | Objectives of the thesis and research questions       | 2  |

|   |      | 1.2.2     | Scope of the thesis                                   | 3  |

|   | 1.3  | Thesis    | outline                                               | 4  |

|   | 1.4  | Resear    | rch contributions                                     | 4  |

|   |      |           |                                                       |    |

| 2 | Prot | tection o | challenges in LVDC and MVDC power grids               | 7  |

|   | 2.1  | LVDC      | and MVDC power grids                                  | 8  |

|   |      | 2.1.1     | Potential applications of LVDC and MVDC power grids . | 9  |

|   | 2.2  | Short-    | circuit current in DC grids                           | 11 |

|   |      | 2.2.1     | Protection strategies in DC grids                     | 12 |

|   | 2.3  | Circui    | t breakers for LVDC and MVDC grids                    | 14 |

|   |      | 2.3.1     | Mechanical breakers with resonance circuit            | 15 |

|   |      | 2.3.2     | Solid-state DC circuit breakers                       | 16 |

|   |      | 2.3.3     | Hybrid DC circuit breakers                            | 16 |

|   | 2.4 | -                    | rative study among mechanical breaker with active reson-<br>rcuit, solid-state breaker and hybrid breaker                  | 17 |

|---|-----|----------------------|----------------------------------------------------------------------------------------------------------------------------|----|

|   |     | 2.4.1                | Impact of the short-circuit current on the design of VSCs .                                                                | 21 |

|   | 2.5 | Conclu               | isions                                                                                                                     | 25 |

| 3 | Pow | er semiø             | conductor devices for solid-state DC breakers                                                                              | 27 |

|   | 3.1 | Backgr               | round                                                                                                                      | 28 |

|   |     | 3.1.1                | Paradigm shift towards SiC-based power semiconductor devices                                                               | 29 |

|   |     | 3.1.2                | Desired characteristics of power devices employed in solid-<br>state DC circuit breakers                                   | 30 |

|   | 3.2 |                      | and SiC semiconductor device technologies for medium-<br>solid-state DC breakers                                           | 32 |

|   |     | 3.2.1                | Commercially available Silicon and SiC power semicon-<br>ductor device technologies in the voltage class of 1200-<br>1700V | 32 |

|   |     | 3.2.2                | Comparative evaluation at nominal gate voltage                                                                             | 36 |

|   |     | 3.2.3                | Comparative evaluation at maximum gate voltage                                                                             | 39 |

|   |     | 3.2.4                | Overdrive operation at high temperatures                                                                                   | 43 |

|   | 3.3 | Semico<br>state bi   | onductor device technologies for high-power MVDC solid-<br>reakers                                                         | 48 |

|   |     | 3.3.1                | Commercially available high-voltage and high-power semi-<br>conductor devices                                              | 49 |

|   |     | 3.3.2                | Modelling and simulation of a high-power solid-state MVDC breaker                                                          | 50 |

|   |     | 3.3.3                | Steady-state simulation results                                                                                            | 50 |

|   |     | 3.3.4                | Dynamic simulation results                                                                                                 | 53 |

|   | 3.4 | Conclu               | isions                                                                                                                     | 54 |

| 4 |     | rvoltage<br>e breake | e suppression configurations for LVDC and MVDC solid-                                                                      | 57 |

57

|   | 4.1   | Design   | principles of a solid-state DC circuit breaker                                                       | 58 |

|---|-------|----------|------------------------------------------------------------------------------------------------------|----|

|   |       | 4.1.1    | Current limiting inductor                                                                            | 58 |

|   |       | 4.1.2    | Overvoltage suppression circuit                                                                      | 58 |

|   | 4.2   |          | analysis of three overvoltage suppression configurations ved in solid-state DC breakers              | 59 |

|   |       | 4.2.1    | CON1: Solid-state DC circuit breaker with MOV                                                        | 59 |

|   |       | 4.2.2    | CON2: Solid-state DC circuit breaker with RCD snubber circuit                                        | 60 |

|   |       | 4.2.3    | CON3: Solid-state DC circuit breaker with MOV and RCD snubber circuit                                | 61 |

|   | 4.3   | Design   | principles of the three overvoltage suppression configurations                                       | 63 |

|   |       | 4.3.1    | Design principles of CON1                                                                            | 63 |

|   |       | 4.3.2    | Design principles of CON2                                                                            | 64 |

|   |       | 4.3.3    | Design principles of CON3                                                                            | 65 |

|   | 4.4   | Perform  | nance evaluation of the three overvoltage suppression circuits                                       | 66 |

|   |       | 4.4.1    | Simulation results for high-power MVDC solid-state breakers                                          | 66 |

|   |       | 4.4.2    | Experimental results for medium-power LVDC and MVDC solid-state breakers                             | 72 |

|   | 4.5   | Conclu   | sions                                                                                                | 82 |

| 5 | Serie | es conne | ection of IGBTs in solid-state MVDC breakers                                                         | 83 |

|   | 5.1   | Voltage  | e imbalances among series-connected IGBTs                                                            | 84 |

|   | 5.2   | Voltage  | e-balancing methods for series-connected IGBTs                                                       | 84 |

|   |       | 5.2.1    | Passive snubber circuits                                                                             | 85 |

|   |       | 5.2.2    | Active gate control circuits                                                                         | 86 |

|   |       | 5.2.3    | Voltage clamping circuits                                                                            | 87 |

|   | 5.3   | -        | ed hybrid method for even voltage distribution in series-<br>ted IGBTs for MVDC solid-state breakers | 87 |

|   |     | 5.3.1    | Design of the proposed hybrid voltage-balancing method .                      | 88  |

|---|-----|----------|-------------------------------------------------------------------------------|-----|

|   |     | 5.3.2    | Simulation results                                                            | 95  |

|   | 5.4 | Experi   | mental results                                                                | 99  |

|   |     | 5.4.1    | Experimental results at $V_{DC} = 1500V$                                      | 101 |

|   |     | 5.4.2    | Experimental results at $V_{DC} = 3000V$                                      | 104 |

|   | 5.5 | Conclu   | usions                                                                        | 106 |

| 6 | An  | automo   | tic and self-powered solid-state DC circuit breaker based                     | а   |

| U |     |          | y-ON SiC JFETs                                                                | 107 |

|   | 6.1 | Backg    | round                                                                         | 108 |

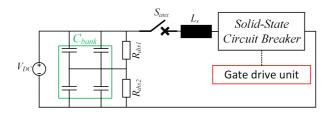

|   | 6.2 | -        | ting principle of the proposed ASP solid-state breaker with lly-ON SiC JFET   | 109 |

|   | 6.3 | -        | n considerations of the proposed ASP solid-state breaker with lly-ON SiC JFET | 112 |

|   | 6.4 |          | ation results                                                                 |     |

|   |     |          |                                                                               |     |

|   | 6.5 | -        | mental results                                                                |     |

|   | 6.6 | Conclu   | usions                                                                        | 121 |

| 7 | Con | clusions | s                                                                             | 123 |

|   | 7.1 | Future   | work                                                                          | 125 |

|   |     |          |                                                                               |     |

# **List of Tables**

| 2.1 | Summary of the performance comparison of the three investigated breakers                                                                 | 21 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Parameters of the investigated hybrid grid                                                                                               | 23 |

| 2.3 | Simulation results during a short-circuit in the DC line in case of using mechanical breakers in AC side for the fault clearance         | 24 |

| 2.4 | Simulation results during a short-circuit in the DC line in case of using solid-state DC circuit breakers for the fault clearance        | 25 |

| 3.1 | Silicon vs SiC material properties                                                                                                       | 29 |

| 3.2 | Design characteristics and rated current of 1200V-class semicon-<br>ductor devices                                                       | 36 |

| 3.3 | Design characteristics and rated current of 1700V-class semicon-<br>ductor devices                                                       | 37 |

| 3.4 | Impact of the overdrive on the conduction loss and junction temperature of the $1200V\mbox{-}class$ devices at maximum DC test current . | 46 |

| 3.5 | Impact of the overdrive on the conduction loss and junction temperature of the $1700V\mbox{-}class$ devices at maximum DC test current . | 47 |

| 3.6 | Parameters of the investigated high-power semiconductor devices employed in a solid-state MVDC breaker                                   | 51 |

| 4.1 | Comparative evaluation of CON1, CON2 and CON3                                                                                            | 66 |

| 4.2 | Parameters of the simulated $1.8 kV_{DC}$ grid and the utilized MOV $$ .                                                                      | 67  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3 | Comparative results of CON1, CON2 and CON3 with respect to the passive components requirements                                                | 67  |

| 4.4 | Simulation results of CON1, CON2 and CON3 during breaking operation                                                                           | 70  |

| 4.5 | Design parameters of the gate drive unit                                                                                                      | 73  |

| 4.6 | Parameters of the experimental setup                                                                                                          | 74  |

| 4.7 | Experimental results for CON1                                                                                                                 | 75  |

| 4.8 | Experimental results for CON2                                                                                                                 | 78  |

| 4.9 | Experimental results for CON3                                                                                                                 | 81  |

| 5.1 | Design and operating parameters of the DC power grid                                                                                          | 96  |

| 5.2 | Simulation results for the investigated cases with $t_d = 1 \mu s$                                                                            | 99  |

| 5.3 | Parameters of the experimental setup                                                                                                          | 101 |

| 5.4 | Design parameters of the gate drive units                                                                                                     | 101 |

| 5.5 | Experimental results for the $RCD_{ref}$ configuration at $V_{DC} = 1500V$ with $1\mu s$ gate signal propagation delay                        | 103 |

| 5.6 | Experimental results for the proposed scheme at $V_{DC} = 1500V$<br>with $1\mu s$ gate signal propagation delay                               | 103 |

| 5.7 | Experimental results for the $RCD_{ref}$ and the proposed configura-<br>tions at $V_{DC} = 3000V$ with $1\mu s$ gate signal propagation delay | 104 |

| 6.1 | Design and operating parameters of the DC power grid                                                                                          | 113 |

| 6.2 | Design parameters of the coupled inductors                                                                                                    | 117 |

| 6.3 | Parameters of the experimental setup (power circuit and gate driver)                                                                          | 117 |

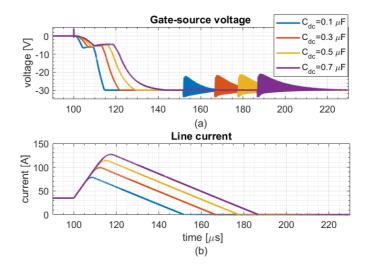

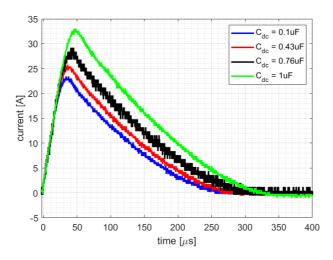

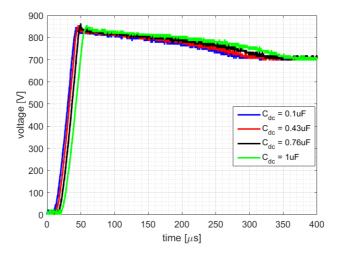

| 6.4 | Numerical experimental results for various $C_{dc}$ values $\ldots$ .                                                                         | 120 |

# **List of Figures**

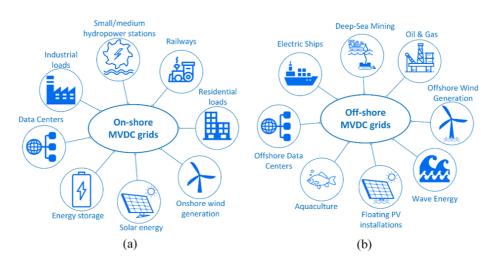

| 2.1 | Potential MVDC grid applications for: (a) onshore and (b) off-<br>shore power grids.                                                                                                                                                                                                                                   | 9  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

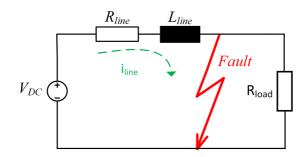

| 2.2 | A simplified DC grid when a short-circuit incident occurs                                                                                                                                                                                                                                                              | 12 |

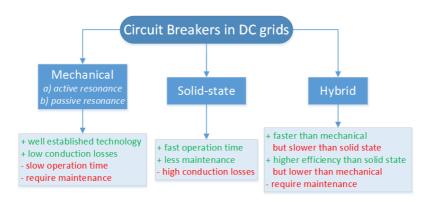

| 2.3 | The advantages and disadvantages of the three DC circuit breaker types.                                                                                                                                                                                                                                                | 14 |

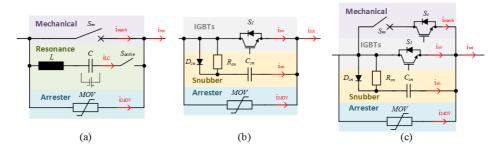

| 2.4 | Schematic diagrams of the main DC circuit breaker types: (a) mechanical breaker with active resonance, (b) solid-state circuit breaker, and (c) hybrid breaker.                                                                                                                                                        | 15 |

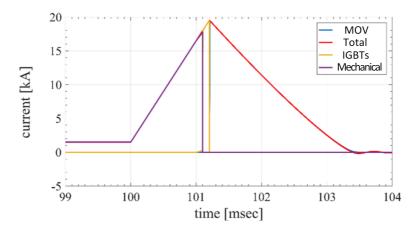

| 2.5 | Modelling of a simplified MVDC grid with circuit breakers                                                                                                                                                                                                                                                              | 17 |

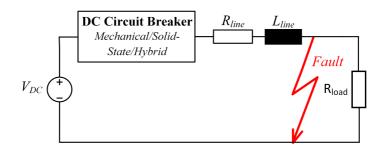

| 2.6 | Simulation results of: (a) the MOV current (blue line), fault line current (red line), LC tank current (yellow line) and mechanical current (purple line) in a breaking operation when mechanical breaker with active resonance circuit is employed in a $15kV_{DC}$ grid, and (b) the corresponding magnified values. | 18 |

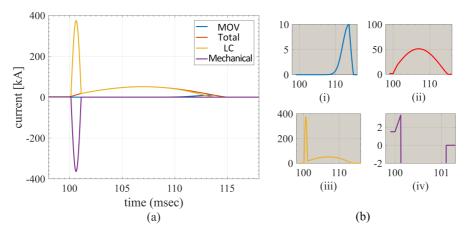

| 2.7 | Simulation results of the MOV current (blue line), snubber current (yellow line), IGBTs current (purple line) and fault line current (red line) in a breaking operation when solid-state breaker is employed in a $15kV_{DC}$ grid.                                                                                    | 19 |

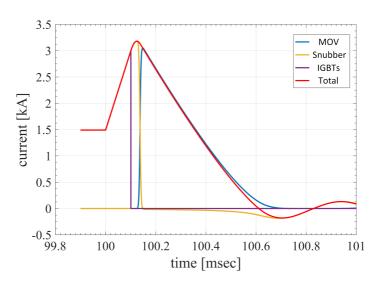

| 2.8 | Simulation results of the MOV current (blue line), fault line current (red line), IGBTs current (yellow line) and mechanical breaker current (purple line) in a breaking operation when hybrid breaker is employed in a $15kV_{DC}$ grid.                                                                              | 20 |

|     |                                                                                                                                                                                                                                                                                                                        |    |

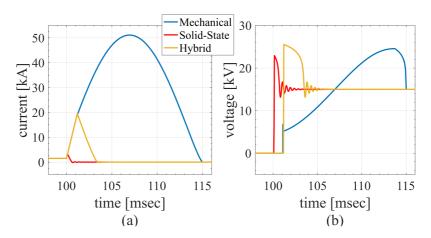

| 2.9  | Performance comparison of the three investigated breaker types during a short-circuit clearance process with respect to: (a) short-circuit current, and (b) transient voltage across each breaker   | 21      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

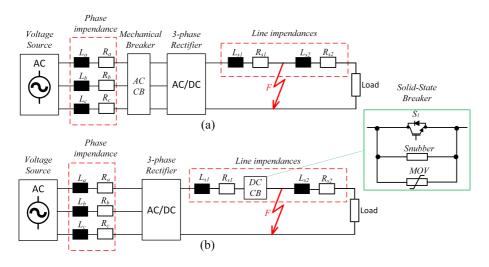

| 2.10 | Schematic diagrams of the two DC grid configurations under study:<br>(a) protection using an AC circuit breaker on the AC side, and (b)<br>protection using a solid-state DC breaker on the DC side | 22      |

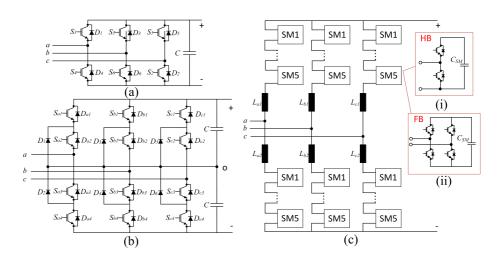

| 2.11 | Schematic diagrams of the basic types of active rectifiers: (a) 2-<br>level VSC, (b) 3-level NPC and (c) MMC consisting of (i) HBs<br>and (ii) FBs                                                  | 23      |

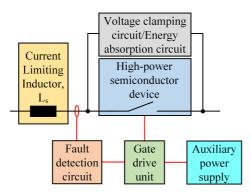

| 3.1  | Block diagram showing the main components of a typical inter-<br>rupting solid-state DC circuit breaker.                                                                                            | 28      |

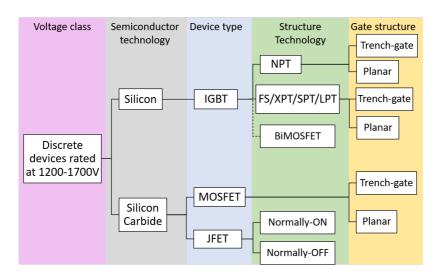

| 3.2  | Commercially available Silicon and SiC power semiconductor device technologies in the voltage class of $1200 - 1700V$                                                                               | 32      |

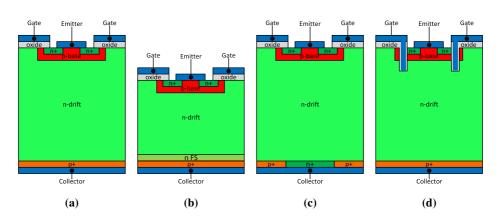

| 3.3  | Typical Silicon IGBT structures: (a) NPT IGBT, (b) FS/XPT/SPT/LPT IGBT, (c) BiMOSFET, and (d) NPT IGBT with trench-gate.                                                                            | Г<br>33 |

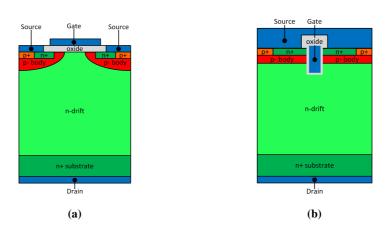

| 3.4  | Typical SiC MOSFET structures with: (a) planar-gate, and (b) trench-gate technology.                                                                                                                | 35      |

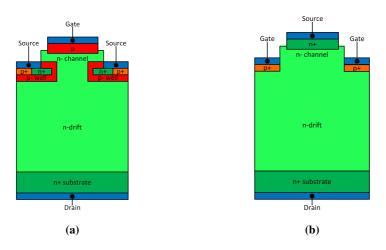

| 3.5  | Typical SiC JFET structures: (a) depletion mode (normally-ON), and (b) enhancement mode (normally-OFF).                                                                                             | 36      |

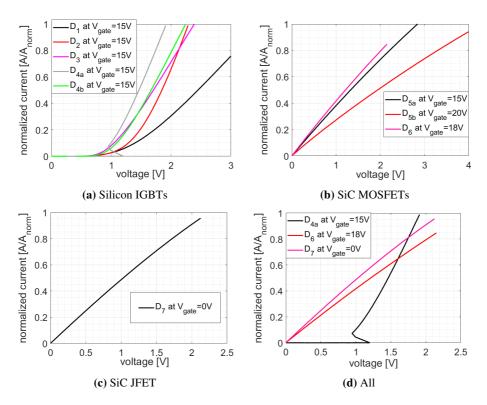

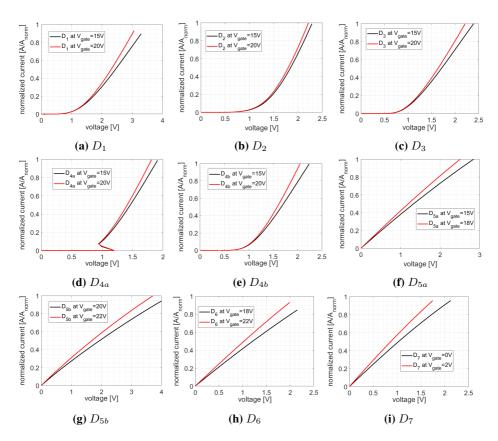

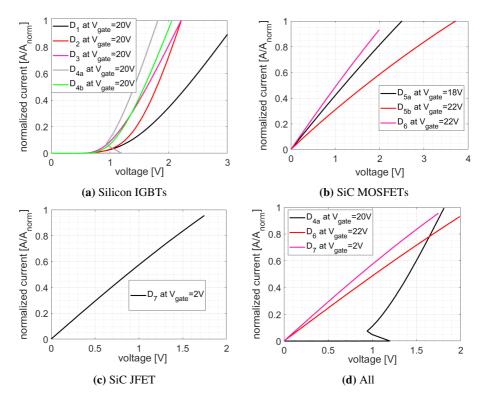

| 3.6  | IV characteristics at nominal gate voltages for all the investigated $1200V$ power semiconductor devices at room temperature ( $25^{\circ}C$ ).                                                     | 38      |

| 3.7  | IV characteristic of power semiconductor devices rated at $1700V$ at room temperature ( $25^{\circ}C$ ) under nominal gate voltages                                                                 | 39      |

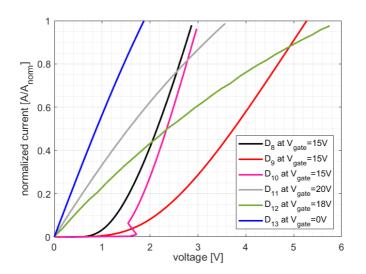

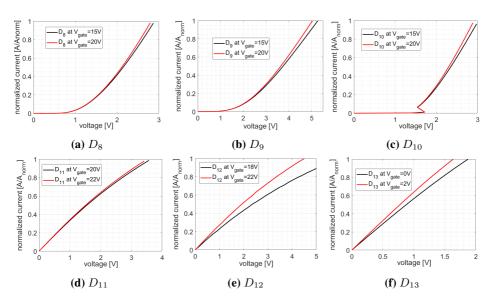

| 3.8  | IV characteristic at nominal and maximum gate voltages for all investigated 1200V-class power semiconductor devices                                                                                 | 40      |

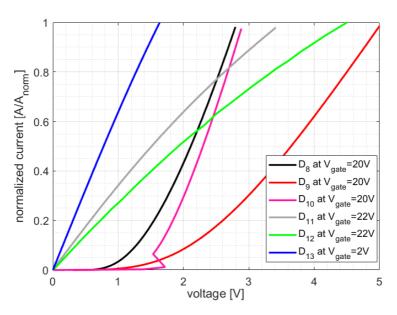

| 3.9  | IV characteristic at maximum gate voltages for all investigated 1200V-class power semiconductor devices.                                                                                            | 41      |

| 3.10 | IV characteristic at nominal and maximum gate voltages for all investigated $1700V$ power semiconductor devices                                                                                     | 42      |

| 3.11 | IV characteristic at maximum gate voltages for all investigated $1700V$ -class power semiconductor devices.                                                                                         | 43      |

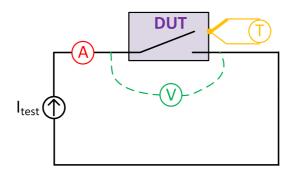

| 3.12 | Schematic diagram of the test circuit for measuring the forward voltage drop across the DUT, and the DUT's case temperature for various $I_{test}$ .                                                                                                          | 44 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.13 | Photograph of the experimental test setup                                                                                                                                                                                                                     | 44 |

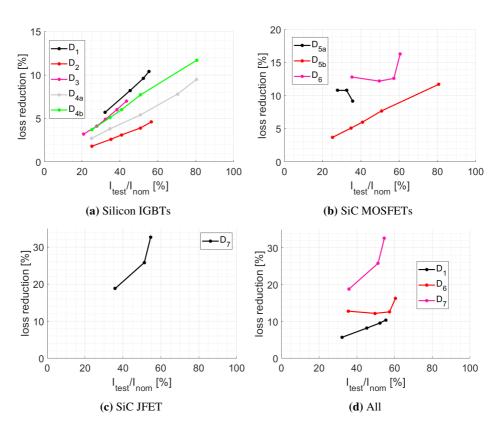

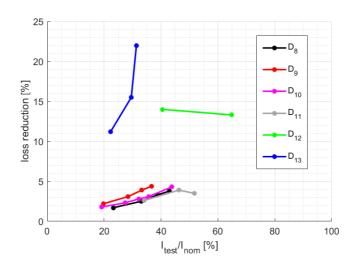

| 3.14 | Conduction loss reduction when applying maximum gate voltages at elevated junction temperatures for all $1200V$ -class DUTs at various $I_{test}$ .                                                                                                           | 45 |

| 3.15 | Conduction loss reduction when applying maximum gate voltages at elevated junction temperatures for all $1700V$ -class DUTs at various $I_{test}$ .                                                                                                           | 47 |

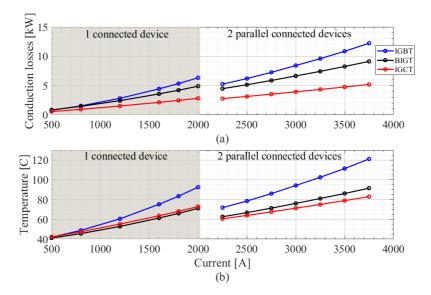

| 3.16 | Steady-state results for the three investigated semiconductor press-<br>pack devices employed in a $3kV$ solid-state DC breaker for various<br>load currents with respect to: (a) conduction power losses, and (b)<br>junction temperature.                   | 51 |

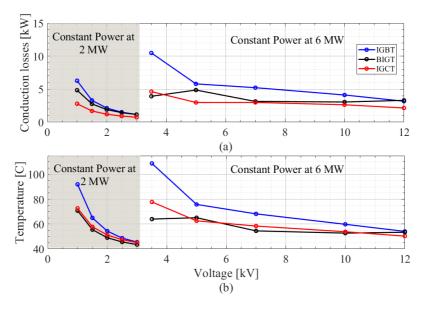

| 3.17 | Steady-state results for the three investigated semiconductor press-<br>pack devices employed in a solid-state breaker for various DC<br>voltage levels and two load demands with respect to: (a) conduc-<br>tion power losses, and (b) junction temperature  | 52 |

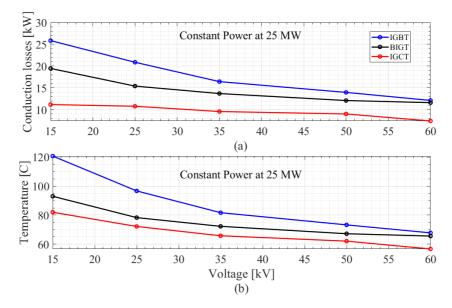

| 3.18 | Steady-state results for the three investigated semiconductor press-<br>pack devices employed in a solid-state breaker for various DC<br>voltage levels and $25MW$ load power with respect to: (a) con-<br>duction power losses, and (b) junction temperature | 53 |

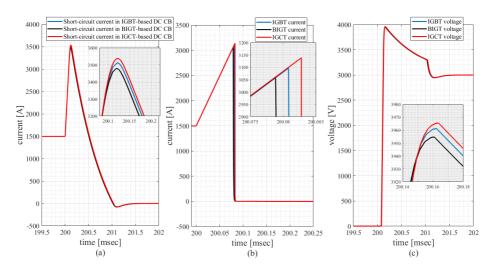

| 3.19 | Dynamic results for the three investigated solid-state breakers in a $3kV$ DC power grid employing IGBTs, BIGTs and IGCTs during a fault incident with respect to: (a) short-circuit line current, (b) switch current, and (c) switch voltage.                | 54 |

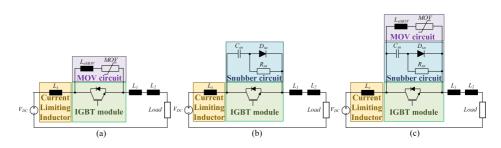

| 4.1  | The three investigated configurations: (a) CON1, (b) CON2, and (c) CON3                                                                                                                                                                                       | 59 |

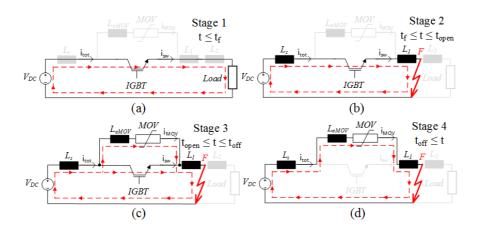

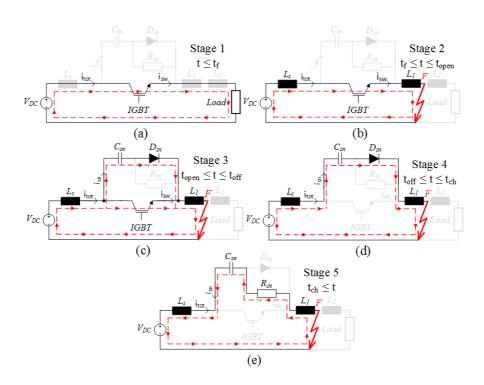

| 4.2  | Schematic diagrams of the discrete operating stages of the solid-<br>state DC circuit breaker using CON1.                                                                                                                                                     | 60 |

| 4.3  | Schematic diagrams of the discrete operating stages of the solid-<br>state DC circuit breaker using CON2.                                                                                                                                                     | 61 |

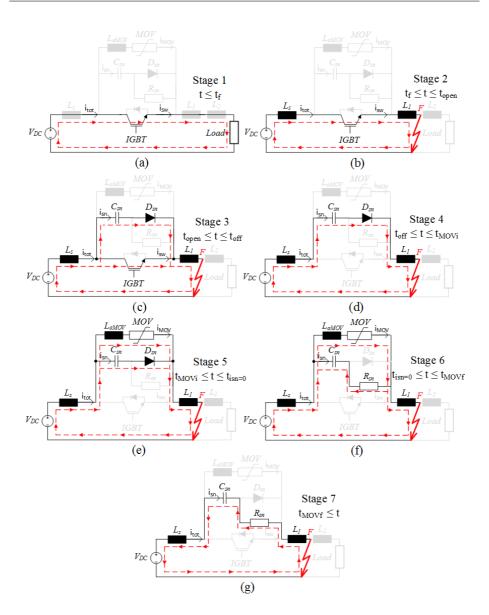

| 4.4  | Schematic diagrams of the discrete operating stages of the solid-<br>state DC circuit breaker using CON3.                                                                                                                                                     | 62 |

|      |                                                                                                                                                                                                                                                               |    |

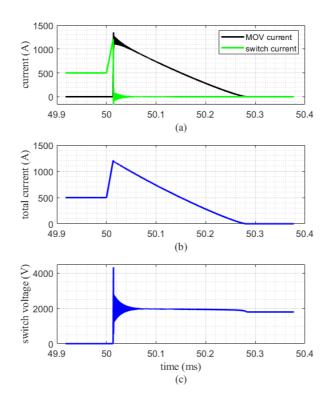

| 4.5  | Characteristic curve of an MOV.                                                                                                                                                                                                                                                                                                 | 63 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

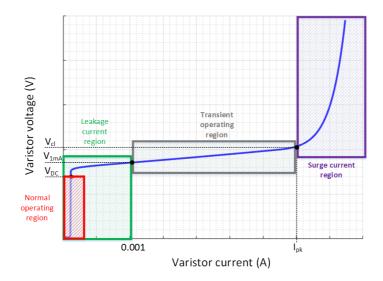

| 4.6  | Simulation results for the CON1 during the short-circuit: (a) MOV and switch currents, (b) total short-circuit current, and (c) switch voltage.                                                                                                                                                                                 | 68 |

| 4.7  | Simulation results for the CON2 during the short-circuit: (a) snub-<br>ber and switch currents, (b) total short-circuit current, and (c) switch<br>voltage.                                                                                                                                                                     | 69 |

| 4.8  | Simulation results for the CON3 during the short-circuit: (a) snub-<br>ber, MOV and switch currents, (b) total short-circuit current, and<br>(c) switch voltage.                                                                                                                                                                | 70 |

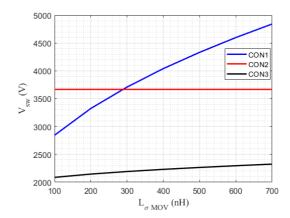

| 4.9  | Impact of the MOV stray inductance on the switch peak voltage for all the investigated configurations.                                                                                                                                                                                                                          | 71 |

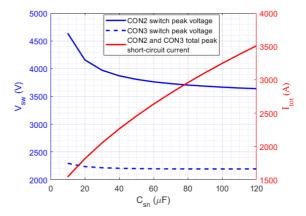

| 4.10 | Impact of the snubber capacitance on the switch peak voltage and total peak short-circuit current.                                                                                                                                                                                                                              | 71 |

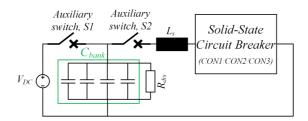

| 4.11 | Schematic diagram of the test circuit.                                                                                                                                                                                                                                                                                          | 72 |

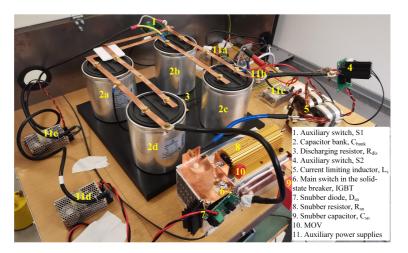

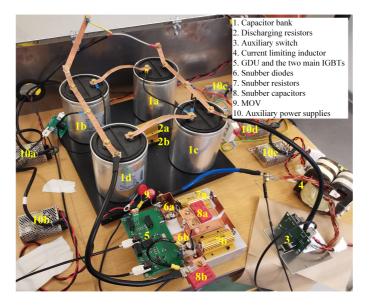

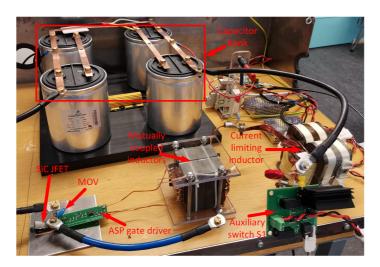

| 4.12 | Photograph of the experimental solid-state breaker prototype using CON3.                                                                                                                                                                                                                                                        | 72 |

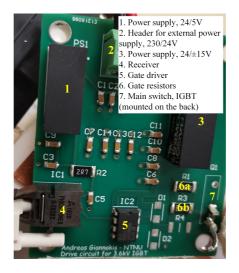

| 4.13 | Photograph of the gate drive unit.                                                                                                                                                                                                                                                                                              | 73 |

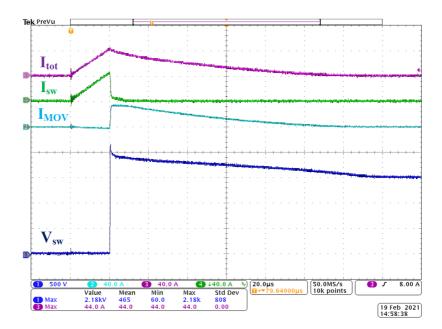

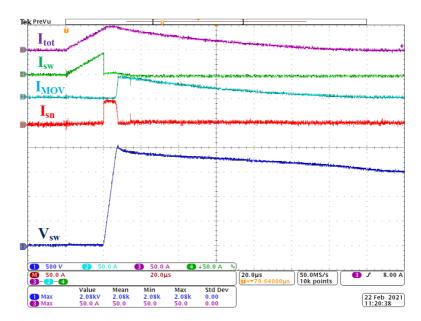

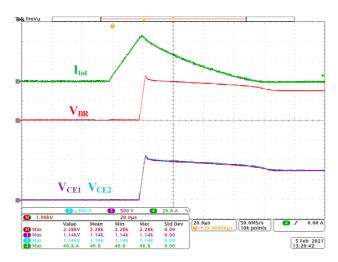

| 4.14 | Experimental results for the CON1 at $1500V_{DC}$ and $44A$ turn-OFF current. Measured line current (purple line, 40A/div), IGBT current (green line, 40A/div), MOV current (light blue line, 40A/div), and IGBT voltage (blue line, 500V/div), (time base $20\mu$ s/div).                                                      | 75 |

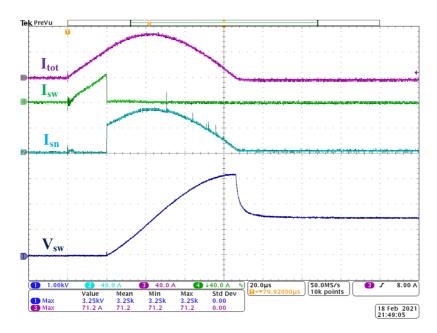

| 4.15 | Experimental results for the CON2 at $1500V_{DC}$ and $71.2A$ turn-<br>OFF current with $C_{sn} = 1\mu F$ . Measured line current (purple line,<br>40A/div), IGBT current (green line, 40A/div), snubber capacitor<br>current (light blue line, 40A/div), and IGBT voltage (blue line,<br>1kV/div), (time base 20 $\mu$ s/div). | 76 |

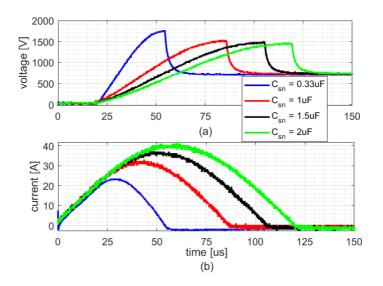

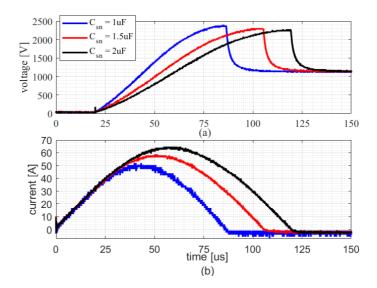

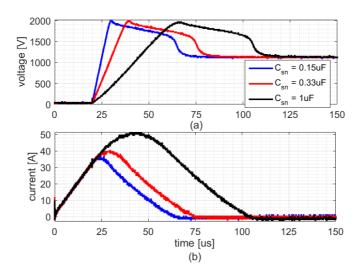

| 4.16 | Experimental results for CON2 at $700V_{DC}$ with several snubber capacitances: (a) switch voltage, and (b) line current                                                                                                                                                                                                        | 77 |

| 4.17 | Experimental results for CON2 at $1100V_{DC}$ with several snubber capacitances: (a) switch voltage, and (b) line current.                                                                                                                                                                                                      | 77 |

| 4.18 | Experimental results for CON2 at $1500V_{DC}$ with several snubber capacitances: (a) switch voltage, and (b) line current.                                                                                                                                                                                                      | 78 |

| 4.19 | Experimental results for the CON3 at $1500V_{DC}$ and $50A$ turn-OFF current with $C_{sn} = 0.15\mu F$ . Measured line current (purple line, 50A/div), IGBT current (green line, 50A/div), MOV current (light blue line, 50A/div), and IGBT voltage (blue line, 500V/div), (time base $20\mu s/div$ ). | 79 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

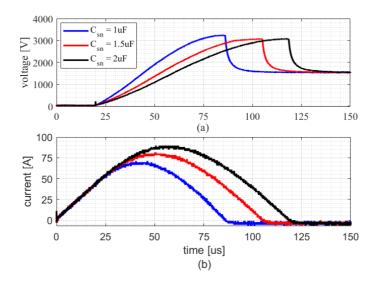

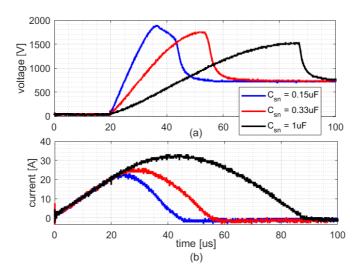

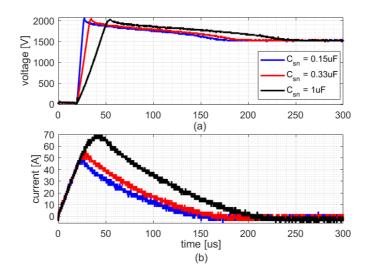

| 4.20 | Experimental results for CON3 at $700V_{DC}$ with several snubber capacitances: (a) switch voltage, and (b) line current.                                                                                                                                                                              | 80 |

| 4.21 | Experimental results for CON3 at $1100V_{DC}$ with several snubber capacitances: (a) switch voltage, and (b) line current                                                                                                                                                                              | 80 |

| 4.22 | Experimental results for CON3 at $1500V_{DC}$ with several snubber capacitances: (a) switch voltage, and (b) line current.                                                                                                                                                                             | 81 |

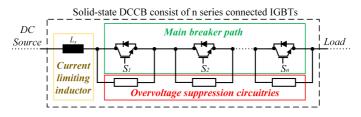

| 5.1  | Basic schematic circuit of an interrupting solid-state MVDC breaker.                                                                                                                                                                                                                                   | 84 |

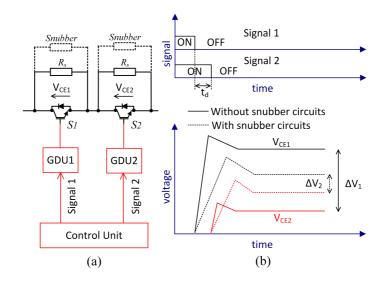

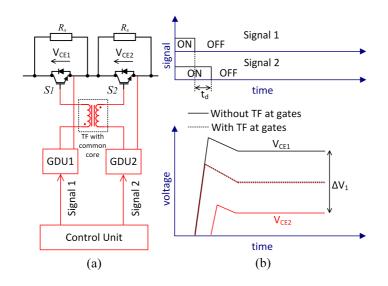

| 5.2  | Block diagrams showing: (a) two series-connected IGBTs with GDUs, static resistances and snubber circuits, and (b) gate signals of the two IGBTs along with their voltages with and without snubber circuits.                                                                                          | 85 |

| 5.3  | Block diagrams showing: (a) two series-connected IGBTs with magnetically coupled GDUs and static resistances and (b) gate signals of the two IGBTs along with their voltages with and without the gate coupled transformer.                                                                            | 86 |

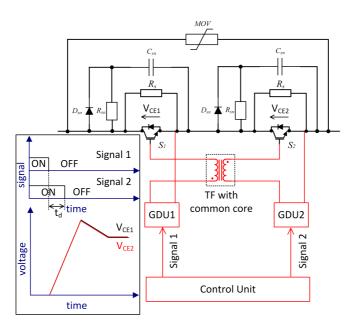

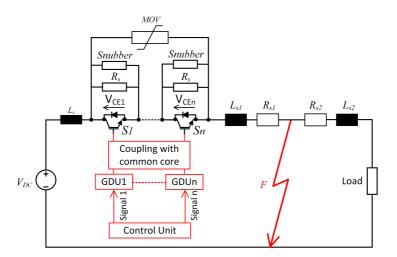

| 5.4  | Schematic diagram of the proposed hybrid voltage-balancing scheme<br>employed in a solid-state MVDC breaker comprising two series-<br>connected IGBTs                                                                                                                                                  | 88 |

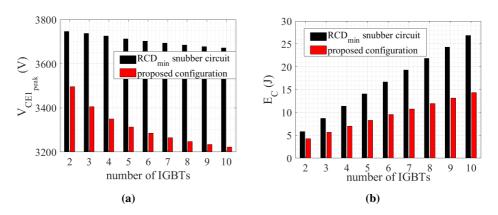

| 5.5  | Comparison between $RCD_{ref}$ and the proposed configuration in terms of: (a) peak voltage of the early turned-OFF IGBT, and (b) total energy storage capability of snubber capacitors with respect to the number of series-connected IGBTs.                                                          | 92 |

| 5.6  | Comparison between $RCD_{ref}$ and the proposed configurations for<br>the required $C_{sn}$ with respect to: (a) $I_{max}$ and $\Delta V_{CE}$ , (b) $I_{max}$ and<br>$t_d$ , and (c) $t_d$ and $\Delta V_{CE}$ .                                                                                      | 92 |

| 5.7  | Comparison between $RCD_{min}$ and the proposed configuration in terms of: (a) peak voltage of the early turned-OFF IGBT, and (b) total energy storage capability of snubber capacitors with respect to the number of series-connected IGBTs.                                                          | 93 |

|      |                                                                                                                                                                                                                                                                                                        | 73 |

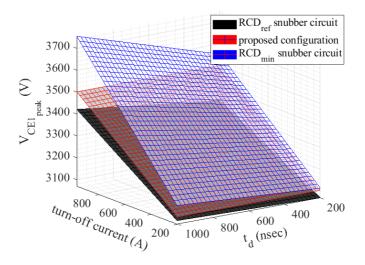

| 5.8  | Peak voltage of the early turned-OFF IGBT with respect to $I_{max}$<br>and $t_d$ at $4kV_{DC}$ in case of $RCD_{ref}$ (black), proposed configura-<br>tion (red), and $RCD_{min}$ (blue)                                                                                                                                                                                                               | 94  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

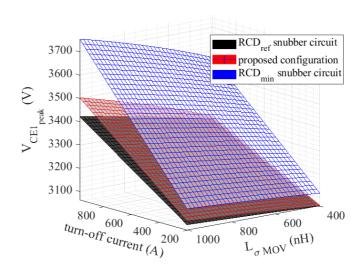

| 5.9  | Peak voltage of the early turned-OFF IGBT with respect to $I_{max}$<br>and $L_{\sigma MOV}$ at $4kV_{DC}$ in case of $RCD_{ref}$ (black), proposed con-<br>figuration (red), and $RCD_{min}$ (blue).                                                                                                                                                                                                   | 95  |

| 5.10 | Schematic diagram of the investigated MVDC power grid with<br>the proposed voltage-balancing configuration employed in a solid-<br>state breaker.                                                                                                                                                                                                                                                      | 96  |

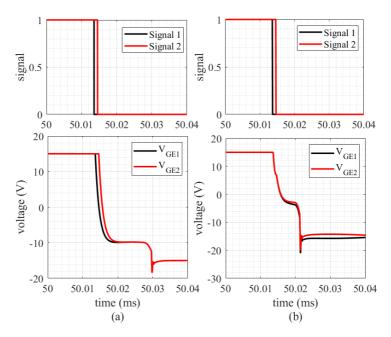

| 5.11 | Simulation results showing two gate signals with a propagation delay of $1\mu s$ between each other and the corresponding gate-emitter voltages for S1 and S2 in case of: (a) RCD snubber configurations $(RCD_{ref} \text{ and } RCD_{min})$ and (b) proposed configuration                                                                                                                           | 97  |

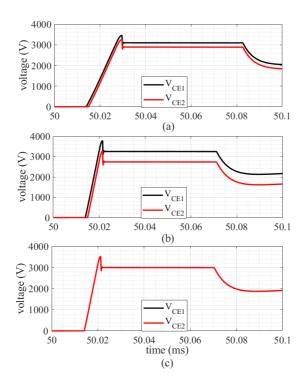

| 5.12 | Simulation results showing the voltages of the early turned-OFF IGBT (S1 with black) and the late turned-OFF IGBT (S2 with red) during a breaking operation in: (a) $RCD_{ref}$ , (b) $RCD_{min}$ , and (c) proposed configurations.                                                                                                                                                                   | 98  |

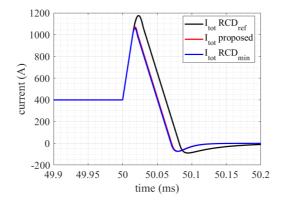

| 5.13 | Simulation results for the line fault currents in case of $RCD_{ref}$ (black), proposed (red) and $RCD_{min}$ (blue) configurations during a breaking operation.                                                                                                                                                                                                                                       | 98  |

| 5.14 | Schematic diagram of the test circuit                                                                                                                                                                                                                                                                                                                                                                  | 99  |

| 5.15 | Photograph of the experimental setup                                                                                                                                                                                                                                                                                                                                                                   | 100 |

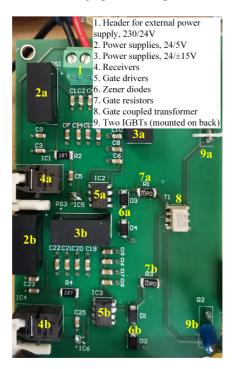

| 5.16 | Photograph of the proposed gate drive unit.                                                                                                                                                                                                                                                                                                                                                            | 100 |

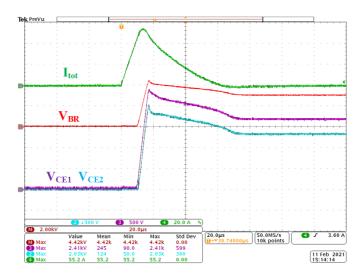

| 5.17 | Experimental results for the $RCD_{ref}$ configuration at $1500V_{DC}$<br>and 46A turn-OFF current with $C_{sn} = 0.15\mu F$ and $t_d = 1\mu s$ .<br>Measured line current (green line, 20A/div), early turned-OFF IGBT<br>voltage (purple line, 500V/div), late turned-OFF IGBT voltage<br>(light blue line, 500V/div), and total breaker voltage (red line,<br>1kV/div) (time base $20\mu s$ /div).  | 102 |

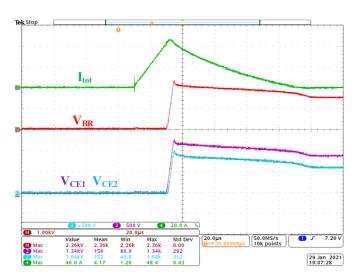

| 5.18 | Experimental results for the $RCD_{ref}$ configuration at $1500V_{DC}$<br>and $56.4A$ turn-OFF current with $C_{sn} = 1\mu F$ and $t_d = 1\mu s$ .<br>Measured line current (green line, 20A/div), early turned-OFF IGBT<br>voltage (purple line, 500V/div), late turned-OFF IGBT voltage<br>(light blue line, 500V/div), and total breaker voltage (red line,<br>1kV/div) (time base $40\mu s/div$ ). | 102 |

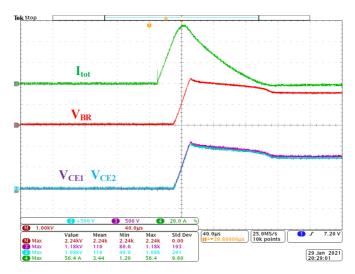

| 5.19 | Experimental results for the proposed configuration at $1500V_{DC}$<br>and 46.8 <i>A</i> turn-OFF current with $C_{sn} = 0.15\mu F$ and $t_d = 1\mu s$ .<br>Measured line current (green line, 20A/div), early turned-OFF IGBT<br>voltage (purple line, 500V/div), late turned-OFF IGBT voltage<br>(light blue line, 500V/div), and total breaker voltage (red line,<br>1kV/div) (time base 20 $\mu$ s/div). | 104                               |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 5.20 | Experimental results for the $RCD_{ref}$ configuration at $3000V_{DC}$<br>and $55.2A$ turn-OFF current with $C_{sn} = 0.15\mu F$ and $t_d = 1\mu s$ .<br>Measured line current (green line, 20A/div), early turned-OFF IGBT<br>voltage (purple line, 500V/div), late turned-OFF IGBT voltage<br>(light blue line, 500V/div), and total breaker voltage (red line,<br>2kV/div) (time base $20\mu s/div$ ).    | 105                               |

| 5.21 | Experimental results for the proposed scheme at $3000V_{DC}$ and $54.4A$ turn-OFF current with $C_{sn} = 0.15\mu F$ and $t_d = 1\mu s$ . Measured line current (green line, 20A/div), early turned-OFF IGBT voltage (purple line, 500V/div), late turned-OFF IGBT voltage (light blue line, 500V/div), and total breaker voltage (red line, 1kV/div) (time base $20\mu s/div$ ).                             | 105                               |

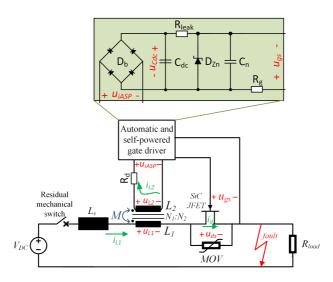

| 6.1  | Schematic diagram of the solid-state DC breaker employing a normal ON SiC JFET with the ASP gate driver.                                                                                                                                                                                                                                                                                                     | ly-<br>110                        |

| 6.2  | Theoretical performance of the proposed DC breaker                                                                                                                                                                                                                                                                                                                                                           | 111                               |

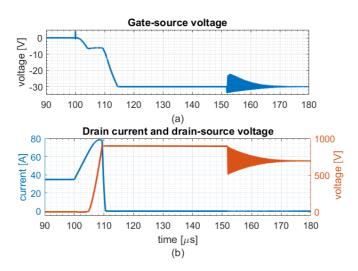

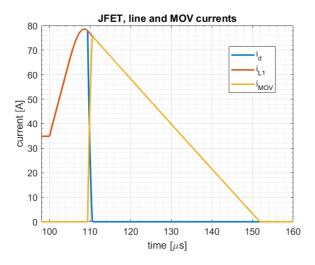

| 6.3  | Simulation results showing: (a) the gate-source voltage, and (b) the drain-source voltage and the drain current of the SiC JFET                                                                                                                                                                                                                                                                              |                                   |

| ( )  | under a short-circuit condition.                                                                                                                                                                                                                                                                                                                                                                             | 114                               |

| 6.4  | under a short-circuit condition                                                                                                                                                                                                                                                                                                                                                                              | <ul><li>114</li><li>114</li></ul> |

| 6.5  | Simulation results showing the drain current of the SiC JFET, the fault line current and the current through MOV under a short-                                                                                                                                                                                                                                                                              | 114                               |

|      | Simulation results showing the drain current of the SiC JFET, the fault line current and the current through MOV under a short-circuit condition                                                                                                                                                                                                                                                             | 114<br>115                        |

| 6.5  | Simulation results showing the drain current of the SiC JFET, the fault line current and the current through MOV under a short-circuit condition                                                                                                                                                                                                                                                             | 114<br>115                        |

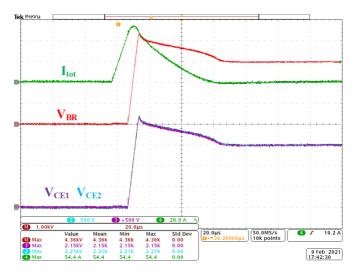

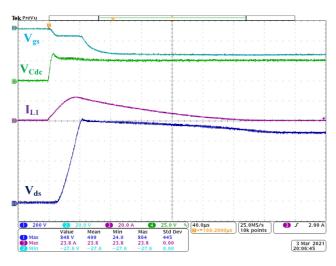

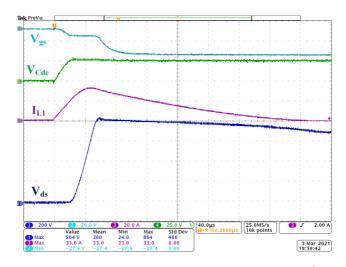

| 6.9  | Experimental results for the solid-state DC breaker with $C_{dc} = 0.1 \mu F$ . Measured line current (purple line, 20A/div), $C_{dc}$ voltage (green line, 25V/div), SiC JFET gate-source voltage (light blue line, 20V/div), and SiC JFET drain-source voltage (blue line, 200V/div), (time base $40 \mu s/div$ ) |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.10 | Experimental results for the solid-state DC breaker with $C_{dc} = 1\mu F$ . Measured line current (purple line, 20A/div), $C_{dc}$ voltage (green line, 25V/div), SiC JFET gate-source voltage (light blue line, 20V/div), and SiC JFET drain-source voltage (blue line, 200V/div), (time base $40\mu$ s/div)      |

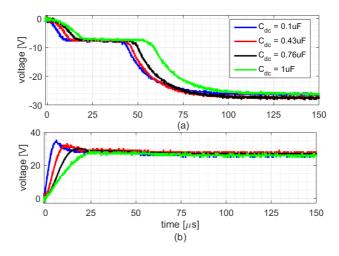

| 6.11 | Experimental results showing: (a) gate-source voltage $u_{gs}$ of the SiC JFET and (b) voltage of $C_{dc}$ , $u_{Cdc}$ for various $C_{dc}$ values 119                                                                                                                                                              |

| 6.12 | Experimental results showing the line current $i_{L1}$ for various $C_{dc}$ values                                                                                                                                                                                                                                  |

| 6.13 | Experimental results showing the drain-source voltage $u_{ds}$ of the SiC JFET for various $C_{dc}$ values                                                                                                                                                                                                          |

## Chapter 1

## Introduction

### 1.1 Background

The urgent need for decarbonization of the environment is imposed by the lowcarbon emission strategies adopted by several countries worldwide [1]. Decarbonization of the electricity sector necessitates the transformation of the existing electric power grid through the ever-increasing integration of renewable energy sources (RES) and the electrification of transportation sector. Grid transformation will be enabled by two key technologies, namely multi-terminal transmission and distribution grids and power electronic converters, which must exhibit the highest ever efficiency, power flow flexibility and supply reliability.

Today, with the tremendous technological development of high-voltage and highpower semiconductor devices, design of high-power electronic converters operating with medium and high-voltages and reaching record efficiencies becomes feasible [2, 3, 4, 5, 6]. Power converters are the catalyst that pave the way towards the development of Low-Voltage Direct Current (LVDC) and Medium-Voltage Direct Current (MVDC) grids. LVDC and MVDC grids ease the integration of RES and utility-scale battery storage dealing with intermittency of RES, as well as the electrification of DC loads such as large-scale charging infrastructure, by minimizing the required electrical energy conversion stages compared to Alternating Current (AC) counterparts. Besides, DC grids exhibit lower transmission and distribution losses than AC grids at the same voltage level [7]. However, the lack of a high-performance short-circuit protection schemes in LVDC and MVDC grids is currently the main showstopper for their further development.

In AC grids, short-circuit faults are cleared by using the state-of-the-art mechanical AC breakers technology. However, this technology is not suitable for clearing DC short-circuit faults due to the absence of current zero crossing, which in AC breaker is the necessary condition to extinguish the fault current. During the last decade,

several LVDC and MVDC circuit breakers have been proposed. A promising DC circuit breaker technology is the solid-state breakers. Solid-state breakers exhibit the shortest fault clearance times and require the least maintenance compared to other DC breaker topologies. Nevertheless, the main design challenge of the solid-state breakers is the high conduction power losses caused in the employed power semiconductor devices. In addition, the development of an application-oriented overvoltage suppression circuit for LVDC and MVDC breakers is also missing. Furthermore, the voltage level of an MVDC grid necessitates the use of multiple series-connected power semiconductor devices, which imposes design challenges related to the even voltage distribution among the devices during the breaking operation. Finally, the fast and efficient coordination between the circuit breaker and the fault detection circuit should also be considered when designing a solid-state breaker. A possible solution to this challenge is the development of an automatic breaker, which detects and interrupts the fault current without the need of external fault detection circuit.

### 1.2 Objectives and scope of the thesis

#### 1.2.1 Objectives of the thesis and research questions

This PhD project was funded by the Faculty of Information Technology and Electrical Engineering at the Norwegian University of Science and Technology, NTNU. The title of the research project was "Power electronics for DC circuit breakers". The primary objective of the project is **''to advance the design and performance of solid-state circuit breakers for LVDC and MVDC applications by delivering novel concepts and methodologies for breakers design and operation.''** From the beginning, two main research questions regarding the main objective were raised; (*i*) are the solid-state breakers a feasible protection solution against DC short-circuits that will ease the development of LVDC and MVDC grids? and (*ii*) what are the design and operating challenges of the solid-state DC breakers?

Several secondary objectives were also defined during the PhD work. These objectives are listed as follow.

- To deliver LVDC and MVDC solid-state breakers exhibiting the lowest conduction losses.

- To assess the state-of-the-art power semiconductor technologies used in solidstate breakers for minimizing conduction losses.

- To design and evaluate application-oriented overvoltage suppression configurations for LVDC and MVDC solid-state breakers.

- To design low-footprint overvoltage suppression configurations for MVDC solid-state breakers.

- To develop a self-triggered solid-state DC breaker.

During the PhD work and towards the accomplishment of these objectives, additional research questions were raised. Among others; (i) can the Silicon Carbide (SiC) power semiconductor devices be utilized in the design of the future solidstate DC breakers in order to minimize the conduction losses? (ii) what is the significance of the overvoltage suppression circuits on the performance and the size of the breaker? (iii) what are the design challenges of a solid-state breaker that requires multiple series-connected semiconductor devices? and (iv) what are the advantages of a self-triggered solid-state breaker?

The main direction of this PhD thesis is to complete the defined objectives by finding answers to the research questions presented above.

#### 1.2.2 Scope of the thesis

The scope of this PhD thesis is to demonstrate the use of solid-state circuit breakers in future LVDC and MVDC grids as a feasible solution. In general, solid-state breakers exhibit fast operation at a cost of high conduction losses. Thus, the optimal design of solid-state breakers for achieving high efficiency has been the main focus of this thesis. The performance evaluation of several Silicon and SiC semiconductor device technologies for the design of such breakers in terms of conduction losses has been conducted. In addition, the concept of overdriving active power semiconductor devices in order to improve their conducting performance by reducing conduction losses has also been proposed and investigated.

Apart from the conduction losses in a breaker design, the overvoltage suppression circuits can also be critical. The applicability and usability of three overvoltages suppression configurations used in LVDC and MVDC solid-state breakers has also been assessed with the focus on minimizing the electrical and thermal stress of the breaker itself and of other grid components.

Besides that, the design of a compact solid-state MVDC breaker is also within the scope of this PhD thesis. A hybrid overvoltage suppression scheme for MVDC solid-state breakers employing series-connected Insulated Gate Bipolar Transistor (IGBT)s for reducing the snubber capacitances requirements is proposed. The minimized snubber circuits lead to lower weight and smaller volume of the overall breaker design and thus, the entire solid-state breaker becomes more compact.

Finally, the development of an automatic and self-powered solid-state DC breaker eliminating the need for fault detection circuit and exhibiting low conduction losses is also in the scope of this PhD thesis. This has been assessed by designing a breaker using normally-ON SiC Junction Field Effect Transistor (JFET)s and coupled inductors, which feeds the gate with the required negative voltage during a breaking operation.

### 1.3 Thesis outline

- Chapter 1 introduces the topic of the thesis. In addition, it presents the scope and the contributions of the PhD thesis.

- Chapter 2 presents the protection challenges against short-circuits in LVDC and MVDC grids focusing on the need for developing high-performance solid-state circuit breakers.

- Chapter 3 analyses several Silicon and SiC power semiconductor device technologies that can be used in solid-state LVDC and MVDC breakers for medium-power and high-power grids. Additionally, the impact of overdriving the active devices on the conduction losses is presented via experiments.

- **Chapter 4** presents three overvoltage suppression configurations for semiconductor devices used in solid-state LVDC and MVDC breakers, as well as their application-specific usability. The advantages and disadvantages of each configuration are analyzed via simulations and experiments.

- Chapter 5 proposes a hybrid method to mitigate voltage imbalances among seriesconnected IGBTs used in an MVDC solid-state breaker during a short-circuit clearance operation. This method includes Resistor-Capacitor-Diode (RCD) snubber circuits and a magnetically coupled gate transformer aiming at minimizing the snubber capacitance requirements. Additionally, simulations and experimental results are also included to validate the proposed method.

- **Chapter 6** presents an automatic and self-powered solid-state breaker concept for  $700V_{DC}$  grids, using normally-ON SiC JFETs. This concept eliminates both fault detection circuit and external auxiliary power supply, and it also achieves low conduction losses. The proposed breaker has been validated through simulations and experiments.

- **Chapter 7** summarizes the main conclusions of the thesis. It also presents future research directions related to the topic of this PhD thesis.

### 1.4 Research contributions

The main contributions of this PhD thesis can be summarized as follow.

- Demonstration and validation of the benefits of using solid-state breakers for LVDC and MVDC grids.

- Identify the normally-ON SiC JFETs as the best-performing power semiconductor technology enabling the lowest conduction losses for the design of medium-power LVDC and MVDC solid-state breakers.

- Develop an overdriving operating methodology for Silicon and SiC power semiconductor technologies to minimize the conduction losses.

- Demonstrate the feasibility and the application-oriented usability of Metal-Oxide Varistor (MOV)s as an overvoltage suppression configuration for mediumpower solid-state LVDC and MVDC breakers.

- Demonstrate the applicability of using both RCD snubber circuits and MOVs as an overvoltage suppression configuration for high-power MVDC solid-state breakers.

- Design of a compact solid-state MVDC breaker employing series-connected IGBTs with minimum snubber capacitances requirements.

- Design of an automatic and self-powered solid-state breaker using normally-ON SiC JFETs, exhibiting low conduction losses and eliminating the need for external auxiliary circuits.

The contributions are further explained in the beginning of each Chapter. The scientific findings from this PhD thesis have been published in four journal articles and six conference papers. These can be found under "List of Publications" below. Additionally, two more conference papers have been published during the PhD work, and these are listed under "Other Publications".

#### **List of Publications**

- [P1] A. Giannakis and D. Peftitsis, "Design Considerations of Power Semiconductor Devices Employed in VSCs Under Short-Circuit Fault Conditions in MVDC Distribution Grids," 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, pp. P.1-P.11.

- [P2] A. Giannakis and D. Peftitsis, "MVDC Distribution Grids and Potential Applications: Future Trends and Protection Challenges," 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), 2018, pp. P.1-P.9.

- [P3] A. Giannakis and D. Peftitsis, "Electro-thermal Design of a Solid-State MVDC Circuit Breaker," 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019 - ECCE Asia), 2019, pp. 1-8, doi: 10.23919/ICPE2019-ECCEAsia42246.2019.8797031.

- [P4] A. Giannakis and D. Peftitsis, "Performance evaluation of high power semiconductor devices employed in solid-state circuit breakers for MVDC grids," 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), 2019, pp. P.1-P.10, doi: 10.23919/EPE.2019.8915533.

- [P5] A. Giannakis and D. Peftitsis, "Performance Evaluation and Limitations of Overvoltage Suppression Circuits for Low- and Medium-Voltage DC Solid-State Breakers," in IEEE Open Journal of Power Electronics, vol. 2, pp. 277-289, 2021, doi: 10.1109/OJPEL.2021.3068531.

- [P6] A. Giannakis and D. Peftitsis, "An Automatic and Self-Powered Solid-State DC breaker with Normally-ON SiC JFETs," PCIM Europe digital days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, pp. 1-7.

- [P7] A. Giannakis and D. Peftitsis, "Voltage Balancing Considerations for Series-Connected IGBTs in MV Solid-State DC Breakers," 2021 IEEE 12th Energy Conversion Congress & Exposition - Asia (ECCE-Asia), 2021, pp. 580-585, doi: 10.1109/ECCE-Asia49820.2021.9479127.

- [P8] Giannakis, A, Peftitsis, D. A universal automatic and self-powered gate driver power supply for normally-ON SiC JFETs. IET Power Electron. 2021; 14: 1820–1833. https://doi.org/10.1049/pel2.12151

- [P9] A. Giannakis and D. Peftitsis, "Overvoltage Suppression Scheme for Minimized Snubber Requirements in MVDC Solid-State Breakers with Series-Connected IGBTs," submitted in IEEE Journal of Emerging and Selected Topics in Power Electronics. (Accepted under major revision)

- [P10] A. Giannakis and D. Peftitsis, "Comparative Evaluation of Silicon and SiC Power Semiconductors for Solid-State DC Breakers," submitted in IEEE Transactions on Power Electronics. (Accepted under major revision)

#### **Other Publications**

- [O1] S. J. K. Berg, A. Giannakis and D. Peftitsis, "Analytical design considerations for MVDC solid-state circuit breakers," 2019 21st European Conference on Power Electronics and Applications (EPE '19 ECCE Europe), 2019, pp. 1-10, doi: 10.23919/EPE.2019.8915142.

- [O2] T. N. Ubostad, A. Giannakis, G. L. Rodal, D. A. Phillips and D. Peftitsis, "Reduction of Parasitic Inductance and Thermal Management in a Multichip SiC Half-Bridge Module," PCIM Europe digital days 2021; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2021, pp. 1-7.

## Chapter 2

# **Protection challenges in LVDC and MVDC power grids**

This Chapter presents the protection challenges in DC power grids. Initially, a short introduction to LVDC and MVDC power grids is given. Then, a short-circuit fault in a DC power line along with its impact on grid components is analyzed. In addition, the basic DC circuit breaker concepts found in literature are briefly discussed. Simulation results of three such breaker concepts are presented. Lastly, the impact of a short-circuit in a DC line on the electrical and thermal stress of power semiconductors in various Voltage Source Converter (VSC)s is also investigated.

#### Contributions

A comparative evaluation of three main DC circuit breakers via simulations has been presented. The superior performance of solid-state DC breakers over mechanical (with active resonance circuit) and hybrid ones in terms of short clearance time and low peak fault current has been revealed [P2]. Additionally, the impact of a short-circuit in an MVDC power line on the design of four VSCs has been investigated [P1]. The simulation results showed that the long reaction time of mechanical breakers connected to the AC side leads to significantly high short-circuit current flowing through the antiparallel diodes of the VSCs. They also revealed that the use of solid-state DC breakers decreases drastically the fault current. This Chapter summarizes the content of three publications [P1, P2, O1].

### 2.1 LVDC and MVDC power grids

Today, even though electric power is transmitted by means of both High-Voltage Direct Current (HVDC) and High-Voltage Alternating Current (HVAC) power grids, the power distribution is only performed using Medium-Voltage Alternating Current (MVAC) systems. The utilization of low-frequency and reliable transformers facilitates the voltage conversion from a high level to a lower one, and vice versa. Therefore, the electric power can be generated, distributed and transmitted efficiently at various AC voltage levels, minimizing the losses at the conversion stages. However, the expansion of distributed generation, as well as the increased demand of DC loads have imposed the need for developing more DC power grids, not only for power transmission, but also for power distribution operating at LVDC and MVDC. Additionally, the liberalization of the energy market has also pave the way for integration of more LVDC and MVDC systems into the existed power grid. The benefits of transmitting electric power through DC grids over AC counterparts are as follow:

- Higher efficiency of power transmission and distribution under the same voltage levels [7]

- No need for frequency synchronization which leads to easier integration of multiple energy sources

- No reactive power and thus, no need for reactive power compensation

Furthermore, a decisive factor for the envisaged expansion of LVDC and MVDC grids is the advancement in high-power semiconductors technology. The main reason is the need for designing efficient high-voltage high-power electronic converters which will be used for the required voltage conversions. Today, the improvement of the semiconductor technology seems able to facilitate such a paradigm shift towards DC distribution grids, designing power electronic converters that minimize the power losses [2, 3, 4, 5, 6].

On the other hand, several challenges may appear when DC grids are developed. The higher investment and installation cost of power converters used in DC applications compared to the transformers in AC counterparts remain a significant drawback. Additionally, the development of a high-performance protection scheme against short-circuits slows down the expansion of more DC grids today. Last but not least, the lack of specific standardization related to the operation and safety (human safety, grounding rules, insulation requirements) of MVDC grids is also an issue that needs to be addressed soon [P2]. However, for the electrification of electric ships using MVDC, standards have been established, i.e. Institute of Electrical

**Figure 2.1:** Potential MVDC grid applications for: (a) onshore and (b) offshore power grids.

and Electronics Engineers (IEEE) standard 1709-2010 [8]. Among others, IEEE recommends that MVDC starts above 1kV and up to and including 35kV. In particular, this framework defines recommended voltage levels at 1.5kV, 3kV, 6kV, 12kV, 18kV, 24kV or 30kV. On the other hand, for HVDC and LVDC power grids, both the International Electrotechnical Commission (IEC) and IEEE have established several standards and regulations [9, 10, 11]. According to IEC 60038, the LVDC is defined up to 1.5kV, which leads to a "grey" zone for voltage levels between 1kV to 1.5kV taking into consideration the IEEE standard 1709-2010 as mentioned above. Therefore, a common standardization handbook regarding the division among LVDC, MVDC and HVDC is clearly lacking.

#### 2.1.1 Potential applications of LVDC and MVDC power grids

The integration of renewable energy sources to the grid can be eased by utilizing DC power due to the nature of these sources. For example, photovoltaic (PV) panels generate DC power leading to the need for developing DC collection grids instead of the current trend of AC counterparts [12]. On top of that, there are plenty of other onshore and offshore applications that can be eased by using DC distribution grids as they can be seen in Fig. 2.1. Both LVDC and MVDC concepts can be used in all these applications depending always on the power and voltage requirements of each case.

Offshore wind power can benefit from utilizing DC grids instead of AC counterparts, achieving higher efficiency [13], as well as minimizing the required equipment (i.e. power converters and high-frequency transformers) compared to the bulky low-frequency transformers used in AC systems [14, 15]. In addition to that, electric ships can be electrified with LVDC or MVDC distribution systems [8, 16, 17]. The advantages will be higher fuel efficiency, lower weight, minimized footprint of the electric equipment, as well as higher control flexibility in comparison with electric vessels electrified with LVAC or MVAC power grids [18]. As mentioned before, a framework related to the on board power distribution of the future electric vessels based on MVDC system has been already established [8], paving the way for further electric ships development.

A microgrid is defined as a grid-connected power cluster of distributed generation, energy storage systems and loads integrated into a unity. LVDC and MVDC microgrids are currently trend solutions to several applications and they are advantageous over AC counterparts in terms of efficiency and mostly of simply integration of various energy sources [19, 20]. Moreover, electric transportation can also benefit from DC electrification. In particular, electric trains could potentially increase their performance by minimizing the power losses associated with the conversion stages, as well as with the lines/cables by utilizing DC supply instead of the state-of-the-art AC. In [21], a comparison between AC and DC electrification of a railway revealed that at elevated power, i.e. 10MW with voltage rating at 10kV, the DC case exhibits better performance compared to AC counterparts.