Benjamin D. Askelund

# 28nm On-Chip Ultra Low Power Switched Capacitor Buck Voltage Regulator for use in Wireless Sensor Nodes and IoT Applications

Masteroppgave i Electronics Systems Design and Innovation Veileder: Trond Ytterdal Medveileder: Pål Øyvind Reichelt Juni 2021

NTNU Norges teknisk-naturvitenskapelige universitet Fakultet for informasjonsteknologi og elektroteknikk Institutt for elektroniske systemer

Benjamin D. Askelund

# 28nm On-Chip Ultra Low Power Switched Capacitor Buck Voltage Regulator for use in Wireless Sensor Nodes and IoT Applications

Masteroppgave i Electronics Systems Design and Innovation Veileder: Trond Ytterdal Medveileder: Pål Øyvind Reichelt Juni 2021

Norges teknisk-naturvitenskapelige universitet Fakultet for informasjonsteknologi og elektroteknikk Institutt for elektroniske systemer

## PREFACE

The presented work is the result of the final project of the TFE4940 Master of Science at Electronics Systems Design and Innovation (ELSYS), as part of the Norwegian University of Science and Technology (NTNU). The project was carried out at the Department of Electronic Systems between January and June of 2021, and has been supervised by Trond Ytterdal (NTNU) and co-supervised by Pål Øyvind Reichelt (Disruptive Technologies AS). The initial idea of this Master's thesis was suggested by Disruptive Technologies AS Oslo.

#### The authors background and experience

During my time at ELSYS, I specialized in design of digital systems. Therefore, my knowledge and experience with analog circuit design is limited. This will probably be reflected in the conducted work and results of this thesis. However, I chose this project because of my interests in power-saving techniques and the future potential of this technology. This thesis may presents a simplified version of a very complex topic. However, I hope that this thesis will contribute with a better understanding of the applicable theory for those who follow. Despite the fact that it felt like an enormous amount of work for someone with limited experience, I have learned a great deal. All figures presented is made by the author.

#### Keywords

IoT, Integrated step-down converter, charge pump, switched capacitor arcitecture. 1MHzClock frequency, 3.3 to 1.8V converter,  $47\mu F$  capacitive load, low-power low-current 1nA to  $10\mu A$  output. 28nm technology.

#### Abstract

This thesis presents the fundamental aspect of a Switched Capacitor Power Converter (SCPC) and how to achieve multiple voltage conversion ratios for a practical application. This thesis builds on existing theoretical concepts, but also contributes by investigating new aspects within the field of research. The end-product is intended to serve as a proof-of-concept. Due to the increased circuit complexity, this thesis focuses on the analysis and design of the power stage of DC-DC converter mainly.

In this thesis, an on-chip switched capacitor step-down voltage regulator (OCVR) utilising three different topologies is designed and simulated with 28nm technology. The converter's load requires only 10  $\mu$ A, and any losses above 10  $\mu$ A is considered critical for the design. The main purpose is therefore to have the most effective power transfer with minimal losses when stepping down a varying input voltage source ranging from 3.3 V to 2.4 V to a stable 1.8V on the output terminal.

It was discovered during testing of the triple-topology module that both capacitors and MOS-switches had to be multiplied with a factor of 3 to meet the specified operation parameters. The final triple-topology design, excluding the control circuits, achieved an efficiency ranging from 71.2% to 95.7%, peaking at 2.4 V, however, area demanding. The proposed converter provides an output voltage of 1.8V well within the requirement as the voltage at the output varied by a maximum of  $\pm$  25 mV in both ripple and DC offset. The final design has also taken into account a 200 mV voltage-drop over the output load. A 47  $\mu$ F load capacitor outside the integrated circuit is used for handling current-spikes when in active mode, as the load may require more power for a short period of time. The device will have a 1MHz clock available when in active mode, which is utilized by the Switch-Capacitor module.

#### Sammendrag

Denne oppgaven tar for seg grunnleggende aspekter i Switched-Capacitor Effekt Omformere (SCPC), og hvordan man kan realisere de nødvendige spenningsomregningsforholdene for et bestemt bruksområde. Denne masteren bygger på eksisterende teoretiske grunnlag, men bidrar også ved å undersøke nye muligheter innen forskningsfeltet. Sluttproduktet er ment som å tjene som et proof-of-concept. På grunn av kretskompleksiteten i dette feltet, fokuserer denne oppgaven hovedsakelig på analyse og utforming av effekt-trinnet til DC-DC-omformeren.

Denne oppgaven presenterer en on-chip switched capacitor step-down voltage regulator (OCVR) som bruker tre forskjellige topologier, og denne er designet og simulert i 28 nm teknologi. Omformerens last krever bare 10 mu A, og eventuelle tap over 10 mu A anses å være kritiske for designet. Hovedformålet er derfor å ha den mest effektive effektover-føringen med minst mulig tap når man trapper ned en varierende inngangsspenning som spenner fra 3,3 V til 2,4 V, til en stabil 1,8 V på utgangsterminalen.

Det ble oppdaget under testing av trippel-topologimodulen, at både kondensatorer og MOS-brytere måtte multipliseres med en faktor på 3 for å oppfylle de spesifiserte driftsparametrene. Det endelige trippel-topologidesignet, unntatt kontrollkretsene, oppnådde en effektivitet fra 71,2% til 95,7%, og nådde maks på 2,4 V, men som betyr at den ble arealkrevende. Den foreslåtte omformeren skal gi en utgangsspenning på 1,8 V, men hvor spenningen ved utgangen kan maksimalt variere med  $\pm$  25 mV i både støy og DC offset. Den endelige utformingen har også tatt hensyn til et 200 mV spenningsfall over utgangslasten. En 47 mu F lastkondensator utenfor den integrerte kretsen brukes til å håndtere strømtopper når den er i aktiv modus, da belastningen kan kreve mer kraft i en kort periode. Enheten vil ha en 1MHz klokke tilgjengelig i aktiv modus, som brukes av Switch-Capacitor-modulen.

## ACKNOWLEDGEMENTS

**Trond Ytterdal**, Professor NTNU, Department of Electronics and Telecommunications: Supervisor at NTNU

**Pål Øyvind Reichelt**, Senior Analog Architect, Disruptive Technologie AS: Co-supervisor

**Pål Gunnar Hogganvik**, PhD Student, Nanoelectronic systems at UiO: General know how in analog circuit design

It would be a understatement to say that I would not have been able to hand in this thesis without some help along the way. First and foremost, I would like to thank Prof. Trond Ytterdal for his support and professional approach while supervising me during my project and master's thesis. His years of experience within the field of nanoscale electronics, and his know how from hundreds of publications have greatly inspired me to improve my work on this thesis. Both Ytterdal and co-supervisor Pål Øyvind Reichelt never failed to encourage me, even when struggling with the task at hand, asking all kinds of questions. They have been both helpful and supporting, which have helped me to improve the way I handle challenging tasks.

I can also not ignore Pål Gunnar Hogganvik's help, which was been crucial for setting up and navigating the complexity of the Cadence software, at the same time explaining to me some fundamental theory within the field of nanoscale CMOS electronics, giving me a good start to it all.

I would also recommend the reader to check out the references provided in this work as there are many great minds working every day to improve this technology.

Lastly I would like to thank my friends and family for all support during this project, and as well throughout my studies. I love you you all!

## PROBLEM DESCRIPTION

The goal of this thesis is to design a proof-of-concept DC-DC voltage regulator aiming to reach the absolute minimum power-loss possible, hence maximising efficiency. This task is one of the highest priorities set by Disruptive Technologies in order to reach the ambitious goal of maximising the lifespan of a 3.3V battery-cell, giving their Wireless Sensor Network technology an astonishing 15 year life expectancy without the possibility of recharging. The most complicated aspect, is the area requirements, which restrict the use of bulky and passive components leaving the only option to implement the voltage regulator as an on-chip integrated circuit using 28nm technology. The required specifications are:

- ▶ Input voltage range: 3.3V to 2.4V

- $\blacktriangleright$  Output voltage: 1.8V

- ▶ Output accuracy:  $\pm 25mV$

- ▶ Maximum load current:  $10\mu A$

- ▶ Load capacitor:  $47\mu F$

- ▶ Maximum clock frequency: 1MHz

This master's thesis is a continuation of the project thesis written by the author in autumn 2020 [5]. The project acted as a feasibility study for this thesis and some parts presented here are directly related to the project thesis. In that project, a circuit design of a multi switched-capacitor circuit was presented situated on Charge Balance Analysis in combination with a Verilog-A-based regulation system. In that project, it was not taken into account any voltage-drop across the load, and non of the topologies used charged in both phases. This approach came close to satisfy the given parameters at some intervals, confirming some of the theory, but fell short when implemented/simulated over a wide input range. This thesis builds upon the work carried out in the specialization project and is a continuation that is intending to improve upon this work by using a Charge Flow Analysis approach. This work will also emphasise on the Charge Balance Analysis versus Charge Flow Analysis and how the two can give different result and performance.

## Abbreviations and Notations

| ARCT CTRL            | Architecture Control                              |

|----------------------|---------------------------------------------------|

| COMP                 | Comperator                                        |

| CLK                  | Clock                                             |

| CMOS                 | Complementary Metal Oxide Semiconductor           |

| DC/dc                | Direct current                                    |

| FPGA                 | Field-Programmable Gate Array                     |

| IC                   | Integrated Circuits                               |

| ICT                  | Information and communication technology          |

| IoT                  | Internet of Things                                |

| KCL                  | Kirchoffs Current Law                             |

| KVL                  | Kirchoffs Voltage Law                             |

| LED                  | Light-emitting diode                              |

| MIM                  | Metal-Insulator-Metal                             |

| MOM                  | Metal-Oxiede-Metal                                |

| MOSFET               | Metal-Oxide-Semiconductor-Field-Effect-Transistor |

| MCU                  | Microcontroller Unit                              |

| NMOS                 | Negative-Channel Metal Oxide Semiconductor        |

| ULP                  | Ultra-Low-Power                                   |

| OCVR                 | On-chip voltage regulator                         |

| PMOS                 | Positive-Channel Metal Oxide Semiconductor        |

| PMIC                 | Power Management Integrated Circuit               |

| PMU                  | Power Management Unit                             |

| $\mathbf{PFM}$       | Pulse-Frequency Modulation                        |

| PWM                  | Pulse-Width-Modulation                            |

| $\mathbf{SC}$        | Switch-Capacitor                                  |

| SCPC                 | Switch-Capacitor Power Circuit                    |

| $\operatorname{SoC}$ | System on Chip                                    |

| SOI                  | Silicon on Isolation                              |

| SW                   | Switch                                            |

| $\mathrm{TG}$        | Transmission Gate                                 |

| VAMS                 | Verilog Analog and Mixed-Signal                   |

| VRM                  | voltage regulator module                          |

| WSN                  | wireless sensor node                              |

|                      |                                                   |

## CONTENTS

| Li            | Preface       i         Abstract       iii         Sammendrag       iv         Acknowledgements       v         Problem description       vi         Abbreviations and Notations       viii         List of Figures       xii |                                                                                                                     |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| $\mathbf{Li}$ | st of                                                                                                                                                                                                                         | Tables xiv                                                                                                          |  |

| 1             | Intr                                                                                                                                                                                                                          | roduction 1                                                                                                         |  |

|               | 1.1                                                                                                                                                                                                                           | State-of-the-Art - Year 2021 Landscape                                                                              |  |

|               |                                                                                                                                                                                                                               | 1.1.1 Figure of Merit                                                                                               |  |

|               | 1.2                                                                                                                                                                                                                           | Goal of Thesis                                                                                                      |  |

|               | 1.3                                                                                                                                                                                                                           | Contributions                                                                                                       |  |

|               | 1.4                                                                                                                                                                                                                           | Thesis outline                                                                                                      |  |

| 0             | <b>T</b> L                                                                                                                                                                                                                    |                                                                                                                     |  |

| <b>2</b>      |                                                                                                                                                                                                                               | eoretical Background 7                                                                                              |  |

|               | $2.1 \\ 2.2$                                                                                                                                                                                                                  | Capacitive DC-DC Converter Structure       8         Converter Characteristics and Fundamentals       8             |  |

|               | 2.2                                                                                                                                                                                                                           |                                                                                                                     |  |

|               |                                                                                                                                                                                                                               | 0                                                                                                                   |  |

|               |                                                                                                                                                                                                                               |                                                                                                                     |  |

|               |                                                                                                                                                                                                                               | 2.2.3       Voltage Gap       9         2.2.4       Efficiency       10                                             |  |

|               |                                                                                                                                                                                                                               | 2.2.4         Enclency                                                                                              |  |

|               | 2.3                                                                                                                                                                                                                           | Introduction to Switched Capacitor Power DC-DC Converters                                                           |  |

|               | 2.0                                                                                                                                                                                                                           | 2.3.1 Basic operation of Switched Capacitor Converters                                                              |  |

|               |                                                                                                                                                                                                                               | 2.3.1 Basic operation of Switched Capacitor Converters                                                              |  |

|               | 2.4                                                                                                                                                                                                                           | Analysis Techniques                                                                                                 |  |

|               | 2.4                                                                                                                                                                                                                           | 2.4.1       Charge Balance Analysis       14                                                                        |  |

|               |                                                                                                                                                                                                                               | 2.4.1       Charge Flow Analysis       14         2.4.2       Charge Flow Analysis       14                         |  |

|               | 2.5                                                                                                                                                                                                                           | 2.4.2       Charge Flow Analysis       14         Output Load Requirements       15                                 |  |

|               | 2.0                                                                                                                                                                                                                           | 2.5.1 The Slow Switching Approximation                                                                              |  |

|               |                                                                                                                                                                                                                               | 2.5.1       The Slow Switching Approximation       10         2.5.2       The Fast Switching Approximation       16 |  |

|               |                                                                                                                                                                                                                               |                                                                                                                     |  |

| Bi | bliog | graphy                                                                                                         | 61        |

|----|-------|----------------------------------------------------------------------------------------------------------------|-----------|

|    | 7.1   | Recommendation for further work                                                                                | 60        |

| 7  | Con   | clusion                                                                                                        | 59        |

|    | 6.3   | Comparison to the current state-of-the-art                                                                     | 57        |

|    | 6.2   | General discussion of the results                                                                              | 57        |

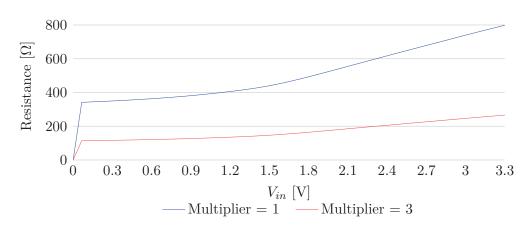

|    |       | 6.1.3 Resistance analysis                                                                                      | 56        |

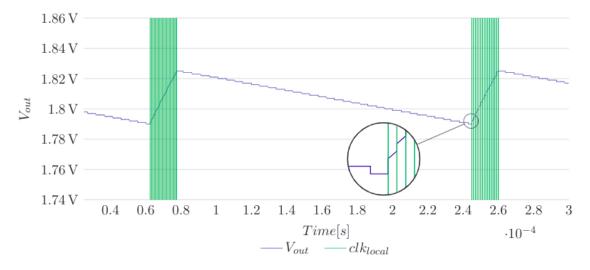

|    |       | 6.1.2 Noise analysis $\ldots$ | 56        |

|    |       | 6.1.1 Consequence of modification                                                                              | 56        |

|    | 6.1   | Evaluation and Analysis of Simulated Data                                                                      | 55        |

| 6  | Dise  | cussion                                                                                                        | 55        |

|    |       |                                                                                                                |           |

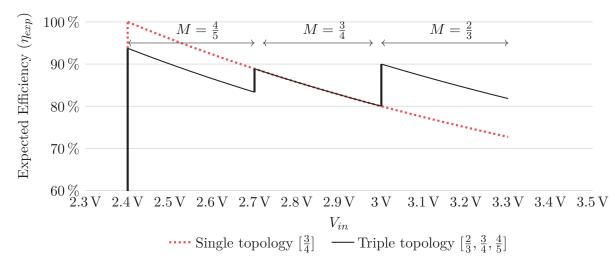

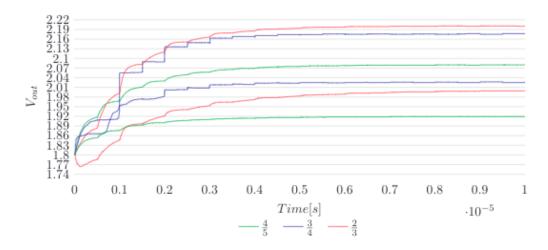

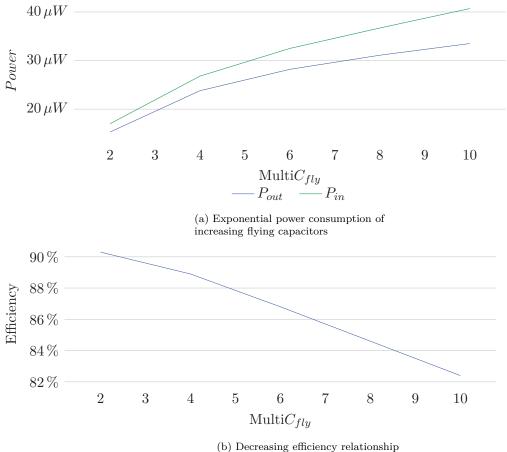

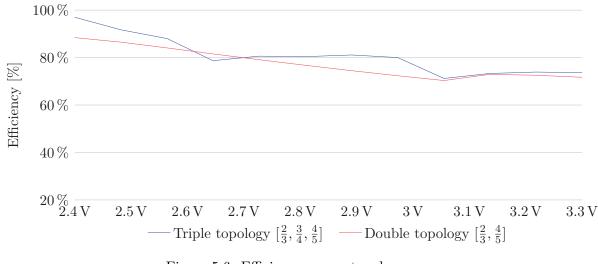

|    | 5.3   | Multi-Topology Efficiency                                                                                      | 53        |

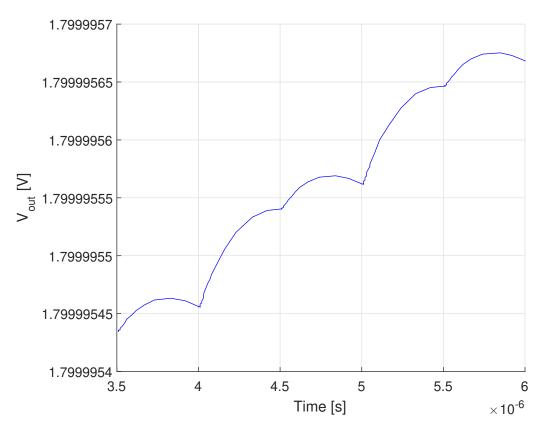

|    | 5.2   | Pulse Frequency Modulation                                                                                     | 52        |

|    |       | 5.1.4 Switching Resistance                                                                                     | 51        |

|    |       | 5.1.3 Capacitor Scaling                                                                                        |           |

|    |       | 5.1.2 Load requirements                                                                                        |           |

|    |       | 5.1.1 Steady-state                                                                                             |           |

|    | 5.1   | Testing methodology                                                                                            | 48        |

| 5  | Res   |                                                                                                                | 47        |

| F  | Б     |                                                                                                                | . –       |

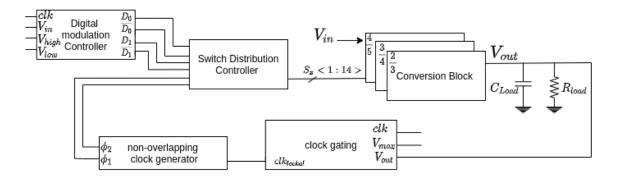

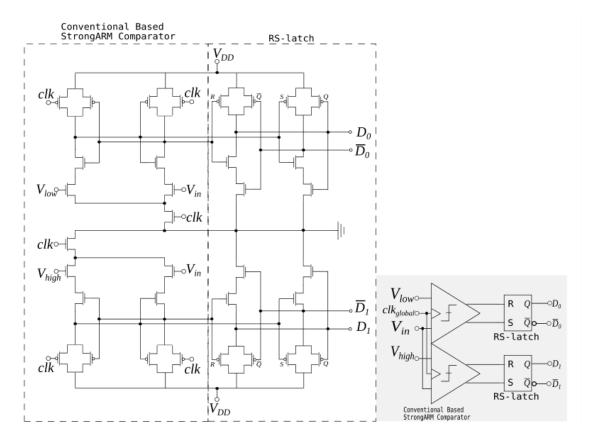

|    | 4.4   | Switch Distribution Controller                                                                                 | 43        |

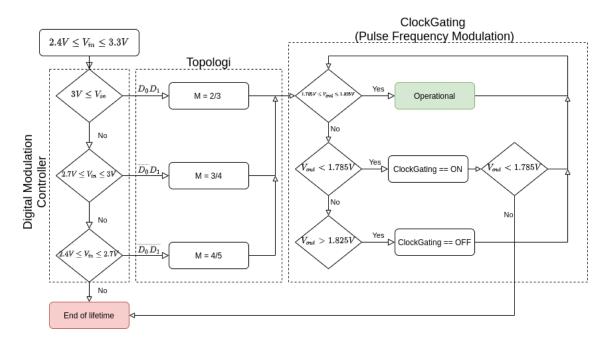

|    | 4.3   | Digital modulation controller                                                                                  | 42        |

|    |       | 4.2.1 Non-overlapping clock                                                                                    | 41        |

|    | 4.2   | Clock Gating                                                                                                   | 40        |

|    | 4.1   | Control Method                                                                                                 | 40        |

| 4  |       | ntrol Block                                                                                                    | 39        |

|    | _     |                                                                                                                |           |

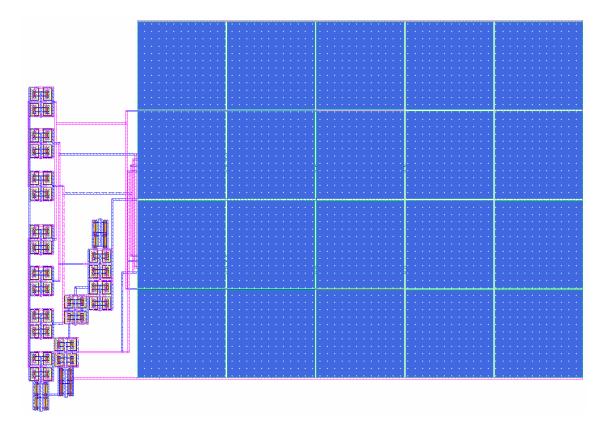

|    | 3.4   | Layout                                                                                                         | 37        |

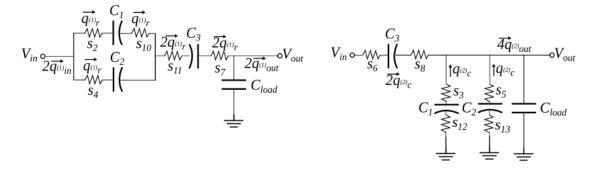

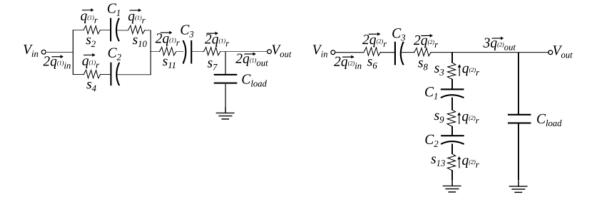

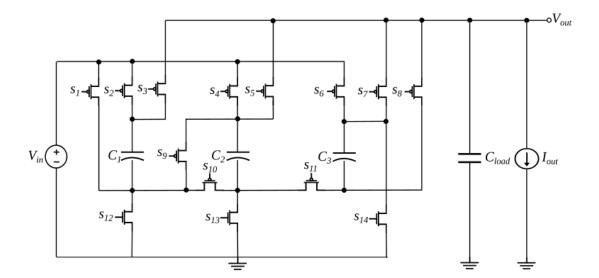

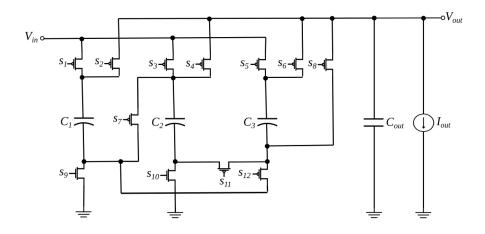

|    |       | 3.3.3 Circuit Diagram                                                                                          | 36        |

|    |       | 3.3.2 Area Estimation                                                                                          | 35        |

|    |       | 3.3.1 Flying Capacitors and Transistor Sizing                                                                  | 35        |

|    | 3.3   | Multi-Topology Converter                                                                                       | 34        |

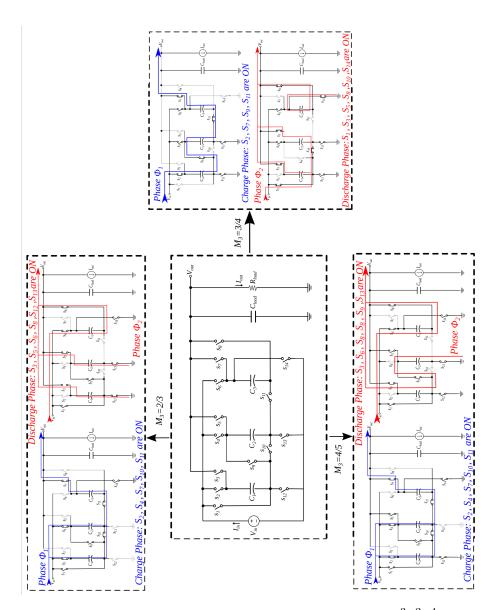

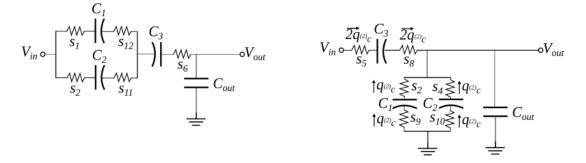

|    |       | 3.2.4 Charge Flow Analysis of the Series-Parallel 4/5 Converter                                                | 33        |

|    |       | 3.2.3 Charge Flow Analysis of the Series-Parallel 2/3 Converter                                                | 32        |

|    |       | 3.2.2 Charge Flow Analysis of the Series-Parallel 3/4 Converter                                                | 30        |

|    |       | 3.2.1 Charge Balance Analysis of the Series-Parallel $3/4$ Converter $\ldots$                                  | 27        |

|    | 3.2   | Topology Synthesis                                                                                             | 27        |

|    | 3.1   | Topology Selection                                                                                             | 26        |

| 3  | Co    | nversion Block                                                                                                 | <b>25</b> |

|    | 2.9   | Converter Control Techniques                                                                                   | 21        |

|    | 0.0   | 2.8.1 Minimize leakage in CMOS technology                                                                      | 21        |

|    | 2.8   | Loss analysis of Switched-Capacitor converters                                                                 | 20        |

|    | 2.7   | Capacitors in Capacitive Converters                                                                            | 18        |

|    | ~ -   | 2.6.1 Switching Properties                                                                                     | 17        |

|    | 2.6   | MOSFET Transistors as Switches in IC Circuits                                                                  |           |

|    |       |                                                                                                                | . –       |

| $\mathbf{A}$ | Input Design Varables             | Α            |

|--------------|-----------------------------------|--------------|

| в            | Two Phases Charging               | В            |

| С            | Double Multi-stage Converter      | С            |

| D            | Logic Gates                       | $\mathbf{E}$ |

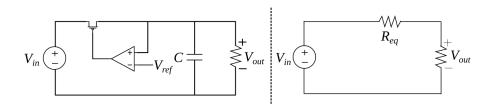

| $\mathbf{E}$ |                                   | F<br>F<br>C  |

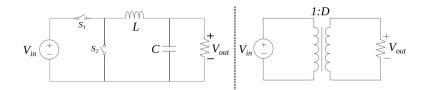

|              | E.0.2 Traditional Buck Converters | G            |

## LIST OF FIGURES

| 1.1          | Technology size comparison between a coin, wireless sensor node and a smartphone                                                                                             | 1               |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

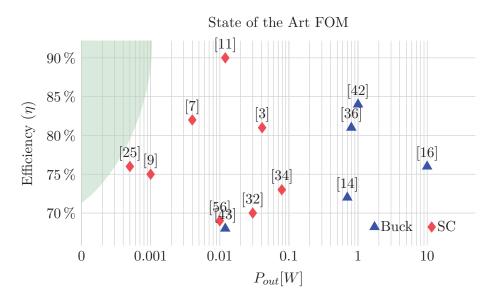

| 1.2          | Quoted efficiency versus power outputted. This thesis's target zone is indi-                                                                                                 | -               |

|              | cated in green                                                                                                                                                               | 4               |

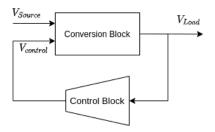

| 2.1          | Graphical representation of a simplified OCVR system                                                                                                                         | 8               |

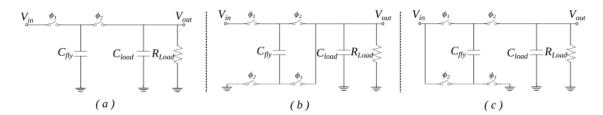

| 2.2          | Three examples of Switched Capacitor Converters: (a) 1-to-1 Topology (b) 2-to-1 Topology (known as the half converter) (c) 1-to-2 Topology                                   | 11              |

| 2.3          | Switched Capacitor converter 1-to-1 Topology                                                                                                                                 | 11              |

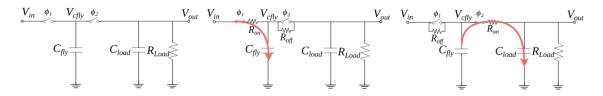

| 2.4          | The venin equivalent SC circuit model for all possible topologies $M_i$ includ-<br>ing an circuit output-resistor combined with load decoupling component                    |                 |

|              |                                                                                                                                                                              | 13              |

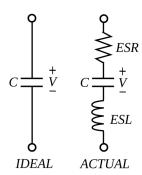

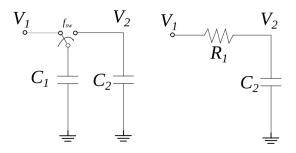

| 2.5          | Theoretical capacitor and its real-world counterpart                                                                                                                         | 19              |

| 2.6          | Charge transfer in Switched-capacitor circuits                                                                                                                               | 19              |

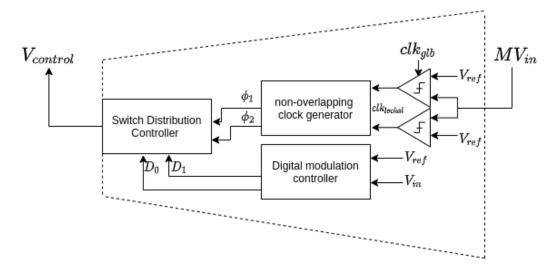

| 2.7          | Visualisation of a multi module control block                                                                                                                                | 21              |

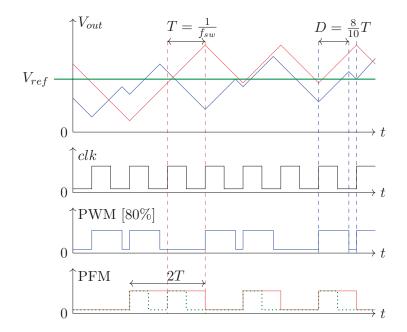

| 2.8          | PWN applying 80% Duty Cycle, versus PFM. Both signals control the output voltage on rising clock                                                                             | 22              |

| 3.1          | Expected efficiency; One topology versus triple topology                                                                                                                     | 27              |

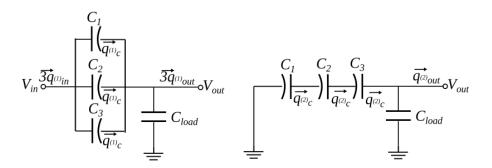

| $3.2 \\ 3.3$ | Two phased single charge input 4-to-3 converter $\ldots \ldots \ldots \ldots \ldots$<br>Circuit representation showcasing the charge capacitor element $a_c^{(1)}$ to the    | 28              |

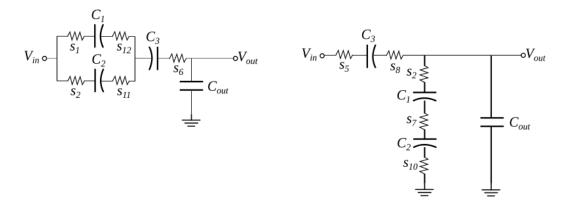

| 3.4          | left when in the charging phase, and $a_c^{(2)}$ to the right in the discharge phase $M_3 = 3/4$ topology utilizing charge input in both phases $\phi_1$ (left) and $\phi_2$ | 30              |

| 0.4          | (right). The switch charge vector $a_r^{(1)}$ and $a_r^{(2)}$ both originates from figure 3.7                                                                                | 21              |

| 3.5          | $M_3 = 2/3 = 4/6$ topology utilizing charge input in both phases $\phi_1$ (left)                                                                                             | 51              |

|              | and $\phi_2$ (right). The switch charge vector $a_r^{(1)}$ and $a_r^{(2)}$ both originates from                                                                              | ~ ~             |

| 9.6          | figure $3.7$                                                                                                                                                                 | 32              |

| 3.6          | $M_3 = 4/5$ topology utilizing charge input in both phases $\phi_1$ (left) and $\phi_2$                                                                                      |                 |

| 97           | (right). The switch charge vector $a_r^{(1)}$ and $a_r^{(2)}$ both originates from figure 3.7                                                                                | 33              |

| $3.7 \\ 3.8$ | Proposed Multi-Topology Converter combining the $\frac{3}{4}, \frac{2}{3}, \frac{4}{5}$ topologies Multi-Topology scheme                                                     | $34 \\ 36$      |

| 3.0          | Common Centroid Layout                                                                                                                                                       | $\frac{30}{37}$ |

| 3.10         | Converter Block Layout                                                                                                                                                       | 37              |

| 4.1          | Block visualisation of the control block as a cascaded connection                                                                                                            | 39              |

| 4.2        | Flow Diagram of the systems control functions                                  | 40 |

|------------|--------------------------------------------------------------------------------|----|

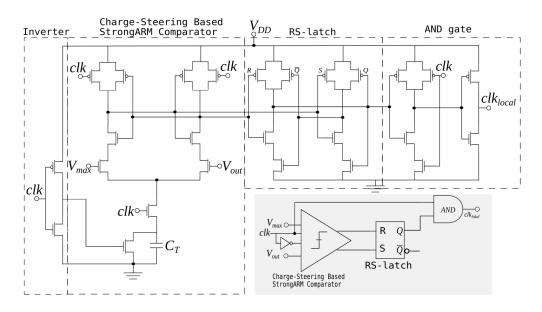

| 4.3        | Transistor level Pulse Frequency Modulation circuit implemented using a        |    |

|            | single hysteretic feedback controller circuit. This is the first ever adapted  |    |

|            | Charge-Steering based strongARM cooperator used in PFM circuit                 | 41 |

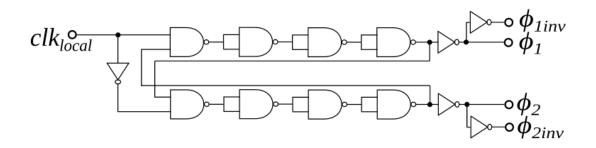

| 4.4        | Non-overlapping clock, implemented with 2x4 logic NAND gates and 2x2           |    |

|            | Inverters                                                                      | 41 |

| 4.5        | Digital modulation using a double feedforward controller                       | 42 |

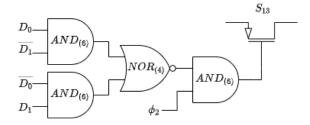

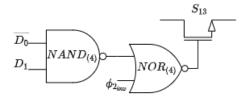

| 4.6        | Logic gate diagram for switch $S_{13}$ based on equation 4.1                   | 43 |

| 4.7        | Logic gate diagram for switch $S_{13}$ based on equation 4.2                   | 43 |

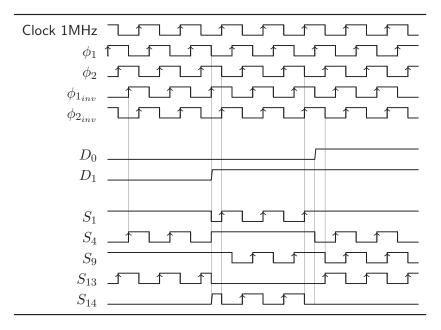

| 4.8        | Timing diagram showcasing a selected five out of fourteen switches. This       |    |

|            | timing diagram illustrates the delay and inversion of both phases $\phi_1$ and |    |

|            | $\phi_2$ . *Figure is not to scale                                             | 44 |

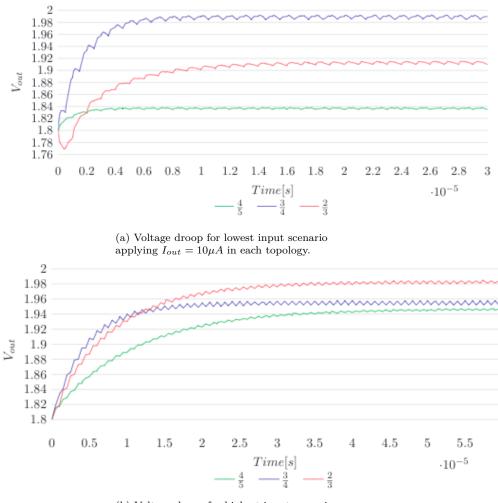

| 5.1        | Maximum and minimum $V_{out}$ values for each topology during steady-state     | 49 |

| 5.2        | Output Voltage Requirements                                                    | 50 |

| 5.3        | Side effects of scaling flying capacitors                                      | 51 |

| 5.4        | On-resistance relationship as a function of input voltage                      | 52 |

| 5.5        | Clock Gating simulation preforming the PFM sequence                            | 52 |

| 5.6        | Efficiency versus topology                                                     | 53 |

|            |                                                                                |    |

| B.1        | $V_{in} = 2.4V$ : Charging in both phases. $T_{sw} = \frac{1}{1MHz} = 1\mu s$  | В  |

| C.1        | Double-Topology Converter                                                      | С  |

| C.2        | 2/3: Left = charge phase, Right = discharge phase                              | D  |

| C.3        | 4/5: Left = charge phase, Right = discharge phase                              | D  |

| 0.0        |                                                                                | 2  |

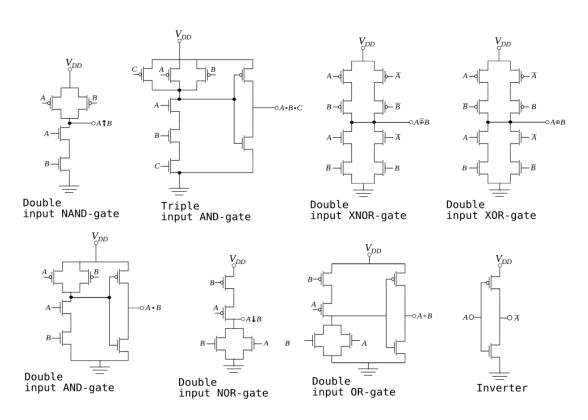

| D.1        | Logic gates                                                                    | Ε  |

| E.1        | DC-DC comparison LR Circuit, illustration obtained from source TokeMyer        | G  |

| E.1<br>E.2 | Traditional Buck converter Circuit                                             | G  |

| 11.Z       |                                                                                | G  |

## LIST OF TABLES

| 2.1          | Available conversion ratios                                                                                                               | 12 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| $3.1 \\ 3.2$ | The ideal 3-stages switching algorithm                                                                                                    |    |

| $4.1 \\ 4.2$ | Topologies and inputs $\dots \dots \dots$ |    |

| $5.1 \\ 5.2$ | Recapitulation of figure 5.1                                                                                                              |    |

| 6.1          | Performance summary and comparison                                                                                                        | 58 |

|              | Fixed Design Variables       Changing Design Variables                                                                                    |    |

|              | The Double-Topology Inputs                                                                                                                |    |

## CHAPTER

## ONE

### INTRODUCTION

Over the past decades, information and communication technology's (ICT) role in society has grown exponentially in conjunction with Moore's [45] and Bell's law [6], leading to an increased demand for computational power. There were about 500-million devices connected to the internet in 2003 [48]. Today, we have reached 35.82-billion devices [49]. With the growing opportunities in "Internet-of-Things" (IoT), an estimation indicates that there will be tens of billions more devices connected by the year 2030 [20]. This development has facilitated an enormous economic potential, and companies are now competing in order to have the best products on the marked. However, a forecast predicts as much as 6000 TWh

annual electricity consumption related to ICT by the year 2035 [41]. This places additional demands on the power comsumption of devices connected to the grid and portable batterydriven devices. In terms of competitiveness, it is in every company's interest to optimize power consumption to meet costumers demand of smaller products with longer life expectancy, as well as becoming more sustainable [37].

Parallel to this development during the last four decades, complex electronic systems went from being entirely built from multiple discrete components mounted on a Printed-Circuit Board (PCB) to circuits in a microscopic scale, also known as system on chip (SoC). SoC is the integration of necessary functional elements in order to implement an electronic system onto a single chip or chipset [10]. This physical reduction in size is illustrated in Figure 1.1, where a modern smart phone is compared to a coinsized battery driven wireless sensor node (WSN).

Figure 1.1: Technology size comparison between a coin, wireless sensor node and a smartphone

The main benefit of integration is the ultra-low-power (ULP) consumption. Therefore, any power-loss is regarded as critical when designing ULP circuits. The reduction in size also leads to some complications such as limited space for passive components or battery cells, which in turn limits the available supply voltages. Additionally, smaller WSNs and SoC means narrower wires handling less current and smaller transistors, which lead to shorter gaps between conductors that can add up to a greater current leakage. Because transistor operation is based on its physical properties, small variations in the manufacturing process can lead to large deviations, which in turn can degrade the performance of an integrated circuit. Another consequence is that the threshold voltage does not scale proportional to supply voltage, and the difference between the supply voltage and transistor threshold voltage is reduced, limiting the switching capabilities of a transistor and at the same time increases parasitic capacitance losses [21]. Additionally, the voltage-source of WSNs are varying as the output voltage of batteries changes over time. A Li-ion battery outputs typically between 2.2V-4.2V [53]. This is also problematic as transistors operating in SoC are sensitive to voltage variations. It is therefore critical to achieve a stable load voltage by conversion in one or more stages. Manipulation of the supply voltage is achieved by inserting a Voltage Regulator Module (VRM) between the regular supply and the loading circuit. Actually, this VRM is nothing more but a well-controlled DC-DC converter.

Digital electronics have come a long way in optimisation and power consumption and contributes to lower power consumption in electronic devices. Analog circuits on the other hand can not compete, becoming a bottleneck in this field [51]. A good deal of energy consumption in electronic devices come from inefficient use of power within the electronic devices via thermal power generation. From a power conversion perspective, one of the main contributors to these power-losses are the voltage regulator modules [8], which are performing the DC-DC conversions in a circuit. These VRMs are however crucial as a stable supply voltage is critical for any microcontroller system. In order to increase the battery efficiency of a WSN, and therefore provide longer operating time, power management units (PMU) such as power management integrated circuits (PMIC) are used to control the power consumption. PMIC are one out of many modules in a microchip system and consists of integrated VRMs, or on-chip voltage regulators (OCVRs). This thesis will investigate how to design an efficient OCVR module for an ultra-low-power WSN which is powered by a battery, or in collaboration with an energy harvester, as this is becoming more common with the advent for IoT technology in recent years.

## 1.1 State-of-the-Art - Year 2021 Landscape

The three main State-of-the-Art OCVR topologies suited for on-chip integration is the linear regulator [27], the traditional <u>Buck converter</u> (inductor-based) [17] and the <u>switched</u> capacitor converter (e.g. [30, 29]). The key differences between these three topologies are the trade-off between the size and performance parameters also known as the figure of merit (FoM). Sometimes a combination of the three can be beneficial. Depending on the application that DC-DC converters is build for, the advantages and disadvantages have to be considered. A more detail explanation of the Line regulator and the Buck converter is given in the appendix E.0.1 and E.0.2 respectively, whereas the switch capacitor power converter will be further investigated in this thesis. A summary of the three alternatives is here given:

**Linear Regulators:** A linear regulator consists of an analog switch that is controlled by an operational amplifier (Opamp) in order to step down an input voltage to the desired output voltage. The Opamp compares the output voltage to a ratio of the input voltage. This small circuit is easy to build and cost-effective. Linear Regulators are efficient when the dropout voltage is small < 100 mV. These circuits also have less noise on the output terminal than compared to switching converters. The main disadvantage for the linear regulator is the challenge of designing the operational amplifier circuit so that it is stable at high switching frequencies.

**Buck Converter:** A Buck converter consists of a transistor and diode, which applies an input voltage to an inductor-capacitor (LC) circuit. The output voltage is then the voltage across the capacitor. The output voltage of the Buck converter is a function of the well-known expression  $V_{out} = DV_{in}$  [19], hence regulation of the output voltage can be done by changing the duty cycle (D). The ideal efficiency of the Buck converter is  $\approx 97 - 99\%$  [12], or approximately 100% when using ideal components. However, the accuracy of the inductor is heavily dependent on the core material as well as the frequency with which the current flows through the coil. This physical limitation is the reason why few Buck converters are implemented in nano-scale microprocessor technology. Traditional Buck converters are preferred in situation where area is not an issue such as on a PCB level where coils can be added outside the PMU.

**Switch Capacitor Converters:** Alternatively there are the switch capacitor converters  $(SCC)^1$  which have high efficiency per area at the cost of circuit complexity. Effectively, SCCs can reach an efficiency >80% [12], which is less than the traditional Buck converter, however similar to the linear regulator while allowing a higher dropout voltage. The efficiency drop is due to the parasitic losses related to the transistor-switching when charging the capacitors that is performing the voltage conversions. Because of these parasitic losses, inductive converters have traditionally been preferred, but it has been shown to be hard to integrate because of the size and accuracy of the inductors. The main advantages of the SC converter is that no inductors are required. The ongoing development of CMOS technology providing high-quality capacitors, and smaller and faster MOSFET transistors for switching, making the SCC more popular among developers. SCCs can also achieve both up- and down-converting topologies. One major drawback of traditional SC DC-DC converters is their ability to provide only a single topology at the time. To overcome this, the state-of-the-art switched capacitor power converters (SCPC) involve the use of recon-

<sup>&</sup>lt;sup>1</sup>First ever published Switched capacitor DC-DC converter was in 1932 [13]

figurable multi-topology stages to supply variable input or output voltages. The main disadvantage is the sheer complexity of the circuit. Higher accuracy demands multiple topologies meaning more switches. Each switch adds another parasitic loss to the system, thus becoming less efficient.

#### 1.1.1 Figure of Merit

The principal figure of merit (FoM) of published OCVR is the efficiency (%) and their power density  $(W/mm^2)$ . This characterizes the integration capability relative to its alternatives. A handful of publications are compared and displayed in figure 1.2 based on their maximum efficiency versus output power.

Figure 1.2: Quoted efficiency versus power outputted. This thesis's target zone is indicated in green

As publications often focus on performance comparison (e.g. power density and efficiency), it is easy to understand their focus in the literature. Therefore, the efficiency of this thesis circuit remains a key parameter. However, the reader has to be aware that the efficiency and power density given in some published works are often achieved in the best topology case [21]. Often people only report the power consumption in their conversion topology, and not together with the control logic<sup>2</sup>, which also goes for this thesis.

Be that as it may, the overview of the main OCVR converters presented in figure 1.2 indicates that the SC circuits are in the lower power ranges. For this reason, the most suitable approach when designing a VRM for a ULP-WSN would be to use a SC circuit. In figure 1.2 the SC can be seen ranging from 68% - 90%, which should be a good indication for the expected maximum efficiency given in this work. Due to the low output power of  $18\mu W$  the estimated target zone is indicated as a green region of the figure.

$<sup>^{2}</sup>$ In [21] they conclude FoM gives a partial view and that this is more often used for convincing reviewers than making a fair comparison.

## 1.2 Goal of Thesis

This thesis deals with the importance and the technological requirements imposed on the design of DC-DC converters. Moreover, this thesis will investigate how to design an efficient OCVR module for an ultra-low-power WSN which is powered by a battery, or in collaboration with an energy harvester, as this is becoming more common with the advent for IoT technology in recent years. The aim of this work is to present a complete analysis and design methodology for a SC converter which is being used for specific practical application.

## **1.3** Contributions

This thesis presents an simplified version of what is a very complex topic. One of the main contributions is that this thesis will help to an better understanding of the applicable theory for those who follow, as there are few who have published how the actual circuits have come about. The author has further contributed by:

- deriving a mathematical term for the  $\frac{3}{4}$  topology when utilizing three charge transfer capacitors using Charge Balance Analysis

- expending the  $\frac{3}{4}$  topology from single to double charge input when utilizing three charge transfer capacitors by applying Charge Flow Analysis, which has never been done before

- ▶ introducing the first ever Low-Power High-Speed Charge-Steering Based StrongARM Comparator [1] in an SC circuits.

- ▶ designing a triple combination topology<sup>3</sup> using the  $\frac{2}{3}$ ,  $\frac{3}{4}$  and  $\frac{4}{5}$  fractions which all utilizes three charge transfer capacitors

- ▶ implementing a set of optimised custom logic gates for used in the low-power control circuit

- ▶ applying the entire concept in 28nm technology

## 1.4 Thesis outline

Instead of directly presenting the final design and layout in this thesis, the key learnings of each design step are presented. It is therefore the hope that the reader can follow the logic of the design decisions being made along the way, ultimately leading to the finale result. Covering all the relevant background material would also not be feasible in this thesis, so the emphasis has been put on theory that is more or less directly used in the subsequent chapters. Explicit citations are given through the chapters when necessary. The outline of the thesis is as follows:

**Chapter 2 - Background theory;** provides the background theory that is necessary in order to understand the work done in this thesis. Mathematical foundations of the switched capacitive conversion theory as well as an introduction to basic CMOS implementation and capacitor properties is given her.

<sup>&</sup>lt;sup>3</sup>topology: "the way in which constituent parts are interrelated or arranged."

**Chapter 3 - Conversion Block;** will look into the method and implementation of the chosen SC topologies regarded to limitations of the given parameters. The given topologies will be explained using matrices based on Charge Flow Analysis in contrast to the Charge Transfer Analysis in order to account for the choices made.

**Chapter 4 - Control Block;** will look into the method and implementation of the chosen control circuity. These extra circuits are implemented in order to minimise the overall power consumption.

Chapter 5 - Results; presents simulation data of the finished model

**Chapter 6 - Discussion;** elaborates on the findings in order to confirm or disclaim the choices made in Chapter 3 and 4. Performance of various state-of-the-art publications is compared to the final result of this thesis in Section 6.3.

**Chapter 7 - Conclusion;** Finally, conclusions are drawn in chapter 7. Lastly, future work and possible modification will be discussed in section 7.1.

## CHAPTER TWO

## THEORETICAL BACKGROUND

The content of this chapter aims to address the necessary background theory of which the main design for this master thesis is based upon. This chapter may resemble some of the work done in this thesis' pre-project [5] written in the previous year. This is necessary in order to build a complete theoretical foundation for this thesis. Fundamental equation within capacitor and transistor theorem will be provided as it is the foundation in SC mechanics. On the other hand, it is not feasible to cover all areas of the SC subject. Therefore, some subject such as energy storage, device cost, optimized capacitor values, optimized switch conductance, etc. is not addressed in this thesis. If necessary, more of the classical switched capacitor theory found in textbooks, such as the half-converter<sup>1</sup>, is presented in this thesis pre-project. Other important theoretical remarks are further given where it is considered necessary throughout this thesis.

<sup>&</sup>lt;sup>1</sup>Multistage converters are a rarity, hence the series-parallel half-converter are used in most of the publications. Common voltages such as 48V, 24V, 12V can be achieved using half-converters.

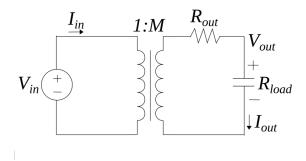

## 2.1 Capacitive DC-DC Converter Structure

Capacitive DC-DC converters consists of two main structures: A Conversion Block and a Control Block. The Conversion Bock is responsible for preforming the voltage conversion between the DC input voltage and the DC output voltage. The Control Block manipulates the behavior of the Conversion Block and can preform tasks such as manipulating duty cycle, turning on or off switching-networks, or just shutting of the Conversion Block entirely in order to save energy. A simplified converter structure is illustrated in figure 2.1 as a point of reference.

Figure 2.1: Graphical representation of a simplified OCVR system

## 2.2 Converter Characteristics and Fundamentals

To give a solid understanding of the switched capacitive conversion theory used in the Conversion Blocks, this section introduces the fundamental converter characteristics of DC-DC converters in general. The following sub-chapters introduces equations provided from textbooks such as [4, 8], which will give the reader some relevant background in the fundamental theorems and building blocks which the DC-DC conversion principles is build up on, thus laying the mathematical foundations for the chosen SC circuit presented later on in Chapter 3.

#### 2.2.1 Voltage Conversion

The main goal of the OCVR conversion block is to transform the output voltage to a desired ratio of the input voltage. This characteristic is often represented in textbooks as the Voltage-Conversion-Ratio (VCR):

$$VCR = \frac{V_{out}}{V_{in}} \tag{2.1}$$

The VCR equals a ratio between an output voltage (load) in relation to a input voltage (source) and is often refereed to as the voltage gain of a VRM. In addition to being featured in VRM, this term is often used in other parts of electronics such as in amplifiers. When the VCR is considered a constant value and not varying it's called an ideal voltage conversion ratio (iVCR). For simplicity this report will from here on represent the iVCR as a fraction named M. This simplification is done in order to ease the readability of further equation given in this thesis<sup>2</sup>. Based on this, the output voltage can be represented as:

<sup>&</sup>lt;sup>2</sup>The representation M (Mode) is not uncommon in publications related to SCC.

$$V_{out} = M V_{in} \tag{2.2}$$

As M is constant the output voltage will change linearly with the input voltage. If M is smaller than one, it is known as a down- or Buck converter, when larger then it is called a up-, or Boost converter. Equation 2.2 represents the DC value of the output voltage which does not take into account any noise factor, meaning that any noise from the input will also be amplified with a factor M. If a varying current flows through a series and parallel-connected RLC-ladder (Resitor, Inductor and Capacitor), the DC voltage of the source is turned into a voltage that exists of a large DC component and an AC signal. This AC signal is called the input noise. A more accurate representation of the output voltage is to say it is an constant DC voltage as an average between upper and a lower limit of the output voltage, also refereed to as the DC offset.

$$V_{out} = |V_{DC} \pm V_{AC}| \tag{2.3}$$

#### 2.2.2 Noise Factor

In the case of a switching capacitor circuit the most prominent noise factor would typical be ripple. Ripple is a byproduct and will appear on the output terminal due to the nature of switching while performing the charge transfer between the capacitors [31]:

$$V_{ripple} = \pm V_{AC} = \frac{I_{out}}{C_{load}} \cdot \frac{T}{2} = \frac{I_{out}}{2f_{sw}C_{load}}$$

(2.4)

where T is the switching period, and  $C_{load}$  is the SCC buffer capacitor. In a situation where the output load is a digital circuit and its main function is to manipulate multiple transistor, such as in a MCU or a FPGA, then the noise outputted by the DC-DC converter can unintentionally influence the threshold voltage by introducing errors in data converters.

#### 2.2.3 Voltage Gap

Voltage gap, or drop out voltage, points out the mismatch between the input voltage and the maximum supply voltages in electronic circuits:

$$\Delta V = V_{in} - V_{out} \tag{2.5}$$

$$= V_{in} - M V_{in} \tag{2.6}$$

In fact, equation 2.6 gives rise to the sizing of the SC charge transfer capacitor.  $\Delta V$  is also associated with the capacitors charge-sharing losses [21]. If the output voltage deviates from this desired level, the efficiency of the SC converter drops. Also, if the variation is large, the power loss becomes unacceptably high due to charge redistribution [54].

#### 2.2.4 Efficiency

The converter's efficiency is calculated through the output power and its losses during operation. Efficiency  $\eta$  is given as the ratio of the converter's output power in relation to the converter's input power, as shown in equation 2.7. The converter's efficiency is one of the most important characteristics of a DC-DC converter. Because  $P_{out}$  is so small when working with ULP converters,  $\eta$  is very dependent on the size of  $P_{loss}$ . This means that there is little margin before  $P_{loss}$  will dominate. In an ideal case there are no power losses, however there are many sources to losses witch will be addressed in the forthcoming chapters.

$$\eta = \frac{P_{out}}{P_{in}} = \frac{P_{out}}{P_{loss} + P_{out}}$$

(2.7)

#### 2.2.5 Power Density

Power Density  $\rho$  indicates how much power the converter can preform/deliver to the output with respect to its occupied area:

$$\rho = \frac{P_{out}}{A} \tag{2.8}$$

Since the system must be implementable, the overall area is also important. Therefore, the best trade-off between size and performance should be found. This is why Power Density is known as one of the key performance metrics.

## 2.3 Introduction to Switched Capacitor Power DC-DC Converters

The essence of the switched-capacitor in ICs is to mimic the function of a resistor by using capacitors and analog switches. In conventional analog circuits, a ratio of resistances is used to set the transfer functions of amplifiers. The frequency responses of active filters and signal generators are determined using the values of the RC product [50].

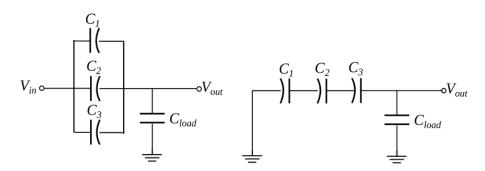

The intention of SCPCs, however, is not to control amplifiers, but rather to affect the output voltage across a load by acting as an adjustable resistance in accordance with the input voltage. The voltage conversion ratios in SCPC can be generated according to the configuration of its switches and capacitors. By turning switches on and off consecutively, a configuration of the charge transfer capacitors changes. A consequence of this is that the output voltage can be equal, higher, lower or opposite in polarity compared to the input voltage. Figure 2.2 illustrates how three different topologies with three different conversion ratios can be implemented when using a single fly-capacitor in combination with two sets of switches to control the output voltage.

Figure 2.2: Three examples of Switched Capacitor Converters: (a) 1-to-1 Topology (b) 2-to-1 Topology (known as the half converter) (c) 1-to-2 Topology

SCPC circuits consist of two types of capacitors, one preforms the charge transfer  $(C_{fly})$ , while the other influences the startup behavior of the load  $(C_{load})$ . The ideal conversion ratio M is determined by the numbers of fly capacitors used in the circuit as well as the frequency governing the parasitic on-state resistance of the switches. The ideal efficiency of an SCC is, at it's maximum, when ratio between the output voltage and the input voltage get close to the ideal conversion ratio:

$$\eta_{ideal.SC} = \frac{V_{out}}{M V_{in}} \tag{2.9}$$

#### 2.3.1 Basic operation of Switched Capacitor Converters

Figure 2.2 illustrates a system in two stages of operation for a 1-to-1 SCC. Here, the two switches are operated by the non-overlapping clock signals,  $\phi_1$  and  $\phi_2$ .

Figure 2.3: Switched Capacitor converter 1-to-1 Topology

When each set of switches are moving charge from one capacitor to another at typically 50% duty cycle<sup>3</sup>, then the system can be seen as two circuits, a charging and discharge circuit. When charge propagates through the circuit, the voltages across each capacitor is affected. The voltage across  $C_{fly}$  is given in equation 2.10:

$$V_{C_{fly}} = V_{out} + (V_{in} - V_{out})e^{-t/\sum (R_{out}C_{fly})}$$

(2.10)

Where the initial voltage is  $V_{in}$  at time zero, and the voltage the capacitor is charging towards is  $V_{out}$ .  $R_{out}$  represents the total amount of resistance across both the flying capacitors and the switches that is utilized by the converter, which will be derived later in equation 2.20. This resistor is the fundamental foundation in switched-capacitor circuits.

<sup>&</sup>lt;sup>3</sup>SCC operating at duty cycles below 50% is possible, effecting the  $R_{out}$  resistance, which is similar to using PWM [30]

This means that this system is effectively working as a controllable voltage divider circuit. In the case of the 1-to-1 SCC, the output would propagate towards the input value as shown:

$$V_{out_T} = \sum_{t=0}^{T} \frac{C_{fly} V_{C_{fly|_t}} + C_{load} V_{out|_t}}{C_{fly} + C_{load}}$$

(2.11)

When in steady state, the load capacitor  $C_{load}$  is fully charged working as a voltage source. In practise, the load capacitor have to be greater than the sum of flying capacitors, however it should be much larger, hence eliminating the ripple at the output terminal[3].

#### 2.3.2 Switched Capacitor Topologies

A math-based theory of possible conversion ratio M ranging from i = 1 to i = 4 flyingcapacitors when using two clock phases <sup>4</sup> is developed and proposed in literature such as [39, 38, 22]<sup>5</sup>, and are here summed up and presented in Table 2.1. According to [22], this table shows which values of M that can be realized (independent on the nm-technology used), but points out that the systematic synthesis of each of these values had so far (2017) not been addressed. One simple reason for this could be that the inductor based technology have been superior, and that there have not yet been a good enough reason to to apply anything else. As we now know, this might change if to adapt to the new demands of low-power miniature electronics. There are however some drawbacks when considering the available conversion ratios, mainly the fact that they can only approach the true ratio when no load i present, e.g. [21, 22, 46, 55]

Table 2.1: Available conversion ratios

| Numbers of Cfly $(i)$ | Available conversion ratios $(M_i)$                                                                                                                                                                                                                                                   |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                     | $\frac{1}{2}, 1, 2$                                                                                                                                                                                                                                                                   |

| 2                     | $\frac{1}{3}, \frac{1}{2}, \frac{2}{3}, 1, \frac{3}{2}, 2, 3$                                                                                                                                                                                                                         |

| 3                     | $\frac{1}{5}, \frac{1}{4}, \frac{1}{3}, \frac{2}{5}, \frac{1}{2}, \frac{3}{5}, \frac{2}{3}, \frac{3}{4}, \frac{4}{5}, 1, \frac{5}{4}, \frac{4}{3}, \frac{3}{2}, \frac{5}{3}, 2, \frac{5}{2}, 3, 4, 5$                                                                                 |

| 4                     | $\frac{1}{8}, \frac{1}{7}, \frac{1}{6}, \frac{1}{5}, \frac{1}{4}, \frac{2}{7}, \frac{1}{3}, \frac{3}{8}, \frac{2}{5}, \frac{3}{7}, \frac{1}{2}, \frac{4}{7}, \frac{3}{5}, \frac{5}{8}, \frac{2}{3}, \frac{5}{7}, \frac{3}{4}, \frac{4}{5}, \frac{5}{6}, \frac{6}{7}, \frac{7}{8}, 1,$ |

|                       | $\left[\frac{8}{7}, \frac{7}{6}, \frac{6}{5}, \frac{5}{4}, \frac{7}{5}, \frac{3}{2}, \frac{8}{5}, \frac{5}{3}, \frac{7}{4}, 2, \frac{7}{3}, \frac{5}{2}, \frac{8}{3}, 3, \frac{7}{2}, 4, 5, 6, 7, 8\right]$                                                                           |

From Table 2.1 we can see that for each extra fly capacitor added, the complexity (multiple switches) and output accuracy (ratios) increases. A single fly capacitor system will have the fewest switches, hence be more power efficient on it's own. However, increasing fly capacitors and combining multiple topologies will increases the average overall efficiency as pointed out in [22]. It is possible to achieve these ratios by adding them, for example adding a half-converter (2-to-1) to another half-converter to get a quarter-converter (4-to-1). There are also many different design techniques in order to achieve these conversion ratios, such as the Ladder, Dickson, Fibonacci, Series-Parallel and Doubler architecture, which is addressed in sources such as [47]. There will always be a trade-of when choosing

<sup>&</sup>lt;sup>4</sup>An expansion of Table 2.1 is possible if to use multi-clock-phase topologies as shown in [22]

$<sup>{}^{5}</sup>$ In 2015 a published paper [29] criticise two of the mentioned articles saying the approach in these works was mathematical and not circuit-design oriented, quote; "The proof provided in [39] and [38] was non-constructive, i.e., it was not possible to directly synthesize the SCPC topologies based on this proof"

these ratios, as higher complexity will take more time to design and test, and also increase the consumed area on the chip. However, it will increase the accuracy and thus becoming more power efficient. Moreover, increasing i capacitors indicates a higher amount of switches in the circuit, effecting the ripple as well as add to the power leakage, thereby becoming less efficient. Even though fractional converters exist for a whole range of conversion ratios, in practice the number of capacitors is kept below four since the output impedance increases fast in function of the number of capacitors and switches used [8]. Capacitors is also the dominant area consumer in CMOS technology, which makes it even more reasonable to minimise the use. How to determine the different topologies will be explained in section 2.4 analysis of SCC.

### 2.4 Analysis Techniques

Analysis techniques are used to determine the ideal convection ratios M for more advanced SCPCs. Because SCPCs are complex time-varying circuits, as pointed out in section 2.3.1, they have to be simplified using a set of static analysing techniques. This is useful as differential equations in power electronic circuits are very time consuming to solve [3]. There are multiple<sup>6</sup> analyses techniques developed within the field of SCPC. Analysis techniques such as Charge Balance Analysis, Charge Flow Analysis or Branch Analysis are the most commonly used methods, leading to different performance tradeoffs. In this thesis, we will only look at two of the most common ones, Charge Balance and Charge Flow techniques.

A steady state behavior of a switched capacitor power converter can be represented as an ideal transformer with a series output impedance meaning one can ignoring frequency dependent parasitic losses [46]. Based on Kirchhoff's laws of conservation, KVL and KCL, it is possible to simplify these circuits as a modeled Thevenin equivalent circuit, as seen in figure 2.4.

Figure 2.4: The venin equivalent SC circuit model for all possible topologies  $M_i$  including an circuit output-resistor combined with load decoupling component

The SCC is at its simplest form when in steady state, meaning the load current equals zero. When no load current is applied,  $I_{out} = 0$ , then the voltage drop across  $R_{out}$  is zero, meaning the total voltage drop across the transformer model must equal  $C_{load}R_{load} \cdot V_{in}$ .

<sup>&</sup>lt;sup>6</sup>Even by 2021 there are not one <u>exact method</u> or theory on how to approach SCC synthesize, making some analysis challenging to apply for SC converters with conversion ratios other then  $M_{i=1}$  [3]

#### 2.4.1 Charge Balance Analysis

The charge balance analysis [55] is a model based on energy conservation when in steady state, and applies KVL and KCL in each connected node between the input terminal and the output terminal in both the charging and discharging circuits. When performing charge balance analysis, [55] states in his work that the capacitor and switch system should be treated as an energy transfer device. Charge balance analysis assumes an absolute amount of charge (Q) in the circuit at a set time. This results in the following charge conservation equation, assuming that energy is conserved with 100% power efficiency; input power equals output power:

$$V_{in}Q_{in} = V_{out}Q_{out} \tag{2.12}$$

rearranging equation 3.1 yields to:

$$\frac{V_{out}}{V_{in}} = \frac{Q_{in}}{Q_{out}} \tag{2.13}$$

Where  $Q_{in}$  refers to the total amount of charge in the charging circuit, and  $Q_{out}$  to the total charge in the discharging circuits. When charge balance analysis is applied to circuits where the number of capacitor i in the circuit is > 1, then the sum of the charge in the capacitors ( $C_{eq}$ ) in parallel can simply be added. However, as pointed out in [55] the capacitors in series when fully charged will not equal  $\frac{C_1C_2}{C_1+C_2}$  but  $\frac{2C_1C_2}{C_1+C_2}$ . The next step is then to simplify equation 2.13 in terms of  $V_{in}$  and  $V_{out}$  by applying KCL (equation 2.30) to solve for any unknown  $V_{C_{fly}}$  in the system.

#### 2.4.2 Charge Flow Analysis

Charge flow analysis [46, 39], which treats the capacitor and switch system as a resistor, demonstrates an intuitive method to determine the VCR ratio of any chosen topology of the capacitive converters mentioned in Table 2.1, assuming steady state conditions. It differs from charge balance analysis as it concerns the change in charge (q) of the components. In this method the VCR  $M_i$  can be derived using KVL and KCL assuming all charge into a node equals to zero:

$$M_{i} = iVCR = \frac{q_{in}}{q_{out}} = \frac{q_{in}^{(1)} + \dots + q_{in}^{(n)}}{q_{out}^{(1)} + \dots + q_{out}^{(n)}}$$

(2.14)

This approach plays an important role in the modeling and design choices presented in this work. The Charge Flow mathematical framework was first introduced in [39] denoting the charge multiplier vector  $a^n$  as a mean of exploring performance limits of switched-capacitor converters. The charge vector  $a^n$  can be split into two types of vectors, the charge capacitor element  $a_c^n$  and the charge resistance element  $a_r^n$ . These vectors play an important role when determining the systems power loss, hence effecting the efficiency  $\eta$ . The general notation of the capacitor element  $a_c^n$  is given in equation 2.15 and can be applied for any n number of phases:

$$a_{c}^{n} = \left[\frac{q_{out}^{n}}{q_{out}}, \frac{q_{c,1}^{n}}{q_{out}}, \dots, \frac{q_{c,i}^{n}}{q_{out}}, \frac{q_{in}^{n}}{q_{out}}\right] = \left[a_{out}^{n}, a_{c,1}^{n}, a_{in}^{n}\right]$$

(2.15)

The charge resistance element  $a_r^n$  can only be deduced by analyzing the circuit, which will be demonstrated later.

Equation 2.15 can be used to determine the topology. Equation 2.15 is valid when:

$$\sum_{n=1}^{N} a_{out}^{n} = a_{out}^{(1)} + \dots + a_{out}^{(n)} = 1$$

(2.16)

### 2.5 Output Load Requirements

A realistic output voltage must take into account the losses related to the non-ideal impedance component  $R_{out}^7$  when charging and discharging a circuit capacitor. The actual output voltage differs from the unloaded ideal output voltage given in equation 2.2 by adding an equivalent non-zero output impedance  $\gamma$  in the equation [8]. The actual output voltage can then be represented as:

$$V_{out|real} = \gamma M V_{in} \tag{2.17}$$

where the equivalent non-zero output impedance  $\gamma$  corresponds to the resistive division between the load resistance and the output impedance, which is depicted in figure 2.4, and quantified as:

$$\gamma = \frac{R_{load}}{R_{load} + R_{out}} \tag{2.18}$$

$R_{load}$  in equation 2.18 is the real component (however frequency dependent) of the  $C_{load}$  impedance, while  $R_{out}$  is the real component of the SC circuit impedance of both switches and flying capacitors. From equation 2.18 we can see that the smaller  $R_{load}$  gets, the more  $R_{out}$  dominates. Meaning that the impedance  $\gamma$  shrinks, where according to equation 2.17 the true output voltage falls. Thus, a voltage drop will occur at the output node as the output impedance  $R_{out}$  increases:

$$V_{loss|real} = M V_{in} - \gamma M V_{in} \tag{2.19}$$

A consequence of this is that some level of margin has to be considered regarding the input voltage range. For example, operating with an input voltage of 3V with a VCR of 3/5 to ensure an output voltage of 1.8V is not realistic since this will require a 0V voltage drop over the output impedance  $R_{out}$ . In this particular example, the approach will not be ideal, and the system will struggled to output the minimum required voltage. It is

<sup>&</sup>lt;sup>7</sup>For the sake of simplicity it is chosen to call the output impedance  $R_{out}$  and not  $Z_{out}$  as the following content only focus on the real component  $\mathbb{R}$  and not the complex  $\mathbb{C}$  of the capacitors impedance (the same goes for  $\gamma$ ).

therefore good practice to implement VCRs which accounts for a minimum margin, such as in this example, where a 200 mV voltage drop over the output impedance  $\gamma$  is sufficient.

The output impedance can been derived from Tellegen's Theorem [18] as a sum of two impedance components, The Slow Switching Limit (SSL) and the Fast Switching Limit (FSL) :

$$R_{out} = \sqrt{R_{SSL}^2 + R_{FSL}^2} \tag{2.20}$$

which should be approximately equal the conventional method:

$$R_{out} = \frac{MV_{in} - \gamma MV_{in}}{I_{out}} \tag{2.21}$$

#### 2.5.1 The Slow Switching Approximation

The SSL as seen from a charge flow analysis perspective when applying two-clock phases, assuming 50% duty cycle when operating with ideal switches, allows currents in the circuit to be modeled as a charge transfer. SSL is therefore expressed as:

$$R_{SSL} = \sum_{i=1}^{j} \frac{(a_{c,i})^2}{C_i f_{sw}} = \frac{1}{C_{tot} f_{sw}} \sum_{i=1}^{j} |a_{c,i}|^2$$

(2.22)

where j equals the total number of flying capacitors that is preforming the charge transfer at a fixed frequency  $f_{sw}$ . The sum of the capacitors multiplying vectors  $a_c$  squared is known to be the dominating factor when analysing the SSL. The SSL related losses can be reduced by either increasing the frequency or the flying capacitors.

#### 2.5.2 The Fast Switching Approximation

When assuming the same conditions mentioned for the SSL, the FSL can be derived as:

$$R_{FSL} = 2\sum_{k=1}^{K} R_{on,k} (a_{r,k})^2$$

(2.23)