Markus Rud

# Power and energy consumption in hardware implemented SPI master devices

Master's thesis in Electronics Systems Design and Innovation Supervisor: Snorre Aunet Co-supervisor: Øystein Moldsvor June 2021

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Markus Rud

# Power and energy consumption in hardware implemented SPI master devices

Master's thesis in Electronics Systems Design and Innovation Supervisor: Snorre Aunet Co-supervisor: Øystein Moldsvor June 2021

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

## Abstract

This thesis presents an analysis of two different VHDL designs of the SPI master device implemented onto a model of a FPGA. The analysis is focused at power and energy consumption in the devices compared with provided functionality. The two devices differ in their design strategy where one is created as a simple design where only the required logic to conduct a SPI transmission are implemented. The second one is a more complex design where it is possible to adjust transmission parameters such as setup and hold time after implementation and a more complex interface to the controlling logic which controls the SPI masters. The complex implementation also implement two FIFO registers to store multiple messages during transmission and reception.

The conducted analysis is based upon different tests in order to give an understanding of which elements of a SPI master who impact the energy consumption in the device. These tests look into the impact of operating frequency, communication frequency, operation mode and alternation to the utilized logic. The designs are implemented onto a model of a FPGA using the development tool Vivado. The two designs are also power optimized using the build in power optimizer in Vivado.

The results from the analysis show that when implementing a SPI master, it is necessary with a trade of between functionality and energy consumption. The different implementations are analysed over a frequency span of 1 MHz to 15 MHz where it is seen that the complex master requires 27.2% more energy than the simple master on average. It is therefore seen that a higher complexity in the design requires more energy. The complex master utilize more than twice as much logic, but not twice as much energy, so the energy cost of added functionality is therefore heavily dependent on the switching activity in the added logic. The results also show that it is preferable to operate the tested SPI masters at the highest frequency possible within the tested frequencies since this gives the lowest energy consumption. This result is to some extend limited by the implementation method as the implementation of the SPI master onto a FPGA removes some potential benefits of operating the design at a low frequency such as smaller transistor sizes and lower operating voltage. It is also seen that the two SPI designs react relatively similar to adjustments to transmission parameters such as communication frequency and operating mode since their percentage energy difference with adjustments are approximately similar for both designs.

The analysis consist of some limitations. The SPI masters are analysed as standalone devices not connected to any controlling device which limits the energy analysis due to missing timing delays. The SPI masters are also relatively small designs so when implemented on a large FPGA compared to the designs, a large static power overhead is added which can hide the actual static power consumption for the designs themselves.

## Sammendrag

Denne oppgaven tar for seg en analyse av to ulike VHDL-design av master enheten på en SPI-buss implementert på en FPGA modell. Analysen er i hovedsak fokusert rundt effekt og energi forbruk sammenliknet med enhetenes funksjonalitet. De to enhetene er designet basert på ulike strategier hvor den første er designet som et simpelt design hvor kun den nødvendige logikken for å gjennomføre en SPI-overføring er implementert. Det andre designet er et mer komplekst design hvor det er mulig å modifisere overførings parametere etter implementasjon samt et mer komplekst grensesnitt inn mot kontrollogikken som styrer SPI masterne. Den komplekse implementasjonen implementerer også to FIFO registre for å mellomlagre meldinger under overføring og mottagelse.

Analysen er basert på ulike tester som er gjennomført med formål om å skape en forståelse av hvilke elementer i en SPI master som påvirker energiforbruket. Disse testene tar for seg påvirkningen fra driftsfrekvens, kommunikasjonsfrekvens, driftsmodus og modifikasjon av implementert logikk. Disse designene er implementert på en modell av en FPGA ved bruk av verktøyet Vivado. Designene er også optimalisert med tanke på effektforbruk ved bruk av den innebygde effekt-optimalisereren i Vivado.

Resultatene viser at ved implementasjon av en SPI master, er det nødvendig å vurdere behovet for funksjonalitet opp mot energi forbruk. De ulike implementasjonene er analysert over et frekvensområde fra 1 MHz til 15 MHz hvor man kan se at den komplekse masteren trenger gjennomsnittlig 27.2% mer energi enn den simple masteren. Dette viser at en høyere kompleksitet gir et høyere energiforbruk. Den komplekse masteren trenger mer enn dobbelt så mye logikk, men ikke dobbelt så mye energi. Dette viser at energikostnaden er svært avhengig av svitsje-aktiviteten i den ekstra logikken. Resultatene viser også at det er gunstig å drifte de to SPI-masterne på høyest mulig frekvens innenfor det testede frekvensområdet siden dette gir det laveste energiforbruket. Dette resultatet er til en viss grad begrenset av hvordan designene er implementert siden man ved å benytte en FPGA mister noen fordeler ved lav driftsfrekvens som mindre transistorstørrelser og lavere driftsspenning. De to designene responderer også relativt likt til modifikasjoner i overføringsparametere som ulik kommunikasjon frekvens og driftsmodus siden den prosentvise endringen etter modifikasjon er tilnærmet lik for begge designene.

Analysen består av enkelte begrensninger. SPI masterne er analysert som selvstendige enheter som ikke er koblet til en kontrollenhet. Dette begrenser energianalysen på grunn av manglende tidsforsinkelser i systemet. SPI masterne er også relativt små design sammenliknet med størrelsen på FPGAen så et stort statisk effektforbruk blir lagt til og kan skjule det faktiske statiske forbruket i selve designene.

## Acknowledgement

This master thesis is written as a finalization of the 5 year master degree program Electronics Systems Design and Innovation at the Norwegian University of Science and Technology (NTNU) in Trondheim. It has been 5 very interesting years where I have learned and experienced a lot both on and off campus.

I would like to thank my supervisors professor Snorre Aunet from NTNU and Øystein Moldsvor from Disruptive Technologies for their guidance throughout this project. They have helped me figuring out how to proceed with the research and pointed out when results and methods have seem weird.

Trondheim June 18, 2021

Markus Rud

Markus Rud

## Contents

| $\mathbf{Li}$ | ist of         | Figur          | es                                                                          | vi   |  |  |

|---------------|----------------|----------------|-----------------------------------------------------------------------------|------|--|--|

| Li            | ist of         | Table          | S                                                                           | viii |  |  |

| A             | crony          | $\mathbf{yms}$ |                                                                             | ix   |  |  |

| 1             | Inti           | Introduction   |                                                                             |      |  |  |

| <b>2</b>      | The            | oretic         | al background                                                               | 4    |  |  |

|               | 2.1            | Energ          | y and power consumption in electrical systems $\ldots \ldots \ldots \ldots$ | 4    |  |  |

|               |                | 2.1.1          | Dynamic power consumption                                                   | 4    |  |  |

|               |                | 2.1.2          | Static power consumption                                                    | 5    |  |  |

|               | 2.2            | Low p          | ower techniques                                                             | 5    |  |  |

|               |                | 2.2.1          | Frequency scaling                                                           | 5    |  |  |

|               |                | 2.2.2          | Clock gating                                                                | 6    |  |  |

|               |                | 2.2.3          | Capacitance reduction                                                       | 6    |  |  |

|               | 2.3            | FPGA           | 1                                                                           | 6    |  |  |

|               |                | 2.3.1          | FPGA design process                                                         | 7    |  |  |

|               |                | 2.3.2          | Power consumption in a FPGA                                                 | 7    |  |  |

|               | 2.4            | FPGA           | A vs ASIC                                                                   | 8    |  |  |

|               |                | 2.4.1          | Clock networks                                                              | 8    |  |  |

|               | 2.5            | Comm           | nunication in digital wired systems                                         | 9    |  |  |

|               | 2.6            | Extern         | nal interface of SPI                                                        | 10   |  |  |

|               | 2.7            | Intern         | al design of SPI masters                                                    | 12   |  |  |

|               |                | 2.7.1          | Simple implementation                                                       | 13   |  |  |

|               |                | 2.7.2          | Complex implementation                                                      | 16   |  |  |

| 3             | Me             | thod           |                                                                             | 19   |  |  |

|               | 3.1            | Imple          | mentation of the SPI masters                                                | 19   |  |  |

|               | 3.2            | Simula         | ation and estimation methodology                                            | 19   |  |  |

|               |                | 3.2.1          | Design constraints                                                          | 20   |  |  |

|               |                | 3.2.2          | Simulation testbench                                                        | 21   |  |  |

|               |                | 3.2.3          | Power estimation                                                            | 22   |  |  |

|               | 3.3            | Condu          | acted tests                                                                 | 23   |  |  |

|               |                | 3.3.1          | Frequency                                                                   | 23   |  |  |

|               |                | 3.3.2          | Alternation of operating mode                                               | 24   |  |  |

|               |                | 3.3.3          | Internal changes to the complex master                                      | 25   |  |  |

|               |                | 3.3.4          | Power optimization                                                          | 25   |  |  |

| 4             | $\mathbf{Res}$ | ults           |                                                                             | 26   |  |  |

|                                    | 4.1   | System frequency                       | 27        |  |  |

|------------------------------------|-------|----------------------------------------|-----------|--|--|

|                                    | 4.2   | SCLK division                          | 31        |  |  |

|                                    | 4.3   | Alternation of operating mode          | 35        |  |  |

|                                    | 4.4   | Internal changes to the complex master | 37        |  |  |

|                                    | 4.5   | Power optimization                     | 39        |  |  |

| <b>5</b>                           | Dis   | cussion                                | 44        |  |  |

|                                    | 5.1   | Estimation method                      | 44        |  |  |

|                                    |       | 5.1.1 Reliability of estimations       | 45        |  |  |

|                                    | 5.2   | System frequency                       | 46        |  |  |

|                                    | 5.3   | SCLK division                          | 47        |  |  |

|                                    | 5.4   | Alternation of operating mode          | 48        |  |  |

|                                    | 5.5   | Internal changes to the complex master | 49        |  |  |

|                                    | 5.6   | Power optimization                     | 49        |  |  |

|                                    | 5.7   | Deviating results                      | 50        |  |  |

|                                    | 5.8   | Tool evaluation                        | 51        |  |  |

| 6                                  | Cor   | nclusion                               | 52        |  |  |

| 7                                  | Fur   | ther work                              | <b>54</b> |  |  |

|                                    | 7.1   | SPI                                    | 54        |  |  |

|                                    | 7.2   | Considerations regarding MBus          | 54        |  |  |

| $\mathbf{R}$                       | efere | nces                                   | 56        |  |  |

| A Simulation/estimation parameters |       |                                        |           |  |  |

## List of Figures

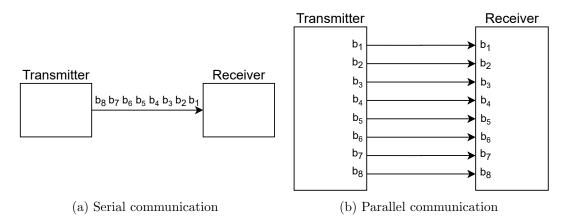

| 2.1  | Alternative ways of communicating in digital systems, from [6]          | 9  |

|------|-------------------------------------------------------------------------|----|

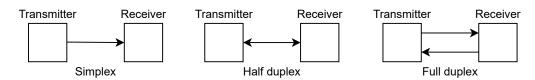

| 2.2  | Setup of bus directions in communication, from [6]                      | 10 |

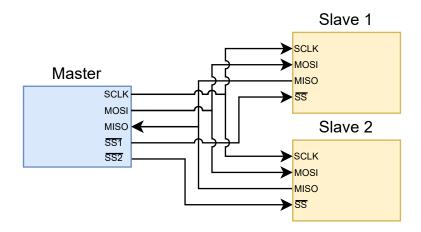

| 2.3  | Example of external SPI interface, from [6]                             | 11 |

| 2.4  | Different operating modes in SPI transmission with alternations to CPOL |    |

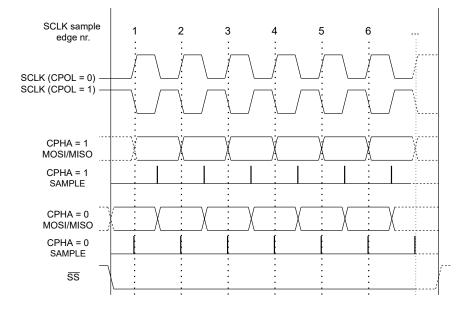

|      | and CPHA, modified from [18]                                            | 12 |

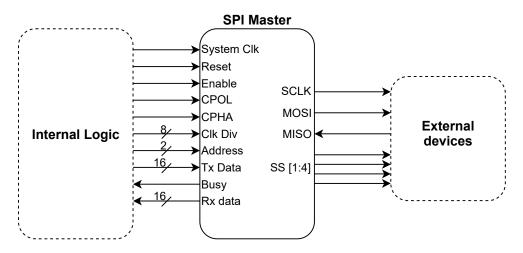

| 2.5  | I/O-connections for simple implementation of SPI master                 | 13 |

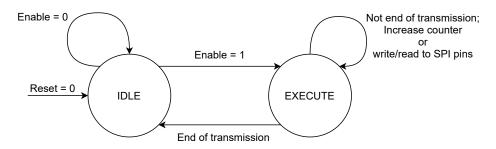

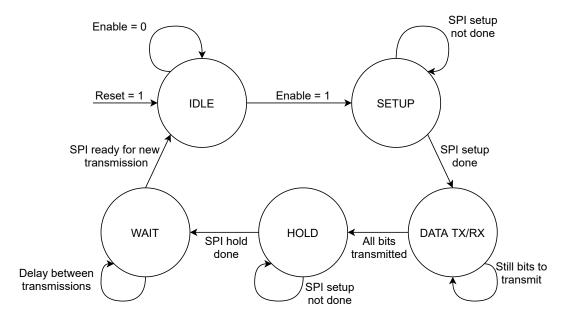

| 2.6  | State machine for simple implementation of SPI master                   | 15 |

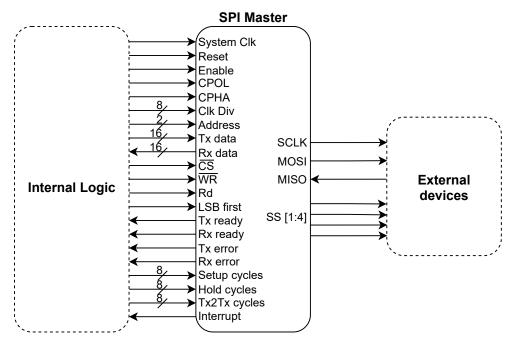

| 2.7  | I/O connections for complex implementation of SPI master                | 16 |

| 2.8  | State machine for complex implementation of SPI master                  | 18 |

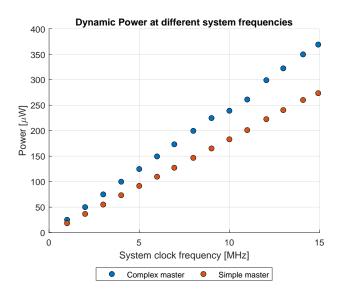

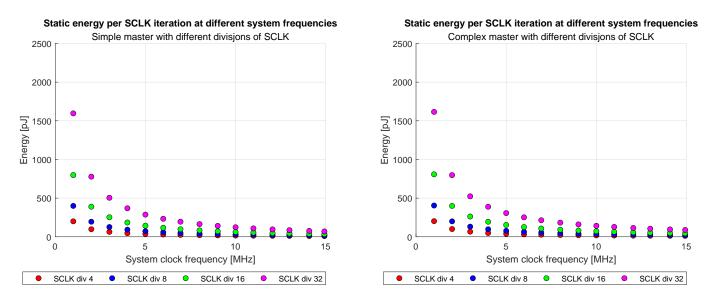

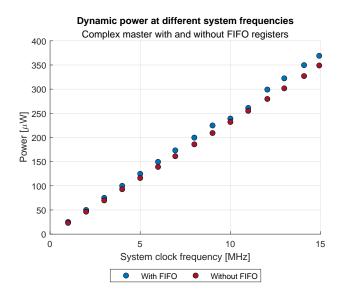

| 4.1  | Average dynamic power consumption in both implementations of the        |    |

|      | SPI master applying different system clock frequencies                  | 27 |

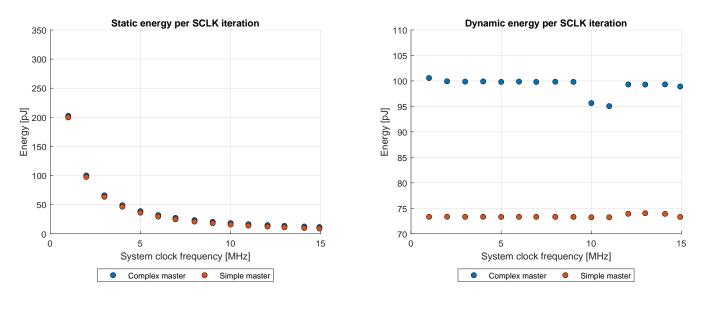

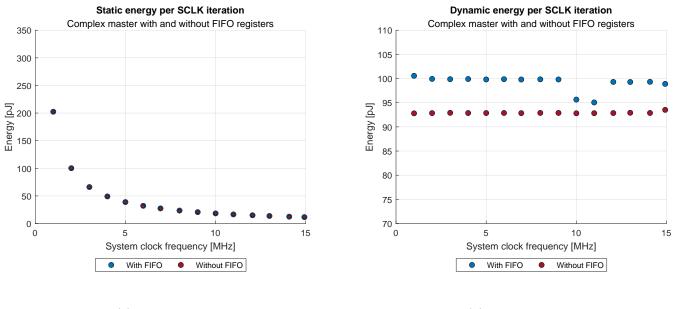

| 4.2  | Energy per SCLK iteration in the different implementations of the SPI   |    |

|      | master divided into static and dynamic consumption                      | 28 |

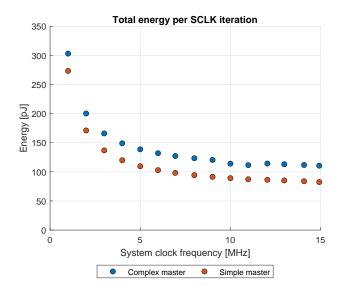

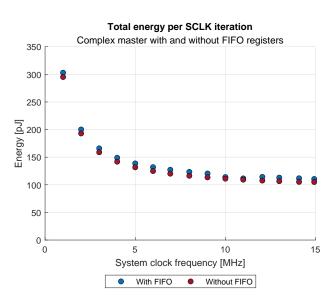

| 4.3  | Total consumption of energy per clock iteration in both implementations |    |

|      | of the SPI master                                                       | 29 |

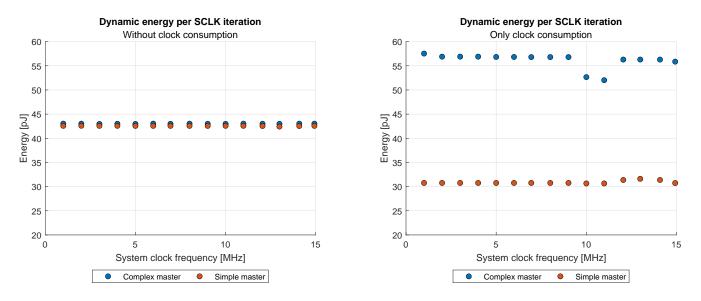

| 4.4  | Energy per SCLK iteration in the different implementations of the SPI   |    |

|      | master with separation of clock contribution to dynamic energy con-     |    |

|      | sumption                                                                | 30 |

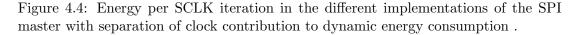

| 4.5  | Average dynamic power consumption for different divisions between the   |    |

|      | system clock and SCLK at different system clock frequencies             | 31 |

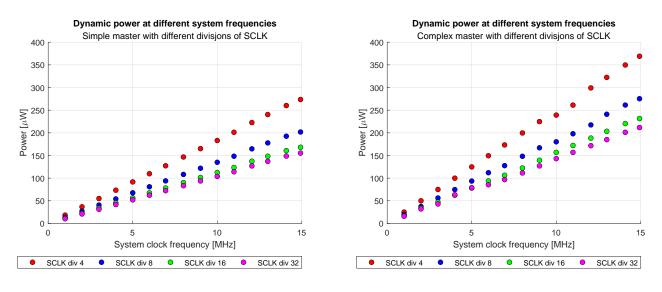

| 4.6  | Static energy consumption per SCLK iteration for different divisions    |    |

|      | between the system clock and SCLK at different system clock frequencies | 32 |

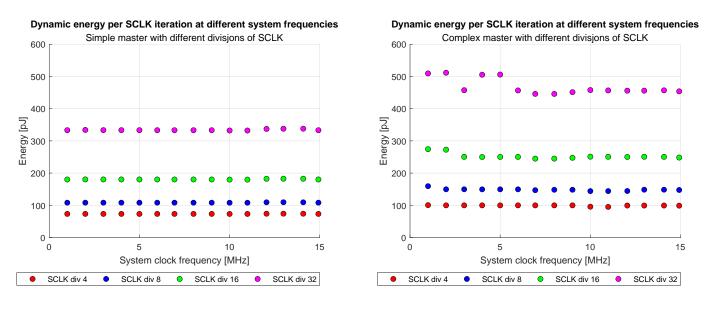

| 4.7  | Dynamic energy consumption per SCLK iteration for different divisions   |    |

|      | between the system clock and SCLK at different system clock frequencies | 33 |

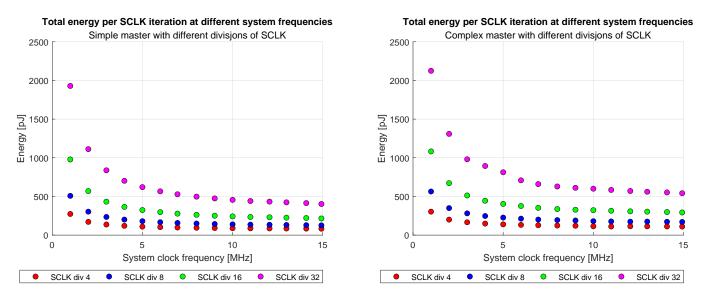

| 4.8  | Total energy consumption at one SCLK iteration for different divisions  |    |

|      | between the system clock and SCLK at different system clock frequencies | 33 |

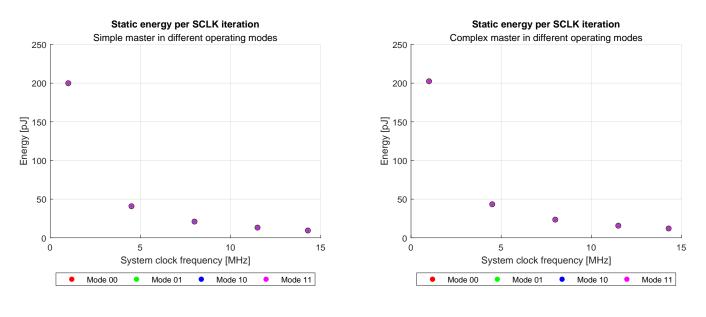

| 4.9  | Static energy per SCLK iteration for different operating modes of the   |    |

|      | SPI masters at different system clock frequencies. Modes displayed as:  |    |

|      | СРОГ СЪНА                                                               | 35 |

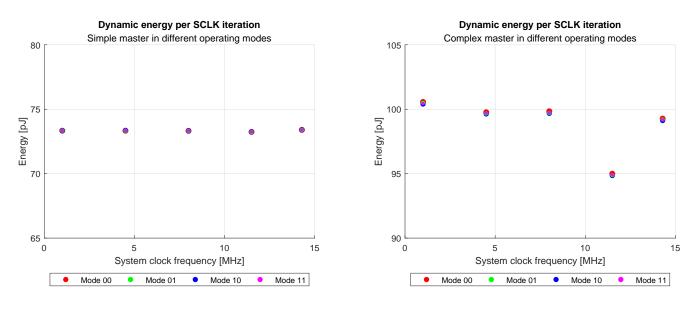

| 4.10 | Dynamic energy per SCLK iteration for different operating modes of      |    |

|      | the SPI masters at different system clock frequencies. Modes displayed  |    |

|      | as: CPOL CPHA                                                           | 36 |

| 4.11 | Average dynamic power consumption in the complex SPI implemen-          |    |

|      | tation with the use of FIFO registers or not at different system clock  |    |

|      | frequencies                                                             | 37 |

| 4.12 | Energy consumption per SCLK iteration in the complex SPI implemen-      |    |

|      | tation with the use of FIFO registers or not at different system clock  |    |

|      | frequencies                                                             | 38 |

| 4.13 | Total energy consumption per clock iteration in the complex SPI im-                               |    |

|------|---------------------------------------------------------------------------------------------------|----|

|      | plementation with the use of FIFO registers or not at different system                            |    |

|      | clock frequencies                                                                                 | 38 |

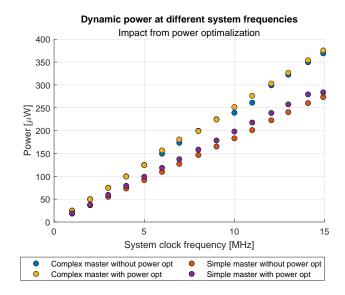

| 4.14 | Average dynamic power consumption for the different SPI implementa-                               |    |

|      | tions with and without power optimization enabled                                                 | 40 |

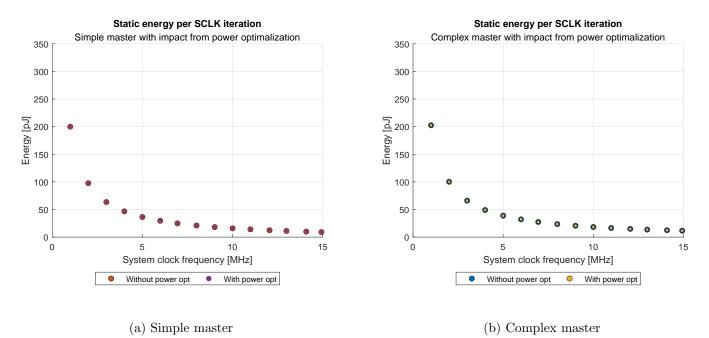

| 4.15 | Static energy per SCLK iteration for the different SPI implementations                            |    |

|      | with and without power optimization enabled $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 40 |

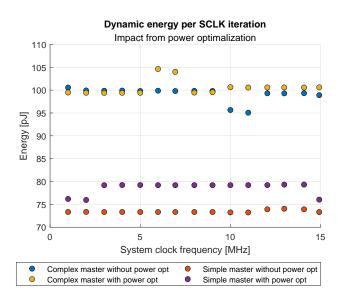

| 4.16 | Dynamic energy per SCLK iteration for the different SPI implementa-                               |    |

|      | tions with and without power optimization enabled                                                 | 41 |

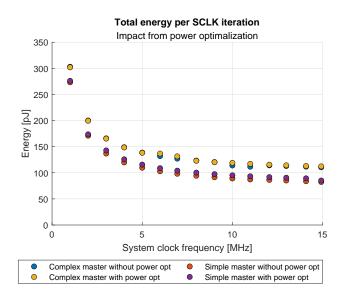

| 4.17 | Total energy per SCLK iteration for the different SPI implementations                             |    |

|      | with and without power optimization enabled $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 42 |

## List of Tables

| 2.1 | Description of I/O-connections for simple implementation of SPI master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Description of I/O-connections for complex implementation of SPI master $% \mathcal{A}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17 |

| 3.1 | Available programmable logic in the applied SoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 19 |

| 3.2 | Port constraints in SPI implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 21 |

| 4.1 | Increased energy in percent from simple master to complex master $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29 |

| 4.2 | Utilized resources in the FPGA with percentage of utilized FPGA re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | sources in parenthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 31 |

| 4.3 | Average energy increase going from SCLK division 4 to other divisions .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34 |

| 4.4 | Average energy decrease with removal of FIFO registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |

| 4.5 | Utilized resources in the FPGA with and without FIFO registers. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | percentage use of FPGA resources are displayed in parenthesis $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

| 4.6 | Average total energy decrease from power optimizations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42 |

| 4.7 | Utilized resources in the FPGA with power optimization enabled. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|     | percentage use of FPGA resources are displayed in parenthesis $\ldots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 43 |

| A.1 | Transmitted/received data in test<br>bench $\hfill \ldots \hfill \hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \hfill \ldots \hfill \hfill \hfill \hfill \ldots \hfill \hfill \hfill \ldots \hfill \hf$ | 59 |

| A.2 | Environmental parameters in power estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 59 |

| A.3 | Voltage parameters in power estimation based on typical values for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|     | operating conditions in the datasheet for the SoC[34] $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

## Acronyms

- ASIC Application-Specific Integrated Circuit. 8, 45, 54

- CPHA Clock Phase. 11, 22, 35, 49

- **CPOL** Clock Polarity. 11, 22, 35, 49

- FIFO First In, First Out. i, ii, 17, 25, 37, 49

- **FPGA** Field-Programmable Gate Array. i, ii, 2, 6, 19, 30, 44, 52, 54

- HDL Hardware Description Language. 7, 14

- I/O Input/Output. 2, 7, 19, 30, 44

- I2C Inter-Integrated Circuit. 1, 54

- **IoT** Internet of Things. 1

- **IP** Intellectual Property. 2, 44

- LSB Least Significant Bit. 16

- $\mathbf{LUT}$ Look-Up Table. 7, 19, 31, 44

- MISO Master In Slave Out. 10, 21

- MOSI Master Out Slave In. 10, 21

- MSB Most Significant Bit. 16

- RTL Register Transfer Level. 7, 19, 30, 51

- SCLK Serial Clock. 10, 20, 26, 46, 52

- SLOC Source Lines Of Code. 30, 47

- SoC System on Chip. 19

- **SPI** Serial Peripheral Interface. i, ii, 1, 5, 10, 19, 26, 44, 52, 54

- ${\bf SS}\,$  Slave Select. 10

VHDL VHSIC Hardware Description Language. i, ii, 7, 21

## 1 Introduction

One of the largest concerns when designing an electrical systems in the modern era is power and energy consumption. The requirements and expectations for electrical systems grow rapidly with the growing Internet of Things (IoT) era where an important element is a long life time for a device from a limited energy source such as a battery[1]. One estimate predicts that more than 41 billion IoT devices can exist by 2027[2] which gives large market opportunities for devices with a low energy consumption. The importance of energy management is not only limited to the IoT area, but also for all other electrical systems as well since energy consumption has a large environmental impact[3]. This creates a demand for devices with a low energy consumption which can have a long battery life time or low power draw.

An electrical system such as an IoT-device often consists of multiple subsystems where each subsystem has its own consumption of power and energy. Naturally it is the total energy consumption for the combined system who is of importance when trying to lower the energy consumption, but due to the combination of subsystems it can be beneficial to focus the effort in energy reduction to a subsystem-level. The different subsystems will often communicate between each other to exchange data and depending on the system, the energy consumption from such internal communication could be of a significant amount and an effort in energy reduction could be beneficial.

Multiple communication methods between subsystems are already defined as communication protocols and made publicly available. These differ with a large variety of communication concepts such as digital or analog, and wired or wireless where the different methods often includes different functionality and area of usage. This thesis is focused on digital wired communication mainly for internal use within an embedded system such as between a sensor and a microprocessor, but it still exists a variety of different protocols with different advantages and disadvantages within this area of usage. Examples of such protocols are SPI, I2C, MBus<sup>1</sup>[4] and more. A new specialized communication method could naturally be created for each new system, but the utilization of a commonly used communication protocol could shorten design time and make it easier to include already created devices such as a sensor made by a different company into the new system.

When implementing a communication protocol into a system, the designer must choose whether the communication functionality should be provided by software or by dedicated hardware. For instance could the communication protocol be implemented in a general purpose processor as a part of the software, or it might be designed as specific modules with dedicated hardware just for communication. There are naturally advan-

$<sup>^{1}</sup>$ Some considerations regarding MB us are described in subsection 7.2 for readers especially interested in the development of this protocol

tages and disadvantages for each of the implementation strategies where one advantage of the hardware implementation is a tendency of a lower energy consumption than a software solution[5], but at the cost of extra area requirements.

With a large amount and variety in established communication protocols, it could be a difficult task to choose the proper one for a specific system. As presented in [6] the proper communication protocol heavily depends on system specifications and requirements such as energy consumption, available I/O, available devices and more. The communication protocol therefore has to be chosen on a case-to-case basis based upon the requirements. The specifications of a communication protocol often only specifies the external interface for how the subsystems should be connected and interact. This gives a large amount of freedom to the designer regarding the implementation of a communication module since as long as the module fulfills the external specifications, the implementation of the modules can be designed freely. This gives the possibility to implement communication modules with different complexity levels such as additional data handling or additional internal communication to a subsystem controlling the communication module. A simple implementation of the communication module where only the bare minimum in order to fulfill the external requirements is implemented might therefore use a lower amount of energy than a complex implementation where added functionality such as temporary storage or other features are implemented due to a simpler implementation.

During the design of a larger system, a designer could typically utilize a premade Intellectual Property (IP) to add functionality or speed up the design process where a communication module is an example of a typical IP to add to the system. Often it is not desired to largely modify such IPs or it might not be possible since they can be encrypted[7]. This creates a need to have an understanding of how the complexity level of the design impact different aspects such as energy consumption and area requirement in order to choose the proper IP or design to include in the system.

This thesis presents an analysis of the energy consumption for two different premade designs of the master device for the SPI protocol. One where only the minimum amount of required functionality in order to operate the external interface is implemented which can be considered a simple design and one with more internal functionality such as more feedback to the controlling subsystem and adjustment of transmission parameters and can therefore be considered a more complex design. These designs are implemented in hardware on a model of a FPGA using the development tool Vivado and their power and energy consumption are estimated and analysed. In order to understand how the differences between the implementations affect the power and energy consumption, multiple tests are conducted. These tests include alternating the operating and communication frequency, different operating modes, modifying the internal hardware and power optimization. A look at already conducted studies on wired communication in embedded systems show that multiple studies compare the different communication protocols towards each other. However, the research done on how different implementations of the same protocol differ within the specifications are limited and is the reason for this study to be conducted.

The different tests are conducted over different operating frequencies ranging from 1 MHz to 15 MHz. The results from these tests show that the complex implementation requires an average of 27.2% more energy than the simple master at the different frequencies. The results also show that the two implementations respond relatively similarly to alternations in communication frequency and operating mode as the percentage energy change are relatively similar throughout the tests. However, due to the larger overall energy consumption for the complex master, the consequence of increase for the complex master is larger even if the percentage increase is similar. Lastly it is seen that performing power optimization on such a small design as a SPI master might have the opposite effect where the energy consumption increased with 5.2% and 1.3%for the simple and complex master respectively after power optimization when it would be more reasonable for the energy consumption to decrease. These results however has certain uncertainties based on the implementation method on the FPGA. The SPI masters are implemented as standalone devices on the FPGA which not gives a completely realistic environment for the designs due to missing control logic. The use of a FPGA is also seen to be unfortunate when the energy consumption of the SPI masters themselves are of interest since the FPGA has an additional energy consumption due to the re-configurable functionality of a FPGA.

This thesis is organized by first presenting some required background knowledge, information about the external interface of the SPI protocol and a description of the differences in the two SPI master implementations in section 2. In section 3 are the Vivado tool and the method for development and analysis presented together with details regarding the applied tests. The results from the different tests are presented in section 4 and discussed in section 5 together with an evaluation of the applied analysis method. Lastly the conclusion is presented in section 6 and some recommendation for future work and some information regarding the MBus protocol are given in section 7

## 2 Theoretical background

Some basic knowledge about electrical concepts and systems are expected from the reader, but specific details are presented in this section.

#### 2.1 Energy and power consumption in electrical systems

The total energy E of an electrical system or design-implementation is equal to the integral of the instantaneous power P(t) over some time interval T as shown in equation 2.1[8]. This equation leads to the following two options for reducing the total energy consumption in a system; either make the design use less power, and/or power the design for a shorter time interval. For instance can a design with a high power consumption still have a low energy consumption as long at the time period is short enough.

$$E = \int_0^T P(t)dt \tag{2.1}$$

The total power consumption  $P_{total}$  for a system is a combination of two types of power dissipation as shown in equation 2.2. These are the dynamic power  $P_{dynamic}$  and the static power  $P_{static}$  where the total power is the sum of these.

$$P_{total} = P_{dynamic} + P_{static} \tag{2.2}$$

The average power consumption  $P_{avg}$  in a system is shown in equation 2.3 and is given as the total energy consumption divided by the total time interval.

$$P_{avg} = \frac{E}{T} \tag{2.3}$$

#### 2.1.1 Dynamic power consumption

The dynamic power consumption in a design is caused by changing signals and consist of both power from switching and from "short-circuits" as shown in equation 2.4. The short circuit power is generated in the brief moments when both the pMOS and nMOS stacks are partially on. This happens when the transistors in the design switches and a path is created directly between the supply voltage  $V_{DD}$  and ground GND[8].

$$P_{dynamic} = P_{switching} + P_{shortcircuit} \tag{2.4}$$

The main contributor to the dynamic power consumption is the switching power as it normally contributes to more than 90% of the total dynamic power[8]. The switching

power is again affected by a variety of factors as shown in equation 2.5 where  $\alpha$  is the activity factor, C is the capacitance and f is the switching frequency. The activity factor is seen as the probability for a node in the circuit switches from 0 to 1.

$$P_{switching} = \alpha C V_{DD}^2 f \tag{2.5}$$

#### 2.1.2 Static power consumption