Felix Allan Schöpe

# Ultra-low power accurate temperature sensor for IoT

Master's thesis in Electronic Systems Design July 2020

**Master's thesis**

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Felix Allan Schöpe

# Ultra-low power accurate temperature sensor for IoT

Master's thesis in Electronic Systems Design Supervisor: Snorre Aunet (IET), Pål Øyvind Gamst Reichelt (Disruptive Technologies Research AS) July 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

### Summary

The analog front-end of a proposed BJT-based temperature sensor has been designed. The design has been analysed using Monte-Carlo simulations with mismatch over all process corners. The design was implemented in a 90nm generic process design kit. The analog front-end achieves ultra-low power consumption with a current consumption of 2.3  $\mu$ A at a temperature of 27 °C and can operate over the military temperature range of -55 °C - 125 °C. It uses a voltage supply of 2 V.

An adaptive self-biasing operational amplifier was implemented in the bandgap reference circuit to ensure sufficiently high DC loop-gain. It operates on an ultra-low current consumption of 631 nA. To reduce errors due to mismatch and process spread two correction techniques have been employed, that is chopping of the input signals of the operational amplifier and dynamic element matching of the current sources in the bipolar core.

The residual temperature reading error at the output of the analog front-end is large and results in significant errors. This is because no compensation technique was implemented in the analog front-end to compensate for process spread of the BJTs and should be implemented digitally. The temperature reading errors due to offset and mismatch in the current sources have been reduced to around 0.03 °C at a temperature of 27 °C. The noise in the circuit was analysed without the dynamic effects of the DEM because of its simple implementation and results in an equivalent temperature error of around 0.12 °C, which indicates the resolution that is achievable. The settling time of the circuit is in the range of 110  $\mu$ s.

## Acknowledgement

I would like to thank my supervisor Professor Snorre Aunet at NTNU for agreeing to supervise this project and helping me with words and deeds.

Furthermore, I would like to express my gratitude to Pål Øyvind Reichelt from Disruptive Technologies Research AS for taking the time to support me throughout this project and answering all my questions in all those e-Mails. I learnt a lot from their guidance and am grateful that they invested the time to teach me.

Also I would like to thank my family for making it possible for me to pursue a master's degree in Norway and always supporting me on my way.

Lastly, I would like to thank my friends for always brighten my days during demanding periods throughout my studies.

## Table of Contents

| Su  | mma                 | ry                         |                                      | i      |

|-----|---------------------|----------------------------|--------------------------------------|--------|

| Ac  | know                | ledgem                     | ent                                  | ii     |

| Ta  | ble of              | Conter                     | nts                                  | v      |

| Li  | st of I             | ables                      |                                      | vii    |

| Li  | st of F             | ligures                    |                                      | X      |

| Li  | st of A             | Abbrevi                    | ations                               | xi     |

| Lis | st of S             | ymbols                     | 3                                    | xiii   |

| 1   | <b>Intro</b><br>1.1 | o <b>ductio</b><br>Pre-Stu | <b>n</b><br>udy                      | 1<br>3 |

| 2   | Lite                | rature I                   |                                      | 5      |

|     | 2.1                 | Introdu                    | action                               | 5      |

|     | 2.2                 | Tempe                      | rature Sensing Methods               | 5      |

|     |                     | 2.2.1                      | Resistor-based Sensors               | 5      |

|     |                     | 2.2.2                      | Thermal Diffusivity Sensors          | 6      |

|     |                     | 2.2.3                      | MOSFET-based Sensors                 | 6      |

|     |                     | 2.2.4                      | BJT-based Sensors                    | 8      |

|     | 2.3                 | Chosei                     | n Temperature Sensor                 | 11     |

| 3   | The                 | Parasit                    | ic Vertical PNP BJT                  | 13     |

|     | 3.1                 | Introdu                    | action                               | 13     |

|     | 3.2                 | Error I                    | Definition                           | 13     |

|     | 3.3                 | Ideal I-                   | -V-Characteristics                   | 14     |

|     | 3.4                 | Non-Ic                     | lealities of the I-V-Characteristics | 14     |

|     |                     | 3.4.1                      | Series Resistance                    | 16     |

|   |                   | 3.4.2 Early Effects                                                      | 7 |

|---|-------------------|--------------------------------------------------------------------------|---|

|   | 3.5               | Temperature Dependencies                                                 | 7 |

|   |                   | 3.5.1 Saturation Current                                                 | 7 |

|   |                   | 3.5.2 Current Gain                                                       | 9 |

|   |                   | 3.5.3 Bias Resistor                                                      | 0 |

|   | 3.6               | Processing Spread                                                        | 0 |

|   |                   | 3.6.1 Preface                                                            | 0 |

|   |                   | 3.6.2 Saturation current                                                 | 1 |

|   |                   | 3.6.3 Current Gain                                                       | 2 |

|   |                   | 3.6.4 Bias Resistor                                                      | 2 |

|   | 3.7               | Noise-Model                                                              | 3 |

|   |                   | 3.7.1 Types of Noise                                                     | 3 |

|   |                   | 3.7.2 Noise in BJTs                                                      | 4 |

|   |                   | 3.7.3 Noise in MOSFETs                                                   | 4 |

|   | ~                 |                                                                          | _ |

| 4 | <b>Com</b><br>4.1 | pensation and Correction Techniques       2         Introduction       2 |   |

|   |                   |                                                                          |   |

|   | 4.2               | Compensation for Finite Current Gain                                     |   |

|   | 4.3               | Chopping         2           Description         2                       |   |

|   | 4.4               | Dynamic Element Matching 2                                               |   |

|   | 4.5               | Curvature Correction                                                     |   |

|   | 4.6               | Trimming                                                                 | I |

| 5 | Desi              | gn of the Temperature Sensor 3                                           | 5 |

|   | 5.1               | Introduction                                                             |   |

|   | 5.2               | Design Specifications                                                    |   |

|   | 5.3               | The Analog Front-End 3                                                   | 6 |

|   | 5.4               | Sensitivity Analysis                                                     | 0 |

|   | 5.5               | Determination of the Bias Current                                        | 2 |

|   | 5.6               | Error Budgeting                                                          | 2 |

|   |                   | 5.6.1 $I_S$ and $R_{bias}$ Errors                                        | 3 |

|   |                   | 5.6.2 Mismatch Errors                                                    | 4 |

|   |                   | 5.6.3 Bias Circuit Errors                                                | 5 |

|   |                   | 5.6.4 Noise Budget                                                       | 6 |

|   |                   | 5.6.5 Budget Summary                                                     | 9 |

|   | 5.7               | Analog Front-End Design                                                  | 9 |

|   |                   | 5.7.1 Introduction                                                       | 9 |

|   |                   | 5.7.2 PNP Transistors and Bias Resistor                                  | 9 |

|   |                   | 5.7.3 Current Mirror                                                     | 0 |

|   |                   | 5.7.4 Operational Amplifier                                              | 2 |

|   |                   | 5.7.5 Chopping Circuit                                                   | 4 |

|   |                   | 5.7.6 Start-up Circuit                                                   | 5 |

|   |                   | 5.7.7 Dynamic Element Matching 5                                         | 7 |

|   |                   | 5.7.8 Test of Initial Design                                             | 7 |

|   |                   | 8                                                                        |   |

| 6  | Simu   | ilation  |                                     | 59 |

|----|--------|----------|-------------------------------------|----|

|    | 6.1    | Introdu  | ction                               | 59 |

|    | 6.2    | Simula   | tions                               | 59 |

|    | 6.3    | Achiev   | ed Performance                      | 60 |

|    |        | 6.3.1    | Performance of the Analog Front-end | 60 |

|    |        | 6.3.2    | Settling Time and Dynamic Effects   | 64 |

|    |        | 6.3.3    | Noise                               | 66 |

|    |        | 6.3.4    | Residual Temperature Error          | 67 |

|    |        | 6.3.5    | Worst Case Analysis                 | 69 |

| 7  | Cone   | clusion  |                                     | 71 |

| Bi | bliogr | aphy     |                                     | 73 |

| Ap | pendi  | ices     |                                     | 75 |

| A  | Gain   | and Pl   | nase Margin                         | 77 |

| В  | Circ   | uit Sche | ematics                             | 79 |

## List of Tables

| 1.1 | Parameter list of the chosen temperature sensors. Excerpt from [4]                              | 4  |

|-----|-------------------------------------------------------------------------------------------------|----|

| 5.1 | Design specifications of the analog front-end.                                                  | 36 |

| 5.2 | Design specifications of the analog front-end.                                                  | 49 |

| 5.3 | Aspect ratios of the current mirror devices $M_{12}$ and $M_{13}$                               | 52 |

| 5.4 | Aspect ratios of the operational amplifier devices.                                             | 54 |

| 5.5 | Aspect ratios of the switch devices.                                                            | 55 |

| 5.6 | Aspect ratios of the start-up circuit devices.                                                  | 56 |

| 5.7 | Final aspect ratios of all devices.                                                             | 58 |

| 6.1 | Area and current consumption of the analog front-end.                                           | 61 |

| 6.2 | Bias current and base-emitter voltage of the bias circuit                                       | 61 |

| 6.3 | Bias current and base-emitter voltage of the bipolar core                                       | 62 |

| 6.4 | Current density ratios of the bias circuit and the bipolar core                                 | 63 |

| 6.5 | DC loop gain, phase margin, gain-bandwidth product and input offset-                            |    |

|     | voltage of the bias circuit.                                                                    | 64 |

| 6.6 | Total noise at the output.                                                                      | 67 |

| 6.7 | Residual errors and the resulting temperature error $\varepsilon(D_{out})$                      | 67 |

| 6.8 | Residual errors and the resulting temperature error $\varepsilon(D_{out})$ of the bias circuit. | 68 |

| 6.9 | Worst cases and their according process corner and temperature                                  | 69 |

|     |                                                                                                 |    |

# List of Figures

| 1.1 | Block diagram of a smart temperature sensor.                           | 2  |

|-----|------------------------------------------------------------------------|----|

| 2.1 | Operating principle of a thermal diffusivity based sensor.             | 6  |

| 2.2 | Block diagram of the MOSFET-based alternative temperature measurement. | 7  |

| 2.3 | Operation principle of a BJT-based CMOS smart temperature sensor       | 8  |

| 2.4 | Cross section of a vertical PNP transistor in a standard CMOS process  | 9  |

| 2.5 | Bias core and generic readout circuit of BJT-based sensors             | 10 |

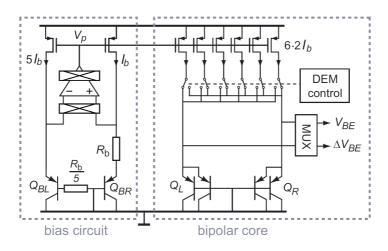

| 2.6 | Circuit diagram of the proposed sensor.                                | 11 |

| 2.7 | Non-linear, monotonic function of X and the linearised function $\mu$  | 12 |

| 2.8 | Block diagram of the Zoom-ADC                                          | 12 |

| 3.1 | Diode-connected PNP transistor.                                        | 15 |

| 3.2 | Forward current gain $\beta_F$ and collector current $I_C$ .           | 16 |

| 3.3 | The temperature dependency of the base-emitter voltage $V_{BE}$        | 18 |

| 3.4 | Curvature of $V_{BE}$                                                  | 19 |

| 3.5 | Spread of $V_{BE}$ due to processing spread of $I_S$                   | 22 |

| 3.6 | Noise sources of a BJT.                                                | 24 |

| 3.7 | Noise sources of a MOSFET                                              | 25 |

| 4.1 | A chopper amplifier.                                                   | 28 |

| 4.2 | Chopping diagram of the voltages.                                      | 29 |

| 4.3 | The chopper switch                                                     | 29 |

| 4.4 | Principle of dynamic element matching                                  | 30 |

| 4.5 | Voltage domain trimming                                                | 32 |

| 4.6 | Current-domain trimming.                                               | 33 |

| 5.1 | Overview of the proposed temperature sensor                            | 36 |

| 5.2 | Overview of the analog front-end.                                      | 37 |

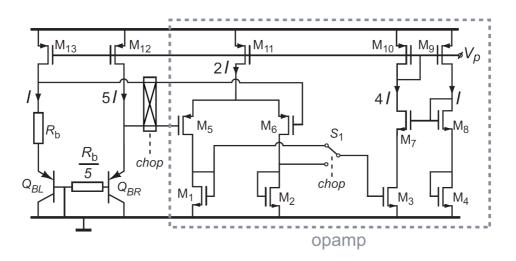

| 5.3 | Proposed circuit of the adaptive self-biasing operational amplifier    | 38 |

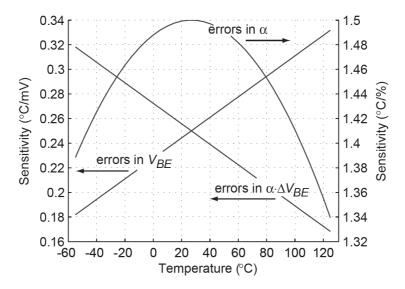

| 5.4 | Sensitivities of the digital output $D_{out}$ to errors.               | 41 |

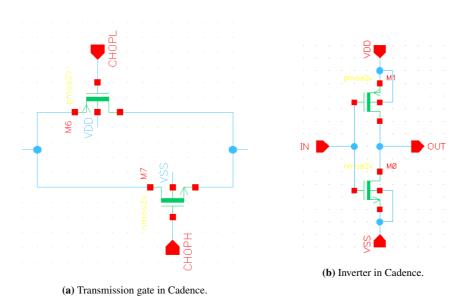

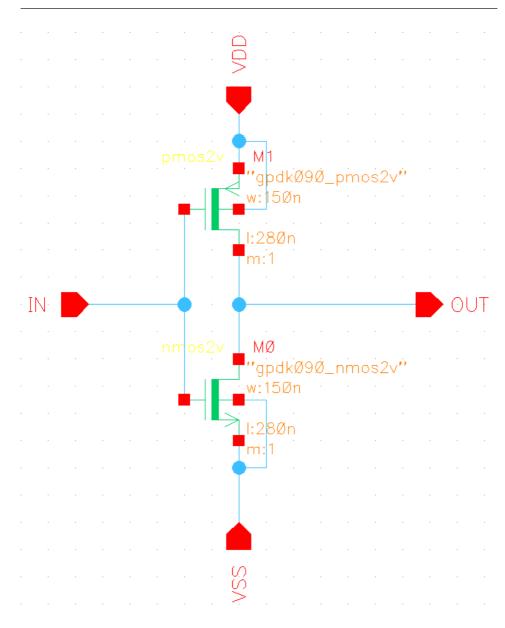

| 5.6 | Transmission gate and inverter in Cadence.                             | 55 |

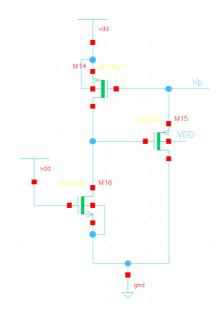

| 5.7         | Start-up circuit in Cadence                          | 56 |

|-------------|------------------------------------------------------|----|

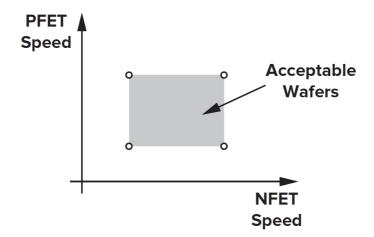

| 6.1         | Process corners and speed of NMOS and PMOS devices   | 60 |

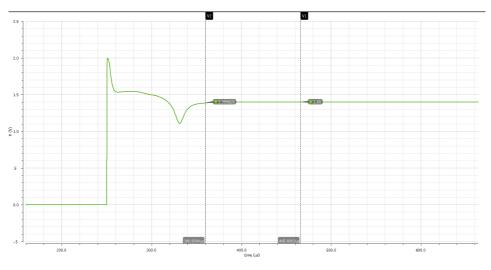

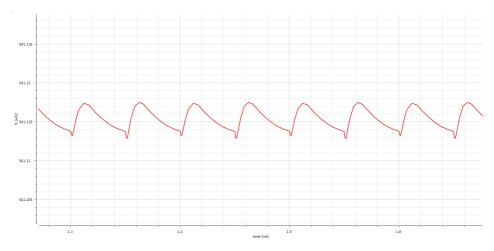

| 6.2         | Settling of voltage V <sub>p</sub>                   | 64 |

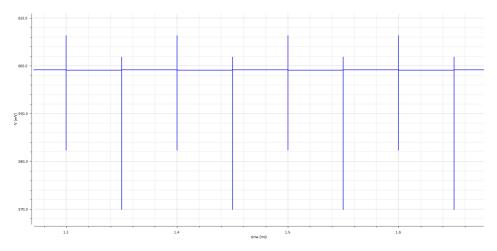

| 6.3         | Voltage spikes due to switching of the chopper.      | 65 |

| 6.4         | Effect of chopping on base-emitter voltage $V_{BE1}$ | 65 |

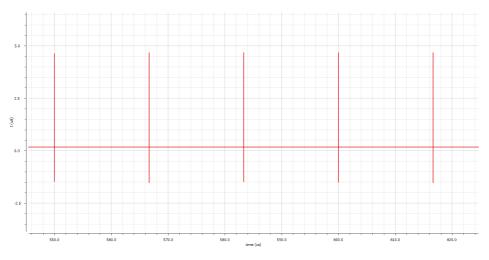

| 6.5         | Current spikes due to DEM switching.                 | 66 |

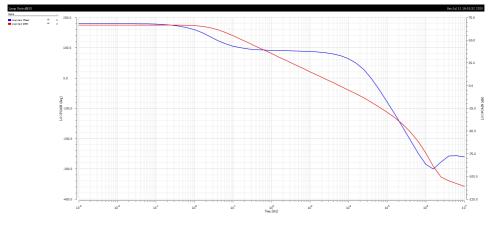

| A.1         | Gain and phase margin for NN at 27 °C                | 77 |

| A.2         | Gain and phase margin for SS at -55 °C               | 78 |

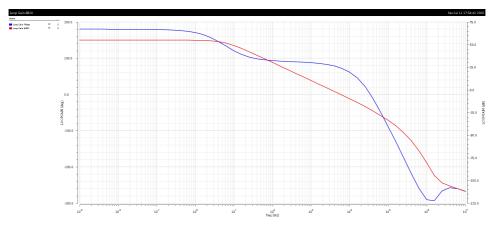

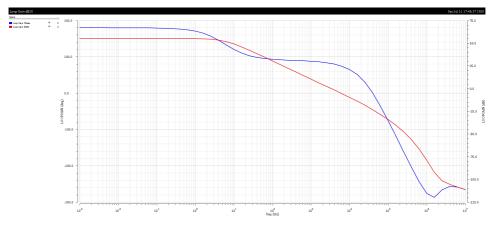

| A.3         | Gain and phase margin for FS at -55 °C               | 78 |

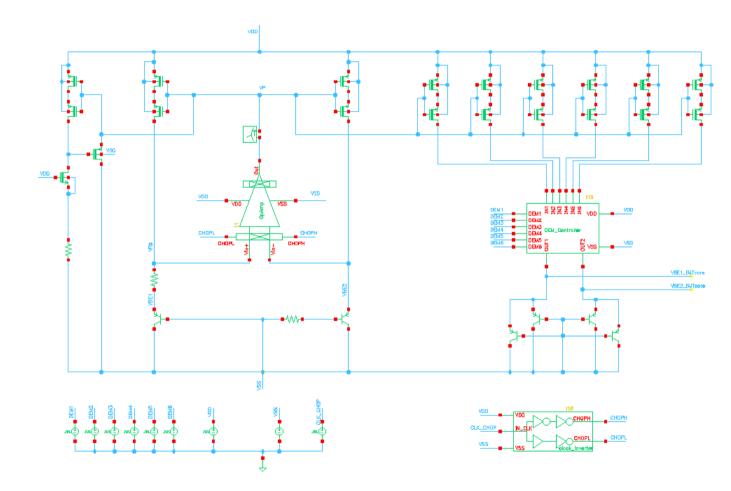

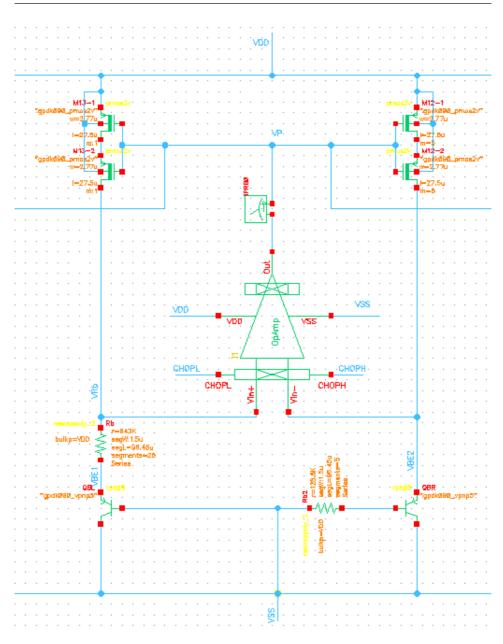

| <b>B</b> .1 | Overview of the analog front-end schematic.          | 80 |

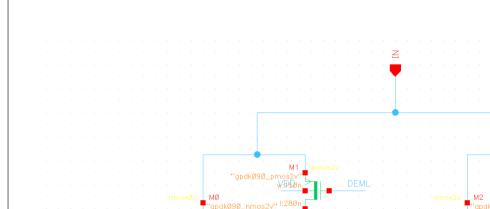

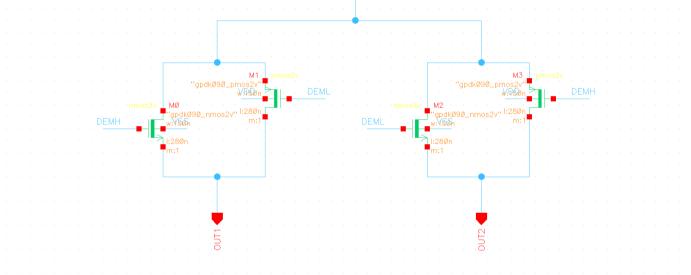

| B.2         | Close-up of the bias circuit schematic.              | 81 |

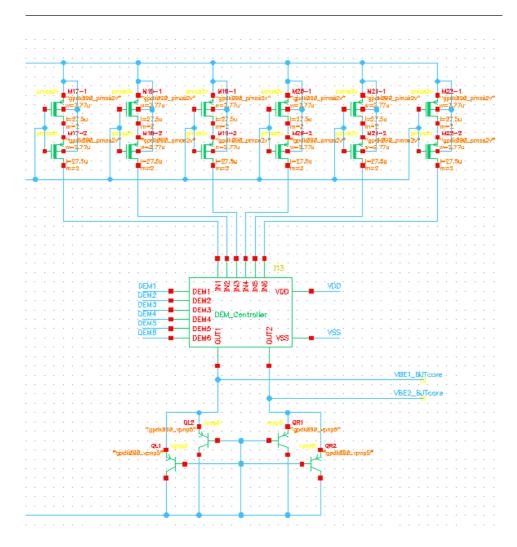

| B.3         | Close-up of the bipolar core schematic.              | 82 |

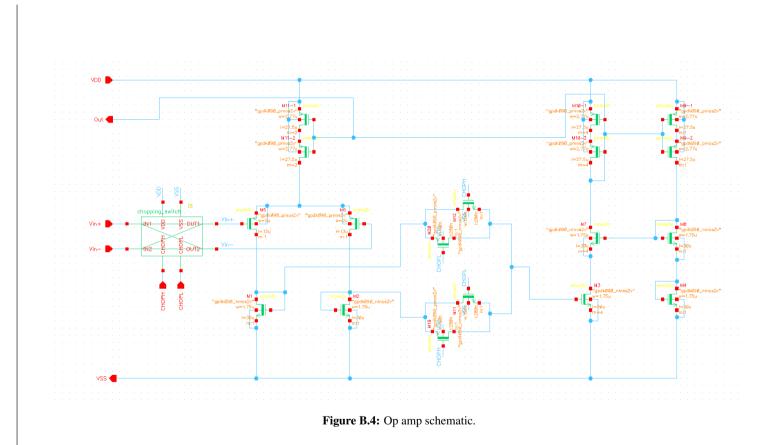

| <b>B.</b> 4 | Op amp schematic.                                    | 83 |

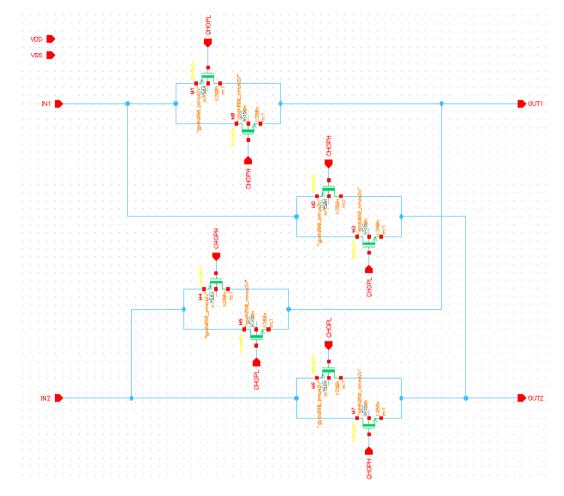

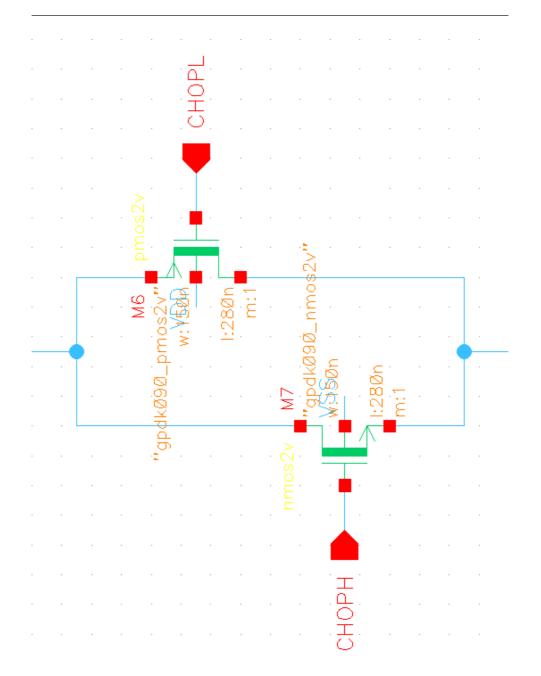

| B.5         | Chopping switch schematic                            | 84 |

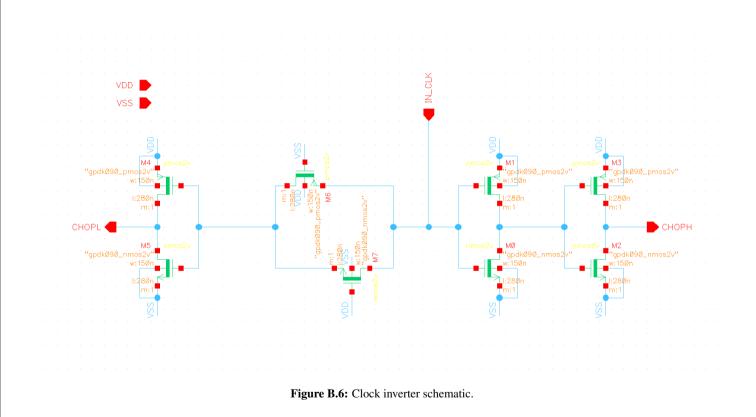

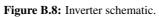

| B.6         | Clock inverter schematic.                            | 85 |

| <b>B</b> .7 | Transmission gate schematic.                         | 86 |

| <b>B.8</b>  | Inverter schematic.                                  | 87 |

| B.9         | DEM switch schematic.                                | 88 |

## **List of Abbreviations**

| Abbreviation        | Definition                                        |

|---------------------|---------------------------------------------------|

| ADC                 | Analog-to-digital converter                       |

| AC                  | Alternating current                               |

| BJT                 | Bipolar junction transistor                       |

| CTAT                | Complementary to absolute temperature             |

| CMOS                | Complementary metal-oxide-semiconductor           |

| DC                  | Direct current                                    |

| DEM                 | Dynamic Element Matching                          |

| FoM                 | Figure of merit                                   |

| GBW                 | Gain-bandwidth product                            |

| LAN                 | Local area network                                |

| MOSFET              | Metal-oxide-semiconductor field-effect transistor |

| MC                  | Monte-Carlo                                       |

| Op amp              | Operational amplifier                             |

| NMOS                | n-channel MOSFET                                  |

| PMOS                | p-channel MOSFET                                  |

| PTAT                | Proportional to absolute temperature              |

| REF                 | Reference                                         |

| SAR-ADC             | Successive-approximation ADC                      |

| Std dev             | Standard deviation                                |

| TC                  | Temperature coefficient                           |

| $\Delta\Sigma$ -ADC | Sigma-delta ADC                                   |

|                     |                                                   |

## **List of Symbols**

| Symbol                    | Definition                                             | Unit |

|---------------------------|--------------------------------------------------------|------|

| А                         | Constant, equal to 600 K                               | K    |

| $A_v$                     | Voltage gain                                           | V/V  |

| A <sub>Vt0</sub>          | Process dependent parameter                            | Vµm  |

| $A_{K}$                   | Process dependent parameter                            | %μ   |

| В                         | Constant, equal to -273 K                              | K    |

| CD                        | Depletion layer capacitance                            | F    |

| Cox                       | Gate-oxide capacitance                                 | F    |

| Dout                      | Temperature reading at the output of the sensor        | °C   |

| $g_{\rm m}$               | Transconductance                                       | S    |

| $I_D$                     | Drain current                                          | А    |

| Is                        | Saturation current                                     | А    |

| I <sub>C</sub>            | Collector current                                      | А    |

| $I_E$                     | Emitter current                                        | А    |

| IB                        | Base current                                           | А    |

| k                         | Boltzmann constant                                     | J/K  |

| $\mathbf{k}_{\mathbf{f}}$ | Flicker noise constant                                 |      |

| L                         | Gate length of a MOSFET                                | m    |

| р                         | Current density ratio                                  |      |

| q                         | Electron charge                                        | С    |

| R <sub>B</sub>            | Base resistance of a BJT                               | Ω    |

| $R_{E}$                   | Emitter resistance of a BJT                            | Ω    |

| R <sub>b</sub>            | Bias resistor                                          | Ω    |

| r <sub>ds</sub>           | Drain-source resistance                                | Ω    |

| Т                         | Absolute temperature                                   | Κ    |

| $V_{BE}$                  | Base-emitter voltage                                   | V    |

| V <sub>PTAT</sub>         | Proportional to absolute temperature dependent voltage | V    |

| V <sub>REF</sub>          | Reference voltage                                      | V    |

| V <sub>GS</sub>           | Gate-source voltage                                    | V    |

| $V_{th}$                  | Threshold voltage                                      | V    |

| V <sub>DD</sub>           | Supply voltage                                         | V    |

| V <sub>t</sub>            | Thermal voltage                                        | V    |

| $V_{g0}$                  | Silicon bandgap voltage                                | V    |

| Vos                       | Offset voltage                                         | V    |

| V <sub>ov</sub>           | Overdrive voltage                                      | V    |

| W                         | Gate width of a MOSFET                                 | m    |

| α                         | Scaling factor                                         |      |

| $\alpha_{\rm TCR}$        | Temperature coefficient                                | 1/K  |

| α <sub>F</sub>            | Common-base current-gain                               |      |

| $\beta_{\rm F}$ | Forward current-gain of BJT                   |             |

|-----------------|-----------------------------------------------|-------------|

| μ               | Electron mobility                             | $cm^2/(Vs)$ |

| μ               | ADC output                                    |             |

| $\Delta V_{BE}$ | Difference voltage of $V_{BE2}$ and $V_{BE1}$ | V           |

| σ               | Standard deviation                            |             |

# Chapter \_

### Introduction

Temperature sensors are used in many measurement, instrumentation and control systems, and even in households they are employed in various places. Examples of where temperature sensors are used are coffee machines, computers, heating systems or cars ([1], p. 1). This makes the temperature to the most-often measured environmental quantity, which leads to a large market. Therefore, it makes sense to integrate temperature sensors on chip with a readout circuitry that provides a digital output to reduce manufacturing costs to a minimum. Such temperature sensors are called *smart temperature sensor*. These sensors are able to directly communicate with computers in a standardised digital format. Nowadays, the digital output is almost mandatory in modern systems ([1], p. 2). Low-power radio systems have become more and more important in recent years which is why wireless temperature sensing has become very attractive for a many applications. Examples are in automotive, building automation or healthcare ([2], p. 1.).

Wireless sensors can be implemented as spatially distributed nodes in a wireless sensor network, which were introduced in the 2000s. Physical or environmental quantities can be measured and monitored by smart sensors, and due to the integrated analog-to-digital converter (ADC) a digital output is generated that is sent to a control unit via the wireless network. This control unit can either be centralised or distributed and receives the data for further processing. ([2], p. 2)

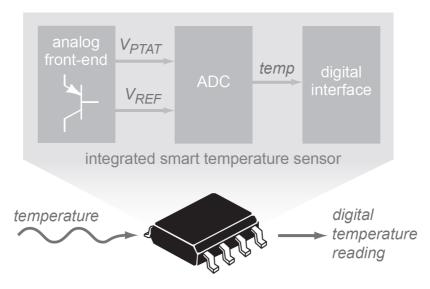

A smart temperature sensor is depicted in figure 1.1, it consists of an analog front-end which includes a temperature sensing circuit and a bias circuit. Additionally, an ADC is present that converts the temperature reading from voltages or currents to a digital format which is then communicated to another system through a digital interface. This digital interface can be, for example,  $I^2C$  for a wired sensor, or wireless local area network (LAN) for a wireless sensor ([1], p. 4), [3].

There are different techniques of designing temperature sensors that exploit the temperature dependency of the device characteristics. The output of the temperature sensing circuit is usually a temperature-dependent analog signal, such as a voltage, current, period or frequency ([1], p. 3). Which is indicated as temperature-dependent voltage  $V_{PTAT}$  in figure 1.1. PTAT stands for proportional to absolute temperature which means it has a linear and positive increase with rising temperature. However, to implement a smart temperature sensor a second analog signal is required to produce a digital representation of the temperature. In this case, it is a reference voltage  $V_{REF}$  to which  $V_{PTAT}$  is compared. This kind of measurement is called a ratiometric measurement ([1], p. 3).

The scope of this thesis is to design the analog front-end of a bipolar junction transistor (BJT) based temperature sensor with ultra-low power consumption. The temperature sensor is to be implemented on-chip for wireless operation, hence the ultra-low power consumption.

The thesis is organised as follows, chapter 2 will describe different sensing methods used in smart temperature sensors and gives a brief overview of achieved performances. Chapter 3 describes the theory of the temperature sensing method using BJTs and their nonidealities. In chapter 4, different correction and compensation techniques are presented to improve the performance. The design of the analog front-end of the chosen temperature sensor is explained in chapter 5. Chapter 6 deals with the simulations that are conducted in the simulation program Cadence Virtuoso to verify the design. The final result will then be analysed using Monte-Carlo (MC) simulations. The last chapter 7 will conclude the thesis and will give an outlook for future work.

Figure 1.1: Block diagram of a smart temperature sensor. It shows the different parts included on the chip ([1], p. 3).

### 1.1 Pre-Study

This master's thesis is based on the findings of a pre-study that was conducted as a part of the two years master's programme at NTNU, Trondheim, at the Department of Electronic Systems [4]. During the pre-study a literature review was conducted with the aim of finding and comparing reported sensor architectures to obtain an architecture that fulfils the requirements. These requirements were set beforehand and are listed here [4]:

- Ultra-low power consumption

- Sampling speed of 1 to 100 samples per second

- One temperature calibration after manufacturing

- Temperature range from -40  $^{\circ}$ C to +100  $^{\circ}$ C

- Absolute accuracy within 0.5 °C from 0 °C to 65 °C

- Resolution of 0.25  $^{\circ}\text{C}$  from 0  $^{\circ}\text{C}$  to 65  $^{\circ}\text{C}$

- Implemented on-chip in 0.18 µm CMOS technology.

A total of 20 articles, comprising different types and architectures of temperature sensors, were compared based on two figure of merits (FoM) and their overall performance. Table 1.1 was extracted from [4] and shows the performance parameters of the two sensors (BJT-sensor [5] and MOS-sensor [6]) that were deemed to be the most promising. At the bottom of the table the two FoMs are compared. The lower the value, the better the performance. It can be seen that the MOS-sensor ([6]) has lower FoM-values than the BJT-sensor ([5]). However, as is described in [4], the BJT-based sensor shows an overall good performance which fulfils all the requirements. The comparatively high power consumption can be reduced by decreasing the resolution and/or the accuracy, as well as the conversion time. One very important aspect is the calibration of the sensor. The MOSFET-based sensor is calibrated with a more expensive 2-point calibration, whereas the BJT-sensor only uses a fast 1-point voltage calibration. The combination of these characteristics is the reason why the BJT-sensor was deemed more promising. The architecture of the BJT sensor is described in chapter 2.3.

| Parameters          | <b>2</b> [5]            | 17 [6]                   |

|---------------------|-------------------------|--------------------------|

| Sensor type         | BJT                     | MOSFET                   |

| CMOS Technology     | 0.16 µm                 | 65 nm                    |

| Chip Area           | $0.08 \text{ mm}^2$     | $0.013 \text{ mm}^2$     |

| Power               | 5.1 μW                  | 640 pW                   |

| Supply Voltage      | 1.5 V - 2 V             | $1.2 V (V_{DDH})$        |

| Supply voltage      | 1.5 V - 2 V             | $0.5 V (V_{DDL})$        |

| Temp. Range         | -55 °C - +125 °C        | -20 °C - +100 °C         |

| Inaccuracy          | ±0.15 °C                | -2.7 °C / +1.8 °C        |

| Resolution          | 0.02 °C                 | 0.25 °C                  |

| Calibration         | voltage                 | 2-point                  |

| Calibration         | 1-point                 | 2-point                  |

| Conv. Time          | 5.2 ms                  | 34.3 ms                  |

| Energy/Conv.        | 27 nJ                   | 0.022 nJ                 |

| Resolution-FoM      | 0.0108 nJK <sup>2</sup> | 0.001375nJK <sup>2</sup> |

| Project-FoM         | 0.0009 nJK              | 0.00020625 nJK           |

| Voltage Sensitivity | 0.5 °C / V              |                          |

Table 1.1: Parameter list of the chosen temperature sensors. Excerpt from [4].

Chapter 2

### Literature Review

### 2.1 Introduction

In section 2.2 a brief overview of different temperature sensing methods that are used in state-of-the-art sensors is given, as well as a brief description of their functionality and the achieved results of state-of-the-art chips. Afterwards, a short outline of the functionality of the chosen temperature sensor is presented in section 2.3.

### 2.2 Temperature Sensing Methods

#### 2.2.1 Resistor-based Sensors

Temperature sensors based on resistors are widely used. Most of the CMOS-compatible resistors have a high temperature-coefficient which is desirable because the temperature is measured based on the resistance variations. Typical temperature coefficients of resistors in CMOS are between 0.1 %/°C and 0.4 %/°C, depending on the resistor type, according to [2]. This means that the resistance value can change about 72 % over a temperature range of -55 °C to 125 °C. Resistor-based sensors can function on very low voltages which is then limited by the minimum supply voltage of the readout circuit.

However, the drawback is that resistors suffer from strong processing spread. In typical CMOS-processes these resistance spreads can be as high as 15 % or 20 %. In addition, the temperature coefficients are also affected by processing spread and higher order non-linearities. That is why this type of temperature sensor can be rather costly since it needs multiple temperature calibrations. ([2], p. 8-9)

Temperature sensors based on resistors are reported to have temperature ranges of -40 °C to +180 °C and achieve inaccuracies of  $\pm 0.15$  °C (for a standard deviation of  $3\sigma$ ) over a temperature range of -55 °C to +85 °C, after trimming the sensor at three temperatures according to [2]. Another sensor is reported to achieve an inaccuracy of  $\pm 1$  °C over a range of -45 °C to +125 °C ([2], p. 9).

#### 2.2.2 Thermal Diffusivity Sensors

According to [2], the thermal diffusivity of silicon is well defined and exhibits a highly temperature dependent characteristic. It is a rate at which the heat diffuses through a silicon substrate which can be used to design temperature sensors. The thermal diffusivity D can be approximated by  $D \propto 1/T^{1.8}$ .

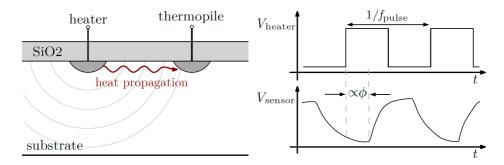

The working principle is shown in figure 2.1. It uses a heater to generate heat pulses which are sensed by a relative temperature sensor, a thermopile, which is placed at a known distance from the heater. The received heat pulses are converted into a small voltage signal. Current pulses with a constant frequency are sent through the substrate while dissipating power into the substrate. This results in temperature fluctuations which also propagate through the substrate and are then sensed by the thermopile. The delay between the pulses of the heater and the sensed temperature fluctuations is related to D. [3]

Figure 2.1: Operating principle of a thermal diffusivity based sensor ([7], p. 15).

However, such a temperature sensor is not suited for low-power operation because of the energy required for the heat pulses. Yet, it is possible to design sensors with decent accuracies without trimming. Sensors with accuracies of  $\pm 0.2$  °C and  $\pm 0.5$  °C ( $3\sigma$ ) over a temperature range from -55 °C to +125 °C are reported. Therefore, this type of sensor can be a solution in applications where uncalibrated accuracy is important, while the power consumption is of second interest. ([2], p. 9-10)

#### 2.2.3 MOSFET-based Sensors

MOSFETs are well defined and optimised in CMOS processes and therefore it is of benefit to use MOSFETs as temperature sensing elements [3]. In addition, when MOS transistors are biased in sub-threshold region their power consumption is very low. When a MOSFET is operated in the sub-threshold region its drain current I<sub>D</sub> and the gate-source voltage V<sub>GS</sub> are temperature-dependent exponentially related which is a similar relation as exhibited by the bipolar junction transistor. Equation 2.1 shows the exponential relationship of I<sub>D</sub> and V<sub>GS</sub> ([2], p. 10).

$$I_D \propto \frac{W}{L} exp \left[ \frac{q}{mkT} \cdot (V_{GS} - V_T) \right]$$

(2.1)

In this equation, k is the Boltzmann's constant, T the absolute temperature, q the electron charge, W and L are the width and the length respectively and m the body effect coefficient, which is computed as  $m = 1 + C_D/C_{OX}$ . Here, C<sub>D</sub> is the depletion-layer and C<sub>OX</sub> is the gate-oxide capacitance.

It is possible that the MOSFET replaces the BJT as sensing element. Though, the MOS transistor performance is dependent on the processing spread of two parameters which results in greater inaccuracies. The parameters that are suffering from processing spread are the threshold voltage  $V_T$  and the oxide capacitance  $C_{OX}$ . Nevertheless, the MOSFET offers the possibility of low supply voltage operation, due to the fact that it is biased in sub-threshold region as mentioned above. Therefore, the gate-source voltage is significantly lower as in saturation region and can be controlled by sizing W or L ([2], p. 11).

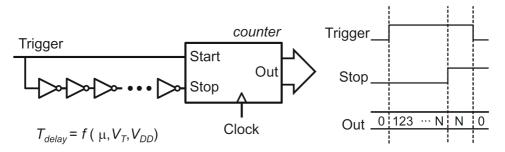

Another method of measuring the temperature is the propagation delay of a CMOS inverter chain or the frequency of a ring oscillator. The operating principle is shown in figure 2.2. It uses a counter to measure the propagation delay where the delay  $T_P$  in an inverter consisting of PMOS and NMOS transistors can be written as follows ([2], p. 11), [3]:

$$T_P = \frac{\left(\frac{L}{W}\right) \cdot C_L}{\mu C_{OX}(V_{DD} - V_{th})} \cdot \ln\left[\frac{3V_{DD} - 4V_{th}}{V_{DD}}\right].$$

(2.2)

The mobility  $\mu$  and the threshold voltage V<sub>th</sub> are temperature dependent. Due to processing spread it is usually necessary to perform a two-point calibration, and in addition it suffers from very high power supply sensitivity, which can be in the range of 10 °C/V ([2], p. 11). A temperature range from -20 °C to +100 °C are reported with inaccuracies of several degrees [8].

Figure 2.2: Block diagram of the alternative temperature measurement, based on MOSFET inverter delay ([2], p. 11).

#### 2.2.4 BJT-based Sensors

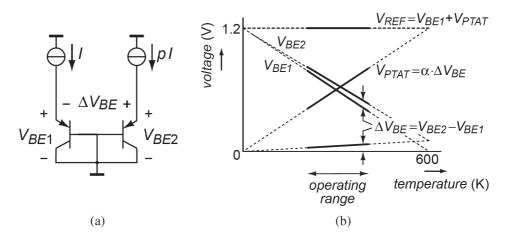

The sensor type that is used in this thesis (the process of choosing this architecture was explained in section 1.1) is based on the bipolar junction transistor and its temperature characteristics. These characteristics exploit two voltages, which is the thermal voltage  $V_t = kT/q$  (where k is the Boltzmann constant, T is the absolute temperature and q is the electron charge) and the silicon bandgap voltage  $V_{g0}$ , for a ratiometric measurement. Figure 2.3 shows that it is possible to use the thermal voltage to generate a voltage  $V_{PTAT}$  that is proportional to absolute temperature (PTAT) while the bandgap voltage is used to generate the temperature-independent reference voltage  $V_{REF}$  ([1], p. 4).

**Figure 2.3:** Operation principle of a BJT-based CMOS smart temperature sensor. a) Two diodeconnected transistors are biased at a well-defined current density ratio 1:p; b) the in that way generated base-emitter voltages are generating the voltage  $V_{PTAT}$  and  $V_{REF}$  for the ratiometric measurement ([1], p. 4).

The two diode-connected transistors are biased at a precise current density ratio p. This results in two base-emitter voltages  $V_{BE1}$  and  $V_{BE2}$  that are complementary to absolute temperature (CTAT) in nature. The difference between these two base-emitter voltages generates the PTAT voltage  $\Delta V_{BE}$ . Since this voltage is rather small it has to be amplified to be useful, which is then the voltage  $V_{PTAT} = \alpha \cdot \Delta V_{BE}$  [[1], p. 4), [3].

As can also be seen from figure 2.3 b) is that the reference voltage  $V_{REF}$  is based on the absolute base-emitter voltage of a BJT. If the base-emitter voltage is extrapolated to

T = 0 K it equals the silicon bandgap voltage  $V_{g0}$  of around 1.2 V. From there, it decreases by about 2 mV/K (equation 2.5) which is why the amplified difference voltage is added to the base-emitter voltage. The reference voltage is approximately temperature-independent ([1], p.5).

The scaling factor  $\alpha$  can be calculated by taking the equation for V<sub>REF</sub>:

$$V_{REF} = V_{BE} + \alpha \cdot \Delta V_{BE}, \qquad (2.3)$$

and solving it such that the temperature coefficient of  $V_{REF}$  is zero ([2], p. 23):

$$S_{V_{BE}}^{T} = \left| \frac{\partial V_{BE}}{\partial T} \right| \approx 2mV/^{\circ}C = \alpha \cdot \frac{k}{q} \cdot \ln(p).$$

(2.4)

Thus, the scaling factor is found to be approximately:

$$\alpha \approx \frac{S_{V_{BE}}^T}{\frac{k}{a} ln(p)}.$$

(2.5)

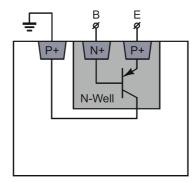

The bipolar transistors that are used for the temperature sensing core are vertical bipolar junction transistors. Vertical PNP BJTs are less prone to processing spread and packaging stress but they are, however, less flexible in terms of implementation. This is due to the collector being inside the P-substrate, and therefore, not directly accessible which is shown in figure 2.4.

The typical forward current gain  $\beta_F$  of a vertical PNP transistor is in the range of 3 to 4, which is rather small compared to the forward current gain of vertical NPN transistors ( $\beta_F \approx 24$ ) ([2], p. 7). This results in a relatively large base current and this in turn in lower sensitivity to non-ideal higher order components in the saturation current I<sub>S</sub> of the BJT. The overall well-defined temperature dependency of V<sub>BE</sub> and  $\Delta V_{BE}$  makes the BJT-based temperature sensor attractive for industrial use. According to [2], temperature sensors with a one-point trim and accuracies of  $\pm 0.5$  °C (3 $\sigma$ ) over a temperature range of -50 °C

to +120 °C, and ±0.1 °C (3 $\sigma$ ) from -55 °C to +125 °C are reported. An additional advantage is that the temperature dependent voltages and the reference voltage are generated from the same circuit which greatly simplifies the implementation ([2], p. 8).

Figure 2.4: Cross section of a vertical PNP transistor in a standard CMOS process ([2], p. 7).

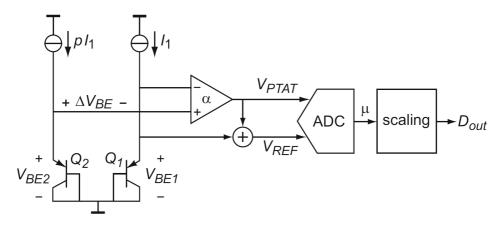

The generic readout of BJT-based sensors scales the generated  $\Delta V_{BE}$  voltage, as was already mentioned in equation 2.3 and shown in figure 2.3. This can be seen in figure 2.5 where the reference voltage and the PTAT voltage are applied to an ADC. The ADC output  $\mu$  is then scaled to generate the according digital temperature reading  $D_{out}$ . The ratio  $\mu$  can be calculated as follows ([2], p. 23)

$$\mu = \frac{\alpha \cdot \Delta V_{BE}}{V_{BE} + \alpha \cdot \Delta V_{BE}} = \frac{V_{PTAT}}{V_{REF}}.$$

(2.6)

This ratio is PTAT and varies between 0 and 1 over a temperature range of 600 K. The digital output  $D_{out}$  can be expressed as

$$D_{out} = A \cdot \mu + B, \tag{2.7}$$

where A = 600 K and B = -273 K ([2], p. 23).

Figure 2.5: Bias core and generic readout circuit of BJT-based bandgap temperature sensors ([2], p. 24).

#### 2.3 Chosen Temperature Sensor

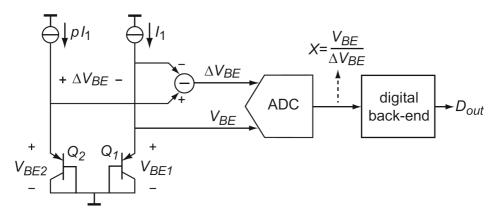

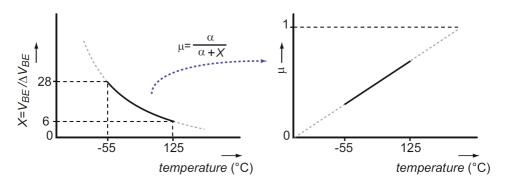

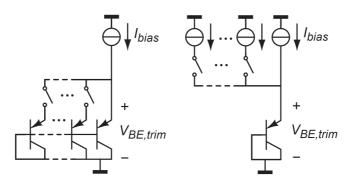

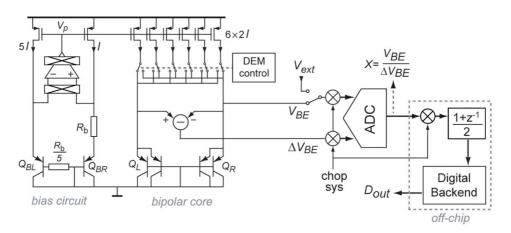

The chosen temperature sensor ([5]) is, as stated in 1.1, based on BJTs and the bandgap reference architecture described in 2.2.4 and shown in figure 2.3. However, instead of generating the reference voltage  $V_{REF} = V_{BE1} + \alpha \cdot \Delta V_{BE}$  it is sufficient to use the ratio  $X = V_{BE1} / \Delta V_{BE}$  which contains all necessary information. A block diagram is shown in figure 2.6.

**Figure 2.6:** Circuit diagram of the proposed sensor. It consists of the bias circuit (not shown), the sensing circuit, the ADC and the digital backend and uses the ratio X to determine the temperature ([2], p. 39.).

The ratio  $X = V_{BE1} / \Delta V_{BE}$  is a non-linear, monotonic function of the temperature for a current density ratio p = 5 (shown in figure 2.7). This temperature dependency can be linearised to:

$$\mu = \frac{\alpha}{\alpha + X},\tag{2.8}$$

and then implemented in the digital backend.

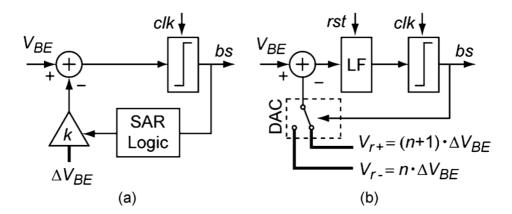

Next to the analog front-end with the biasing and sensing circuits, a 2nd-order Zoom-ADC is existent. It consists of a coarse 5-bit SAR-ADC and a fine 10-bit  $\Delta\Sigma$ -ADC. The Zoom-ADC firstly finds the coarse temperature range which lies between the integers n and n+1. During the coarse conversion phase a clocked comparator compares the base-emitter voltage V<sub>BE</sub> to integer multiples of  $\Delta V_{BE}$ . Five steps are executed in which the SAR-ADC adjusts the scaling factor until the integer n is found. Afterwards, the fine conversion zooms into this range and finds the fraction part of the temperature value. A block diagram of the Zoom-ADC is shown in figure 2.8. Every cycle of the fine conversion requires an integration. The voltages V<sub>BE</sub> and  $\Delta V_{BE}$  are sampled during the same clock cycle and integrated the next cycle. Thus, the conversion time can be reduced by half, which in turn improves the energy efficiency.

**Figure 2.7:** Non-linear, monotonic function of X and the linearised function  $\mu$  as a function of the temperature ([2], p. 40).

The zoom-in phase reduces the complexity of the ADC and the power consumption because it reduces the resolution requirements on the  $\Delta\Sigma$ -ADC. In addition, a second order Zoom-ADC is employed instead of a first order ADC which was done in previous works. This approach shows significant improvements in speed and energy conversion.

Figure 2.8: Block diagram of the Zoom-ADC during a) coarse and b) fine conversion [5].

# Chapter 3

## The Parasitic Vertical PNP BJT

### 3.1 Introduction

Chapter 3 describes the physics and characteristics of bipolar junction transistors. First, a categorisation of random and systematic errors is given in section 3.2. Afterwards in section 3.3, the ideal characteristics of the BJT are described. Hereinafter, the non-idealities of the I-V-Characteristics are explained in section 3.4 which are causing inaccuracies in the currents and voltages. In addition to the non-idealities, processing spreads and temperature dependencies are adding to errors in the temperature reading at the output of the sensor. In the end, the noise model of the BJT and MOSFET will be briefly explained (section 3.7).

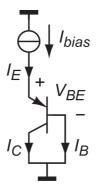

In the literature it is common to use the same sign conventions for PNP as for NPN transistors, also indicated in figure 3.1. This means, the base-emitter voltage of the PNP transistor is called V<sub>BE</sub> and difference voltage  $\Delta V_{BE}$  instead of the technically correct terms V<sub>EB</sub> and  $\Delta V_{EB}$ . Therefore, V<sub>BE</sub> should be read as  $|V_{BE}|$  or V<sub>EB</sub>.

### 3.2 Error Definition

The error sources in a temperature sensor can be distinguished in different categories, systematic errors, random errors and process errors ([1], p. 55, [9], p. 96).

Systematic errors are predictable and the same for each sensor. It is possible to correct them by design. An example for a systematic error is the curvature of the  $V_{BE}$  voltage ([1], p. 55).

Random errors on the other hand are unpredictable and vary from sensor to sensor but they are zero on average. These errors are statistical in nature and are present in each sensor. An example is the mismatch of two transistors that were fabricated under the same nominal conditions ([1], p. 55, [9], p. 96).

Process errors result from the manufacturing process which conditions can never be kept precisely the same (temperature, concentration levels, oxide thickness, etc.). Therefore,

the nominal properties of a circuit differ from sample to sample ([9], p. 96).

#### **3.3 Ideal I-V-Characteristics**

The collector current, and therefore the collector current base-emitter voltage relation of a bipolar junction transistor can be written as ([1], p. 16)

$$I_C = I_S \cdot exp\left(\frac{qV_{BE}}{kT}\right). \tag{3.1}$$

The saturation current  $I_S$  is given by ([1], p. 16)

$$I_S = \frac{qA_E n_i^2 \overline{D_p}}{W_B N_d} = \frac{kT A_E n_i^2 \overline{\mu_p}}{G_B},\tag{3.2}$$

where q is the elementary charge of an electron,  $A_E$  is the emitter area,  $n_i$  is the intrinsic carrier concentration,  $D_p$  is the average diffusion constant of holes in the base,  $W_B$  is the base width and  $N_d$  is the donor concentration. The product  $W_B N_d$  indicates the number of impurities per unit area of the base, and is also called Gummel number  $G_B$ . The effective hole diffusion constant  $\overline{D_p}$  can be expressed as

$$\overline{D_p} = \frac{kT}{q} \cdot \overline{\mu_p}.$$

(3.3)

The variable  $\overline{\mu_p}$  is the effective hole mobility, T is the absolute temperature and k the Boltzmann constant.

By rearranging equation 3.1, it is thus possible to express the ideal base-emitter voltage as follows

$$V_{BE} = \frac{kT}{q} \cdot ln\left(\frac{I_C}{I_S}\right). \tag{3.4}$$

#### **3.4** Non-Idealities of the I-V-Characteristics

In practice, non-ideal currents have to be taken into account that affect the accuracy of the difference voltage  $\Delta V_{BE} = V_{BE2} - V_{BE1}$ .

Generation of carriers in the base-collector junction and diffusion of minority electrons in the collector result in leakage currents. Therefore, the PNP transistors are used in a diode-connected configuration (figure 3.1), where the base-collector voltage is set to zero, which reduces the leakage current to negligible levels ([2], p. 20, [1], p. 17).

To account for these differences in the hole concentration the collector current is thus ([1], p. 17)

$$I_C = I_S \cdot exp\left(\frac{qV_{BE}}{kT} - 1\right). \tag{3.5}$$

Figure 3.1: Diode-connected PNP transistor and the indicated base-emitter voltage drop  $V_{BE}$  ([1], p. 19).

This results in a better approximation of the base-emitter voltage  $V_{BE}$

$$V_{BE} = \frac{kT}{q} \cdot ln\left(\frac{I_C + I_S}{I_S}\right).$$

(3.6)

Accordingly, the difference voltage  $\Delta V_{BE}$  is calculated as follows, by taking the baseemitter voltages of the two PNP transistors in the sensing circuit (compare figure 2.3)

$$\Delta V_{BE} = V_{BE2} - V_{BE2} = \frac{kT}{q} \cdot ln\left(\frac{p \cdot I_C + I_S}{I_S}\right) - \frac{kT}{q} \cdot ln\left(\frac{I_C + I_S}{I_S}\right)$$

$$= \frac{kT}{q} \cdot ln\left(\frac{p \cdot I_C + I_S}{I_S} \cdot \frac{I_S}{I_C + I_S}\right) = \frac{kT}{q} \cdot ln\left(\frac{p \cdot I_C + I_S}{I_C + I_S}\right)$$

(3.7)

The term kT/q is the thermal voltage V<sub>t</sub> which equals around 26 mV at room temperature. Even though the voltage seems to have a positive temperature coefficient, it is actually negative due to the strong temperature dependency of I<sub>S</sub> ([2], p. 21). This will be explained in the sections 3.5 and 3.6.

As long as the collector current  $I_C$  is significantly larger than the saturation current  $I_S$  it is possible to say that

$$\Delta V_{BE} = \frac{kT}{q} \cdot ln(p). \tag{3.8}$$

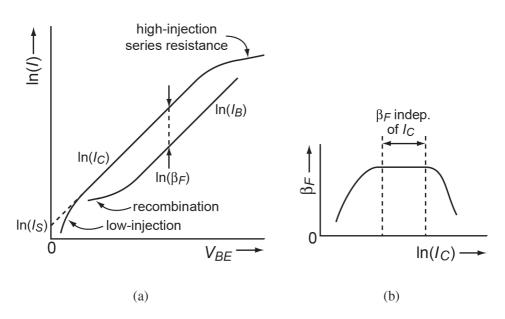

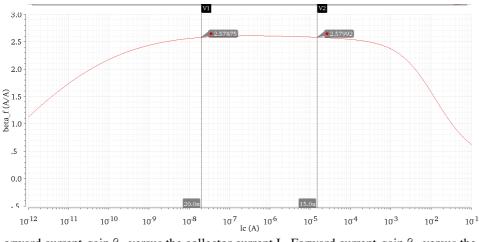

This indicates that the collector current should be chosen as high as possible. However, it cannot be chosen arbitrarily high. Self-heating and a considerable voltage drop across series resistances are results of a current that is too high. According to ([1], p. 17), the second reason is that the transistor would enter the high-injection region. In this region the concentration of the minority carrier is low in comparison to the majority carrier concentration. That means that the logarithm of the collector current  $\ln(I_C)$  becomes proportional to  $qV_{BE}/(2kT)$ . Figure 3.2 shows this effect and the plotted collector current and current-gain.

**Figure 3.2:** a) The collector current  $I_C$  and the base current  $I_B$  are shown as a function of the baseemitter voltage  $V_{BE}$ ; b) the corresponding forward current-gain  $\beta_F$  versus the collector current ([1], p. 18).

Another non-ideality is that the transistor is biased via its emitter node instead of the collector node which makes it necessary to take the base current into account when determining the base-emitter voltage. Diode-connected substrate PNP transistors have their base grounded to make sure that the base-collector voltage is zero. That, however, means that the resulting collector current is smaller than the emitter current ([1], p. 18).

$$I_C = I_E - I_B = \alpha_F \cdot I_E = \frac{\beta_F}{1 + \beta_F} \cdot I_E$$

(3.9)

$\alpha_F$  is the common-base current-gain, and  $\beta_F$  is the common-emitter current-gain, which is equal to  $I_C/I_B$ . The common-base current-gain  $\alpha_F$  is an indicator for how much of the emitter current flows to the collector. It is ideally one.

#### 3.4.1 Series Resistance

The voltages of the BJT are differing because of resistances in the BJT. The base-emitter voltage is a sum of the intrinsic base-emitter voltage  $V_{B'E'}$  and the voltages across the base and emitter resistances,  $R_B$  and  $R_E$ , respectively ([1], p. 36).

$$V_{BE} = V_{B'E'} + I_E R_E + I_B R_B$$

$$V_{BE} = V_{B'E'} + I_E \left( R_E + \frac{R_B}{\beta_F + 1} \right)$$

(3.10)

Combining the base and emitter resistances into a single resistance  $R_S$  in series with the emitter, the base-emitter voltage can be written as follows ([1], p. 36)

$$V_{BE} = \frac{kT}{q} ln \left(\frac{I_{bias}}{I_S}\right) + I_{bias} R_S, \qquad (3.11)$$

where  $I_{bias} = I_E$  and the finite current-gain is ignored. This series resistance affects the difference voltage  $\Delta V_{BE}$ , too

$$\Delta V_{BE} = \frac{kT}{q} \cdot \ln\left(p\right) + I_{bias}\left(p-1\right)R_S.$$

(3.12)

For currents in the range of a few  $\mu A$  or lower, the resulting voltage drop is small enough to be neglected in comparison to  $V_{BE}$ . But for  $\Delta V_{BE}$  it can be significant.

#### **3.4.2 Early Effects**

There are two Early effects in the BJT that affect the base-emitter voltage  $V_{BE}$ , the forward and reverse Early effect.

A voltage drop across the base resistance  $R_B$  and the collector resistance  $R_C$  results in a non-zero base-collector voltage which in the end affects the effective base width  $W_B$  of the transistor. Thus, it causes the collector current of a BJT to depend on the base-collector voltage. Typically, this forward Early voltage is quite large (according to [1] around 100 V) which is why this effect is usually negligible ([1], p.38).

The reverse Early effect also has an impact on the base width which changes the collector current  $I_C$ . It introduces a multiplicative error in the base-emitter voltage  $V_{BE}$ . However, if the temperature sensor uses a ratiometric measurement which is common for smart temperature sensors, then the multiplicative error cancels due to division of the base-emitter voltages ([1], p. 39).

#### **3.5** Temperature Dependencies

#### 3.5.1 Saturation Current

The base-emitter voltage  $V_{BE}$  is affected by the temperature dependency of the saturation current  $I_S$ . The saturation current has several temperature dependencies as following equation shows

$$I_S = \frac{kTAn_i^2(T)\overline{\mu_p}(T)}{G_B(T)}.$$

(3.13)

As can be seen, the intrinsic carrier concentration  $n_i$ , the effective hole mobility  $\overline{\mu_p}$  and the Gummel number  $G_B$  are temperature dependent in different ways. Therefore, the saturation current can be written as ([2], p. 20, [1], p. 21)

$$I_S(T) = CT^{\eta} exp\left(-\frac{qV_{g0}}{kT}\right),\tag{3.14}$$

17

where C is a constant,  $\eta = 4$  - n, and  $V_{g0}$  is the extrapolated bandgap voltage at 0 K. Inserting 3.14 into 3.1 results in

$$I_C(T) = CT^{\eta} exp\left(\frac{q(V_{BE}(T) - V_{g0})}{kT}\right).$$

(3.15)

Rearranging this expression yields:

$$V_{BE}(T) = V_{g0} + \frac{kT}{q} \cdot ln\left(\frac{I_C(T)}{CT^{\eta}}\right).$$

(3.16)

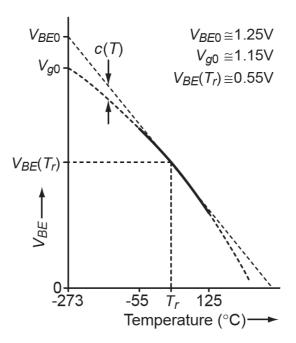

In figure 3.3 which is taken from [1], the curvature of the base-emitter voltage is figuratively depicted. The variable  $V_{BE0}$  is the extrapolated bandgap voltage without curvature at T = 0 K,  $V_{g0}$  is the extrapolated bandgap voltage with curvature at T = 0 K and  $V_{BE}(T_r)$ is the base-emitter voltage at a reference temperature of T = 300 K.

Figure 3.3: The temperature dependency of the base-emitter voltage  $V_{BE}$  ([1], p. 23).

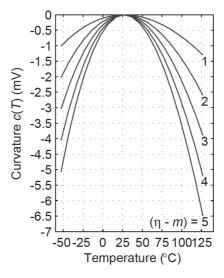

In [1] it is described that the curvature for a collector current that exhibits PTAT behaviour can be calculated as follows

$$c(T) = \frac{k}{q} \cdot (\eta - m) \left( T - T_r - T \cdot ln \left( \frac{T}{T_r} \right) \right).$$

(3.17)

Figure 3.4 shows different curvatures for different values of  $(\eta - m)$ . In the Spectre model of the 90nm process kit used for this work, the variables  $V_{g0}$  and  $\eta$  are called EG and XTI, respectively. The bandgap voltage EG = 1.11 V, and XTI = 3. Therefore, the curve for  $(\eta - m)$

m) = 2 (for m = 1, because the collector current  $I_C$  is proportional to  $T^1$ ) is valid. However, this should be understood as a rough estimate.

Figure 3.4: Curvature of  $V_{BE}$  for different values of  $(\eta - m)$  ([1], p. 23).

# 3.5.2 Current Gain

The common-base current (equation 3.9) is temperature dependent and can vary significantly which has to be taken into account when the temperature dependency of  $V_{BE}$  is derived. Taking equation 3.9 and adding the temperature dependence of  $\beta_F$

$$\alpha_F(T) = \frac{\beta_F(T)}{1 + \beta_F(T)},\tag{3.18}$$

where  $\beta_F$  can be written as

$$\beta_F(T) = \beta_{F0} \left(\frac{T}{Tr}\right)^{X_{TB}}.$$

(3.19)

The term  $\beta_{F0}$  is the nominal current-gain,  $T_r$  is a reference temperature and  $X_{TB}$  is a temperature exponent found by fitting the equation to measured data ([1], p. 24).

This temperature dependency of  $I_C(T) = \alpha_F(T)I_E(T)$  results in an additional term in  $V_{BE}(T)$

$$V_{BE}(T) = V_{BE}(T)|_{\alpha_F = constant} + \frac{kT}{q} \cdot ln\left(\frac{\alpha_F(T)}{\alpha_F(T_r)}\right)$$

$$= V_{BE}(T)|_{\alpha_F = constant} + \frac{kT}{q} \cdot ln\left(\frac{\left(1 + \beta_{F0}\right)\left(\frac{T}{T_r}\right)^{X_{TB}}}{1 + \beta_{F0}\left(\frac{T}{T_r}\right)^{X_{TB}}}\right).$$

(3.20)

With the aid of compensation techniques it is possible to reduce the additional term in  $V_{BE}$  to negligible levels ([1], p. 24).

#### 3.5.3 Bias Resistor

The bias resistor in the biasing circuit affects the collector current, too. The collector current is dependent on the temperature dependency of the bias voltage and the bias resistor. The collector current can therefore be written as

$$I_C(T) = \frac{V_{bias}(T_r)}{R_{bias}(T)} \left(\frac{T}{T_r}\right)^m,$$

(3.21)

where the bias voltage  $V_{bias}$  is assumed to be proportional to a power of T ([1], p. 42). This temperature dependency of the bias resistor results in an additional term in  $V_{BE}(T)$  ([1], p. 42):

$$V_{BE}(T) = V_{BE}(T)|_{R_{bias} = constant} - \frac{kT}{q} ln(1 + \alpha_{TCR1}(T - T_r) + \alpha_{TCR2}(T - T_r)^2).$$

(3.22)

The variables  $\alpha_{TCR1}$  and  $\alpha_{TCR2}$  are the first- and second-order temperature coefficients. The contribution of the second-order coefficient is usually small enough to be ignored. The first-order coefficient on the other hand can have a quite significant effect on the baseemitter voltage and its curvature. This effect can have both, negative and positive effects on the curvature. For negative values of  $\alpha_{TCR1}$  the curvature of V<sub>BE</sub> is reduced. However, for positive values the curvature is increased ([1], p. 43).

# **3.6 Processing Spread**

#### 3.6.1 Preface

Every chip is subject to processing spread which affects the performance of the devices. The temperature under which the manufacturing steps are done can vary, or the concentration of elements that is introduced differs from chip to chip ([9], p. 98). Even though it is attempted to minimise the variations during the fabrication there will always be some spread, and this spread can be significant. In [9] it is stated that device parameter variations

can occur that are equal to, for example, a change of 100 mV in the threshold voltage  $V_{th0}$ . This section describes the processing spread of the saturation current and current gain and its effect on the base-emitter voltage  $V_{BE}$ .

#### 3.6.2 Saturation current

The saturation current  $I_S$  is not only dependent on temperature variations but is also subject to processing spread. This becomes clear when equation 3.2 is examined, which is repeated here

$$I_S = \frac{kTAn_i^2 \overline{\mu_p}}{W_B N_p}.$$

(3.23)

The base doping  $N_d$  depends on tolerances in the manufacturing process. An n-well forms the base region and its spread can be estimated by using the n-well sheet resistance which can vary up to 50 %, according to ([1], p. 29). Such variations would result in similar changes in  $I_S$  and variations in  $V_{BE}$  up to  $\pm 13$  mV. Usually however, the spread is much smaller.

The base width  $W_B$  differs from the ideal value because of lithographic errors and variations in the depth of diffusions. Spreads in the area can result in changes of  $V_{BE}$  of up to  $\pm 0.25$  mV. The base width is determined by the difference in the depth between the base and the emitter diffusions. It is typically small to optimise the current gain ([1], p. 30).

The intrinsic carrier concentration  $n_i$  and  $\overline{\mu_p}$  are both subject to variations due to mechanical stress ([1], p. 30). The mechanical stress will not be further investigated in this thesis.

The spread of the base-emitter voltage  $V_{BE}$  due to the spread in the saturation current  $I_S$  can therefore be expressed as follows ([1], p. 29)

$$V_{BE} = \frac{kT}{q} \cdot ln \left( \frac{I_C}{I_S + \Delta I_S} \right)$$

=  $\frac{kT}{q} \cdot ln \left( \frac{I_C}{I_S} \right) - \frac{kT}{q} \cdot ln \left( 1 + \frac{I_S}{\Delta I_S} \right)$

$\approx V_{BE}|_{\Delta I_S = 0} - \frac{kT}{q} \frac{\Delta I_S}{I_S},$  (3.24)

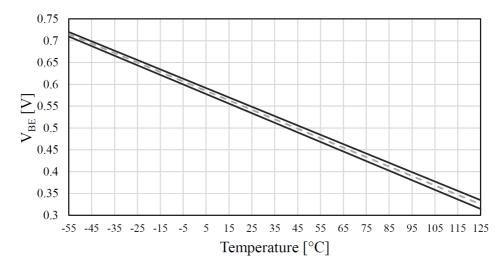

where the approximation  $\ln(1 + x) = x$  for  $x \ll 1$  is used. For the used process kit gpdk090 this V<sub>BE</sub> spread results in a change of up to  $\pm 10$  mV over the temperature range of -50 °C to 125 °C. This is shown in figure 3.5. The dotted line indicates the normal base-emitter voltage without process spread. The two black lines indicate the process spread for the worst cases which are retrieved by using corner simulations.

As was already stated, these process variations persist and are random which is why they cannot be controlled by the circuit designer. It is necessary to expect at least a few mV of  $V_{BE}$  spread. This will result in significant errors in the temperature accuracy of the sensor which have to be trimmed. The sensitivity analysis is done in chapter 5.6.

Figure 3.5: Spread of  $V_{BE}$  due to processing spread of the saturation current  $I_S$  for a PNP BJT in gpdk090nm.

#### 3.6.3 Current Gain

The common-base current gain  $\alpha_F$  (see 3.4) is also subject to processing spread which results in spread of V<sub>BE</sub>. This can written as ([1], p. 31)

$$V_{BE} = \frac{kT}{q} \cdot ln\left(\frac{(\alpha_F + \Delta\alpha_F)I_E}{I_S}\right)$$

=  $\frac{kT}{q} \cdot ln\left(\frac{\alpha_F I_E}{I_S}\right) + \frac{kT}{q} \cdot ln\left(1 + \frac{\Delta\alpha_F}{\alpha_F}\right)$

$\approx V_{BE}|_{\Delta\alpha_F=0} + \frac{kT}{q}\frac{\Delta\alpha_F}{\alpha_F}$  (3.25)

This shows that the spread in the current gain  $\alpha_F$  affects  $V_{BE}$  similarly as the saturation current  $I_S$ . If the current gain was independent of the temperature, it would result in a PTAT spread in  $V_{BE}$  that could be trimmed out. However,  $\Delta \alpha_F / \alpha_F$  is likely dependent on the temperature because of the spread in different base-current components. Thus, the resulting spread is not PTAT and cannot be fully removed by trimming ([1], p. 32).

#### 3.6.4 Bias Resistor

Due to processing spread the nominal value and the temperature dependency of the resistor will vary. The spread in  $V_{BE}$  due to the bias resistor adds directly to the spread as a result of the spread in the saturation current. The base-emitter voltage can be written as ([1], p. 43)

$$V_{BE} = V_{BE}(T)|_{R_{bias}=constant} - \frac{kT}{q} ln\left(\frac{R_{bias} + \Delta R_{bias}}{R_{bias}}\right)$$

=  $V_{BE}(T)|_{R_{bias}=constant} - \frac{kT}{q} \frac{\Delta R_{bias}}{R_{bias}}.$  (3.26)

The resistor value  $R_{bias}$  can be determined by taking the sheet resistance  $R_{sh}$  and the resistor's length and width:

$$R_{bias} = R_{sh} \frac{L}{W}.$$

(3.27)

It is possible to decrease the spread of the length and width ratio to negligible levels by making W several times larger than the minimum width ([1], p. 43). This means that the spread of the bias resistor is only dependent of the sheet resistance which is subject to spread in the doping and thickness of the resistive layer and other parameters ([1], p. 43). If the spread  $\Delta R_{\text{bias}}/R_{\text{bias}}$  is temperature independent it would be PTAT. Such a spread can be trimmed out based on a temperature calibration. However, in practice the temperature coefficients of resistors depend on the doping level and other parameters. Therefore, it is not possible to say that the bias resistor spread is PTAT. To be able to trim out the effects of the spread it is necessary to measure the absolute value of the resistor and determine the temperature coefficients. ([1], p. 45)

# 3.7 Noise-Model

#### 3.7.1 Types of Noise

There are various noise sources in electronic circuits. The three most important noise sources are *thermal noise*, *flicker noise* and *shot noise*.

The *thermal noise* is related to the random motion of electrons in a conductor. It has a white spectral density and is directly proportional to the absolute temperature. This type of noise occurs in all resistors and semiconductors. Thermal noise is always existent above the absolute zero temperature also when there is no current present. It is therefore unaffected by the bias conditions of the system. This noise imposes fundamental limits on the dynamic range achievable in electronic circuits. ([9], [10], [11])

*Flicker noise* is existent in every active device. However, contrary to the thermal noise, it only occurs if a dc current is flowing. This kind of noise arises because some carriers are trapped in the semiconductor for some time period and then released. It can be modelled with a dependency of 1/f, where f is the frequency. This shows that the flicker noise is most significant at low frequencies. ([9], [10], [11])

*Shot noise* occurs in pn-junctions and appears because a dc current is not continuous or smooth but rather a consequence of pulses induced by the flow of individual carriers. Therefore, it is dependent on the dc bias current and is typically larger than thermal noise. It can also be modelled as a white noise source. ([9], [11])

#### 3.7.2 Noise in BJTs

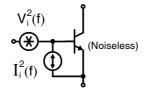

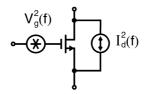

The noise of bipolar transistors is a result of shot noise in the collector and the base currents, flicker noise of the base current and thermal noise of the base resistance. All noise sources are independent of each other and can therefore be summed. The mean-square values of the different noise sources are usually combined in two equivalent noise sources at the base of the BJT, see figure 3.6. The input voltage noise  $V_i(f)$  is given by ([9], p. 380)

$$\frac{V_i^2(f)}{\Delta f} = 4kT\left(r_b + \frac{1}{2g_m}\right),\tag{3.28}$$

where  $\Delta f$  is the bandwidth, k is the Boltzmann constant, T the absolute temperature,  $r_b$  is the base resistance and the  $g_m$  term is due to the shot noise in the collector current referred back to the input. The second source is the equivalent input current noise,  $I_i$  ([9], p. 380)

$$\frac{I_i^2(f)}{\Delta f} = 2q \left( I_B + \frac{k_f I_B}{f} + \frac{I_C}{|\beta(f)|^2} \right),$$

(3.29)

where q is the electron charge, the term  $2qI_B$  is the base current shot noise, the  $k_f I_B/f$  term is the flicker noise (k<sub>f</sub> is a process dependent parameter), and the  $I_C/|\beta(f)|^2$  term is the input-referred collector current shot noise which is often ignored.

Typically, the noise in a BJT is dominated by thermal noise due to the series base resistance and shot noise in the base-current junction.

Figure 3.6: Noise sources of a BJT ([9], p.379).

### 3.7.3 Noise in MOSFETs

The noise in MOSFETs is typically dominated by flicker and thermal noise and is modelled as a noise-voltage source at the gate of the MOSFET and noise-current source from drain to source, which can be seen in figure 3.7.

The voltage source at the gate models the flicker noise as follows ([9], p. 380)

$$\frac{V_g^2(f)}{\Delta f} = \frac{k_f}{WLC_{ox}f},\tag{3.30}$$

where  $k_f$  is again the process dependent parameter, W is the width, L the length and  $C_{ox}$  the oxide capacitance of the transistor. The 1/f-noise in MOSFETs typically dominates at low frequencies and is therefore very important. As equation 3.30 indicates larger devices

have lower flicker noise, and in addition, the flicker noise in PMOS devices is lower than in their counterparts, the NMOS.

The thermal noise is due to the resistive channel of the MOSFET in the active region and can be modelled as ([9], p. 381)

$$\frac{I_d^2(f)}{\Delta f} = 4kT\gamma g_m,\tag{3.31}$$

where  $\gamma$  is the white noise parameter and equal to 2/3 for long-channel devices. For short gate-length devices much higher values are possible.

Figure 3.7: Noise sources of a MOSFET ([9], p. 379).

# Chapter 4

# Compensation and Correction Techniques

# 4.1 Introduction

Chapter 4 gives insight into advanced circuit techniques to reduce errors introduced by random and systematic errors that were discussed in chapter 3. Different techniques are mentioned and explained that address different errors in the system to reduce them to acceptable levels.

# 4.2 Compensation for Finite Current Gain

In chapter 3.5.2 it was explained that the error of the current gain affects the base-emitter voltage  $V_{BE}$  of the PNP transistor. The collector current  $I_C$  of a BJT depends on the forward current gain  $\beta_F$  and therefore it might be obvious to control the collector current in some way instead of the emitter current. However, since the collector node of substrate PNP transistors is grounded this could only be done indirectly ([1], p. 92).

Therefore, an alternative is employed to reduce the error due to finite current gain. A resistor is added to the base of the PNP transistor  $Q_{BL}$  (see figure 5.2) with the higher current in the bias circuit. Due to the feedback loop the input voltage of the op amp is zero, and thus ([1], p. 93)

$$V_{BE,QBL} + I_{bias}R_b = mI_{bias}\frac{1}{1+\beta_F}\frac{R_b}{m} + V_{BE,QBR}.$$

(4.1)

Solving this equation for Ibias results in

$$I_{bias} = \frac{1 + \beta_F}{\beta_F} \frac{V_{BE,QBR} - V_{BE,QBL}}{R_b} = \frac{1 + \beta_F}{\beta_F} \frac{\Delta V_{BE}}{R_b}.$$

(4.2)

Applying this current to the emitter of the BJT results in a base-emitter voltage of

$$V_{BE} = \frac{kT}{q} ln \left( \frac{I_b}{I_S} \frac{\beta_F}{\beta_F + 1} \right) = \frac{kT}{q} ln \left( \frac{\Delta V_{BE}}{R_b I_S} \right).$$

(4.3)

Now the base-emitter voltage is independent of  $\beta_F$ . In practice, the base resistance of  $Q_{BL}$  has to be taken into account because it adds to the resistor  $R_b/m$  ([1], p. 94)

# 4.3 Chopping

The offset at the input of the op amp is a significant source of inaccuracy in the system. CMOS amplifiers usually exhibit offset voltages in the mV range which is caused by transistor mismatch in the input pair of the differential amplifier. This mismatch can be reduced by using larger transistors but to achieve offset levels in the  $\mu$ V range it is necessary to employ offset cancellation techniques, such as chopping. The chopping technique is a dynamic process that is able to not only remove the offset of the amplifier but also 1/f-noise, as well as offset drift ([1], p. 175).

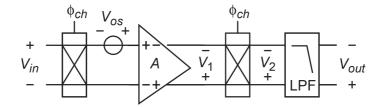

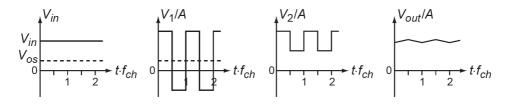

The principle of this technique is shown in figures 4.1 and 4.2. The input signal  $V_{in}$  is passed through a switch (see figure 4.3), which can be implemented as a transmission gate, that changes the polarity of the inputs of the differential amplifier. This switch is driven by a clock signal  $\varphi_{ch}$ . Because of the periodically switched polarity of the inputs the signal  $V_{in}$  is modulated by a square wave. This modulated signal is then passed through the differential amplifier with the offset  $V_{os}$ . At the output of the amplifier the input signal is found at the harmonics of  $\varphi_{ch}$  and the amplified offset voltage is found at DC. A second chopping demodulates the amplified signal back to DC and modulates the offset to the harmonics of  $\varphi_{ch}$ . The harmonics are then filtered out by a low-pass filter which leaves the amplified input signal without the offset ([1], p. 176).

**Figure 4.1:** A chopper amplifier. Containing two chopper switches, the amplifier and a low-pass filter ([1], p.177).

The duty cycle of the chopping switch control signal needs to be exactly 50 % to average out the offset voltage.

The residual offset of chopper amplifiers is due to charge injection and clock feed-through in the chopper switches which results in voltage spikes. If these voltage spikes are at the input or output of the amplifier they will be demodulated by the second chopper which appears as an average DC offset. This offset is typically in the range of a few tens of  $\mu V$ .

Figure 4.2: The voltages V<sub>in</sub>, V<sub>os</sub>, V<sub>1</sub>, V<sub>2</sub> and V<sub>out</sub> as function of time ([1], p.177).

([1], p. 179)

The residual offset can be reduced by reducing the switching frequency  $f_{ch}$  of the chopping switches. This results in less voltage spikes. However, this is limited by the corner frequency of the flicker noise because if the frequency  $f_{ch}$  is lower than the corner frequency of the flicker noise it will not be entirely averaged out.

Figure 4.3: The chopper switch. Taken from ([1], p.177).

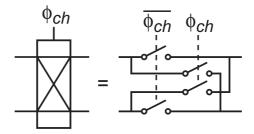

# 4.4 Dynamic Element Matching

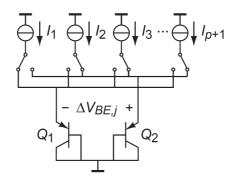

Dynamic element matching is a technique to reduce errors due to mismatch. If, for example, six current sources are used to generate a bias current ratio of 1:5, where each current source generates the unit current then the voltage  $\Delta V_{BE}$  will have six possible values. This is due to the mismatch between the current sources. It is possible to average out the error of the mismatch which results in an error of almost zero. Figure 4.4 shows a possible implementation of dynamic element matching for current sources. It shows that each current can be directed to the bipolar transistors Q<sub>1</sub> or Q<sub>2</sub>. If current I<sub>n</sub>, (where  $1 \le n \le p + 1$ ) flows through Q<sub>1</sub> and the remaining currents through Q<sub>2</sub> then the generated difference voltage  $\Delta V_{BE}$  is equal to ([1], p. 60)

$$\Delta V_{BE,n} = \frac{kT}{q} \cdot ln\left(\frac{\sum_{i \neq n} I_i}{I_n}\right) = \frac{kT}{q} \cdot ln(p + \Delta p_n).$$

(4.4)

The mismatch between the currents  $I_n$  and the average of the remaining currents is  $\Delta p_n$  / p.

The average of the p + 1 possible difference voltages  $\Delta V_{BE}$  can be computed as follows ([1], p. 60)

$$\Delta V_{BE,avg} = \frac{1}{p+1} \sum_{n=1}^{p+1} \Delta V_{BE,n}.$$

(4.5)

According to [1] this technique cancels the first-order errors but a second-order error is still existent. The second-order error can be expressed as

$$\left|\Delta V_{BE,avg} - \Delta V_{BE|\Delta p=0}\right| < \frac{1}{2} \frac{kT}{q} \left(\frac{\Delta p}{p}\right)^2,\tag{4.6}$$

where  $\Delta p / p$  is the worst-case mismatch between the currents. Dynamic element matching can be easily implemented and reduces errors to levels of a few  $\mu V$  in  $\Delta V_{BE}$ .

The same procedure can be employed to reduce mismatch errors in the bipolar transistors. However, if only two transistors are used with the same emitter area then it is possible to completely eliminate the mismatch error between the transistors without any additional switches in series. It is enough if the circuit from figure 4.4 is used. This is due to the fact that the difference voltage  $\Delta V_{BE}$  is the difference between two  $\Delta V_{BE}$  voltages that are generated by the same current  $I_n$  flowing through  $Q_1$  first and then  $Q_2$ . The resulting  $\Delta V_{BE}$  can be written as ([1], p. 62)

$$\Delta V_{BEA,n} - \Delta V_{BEB,n} = 2 \cdot \frac{kT}{q} ln(p + \Delta p_n).$$

(4.7)

The error is then removed by averaging the p + 1 difference voltages as is done in equation 4.5. It takes 2(p + 1) steps to run through the entire DEM process which results in an overall average that is free from first-order mismatch errors.

Figure 4.4: Principle of dynamic element matching for current sources to generate an accurate  $\Delta V_{BE}$  ([1], p. 61).

# 4.5 Curvature Correction

In section 3.5 it was described that the base-emitter voltage is experiencing a curvature due to the temperature dependency of the collector current, see equations 3.16 and 3.17. There are many ways to correct the curvature of the base-emitter voltage, therefore, only a small selection is presented here.

One way of reducing the curvature of  $V_{BE}$  is to use a bias current that is dependent of the temperature since the saturation current  $I_S$  is the reason of the curvature in the first place. The bias current is proportional to  $T^m$ , as can be seen in equation 3.17 which leads to the curvature in  $V_{BE}$  to be proportional to  $(\eta - m)$ . If the bias current is also dependent on the temperature, for example, as a PTAT/R current then the bias current is proportional to  $T^1$ , with m = 1. The outcome is a smaller curvature of the base-emitter voltage ([1], p. 81).

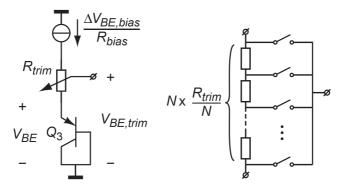

It is possible to make the bias current proportional to  $m \approx \eta$ . This would cancel the majority of the curvature. However, this technique is hard to implement in standard CMOS processes.