## Embla Trasti Bygland

# Power Modeling of Complex Designs

Master's thesis in Electronics Systems Design and Innovation Supervisor: Snorre Aunet, Knut Austbø July 2020

nology ctrical Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Embla Trasti Bygland

# **Power Modeling of Complex Designs**

Master's thesis in Electronics Systems Design and Innovation Supervisor: Snorre Aunet, Knut Austbø July 2020

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

## Abstract

In this project, a tool for making power models of designs at the Register Transfer Level (RTL) is implemented. The generated power model is intended to be used with a power estimation tool, to give an early, fast and accurate power estimate. Nordic Semiconductor ASA issues this masters project with the motivation of making RTL simulations power-aware. Discovering power bugs early in the implementation of a design may save iterations in the Application Specific Integrated Circuit (ASIC) design flow, and thus reduce time to market for a product.

The method for estimating power at the RTL called the top-down method was chosen for the implementation. Among other desired qualities, it does not require a gate-level representation of the design to produce a power estimate. This allows for power estimation to be done concurrently to simulations for functional verification of the RTL, before synthesis of the design.

The power modeling problem is divided into three tasks:

- 1. Extracting structural information from an elaborated SystemVerilog representation of the design.

- 2. Extracting information about available cells and their power consumption characteristics from the cell library.

- **3.** Combining the structural representation with the cell- and power information retrieved, in order to create a power model.

In the implementation, the structure of the design is represented by a node tree, while a cell library object was created to represent available cells from the cell library and their power data. In order to produce a power model, the implementation takes sequences of generic cells from the structure tree and replace them with cells obtained from the cell library. The power model consists of several power-aware node trees. The power model representation is more similar to the gate-level netlist than the elaborated SystemVerilog representation. However, more work is needed to obtain a proper comparison between them.

The implementation shows promise for accurate and fast power estimation. Several ab-

stractions are done in the process so that fast estimations can be made, and their effect on the power consumption have been evaluated together with other alternatives. When creating the power-aware node tree, cells from the generic cell library are grouped to more complex cells from the cell library. This grouping ensures a reduction in the number of cells, which brings the model closer to the gate-level representation.

Some work remains to complete the power model; the most complex generic cells from the elaborated SystemVerilog file need to be constructed from several cells from the cell library. Complex cells with no equivalent yet are those representing arithmetic operations, shifters and comparators. When these cells have a representation, switching activity can be propagated through the structure trees in order to get a power consumption estimate for each of them. The final job of the power estimation tool is to solely use the activity data from the RTL simulation, together with the power values from each structure tree to yield the power estimate.

## Sammendrag

I dette prosjektet implementeres et verktøy for å lage effektmodeller av RTL design. Den genererte effektmodellen er ment å brukes sammen med et effektestimeringsverktøy for å gi et tidlig, raskt og nøyaktig effektestimat. Nordic Semiconductor ASA utsteder dette masterprosjektet med motivasjonen å gjøre RTL simuleringer effektbevisste. Å oppdage power bugs tidlig i implementeringen av en design kan spare iterasjoner i ASIC designflyten, og dermed redusere tiden som kreves for å få et produkt på markedet.

Metoden for å estimere effekt på RTL kalt top-down metoden ble valgt for implementeringen. Blant andre ønskede kvaliteter krever det ikke en syntetisert nettliste-representasjon av designet for å produsere et effektestimat. Dette gjør at effektestimering kan gjøres samtidig med simuleringer for funksjonell verifisering av RTL, før syntesen av designet.

Effektmodelleringen er delt inn i tre deler:

- 1. Hente ut strukturell informasjon fra en prosessert SystemVerilog representasjon av designet.

- 2. Hente ut informasjon om tilgjengelige celler og deres effektforbruk fra cellebiblioteket.

- **3.** Kombinere den strukturelle representasjonen med celle- og effektinformasjonen, og lage en effektmodell.

I implementasjonen er strukturen til et design representert av et nodetre, mens et cellebibliotekobjekt er laget for å representere tilgjengelige celler fra cellebiblioteket og effektforbruket deres. For å produsere en effektmodell tar implementasjonen sekvenser av generiske celler fra strukturtreet og erstatter dem med celler hentet fra cellebiblioteket. Effektmodellen består av flere effektbevisste nodetrær. Den effekt-bevisste representasjonen har mange likheter med den syntetiserte nettlisten. Dog, mer arbeid er nødvendig for å lage en god sammenligning mellom representasjonene.

Implementasjonen er lovende for nøyaktig og rask høy-nivås estimering av effektforbruk. Flere abstraksjoner blir gjort i prosessen slik at estimasjonen er rask. Hvordan abstraksjonene påvirker effektestimatet er evaluert sammen med andre alternativer. Når et effektbevisst nodetre lages, grupperes generiske celler til mer komplekse celler fra cellebiblioteket. Denne grupperingen gjør at antall celler i representasjonen reduseres, noe som bringer modellen nærmere den syntetiserte nettlisten.

Noe arbeid gjenstår for å gjøre effektmodellen komplett; flere komplekse generiske cellene fra den prosesserte SystemVerilog-filen må settes sammen av tilgjengelige celler fra cellebiblioteket. Komplekse generiske celler som ennå ikke har noen ekvivalent effektbevisst representasjon er de som representerer aritmetiske operasjoner, skiftere og komparatorer. Når disse generiske cellene har en representasjon i effektmodellen, kan signaler propageres gjennom strukturtrærne, og et effektestimat lages for hvert nodetre. Jobben til effektestimeringsverktøyet som skal bruke effektmodellen er å kombinere aktivitetsdata fra en RTLsimulering med effektverdiene fra hvert nodetre i et vilkårlig design, og gi et effektestimat for designet.

## Preface

This Master's Thesis concludes a five-year M.Sc. degree at the Norwegian University of Science and Technology (NTNU) at the programme Electronics Systems Design and Innovation, with a specialisation in Design of Digital Systems.

Preliminary research was done during the fall semester of 2019, which resulted in an unpublished literary review on Register Transfer Level power estimation. Methods discussed in this review are reconsidered, and one method is selected for the implementation of a power model.

The thesis is written in cooperation with Nordic Semiconductor ASA. They have contributed with the required Synopsys licenses, a workplace with a computer, and a wonderful supervisor Knut Austbø, who does not seem to mind late-night readthroughs of text with too few commas in it. I also had great supervision from Snorre Aunet from the Institute of Electronic Systems at NTNU. They both have my gratitude.

I would also like to thank my friends from my study programme for providing companionship and focus through video chat during long days of working from home. I am grateful for their help, and the opposite of grateful to the corona virus and the backache working from my kitchen table has given me.

Lastly, I wish to thank my mom, and if there is a Best Mom Award given by any reader of this thesis, I hereby nominate her.

# Contents

| Al | bstra  | $\operatorname{ct}$                      | i |

|----|--------|------------------------------------------|---|

| Sa | mme    | endrag ii                                | i |

| Pı | reface |                                          | v |

| Co | onter  | ts                                       | v |

| G  | lossa  | x x                                      | i |

| A  | crony  | rms xii                                  | i |

| 1  | Intr   | oduction                                 | 1 |

|    | 1.1    | Motivation                               | 1 |

|    | 1.2    | Problem description                      | 3 |

|    | 1.3    | Report structure                         | 4 |

| 2  | The    | ory                                      | 7 |

|    | 2.1    | Terminology                              | 7 |

|    | 2.2    | The ASIC design flow                     | 8 |

|    | 2.3    | CMOS power consumption                   | ) |

|    |        | 2.3.1 Dynamic power consumption          | ) |

|    |        | 2.3.2 Static power consumption           | 2 |

|    | 2.4    | Process, Voltage and Temperature corners | 2 |

| 3  | Bac    | kground 1                                | 5 |

|    | 3.1    | Bottom-up power estimation               | ĵ |

|    | 3.2    | Top-down power estimation                | 7 |

|    |        | 3.2.1 Fast synthesis power estimation    | 9 |

|    | 3.3    | Prestudy                                 | ) |

| 4  | Sug    | gesting a solution 23                    | 3 |

|    | 4.1    | Structural information                   | 5 |

|    | 4.2    | Cell library information                 | 5 |

|   | 4.3            | The p   | ower modeling flow                             | 26 |

|---|----------------|---------|------------------------------------------------|----|

| 5 | Des            | ign to  | ols and file formats                           | 29 |

|   | 5.1            | Design  | n elaboration                                  | 29 |

|   | 5.2            | Libert  | y file format                                  | 33 |

|   |                | 5.2.1   | Power characteristics                          | 33 |

|   |                | 5.2.2   | Power related library attributes and groups    | 36 |

|   |                | 5.2.3   | Cell attributes and groups                     | 37 |

|   |                | 5.2.4   | Pin attributes and groups                      | 38 |

|   | 5.3            | Test fi | iles and modules                               | 39 |

|   |                | 5.3.1   | Test modules                                   | 39 |

|   |                | 5.3.2   | Calibration netlist                            | 39 |

|   |                | 5.3.3   | Liberty file                                   | 39 |

|   |                | 5.3.4   | Project files                                  | 39 |

| 6 | $\mathbf{Ext}$ | racting | g design structure                             | 41 |

|   | 6.1            | Elabo   | rated SystemVerilog                            | 42 |

|   | 6.2            | Struct  | ural representation of a design                | 43 |

|   | 6.3            | Abstra  | actions made                                   | 45 |

|   | 6.4            | Elabo   | rated SystemVerilog parser implementation      | 46 |

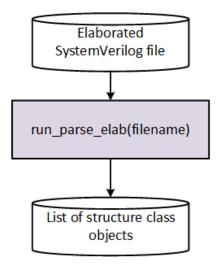

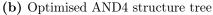

|   |                | 6.4.1   | Parsing                                        | 47 |

|   |                | 6.4.2   | Post-processing                                | 47 |

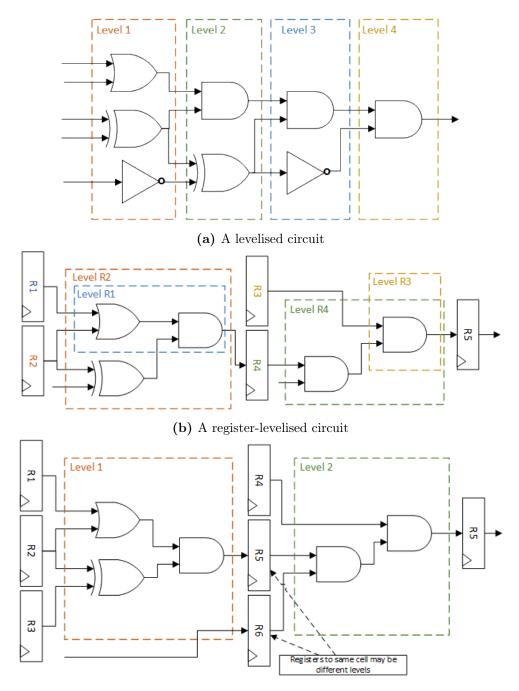

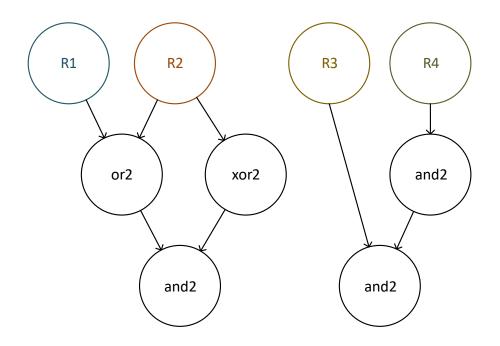

|   |                | 6.4.3   | Register levelised structure trees             | 48 |

|   | 6.5            | Comp    | aring cell counts                              | 49 |

|   | 6.6            | Struct  | ural representation discussion                 | 51 |

|   |                | 6.6.1   | Cell counts                                    | 51 |

|   |                | 6.6.2   | The register-levelised node tree               | 52 |

|   |                | 6.6.3   | Abstractions introduced by generic cell groups | 53 |

|   |                | 6.6.4   | Registers being optimised away                 | 53 |

|   |                | 6.6.5   | Possible optimisations                         | 54 |

| 7 | $\mathbf{Ext}$ | racting | g library information                          | 55 |

|   | 7.1            | Releva  | ant power data                                 | 56 |

|   | 7.2            | Abstra  | actions                                        | 56 |

|   |                | 7.2.1   | The difference between fall- and rise power    | 56 |

|   |                | 7.2.2   | The difference between data input pins         | 57 |

|   |                |         |                                                |    |

| в  | Tecl | nnical  | implementation of the liberty parser                                                                                          | B-1  |

|----|------|---------|-------------------------------------------------------------------------------------------------------------------------------|------|

| Α  | Tecl | nnical  | implementation of the elaborated SystemVerilog parser                                                                         | A-1  |

|    | 10.2 | Impler  | menting a power estimation tool                                                                                               | . 87 |

|    |      |         | ing the power model                                                                                                           |      |

| 10 | Futu | ure wo  | rk                                                                                                                            | 87   |

| 9  | Con  | clusio  | n                                                                                                                             | 85   |

|    |      | 8.8.5   | The accuracy/speed trade-off                                                                                                  | . 83 |

|    |      | 8.8.4   | Improvements to consider                                                                                                      | . 82 |

|    |      | 8.8.3   | Evaluating the power model                                                                                                    |      |

|    |      | 8.8.2   | Consequences of abstractions                                                                                                  | . 80 |

|    |      | 8.8.1   | The quality of the cell mapping                                                                                               | . 79 |

|    | 8.8  | Discus  | sion                                                                                                                          | . 79 |

|    | 8.7  | Result  | s                                                                                                                             | . 76 |

|    | 8.6  | Impler  | mentation                                                                                                                     | . 74 |

|    | 8.5  | Estima  | ating the switching power                                                                                                     | . 74 |

|    |      | 8.4.1   | The <i>select</i> cell                                                                                                        | . 72 |

|    | 8.4  | Generi  | ic cells with no library equivalent                                                                                           | . 72 |

|    |      | 8.3.1   | Need for optimisation                                                                                                         |      |

|    | 8.3  |         | ining the structural information and the liberty data                                                                         |      |

|    | 8.2  |         | ations introduced by the cell library representation                                                                          |      |

|    | 8.1  |         | ations introduced by the structural representation                                                                            | . 66 |

| 8  | Gen  | eratin  | g a power model                                                                                                               | 65   |

|    |      | 7.5.3   | On the calibration                                                                                                            | . 64 |

|    |      | 7.5.2   | Other representations                                                                                                         | . 64 |

|    |      | 7.5.1   | Choosing a cell from a group                                                                                                  | . 63 |

|    | 7.5  | Discus  | sion                                                                                                                          | . 63 |

|    |      | 7.4.3   | Summary                                                                                                                       |      |

|    |      | 7.4.2   | Putting together a cell library object                                                                                        | . 63 |

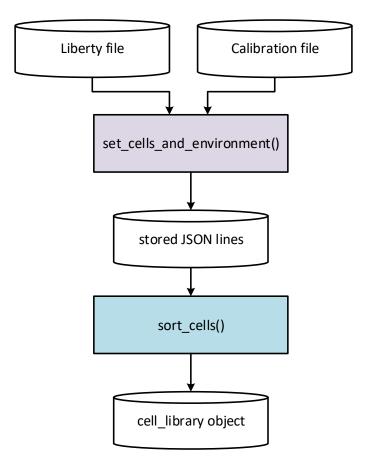

|    |      | 7.4.1   | Parsing Liberty and storing data                                                                                              |      |

|    | 7.4  |         | $mentation \dots \dots$ |      |

|    | 7.3  | Cells v | with same functionality                                                                                                       |      |

|    |      | 7.2.3   | The state-dependency of leakage power                                                                                         | . 59 |

| С            | Technical implementation of the power model | C-1 |

|--------------|---------------------------------------------|-----|

| D            | Code implemented in Chapter 6               | D-1 |

| $\mathbf{E}$ | Code implemented in Chapter 7               | E-1 |

| $\mathbf{F}$ | Code implemented in Chapter 8               | F-1 |

## Glossary

- **Dennard Scaling** A MOSFET scaling law claiming the power density stays constant as transistors scale, thus making it possible to reduce power consumption by reducing the design size. This has held until recently, as leakage power is not negligible anymore with the smaller gate lengths in newer technology

- fan-in is the reduction of signals caused by several signals being connected to a cell with fewer outputs than inputs. E.g. a 3-inputs AND gate has a fan-in of 3.

- fan-out is the number of input gates that is driven by an output of a logic gate

- **JSON** stands for JavaScript Object Notation and is a format for representing structured data.

- **Liberty** is a widely adopted library format. The format is managed by the Liberty Techincal Advisory Board, which is sponsored by Synopsys [1]

- one-hot is form of signal encoding where only one bit of the signal can be high at a time

- **power bug** is a fault with the design causing the power consumption to behave unexpectedly. It may cause the design to violate its power constraints.

- SystemVerilog is a hardware description- and hardware verification language

- VHDL is a hardware description- and hardware verification language

# Acronyms

- ASIC Application Specific Integrated Circuit

- **BDD** Binary Decision Diagram

- ${\bf BN}\,$ Boolean Network

CDFG Control flow Data Flow Graph

CMOS Complementary Metal-Oxide-Semiconductor

HDL Hardware Descriptive Language

I/O Input/Output

- IC Integrated Circuit

- **IEEE** Institute of Electrical and Electronics Engineers

LUT Lookup Table

**RT-level** Register Transfer Level

**RTL** Register Transfer Level

$\mathbf{SV}$  SystemVerilog

# List of Tables

| 5.1 | Elaborated cells                                                                 | 9 |

|-----|----------------------------------------------------------------------------------|---|

| 5.2 | Groups of elaborated SystemVerilog constructs                                    | 2 |

| 5.3 | Library group and attribute overview                                             | 6 |

| 5.4 | Power related cell groups and attributes overview                                | 7 |

| 5.5 | Pin power related groups and attributes overview                                 | 8 |

| 5.7 | Code listings and code documentation                                             | 0 |

| 6.1 | Gate counts from elaborated structure and synthesised file                       | 9 |

| 7.1 | Increase in leakage power from least consuming to most consuming state 59        | 9 |

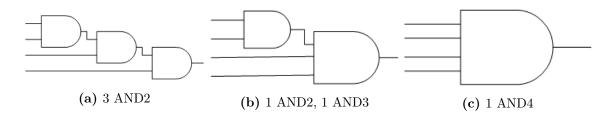

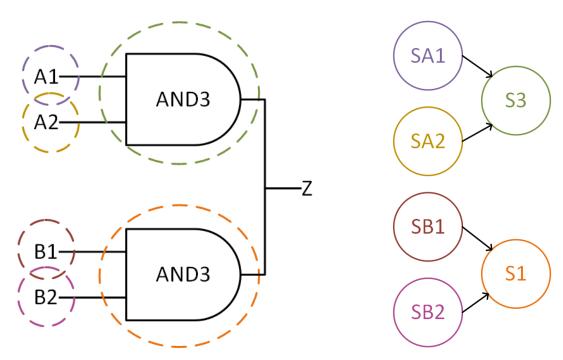

| 8.1 | Power consumption in AND cells of different sizes using AND2 as the reference 69 | 9 |

| 8.2 | Power consumption in AND4 optimisations, in comparison to the three              |   |

|     | AND2 gate implementation in Figure 8.3a                                          | 0 |

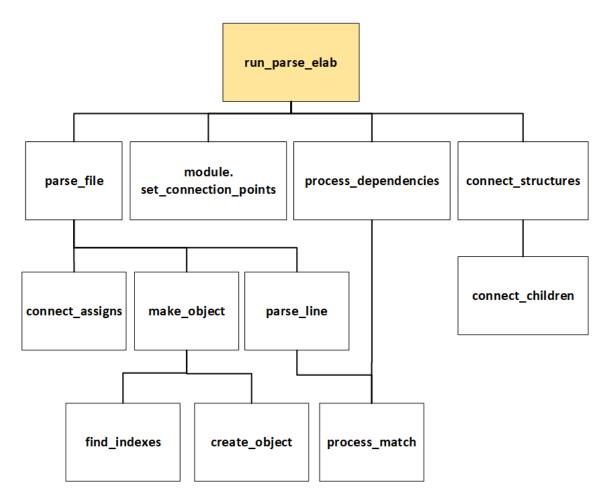

| A.1 | Overview of the functions in the elaborated SystemVerilog (SV) parser A-2        | 2 |

| A.2 | Helper functions for the elaborated SV parser                                    | 3 |

| A.3 | Overview of classes in the elaborated SV parser and their variables and          |   |

|     | procedures                                                                       | 4 |

| B.1 | functions for processing the liberty file information                            | 2 |

| B.2 | Class overview for processing the liberty file information                       | 3 |

| C.1 | functions for making the power model                                             | 2 |

| C.2 | Class overview for the power model                                               | 2 |

# List of Figures

| 1.1        | Graph relating design abstraction level and power estimation accuracy                                                                                                      | 2  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1<br>2.2 | Illustration of the iterative ASIC design flow, [2] $\ldots \ldots \ldots \ldots \ldots$<br>Illustration of the short-circuit power in CMOS logic [3]. When $V_{IN}$ rises | 9  |

|            | and falls $I_{SC}$ will flow from $V_{DD}$ to ground for a short period of time                                                                                            | 11 |

| 2.3        | Complementary Metal-Oxide-Semiconductor (CMOS) design corners [4]                                                                                                          | 13 |

| 3.1        | The estimation flow in the case of bottom-up power estimation $\ldots \ldots \ldots$                                                                                       | 17 |

| 3.2        | A top-down estimation flow                                                                                                                                                 | 18 |

| 3.3        | The estimation flow in the case of fast synthesis estimation $\ldots \ldots \ldots$                                                                                        | 20 |

| 4.1        | The intended estimation flow of the top-down power estimation. The blocks<br>highlighted in green are already existing, while the orange ones have to be                   |    |

| 1.0        | implemented to make the top down power estimator.                                                                                                                          | 24 |

| 4.2        | A refined flow for the top-down power estimation. The already existing<br>Liberty parser is highlighted in yellow. The part of the flow that is out of                     |    |

|            | scope is drawn in dotted lines                                                                                                                                             | 27 |

| 4.3        | An overview of the synthesis process from RTL to netlist                                                                                                                   | 28 |

| 6.1        | The modeling flow with the part of the flow relevant to this chapter highlighted                                                                                           | 41 |

| 6.2        | Different methods to levelise a logic circuit                                                                                                                              | 44 |

| 6.3        | The elaborated SystemVerilog file is parsed and a set of <i>structure</i> class objects are made                                                                           | 46 |

| 6.4        | A structural representation of the circuit in Figure 6.2b as a tree of <i>structure</i>                                                                                    | 40 |

|            | objects                                                                                                                                                                    | 48 |

| 7.1        | The modeling flow with the part related to retrieving power information from                                                                                               |    |

|            | the cell library highlighted.                                                                                                                                              | 55 |

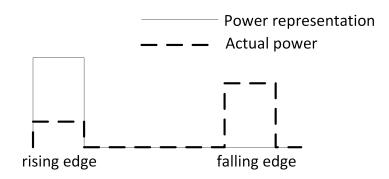

| 7.2        | The impact on power estimation when summarising rise- and fall power $\ .$ .                                                                                               | 57 |

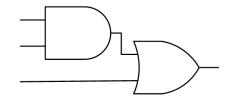

| 7.3        | ANDOR21                                                                                                                                                                    | 58 |

| 7.4        | The dataflow of retrieving the relevant Liberty data.                                                                                                                      | 61 |

| 8.1        | The modeling flow with the flow relevant to this chapter highlighted                                                                                                       | 65 |

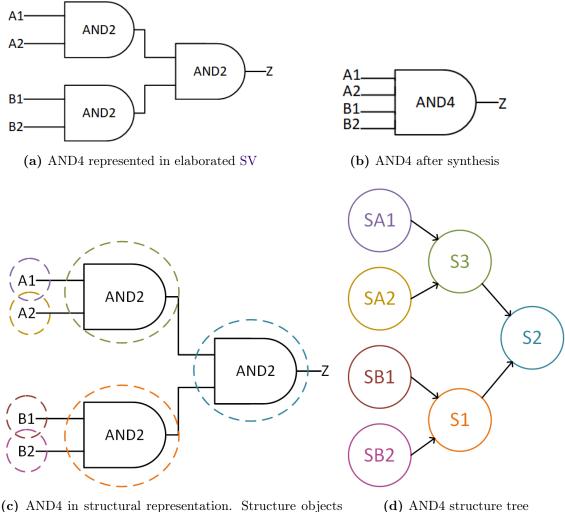

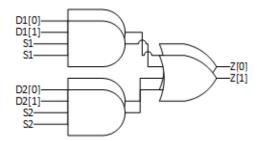

| 8.2 | Different representations of an AND4 gate                                                                      | 67  |

|-----|----------------------------------------------------------------------------------------------------------------|-----|

| 8.3 | Different implementations of a 4-input AND gate                                                                | 69  |

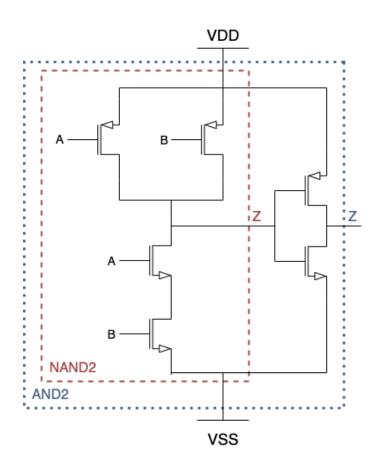

| 8.4 | A common CMOS schematic for a NAND2 and an AND2 gate. The AND2                                                 |     |

|     | schematic is the same as the NAND2 but with an added inverter                                                  | 71  |

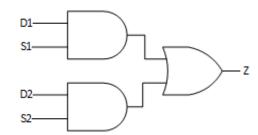

| 8.5 | One-hot multiplexers with different data<br>width                                                              | 73  |

| 8.6 | An AND4 gate as made by the power model generator                                                              | 75  |

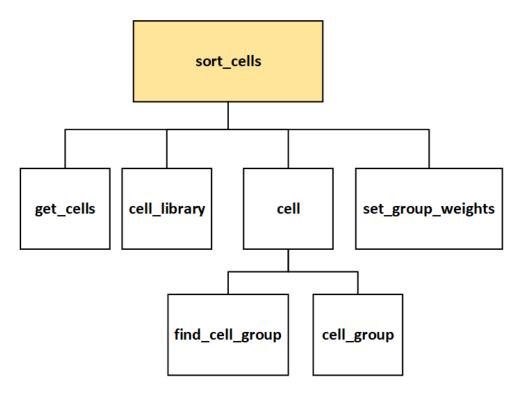

| A.1 | The function hierarchy of the elaborated SV parser. Functions at the same level are called from left to right. | A-1 |

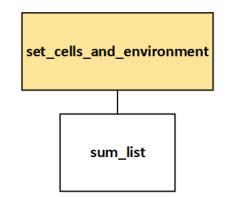

| B.1 | The function hierarchy of the liberty parser                                                                   | B-1 |

| B.2 | The function hierarchy of the liberty power data retrieving                                                    | B-2 |

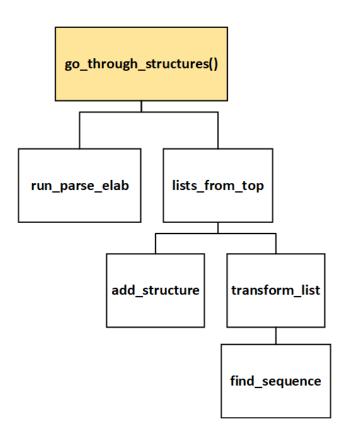

| C.1 | Function hierarchy for the power model implementation                                                          | C-1 |

# 1 Introduction

### 1.1 Motivation

Power consumption is becoming increasingly important in Integrated Circuit (IC) design with the emergence of more and more battery-driven devices [5]. Transistor dimensions have continuously been shrinking to lower the power consumption of ICs. However, with the breakdown of Dennard Scaling [6] in the 2000s, leading to an increase in power density with smaller dimensions, downscaling has less effect on power consumption than it used to. Designers are now pushed to focus more on power consumption in their designs, and designing circuits for low power usage is becoming just as important as designing for high performance. The latter may be easier for designers, while many may lack the intuition to create circuits with low power in mind. To aid designers in this endeavour, tools for estimating the power consumption are essential.

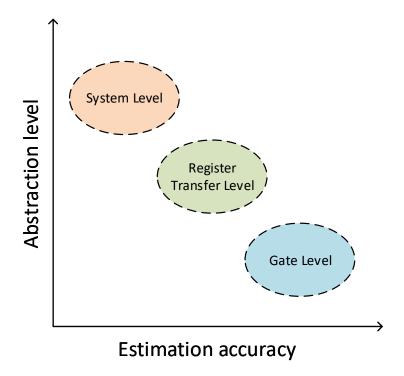

Power estimation can be done at all design stages, until, in the end, it can be measured on the physical IC. The closer one is to the final implementation; the more accurate the power estimation typically can get. The less abstract the design representation is, the more one knows about parameters critical to power consumption. This is illustrated in Figure 1.1.

The system-level representation of a design is very abstract, and few aspects of the physical endproduct are known. The RTL representation is less abstract than the system-level representation, but still much remains unknown about the physical IC. The gate-level representation is closer to the endproduct than the two others, and many parameters relating to power consumption are determined at this level. The accuracy of power estimation will typically follow the trend of the graph; being more accurate the less abstract the design representation is.

Figure 1.1: Graph relating design abstraction level and power estimation accuracy.

The ASIC design process is an iterative process, described in Section 2.2. Discovery of issues at a particular stage might bring one back to earlier stages in the design process, where more significant changes can be done. Each iteration is costly in development time and effort, and may increase the time to market for a product. Ideally, the design should be made with as few iterations as possible. Discovering and fixing power bugs already at the RTL is thus beneficial, possibly reducing the number of design iterations necessary.

There is a lack of suitable tools for estimating power at the RTL. They tend to be either too time consuming to run or too inaccurate to give assured results. Many also output an average power estimate with no granularity in time and space, which is needed if one is to use this estimate to deal with power bugs.

### 1.2 Problem description

This project aims to investigate and develop power models for use in power estimation at the RTL. A general method for making these models is found and it holds for all types of RTL designs. To make this model, information about the cell library used is necessary together with an RTL description of the design.

Nordic Semiconductor ASA requested this project, and their motivations are to be able to discover power bugs early and enhance their design flow by developing a power estimation tool able to yield power estimates corresponding to the RTL simulations. It is necessary to have a low spatial and temporal granularity in the model made, in order to discover power bugs.

In Chapter 4, different approaches to RTL power estimation are investigated, and an implementation using the top-down method is decided upon. An advantage of the top-down method is its ability to yield a power estimate before having a gate-level representation of the design. This way, the estimation method does not introduce extra iterations to the design flow described in Section 2.2.

The top-down method tends to be less accurate than other options for RTL power estimation. The approach presented in this thesis tries to atone for this by using the Liberty file to get accurate power information about the cells to be used in the design, and combine this cell information with elaborated Hardware Descriptive Language (HDL) structural information, which potentially yields a better structural representation than an unprocessed HDL representation. The HDL elaboration will be done using Synopsys HDL Compiler.

This project implementation is divided into three main tasks:

#### 1. Analysing the structure of a design

By using an elaborated HDL implementation, information about the structure of a design, necessary for estimating power, will be retrieved. This information could be the number of gates, number of registers, amount of combinatorial logic, how the signals are connected, and so on.

#### 2. Obtaining power characteristics from the technology library

Finding a means to retrieve information about the available cells and their power characteristics from the cell library. Power characteristics being the leakage power and the dynamic power of the cells. It is also necessary to retrieve information about the cells in question to be able to relate their functionality to the power data.

#### 3. Creating a power model

Combining information about the structure retrieved in task **1** and information about the available cells retrieved in task **2** to make a power model of a design, representing all the signals and logic in the HDL representation.

The novelty of this power model is its generality and its use of the elaborated HDL and a cell library. The generality allows power models being made for any RTL as long as it can be elaborated by Synopsys HDL Compiler. The power models can be made with any cell library, their dimensions being irrelevant. The use of a cell library in the power model generation and a structural representation derived from elaborated SystemVerilog aims to achieve a high accuracy to future power estimations at the RTL.

## **1.3** Report structure

After this introduction this report consists of the following chapters:

| 2 Theory                         | In this chapter some relevant and useful theory for<br>the project is presented.                              |

|----------------------------------|---------------------------------------------------------------------------------------------------------------|

| 3 Background                     | This chapter presents related work and gives an introduction to RTL power estimation.                         |

| 5 Design tools and file formats  | Here relevant design tools and file formats are pre-<br>sented.                                               |

| 6 Extracting design structure    | Describes how the structural information is re-<br>trieved from the RTL representation.                       |

| 7 Extracting library information | Describes how the power relevant information in<br>the cell library is found, stored and used.                |

| 8 Generating a power model       | This chapter combines the information retrieved<br>in the two preceeding chapters to create a power<br>model. |

## 9 Conclusion

Concludes the work done.

#### 10 Future work

Suggestions towards future work of improving the power model and applying it in top-down RTL power estimation.

# 2 Theory

## 2.1 Terminology

Some terminology that will be used in this report is shown below.

| GATE"N"           | Logic gates will be referred to in capital letters annotated with the<br>number of inputs the gate has. For instance, a 2-input and gate will<br>be written AND2. For more complex gates the numbers annotated<br>refer to clusters of inputs, if this number is one it often skips the<br>firs operator. For example ANDOR21 is a AND2 gate followed<br>by an OR2 gate, where one of the OR2 inputs is the output of the<br>AND2 gate. These more complex gates will be explained with logic<br>functions or figures to make this clearer. |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | functions of figures to make this clearer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *                 | Logical AND operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| +                 | Logical OR operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| !                 | Logical NOT operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| cell              | A building block in ASIC design. A transistor circuit encapsulated<br>into a logic function, such as an AND gate. Could also describe<br>building blocks with other purposes, but in this project this will<br>not be visited. All available cells are gathered in a cell library.                                                                                                                                                                                                                                                          |

| generic gate/cell | A cell of the generic cell library used by Synopsys HDL Compiler<br>when doing the design elaboration. In cases where the cell repre-<br>sents a logic gate, it may be referred to as a generic gate instead of<br>a generic cell.                                                                                                                                                                                                                                                                                                          |

## 2.2 The ASIC design flow

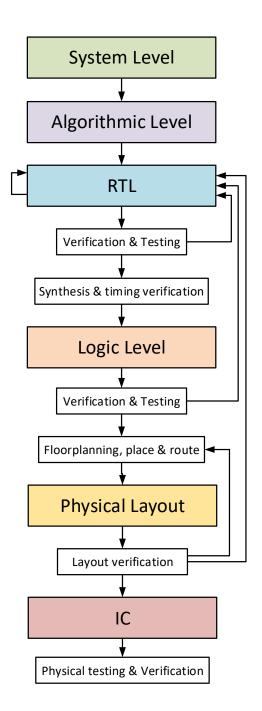

The ASIC design flow is a mature design flow used in the making of Integrated Circuits. This flow allows one to, step-by-step, go from an abstract design description, towards the layout sent to a foundry for manufacturing the physical IC. The flow is iterative and may, at any point before the physical IC is produced, return to an earlier stage, where larger changes can be made [2].

In Figure 2.1 different ways to represent the circuit with decreasing abstraction is shown. The steps in the design flow is described below.

| System Level            | At this level the design is described as a set of functionalities,<br>characteristics and constraints.                                                                                                                                                                                                               |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Algorithmic level       | Here the design is described and verified on an algorithmic level,<br>often using high level programming languages.                                                                                                                                                                                                  |

| Register Transfer Level | This representation makes use of a hardware descriptive lan-<br>guage, to describe the design as digital signals, logic operations<br>and registers, and verified as such, for instance using SystemVer-<br>ilog or VHDL.                                                                                            |

| Logic Level             | The Register Transfer Level description of the design can be <i>synthesised</i> into a Logic level description. Here the description is mapped to the available logic cells in the cell library. The synthesis process also checks timing and area constraints so one knows whether these hold or not at this level. |

| Physical Layout         | For the physical layout representation the cells from the logic<br>level representation are placed and connected on a theoretical<br>chip. Analog phenomenon, eg. wire capacitances, are taken into<br>concern in an attempt to model the physical IC.                                                               |

| IC                      | Here the endproduct of the process is made in a foundry. based<br>on a GDSII file from the physical layout, which contains all<br>information necessary to produce the IC.                                                                                                                                           |

Figure 2.1: Illustration of the iterative ASIC design flow, [2]

## 2.3 CMOS power consumption

The power consumption in digital CMOS-based circuits can be divided into dynamic and static power consumption. The dynamic power consumption is caused by the switching activity in the system, while the static power consumption is caused by leakage in the CMOS transistors [4]. The total power consumption of the system is the sum of these two as is given by Equation (2.1).

$$P_{total} = P_{dynamic} + P_{static} \tag{2.1}$$

#### 2.3.1 Dynamic power consumption

The dynamic power consumption can be divided into switching power and short-circuit power [4].

The main contributor to the dynamic power consumption is the switching power, which is the power it takes to charge and discharge the output capacitance of a logic gate. It can be calculated as shown in Equation (2.2), where  $\alpha$  is an activity factor describing how often the output switches (changes value).  $C_L$  is the load capacitance on the gate output,  $V_{dd}$  is the supply voltage and  $f_{clock}$  is the clock frequency.

$$P_{SW} = \frac{\alpha}{2} C_L V_{dd}^2 f_{clock} \tag{2.2}$$

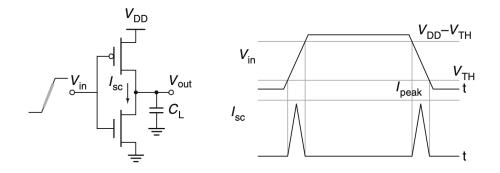

Another contributor to dynamic power consumption is the short-circuit current. When CMOS logic is in the middle of switching both the NMOS and the PMOS transistor will be partially open, allowing some current to flow from  $V_{dd}$  to ground. This is illustrated in Figure 2.2.

Figure 2.2: Illustration of the short-circuit power in CMOS logic [3]. When  $V_{IN}$  rises and falls  $I_{SC}$  will flow from  $V_{DD}$  to ground for a short period of time.

The short-circuits contribution to power consumption can be calculated using the expression shown in Equation (2.3), where  $t_{sc}$  is the duration of the short circuit current,  $V_{dd}$  is the supply voltage of the system,  $I_{sc}$  is the average short-circuit current and  $f_{clock}$  is the clock frequency.

$$P_{SC} = t_{sc} V_{dd} I_{sc} f_{clock} \tag{2.3}$$

The total dynamic power consumed in the circuit will be the sum of the switching power and the short-circuit power consumed by all the transistors in a design, shown in Equation (2.4). N is the number of transistors,  $P_{SW_t}$  is the switching power- and  $P_{SC_t}$  is the short-circuit power of transistor t.

$$P_{dynamic} = \sum_{t=0}^{N} \left( P_{SW\_t} + P_{SC\_t} \right)$$

$$(2.4)$$

#### Dynamic power consumption from a logic circuit perspective

A different way of viewing switching power consumption, more suited for logic designs, is gotten from dividing the power consumption in two contributions: The contribution from switching of nets in a design, the **switching power**, and the contribution from the switching of internal signals in a logic cell, which also includes the short-circuit contribution, **internal power**. The total dynamic power of a design can thus be seen as a sum of the **switching power**,  $P_{SW}$ , of all nets, and the **internal power**,  $P_{IN}$ , of all cells. This is shown in Equation (2.5).

$$P_{dynamic} = P_{SW} + P_{IN} \tag{2.5}$$

#### 2.3.2 Static power consumption

The static power consumption in the CMOS transistors is caused by leakage current. This leakage has traditionally been negligible compared to the switching power, but the downscaling of the technologies and the lower supply voltages, which in turn has lead to lower threshold Voltage,  $V_t$ . Nowadays the static power consumption of transistors, is just as significant as the switching power. Contributions to the leakage current come from the sub-threshold leakage, the gate leakage and the junction leakage [4].

- Sub-threshold leakage is current leaking from source to drain while the transistor is operating in the weak inversion region ( $V_G < V_t$ ). It increases exponentially when lowering  $V_t$  [4] and is the largest contributor to the static power consumption.

- Gate leakage is current caused by electrons tunnelling through the oxide layer of the gate.

- Junction leakage is caused by potential differences between the drain diffusion region and the substrate. It is often negligible compared to the other two contributors.

## 2.4 Process, Voltage and Temperature corners

Variations in the manufacturing and the environment will lead to significant changes in the characteristics of a transistor. These changes may cause the IC behaviour to vary. To make a circuit operate as expected these variations should be taken into account. The sources of these variation are **process variation**, **supply voltage** and **temperature** [4].

The **process variation** is caused by slight variations in the manufacturing process, like the concentration of dopants or the oxide thickness.

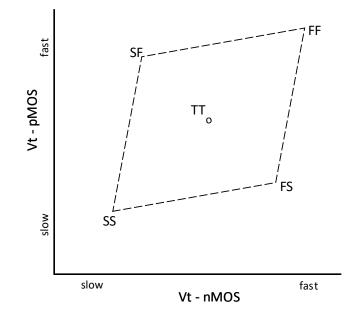

These variations lead to manufactured transistors having varied characteristics. These are described as; F (fast) and S (slow) for the corner-cases, where the transistor will operate faster and slower than expected, and T (typical) describing an average transistor. For a CMOS transistor, consisting of one PMOS and one NMOS transistor this yields four operating corner-cases describing a constricted area, in which the pair og transistors will always operate within. FF, SS, SF and FS. The center of this area is (TT), the average transistor. This is illustrated in Figure 2.3.

Figure 2.3: CMOS design corners [4]

The variation in **temperature** also affects the transistor's operation significantly as it lowers the threshold voltage. If the operating temperature is high the transistor will have a higher leakage, which increase its power consumption.

Lastly, the **supply voltage** can deviate from the intended value for many reasons, such as the tolerance of the voltage regulators and noise.

Thus, it is not enough to only take an average transistor in the TT corner, operating in room temperature with the intended supply voltage into account. One also needs to consider the transistor in its slow corner, operating on a high temperature with a low voltage, and all other corner-cases.

# 3 Background

As demands to power consumption rise, the size of battery-driven devices sink and smaller transistor dimensions lead to higher power density, the need for power estimation tools rise. The designers wish to optimise the ASIC design flow and minimise the time to market, while still keeping up with state of the art power demands. Power can be estimated at all stages in the design process described in Section 2.2.

At the system level, accurate power estimation tools are few, but maybe not for much longer. In 2019 Institute of Electrical and Electronics Engineers (IEEE) released a new standard for power modeling at the system level [7]. There has not been a standard way of representing power data at the system level before. The organisation suggests the lack of such a standard could be why the industry is still inadequate in this field.

At the functional level, there power estimation tools exist, but they are mainly meant to speed up the simulations. One can argue that there are two main reasons one can wish to estimate power at a high level;

- 1. One wants to get an approximate indication of the power consumption at this level before lower-level representations are made.

- 2. Simulations at this level is faster than low-level simulation

In 2. one returns to a more abstract design representation to run faster simulations. Increasing the simulation speed is the primary motivation for the functional level power estimation tools. They are based on already existing gate-level representations.

Zhong et al. [8] try to estimate power at the functional level using some RTL power models derived from a gate-level representation of the design. Here a cycle-accurate functional description is merely an abstraction of the known RTL, in order to to speed up the RTL power estimation by going up an abstraction level for the simulation. In another paper, Zhong et al. [9] further improve their solution. Lee and Gerstlauer [10] annotates a functional model of a design with constructs allowing the capturing of activity. Using machine learning, power models can be synthesised from this functional model. An advantage of this method is that it allows for high-speed simulations. However, the functional model requires an existing gate-level representation of the design to train the power model. The methods for estimating power at the RTL can be divided into two main methods of implementation. They will be referred to as bottom-up and top-down methods. The bottom-up method starts with a less abstract representation of the design, such as the gate-level representation, and tries to relate power estimates done at this level to factors that are also known at the RTL [11], [12], [13]. The estimation method then returns to the RTL representation of the design and does power estimation on different scenarios there. The top-down method, on the other hand starts at the abstract RTL and tries to estimate lower-level information about the design in order to estimate power directly [14], [15], [16].

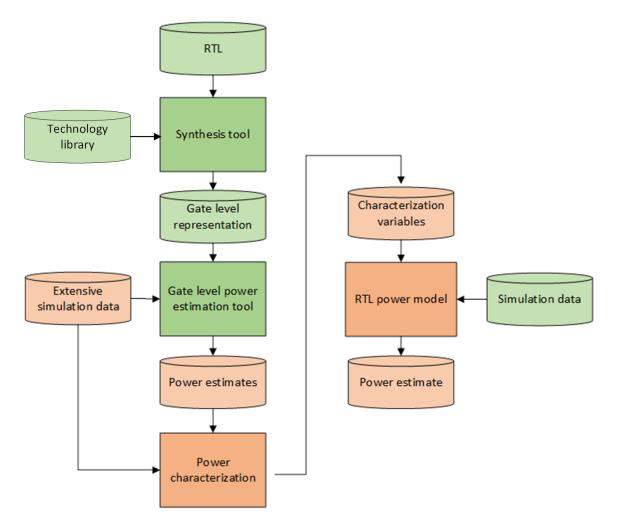

## **3.1** Bottom-up power estimation

In Figure 3.1 a typical estimation flow of bottom-up power estimation can be seen. The available input data is a gate-level netlist with corresponding simulation data. However, this requires that synthesis and layout with the desired technology library have been performed. A power estimation tool is then run on the gate level representation with a broad set of activity data. This results in a set of power estimates and simulation data that can be used to characterise the design, often relating the Input/Output (I/O)-switching to the power consumption. To get a power estimate, characterisation variables or a Lookup Table (LUT) are then fed to a general power model at the RTL, together with the simulation data of the scenario from which one wishes to estimate power.

Ravi et al. [11] makes an extensive set of macromodels from RTL components. These models are then translated into simulatable power model libraries. The creation of new designs then solely make use of these components for which power estimates are available.

Gupta et al. [12] made a macromodel relating gate-level power estimates to the hamming distance between consecutive input vectors. A complicated characterisation stage is necessary to exploit this relation.

Mehta et al. [13] also takes basis in making a macromodel for every possible RTL component. A clustering algorithm is used to group input vectors leading to similar power consumption in the circuit. These groups are then placed in a LUT. This clustering makes their model faster, as there are fewer values to look up.

Figure 3.1: The estimation flow in the case of bottom-up power estimation

## 3.2 Top-down power estimation

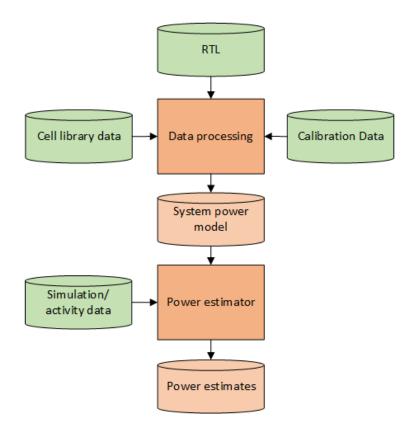

The estimation flow of a top-down power estimation approach can be seen in Figure 3.2. The method needs to take in information about the structure, readily available at the RTL, for instance, a HDL description. It also needs to take the cell library into account. The cell library can be considered by, for example, knowing the power characteristics of a standard gate from the cell library, or by processing the entire cell library as an input. It could also be possible to do some characterisation. If one, for instance, has a design that will be synthesised with strict timing constraints, this will increase its power consumption compared to a design with less strict timing constraints.

Zafalon et al. [14] have developed both a top-down and a bottom-up technique for power

Figure 3.2: A top-down estimation flow.

estimation. Their top-down approach is based on using a Binary Decision Diagram (BDD) to represent the circuit. Representing a design as a BDD is the same as making the design using only 2-to-1 multiplexers. This design is then optimised to some degree decided by the user, and the power estimate is tuned to the target technology. The user decides whether the actual synthesis will focus on power, timing or area and the model is also tuned based on that input.

Buyuksahin and Najm [15] make use of a Boolean Network (BN), a directed acrylic graph where each node is a boolean function, and its edges represent the connection between nodes. They use this network to estimate the gate count of the design, which yields an estimate of the circuit's total capacitance.

Sambamurthy et al. [16] use a Control flow Data Flow Graph (CDFG) to represent the circuit. This graph allows for modeling both the data operations done and conditionals. The number of stages necessary to implement a function is then estimated from the maximum input number of gates in the target technology and the function's size to be computed. The probability of switching at each node is then estimated from input switching from simulation

or the input switching probabilities and the likelihood of that switching propagating all the way to the logic depth of the function. The method of Logic Effort is used to make a capacitance estimate. All of the above is then combined into a power estimate.

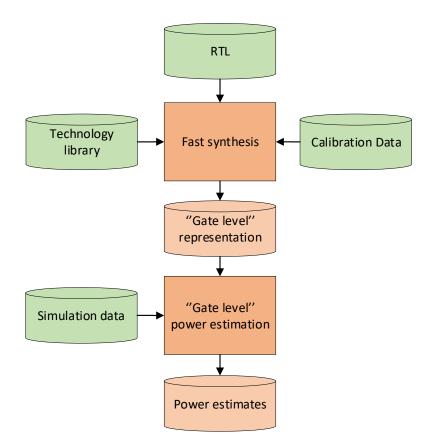

#### 3.2.1 Fast synthesis power estimation

Several vendors provide tools for estimating power at the RTL. To mention a few; Ansys has PowerArtist [17], Synopsys has Spyglass Power [18], Mentor Graphics has PowerPro [19] and Cadence has Joules RTL Power Solution [20]. These are typically based on some variant of fast synthesis power estimation, mapping the RTL description to cells in a cell library and estimating the power consumption based on these cells. This method is applied by vendors already providing synthesis tools to provide a power estimation tool faster than gate-level estimation.

The power estimation flow of such tools is shown in Figure 3.3. The figure is simplified as the internal synthesis, and power estimation flow is undisclosed information private to the tool vendors. It is based on a synthesis tool that omits information not crucial to power estimation in order to speed up the synthesis. After the fast synthesis, an estimation tool will be used to estimate power. It gets its parameters from the "synthesised" design, activity data and possibly calibration data. As these methods bring the design closer to a gate-level representation, they allow for accurate power estimates but introduces a synthesis process which, though it is faster than a regular synthesis, may still be slow.

Figure 3.3: The estimation flow in the case of fast synthesis estimation

# 3.3 Prestudy

This thesis is written in collaboration with Nordic Semiconductor ASA. An unpublished literary review has been conducted on RTL power estimation to find a method suiting their motivations, which can be summarised as:

- Wanting to make RTL simulation power-aware.

- Being able to use this power awareness to detect power bugs.

The prestudy can be found on GitHub [21]. The following is a quick outline of the main differences between the top-down and bottom-up estimation flows and a summary of the prestudy conclusion.

The bottom-up methods have their foundation at the gate level and thus tend to have a

more accurate power estimation due to more information about the design being available as the power model is made. The challenge of bottom-up power estimation is to get the power estimates to correlate well with the input and output switching statistics of the design so that the model can be used at the RTL. The top-down methods tend to be less accurate, but lack the time-consuming characterisation stage of the bottom-up methods, making them faster for new designs and possibly more suited for design exploration if they take the internals of the RTL description into account.

To make the RTL simulation power-aware a power estimation tool for the RTL is needed. It is a significant advantage if this model is available before the design has been synthesised. Otherwise, it will introduce an extra iteration into the design flow, which may be avoided using the top-down method.

To detect power bugs with this power estimation, it needs time/cycle awareness. It could either work for smaller time-frames or do estimation cycle-by-cycle in the simulation. The latter is preferable. In addition to this temporal granularity, the tool should also have some spatial granularity. When running simulations on larger modules and observing unexpected power behaviour, it is an advantage to see where this behaviour occurs.

If the desire had been to increase simulation speeds when running power scenarios, then going from a gate-level representation to a RTL representation makes sense. Otherwise, this introduces an extra iteration to the design flow, which may be avoided using the top-down method.

If a top-down estimation approach does not provide enough accuracy, it could be supported by bottom-up models for existing design blocks to increase the estimation accuracy.

# 4 Suggesting a solution

The top-down method has been chosen for implementation due to its desirable estimation flow. The top-down flow is simple and starts at the RTL and makes a power estimate directly. For a bottom-up flow, on the other hand, a gate level representation of the design is needed **before** a RTL power estimate can be made. Using the top-down method a design can be changed or discarded because of power concerns early in the design flow, without ever needing to be synthesised, if the power estimates are accurate enough. With the topdown method it is possible to verify the power behaviour concurrently to the functional verification of the RTL.

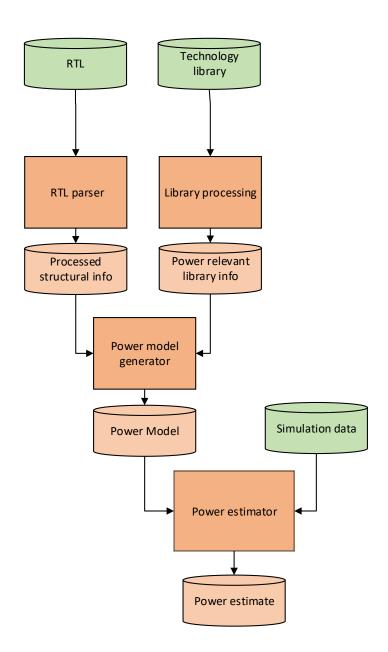

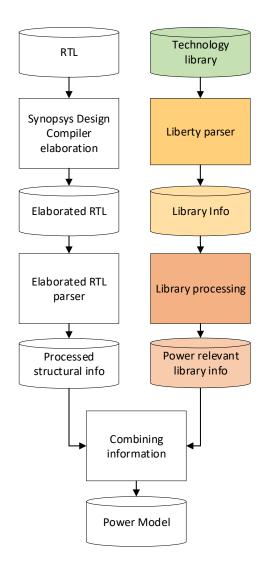

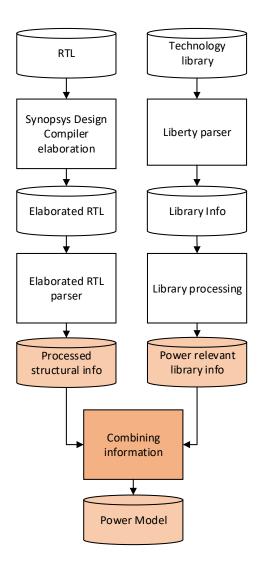

The suggested estimation flow can be seen in Figure 4.1. Here the RTL representation of a design and data from the cell library is retrieved and processed separately, to later be combined into a power model. The power model is used together with activity data by a power estimation tool to yield a power estimate. Already existing data and tools are highlighted in green, while the parts highlighted in orange would have to be implemented.

It is necessary to implement a system processing the structural information found in the RTL representation, and another system processing power information related to the cell library. Then, the retrieved information from both systems can be combined into a power model, which will serve as an input to a power estimator together with simulation- or activity data.

Figure 4.1: The intended estimation flow of the top-down power estimation. The blocks highlighted in green are already existing, while the orange ones have to be implemented to make the top down power estimator.

## 4.1 Structural information

The processed structural info-block in Figure 4.1 should contain information about which operations are done on which signals and how they are all connected. Later, in the Power model generator-block this will be related to power information. The structural information should also allow for some estimation of activity in the structure, depending on observable, (input, output and/or register), switching activity. It is also important that the structure remains relatable to the RTL it represents.

Most synthesis tools have an *elaboration* stage where they retrieve structural information from the RTL as a pre-processing stage for the *synthesis*. This is done by breaking down coding constructs and compiler directives and mapping the code to cells from a *generic* library. This library does not correspond to any physical library and the *generic cells* represent logic- and arithmetic functions on the signals only. With this representation as a foundation the *operations* are the generic cells in the elaborated netlist and the *signals* are their connections.

Using the elaborated structural information, rather than unprocessed RTL, brings one a bit closer to the gate level representation of the design and possibly towards more accurate power estimates. It is not desirable to go all the way to a gate level representation as the synthesis process is time consuming, especially for larger designs. It is interesting to see what kind of power model can be developed with this elaborated design as a starting point rather than the RTL it is elaborated from or the netlist it is synthesised into. Detailed information about the elaborated SystemVerilog format can be seen in Section 5.1

## 4.2 Cell library information

A common approach in high level power estimation is to abstract away the cell library by using a general gate representing all the gates in the design instead of differentiating between gates. Such a cell is commonly a NAND2 cell with the correct gate length and power characteristics corresponding to the cell library. This project attempt to lay the foundation of accurate RTL power estimation and thus want differentiate between the cells in the design to some extent. Knowing what cells are where and what they are affected by will possibly improve the accuracy of temporal and spatial power estimates even if the average power estimate remains the same. Finding out *what* cells are available and what power consumption these cells have will be the job of the *Library Processing*-block in Figure 4.1. The library power information is commonly stored in a Liberty file. Liberty is a standard format for representing timing and power characteristics of a cell library. More information on the format is found in Section 5.2.

Nordic Semiconductor ASA has a Liberty parser that can retrieve information from the Liberty file, but further processing is necessary to structure and select the information necessary to do power estimates, which is information relating to the static and dynamic power consumption of the cells. Synopsys has a HDL compiling tool doing design elaboration, but it will be necessary to retrieve structural information from the elaborated SystemVerilog file. Lastly this project will combine the structural information from the elaborated SystemVerilog and the power-focused information from the cell library into a power-aware representation of the design, a *power model*, which can in turn be used for power estimation.

## 4.3 The power modeling flow

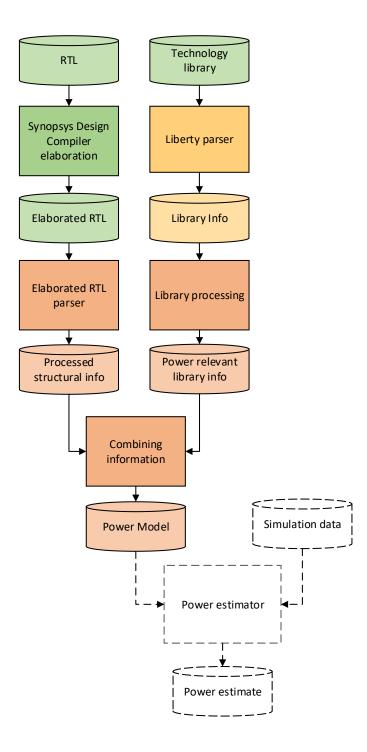

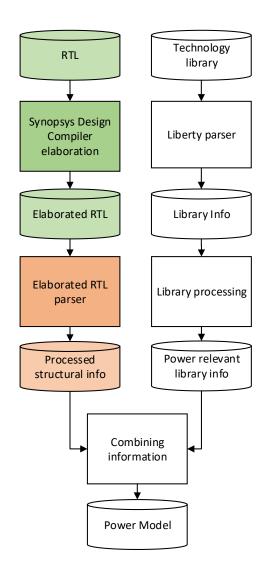

Figure 4.2 is a refined version of Figure 4.1. It goes more into detail on the estimation flow adding the Liberty parser and the elaborated SystemVerilog. The highlighted blocks are those involved in developing a power model, and thus the scope of this project. The power model will combine the structural information retrieved from the elaborated SystemVerilog and the power- and cell information retrieved from the Liberty file.

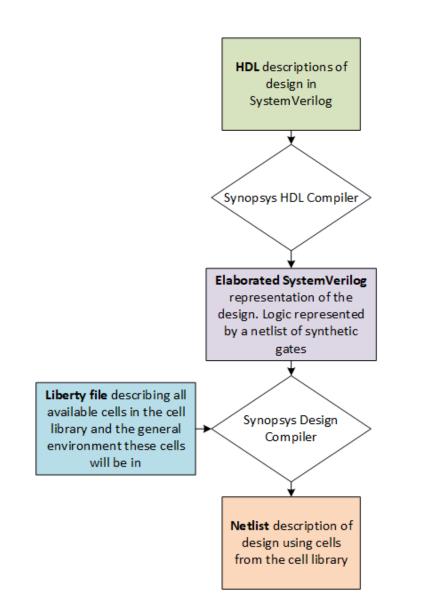

The elaborated file can be made using Synopsys HDL Compiler. A tool part of the Synopsys synthesis flow shown in Figure 4.3. In their flow the HDL is first compiled into an elaborated SystemVerilog netlist. The elaborated design is then fed to Synopsys DesignCompiler together with the Liberty file to yield the gate level netlist.

**Figure 4.2:** A refined flow for the top-down power estimation. The already existing Liberty parser is highlighted in yellow. The part of the flow that is out of scope is drawn in dotted lines.

Figure 4.3: An overview of the synthesis process from RTL to netlist

# 5 Design tools and file formats

## 5.1 Design elaboration

Wire

wire

When synthesising a design, the constructs in the RTL are mapped to cells in the cell library, creating a hardware design with equivalent functionality as the one described in the RTL. This representation is called a netlist. Most synthesis tools do this by going through an elaboration stage. Here the constructs in the RTL are first optimised and mapped to cells from a *generic* cell library. A *generic* cell library is a library with functional cells not corresponding to physical ones. They do not have any power- or timing data. The elaboration also goes through the compiler directives, which are direct instructions on how to process the HDL, such as **'ifdefs**. The results of the elaboration stage is an intermediate file, similar to the netlist, using cells from a generic library, rather than cells from the library used in synthesis.

To complete the synthesis process, the elaborated file is optimised further and mapped to the cells in the cell library. In this project, Synopsys HDL Compiler has been used to get an elaborated representation of the design. In Table 5.1, a simplified list of these elaboration constructs made by this synthesis tool can be seen. The *module*, *input*, *output* and *assign* constructs are the same as in the RTL file. The *wire* represents all connections between objects. The rest of the objects have replaced the more complex RTL with simple, generic gates like an AND2 gate. The elaborated netlist is not technology-specific and, thus, does not contain any power information.

| Construct | generic cells | Description                           |

|-----------|---------------|---------------------------------------|

| Module    | module        | A SystemVerilog module declaration or |

|           |               | instantiation                         |

| Input     | input         | An input port of variable bitwidth    |

| Output    | output        | An output port of variable bitwidth   |

|           |               |                                       |

Table 5.1: Elaborated cells

A wire of variable bitwidth

| Assign       | assign                                                                                                                                                                                      | Assigning one wire to another wire or a constant                                                                    |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Multiplexer  | MUX_OP                                                                                                                                                                                      | A multiplexer with variable datawith and select signal width                                                        |

| Register     | SEQGEN                                                                                                                                                                                      | A one bit register                                                                                                  |

| AND2         | GTECH AND2                                                                                                                                                                                  | A two-input AND gate                                                                                                |

| OR2          | GTECH OR2                                                                                                                                                                                   | A two-input OR gate                                                                                                 |

| XOR2         | GTECH_XOR2                                                                                                                                                                                  | A two-input XOR gate                                                                                                |

| Select       | SELECT_OP                                                                                                                                                                                   | This sends one of several data signals out,<br>depending on a control signal                                        |

| Adder        | ADD_UNS_OP,<br>ADD_UNS_CI_OP,<br>ADD_TC_OP,<br>ADD_TC_CI_OP                                                                                                                                 | Adder with inputs and outputs of variable width                                                                     |

| Subtractor   | SUB_UNS_OP,<br>SUB_UNS_CI_OP,<br>SUB_TC_OP,<br>SUB_TC_CI_OP                                                                                                                                 | Subtractor with inputs and outputs of variable width                                                                |

| Shift        | ASH_UNS_UNS_OP,<br>ASH_UNS_TC_OP,<br>ASH_TC_UNS_OP,<br>ASH_TC_TC_OP,<br>ASHR_UNS_UNS_OP,<br>ASHR_UNS_TC_OP,<br>ASHR_TC_UNS_OP,<br>ASHR_TC_TC_OP,<br>SRA_UNS_OP,<br>SRA_UNS_OP,<br>SRA_TC_OP | Shifting a signal in a certain direction,<br>possible to take the sign into account                                 |

| Barrel shift | BSH_UNS_OP,<br>BSH_TC_OP,<br>BSHL_TC_OP,<br>BSHR_UNS_OP,<br>BSHR_TC_OP                                                                                                                      | Shifting, rolling the bit shifted out to<br>the opposite side of the signal instead of<br>shifting in zeros or ones |

| Shift-and-add | SLA_UNS_OP,    | Shift signal before adding              |

|---------------|----------------|-----------------------------------------|

|               | SLA_TC_OP      |                                         |

| Multipliers   | MULT_UNS_OP,   | Multiply two signals and output the re- |

|               | MULT_TC_OP     | sult                                    |

| Division      | DIV_UNS_OP,    | Divide a signal by another and output   |

|               | MOD_UNS_OP,    | the result                              |

|               | REM_UNS_OP,    |                                         |

|               | DIVREM_UNS_OP, |                                         |

|               | DIVMOD_UNS_OP, |                                         |

|               | DIV_TC_OP,     |                                         |

|               | MOD_TC_OP,     |                                         |

|               | REM_TC_OP,     |                                         |

|               | DIVREM_TC_OP,  |                                         |

|               | DIVMOD_TC_OP   |                                         |

| Comparators   | LT_UNS_OP,     | Compare two signals of variable width   |

|               | LT_TC_OP,      |                                         |

|               | GT_UNS_OP,     |                                         |

|               | GT_TC_OP,      |                                         |

|               | LEQ_UNS_OP,    |                                         |

|               | LEQ_TC_OP,     |                                         |

|               | GEQ_UNS_OP,    |                                         |

|               | GEQ_TC_OP,     |                                         |

|               | EQ_UNS_OP,     |                                         |

|               | NE_UNS_OP,     |                                         |

|               | EQ_TC_OP,      |                                         |

|               | NE_TC_OP       |                                         |

|               |                |                                         |

| Not           | GTECH_NOT      | An single bit inverter                  |

Many of the more complex generic cells are grouped into the same constructs. These cells differ depending on the representation of their input signal representations but are otherwise similar in functionality. The Synopsys elaboration differs between *unsigned*, UNS, and *twos'* complement, TC, representations. In the table, cells with different signal representations but otherwise the same functionality is put in the same group.

Many comparators have been grouped together into one. It can be argued that their power consumption is quite similar, as the logic needed to implement them are the same. However, the larger-than and smaller-than comparisons introduce more complexity than the equal and not equal, so it can also be an option to divide the comparators into two (or more) groups.

Table 5.2 shows the elaborated cell groups sorted by functionality.

| Group                | Construct     |

|----------------------|---------------|

| Connects             | inputs        |

|                      | outputs       |

|                      | wire          |

|                      |               |

| Buffers              | Buffer        |

|                      |               |

| Multiplexer          | Multiplexer   |

|                      |               |

| Register             | Register      |

|                      |               |

| Logic operators      | AND2          |

|                      | OR2           |

|                      | XOR2          |

|                      | Comparator    |

|                      | Not           |

|                      | Shifter       |

|                      | Barrel shift  |

|                      |               |

| Arithmetic operators | Adder         |

|                      | Subtractor    |

|                      | Shift-and-add |

|                      | Multiplier    |

|                      | Divisor       |

Table 5.2: Groups of elaborated SystemVerilog constructs

The generic *select* cell is unique as it does not have a cell equivalent in any cell library.

An *if* or *case* statement is elaborated into a generic *select* cell by Synopsys HDL compiler unless it is specified in the HDL representation that one wants it to be inferred as a multiplexer. The *select* statement is then synthesised by Synopsys DesignCompiler into either logic or a multiplexer depending on the available cells and unknown DesignCompiler conditions.

## 5.2 Liberty file format

The cell library's timing and power characteristics are found in a Liberty file. The Liberty file format is an industry standard used to describe cells of a particular technology. Information regarding timing, power, area, functionality and operating conditions of cells in the cell library can be found in this file.

The Liberty file consists of three types of statements:

#### • Group statements

A collection of statements grouped together. In a library, the uppermost group is a *library* group, and no other such groups can be made in a Liberty file. A group internal to the library can, for example, be a *cell* group, and a group internal to the cell can be a *pin* group.

#### • Attribute statements

A statement used to describe the characteristics of objects (groups) in the library. Such attributes can, for instance, be the size of a cell or the unit of leakage current in the library.

#### • Define statements