Johan Hopland Lofstad

# Alternative error prevention scheme for non-volatile memories

Master's thesis in Cybernetics and Robotics Supervisor: Geir Mathisen & Rainer Herold June 2019

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Engineering Cybernetics

Master's thesis

Johan Hopland Lofstad

## Alternative error prevention scheme for non-volatile memories

Master's thesis in Cybernetics and Robotics Supervisor: Geir Mathisen & Rainer Herold June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Engineering Cybernetics

NTNU Norges teknisk-naturvitenskapelige universitet Fakultet for informasjonsteknologi, matematikk og elektroteknikk Institutt for teknisk kybernetikk

#### **HOVEDOPPGAVE/MASTER THESIS**

Kandidatens navn:

Johan Hopland Lofstad

Fag:

Teknisk kybernetikk

Oppgavens tittel (norsk):

Alternativ feilhåndteringsmetode for ikke flyktig dataminne.

Oppgavens tittel (engelsk):

Alternative error prevention scheme for Non-volatile memories

#### **Oppgavens tekst:**

A weakness of Flash (NVM) Memory is the non-zero probability of a memory cell of flipping its logic state due to charge loss over time. Traditionally, to handle these problems, error correction is used, correcting the error after it has occurred. An error **prevention** scheme aims to detect and prevent these errors before they occur. The aim of this thesis is to explore and possibly develop such an error prevention scheme based on the flash memories cell charge.

#### Scope of thesis:

- Based on a literature study, describe how Error Correction Codes (ECC) are used today in NVM technologies based on Floating Gate Architecture.

- Based on a literature study, describe the characteristics of flash failure modes.

- Design and implement a simulator of flash memories, specifically emulating different failure modes of single bits.

- Design and implement an error prevention system of flash cells based on their cell charge using the simulator described above. Explore different solutions to the problem.

Oppgaven gitt: 09. January, 2019 Besvarelsen leveres: 03. June, 2019

Utført ved Institutt for Teknisk kybernetikk

Hovedveileder: Rainer Herold

Trondheim, den 09.01.2019

Geir Mathisen Faglærer

### Abstract

Flash memory is a common memory used in a variety of devices, using an electric charge to store data. This electric charge can leak and cause an error in the form of a bit-flip. Traditionally methods such as Error Correction Codes (ECC) has been used to mitigate these errors.

The following thesis presents an alternative to the conventional ECC method to find and reduce these errors. By measuring, storing, and evaluating the electrical charge over time, leakage can be detected and prevented before the error propagates into a failure.

To develop and test the proposed system, a simulator for flash has been developed. The simulator uses statistical properties collected from previous work to simulate a flash cell distribution with various error modes introduced.

The proposed error prevention system has been developed on the x86 platform as a proof of concept, with a port to AVR32 in mind. The system has been evaluated against the simulator, resulting in a functioning system. The proposed system manages to find, track, and reprogram cells with a leakage trending towards failure.

### Sammendrag

Flashminne er et vanlig dataminne brukt i en rekke enheter som bruker elektrisk ladning til å lagre data. Denne ladningen kan lekke og foråsake en bit-flip feil. Tradisjonelt har metoder som feilkorrigeringskoder (ECC) blitt brukt til å redusere disse feilene.

Følgende avhandling gir et alternativ til den konvensjonelle ECC-metoden for å finne og redusere forekommelsen av disse feilene. Ved å måle, lagre og evaluere den elektriske ladningen over tid kan denne lekkasjen detekteres og forhindres før det forplanter seg til en feil.

For å utvikle og teste det foreslåtte systemet har en simulator for flash blitt utviklet. Simulatoren bruker statiske egenskaper som er samlet fra tidligere arbeider til å simulere en fordeling av flash cellene. Forskjellige feilmoduser er introdusert i distribusjonen.

Det foreslåtte systemet har blitt utviklet mot x86 plattformen som et bevis på konseptet, hvor en port til AVR32 arkitekturen er tatt i betraktning. Systemet har blitt evaluert med simulatoren, med et fungerende system som resultat. Det foreslåtte systemet klarer å finne, følge og reprogrammere celler med en lekkasje som går mot en feil.

### **Preface**

This thesis is written for the department of cybernetics at NTNU (Norwegian University of Science and Technology) in collaboration with Microchip Technology Inc. The author of this thesis was approached by Microchip with a proposal to investigate erratic and moving bits in flash memories, and how these could be detected and prevented using internal test methods.

A prelude project for this thesis was conducted fall of 2018, exploring the problem of measuring the cell charge of flash memories internally. This thesis is largely based on the work from the prelude project written by the same author.

There are two supervisors for this thesis, Prof. Geir Mathisen from NTNU and Rainer Herold from Microchip. Rainer Herold provided supervision for the contents of the thesis. Rainer provided help with the direction of the thesis, which avenues to explore and general questions regarding non-volatile memory. Geir Mathisen has provided supervision for the structure of the thesis, such as the disposition and general layout.

Sections of the chapters Introduction, Theory and Literature Study has been taken from the prelude project. These sections has been marked. The remaining contents of the thesis is work done by the author during in the period January - June 2019.

Approved:

Prof. Geir Mathisen Supervisor of thesis

Approved:

Johan Hopland Lofs Author of thesis

### Table of Contents

| Tł | nesis d | lescription                         | i   |

|----|---------|-------------------------------------|-----|

| Ał | bstrac  | t                                   | ii  |

| Sa | mme     | ndrag                               | iii |

| Pr | eface   |                                     | iv  |

| Та | ble of  | Contents                            | v   |

| Li | st of ] | <b>Fables</b>                       | ix  |

| Li | st of I | ligures                             | xi  |

| Ał | bbrevi  | ations                              | xiv |

| 1  | Intr    | oduction                            | 1   |

|    | 1.1     | Background                          | 1   |

|    | 1.2     | Motivation                          | 1   |

|    | 1.3     | Limitations                         | 2   |

|    | 1.4     | Disposition                         | 2   |

| 2  | The     | ory                                 | 5   |

|    | 2.1     | Non-Volatile Memory                 | 5   |

|    |         | 2.1.1 Floating Gate Transistor      | 5   |

|    |         | 2.1.2 NAND Flash Memory             | 8   |

|    |         | 2.1.3 Multi-Level Cells (MLC)       | 9   |

|    | 2.2     | Error Correction Codes (ECC)        | 10  |

|    |         | 2.2.1 Hamming codes and parity bits | 10  |

|    | 2.3     | Machine Learning - Neural Networks  | 14  |

|    |         | 2.3.1 Neurons                       | 14  |

|   |      | 2.3.2 Neural Network                   |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|---|------|----------------------------------------|-----|---|---|-----|-----|-----|---|---|-----|---|--------|---|---|---|-----|----------|

|   |      | 2.3.3 Recurrent Neural Networks        |     | · | · |     | •   | • • | • | • |     | • | •      | • | • | • | . 1 | 5        |

| 3 | Lite | ature Study                            |     |   |   |     |     |     |   |   |     |   |        |   |   |   | 1   | 7        |

|   | 3.1  | Failure modes in Non-Volatile Memor    | у.  |   |   |     |     |     |   |   |     |   |        |   |   |   | . 1 | 7        |

|   |      | 3.1.1 Erratic bits                     |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     | 7        |

|   |      | 3.1.2 Moving Bits                      |     |   |   |     |     |     |   |   |     |   |        |   |   |   | . 1 | 9        |

|   | 3.2  | Error correction in Non-Volatile Mem   | ory |   |   |     |     |     |   |   |     |   |        |   |   |   | . 2 | 1        |

|   |      | 3.2.1 Classifying erratic bits         |     |   |   |     |     |     |   |   |     |   |        |   |   |   | . 2 | 1        |

|   |      | 3.2.2 Machine Learning approach        |     | • | • |     |     |     | • | • |     |   |        | • | • | • | . 2 | 3        |

| 4 | Snec | ification of project                   |     |   |   |     |     |     |   |   |     |   |        |   |   |   | 2   | 5        |

| • | 4.1  | Functional specifications              |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 4.2  | Acceptance criteria                    |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   |      |                                        |     | • | • |     |     |     | • |   |     | - | •      |   | • | - | . – | Ĩ        |

| 5 |      | gn of simulator                        |     |   |   |     |     |     |   |   |     |   |        |   |   |   | 2   |          |

|   | 5.1  | Introduction                           |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 5.2  | Simulation Loop                        |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 5.3  | Network Interface                      |     | · | • | • • | •   | ••• | • | • | • • | • | •      | • | • | • | . 2 | 9        |

| 6 | Imp  | ementation of simulator                |     |   |   |     |     |     |   |   |     |   |        |   |   |   | 3   | 1        |

|   | 6.1  | Introduction                           |     |   |   |     |     |     |   |   |     |   |        |   |   |   | . 3 | 1        |

|   | 6.2  | Simulation Loop                        |     |   |   |     |     |     |   |   |     |   |        |   |   |   | . 3 | 2        |

|   |      | 6.2.1 Calculating the next iteration   |     |   |   |     |     |     |   |   |     |   |        |   |   |   | . 3 | 3        |

|   | 6.3  | Temperature effect                     |     |   |   |     |     |     |   |   |     |   |        |   |   |   | . 3 | 6        |

|   | 6.4  | Network Interface & The manager Mo     |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     | 7        |

|   |      | 6.4.1 Command list                     |     |   | • |     | •   |     | • |   |     | • | •      | • | • | • | . 3 | 8        |

| 7 | Desi | gn of error prevention system          |     |   |   |     |     |     |   |   |     |   |        |   |   |   | 3   | 9        |

| • | 7.1  | Introduction                           |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 7.2  | Main Loop                              |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 7.3  | Storing data points                    |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 7.4  | Temperature effect                     |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

| 0 | T    |                                        |     |   |   |     |     |     |   |   |     |   |        |   |   |   | 4   | <b>7</b> |

| 8 | 8.1  | ementation of error prevention syste   |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     | -        |

|   | 8.2  | Searching                              |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     | -        |

|   | 0.2  | 8.2.1 Which cells to measure           |     |   |   |     |     |     |   |   |     |   |        |   |   |   | • • |          |

|   |      | 8.2.2 Which cells to store             |     | - | • |     | •   |     |   | • |     | - | •      |   | • | • |     |          |

|   |      | 8.2.3 Which cells to reprogram         |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   |      | 8.2.4 Removing data points             |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 8.3  | Storing data points                    |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 0.0  | 8.3.1 Adding data points               |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   |      | 8.3.2 Deleting data points             |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 8.4  | Simulator interfacing - Network Interf |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   | 8.5  | Main Loop - Putting it all together .  |     |   |   |     |     |     |   |   |     |   |        |   |   |   |     |          |

|   |      |                                        |     | • | - |     | · · |     | - | - | •   | - | ,<br>, | - | 1 | 1 | -   |          |

|    | 8.6    | Contro   | l Panel & Data                  | alog .    | ••• |       |       |    |     | • |     | • | • • | • | • | • | • |   |     |   | • | 55              |

|----|--------|----------|---------------------------------|-----------|-----|-------|-------|----|-----|---|-----|---|-----|---|---|---|---|---|-----|---|---|-----------------|

| 9  | Mac    | hine Le  | arning Appro                    | ach       |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 57              |

| ,  | 9.1    |          | iction                          |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 57              |

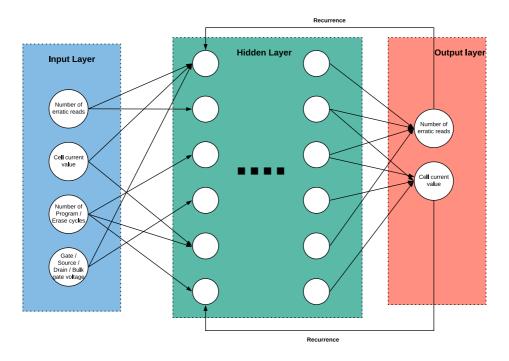

|    | 9.2    |          | rk                              |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 58              |

|    | 9.3    |          | ting data                       |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 58              |

|    |        |          | -                               |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   |                 |

| 10 |        |          | e effect on "F                  |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 61              |

|    |        |          | iction & Hypo                   |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 61              |

|    |        |          | ment setup and                  |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 61              |

|    |        |          | S                               |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 62<br>62        |

|    | 10.4   | Discus   | sion and Conc                   | lusion    | • • | • •   | • •   | ·  | ••• | • | • • | • | • • | • | • | • | • | • | ••• | · | • | 02              |

| 11 | Testi  | ing      |                                 |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 65              |

|    |        | -        | sts                             |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 65              |

|    |        | 11.1.1   | Storage mod                     | ule.      |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 66              |

|    |        |          | Search modu                     |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 66              |

|    |        | 11.1.3   | Simulator .                     |           |     |       |       |    |     | • |     |   |     |   |   | • |   |   |     |   |   | 67              |

|    | 11.2   | System   | Tests                           |           |     |       |       |    |     | • |     |   |     | • | • | • | • |   |     |   |   | 67              |

| 10 | D      | 14.      |                                 |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | <b>F</b> 1      |

| 12 | Resu   |          | 4 .                             |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | <b>71</b><br>71 |

|    |        |          | ests                            |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 71              |

|    |        |          | tor System Te<br>tion System Te |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 72              |

|    | 12.3   |          | Test one & ty                   |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 72              |

|    |        |          | Test three &                    |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 77              |

|    |        |          | Deletion of c                   |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 77              |

|    |        | 121010   | 20101101101                     | • • • • • | Gut | ap or |       | ·  |     | • |     | • |     | • | • | • | • | • |     | • | • |                 |

| 13 | Disc   | ussion   |                                 |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 81              |

|    | 13.1   | Simula   | tor                             |           |     |       |       |    |     | • |     |   |     | • | • | • | • |   |     |   | • | 81              |

|    |        |          | Moving Bits                     |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 81              |

|    |        |          | Erratic Bits                    |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 82              |

|    |        |          | Improving Pe                    |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 82              |

|    | 13.2   |          | Prevention Sys                  |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 83              |

|    |        |          | Mode one &                      |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 83              |

|    |        | 13.2.2   | System Perfo                    | ormanc    | e & | V18   | ıbili | ty | • • | • | • • | · | • • | • | • | • | · | • |     | · | · | 84              |

| 14 | Con    | clusion  |                                 |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 87              |

| 15 | Furt   | her Wo   | rk                              |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 89              |

| Bi | bliogr | aphy     |                                 |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 91              |

| A  | n      |          |                                 |           |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 0.2             |

| Ар | -      |          | ource Code<br>ew of files .     |           |     |       |       |    |     | • |     |   |     | • |   | • |   |   |     |   |   | <b>93</b><br>93 |

| Ар | pend   | ix B - P | relude Projec                   | t         |     |       |       |    |     |   |     |   |     |   |   |   |   |   |     |   |   | 95              |

### List of Tables

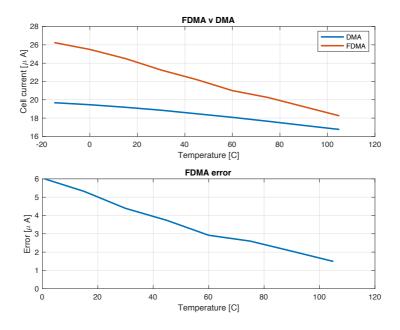

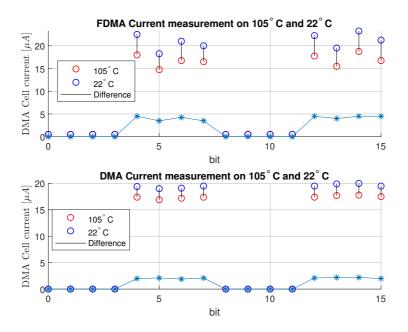

10.1 DMA and FDMA measured on different temperatures. . . . . . . . . . . . . . . . . . 62

### List of Figures

| A Floating Gate MOSFET (FGMOS) Transistor.                                                                                                                                                                                        | 6                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Illustration of current readout from a flash cell.                                                                                                                                                                                | 7                                                  |

| NAND Flash Configuration [18]                                                                                                                                                                                                     | 8                                                  |

| Two representation of MLC.                                                                                                                                                                                                        | 9                                                  |

| Illustration of block ECC codes.                                                                                                                                                                                                  | 10                                                 |

| ECC Flow. A message $m$ of length $k$ is encoded into a codeword $c$ of                                                                                                                                                           |                                                    |

|                                                                                                                                                                                                                                   |                                                    |

| codeword $r$ . The damaged codedword $r$ is decoded with the error cor-                                                                                                                                                           |                                                    |

|                                                                                                                                                                                                                                   | 11                                                 |

|                                                                                                                                                                                                                                   | 12                                                 |

|                                                                                                                                                                                                                                   | 12                                                 |

|                                                                                                                                                                                                                                   | 14                                                 |

| An illustration of a neural network [17]                                                                                                                                                                                          | 15                                                 |

| High level block diagram of a recurrent neural network                                                                                                                                                                            | 15                                                 |

| Computational graph of recurrent neural networks                                                                                                                                                                                  | 16                                                 |

| Positively charged cluster causing erratic behavior [19]                                                                                                                                                                          | 18                                                 |

|                                                                                                                                                                                                                                   |                                                    |

|                                                                                                                                                                                                                                   | 18                                                 |

| a) Schematics of a 3-dimensional distribution of traps building a leakage<br>path. b) Influence of misalignment on the band diagram of hthe effective<br>tunneling path c) Trap-assisted charge transport taking different energy |                                                    |

|                                                                                                                                                                                                                                   | 19                                                 |

|                                                                                                                                                                                                                                   |                                                    |

|                                                                                                                                                                                                                                   | 20                                                 |

| "Examples of different EB (Erratic Bit) signatures. Normal and Erratic                                                                                                                                                            |                                                    |

|                                                                                                                                                                                                                                   | 22                                                 |

| Reliability improvement with Proactive Bit Redundancy [4]                                                                                                                                                                         | 23                                                 |

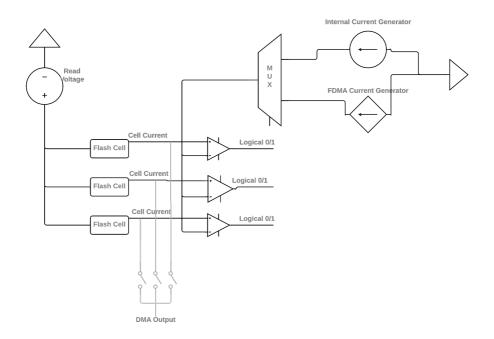

|                                                                                                                                                                                                                                   | Illustration of current readout from a flash cell. |

| 5.1                                                                                      | Flowchart of the simulation loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28                               |

|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> </ul> | UML Activity Diagram of the simulation loop.Simulation of a normal cell.Algorithm for calculating then next iteration of a normal cell.Simulation of a moving bit.Simulation of an erratic cell. Blue cells are showing normal behavior. Thered cell shows erratic behavior.A UML Sequence diagram showing the communication for a simulationspecific request.                                                                                                                             | 32<br>33<br>34<br>35<br>36<br>37 |

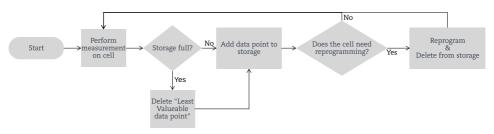

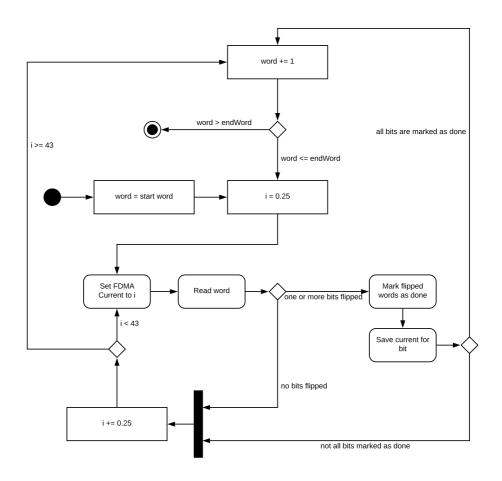

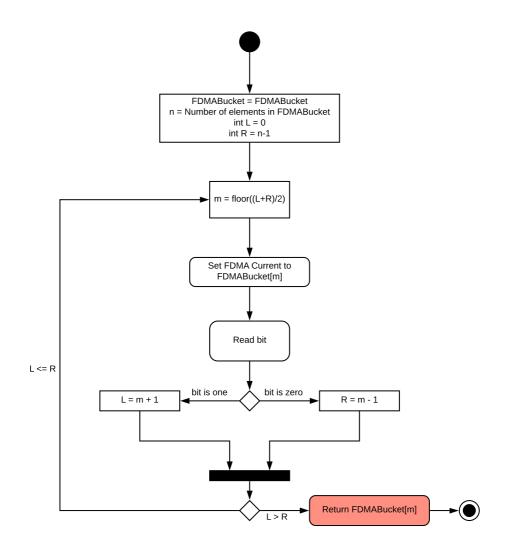

| 7.1<br>7.2                                                                               | The main loop of the system as a flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40<br>41                         |

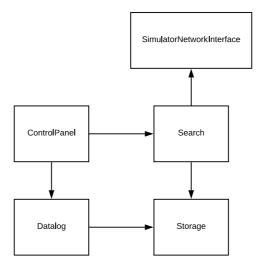

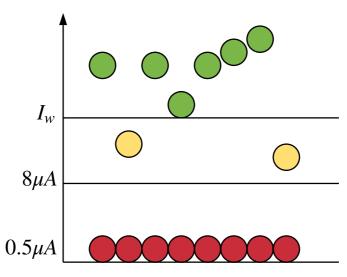

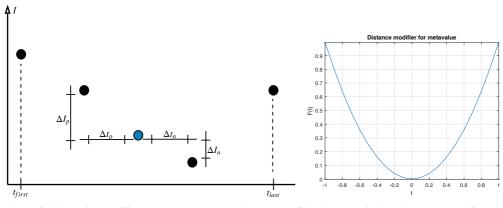

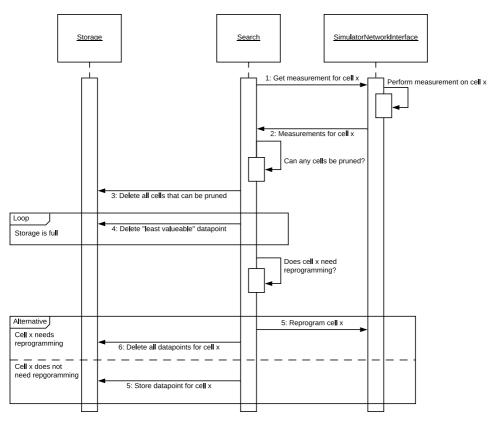

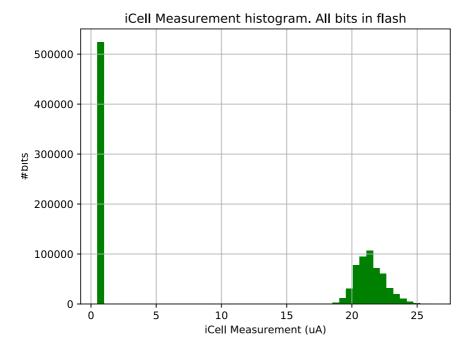

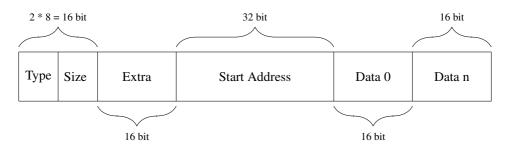

| 8.1<br>8.2                                                                               | The overall design of the error prevention system. Arrows indicate depen-<br>dency                                                                                                                                                                                                                                                                                                                                                                                                         | 44                               |

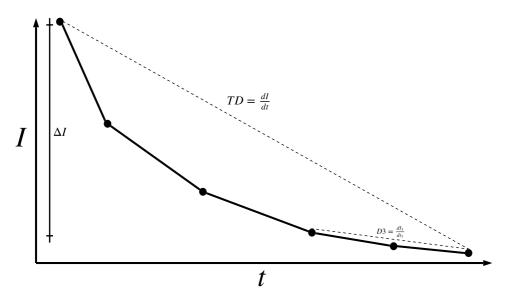

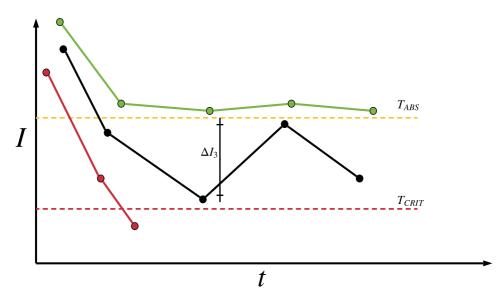

| 8.3<br>8.4<br>8.5                                                                        | programmed (0), green cells are erased (1), and yellow cells are the pro-<br>grammed cells below $I_w$ . Please note that this graph is 1D (no x line) Representation of metavalue $M$ from Eq 8.1 Definition of the different parameters used in Eq 8.2 A graph illustrating reprogramming on three different cells. The green cell is over the $T_{ABS}$ and is never reprogrammed. The red cell is below $T_{CRIT}$ and is always reprogrammed. The black cell is reprogrammed based on | 45<br>47<br>48                   |

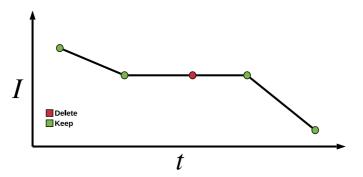

| 8.6<br>8.7                                                                               | $\Delta I_3$ and TD                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50<br>51<br>51                   |

| <ul><li>8.8</li><li>8.9</li><li>8.10</li></ul>                                           | Linked list implementation of data point storage. Each "block" can hold<br>one data point                                                                                                                                                                                                                                                                                                                                                                                                  | 52<br>53                         |

|                                                                                          | sponse.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>55<br>56                   |

| 9.1                                                                                      | An example of an RNN network for the given problem. Number of nodes in the hidden layer is only for illustration.                                                                                                                                                                                                                                                                                                                                                                          | 59                               |

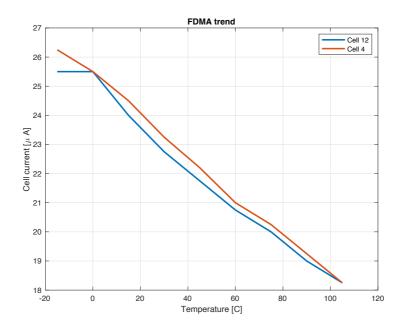

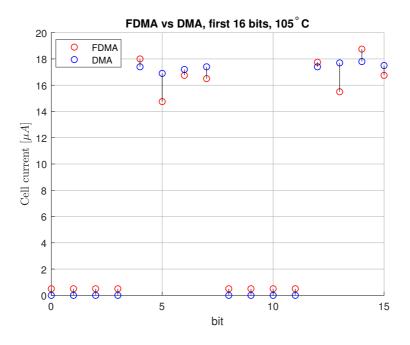

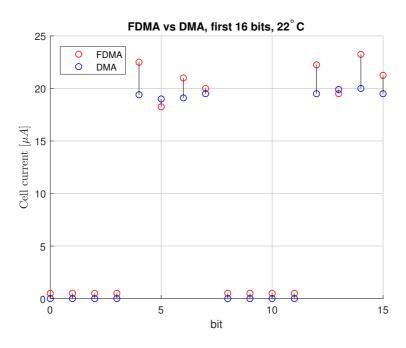

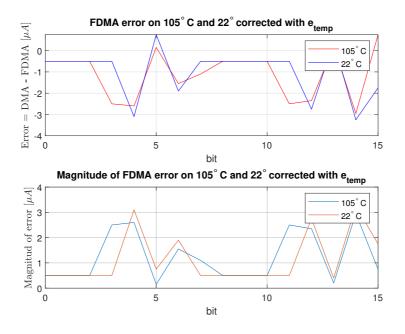

|                                                                                          | DMA and FDMA measured on different temperatures. The error ( $e =  DMA - FDMA $ ) is plotted for every temperature                                                                                                                                                                                                                                                                                                                                                                         | 63<br>63                         |

| 11.1                                                                                     | The four tests conducted on the prevention system. Modes are constant on the rows, reprogramming and erratic bits are constant on the columns                                                                                                                                                                                                                                                                                                                                              | 68                               |

| 12.1                                                                                     | Results from unit tests on the prevention system.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                               |

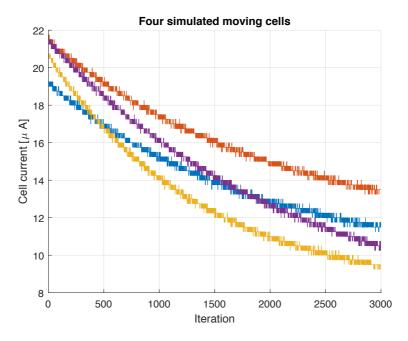

| 12.2  | Four simulated moving cells. All four bits follow a decaying exponential       |    |

|-------|--------------------------------------------------------------------------------|----|

|       | curve                                                                          | 73 |

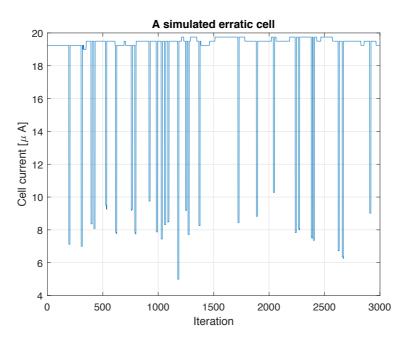

| 12.3  | A simulated erratic cell. Shows sudden jumps in the cell current levels,       |    |

|       | otherwise behaving like a normal cell                                          | 73 |

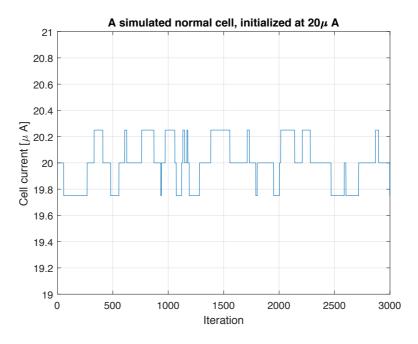

| 12.4  | A simulated normal bit. Cell current is more or less constant, shows minor     |    |

|       | fluctuations.                                                                  | 74 |

| 12.5  | Profiling results of the simulator. Time is the real-time the method used.     |    |

|       | Own time is the time used by the method subtracted the time used by called     |    |

|       | methods                                                                        | 74 |

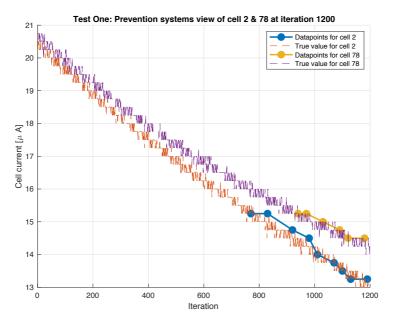

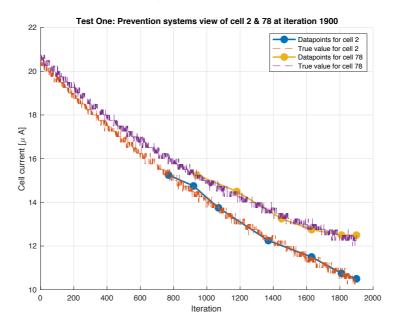

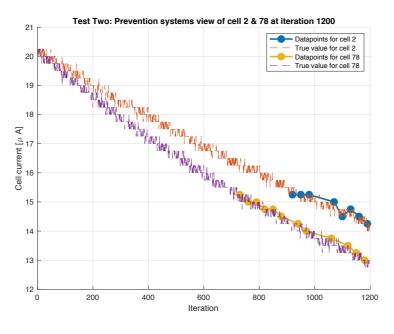

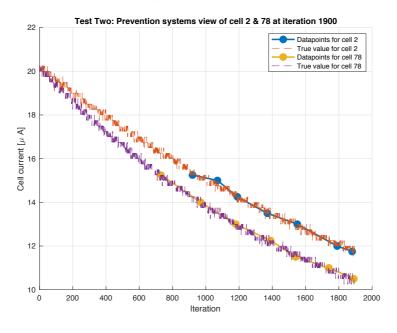

| 126   | <b>Test one</b> : Prevention system view of cell 2 & 78 at iteration 1200 and  | 74 |

| 12.0  | •                                                                              |    |

|       | 1900. The dots are the data points the prevention system has stored, the       | 75 |

|       | dotted lines is the "true" value, which the prevention system tries to follow. | 75 |

| 12.7  | Test two: Prevention system view of cell 2 & 78 at iteration 1200 and          |    |

|       | 1900. The dots are the datapoints the prevention system has stored, the        |    |

|       | dotted lines are the "true" values, which the prevention system tries to       |    |

|       | follow                                                                         | 76 |

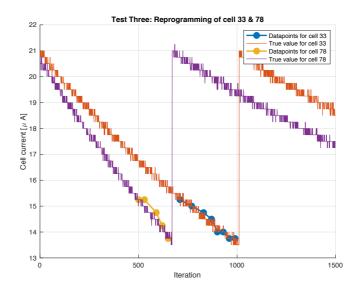

| 12.8  | Test Three: Prevention system view of two cells being reprogrammed.            |    |

|       | Yellow and blue dots are the datapoints from the prevention system, dotted     |    |

|       | lines are from the simulator.                                                  | 77 |

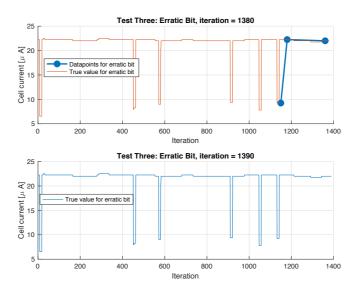

| 12.9  | Test Three: Prevention system view of an erratic cell for iteration 1380       |    |

|       | and 1390. Erratic prune removed all data points from 1380 to 1390              | 78 |

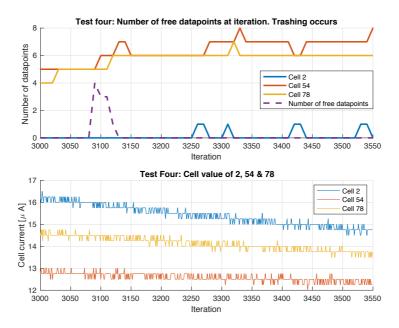

| 12 10 | <b>Test Four:</b> Evidence of trashing. Cell 2 does not get to keep any of its | 10 |

| 12.10 | data points, as they are discarded immediately.                                | 78 |

| 10.11 |                                                                                | 10 |

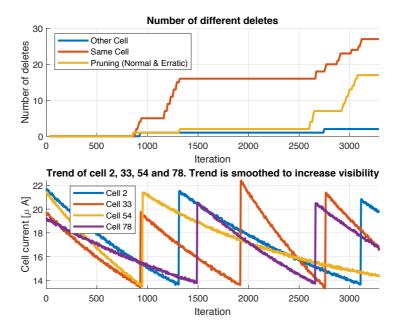

| 12.1  | The amount of different deletes performed plotted against the real trend of    | 70 |

|       | all the moving cells in the system.                                            | 79 |

### Abbreviations

| RNN          | = | Recurrent Neural Network   |

|--------------|---|----------------------------|

| ECC          | = | Error Correction Codes     |

| HW           | = | Hardware                   |

| NVM          | = | Non-Volatile Memory        |

| MLC          | = | Multi Level Cell           |

| FGMOS        | = | Floating Gate Mosfet       |

| BER          | = | Bit Error Rate             |

| PD           | = | Program Disturb            |

| mXT          | = | MaxTouch <sup>®</sup>      |

| FN Tunneling | = | Fowler Nordheim Tunneling  |

| DMA          | = | Direct Memory Access       |

| FDMA         | = | Fast Direct Memory Access  |

| IC           | = | Integrated Circuit         |

| PR           | = | Presence Ratio             |

| ToL          | = | Time Of Life               |

| JSON         | = | Javascript Object Notation |

|              |   | 1 5                        |

### Introduction

#### 1.1 Background

Flash memories are a commonly used type of Non-Volatile Memory<sup>1</sup>. These memories are used in a wide variety of applications, such as Solid State Drives (SSD) for personal computers and holding the program code for microcontrollers.

These memories use an electrical charge to store its logical state, zero or one. Flash memories suffer from a weakness where the logical state of a cell can flip due to anomalous charge loss. This charge loss happens over time due to imperfections in the silicon known as traps. It may take months to years before the charge loss accumulates high enough to cause an error.

Hardware Error Correction Codes (HW ECC)<sup>2</sup> is widely used in various forms to reduce these errors. ECC are numerical codes calculated from the logical state of several cells and can correct multiple errors. These codes are especially common when a flash cell holds more than one bit in a Multi-Level Cell (MLC).

#### 1.2 Motivation

HW ECC comes at a significant silicon cost and introduces overhead when reading and writing. A software solution could be explored to reduce this cost. If a software solution were to obtain the same accuracy as the HW solution, error correction codes must be stored on the flash. Thus a partition of the flash must be reserved for storing these codes, as well as introducing CPU overhead larger than the HW ECC solution.

<sup>&</sup>lt;sup>1</sup>Memory which does not lose data on power loss

<sup>&</sup>lt;sup>2</sup>ECC implemented with hardware, i.e. with silicon and not software

Instead, an error prevention scheme is proposed. The charge level<sup>3</sup> can be measured and stored. By looking at the trend and value of the stored measurements, it might be possible to predict a cell failure before it happens. Such a solution would require less storage, and the measurement and calculations could take place as the CPU idles.

#### 1.3 Limitations

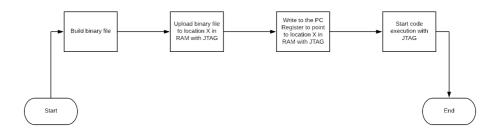

This thesis limits itself to a proof of concept for such a system. It is not implemented on an AVR32-Microcontroller (which is the targeted architecture), but on  $x86^4$ . The x86 platform gives access to more powerful debugging tools, simulators, and faster evaluation of different strategies.

A system which measures the cell current of flash cells has been previously developed in [5], and is therefore not a part of this thesis. Small summaries from [5] are found throughout the text where the relevant background knowledge is needed.

A challenge with writing this text is the abstraction level. As this project is a deeply technical one, the interesting results and problems occur on a particularly low abstraction level, which requires the reader to have certain background knowledge. At the same time, the text should be easily readable to understand what has been done and what the results represent.

Because of this challenge, parts of the text is not required to read if the reader does not desire a deeper understanding. Throughout the text, these "non-mandatory" sections have been attempted marked, and the reader is free to skip these on his or her leisure.

#### 1.4 Disposition

This section gives a quick overview of what the different chapters contain.

**Chapter 2: Theory** introduces the theory needed to understand non-volatile memory, flash memory, ECC codes, and machine learning. This is required reading to understand the problem at hand.

**Chapter 3: Literature Study** explores two failure modes in non-volatile memory, specifically erratic and moving bits. It looks at the current state of error correction codes in NVM and a new machine learning approach which shows promise but has no known wide commercial use at the time of writing.

**Chapter 4: Specification of project** outlines the project specification and acceptance criteria. It presents what is to come in the coming chapters.

<sup>&</sup>lt;sup>3</sup>The actual electrical charge, not the logical state

<sup>&</sup>lt;sup>4</sup>Intel x86 is the architecture most modern PCs use

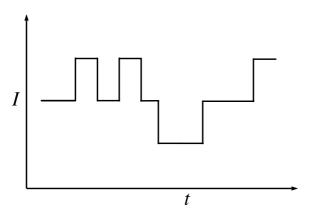

**Chapter 5: Temperature effect on FDMA (Fast Direct Memory Access)** presents an experiment performed on the temperature effect on FDMA. It proposes a hypothesis, presents the experimental setup and methodology before concluding after a discussion.

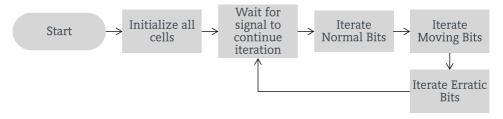

**Chapter 6: Design of Simulator** introduces how a simulator of the flash is designed. To test the proposed error prevention system, a simulator is required for rapid development. It goes into how the simulation loop functions, which error modes are simulated and how its interface works.

**Chapter 7: Implementation of Simulator** introduces an implementation of the design in Chapter 6. It discusses the simulation loop in detail, how the different types of cells are calculated for the next iteration. Other topics include temperature effect, network interface, and an accompanying command list.

**Chapter 8: Design of Error Prevention System** introduces how the error prevention system is designed. It discusses the main loop of the system, measuring, storing, and reprogramming cells. The chapter ends with a summary from the prelude project on the measurement system and a discussion on storing data points and dealing with temperature.

**Chapter 9: Implementation of Error Prevention System** outlines the implementation of the design in Chapter 8. It includes the different modules and their interaction and which cells are measured, stored, and reprogrammed in detail. It finishes with the storage module and a section on the main loop, putting it all together.

**Chapter 10: Machine Learning Approach** outlines and discusses a machine learning approach. The proposed approach is an alternative to the error prevention system. The chapter presents a starting point for a design with an accompanying discussion.

**Chapter 11: Testing** explains the setup and methodology for the tests performed on the error prevention system and simulator. It presents unit tests and system tests for both systems.

**Chapter 12: Results** presents the results gathered from the chapter on testing. This includes the results of the unit tests, system tests, a performance analysis of the simulator, and accompanying plots.

**Chapter 13: Discussion** discusses the results obtained, and if the acceptance criteria have been met.

The remaining chapters, **Conclusion** and **Further Work** concludes the thesis and proposes further work on the topic.

### Theory

This chapter presents theory which might be required to understand the rest of the text. The theory presented is on non-volatile memory, with the floating gate transistor and how it used in a NAND flash configuration and the difference between SLC and MLC technology. An introduction on error correction codes with an emphasis on Hamming codes follows. The chapter finishes with an introduction to machine learning, neural network, and recurrent neural networks.

#### 2.1 Non-Volatile Memory

The following section on Non-Volatile memory is taken from the theory section in [5] with some modifications and additions. The section on MLC and parts on NAND Flash Memory is new.

Digital memory is often divided into two categories, volatile and non-volatile. Non-volatile memory, in contrast to volatile memory, retains data on power loss. One type of non-volatile memory is called Flash memory<sup>1</sup>. Flash memory is widely used in several applications where high capacity, low cost non-volatile memory is needed, and uses the **floating gate MOSFET** to store data.

#### 2.1.1 Floating Gate Transistor

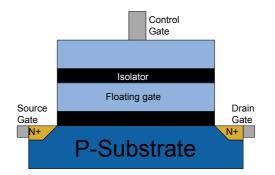

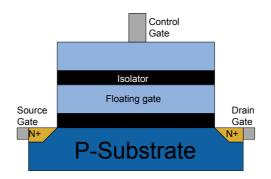

Every bit in a flash memory is a Floating Gate MOSFET, abbreviated to **FGMOS**. An illustration can be seen in Figure 2.1 and consists of three gates, the *control, source* and *drain* gate. The structure is similar to a conventional MOSFET which have the same gates.

<sup>&</sup>lt;sup>1</sup>The name comes from its fast erase, it erases in a "Flash"

In a conventional MOSFET transistor, as a voltage is applied to the control gate, current is allowed to flow from the source to the drain. This happens as the "barrier" between the N-Type and P-Type silicon are broken down, allowing electrons to freely move across from source to drain. In a MOSFET transistor the current from source to drain is a function of the voltage on the gate,  $I_{sd} = g(V_c)$ . In flash memory, every such FGMOS is referred to as a **cell**.

Figure 2.1: A Floating Gate MOSFET (FGMOS) Transistor.

In a MOSFET the amount of voltage applied on the control gate when it becomes conductive is called the **threshold voltage**. In other words, the threshold voltage is the minimum voltage needed to make the p-substrate become conductive.

The principal idea in a FGMOS is to store electric charge in the so called "floating gate", which sits in the middle of two isolators, i.e. completely electrically isolated. This allows for the storage of data in the form of charge in the floating gate which persists when power is lost. When there is no charge, the cell is labeled as **erased** and has a logical value of *one*. When there is a set amount of charge, the cell is labeled as **programmed** and has a logical value of *zero*.

In order to read a cell (i.e. measure the charge in the floating gate), a voltage is applied on the control gate (as in a MOSFET). However, in contrast to a MOSFET the FGMOS also contains charge in the floating gate "resisting" the p-substrate to become conductive. In other words, the amount of voltage required to make the transistor conductive is a function of both applied voltage and stored charge in the floating gate  $V_{threshold} = g(V_{gate}, Q_{floating gate})$ .

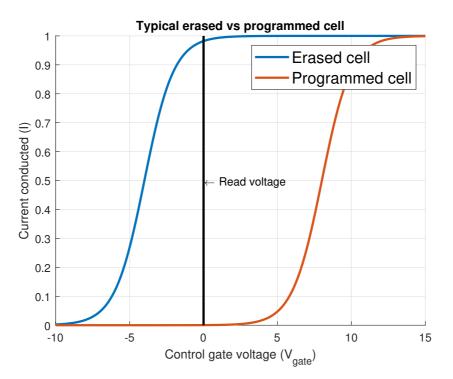

A related concept to the threshold voltage is the **cell current**. When applying a known fixed voltage between the source and drain gate, and a known fixed voltage on the control gate (called the **read voltage**), the current between the source and drain is the cell current. As the threshold voltage increases with an increasing  $Q_{floating gate}$ , the transistor becomes more conductive and thus more current flows. In flash memories, the cell current is used to determine if a cell is programmed or erased.

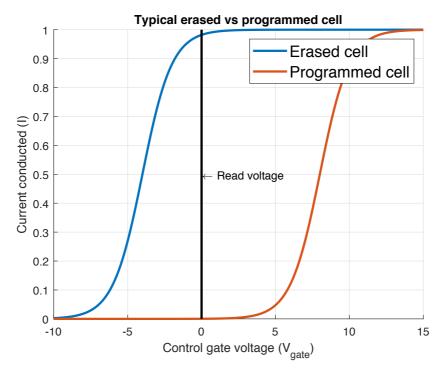

The cell current for a typically erased and programmed cell is shown in Figure 2.2. Both follow the *sigmoid* function, but they are shifted related to each other. The erased cell

conducts "all" the current at the read voltage of zero volts while the programmed cell outputs no current at all. This is the general idea of how a flash cells state is read.

In order for a flash cell to be useful, it must be able to be programmed and erased. The question is how to insert charge in the isolated floating gate. One way of adding and removing charge is **Fowler Nordheim Tunneling (FNT)**, which lets electrons "tunnel" through isolators. To **erase** a cell and remove the charge, a high voltage is applied between the control gate and source. By FNT, the charge is tunneled through the isolator, removing the charge.

To **program** a cell, a high voltage between the source and drain is applied. A high sufficiently high voltage between the control gate and ground makes the transistor conductive. If these conditions are met, a high current flows from source to drain, making some electrons to jump into the floating gate. This technique is called **hot electron injection**.

As these high voltages and currents damage the transistor, a flash cell has a limited amount of program / erase cycles. After the transistor has been programmed / erased an amount of time, charge starts to leak from the floating gate until it is unable to hold charge for useable amount of time.

Figure 2.2: Illustration of current readout from a flash cell.

#### 2.1.2 NAND Flash Memory

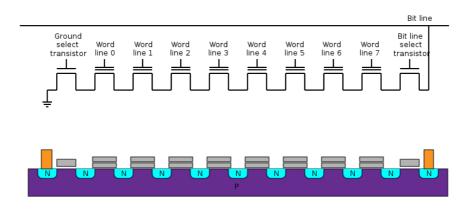

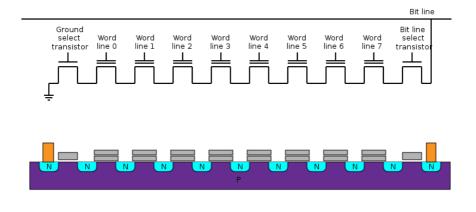

NAND (Not-AND) Flash memory is a type of **non-volatile** memory where the data is stored in a hierarchy of floating gate MOSFETs. The term **NAND** refers tosec:temperature-effect-on-fdmaected in series as can be seen in Figure 2.3.

The memory is divided into **blocks** with a number of **pages**. A page is defined as all the bits connected to the same word line. A *block* contains 32 or 64 pages and is the smallest *erasable* unit. A *page* is typically 2 or 4 Kbytes and is the smallest *programmable* unit [12]. When **reading** a NAND flash, the read voltage is applied to the *wordline* of the bit (a word

Figure 2.3: NAND Flash Configuration [18].

is a collection of bits, usually in the size of 16, 24 or 32 bits, the wordline selects which word is read). The *bit line select transistor* for the desired bit is set high. All the other wordlines in the bitline are set to a high voltage (Figure 2.3 is one bitline). This makes all the other transistors in the bitline conductive no matter the stored charge, as can be seen from the graph in Figure 2.2. The current value of the cell can now be read at the bitline.

Since it is not possible to erase individual bits, a full **erase-write** cycle must be performed when changing a bit. The data already existing on the block must be stored somewhere else, the block must be erased before the altered data can be written back to all the pages in the block. This degrades the oxide layer on the FGMOS, until a point where it can

no longer hold the charge on the floating gate. This is why flash memory has a **limited number of writes/erases** before it is no longer usable.

To increase the lifetime of a flash memory, several techniques are applied. By storing **Error Correction Code (ECC)** for each block, the flash controller can detect faulty blocks and mark them as unusable. The flash controller also tries to spread out the writes between all the block, such that no block is written to excessively [12].

#### 2.1.3 Multi-Level Cells (MLC)

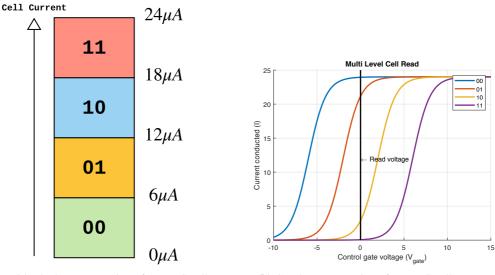

All the flash cells introduced so far only holds one bit per FGMOS transistor; this is called SLC (Single Level Cell). However, multiple bits are encoded into the same cell to increase the density of flash memories. Such a scheme is called MLC (Multi-Level Cell). Figure 2.4 shows two representations of this encoding. The main difference is that SLC only has two states (0 or 1), while MLC has four or more states (00, 01, 10, 11).

(a) Block representation of an MLC cell.

(b) Graph representation of an MLC cell.

Figure 2.4: Two representation of MLC.

The most significant advantage of MLC compared to SLC is the increased density. An MLC cell can hold quadruple the storage as SLC for the same amount of silicon. The biggest drawback is the endurance, as it is more susceptible to cell current drift. This drift is caused by the state limits being closer together, and as such erratic and moving bits are a much bigger problem. As errors occur more frequently in MLC, more advanced error correction mechanisms are applied compared to SLC[7, 8].

#### 2.2 Error Correction Codes (ECC)

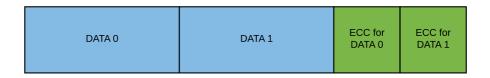

Error correction codes (ECC) are numerical codes used to correct errors in data. When the data is "healthy" (no error has occurred), the respective ECC for that piece of data is calculated and stored. This extra data can then be used to detect and repair errors. These codes are beneficial to mitigate errors in NVM, and is the primary method to handle NVM error modes such as erratic and moving bits.

There are several ECC algorithms which fall into two main categories, **Block ECC**, and **Convolutional ECC**. Block ECC calculates codes for a *block* which is a fixed size of data. Figure 2.5 shows the concept of data blocks with their respective ECC data. Convolutional ECC uses a circular pattern to store information but is not covered in this thesis.

Figure 2.5: Illustration of block ECC codes.

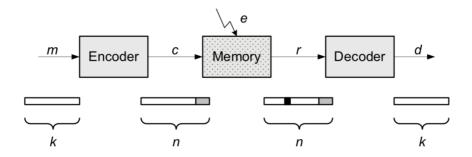

The basic concept is illustrated in Figure 2.6. A block of data or *message* ( $\mathbf{m}$ ) is encoded into a *codeword* ( $\mathbf{c}$ ). A codeword is the data *plus the error correction code*. This codeword is stored in memory, as illustrated in Figure 2.5. As an error occurs, the stored codeword is damaged. When decoding the codeword, this error is corrected as long as the damage is not too great.

A **syndrome** is calculated to detect errors. The syndrome is a vector indicating which bit positions an error has occurred and if it can be salvaged.

#### 2.2.1 Hamming codes and parity bits

Hamming codes are a type of **Linear Block Error Correction Codes** first introduced by Richard Hamming, hence the name. Due to their simplicity and effectiveness, Hamming codes are widely used.

#### **Parity Bits**

Hamming codes uses the concept of *parity bits* to encode the data. A parity bit is an extra bit put onto a block, indicating if there is an even or odd number of one's. For instance, the 8-bit message [1, 0, 0, 1, 1, 0, 1, 0] would generate a parity bit of zero, as there is an even number of one's.

Figure 2.6: ECC Flow. A message m of length k is encoded into a codeword c of length n. An error e occurs on the codeword c resulting in the damaged codeword r. The damaged codedword r is decoded with the error corrected into d. Figure taken from [8].

The big drawback of such a parity bit scheme is that it can only detect errors, and not correct them. If a parity bit of one is recorded, and the message is read as [1, 0, 0, 1, 1, 0, 1, 1] (the last bit is corrupted), the scheme would only know that an error has occurred, and not which bit caused the error. That is, it can detect *single bit errors, but correct none*

#### **Hamming Codes**

Hamming codes solve the correction problem of parity bits, by allowing for correction and not just detection. The basic idea is to use more than one parity bit, and compare the results between these parity bits. Hamming codes are best explored through an example.

#### Example: Hamming[7,4] correction

A hamming code with four bits is encoded with three parity bits, creating a seven-bit message called the Hamming[7,4] code. Imagine wanting to encode the message m as shown in Eq 2.1.

$$m = \begin{bmatrix} m_1 & m_2 & m_3 & m_4 \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & 1 \end{bmatrix}$$

(2.1)

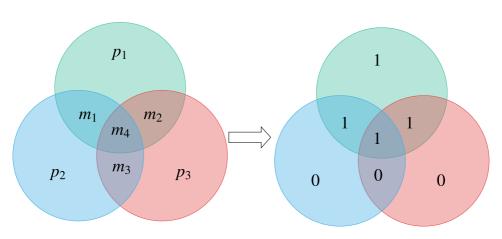

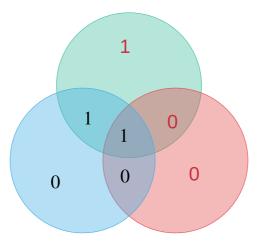

There are three parity bits:  $p_1$ ,  $p_2$  and  $p_3$ . These indicate the parity of different sets of data bits. Specifically  $p_1$  indicates the parity of  $m_1$ ,  $m_2$  and  $m_3$ .  $p_2$  indicates the parity of  $m_1$ ,  $m_3$  and  $m_4$ .  $p_3$  indicates the parity of  $m_2$ ,  $m_3$  and  $m_4$ . For instance,  $p_1 = 1$  as there is an even number of one's in  $m_1$ ,  $m_2$  and  $m_3$ . This is illustrated as a venn diagram in Figure 2.7.

Imagine an error occurs for  $m_2$ , giving us  $m_c = \begin{bmatrix} 1 & 0 & 0 & 1 \end{bmatrix}$ . When calculating p for  $m_c$ , one finds that  $p_1$  and  $p_3$  changes, while  $p_2$  stays constant. From this one can conduct that the error is in the intersection between  $p_1, p_3$ , but not in the intersection  $p_1, p_2$  or  $p_1, p_3$ , which leaves one bit namely  $m_2$  as the faulty bit. This is illustrated in Figure 2.8

Figure 2.7: Hamming[7,4] illustrated as a venn diagram.

Figure 2.8: Hamming[7,4] illustrated as a venn diagram.

#### Generating the codeword and syndrome with matrices

As Hamming codes are linear, the encoding process can be done with a simple matrix modulo two multiplication. The codeword c of the message m is calculated in Eq 2.2. The matrix G is called a *Generator Matrix*

$$c = mG \tag{2.2}$$

As described above, the **syndrome** indicates whether or not an error has occurred. For hamming codes, the syndrome s on the corrupted codeword r is also calculated with a simple matrix calculation.

$$s = rH^T \tag{2.3}$$

The H Matrix is called the *Parity Check Matrix*. How to produce the G and H matrices are not discussed here.

#### Example: Hamming[7,4] with matrices

Imagine the same problem as the earlier example, but this time solved using matrices. The message  $m = \begin{bmatrix} 1 & 1 & 0 & 1 \end{bmatrix}$  is corrupted to  $m_c = \begin{bmatrix} 1 & 0 & 0 & 1 \end{bmatrix}$ . Two possible forms of the G and H matrix for Hamming[7,4] are given in Eq 2.4.

$$G = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix} H = \begin{bmatrix} 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 \end{bmatrix}$$

(2.4)

Notice the form of  $G = [I_k|A]$ . The columns in A indicates our parity bits. The first column indicates  $m_2$ ,  $m_3$  and  $m_4$ , the second  $m_1$ ,  $m_3$  and  $m_4$  and so forth.

#### **Step 1: Calculate the codeword** *c*

$$c = mG$$

$$= \begin{bmatrix} 1 & 1 & 0 & 1 \end{bmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 1 & 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix}$$

$$= \begin{bmatrix} 1 & 1 & 0 & 1 & 2 & 2 & 3 \end{bmatrix}$$

$$= \begin{bmatrix} 1 & 1 & 0 & 1 & 0 & 0 & 1 \end{bmatrix}$$

Remember that these are modulo two multiplication, hence the last equality.

#### Step 2: Introduce error and calculate syndrome

The error (e) is introduced into our codeword (c).

$r = c + e = \begin{bmatrix} 1 & 0 & 0 & 1 & 0 & 0 \end{bmatrix}$

As per Eq 2.3, the syndrome s is

$$s = rH^{T}$$

$$= \begin{bmatrix} 1 & 0 & 0 & 1 & 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 1 & 0 & 1 & 0 & 1 & 0 & 1 \end{bmatrix}$$

$$= \begin{bmatrix} 2 & 1 & 2 \end{bmatrix}$$

$$= \begin{bmatrix} 0 & 1 & 0 \end{bmatrix} = 2$$

The last equality is due to 010 in binary equals two as H was constructed for this property, indicating that the **error is in the second bit position**.

#### 2.3 Machine Learning - Neural Networks

Artificial Neural Networks is a type of machine learning that mimics biological neural networks to learn and predict mathematical functions. In essence, given a set of X's and Y's, a neural network tries to predict F as accurately as possible where Eq 2.5 holds [11, 13, 9].

$$Y = F(X) \tag{2.5}$$

#### 2.3.1 Neurons

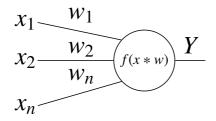

A neural networks is built on **neurons**, which are takes some input X and produces one output, an illustration of which is shown in Figure 2.9. The weights (w's in Figure 2.9) determine how much each input controls the output of the neuron. The function f is called the **activation function**<sup>2</sup>, and determines the output Y depending on the input X and weights W.

Figure 2.9: A neuron with input X, evaluation function f and output Y.

#### 2.3.2 Neural Network

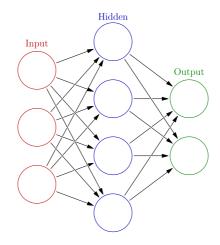

A **neural network** is obtained by combining these neurons in a network, connecting the output of some neurons to the input of other neurons. Most often neurons are arranged in *layers* as seen in Figure 2.10, which has three layers (input, hidden and output). One might stumble on the term **deep neural network**, which refers to a neural network with many layers <sup>3</sup>, hence the naming *deep*.

The first layer is widely referred to as the **input layer**, which takes the input to the network. The last layer is the **output layer**, which outputs the final result. The network is **trained** by giving it training data in the form of (X, Y) pairs. The error on the output  $(e = output \ of \ last \ layer - Y)$  is propagated backward in the network to figure out how much each weight w contributed to the error. This is called **backpropagation**. By using gradient descent, these weights are gradually updated with each training example to converge towards the true function F.

<sup>&</sup>lt;sup>2</sup>There exists many activation functions, but a commonly used function is the *sigmoid function* <sup>3</sup>How many layers for a network to become deep is not defined

Figure 2.10: An illustration of a neural network [17].

#### 2.3.3 Recurrent Neural Networks

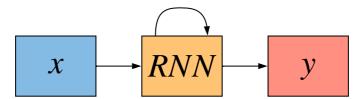

The neural network described above is a **feed-forward network** (FFN) as the information is fed forward in the network, and nothing feeds backward (all computation goes from left to right). FFN assumes that the decision is independent of the previous decision, which is not always the case. The concept of **Recurrent Neural Networks** (**RNN**) was introduced to solve this problem.

Imagine the problem of predicting the next character in a sequence given the previous character. For instance, a neural network which generates sentences. If the first decision was a "T", then it is more likely that the next character is an "h" then a "p". By using a hidden state  $h_t$ , and updating this state after every computation, the network stores information on previous computations.

A high-level block diagram of an RNN is shown in Figure 2.11. As with conventional neural networks, an input vector x feeds into the network producing an output y. However, in addition to producing the y, the internal state h is updated as indicated by the arrow in Figure 2.11.

Figure 2.11: High level block diagram of a recurrent neural network.

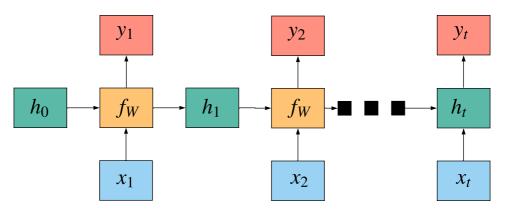

The general equation for the hidden state in a recurrent neural network is Eq 2.6.

$$h_t = f_W(h_{t-1}, x_t) \tag{2.6}$$

Where

- $h_t$  is the hidden state at "time" t

- $f_W$  is some function with some weights W

- $h_{t-1}$  is the hidden state at "time" t-1

- $x_t$  is the input at "time" t

In order to understand RNNs, it might be helpful to look at its computational graph in Figure 2.12. At the start our hidden state is initialized as  $h_0$ . When the first input arrives,  $x_1$ , the  $f_W$  function takes both  $h_0$  and  $x_1$  and computes  $h_1$  as in Eq 2.6 and outputs the result y. When  $x_2$  is entered, the network remembers by using  $h_1$ .

Figure 2.12: Computational graph of recurrent neural networks.

# Chapter 3

### Literature Study

This chapter presents the literature study preceding the design and implementation. The first part presents failure modes in Non-Volatile Memory, classifying two common modes of failures. The second part looks at a machine learning approach taken to mitigate these errors.

If the reader does not seek a deeper understanding of these topics, parts of this chapter can be skipped. It is recommended that the basics are understood, such as definitions, before proceeding to the next chapter.

#### 3.1 Failure modes in Non-Volatile Memory

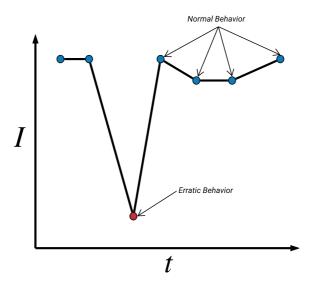

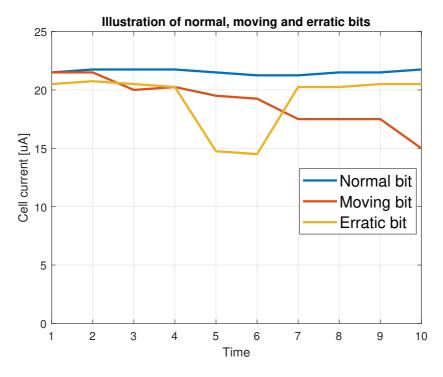

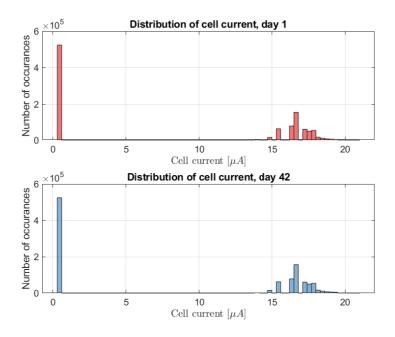

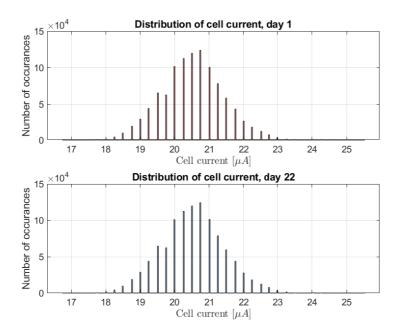

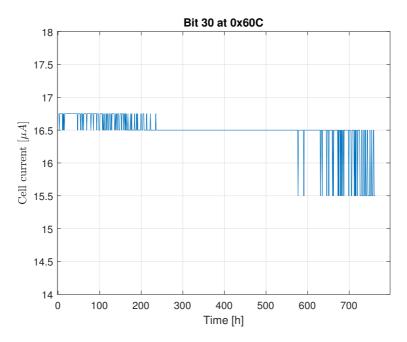

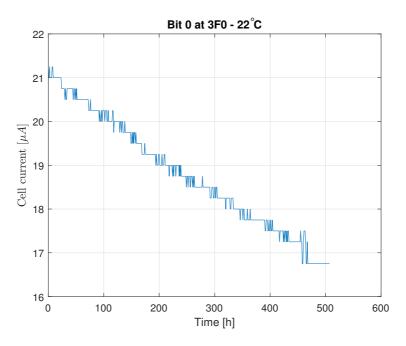

Flash cells have multiple failure modes, with two of the most common being **erratic** and **moving bits**. A moving bit loses charge over time, causing an error when the leaked charge accumulates to a high enough level. An erratic bit shows sudden and unexpected jumps in charge levels while not showing a clear trend as a moving bit.

#### 3.1.1 Erratic bits

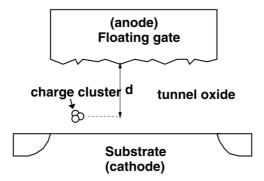

An erratic bit is defined as a bit showing sudden and unexpected jumps between threshold voltage. These jumps are thought to be caused by positively charged clusters in the FG-MOS isolator. These clusters are caused by high voltage during erase and programming operations, such as Fowler-Nordheim tunneling [3].

The erratic behavior occurs through the dynamics of the creation or destruction of the clusters. These clusters are created by hot electron injection and destroyed by thermally

emitted electrons detrapping the clusters [19]. An illustration of such a charged cluster can be seen in Figure 3.1.

Figure 3.1: Positively charged cluster causing erratic behavior [19].

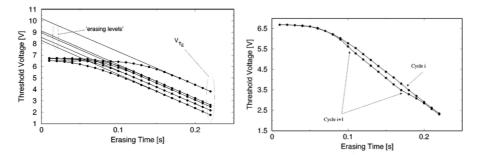

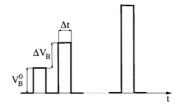

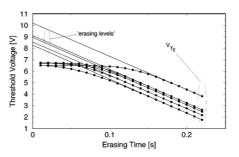

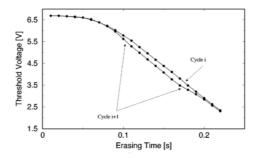

There have been attempts to analyze the behavior of these erratic bits such as *Analysis of erratic bits in flash memories* by Chimention [3]. A special erase pulse was applied on some flash cells, measuring their threshold voltage after each pulse. Healthy bits followed a linear trend as seen in Figure 3.2a, while erratic bits showed a deviation from the linearity as seen in Figure 3.2b.

(a) Healthy bit linear trend during special erasing (b) Erratic bit linear trend deviation during special pulse [3]. erasing pulse[3].

**Figure 3.2:** Healthy and erratic bit threshold voltage trend with special erase pulse. Figures taken from [3].

#### 3.1.2 Moving Bits

The following subsection on moving bits is taken from the literature study in [5].

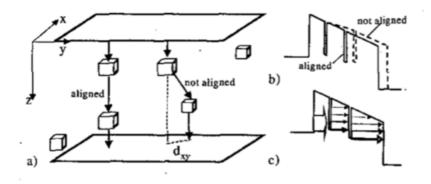

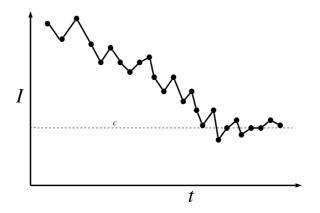

A bit is defined as **moving** when its threshold voltage moves slowly over time, on a timescale of months to years due to anomalous charge loss. One way moving bits differ from erratic bits is that moving bits are more predictable. By measuring the threshold voltage over time, a moving bit can be identified by looking at the slope. According to Schuler "Anomalous charge loss in cells with tunnel oxide thickness of more than 6.4 nm results from chains of at least two or more less aligned defects" [14].

The rest of this section explores the reason for this leakage. *This gives insight into the nature of moving bits but is not necessary to understand or follow the rest of the text.*

When used to make electrical circuits, parts of the semicoductor is "doped" to either be conductive or isolating. Sometimes atoms are not doped correctly, causing them to stay semiconducting when designed to be isolating.

The defects Schuler writes about are these "wrong" atoms and are known as **traps**, which forms a conductive path through the silicon. Figure 3.3a illustrates how these traps construct this conductive path. If these traps align, a conductive path is constructed. This causes the electric charge stored in the cell to slowly leak over time.

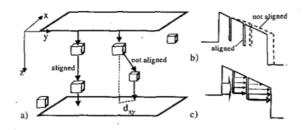

Figure 3.3: a) Schematics of a 3-dimensional distribution of traps building a leakage path.b) Influence of misalignment on the band diagram of hthe effective tunneling pathc) Trap-assisted charge transport taking different energy lvels into account. Figure taken from [14].

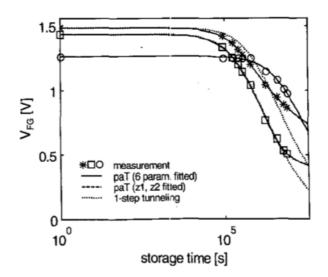

According to F. Schuler, the leakage current can be modelled exponentially by a 1-step

tunneling model.

$$I_{leak} = \sigma A_{FN} F^2 exp\{-\frac{4}{3h}\sqrt{2qm^*(\phi_1 - \Delta\phi)^3} \frac{1 - (1 - \frac{Fx_t}{(\phi_1 - \Delta\phi)})^{\frac{3}{2}}}{F}\}$$

(3.1)

$$\Delta\phi = \sqrt{\frac{qF}{4\pi\epsilon_{ox}\epsilon_0}} \qquad (3.2)$$

Where

- $\Delta \phi$  is the barrier lowering

- F is the electric field

- $A_{FN}$  is the Fowler-Nordheim parameter

- $\phi_i$  is the trap depth

- $\sigma$  is the effective cross-section

- $x_t$  is the tunneling distance

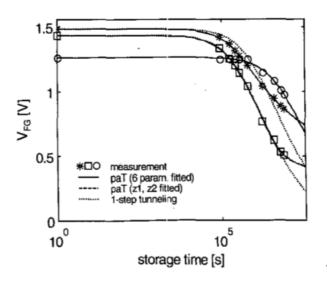

The full model explanation can be found in [14]. The model in Eq 3.2 is a simplified version of the *Multi-Phonon-Assisted tunneling model* presented in the same study, where the *trap to trap* distance was found as the most dominant parameter. The multi-phonon-assisted tunneling model found that there is a slow down of charge loss of some bits, which the simplified model could not predict as shown in Figure 3.4.

**Figure 3.4:** Measured transient charge loss of some typical Moving Bits as well as the simulated charge loss characteristic using the multi-phonon-assisted tunneling. Figure taken from [14].

## 3.2 Error correction in Non-Volatile Memory

Error correction codes are prevalent in flash memory due to the reliability issues with floating gate [8, 7]. In later years there has been an increase in the usage of MLC (Multi-Level Cell) technologies, which incorporates several bits on the same FGMOS transistor. As such, most modern research on increasing endurance in flash memory is done on MLC cells, as they are much more susceptible to error modes such as moving and erratic bits.

Traditionally simple Hamming code has been used on SLC, and are still used to some extent. It has however been an increase in the use of cyclic error correction codes such as Bose-Chaudhuri-Hocquenghem (BCH) codes, as simple linear codes such as Hamming codes are no longer sufficient on the larger page sizes of MLC [2, 8].

BCH codes offer multiple error correction capabilities, and efficient decoding algorithms exist. A major drawback of BCH codes is the need for highly parallel implementations too met the speed requirements for decoding, especially for MLC with large page sizes. A large area of silicone is needed to meet this speed requirement.

A paper by Chen et al. explored the possibility to use Reed-Solomone (RS) codes for error correction in NAND memories, and thus reduce the area needed [2]. RS codes are especially good at correcting burst errors, while errors in flash memories are random errors (they appear one at a time), making them on the surface not seem like an appealing choice. Chen argues that the reduction in complexity gained from RS codes compared to BCH codes still gives it a significant advantage.

The paper concludes with

"It can be concluded that the RS codes can achieve similar error correcting performance as the BCH codes in MLC flash memory applications with lower decoding complexity. Therefore, RS codes are more suitable for these applications. [2]"

#### **3.2.1** Classifying erratic bits

The following section explores a method for classifying erratic bits. *This gives insight into the nature of erratic bits but is not necessary to understand or follow the rest of the text.*

In *Erratic Bits Classification for Efficient Repair Strategies in Automotive Embedded Flash Memories*, Zambelli et al. looked at classifying erratic bits into different categories. The classification method is proposed to be during processes such as Wafer Sort in the factory to monitor which type of erratic bit occurs in the specific flash implementation. By using these result, it is possible to speculate on the best strategy to combat erratic bits (ECC, Redundancy bits, or other solutions).

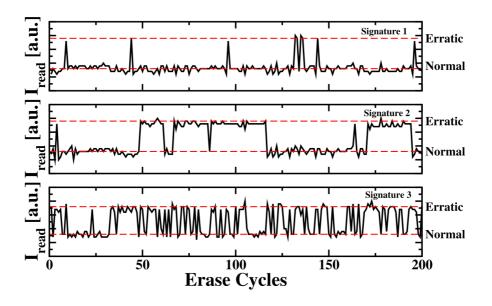

The paper proposes two statistical properties to classify erratic bits.

1. "**Presence Ratio** (**PR**) is defined as the ratio of the erratic event occurrences during the test concerning the total erase cycles number" [19]

2. "Time of Life (ToL) is defined as the maximum number of consecutive erase cycles displaying erratic behavior." [19]

In simpler terms, *PR* tells how much erratic behavior is taking place while *ToL* tells how long an erratic behavior lasts. By calculating the average of these properties, they can be used to define three signatures for erratic bits.

- Signature 1: Low PR (lower than the average PR) and short ToL(shorter than the average ToL)

- Signature 2: High PR, Long ToL

- Signature 3: High PR, Short ToL

Figure 3.5 shows an example of a erratic bit under the signatures described above.

**Figure 3.5:** "Examples of different EB (Erratic Bit) signatures. Normal and Erratic states for the read current ( $I_{read}$ ) are highlighted for clarity" [19].

Zambelli suggests that the first signature can be treated only by ECC, as they occur quite seldom. The second signature can be treated with redundancy bits, as they have a higher occurrence probability and have predictable failing behavior. The third signature is very unpredictable and often occurs, making them the most dangerous for the flash. These can be handled with either redundancy or ECC.

#### 3.2.2 Machine Learning approach

The following sections look at using machine learning to reduce flash failures in contrast with traditional ECC. It is recommended reading before Chapter 9.

One of the big drawbacks of ECC is the amount of redundant storage required. In order to recover about 1-2% of the errors in a page, 5-10% of the memory area is needed to store this information [4]. This 1-2% error is referred to as the **Bit Error Rate (BER)**.

In order to reduce the amount of redundant information stored, a machine learning approach has been explored to predict cell failure [4, 10]. By predicting cell failure, **redundant bits** for these predicted cells can be stored instead of ECC for the entire page. Redundant bits only require 1% of data to recover 1% of the memory area, vastly reducing the amount of storage needed in contrast to conventional ECC solutions.

In "Machine Learning Prediction for 13x Endurance Enhancement in ReRAM SSD System", such as solution was explored for ReRAM. ReRAM is a type of Non-Volatile memory which shows promise but suffers from a higher variability than traditional flash memories [4, 1]. The study explored several solutions to predicting cell failure, two machine learning approaches, and one non machine learning approach.

Two prediction types were evaluated, one to predict random behavior between PRO-GRAM/ERASE cycles, and one to predict likely-to-fail cells. Both of these types were tested on different machine learning methods, *Random Forest, Neural Network* and *Support Vector Machine*.

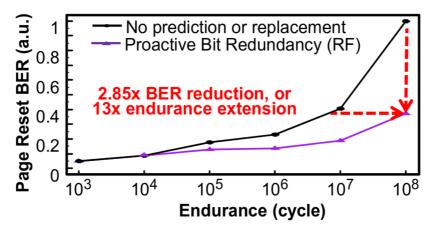

The "predict likely-to-fail cells" used 12 variables on  $12 * 10^3$  points of data. As can be seen in Figure 3.6, the endurance can either be increased by 13 times, or the BER can be reduced by 2.85 times compared to having no prediction or replacement. The best result came from the Random Forest algorithm, predicting 65% of the failures correctly.

Figure 3.6: Reliability improvement with Proactive Bit Redundancy [4].

#### Attempts made on flash memories

There has been some attempt to use machine learning for flash in the same manner as ReRAM. In "Machine Learning-Based Proactive Data Retention Error Screening in 1Xnm TLC NAND Flash", the usage of machine learning algorithms to detect "Program Disturb" errors. A **program disturb** (**PD**) error is the phenomena where a neighbouring cell is incorrectly programmed. These *PD-Weak* cells have 2.4x worse data retention than their non-weak cells [10].

The study used three different machine learning algorithms, *Logistic Regression, Random Forest* and *Support Vector Machine*. Two metrics were used to describe the performance, *detection rate* and *cost* which are both described in Eq 3.3 and Eq 3.4

$$Detection \ rate = \frac{Correctly \ identified \ PD \ cells}{All \ PD \ Weak \ Cells}$$

(3.3)

$$Cost (False Detection) = \frac{Incorrectly detected as PD - Weak}{All PD Weak Cells}$$

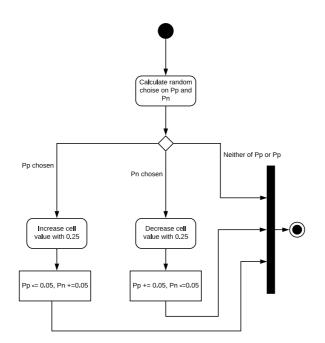

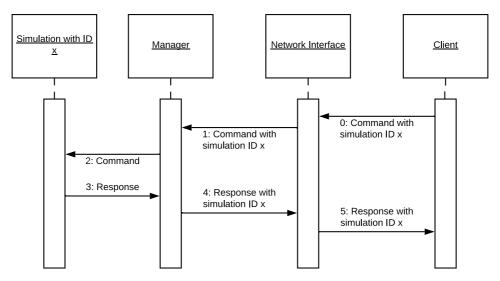

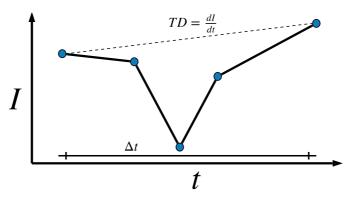

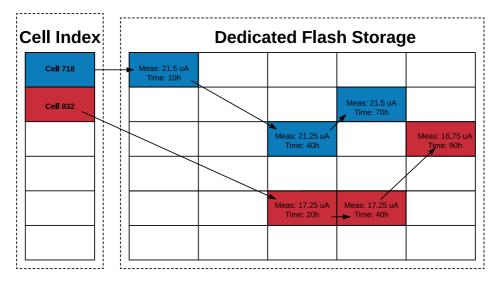

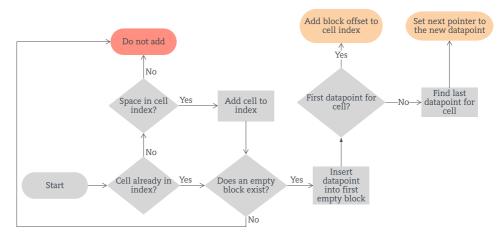

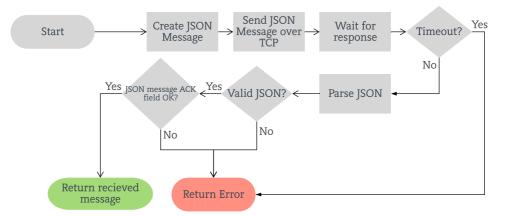

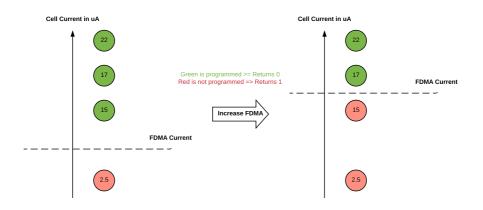

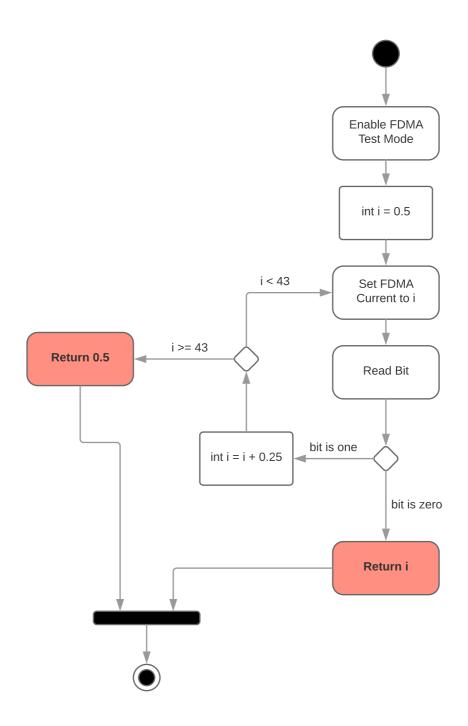

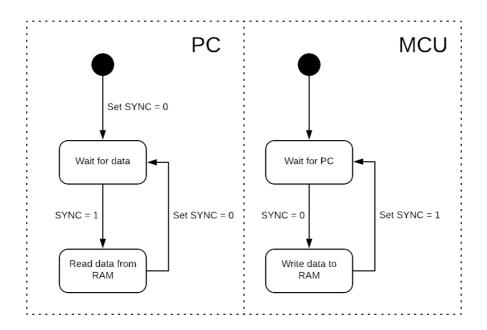

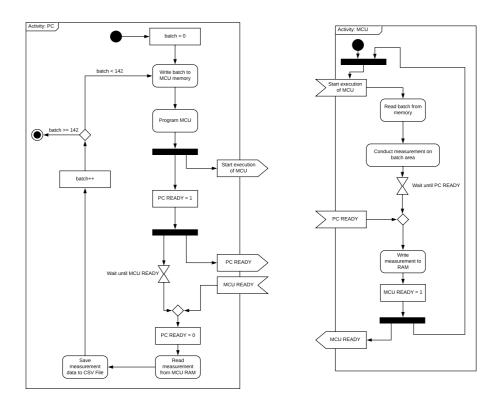

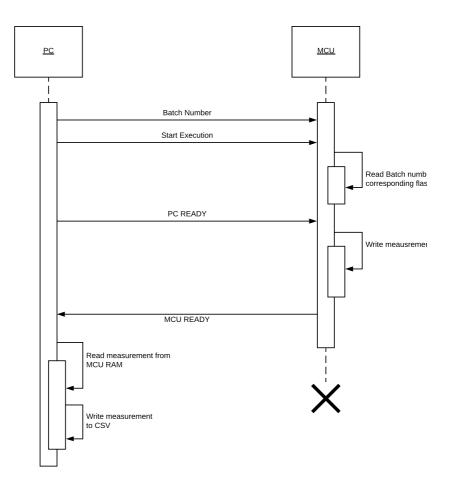

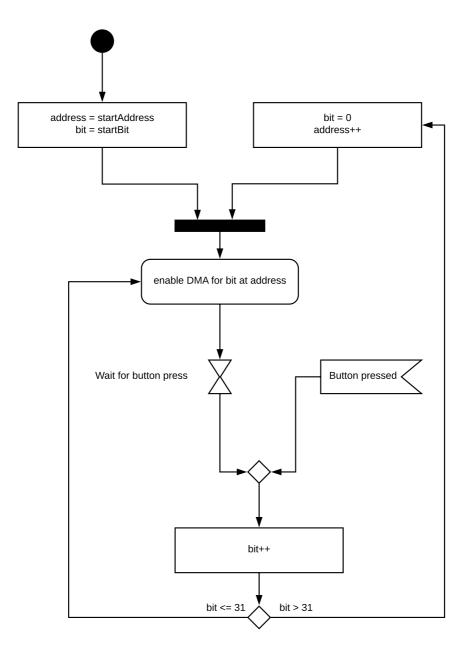

(3.4)