Dordije Boskovic

## Hardware implementation of a target detection algorithm for hyperspectral images

Master's thesis in Embedded Computing Systems June 2019

Master's thesis

NDrwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

Dordije Boskovic

## Hardware implementation of a target detection algorithm for hyperspectral images

Master's thesis in Embedded Computing Systems Supervisor: Kjetil Svarstad and Milica Orlandic June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

## Abstract

Hyper-Spectral Imager for Oceanographic Applications (HYPSO) is being developed as a part of SmallSat laboratory at NTNU. The satellite capable of capturing and processing of hyperspectral images will be equipped with Zynq-7000 on-board processing system consisting of ARM<sup>®</sup>-based processor with the hardware programmability of an FPGA. FPGA offers inherent reconfigurability, smaller size and weight, substantially lower power consumption and reduced costs, compared to its counterpart in other technologies. In this thesis, a part of on-board hyperspectral processing in FPGA is explored.

Hyperspectral images obtained by imaging spectrometer contain a vast amount of data which require techniques such as target detection to extract useful information. This thesis presents implementations of target detection algorithms for hyperspectral images. The algorithms are implemented as hardware-software partitioned system on Xilinx Zynq-7000 development platform. Prior to FPGA implementation, the algorithms such as ACE, SAM, CEM and ASMF were reviewed and tested on 5 different hyperspectral datasets. The detection performance of the algorithms was evaluated using MCC score, visibility score and ROC curves.

Two FPGA solutions for target detection are presented: HW/SW partitioned design and full FPGA solution. The designs were modelled using VHDL in attempt to gain the most optimal solution for our application. The operations of algorithms are partitioned on the heterogeneous platform between processing system and programmable logic with special consideration of background estimation. In HW/SW partitioned design, background estimation is performed prior to detection statistic calculation, while in full-FPGA implementation background is estimated in real-time as image frames are captured using the imager. Both solutions provide certain advantages depending on the desired application. Algorithm modelling and testing was performed in MATLAB environment, while FPGA modules were synthesized using Xilinx Vivado Design Suite.

In addition to target detection algorithm implementations, PPI endmember extraction algorithm was implemented using Vivado HLS. This implementation illustrates productivity benefits of a C-based development flow using HLS.

## Preface

This master's thesis is the final part of my Master of Science degree in Embedded Computing Systems (EMECS). The thesis work was conducted at the Norwegian University of Science and Technology within a SmallSat project (HYPSO). It is an exploratory work concerning topics such as hyperspectral remote sensing and FPGA design. As I have not been introduced to hyperspectral imaging prior to the specialization and thesis work, it has been a challenging learning experience, but also a gratifying and rewarding practice which has greatly improved my research skills.

First of all, I would like to thank my supervisor Milica Orlandić for her support, encouragement and great guidance. Our work together resulted in my first conference paper, awarded as the best student paper. Furthermore, I would like to thank my fellow students in the SmallSat lab for creating supportive environment in which one could pleasantly work and socialize. Special thanks to my family and friends for their continuous support throughout the years.

Đorđije Bošković June, 2019

## Table of Contents

| Su | Summary    |                                              |      |  |  |

|----|------------|----------------------------------------------|------|--|--|

| Pr | Preface ii |                                              |      |  |  |

| Та | ble of     | Contents                                     | v    |  |  |

| Li | st of T    | <b>Fables</b>                                | viii |  |  |

| Li | st of F    | ligures                                      | xi   |  |  |

| Ał | obrevi     | ations                                       | xii  |  |  |

| 1  | Intro      | oduction                                     | 1    |  |  |

|    | 1.1        | Motivation                                   | 1    |  |  |

|    | 1.2        | Hyperspectral imaging and processing         | 1    |  |  |

|    | 1.3        | Target Detection in context of HYPSO mission | 2    |  |  |

|    | 1.4        | HYPSO mission payload                        | 4    |  |  |

|    | 1.5        | Main contributions                           | 5    |  |  |

|    | 1.6        | Structure of the Thesis                      | 6    |  |  |

| 2  | Back       | sground                                      | 7    |  |  |

|    | 2.1        | Hyperspectral data representation            | 7    |  |  |

|    |            | 2.1.1 Geometrical data representation        | 8    |  |  |

|    |            | 2.1.2 Spectral variability and mixing        | 8    |  |  |

|    |            | 2.1.3 Statistical data representation        | 9    |  |  |

|    |            | 2.1.4 Hyperspectral image organization       | 10   |  |  |

|    | 2.2        | Pixel Purity Index Algorithm                 | 12   |  |  |

|    | 2.3        | Target detection algorithms                  | 13   |  |  |

|    |            | 2.3.1 Spectral angle mapper                  | 14   |  |  |

|    |            | 2.3.2 Constrained energy minimization        | 14   |  |  |

|    |            | 2.3.3 Adaptive coherence/cosine estimator    | 15   |  |  |

|   |      | 2.3.4    | Adjusted Spectral Matched Filter                                    | 16 |

|---|------|----------|---------------------------------------------------------------------|----|

|   | 2.4  |          | inversion                                                           | 17 |

|   |      | 2.4.1    | Gauss-Jordan elimination                                            | 17 |

|   |      | 2.4.2    | LU decomposition with partial pivoting                              | 18 |

|   |      | 2.4.3    | Sherman-Morrison formula                                            | 19 |

|   |      | 2.4.4    | Computational complexity of algorithms                              | 19 |

|   | 2.5  | Overvi   | ew of Zynq-7000, FPGA cores and primitives                          | 20 |

|   |      | 2.5.1    | DSP blocks on Zynq                                                  | 20 |

|   |      | 2.5.2    | AXI protocols                                                       | 21 |

|   |      | 2.5.3    | DMA core                                                            | 22 |

|   |      | 2.5.4    | Block RAM                                                           | 23 |

|   |      | 2.5.5    | AXI divider                                                         | 24 |

|   | 2.6  |          | HLS                                                                 | 25 |

|   | 2.7  |          | of-the-art target detection algorithm implementations on FPGA plat- |    |

|   |      |          |                                                                     | 27 |

|   |      |          |                                                                     |    |

| 3 | Revi | ew of st | tate-of-the-art target detection algorithms                         | 29 |

|   | 3.1  | Hypers   | spectral datasets                                                   | 29 |

|   |      | 3.1.1    | Salinas scene                                                       | 29 |

|   |      | 3.1.2    | Hopavågen scene                                                     | 31 |

|   |      | 3.1.3    | Indian Pines scene                                                  | 31 |

|   |      | 3.1.4    | Pavia University scene                                              | 33 |

|   |      | 3.1.5    | HyMap Cooke City scene                                              | 34 |

|   | 3.2  | Target   | detection performance metrics                                       | 36 |

|   |      | 3.2.1    | Matthews correlation coefficient                                    | 36 |

|   |      | 3.2.2    | Receiver operating characteristic curve                             | 37 |

|   |      | 3.2.3    | Visibility score                                                    | 37 |

|   | 3.3  | Target   | detection algorithm adaptations                                     | 37 |

|   |      | 3.3.1    | Adaptive Cosine Estimator using correlation matrix                  | 38 |

|   | 3.4  | Algorit  | thm testing                                                         | 39 |

|   |      | 3.4.1    | Salinas scene                                                       | 39 |

|   |      | 3.4.2    | Hopavågen scene                                                     | 40 |

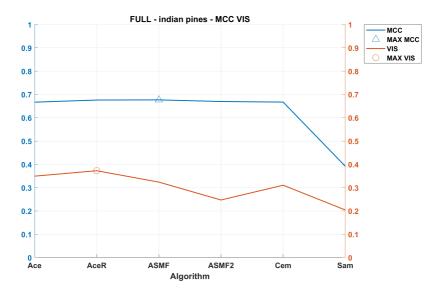

|   |      | 3.4.3    | Indian Pines scene                                                  | 40 |

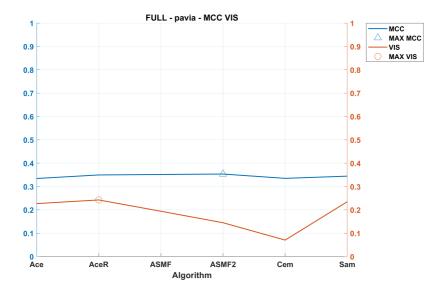

|   |      | 3.4.4    | Pavia University scene                                              | 41 |

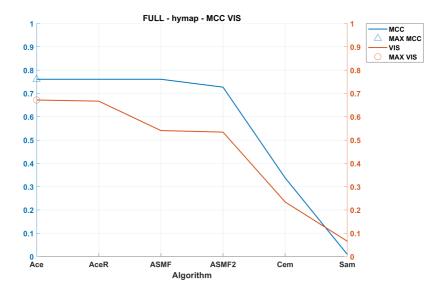

|   |      | 3.4.5    | HyMap Cooke City scene                                              | 41 |

|   |      |          |                                                                     |    |

| 4 | FPG  | A imple  | ementation                                                          | 43 |

|   | 4.1  |          | are-Software codesign implementation                                | 43 |

|   |      | 4.1.1    | Input logic                                                         | 44 |

|   |      | 4.1.2    | Processing logic                                                    | 46 |

|   |      | 4.1.3    | Output logic                                                        | 51 |

|   |      | 4.1.4    | Software solution for using the FPGA accelerator                    | 52 |

|   | 4.2  |          | PGA implementation                                                  | 53 |

|   |      | 4.2.1    | Adaptation of inverse matrix calculation for FPGA implementation    | 53 |

|   |      | 4.2.2    | Adaptation of target detectors for real-time processing             | 55 |

|   |      | 4.2.3    | Input logic                                                         | 56 |

|    |             | 0 0                                                | 58<br>51  |

|----|-------------|----------------------------------------------------|-----------|

|    |             |                                                    | 53        |

|    | 4.3         |                                                    | 54        |

| 5  | Res         |                                                    | 7         |

|    | 5.1         | 8 I                                                | 57        |

|    |             |                                                    | 57        |

|    |             | 5.1.2 Resource utilization                         | 58        |

|    |             | 5.1.3 Detection performance analysis               | 1         |

|    | 5.2         | Full FPGA implementation results    7              | '5        |

|    |             | 5.2.1 Performance analysis                         | '5        |

|    |             |                                                    | 6         |

|    |             | 5.2.3 Detection performance analysis               | 7         |

|    | 5.3         | PPI algorithm implementation results               | 81        |

| 6  | Con         | clusion 8                                          | 33        |

|    | 6.1         | Target detection algorithms    8                   | 33        |

|    | 6.2         | FPGA implementations                               | 33        |

|    | 6.3         | Future work   8                                    | 34        |

| Bi | bliog       | aphy 8                                             | 85        |

| Aŗ | pend        | ices 8                                             | <b>19</b> |

| A  | Dim         | ensionality reduction 8                            | <b>19</b> |

| В  | Usin        | g HW/SW codesign implementation on Zynq platform 9 | 91        |

|    | <b>B</b> .1 | Creating project in Xilinx Vivado                  | )1        |

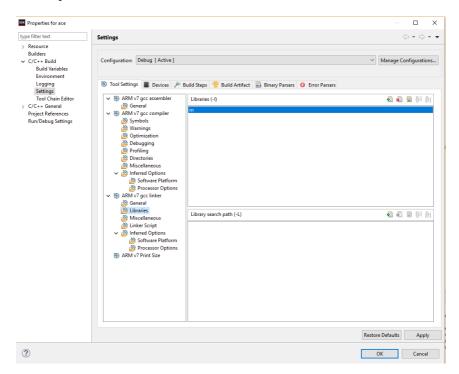

|    | <b>B</b> .2 |                                                    | 92        |

|    | B.3         | Synthesis and implementation                       | 94        |

|    | <b>B.</b> 4 |                                                    | )4        |

## List of Tables

| 2.1 | Vivado HLS optimization directives                                           | 26 |

|-----|------------------------------------------------------------------------------|----|

| 3.1 | Salinas ground truth endmembers                                              | 30 |

| 3.2 | Hopavågen ground truth endmembers                                            | 31 |

| 3.3 | Indian Pines ground truth endmembers                                         | 32 |

| 3.4 | Pavia University ground truth endmembers                                     | 33 |

| 3.5 | HyMap Cooke City ground truth - targets                                      | 35 |

| 4.1 | AXI-lite register file description for HW/SW codesign solution               | 45 |

| 4.2 | Stage 2 multiplexer signals and products                                     | 47 |

| 4.3 | Stage 3 multiplexer signals and products                                     | 48 |

| 4.4 | Generics and example values for HW/SW codesign solution                      | 49 |

| 4.5 | AXI-lite register file description for full FPGA solution                    | 56 |

| 4.6 | Fixed-point data types for Sherman-Morrison implementation                   | 62 |

| 4.7 | Generics for full FPGA solution                                              | 62 |

| 5.1 | Performance comparison for HW/SW codesign solution                           | 68 |

| 5.2 | Performance analysis of HW modules for HW/SW codesign solution               | 68 |

| 5.3 | Resource utilization report 32x16, 16 bands, 32-bit intermediate data, HW/SW | 7  |

|     | codesign solution                                                            | 69 |

| 5.4 | Resource utilization report 25x16, 16 bands, 25-bit intermediate data, HW/SW | 7  |

|     | codesign solution                                                            | 69 |

| 5.5 | Comparison of detection performance scores for fixed- and floating-point     |    |

|     | solutions; Salinas scene using HW/SW codesign solution                       | 71 |

| 5.6 | Comparison of detection performance scores for fixed- and floating-point     |    |

|     | solutions; HyMap scene, target signature F1, using HW/SW codesign so-        |    |

|     | lution                                                                       | 73 |

| 5.7 | Comparison of detection performance scores for fixed- and floating-point     |    |

|     | solutions; HyMap scene, target signature F4, using HW/SW codesign so-        |    |

|     | lution                                                                       | 74 |

| 5.8 | Sensors and FPGA processing data rate for full FPGA solution                 | 75 |

|     |                                                                              |    |

| 5.9  | Comparison of data processing speed for the FPGA implementations                                                                                               | 75       |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | Resource utilization report, 32 bands, 32-bit intermediate data, full FPGA solution                                                                            | 76       |

| 5.11 | Comparison of used resources for SBS-CEM, DPBS-CEM and our imple-<br>mentation                                                                                 | 76       |

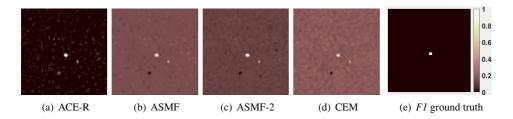

| 5.12 | Comparison of detection performance scores using different fixed-point types for Salinas scene using full FPGA solution                                        | 78       |

| 5.13 | Comparison of detection performance scores using different fixed-point types for Salinas scene using full FPGA solution with fixed-point type                  |          |

| 5.14 | altering Comparison of detection performance scores using different fixed-point types for HyMap Cooke City scene, target signature <i>F1</i> , using full FPGA | 78       |

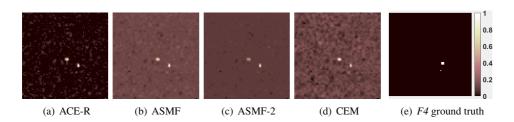

| 5.15 | solution                                                                                                                                                       | 79       |

|      | types for HyMap Cooke City scene, target signature F4, using full FPGA                                                                                         | 80       |

| 5.16 | solution          Resource utilization report for PPI algorithm implementation                                                                                 | 80<br>81 |

## List of Figures

| 1.1  | The satellite image shows an algae bloom in the sea off the coast of North-<br>ern Norway. This rapid increase of algae population in marine water can<br>be harmful and have significant negative impact on human health, econ-<br>omy and environment. | 2  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Push-broom scanner concept.                                                                                                                                                                                                                              | 4  |

| 2.1  | Illustration of a hyperspectral data cube, along with spectra plot for a sin-                                                                                                                                                                            |    |

|      | gle pixel and a single spectral channel intensities shown in grayscale                                                                                                                                                                                   | 7  |

| 2.2  | Measures of spectral similarity and linear mixing model illustration                                                                                                                                                                                     | 9  |

| 2.3  | Storage formats for hyperspectral images                                                                                                                                                                                                                 | 11 |

| 2.4  | An example showing the operation of PPI algorithm with three skewers in                                                                                                                                                                                  |    |

|      | 2-dimensional space.                                                                                                                                                                                                                                     | 12 |

| 2.5  | Illustration of a typical hyperspectral target detection system                                                                                                                                                                                          | 13 |

| 2.6  | Overview of Zynq-7000 architecture                                                                                                                                                                                                                       | 20 |

| 2.7  | Simplified schematic of DSP48E1 block                                                                                                                                                                                                                    | 21 |

| 2.8  | AXI-Lite interface.                                                                                                                                                                                                                                      | 22 |

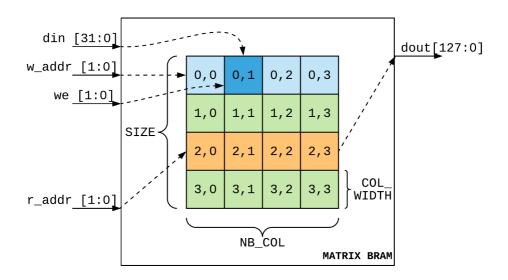

| 2.9  | Matrix storage using BRAM                                                                                                                                                                                                                                | 23 |

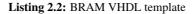

| 2.10 | Generated Divider Block in Xilinx Vivado                                                                                                                                                                                                                 | 24 |

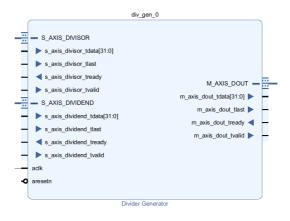

| 2.11 | Vivado HLS design flow.                                                                                                                                                                                                                                  | 25 |

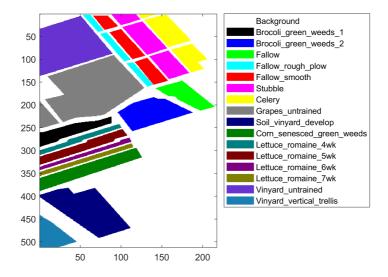

| 3.1  | Salinas ground truth map                                                                                                                                                                                                                                 | 30 |

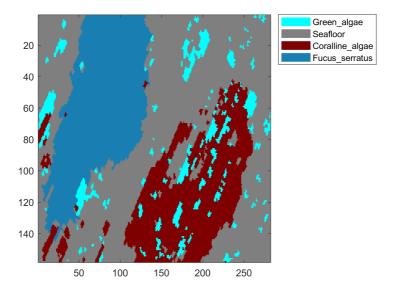

| 3.2  | Hopavågen ground truth map                                                                                                                                                                                                                               | 31 |

| 3.3  | Indian Pines ground truth map                                                                                                                                                                                                                            | 32 |

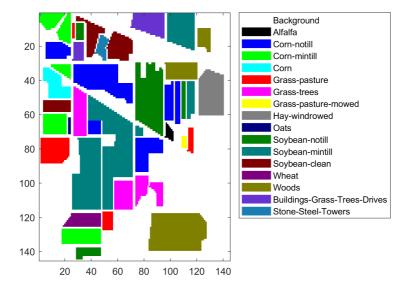

| 3.4  | Pavia University ground truth map                                                                                                                                                                                                                        | 33 |

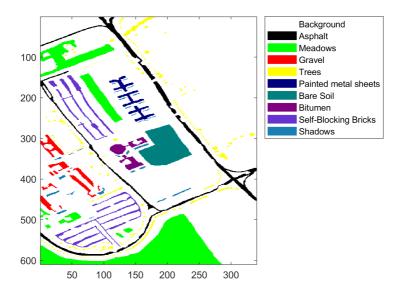

| 3.5  | True color image of Cooke City scene                                                                                                                                                                                                                     | 34 |

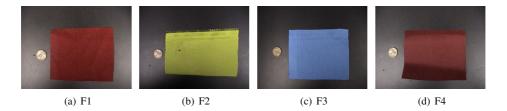

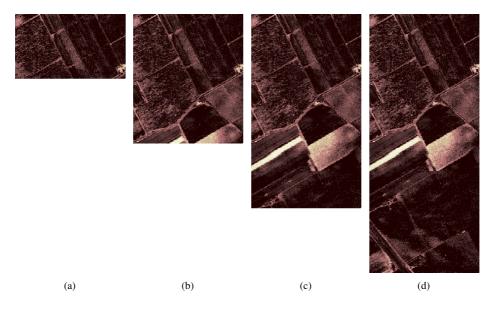

| 3.6  | Photos of placed targets in Cooke City scene - F1, F2, F3 and F4                                                                                                                                                                                         | 34 |

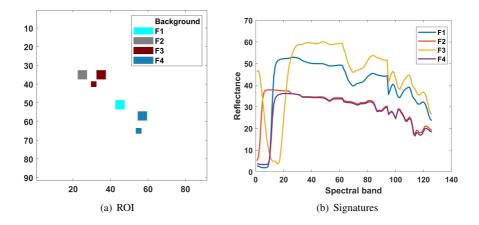

| 3.7  | Region of interest and signatures in HyMap Cooke City scene                                                                                                                                                                                              | 35 |

| 3.8  | Confusion matrix for a binary classifier                                                                                                                                                                                                                 | 36 |

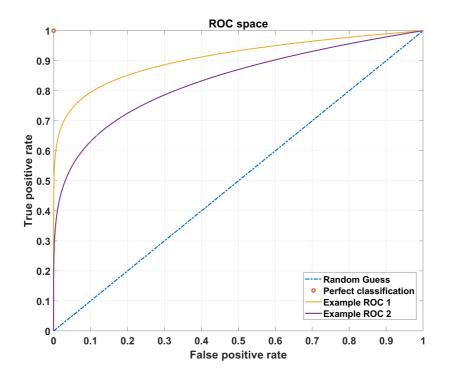

| 3.9  | The ROC space and example ROC curves                                                                                                                                                                                                                     | 38 |

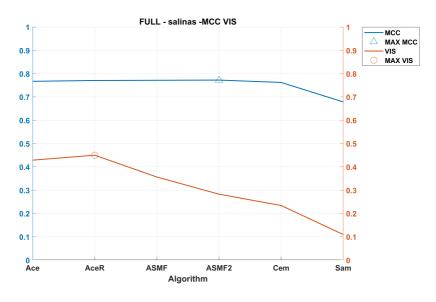

| 3.10 | MCC and visibility values for Salinas scene                                                                                                                                                                                                              | 39 |

|      |                                                                                                                                                                                                                                                          |    |

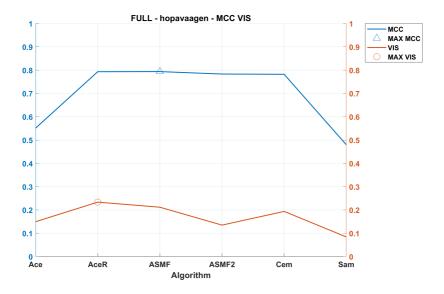

| 3.11       | MCC and visibility values for Hopavågen scene                                    | 40 |

|------------|----------------------------------------------------------------------------------|----|

|            | MCC and visibility values for Indian Pines scene                                 | 41 |

|            | MCC and visibility values for Pavia University scene                             | 42 |

|            | MCC and visibility values for HyMap Cooke City scene                             | 42 |

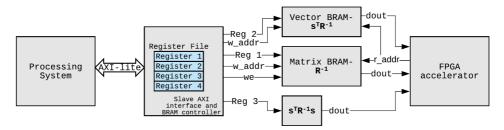

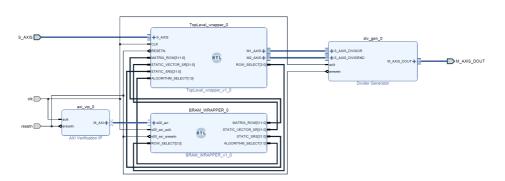

| 4.1        | Block design of the FPGA accelerator for target detection.                       | 43 |

| 4.2        | Block diagram of BRAM module for HW/SW codesign solution                         | 45 |

| 4.3        | RTL design of the Stage 1 of the FPGA accelerator.                               | 46 |

| 4.4        | RTL design of the Stage 2 of the FPGA accelerator.                               | 47 |

| 4.5        | RTL design of the Stage 3 of the FPGA accelerator.                               | 48 |

| 4.6        | Task-level pipeline of the accelerator stages.                                   | 49 |

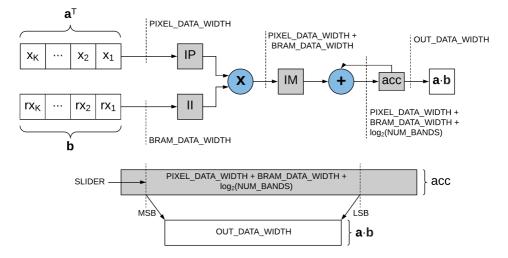

| 4.7        | Example of a dot product unit with specified bit widths. Using a slider to       |    |

|            | truncate the result at a specified position                                      | 50 |

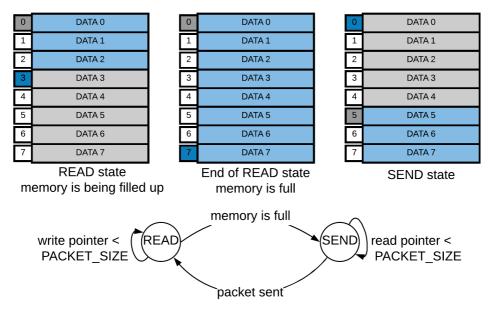

| 4.8        | An example of packet FIFO behaviour with 8 elements                              | 51 |

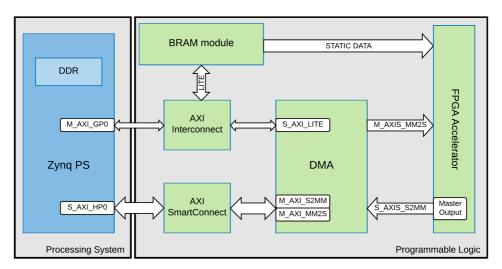

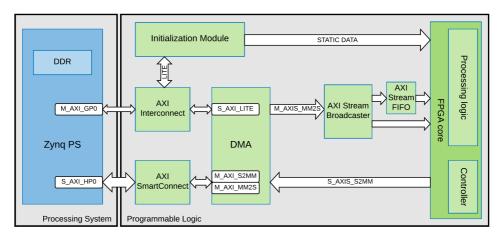

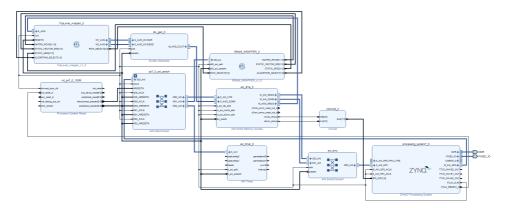

| 4.9        | Block design of the full FPGA solution for target detection                      | 53 |

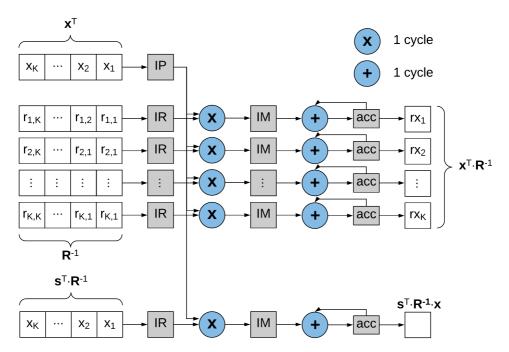

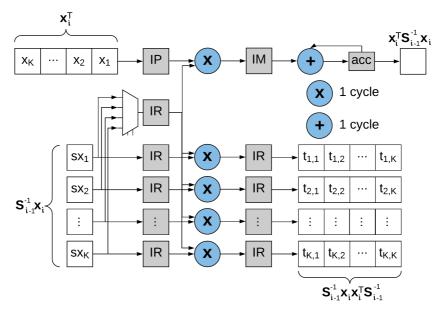

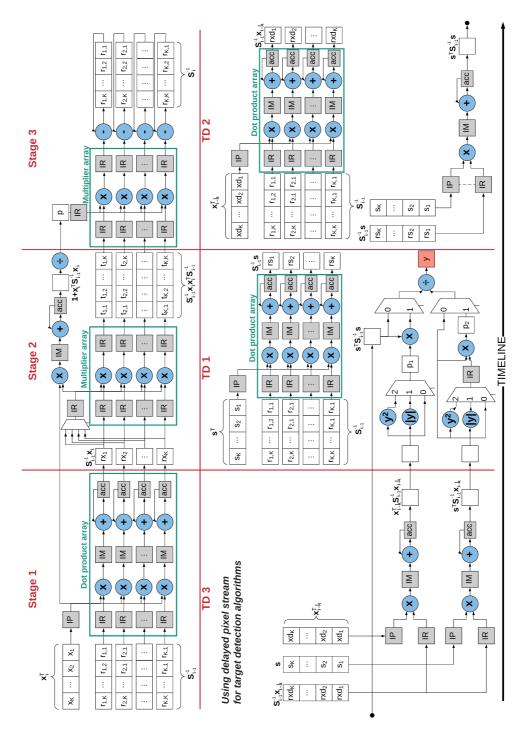

| 4.10       | RTL design of the Stage 2 of the FPGA core                                       | 58 |

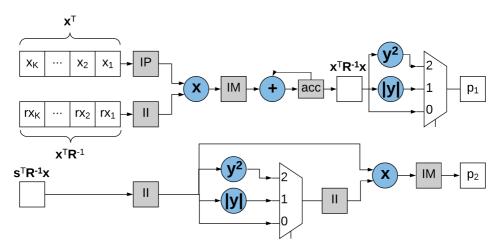

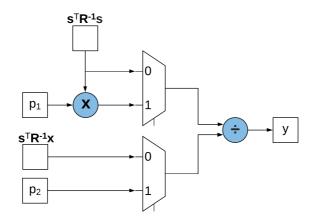

| 4.11       | RTL design of the Stage 3 of the FPGA core.                                      | 59 |

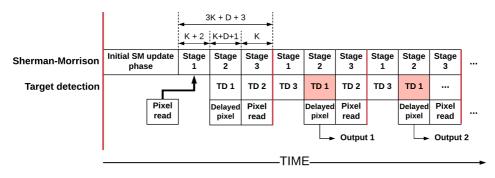

| 4.12       | Timeline of operation stages in Sherman-Morrison updating and target de-         |    |

|            | tection                                                                          | 60 |

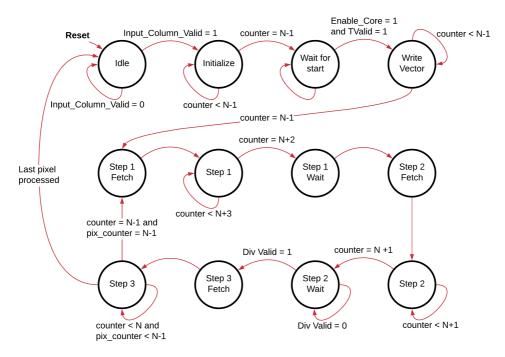

| 4.13       | Timing diagram for Sherman-Morrison updating and target detection hard-          |    |

|            | ware                                                                             | 61 |

| 4.14       | State machine for Sherman-Morrison updating and target detection hard-           |    |

|            | ware                                                                             | 63 |

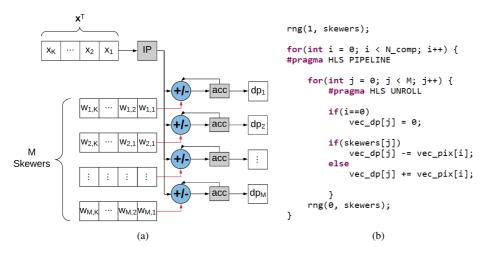

|            | RTL design of PPI projections (a) and the corresponding C code in HLS (b).       | 64 |

| 4.16       | RTL design of a unit determining the maximum/minimum extrema (a) and             |    |

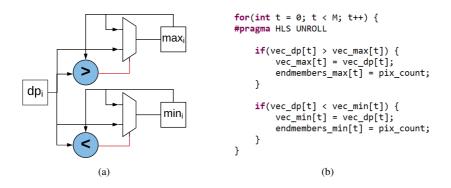

|            | the corresponding C code in HLS (b).                                             | 65 |

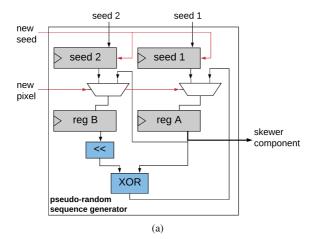

| 4.17       | RTL design of a pseudo-random sequence generating unit (a) and the cor-          |    |

|            | responding C code in HLS (b)                                                     | 66 |

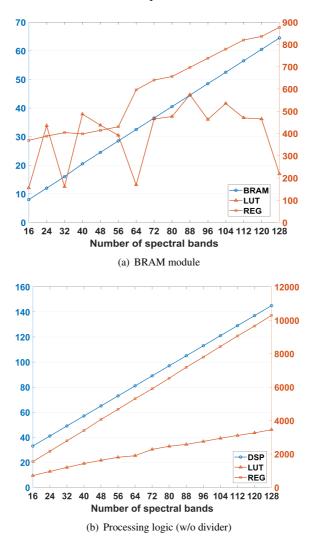

| 5.1        | Resource utilization as a function of different number of spectral bands for     |    |

|            | BRAM module and processing logic, respectively                                   | 70 |

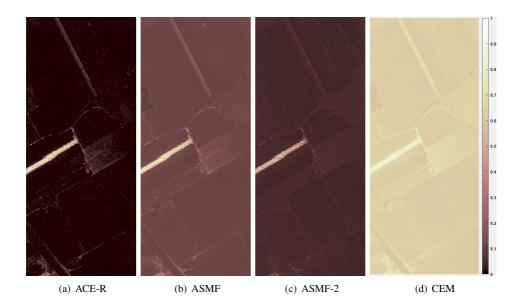

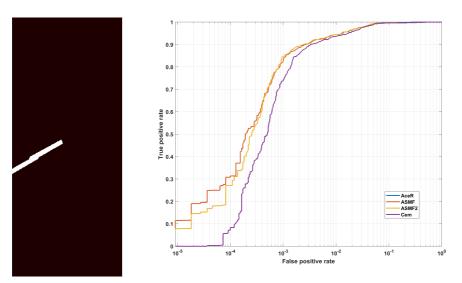

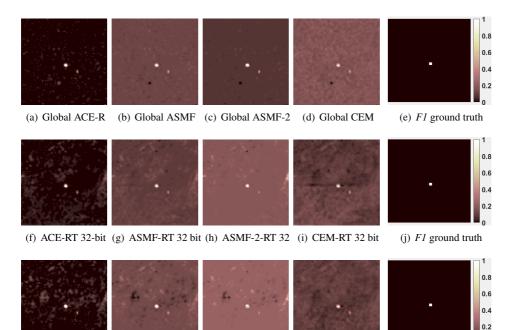

| 5.2        | Detection results (probability images) for Lettuce romaine 4th week target       |    |

|            | signature from Salinas scene obtained using the implemented accelerator.         | 72 |

| 5.3        |                                                                                  | 72 |

| 5.4        | Detection results (probability images) for <i>F1</i> target signature from HyMap |    |

|            | Cooke City scene obtained using the implemented accelerator                      | 73 |

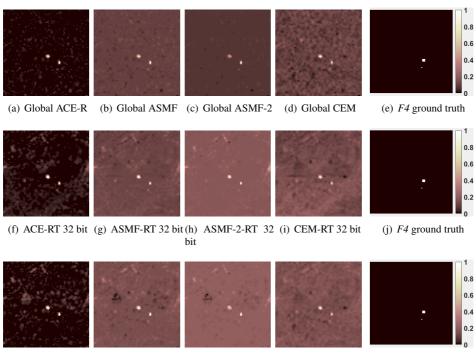

| 5.5        | Detection results (probability images) for F4 target signature from HyMap        |    |

|            | Cooke City scene obtained using the implemented accelerator                      | 74 |

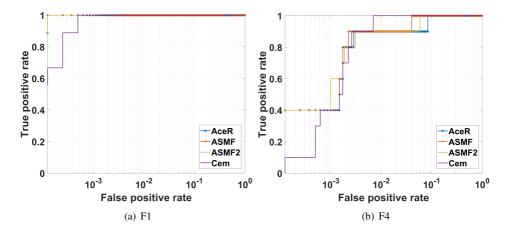

| 5.6        | ROC curves obtained by different algorithms for the detection of <i>F1</i> and   |    |

|            | <i>F4</i> target signatures.                                                     | 74 |

| 5.7        | Real-time detection results using Salinas scene and Lettuce romaine 4th          |    |

| <b>5</b> 0 | week as the target signature.                                                    | 77 |

| 5.8        | Detection results (probability images) for <i>F1</i> target signature from HyMap |    |

|            | Cooke City scene obtained using the full FPGA implementation with Sherman        |    |

|            | Morrison updating.                                                               | 79 |

| 5.9         |                                                                                                          | 80       |

|-------------|----------------------------------------------------------------------------------------------------------|----------|

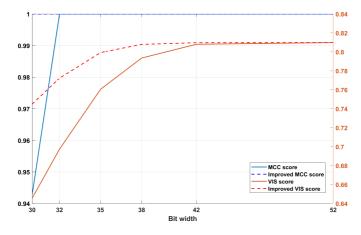

| 5.10        | Comparison of detection performance scores using different fixed-point types for adapted ACE-R detector. | 81       |

| <b>D</b> 1  |                                                                                                          | 92       |

|             |                                                                                                          | 92<br>92 |

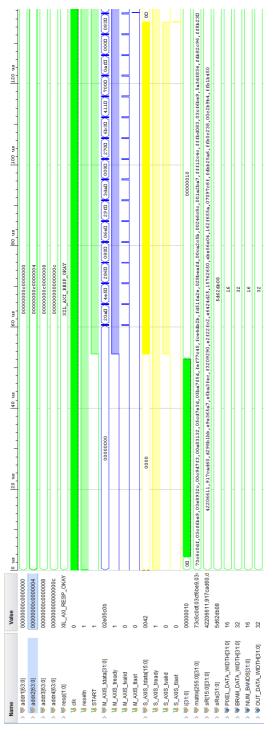

| B.3         | Example simulation waveform                                                                              | 93       |

| <b>B.</b> 4 | SDK - create application project                                                                         | 94       |

| B.5         | SDK - change project settings                                                                            | 95       |

## Abbreviations

| ACE   | = | Adaptive Coherence/Cosine Estimator                  |

|-------|---|------------------------------------------------------|

| ASMF  | = | Adjusted Spectral Matched Filter                     |

| AXI   | = | Advanced eXtensible Interface                        |

| CEM   | = | Constrained Energy Minimization                      |

| DMA   | = | Direct Memory Access                                 |

| DSP   | = | Digital Signal Processing                            |

| FPGA  | = | Field Programmable Gate Array                        |

| GPU   | = | Graphic Processing Unit                              |

| HLS   | = | High-Level Synthesis                                 |

| HSI   | = | Hyperspectral Imager                                 |

| HW    | = | Hardware                                             |

| HYPSO | = | Hyper-Spectral Imager for Oceanographic Applications |

| MAC   | = | Multiplier–Accumulator                               |

| MCC   | = | Matthews Correlation Coefficient                     |

| PL    | = | Programmable Logic                                   |

| PS    | = | Processing System                                    |

| SAM   | = | Spectral Angle Mapper                                |

| SoC   | = | System on Chip                                       |

| SW    | = | Software                                             |

| VHDL  | = | VHSIC Hardware Description Language                  |

|       |   |                                                      |

# Chapter \_

## Introduction

### 1.1 Motivation

The ocean covers more than 70% of the Earth's surface. This vast body of water is a principal component of life and home to the first organisms on Earth. Many years later, the ocean plays an integral role in the human economy, society and most importantly survival. The human kind is facing the world-changing challenges such as climate change and global warming, waiting for an extensive solution for the years to come. This is where HYPSO mission makes its impact on our everyday life.

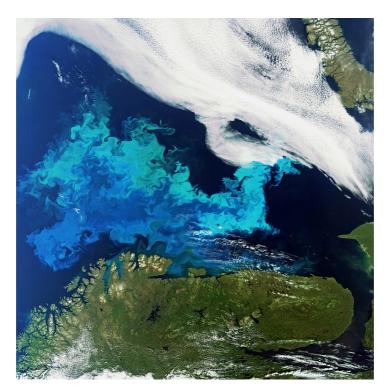

Hyper-Spectral Imager for Oceanographic Applications (HYPSO) mission is being developed at the NTNU, Trondheim. The imager will observe the oceanographic phenomena by using a small satellite equipped with a hyperspectral camera on-board [1], operating in cooperation with aerial, surface, and underwater vehicles. This approach is employed since a variety of phenomena can be observed from the space on a large scale, such as ocean color data or harmful algae blooms approaching fish farms as shown in Fig. 1.1. This master thesis is a part of the HYPSO mission.

### 1.2 Hyperspectral imaging and processing

The hyperspectral camera captures hundreds of images, where each corresponds to a certain wavelength range in the electromagnetic spectrum, for the same area on Earth. This is the basis of hyperspectral imaging, which exquisitely combines remote sensing and spectrometry. In contrast to true color imaging which is adjusted to human spectral sensitivity, hyperspectral imaging can include abundance of wavelength channels outside and inside the visible spectrum. Such channels are usually referred to as bands.

The increasing amount of spatio-spectral data obtained using modern hyperspectral imagers (HSI) has brought in new challenges in the analysis and extraction of useful information from hyperspectral datasets, especially in scenarios which require real-time operation. Modern satellite missions tend to incorporate new HSI with increased spatial and

**Figure 1.1:** The satellite image shows an algae bloom in the sea off the coast of Northern Norway [2]. This rapid increase of algae population in marine water can be harmful and have significant negative impact on human health, economy and environment.

temporal resolution, causing dramatic growth of hyperspectral data and its dimensionality. Unfortunately, the available satellite down-link bandwidth to ground stations is not following this trend [3]. Those reasons lead to the necessary incorporation of high-performance computing platforms into certain stages of hyperspectral processing on-board and on the ground, such as: graphic processing units (GPUs), parallel computing and most importantly field programmable gate arrays (FPGAs) [4]. The hyperspectral data processing is usually pipelined, consisting of the following stages: binning, optical and sensor corrections, radiometric corrections, geo-referencing and registration, motion blur correction, super-resolution [5], atmospheric correction, dimensionality reduction [6], classification, target detection and compression [7, 8]. This thesis explores the target detection algorithms and how they could be implemented on FPGA.

### 1.3 Target Detection in context of HYPSO mission

The objective of target detection algorithms is to find an object of interest in the hyperspectral image, i.e, target detection algorithms are inspecting the presence of a specific material in the image. As such, they require spectral information about the target of interest obtained either from spectral libraries or extracted from the scene. With regard to HYPSO mission, target detection is the main part of mission objectives [1] listed below:

- To provide and support ocean color mapping through a Hyperspectral Imager (HSI) payload, **autonomously processed data**, and on-demand autonomous communications in a concert of robotic agents at the Norwegian coast;

- To collect ocean color data and **to detect and characterize spatial extent of algal blooms**, measure primary productivity using emittance from fluorescence-generating micro-organisms, and other substances resulting from aquatic habitats and pollution to support environmental monitoring, climate research and marine resource management;

as well as user and mission requirements:

- Operational data shall be compressed, have at least 20 spectral bands, and include radiometric calibration, atmospheric correction, classification, super-resolution and **target detection**;

- Should **determine** many specific plant pigments as well as certain organic and inorganic compounds.

The algorithms inspected in this thesis are based on the statistical approach, where spectral reflectance features are exploited to identify the target. The concept of many target detection algorithms has been established in the domain of signal processing, radar and pattern recognition [9]. Later, the algorithms have been adapted for hyperspectral processing, with some originally developed in this field due to the amount of spectral detail [10]. As such, hyperspectral target detection algorithms are usually affiliated with spectral rather than spatial processing techniques. In the domain of spectral processing, spatial arrangement of pixels and geometrical shapes are not carrying any information. Instead, each pixel corresponds to a certain ground-resolution cell containing a spectrum used to determine specific materials [11].

In statistical signal processing, target detection is regarded as binary hypothesis testing between a null and alternative hypothesis. A null hypothesis asserts that the pixel being tested is not a target, while an alternative hypothesis asserts the opposite. This way, each pixel is either regarded as a target pixel or something other than a target, which is referred to as background [12]. Modelling the signals under both hypothesis is different and characteristic for each target detection algorithm.

Target detection algorithms come with a set of challenges related to their application in a certain field, such as detection of plant pigments. Their performance is limited by many factors, while some of them are:

- Spatial extent of the target in the hyperspectral image

- · Number of spectral bands used for target detection

- · Appropriate usage of radiance or reflectance domain in target detection

- Estimation and modeling of the image background for optimal detection

- Selection of threshold for automated target detection

- Spectral variability of the target due to spectral mixing in a subpixel target

In this thesis, target detection algorithms are implemented in hardware, specifically designed for FPGA platform, and therefore, not only concerns about the detection performance of the algorithm arise. In addition to that, the algorithm has to perform in real-time with specific hardware platform constraints accounted for. The algorithms and tests performed are further explained in section 2.3 and chapter 3.

### 1.4 HYPSO mission payload

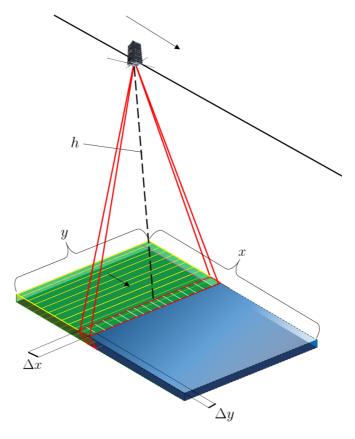

At NTNU SmallSat laboratory, we are developing HYPSO payload which will be able to capture and process a hyperspectral image. The camera used in HYPSO payload is a pushbroom scanner, where the image is acquired one line (frame) at a time, as shown in Fig. 1.2. Each frame has two dimensions, one spatial, telling the position of captured pixel, and one

Figure 1.2: Push-broom scanner concept [1].

spectral telling the pixel intensity at each wavelength channel. The hyperspectral image is built from top to bottom, frame by frame. Therefore, the image is usually represented as a three-dimensional cube (two spatial and one spectral dimension).

To process hyperspectral data, HYPSO payload will be equipped with Xilinx Zynq-7000 All Programmable System on Chip (SoC). This SoC contains ARM Cortex-A9 processor along with FPGA programmable logic. Over the years, FPGAs have become one of the preferred choices for fast processing of hyperspectral data, due to their reconfigurability, parallelization properties, short development time, easy data handling and low power consumption. Also, new FPGA devices have enhanced resistance to ionizing radiation inherently present in space (does not refer to Zynq-7000).

Compared to computer clusters or GPUs, FPGAs offer much smaller size and weight, as well as substantially lower power consumption. The adaptivity of FPGA through reconfigurability offers on-the-fly changes which indeed extend the life span of remote sensing satellites. This opens possibility to select algorithms from a ground station [13]. It should be noted that GPUs are still not incorporated in satellite Earth observation missions due to radiation-tolerance and power consumption issues, despite the increasing programmability of low-power GPUs such as those available in smartphones.

The Zynq-7000 SoC offers high performance ports to connect ARM Processing System (PS) and FPGA programmable logic (PL). This is very desirable for hardware and software codesigned implementations. By deciding which elements will be performed by the programmable logic, and which elements will run on the ARM Cortex-A9, we partition the computation system leading to the accelerated execution of hyperspectral processing algorithms.

In conclusion, FPGA is a reasonable choice for HYPSO SmallSat mission. Example is a scenario where processing of hyperspectral images is performed on-board, so that only obtained results are transmitted to the ground station. This scenario does not exclude the possibility to compress the data and transmit it after transmitting operational data [14].

### **1.5 Main contributions**

The project assignment for master thesis lists the main tasks:

- Further integration of FPGA and SW modules through implementation of correlation matrix and inversion matrix calculation

- Analysis of additional speed-up potential for HW/SW codesigned implementation

- · Further analysis of numerical error induced by fixed-point implementation in FPGA

These tasks were approached through two proposed FPGA solutions - HW/SW implementation and full FPGA implementation.

HW/SW implementation includes the FPGA accelerator and software solution used to handle a selection of target detection algorithms. After partitioning of the system, main computation parts of the target detection algorithms were extracted and implemented on FPGA platform. Static elements of the algorithm which can be used for subsequent runs are software-based. The design was developed during the specialization project, and improved during the thesis work in terms of performance, interoperability and testability. Additionally, it was upgraded to support two more detectors - ASMF and CEM. Most importantly, the accelerator has the speed-up factor of **28.54** compared to SW model run on ARM Cortex-A9. Furthermore, detailed analysis of the influence of numerical error induced by fixed-point implementation in FPGA on detection performance is done.

Full FPGA implementation is a standalone FPGA solution which performs all required computation using FPGA fabric. The implementation combines correlation matrix and inversion matrix calculation using Sherman-Morrison formula, with the possibility of realtime operation. The implementation supports ACE-R, CEM and ASMF detectors, and achieves comparable or better performance than state-of-the-art solutions.

A conference paper has been submitted and presented based on the work during thesis and specialization project:

Đ. Bošković, M. Orlandić, S. Bakken and T. A. Johansen, "HW/SW Implementation of Hyperspectral Target Detection Algorithm", 8th Mediterranean Conference on Embedded Computing (MECO), Budva, Montenegro, June 2019.

In addition to aforementioned target detection algorithm implementations, PPI endmember extraction algorithm was implemented using Vivado HLS. This implementation illustrates productivity benefits of a C-based development flow using HLS. The VHDL, MATLAB and C code developed during the thesis are available on [15].

#### **1.6** Structure of the Thesis

The thesis is divided into 6 chapters. The remainder of the thesis is organized as follows:

**Chapter 2** introduces the background information necessary for testing and development of target detection algorithm hardware implementation. The chapter presents target detection algorithms. In addition to that, brief overview of Zynq-7000 platform is provided, with the state-of-the-art target detection algorithm implementations on FPGA platforms. Chapter 2 also introduces Vivado HLS and PPI endmember extraction algorithm.

**Chapter 3** reviews state-of-the-art target detection algorithms. The chapter describes hyperspectral datasets used for testing as well as metrics used to estimate their detection performance, and presents the findings of algorithm testing and evaluation.

**Chapter 4** presents hardware-software codesigned implementation of target detection accelerator in section 4.1, full FPGA solution using Sherman-Morrison updating for matrix inversion in 4.2 and PPI algorithm implementation in 4.3.

**Chapter 5** discusses the results of FPGA implementations with respect to hardware performance, resource utilization and detection performance.

Chapter 6 concludes with guidelines for future development.

Chapter 2

## Background

### 2.1 Hyperspectral data representation

This section is strongly influenced and developed from [12] and [11]. Different data representations of hyperspectral images regarding target detection algorithms are presented in this section.

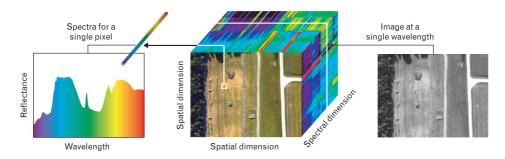

Hyperspectral images contain both spatial and spectral information. We can illustrate one image as a hyperspectral data cube shown in Fig. 2.1. The cube has three dimensions, of which two are spatial and one is spectral dimension. If we extract one pixel from a certain spatial location, we can plot the spectral reflectance curve as a function of wavelength. On the other side, by choosing one spectral channel, it is possible to extract an intensity (grayscale) image which will represent the spatial distribution of reflectance captured by the imager. As spectral information is of primary focus regarding target detection algorithms, data is typically represented as a set of spectral measurements. Therefore, a pixel  $\mathbf{x}_i$  is a vector containing spectral information and it is formulated as:

**Figure 2.1:** Illustration of a hyperspectral data cube (in the center), along with spectra plot (on the left) for a single pixel and a single spectral channel intensities shown in grayscale (on the right) [11].

$$\mathbf{x}_i = \begin{bmatrix} L_i(\lambda_1) & L_i(\lambda_2) & \dots & L_i(\lambda_K) \end{bmatrix}^T$$

(2.1)

where  $L_i(\lambda_k)$  is a measurement of a spectral band with a center frequency  $\lambda_k$ . Hyperspectral image can then be stored as a matrix **X** with N pixels and K spectral bands:

$$\mathbf{X} = \begin{bmatrix} \mathbf{x}_1 & \mathbf{x}_2 & \dots & \mathbf{x}_N \end{bmatrix} = \begin{bmatrix} L_1(\lambda_1) & L_2(\lambda_1) & \dots & L_N(\lambda_1) \\ L_1(\lambda_2) & L_2(\lambda_2) & \dots & L_N(\lambda_2) \\ \vdots & \vdots & \ddots & \vdots \\ L_1(\lambda_K) & L_2(\lambda_K) & \dots & L_N(\lambda_K) \end{bmatrix}.$$

(2.2)

Matrix  $\mathbf{X}$  does not expose spatial relations between pixels, but the ordering of pixels and information about image size parameters allow easy conversion to appropriate pixel arrangement for extraction of spatial information.

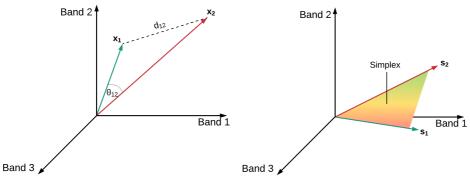

#### 2.1.1 Geometrical data representation

As such, a pixel is a vector in K-dimensional Euclidean space, where K is the number of spectral bands. Since spectral measurements  $L_i(\lambda_k) \ge 0$ , all pixel vectors belong to the positive cone of K-dimensional space. As Euclidean spaces also generalize to higher dimensions, we can define two similarity metrics between pixels  $\mathbf{x}_1$  and  $\mathbf{x}_2$ :

$$d_{12} = \sqrt{(\mathbf{x}_1 - \mathbf{x}_2)^T (\mathbf{x}_1 - \mathbf{x}_2)}$$

(2.3)

$$\theta_{12} = \cos^{-1} \frac{\mathbf{x}_1^T \mathbf{x}_2}{\sqrt{(\mathbf{x}_1^T \mathbf{x}_1)(\mathbf{x}_2^T \mathbf{x}_2)}}$$

(2.4)

where  $d_{12}$  represents the distance measure, and  $\theta_{12}$  is the spectral angle measure. It is, however, advisable to use Eq. 2.4 rather then Eq. 2.3 to measure spectral similarity. Eq. 2.3 has a particular issue with the variation of pixel illumination, when one pixel is scaled with factor  $\alpha$ ,  $\mathbf{x}_i = \alpha \mathbf{x}$ . In this case, spectra has the same shape, but the change of illumination intensity scales the length of a vector representing the pixel. This is the basis for geometrical representation of hyperspectral data. An example is shown in Fig. 2.2(a), where two pixels  $\mathbf{x}_1$  and  $\mathbf{x}_2$  are placed in three dimensional space (three spectral bands). The distance and angle between pixels is annotated as  $d_{12}$  and  $\theta_{12}$ , respectively.

#### 2.1.2 Spectral variability and mixing

The observed spectra in remote sensing applications is never fixed, but exhibits inherent variability due to atmospheric conditions, sensor noise, ground-cell position, material mixing, spatial resolution and other factors. As such, measured spectra with variability produces a cloud of points (tips of vectors) in spectral space. By contrast, deterministic invariable spectra is a single fixed vector and it is usually idealized spectra from spectral libraries. Moreover, hyperspectral data exploitation algorithms also encounter problem of sub-pixel abundances explained by spectral mixing.

Spectral mixing occurs when spatial resolution of HSI is lower than spatial extent of ground-cell materials. Therefore, it is very probable that many materials contribute to the

(a) Measures of spectral similarity and geometrical (b) Linear mixing model and a simplex formed with data representation two pure materials

Figure 2.2: Measures of spectral similarity (on the left) and linear mixing model (on the right)

measured spectrum. Such spectrum is regarded as a mixed pixel (sub-pixel), whereas a pure pixel contains only one material called endmember. In other words, endmembers are spectrally pure, unique materials which occur in the scene. If the spectral mixture is macroscopic, then each reflected photon reacts with a single surface material present in the observed ground cell. The reflectance is therefore a combination of all reflected photons mixed linearly corresponding to the area each material covers on the ground cell. Assuming that  $\mathbf{s}_i$ , i = 1...M, are the endmembers and  $a_i$  their area fractions (abundances) of the ground cell, then linear mixing can be defined as:

$$\mathbf{x} = \sum_{i=1}^{M} a_i \mathbf{s}_i + \mathbf{n}$$

(2.5)

where **n** is the additive noise vector. An example is shown in Fig. 2.2(b), where vertices of two endmembers  $\mathbf{s}_1$  and  $\mathbf{s}_2$  form a simplex. Any linear mixture of these two endmembers would be a point lying in 2-simplex, regardless of how many spectral dimensions existed in the data. In general, the endmembers in the scene are not known, but extracted from the scene using many endmember extraction techniques, such as PPI and N-FINDR [16]. Pixel purity index (PPI) algorithm is described in section 2.2.

Not only low spatial resolution can cause spectral mixing in a pixel, but mixed pixels can also appear when distinct materials are combined into a homogeneous mixture. The spectral mixing can also be modelled using nonlinear mixing model, while spectral variability is further described using subspace model and probability density models. The probability density model is used for statistical representation of hyperspectral images.

#### 2.1.3 Statistical data representation

Geometrical representation is particularly useful for describing spectral mixing, similarity and change transformation due to illumination and environmental conditions. However, geometrical representation is not an adequate model for noise and the stochastic nature of hyperspectral data. Therefore, statistical approach for describing hyperspectral images is employed using three main parameters: mean vector  $\mu$ , covariance matrix  $\Sigma$  and correlation matrix **R**.

If we assume noise model **n** and the additive model  $\mathbf{x} = \mathbf{s} + \mathbf{n}$ , where **s** is a deterministic signature, then the probability density function is:

$$p(\mathbf{x};\theta) = \frac{1}{2\pi^{K/2}} \frac{1}{|\mathbf{\Sigma}|^{1/2}} e^{-\frac{1}{2}(\mathbf{x}-\boldsymbol{\mu})^T \mathbf{\Sigma}^{-1}(\mathbf{x}-\boldsymbol{\mu})}$$

(2.6)

with parameters of the distribution  $\theta = \{\mu, \Sigma\}$ . Assuming zero-mean noise, mean vector  $\mu = \mathbf{s}$ , whereas covariance matrix  $\Sigma = \sigma^2 \mathbf{I}$  due to wavelength independent variance assumption.

The multivariate probabilistic model in Eq. 2.6 with corresponding assumptions can only characterize the sensor noise of the dataset. This simple normal distribution is unable to fully incorporate the aforementioned stochastic nature of spectral properties of observed objects in the image. Typically, the parameters  $\theta$  are unknown and are estimated from the provided dataset using sample statistics. The standard statistical method employed for estimating the unknown parameters is the maximum likelihood estimation, explained in detail in [12]. Resulting sample statistics are following:

mean vector

$$\boldsymbol{\mu} = \frac{1}{N} \sum_{i=1}^{N} \mathbf{x}_i,$$

(2.7)

covariance matrix

$$\boldsymbol{\Sigma} = \frac{1}{N} \sum_{i=1}^{N} [\mathbf{x}_i - \boldsymbol{\mu}] [\mathbf{x}_i - \boldsymbol{\mu}]^T = \frac{1}{N} \mathbf{X} \mathbf{X}^T - \boldsymbol{\mu} \boldsymbol{\mu}^T$$

(2.8)

and correlation matrix

$$\mathbf{R} = \frac{1}{N} \mathbf{X} \mathbf{X}^{T}$$

. (2.9)

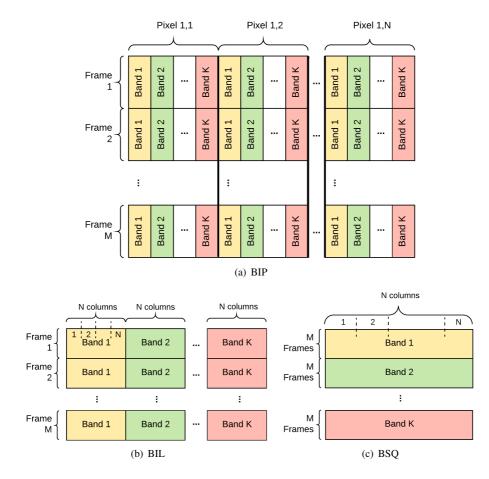

#### 2.1.4 Hyperspectral image organization

There are three common methods of organizing hyperspectral images in memory: band interleaved by pixel (BIP), band interleaved by line (BIL) and band sequential (BSQ). Each of these component ordering schemes provide different computational complexity for real-time processing of hyperspectral data [17], especially if the data is streamed in a certain fashion to the processing cores. The schemes are shown in Fig. 2.3.

In BIP format, all spectral components of one pixel are written in subsequent locations, followed by another pixel in a frame. Next row is formed for the next frame obtained by a push-broom imager. Therefore, bands 1 to K are written for pixel 1 which is part of frame 1, followed by components of pixel 2, and so on. On the other side, since the imager obtains one frame at a time, the image can be stored in BIL format. In this case, data is stored band by band for each frame. Finally, by storing data band by band for all pixels, we have created the image in BSQ format. Target detection algorithms presented in this thesis access the image in BIP format.

Figure 2.3: Storage formats for hyperspectral images.

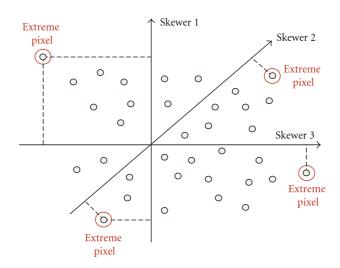

### 2.2 Pixel Purity Index Algorithm

PPI algorithm is used to find the most spectrally pure pixels in a hyperspectral image. In other words, PPI is an endmember extraction algorithm, widely used with dimensionality reduction techniques such as minimum noise factoring (MNF) to reduce the computational complexity of the algorithm. The PPI algorithm is simple and highly parallelizable, thus very feasible for FPGA implementation. The full description of the original algorithm (ENVI's PPI) is not available in the literature; however similar interpretation is available in [18] and will be described here.

The PPI algorithm consists of 4 steps: initialization, PPI projections, candidate selection and endmember extraction. The PPI projections step is the most computationally expensive part of the algorithm. The steps are described as follows:

- 1. In the initialization step, M unit vectors, named skewers, are randomly generated.

- 2. For each skewer<sub>j</sub>, j = 1, ..., M, all pixel vectors  $\mathbf{x}_i$ , i = 1, ..., N, from a hyperspectral image  $\mathbf{X}$ , are projected onto the skewer. Each skewer forms an *extrema set* consisting of processed pixel vectors. An example of the projection step on three skewers is shown in Fig. 2.4.

- 3. In the candidate selection step, we find the PPI scores  $N_{PPI}(\mathbf{x}_i)$  for all pixels. PPI score is defined as the sum of appearances in the extrema sets of all skewers for each pixel vector.

- 4. Endmember extraction step requires a threshold value  $t_v$  for the PPI score in order to extract all pixel vectors with  $N_{PPI}(\mathbf{x}_i) \ge t_v$ .

Figure 2.4: An example showing the operation of PPI algorithm with three skewers in 2-dimensional space [18].

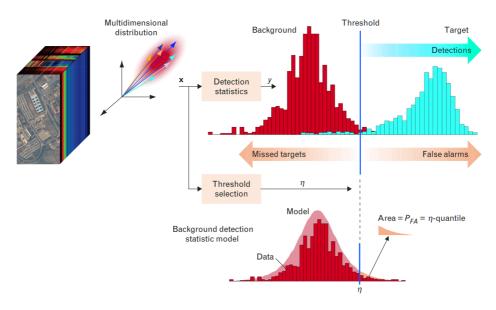

### 2.3 Target detection algorithms

Target detection algorithms search for objects of interest in the remotely obtained hyperspectral scene. Detection in a general sense also includes searching for anomalies without the knowledge about a specific spectral signature. In this thesis, the focus is on target detection where a signature is provided to the algorithm to determine if the target is present in the scene. Those detectors belong to the group of signature-matched detectors. This section is mainly based on [11, 10, 12].

The simplest reasonable approach to determine the presence of a target in a pixel would be to use one of the spectral similarity metrics as in Eq. 2.4. The measure of angle between data pixel and a reference signature is known as a spectral angle, and under certain conditions it becomes spectral angle mapper (SAM) target detection algorithm. However, many algorithms are based on the estimation of the image background for better distinction between target and non-target pixels.

Typical target detection system is shown in Fig. 2.5. The system consists of a target detection algorithm  $(D(\mathbf{x}))$  and threshold selection system. The input pixel vector  $\mathbf{x}$  is mapped onto a scalar value  $y = D(\mathbf{x})$ , which is called detection statistic. On the other side, threshold selection system constructs a background statistic model which would be used to produce the appropriate threshold value  $\eta$ .

The target detection algorithm provides our system with a value which, when compared with the threshold value, correctly determines if a pixel under test contains a designated target. In other words, the value produced by target detection algorithm corresponds to the probability of the input pixel to be a designated target. It is the task of threshold selection system to set the optimum threshold so that a significant amount of present tar-

Figure 2.5: Illustration of a typical hyperspectral target detection system, modified from [11].

gets are detected while the false alarm rate (false positive rate, i.e., wrongly categorized as targets) is kept below a certain value. That system is typically constant false alarm rate (CFAR) processor, which is the important part of automatic target detection systems. Threshold selection systems are not discussed further in this thesis.

The mathematical framework for development and analysis of target detection comes from statistical signal processing, where target detection is regarded as binary hypothesis testing between two competing hypothesis. Hypothesis  $H_0$ , also called null hypothesis, asserts that the pixel being tested is not a target. On the contrary, an alternative hypothesis  $H_1$  asserts that the pixel under test contains the target. Each target detection algorithm was developed under different models of the signals for both hypotheses. Those models are characteristic for the algorithm and they strongly influence the performance of detection. The models are introduced in the following subsections.

#### 2.3.1 Spectral angle mapper

The detection problem can be modelled as follows:

$$H_0 : \mathbf{x} = \mathbf{b}$$

$$H_1 : \mathbf{x} = \alpha \mathbf{s} + \mathbf{b}$$

(2.10)

where **b** is the combination of background and inherent random noise, **s** is the known spectral signature and  $\alpha$  is the factor used to scale the unresolved intensity of signal **s**. The uncertainty modelled by  $\alpha$  is due to illumination and spectral mixing characteristic for subpixel targets. To derive SAM algorithm, we assume that background **b** is random, zero-mean and normally distributed with variance  $\sigma$ . Then, SAM is defined as:

$$D_{SAM}(\mathbf{x}) = \frac{(\mathbf{s}^T \mathbf{x})^2}{(\mathbf{s}^T \mathbf{s})(\mathbf{x}^T \mathbf{x})}.$$

(2.11)

An equivalent detection statistic is:

$$D_{SAM}(\mathbf{x}) = -\cos^{-1} \frac{\mathbf{s}^T \mathbf{x}}{\sqrt{(\mathbf{s}^T \mathbf{s})(\mathbf{x}^T \mathbf{x})}}$$

(2.12)

since both square root as well as cosine operation are monotonic functions. Eq. 2.12 is equivalent to the aforementioned measure of the angle between a reference spectrum and a pixel under test in the spectral space. SAM is derived to achieve CFAR characteristics and therefore, the variance  $\sigma$ , which is presumably varying spatially across the image, is estimated as the square of spectrum magnitude  $\mathbf{x}^T \mathbf{x}$ . In conclusion, SAM is fast and simple algorithm relatively robust to illumination effects. However, the algorithm is limited in performance due to the initial assumptions about background modelling.

#### 2.3.2 Constrained energy minimization

CEM is designed using a finite impulse response (FIR) filter with detection statistic defined as:

$$D_{CEM}(\mathbf{x}) = \mathbf{h}^T \mathbf{x},\tag{2.13}$$

where  $\mathbf{h} = [h_1, h_2, ..., h_K]^T$  is the weight factor used to minimize the output power of a filter [19]. The weight vector is optimized so that the algorithm better separates the background and the known signature s. Then, the minimization problem is defined under the following constraint:

$$min_{\mathbf{h}}(\frac{1}{N}\sum_{i=1}^{N}(\mathbf{h}^{T}\mathbf{x}_{i})^{2}) = min_{\mathbf{h}}(\mathbf{h}^{T}\mathbf{R}\mathbf{h}) \quad subject \quad to \quad \mathbf{h}^{T}\mathbf{s} = 1$$

(2.14)

where **R** is the sample correlation matrix calculated as  $\mathbf{R} = \frac{1}{N} \sum_{i=1}^{N} \mathbf{x}_i \mathbf{x}_i^T$ . The constraint  $\mathbf{h}^T \mathbf{s} = 1$  forces the perfect detection statistic (full match) to have the value 1. Derived weight factor proposed by problem 2.14 is:

$$\mathbf{h} = \frac{\mathbf{R}^{-1}\mathbf{s}}{\mathbf{s}^T \mathbf{R}^{-1}\mathbf{s}}.$$

(2.15)

Finally, the resulting detection statistic after applying linear operation  $\mathbf{h}^T$  is:

$$D_{CEM}(\mathbf{x}) = \frac{\mathbf{s}^T \mathbf{R}^{-1} \mathbf{x}}{\mathbf{s}^T \mathbf{R}^{-1} \mathbf{s}}.$$

(2.16)

As in majority of other signature-based detection algorithms, low-probability distribution of target pixels is assumed. This assumption has direct impact on estimation of the sample correlation matrix, which can be contaminated if the number of target pixels surpasses a certain limit. On the contrary, if the number of target pixels is small, their influence when estimating  $\mathbf{R}$  can be neglected. Therefore, CEM is considered a small target detector.

#### 2.3.3 Adaptive coherence/cosine estimator

The binary hypotheses defined in Eq. 2.17 lead to the formulation of ACE algorithm.

$$H_0 : \mathbf{x} = \beta \mathbf{b}$$

$$H_1 : \mathbf{x} = \alpha \mathbf{s} + \beta \mathbf{b}$$

(2.17)

In the extension of hypotheses shown in Eq. 2.10 for deriving SAM algorithm, here we have newly introduced scaling factor  $\beta$  of the background and noise combination signal **b** under both hypotheses. If we assume that **b** is a zero-mean, white random vector process ( $\mathbf{b} \sim N(\mu, \sigma)$ ) we can derive ACE algorithm:

$$D_{ACE}(\mathbf{x}) = \frac{(\mathbf{s}^T \boldsymbol{\Sigma}^{-1} \mathbf{x})^2}{(\mathbf{s}^T \boldsymbol{\Sigma}^{-1} \mathbf{s})(\mathbf{x}^T \boldsymbol{\Sigma}^{-1} \mathbf{x})}.$$

(2.18)

In Eq. 2.18, the covariance matrix  $\Sigma$  is typically estimated from the hyperspectral data of the scene. In certain cases, designated targets are extracted from the provided scenes

and especially ACE algorithm performs well in these conditions. However, it is possible that the algorithms may have different performance with normalized laboratory signatures. Both ACE and CEM are able to achieve CFAR characteristics, and most importantly, they do not require knowledge about all present endmembers in the hyperspectral image. Unlike SAM which is considered first-order hyperspectral measure, both CEM and ACE are second-order hyperspectral measures because of covariance and correlation matrices [20].

#### 2.3.4 Adjusted Spectral Matched Filter

Adaptive spectral matched filter (ASMF) [21] is constructed using the simplified Reed-Xiaoli (RX) anomaly detector [22] to adjust the output of CEM detector in Eq. 2.16. The adjustment is implemented by introducing a non-target pixel suppression factor A defined as:

$$A = \left| \frac{\mathbf{x}^T \mathbf{R}^{-1} \mathbf{s}}{\mathbf{x}^T \mathbf{R}^{-1} \mathbf{x}} \right|.$$

(2.19)

The factor A with the variable power n is then combined with CEM as follows:

$$D_{ASMF}(\mathbf{x}) = D_{CEM}(\mathbf{x}) \cdot A^n = \frac{\mathbf{s}^T \mathbf{R}^{-1} \mathbf{x}}{\mathbf{s}^T \mathbf{R}^{-1} \mathbf{s}} \cdot \left| \frac{\mathbf{s}^T \mathbf{R}^{-1} \mathbf{x}}{\mathbf{x}^T \mathbf{R}^{-1} \mathbf{x}} \right|^n.$$

(2.20)

Depending on the power n, different spectral features are amplified or suppressed. By setting n to 0, the ASMF becomes CEM algorithm. Alternatively, by setting n to 1, similar form to *ACE-R* is obtained (which is introduced in section 3.3.1). Weight n can also be non-integer number, such as 0.5, 1.5 or similar. Setting the weight to provide substantial detection performance depends on the related scenes used for testing as well as the designated targets and their properties.

### 2.4 Matrix inversion

The computation of the inverse of a matrix is a part of almost all considered target detection algorithms. This computationally intensive task is usually performed directly or iteratively, and the choice of the method affects the performance and/or precision of the solution. Direct computation of the inverse requires a fixed number of operations to obtain the solution, whereas iterative methods converge to a solution by subsequent updates of the estimate [23].

Direct methods for inverting matrices, such as Gauss-Jordan elimination, LU decomposition, and Cholesky decomposition require a-priori created matrix ready for inversion, for example correlation matrix. This usually means that they are not able to operate as a part of a system with real-time constraints. In such cases, iterative methods are employed, such as Sherman-Morrison formula. In the following subsections, Gauss-Jordan elimination, LU decomposition and Sherman-Morrison formula are briefly presented. Additionally, they have been compared in terms of computational complexity for real-time and non-real time problems.

#### 2.4.1 Gauss-Jordan elimination

for i = 1 : n

If **A** is a square invertible matrix, we augment it with identity matrix of the same size and form matrix **X**, **X** = [**A**, **I**]. Then, by performing Gauss-Jordan elimination as explained through MATLAB code in Listing 2.1 (inspired by [24]), the left block of matrix **X** is reduced to identity matrix through application of row operations. Finally, the right block of matrix **X** is the solution: inverted matrix  $\mathbf{A}^{-1}$ .

The total effect of all the row operations is equivalent to multiplication of **X** with  $A^{-1}$  from left side as shown in Eq. 2.21. If the algorithm is unable to reduce the left block of matrix **X** to an identity matrix, then **A** is not invertible.

$$[\mathbf{A} | \mathbf{I}] \to [\mathbf{A}^{-1}\mathbf{A} | \mathbf{A}^{-1}\mathbf{I}] \to [\mathbf{I} | \mathbf{A}^{-1}]$$

(2.21)

Listing 2.1: Gauss-Jordan elimination

```

if(X(i,i) == 0)

for j = i+1 : n

if(X(i,j) ~= 0)

%row swapping

X([i j],:) = X([j i],:);

break;

end

end

end

if(X(i,i) == 0) error('singular matrix, exit!'); end

%building upper triangular matrix

```

```

for j = i+1 : n

%forward elimination

X(j_{i}:) = X(j_{i}:) - X(i_{i}:) * (X(j_{i}i) / X(i_{i}i));

end

end

%building diagonal matrix

for i = n :-1: 2

for j = i-1 : -1: 1

%backward elimination

X(j,:) = X(j,:) - X(i,:) * (X(j,i) / X(i,i));

end

end

%building identity matrix

for i = 1 : n

%last division to build matrix I

X(i,:) = X(i,:) * (1/X(i,i));

end

```

#### 2.4.2 LU decomposition with partial pivoting

After decomposing the matrix using LU decomposition, it is straightforward to find its inverse. LU decomposition starts with factoring of a matrix into a product of upper and lower triangular matrices, U and L, respectively. Assuming that P is the permutation matrix obtained by partial pivoting, and A is the matrix being decomposed, it follows:

$$\mathbf{PA} = \mathbf{LU}.\tag{2.22}$$

The method consists of three main steps:

- 1. Find the row in column k that contains the largest absolute value entry

- 2. Swap the rows of A and P (perform partial pivoting)

- 3. Perform the k-th step of Gaussian elimination

Upon obtaining L and U, we can find the inverse X of matrix A:

$$AX = I$$

$$PAX = PI$$

$$LUX = PI,$$

(2.23)

which can be rewritten as:

$$LY = PI$$

$$UX = Y.$$

(2.24)

Solving equations in 2.24 row by row (using forward and back substitution), leads to the inverse matrix  $\mathbf{X} = \mathbf{A}^{-1}$ .

#### 2.4.3 Sherman-Morrison formula

If  $\mathbf{u}$  and  $\mathbf{v}$  are two arbitrary column vectors and  $\mathbf{A}$  is an invertible square matrix, then Sherman-Morrison formula is expressed as:

$$(\mathbf{A} + \mathbf{u}\mathbf{v}^{T})^{-1} = \mathbf{A}^{-1} - \frac{\mathbf{A}^{-1}\mathbf{u}\mathbf{v}^{T}\mathbf{A}^{-1}}{1 + \mathbf{v}^{T}\mathbf{A}\mathbf{u}}$$

(2.25)

To invert the matrix A using Sherman-Morrison formula, we initialize matrix X to an identity matrix of the same size as A. Then, the following iteration scheme is used:

$$\mathbf{X}_{0} = \mathbf{I}$$

$$\mathbf{X}_{i} = \mathbf{X}_{i-1} - \frac{\mathbf{X}_{i-1}(\mathbf{a}_{i} - \mathbf{i}_{i})\mathbf{i}_{i}^{T}\mathbf{X}_{i-1}}{1 + \mathbf{i}_{i}^{T}\mathbf{X}_{i-1}(\mathbf{a}_{i} - \mathbf{i}_{i})}$$

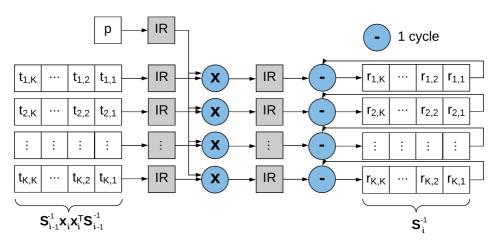

(2.26)

where  $\mathbf{a}_i$  is the *i*-th column of matrix  $\mathbf{A}$ , and  $\mathbf{i}_i$  is the *i*-th column of the identity matrix. After *n* iterations, where *n* is the number of columns of matrix  $\mathbf{A}$ , the inverse  $\mathbf{X}_n = \mathbf{A}^{-1}$  is obtained. Most importantly, Sherman-Morrison formula can be used to compute the corrected inverse of matrix  $\mathbf{A}$  after it is subjected to rank-1 update. Using Eq. 2.25, we avoid the costly computation of inverting  $\mathbf{A} + \mathbf{u}\mathbf{v}^T$  anew.

#### 2.4.4 Computational complexity of algorithms

In case of a non-real time system, full image or its subset is needed to calculate the correlation matrix. Then, its inverse can be found using the aforementioned methods. To calculate the correlation matrix of an image with N pixels consisting of K spectral components, it is necessary to perform  $NK^2$  multiplications. Afterwards, the inverse is performed using a method with general complexity of  $O(K^3)$  multiplications.

Using Sherman-Morrison formula as in Eq. 2.25,  $N(3K^2 + K)$  multiplications are needed to obtain the final inverse matrix. This is much higher computational complexity than non-real time system when all pixels are used. Nevertheless, Sherman-Morrison formula enables the system to estimate certain spectral features on-the-fly as pixels are being acquired. If other matrix inversion methods were used under real-time constraints, they would need  $K^2 + O(K^3)$  multiplications for each incoming pixel, while Sherman-Morrison formula requires only  $(3K^2 + K)$  multiplications. As such, operation of a target detection algorithm in real-time using Sherman-Morrison formula is explained in section 4.2. On the other side, both Gauss-Jordan elimination and LU decomposition for matrix inversion are implemented in software for use in HW/SW codesign implementation explained in section 4.1.

## 2.5 Overview of Zynq-7000, FPGA cores and primitives

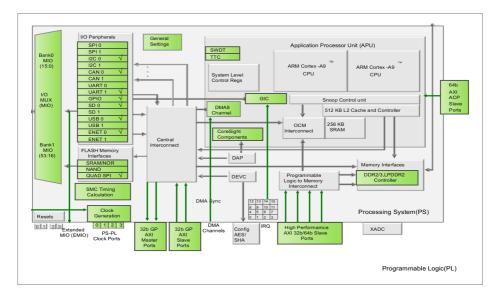

Zynq-7000 is a family of Xilinx System-on-Chip (SoC) products which provide full programmability using ARM-based processor and FPGA technology. The aforementioned high performance communication between PS and PL on a single chip allows integration and acceleration of software and hardware designs. Zynq-7000 chips are equipped with Artix-7 or Kintex-7 FPGA fabric with appreciable performance-per-watt metrics. The overview of the Zynq architecture is shown in Fig. 2.6, showing processing system with two processor cores and programmable logic connected using AXI ports.

Figure 2.6: Overview of Zynq-7000 architecture

The remainder of this section will be dedicated to essential FPGA primitives and cores found on Zynq platform, such as AXI protocol, DSP blocks, BRAM blocks, DMA core and AXI divider.

### 2.5.1 DSP blocks on Zynq

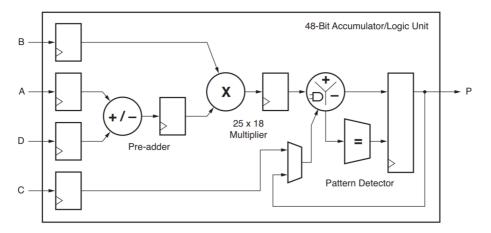

The programmable logic on Zynq SoC contains digital signal processing (DSP) blocks with the structure as depicted in Fig. 2.7. These dedicated blocks are used to enhance the speed of the design involving multiply-accumulate (MAC) operations, barrel shifting or wide bus multiplexing. Zynq PL has a limited amount of DSP blocks available, and therefore the fundamental features and characteristics must be known to the designer so that implementation of the source code can appropriately exploit these resources.

The DSP block contains a multiplier and an accumulator, with three additional pipeline data registers. If full pipelining is utilized for multiplication and addition operations, then the DSP block can run at full speed for MAC units. The pipelining is used to boost the performance as well as reduce the overall power consumption.

Figure 2.7: Simplified schematic of DSP48E1 block [25].

The accumulator is 48-bits wide, while one DSP multiplier has the capability to operate on a pair of operands with the width of 25 and 18-bits. For arithmetic operations requiring operands with wider data bus such as multiplication, the DSP block can perform a right wire shift by 17, which is used to combine and add partial products from two DSP slices and produce the final result. Therefore, it is possible to build larger multipliers, which are not limited by the inherent size of DSP block operands.

#### 2.5.2 AXI protocols

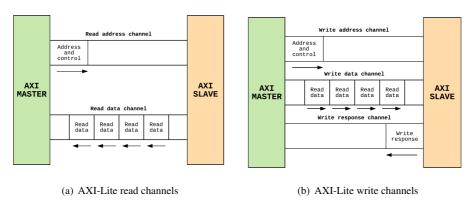

Advanced eXtensible Interface (AXI) is a part of ARM Advanced Microcontroller Bus Architecture (AMBA) interface widely used with the ARM Cortex-A processors, as well as in Zynq architecture. There are three types of AXI bus interfaces: AXI (full), AXI-lite and AXI-stream. As Zynq uses AMBA 4.0 released in 2010, the focus is placed on that version.

#### **AXI4-lite interface**

AXI and AXI-lite interfaces are defined by three channels: address, data and response channels, and two data flow directions: write and read. AXI4 allows simultaneous and bidirectional data transfer by separating data buses for reading and writing, along with the corresponding address buses.

Two end-points of the interface are called master and slave. The master initiates all data transfers by setting signals on corresponding address and data channels. One read transfer is shown in Fig. 2.8(a), where master sends the corresponding address on the read address channel and waits for the slave to respond with the requested data on the read data channel. Similarly, writing is performed by sending an address on the write address channel and corresponding data on the write data channel, as in Fig. 2.8(b). Additionally, there is a write response channel used to inform the master that the transfer was successful

and complete.

The slave responds to master's requests using a common handshake protocol consisting of *VALID* and *READY* signal. If both handshake signals are asserted during one clock cycle, the transfer occurs. Moreover, all AXI and AXI-lite transactions are memory mapped, which allows direct access to the slave registers on PL from PS. AXI interface has more optional signals, allowing burst transfers, which are explained in detail in [26].

#### Figure 2.8: AXI-Lite interface.

#### **AXI-stream interface**

AXI-stream is a simplified AXI interface used for high-speed data streaming with unlimited burst mode. The simplification consists of removing the concept of addresses and memory-mapping, and defining the protocol using a single write or read channel. Two consecutive transfers can be differentiated using additional handshake signal - *LAST*, which is asserted at the end of the transfer. Stream interfaces are usually connected to the DMA core which performs memory-mapped to stream conversion.

#### 2.5.3 DMA core