## Anders Nilsen

# Accelerating keyword spotting neural networks on FPGAs using Intel OpenVINO and Xilinx DNNDK

Master's thesis in Electronic Systems Design Supervisor: Kjetil Svarstad June 2019

## Anders Nilsen

# Accelerating keyword spotting neural networks on FPGAs using Intel OpenVINO and Xilinx DNNDK

Master's thesis in Electronic Systems Design Supervisor: Kjetil Svarstad June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electronic Systems

# Accelerating keyword spotting neural networks on FPGAs using Intel OpenVINO and Xilinx DNNDK

#### Anders Nilsen

Master of Science in Electrical Engineering

Submission date: June 2019

Supervisor: Kjetil Svarstad, IET

Co-supervisor: Florian Bochud, Cisco Norway AS

Norwegian University of Science and Technology

Department of Electronic Systems

## **Project Assignment**

Candidate name: Anders Nilsen

**Assignment title:** FPGA Implementation of the Google Speech recognition challenge

#### Assignment text

Background: Machine Learning has increased dramatically in popularity the last years and is now being used in various applications like web search, speech recognition, object detection, face recognition, etc.

Huge set of data are used to train a neural network (Learn), before the network can be used stand-alone to classify new patterns (inference).

Today's most common Machine Learning architecture is deep neural networks, which can be seen as layers of matrix multiplication. The network can have typically many layers with many weights (up to several 100k). Therefore, inference requires heavy processing resources, usually run on a GPU.

Both pre-processing of audio/video data and inference of neural networks is very well adapted for FPGA acceleration, due to its huge parallel-processing capabilities. This project will go through the step to achieve this accelerations.

In this project, the student will:

- Train a neural network for a speech recognition applications. Network like Convolutional neural network (CNN) or Long short term memory network (LSTM) should be trained with different parameters, ideally a in order to get a good classification of the data samples from the Google Speech recognition challenge: https://www.kaggle.com/c/tensorflow-speech-recognition-challenge/data

- Accelerate the network on a FPGA development kit (Altera or Xilinx)

- Implement the data pre-processing in the FPGA (sliding window FFT), using available IP and own coding. High-level-Synthesis (HLS) is recommended. Pre-processing: https://github.com/udacity/AIND-VUI-Capstone/blob/master/utils.py

i

- Implement a C++ application instantiating both the pre-processing acceleration and the neural network, preferable getting the input data from a laptop/desktop microphone.

To implement these networks, the student will use:

- Xilinx SDAccel and XFDNN (https://www.xilinx.com/applications/megatrends/machine-learning.html) on an Amazon AWS F1 cloud platform.

- Intel/Altera Deep Learning development toolkit (https://software.intel.com/en-us/computer-vision-sdk ) running on an Intel development kit available in a NTNU server.

**Assignment proposer/co-supervisor:** Florian Bochud (flobochu@cisco.com)

**Supervisor:** Kjetil Svarstad (kjetil.svarstad@ntnu.no)

## **Abstract**

Neural networks are used for almost all devices performing speech recognition, such as Amazon's Alexa and Apple's Siri. The networks have to process and understand large vocabularies while having a small of a processing time as possible. This requires substantial computational power, which is difficult to achieve in edge devices. The computational requirements have led to keyword spotting neural networks being implemented on these edge devices. These networks specialise in detecting a small vocabulary of words, establishing an uplink to a server if a target word is detected. Though small, the networks still require substantial amounts of computational power to perform keyword spotting in addition to the associated pre-processing.

Research is being made into accelerating these networks using Field-Programmable Gate Arrays (FPGAs), an attractive target due to their high performance-per-watt ratio and relatively small size. Traditionally, FPGAs have required specialised skill to be programmed. High-level Synthesis (HLS) tools aim to remove the need for these skills by generating Hardware Description Language (HDL) code from high-level languages such as C++. Additionally hardware manufacturers are developing toolkits to help developers accelerate neural networks on FPGAs.

This thesis examines the acceleration possibilities of using HLS for the acceleration of speech recognition pre-processing, as well as the FPGA-acceleration possibilities for Intel OpenVINO and Xilinx DNNDK for three types of neural networks: Convolutional Neural Network (CNN), Long Short-Term Memory (LSTM) and Attentive LSTM (att-LSTM).

Though pre-processing implementation was unsuccessful, it was estimated to be accelerated from 718.61 ms to 111.5 ms by running on an FPGA. Of the three networks, only the convolutional network was accelerated on an FPGA using OpenVINO, achieving a median classification time of 3.69 ms with 0.02% loss in classification accuracy on an Intel Arria 10 GX. Network acceleration using DNNDK was unsuccessful due to incompatibilities with non-image data, though initial testing shows promising possibilities for the Software Development Kit (SDK).

**Keywords:** Neural networks, FPGA acceleration, Keyword spotting, High level synthesis, Speech recognition

# Sammendrag

Nevrale nettverk brukes i nesten alle enheter med talegjenkjenning, som blant annet Alexa fra Amazon og Siri fra Apple. Disse nettverkene må kunne klassifisere store ordforråd med så liten forsinkelse som mulig. Dette krever betydelige mengder prosesseringskraft, noe som er vanskelig å få til i såkalte "edge devices". Disse prosesseringskravene har ført til at man i stedet implementerer nevrale nettverk for søkeordsdeteksjon. De resulterende nettverkene har små ordforråd, og oppretter automatisk en forbindelse til en server dersom et av ordene oppdages. Selv om de er mindre krever disse nevrale nettverkene relativt store mengder prosesseringskraft for å utføre søkeordsdeteksjon i tillegg til den tilhørende forhåndsprosesseringen.

På grunn av høy ytelse-per-watt og relativt liten størrelse forskes det på hvordan man kan aksellerere nevrale nettverk på FPGAer. Tradisjonelt sett har FPGA-programmering krevd spesialisert kunnskap, og for å redusere kunnskapen som trengs prøver verktøy for høynivå-syntese å generere HDL-kode fra høynivå-programmeringsspråk som C++. I tillegg til FPGA-aksellerering av høynivå-kode lager maskinvareprodusenter verktøy for å gjøre det lettere å aksellerere nevrale nettverk på FPGA.

Denne oppgaven undersøker mulighetene for FPGA-aksellerering av forhåndsprosesseringen til nevrale nettverk for stemme- og nøkkelordsgjenkjenning, i tillegg til mulighetene for FPGA-aksellering av tre nevrale nettverkstopologier med Intel OpenVINO og Xilinx DNNDK: CNN, LSTM og att-LSTM.

Forhåndsprosesseringen ble ikke kjørt på FPGA, men ble estimert til å bli aksellerert fra en kjøretid på 718.61 ms til 111.5 ms. Av de tre nettverkene ble bare CNN-nettverket

aksellerert på FPGA med OpenVINO, og fikk en median-kjøretid på 3.69 ms med 0.02% tap i klassifiseringstreffsikkerhet på en Intel Arria 10 GX FPGA. Aksellerering av nevrale nettverk med DNNDK ga ingen resultater på grunn av begrensninger under nettverksoptimalisering, men sett bort fra dette virker DNNDK lovende for FPGA-aksellerering av nevrale nettverk.

**Nøkkelord:** Nevrale nettverk, FPGA-aksellerering, Nøkkelorddeteksjon, Høynivå syntese, Stemmegjenkjenning

## Acknowledgements

I'd like to thank my supervisor at NTNU, Kjetil Svarstad, and my co-supervisor at Cisco, Florian Bochud, for their invaluable assistance throughout the thesis. I'd also like to thank Håkon Sandsmark at Cisco for helping me with problems related to neural networks and Adrian Sparrenborn and Graham McKenzie at Intel for technical assistance regarding OpenVINO. Finally, I'd like to thank my friends and family for supporting me throughout the studies.

Anders Nilsen Trondheim, June 2019

# **Contents**

| 1 | Intr | oduction                                                 | 1  |

|---|------|----------------------------------------------------------|----|

|   | 1.1  | Problem description                                      | 1  |

|   | 1.2  | Own contributions                                        | 2  |

|   | 1.3  | Method                                                   | 3  |

|   | 1.4  | Thesis structure                                         | 4  |

| 2 | Bac  | kground                                                  | 5  |

|   | 2.1  | Machine learning                                         | 5  |

|   | 2.2  | Speech recognition                                       | 6  |

|   | 2.3  | Previous work                                            | 7  |

|   |      | 2.3.1 Google Speech Commands dataset                     | 7  |

|   |      | 2.3.2 The Kaggle TensorFlow Speech Recognition Challenge | 8  |

|   |      | 2.3.3 Kaggle Speech Challenge neural networks            | 8  |

|   |      | 2.3.4 Keras                                              | 10 |

|   |      | 2.3.5 Microsoft MMdnmn                                   | 10 |

|   |      | 2.3.6 Semester project                                   | 10 |

|   | 2.4  | Neural Networks on FPGA                                  | 11 |

|   |      | 2.4.1 FPGA acceleration frameworks                       | 12 |

|   | 2.5  | High level synthesis                                     | 15 |

|   |      | 2.5.1 Vivado HLS                                         | 15 |

| 3 | The | oretica | l background                                         | 17 |

|---|-----|---------|------------------------------------------------------|----|

|   | 3.1 | Neura   | l networks                                           | 17 |

|   |     | 3.1.1   | Neural network basics                                | 17 |

|   |     | 3.1.2   | Topologies                                           | 27 |

|   |     | 3.1.3   | Neural network optimisations                         | 28 |

|   | 3.2 | High l  | level synthesis                                      | 29 |

|   | 3.3 | Speec   | h recognition                                        | 30 |

|   |     | 3.3.1   | Speech recognition fundamentals                      | 30 |

|   |     | 3.3.2   | Hidden Markov Models                                 | 30 |

|   | 3.4 | Speec   | h pre-processing                                     | 31 |

|   |     | 3.4.1   | Fast Fourier Transform                               | 31 |

|   |     | 3.4.2   | Framing                                              | 33 |

|   |     | 3.4.3   | Window function                                      | 35 |

|   |     | 3.4.4   | Mel-frequency scaling                                | 36 |

|   |     | 3.4.5   | Mel-scale filterbank                                 | 37 |

|   |     | 3.4.6   | Mel Frequency Cepstral Coefficients                  | 37 |

| 4 | Imp | lemen   | tation                                               | 39 |

|   | 4.1 | Pre-pr  | rocessing                                            | 39 |

|   |     | 4.1.1   | Testing using Xilinx FFT example code                | 39 |

|   |     | 4.1.2   | Prototyping in C++                                   | 41 |

|   |     | 4.1.3   | Porting the code to Vivado HLS                       | 44 |

|   |     | 4.1.4   | Integrating the HLS IP with the Zynq Processing Unit | 45 |

|   | 4.2 | Neura   | l network training                                   | 46 |

|   |     | 4.2.1   | Deciding the network topology                        | 46 |

|   |     | 4.2.2   | Preparing the input data                             | 47 |

|   |     | 4.2.3   | Loading data into the network                        | 48 |

|   |     | 4.2.4   | Training the network                                 | 48 |

|   |     | 4.2.5   | Verifying network functionality                      | 49 |

|   | 4.3 | FPGA    | acceleration                                         | 50 |

|   |     | 4.3.1   | Intel OpenVINO                                       | 50 |

|   |      | 4.3.2   | Xilinx DNNDK                                      | 52 |

|---|------|---------|---------------------------------------------------|----|

| 5 | Res  | ults    |                                                   | 55 |

|   | 5.1  | Pre-pr  | ocessing                                          | 55 |

|   |      | 5.1.1   | On Processing Unit                                | 55 |

|   |      | 5.1.2   | On FPGA                                           | 56 |

|   | 5.2  | Neura   | l networks                                        | 58 |

|   |      | 5.2.1   | Training results                                  | 59 |

|   |      | 5.2.2   | Verification results                              | 60 |

|   | 5.3  | Neura   | l network acceleration using OpenVINO             | 64 |

|   |      | 5.3.1   | On CPU                                            | 64 |

|   |      | 5.3.2   | On FPGA                                           | 65 |

| 6 | Disc | cussion |                                                   | 73 |

|   | 6.1  | Pre-pr  | ocessing                                          | 73 |

|   |      | 6.1.1   | Comparing C++ and HLS                             | 73 |

|   |      | 6.1.2   | Using Vivado HLS for FPGA acceleration            | 75 |

|   | 6.2  | Neura   | l networks                                        | 76 |

|   |      | 6.2.1   | Accuracy evaluation                               | 76 |

|   |      | 6.2.2   | Runtime comparison                                | 77 |

|   |      | 6.2.3   | Using Keras for neural network development        | 77 |

|   | 6.3  | FPGA    | acceleration                                      | 78 |

|   |      | 6.3.1   | OpenVINO accuracy                                 | 78 |

|   |      | 6.3.2   | OpenVINO runtimes                                 | 78 |

|   |      | 6.3.3   | Using Xilinx DNNDK for FPGA acceleration          | 79 |

|   |      | 6.3.4   | Using OpenVINO for FPGA acceleration              | 80 |

|   | 6.4  | Error   | sources                                           | 80 |

|   |      | 6.4.1   | Classification accuracy                           | 80 |

|   |      | 6.4.2   | Classification times                              | 81 |

|   | 6.5  | Furthe  | er work                                           | 82 |

|   |      | 6.5.1   | FPGA acceleration of pre-processing               | 82 |

|   |      | 6.5.2   | FPGA acceleration of the whole CNN using OpenVINO | 82 |

|    | 6.5.3       | FPGA acceleration using DNNDK                      | 82       |

|----|-------------|----------------------------------------------------|----------|

|    | 6.5.4       | FPGA acceleration of LSTM networks                 | 83       |

| 7  | Conclusion  | 1                                                  | 85       |

| Re | ferences    |                                                    | 87       |

| A  | Inference I | Engine per-layer execution times                   | 99       |

| В  | Precision a | and recall curves for the 12 classification words  | 101      |

| C  | Confusion   | matrices for FPGA-inferred CNN networks using Open | ıVINO115 |

# **List of Tables**

| 3.1        | List of common neural network activation functions                   | 22  |

|------------|----------------------------------------------------------------------|-----|

| 5.1        | Execution times for each part of the C++ pre-processing code running | 56  |

| <b>5</b> 0 | on an Ultra96                                                        | 36  |

| 5.2        | Resource usage estimates for synthesised single-precision mel-log-   |     |

|            | filterbank energy pre-processing on Ultrascale+ ZU3EG A484 FPGA .    | 59  |

| 5.3        | Execution time minimums, medians and averages for OpenVINO ac-       |     |

|            | celerated CNNs on different inference targets and precisions         | 66  |

| 5.4        | Classification accuracies for OpenVINO accelerated CNNs on different |     |

|            | inference targets and precisions                                     | 67  |

| A.1        | Execution times for each layer of the CNN on Central Processing Unit |     |

|            | (CPU) and single-precision- and half-precision FPGA. Dashed entry    |     |

|            | means that the layer was not run on the inference target             | 100 |

# **List of Figures**

| 2.1 | Example of dilated convolutions, converting a 2D data matrix into a    |    |

|-----|------------------------------------------------------------------------|----|

|     | 3D data cube                                                           | 9  |

| 2.2 | Program flow for the Intel OpenVINO Inference Engine                   | 14 |

| 2.3 | Code example showing the use of pragmas in Vivado HLS                  | 16 |

| 3.1 | Perceptron model as described by Frank Rosenblatt [28]. The activation |    |

|     | function is an adjustable threshold for deciding whether the result of |    |

|     | the input function is 1 or 0 $\hdots$                                  | 18 |

| 3.2 | Types of artificial neural networks [30]                               | 19 |

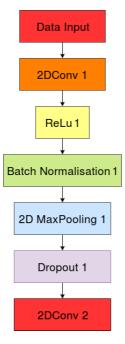

| 3.3 | Convolutional neural network layer containing several layer types to   |    |

|     | form one deep convolution layer, starting at 2DConv 1 and ending at    |    |

|     | Dropout 1                                                              | 21 |

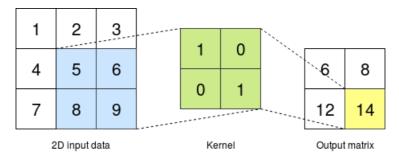

| 3.4 | Simple 2D-convolution of a 3x3 matrix with a 2x2 kernel producing a    |    |

|     | 2x2 output matrix                                                      | 23 |

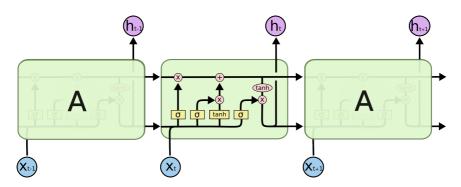

| 3.5 | An LSTM layer for three discrete time steps [34]                       | 23 |

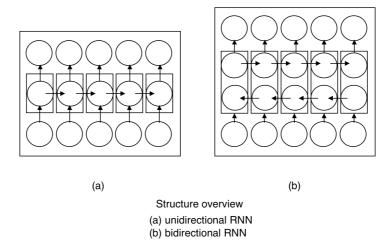

| 3.6 | Comparison of a Recurrent Neural Network (RNN) and Bidirectional       |    |

|     | Recurrent Neural Network (BRNN) layer functionality [36]. In an        |    |

|     | LSTM network, the LSTM layers are used for the squared circles of the  |    |

|     | figure                                                                 | 24 |

| 3.7 | Hidden Markov Model (HMM) showing the probability of different         |    |

|     | activities occurring based on the current weather [49]                 | 31 |

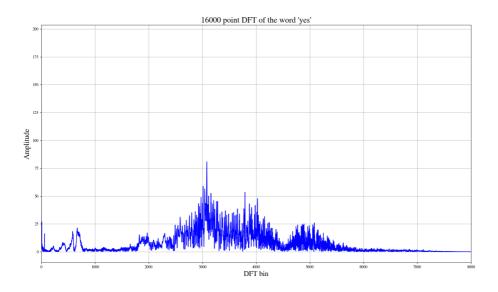

| 3.8  | Discrete Fourier Transform (DFT) of the word "yes" with an Fast Fourier           |    |

|------|-----------------------------------------------------------------------------------|----|

|      | Transform (FFT) size of 16000                                                     | 33 |

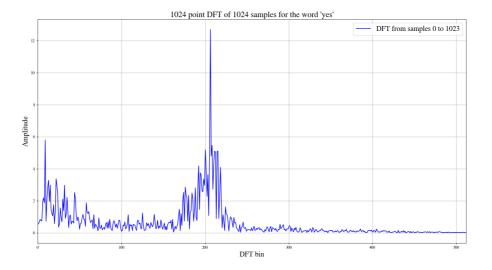

| 3.9  | DFT with a length of 1024 for the word "yes"                                      | 34 |

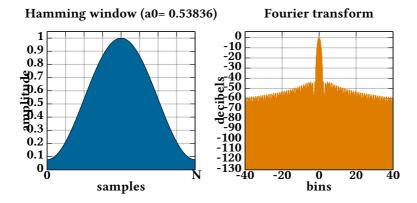

| 3.10 | Hamming window weighting with corresponding FFT [52]                              | 35 |

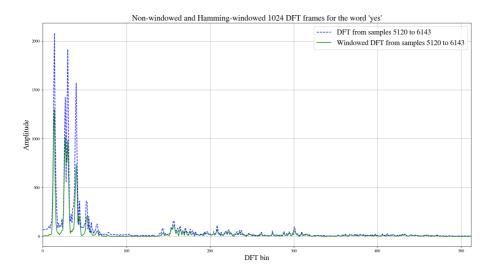

| 3.11 | Non-windowed and Hamming-windowed DFT frames for 1024 samples                     |    |

|      | of the word "yes"                                                                 | 36 |

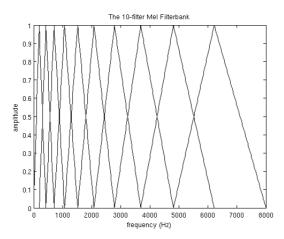

| 3.12 | Mel-filterbank of 10 filters from 0 Hz to 8000 Hz [55]                            | 37 |

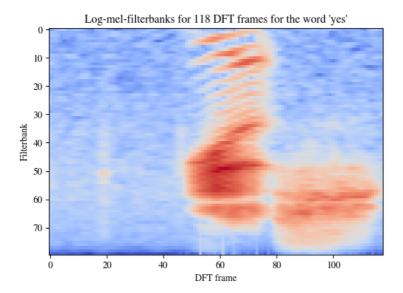

| 4.1  | Hot/cold Colormap-representation of log-mel-filterbank energies for               |    |

|      | the word "yes". Calculated using an FFT windows size of 1024, a shift             |    |

|      | length of 128 and 80 mel-filter<br>banks from 300 Hz to 8000 Hz $$                | 43 |

| 4.2  | Settings struct used for the Xilinx FFT IP-core in Vivado HLS                     | 44 |

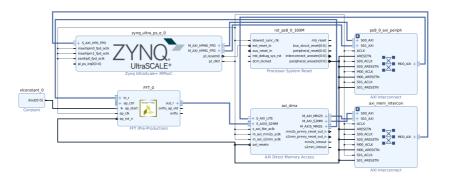

| 4.3  | Block diagram from Vivado IP Block Design tool for the communication              |    |

|      | between the FFT HLS IP block and the Zynq Processor System (PS) $$ .              | 46 |

| 4.4  | Layer execution times as reported by the Inference Engine                         | 51 |

| 4.5  | Execution times and throughputs reported at the end of Inference                  |    |

|      | Engine-based prediction using OpenVINO                                            | 52 |

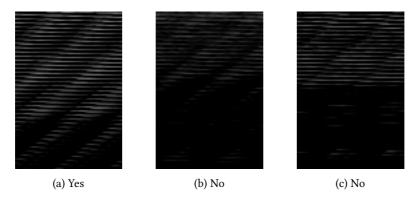

| 4.6  | DECENT input images generated from log-mel-filterbank energies                    |    |

|      | using the Pillow library for Python                                               | 53 |

| 4.7  | Error message generated by DNNC upon kernel compilation                           | 54 |

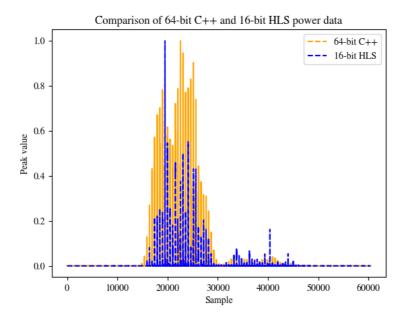

| 5.1  | Comparison of power data calculated using 64-bit C++ and 16-bit HLS               | 57 |

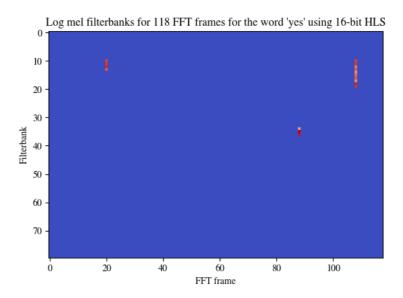

| 5.2  | Hot/cold Colormap-representation of log-mel-filterbank energies for               |    |

|      | the word "yes". Calculated using 16-bit HLS FFT with a window size of             |    |

|      | 1024, shift length of 128 and 80 mel-filterbanks from 300 Hz to $8000\mathrm{Hz}$ | 58 |

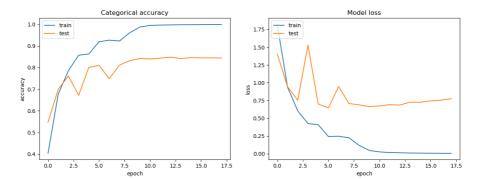

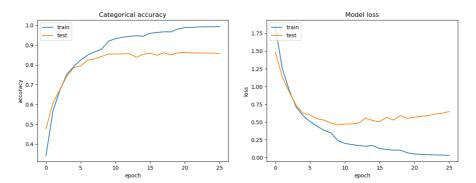

| 5.3  | Training and validation loss and accuracy for CNN                                 | 60 |

| 5.4  | Training and validation loss and accuracy for LSTM network                        | 61 |

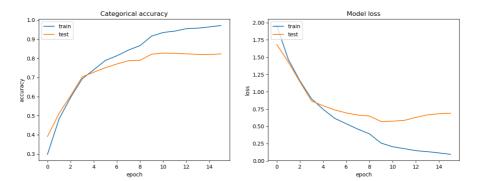

| 5.5  | Training and validation loss and accuracy for att-LSTM network                    | 62 |

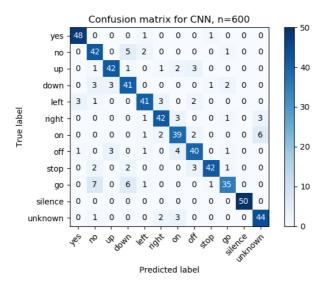

| 5.6  | Confusion matrix for CNN for 12 words with no thresholding                        | 63 |

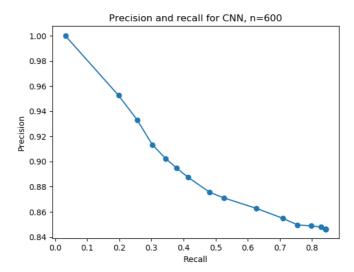

| 5.7  | Precision and recall curve for CNN with thresholding from 1.00 to 0.00            |    |

|      | with 0.05 decrements per step                                                     | 64 |

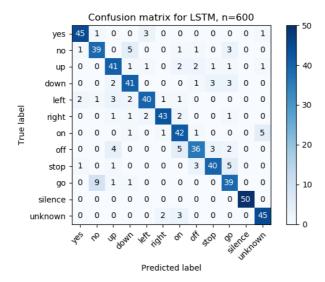

| 5.8  | Confusion matrix for Keyword Spotting (KWS) LSTM for 12 words                     |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | with no thresholding                                                              | 65  |

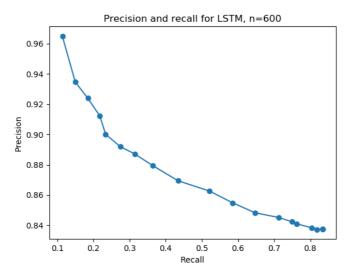

| 5.9  | Precision and recall curve for KWS LSTM network with thresholding                 |     |

|      | from 1.00 to 0.00 with 0.05 decrements per step                                   | 66  |

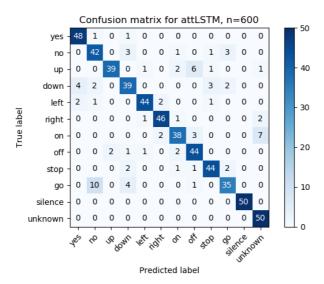

| 5.10 | Confusion matrix for KWS att-LSTM network for 12 words with no                    |     |

|      | thresholding                                                                      | 67  |

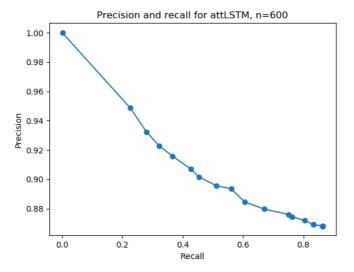

| 5.11 | Precision and recall curve for KWS att-LSTM network with threshold-               |     |

|      | ing from 1.00 to 0.00 with 0.05 decrements per step $\ \ldots \ \ldots \ \ldots$  | 68  |

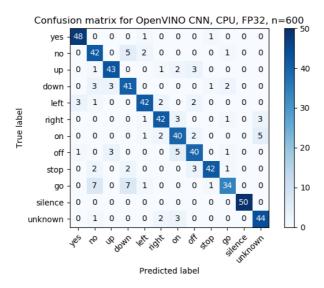

| 5.12 | Confusion matrix for single-precision CPU-inferred KWS CNN $$                     | 69  |

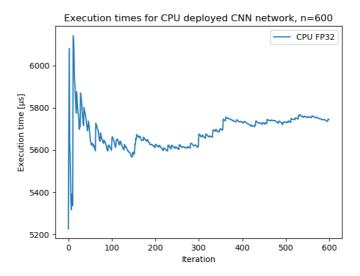

| 5.13 | Runtimes for single-precision CPU-inferred KWS CNN                                | 70  |

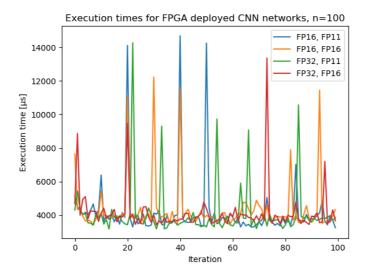

| 5.14 | Execution times for different precision CPU/FPGA-deployed KWS                     |     |

|      | CNNs using OpenVINO                                                               | 71  |

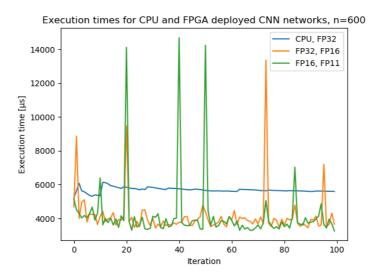

| 6.1  | Classification times across 100 iterations with CPU and FPGA as infer-            |     |

|      | ence targets using OpenVINO                                                       | 79  |

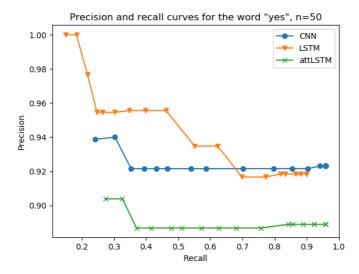

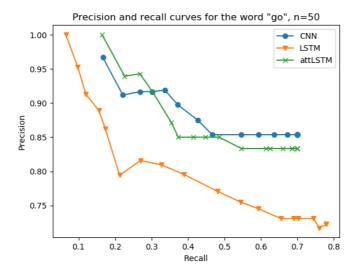

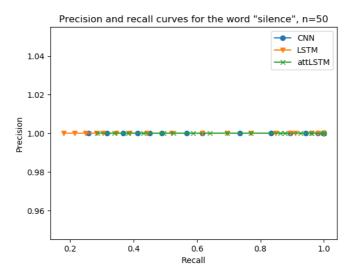

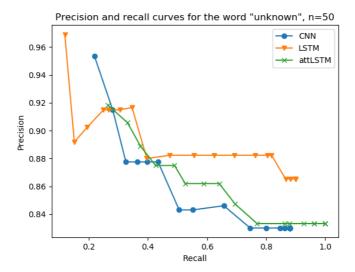

| B.1  | Precision and recall curve for the word "yes" for all networks                    | 102 |

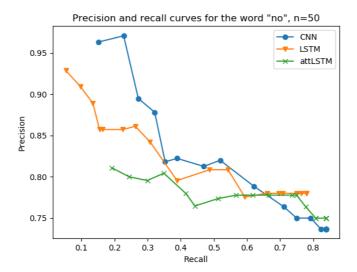

| B.2  | Precision and recall curve for the word "no" for all networks $\ \ldots \ \ldots$ | 103 |

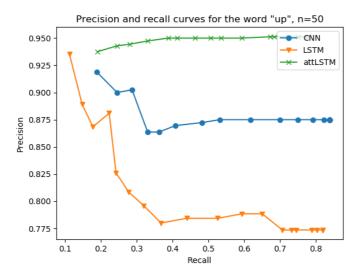

| B.3  | Precision and recall curve for the word "up" for all networks $\ \ldots \ \ldots$ | 104 |

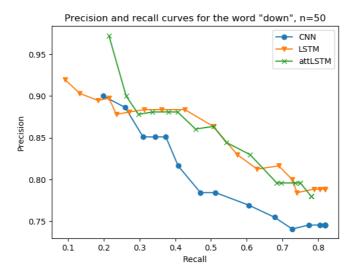

| B.4  | Precision and recall curve for the word "down" for all networks $$                | 105 |

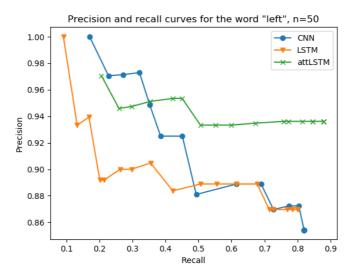

| B.5  | Precision and recall curve for the word "left" for all networks                   | 106 |

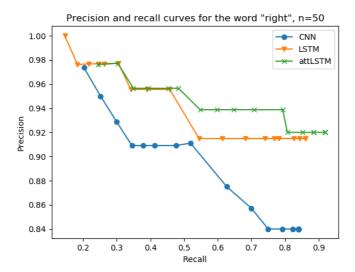

| B.6  | Precision and recall curve for the word "right" for all networks                  | 107 |

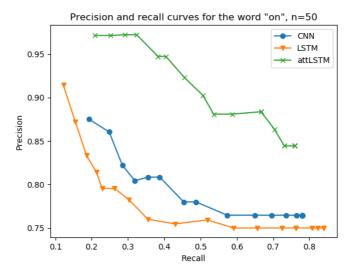

| B.7  | Precision and recall curve for the word "on" for all networks                     | 108 |

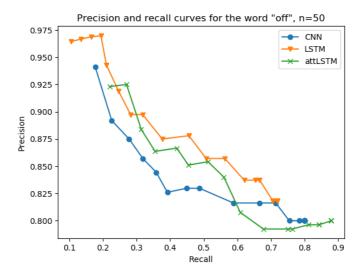

| B.8  | Precision and recall curve for the word "off" for all networks                    | 109 |

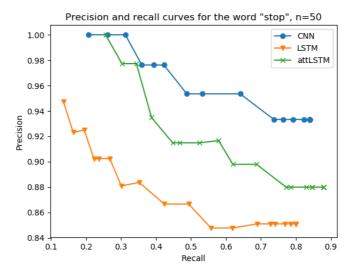

| B.9  | Precision and recall curve for the word "stop" for all networks                   | 110 |

| B.10 | Precision and recall curve for the word "go" for all networks                     | 111 |

| B.11 | Precision and recall curve for the "silence" for all networks                     | 112 |

| B.12 | Precision and recall curve for the unknown word ("marvin)" for all                |     |

|      | networks                                                                          | 113 |

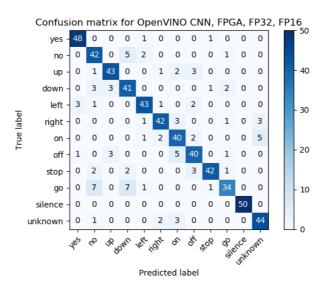

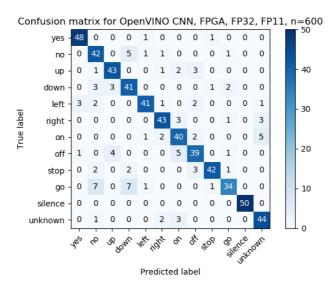

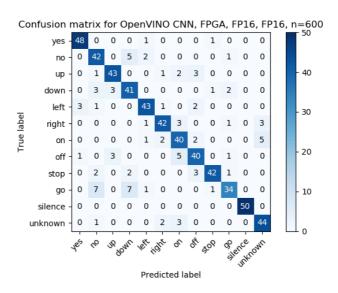

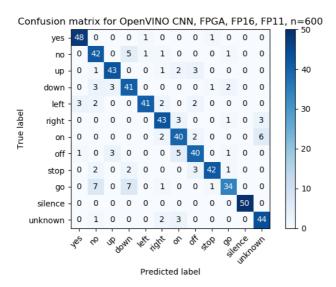

| C.1  | Confusion matrix for single-precision KWS CNN inferred on half-                   |     |

|      | precision bitstream                                                               | 116 |

| C.2 | Confusion matrix for single-precision KWS CNN inferred on 11-bit                 |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | precision bitstream                                                              | 117 |

| C.3 | $Confusion\ matrix\ for\ half-precision\ KWS\ CNN\ inferred\ on\ half-precision$ |     |

|     | bitstream                                                                        | 118 |

| C.4 | Confusion matrix for half-precision KWS CNN inferred on 11-bit pre-              |     |

|     | cision hitstream                                                                 | 119 |

# Chapter 1

## Introduction

This chapter briefly explains the problem, the contributions made during the project and the report structure.

### 1.1 Problem description

Speech recognition is the process of recording, converting and interpreting spoken words and sentences. One device performing speech recognition is Amazon's Alexa, which takes user commands and responds based on these commands. Speech recognition requires large vocabularies on the receiving end, something which has traditionally been done using Hidden Markov Models (HMMs), though recently Deep Neural Networks (DNNs) have become the standard for such tasks. DNNs for large-vocabulary tasks can have several million parameters and computations, requiring large amounts of computational power, usually computed using powerful servers and computers. The power required makes these networks unsuitable for edge-deployment on devices such as Microcontroller Units (MCUs), small CPUs or FPGAs. To solve this, keyword detection networks are used, which specialise in recognising a subset of words. If the network detects one of the words in question, it establishes a link to a server which can classify the rest of the sentence and the words to come.

Keyword detection networks still require relatively large amounts of computational power when compared to traditional embedded systems such as smart-devices. To solve this, neural networks can be optimised and accelerated on FPGAs, exploiting the parallel computation capabilities of the device along with its low power consumption. This results in energy-efficient and accurate neural networks with relatively short classification times.

Previously, a keyword spotting neural network was accelerated on an Intel Arria 10 GX FPGA using OpenVINO as part of a semester project at NTNU in 2018. The network had been trained using the Caffe framework to detect the phrase "Hey Spark". A C++ program was developed to interface with OpenVINO's Inference Engine which also recorded live audio from a microphone and pre-processed the recording using a pre-compiled binary file from Cisco.

This thesis will focus on training and accelerating three different neural networks to perform KWS based on the Google Speech Commands dataset using Keras. The networks will then be accelerated on an FPGA using Intel OpenVINO or Xilinx DNNDK. The pre-processing required for the network will be programmed using C or C++ and also accelerated on an FPGA using Vivado HLS.

#### 1.2 Own contributions

The following own contributions have been made to the thesis:

- A literary study of speech recognition neural networks in regards to history, theory and previous work. The previous work is mostly in regards to the Kaggle Speech Recognition challenge.

- A C++-implementation of the required pre-processing, converting .wav audio files into log-mel-filterbank energies.

- A synthesisable C++ implementation of the pre-processing, developed using Vivado HLS.

1.3. METHOD 3

A modified Vivado HLS example for performing pre-processing with 16-bit floating point precision on an FPGA and PS.

- Development of a Python program for training KWS neural networks using Keras.

- Development of a Python program for verifying the functionality of KWS neural networks using Keras.

- An updated C++-program for inferring an optimised neural network using Intel OpenVINO on an Intel Arria 10 GX or on a CPU. Also involves verification of the inferred network.

- An exploration into using Intel OpenVINO and Xilinx DNNDK for acceleration of KWS neural networks on FPGA.

- Recommendations for future works in regards to FPGA acceleration of KWS neural networks.

#### 1.3 Method

To test the FPGA acceleration possibilities of Intel OpenVINO and Xilinx DNNDK, some neural networks have to be trained. This requires networks, either pre-designed or designed from scratch, and corresponding training data. Training data has to be created or generated for the purpose, and most likely require some pre-processing before being used by the network. This pre-processing requires theoretical knowledge in the field of signal processing.

After training data has been generated, the networks have to be trained and validated. Once trained, the networks can be accelerated on FPGAs using OpenVINO or DNNDK. This requires setting up the SDKs and programming the required programs using their respective Application Programming Interfaces (APIs), as well as preparing the networks as required. In addition, the pre-processing has to be accelerated on an FPGA using Vivado HLS. Using these tools and programs requires knowledge about how they work and how to use them.

To verify that the pre-processed data is correct, the generated training data, using the non-accelerated C++ code, is compared against the data generated by a known good implementation, and the FPGA-accelerated pre-processing is verified against the non-accelerated results. In the case of the network classifications, the classifications are verified by earmarking a part of the dataset for verification purposes prior to training.

The results are analysed and discussed to evaluate the performance of the SDKs, in terms of speedup, accuracy and usability, as well as the performance of the networks, to determine what network type is most suitable for FPGA acceleration and possibly deployment. If no direct result can be achieved, an estimate can be made if enough related results are available.

#### 1.4 Thesis structure

This chapter, chapter 1, introduces the problem, the contributions made to the thesis, the method for solving the problem and the thesis structure. Chapter 2 presents some background information in regards to the history and concepts of machine learning and speech recognition, as well as some previous work in the field of speech recognition and keyword detection. Chapter 2 also presents some FPGA acceleration SDKs and HLS tools. In chapter 3, theory for neural networks, HLS, speech recognition and speech pre-processing is presented. Chapter 4 covers the development and implementation process of: Developing and accelerating speech recognition pre-processing code, using C++ and Vivado HLS; neural network training, using Keras; and FPGA acceleration, using Intel OpenVINO and Xilinx Deep Neural Network Development Kit (DNNDK). Next, chapter 5 presents the results of the training and acceleration, while chapter 6 discusses the results achieved. Chapter 7 presents the conclusion of the thesis.

# **Chapter 2**

# **Background**

This chapter presents a brief history of machine learning and speech recognition, as well as some related work in neural network speech recognition and FPGA acceleration. Additionally, this chapter presents some information on the Google Speech Commands dataset and the accompanying Kaggle Speech Challenge, some related works and examines some frameworks for FPGA acceleration of neural networks and HLS. Chapters 2.4.1.1 and 2.4.1.2 were initially written for the semester project.

## 2.1 Machine learning

Machine learning is a concept which dates back to 1959 when the term was coined by Arthur Samuel [1], though its origins can be traced back to Alan Turing [2] and his concept of the "learning computer". The concept revolves around using statistical techniques to make a computer "learn" an operation using sets of data instead of manually adjusting and writing the program to achieve the desired response. Initially, machine learning was restricted to relatively simple tasks such as playing checkers [3]. Though advances were being made, the field experienced periods of disinterest and reduced funding, caused mainly by unsatisfied expectations, notably in the Lighthill Report from 1973 [4]. Interest in machine learning remained dormant, increasing and

decreasing for small periods during the 1980s, until the 1990s when interest flourished. Development shifted from general-purpose A.I. to task-specific applications, leading to more clearly defined goals and less heightened expectations from the public. 2002 saw the release of Torch [5], a machine learning framework, to simplify the development of neural networks. Publicly available tools, lower cost of computational power and public interest saw the creation of other frameworks, such as free and open-source frameworks such as TensorFlow [6] and Caffe [7].

### 2.2 Speech recognition

The field of speech recognition can be traced back to Bell Labs' 1952 system "Audrey" [8], a primitive computer capable of recognising digits uttered by a single speaker. Early systems were limited to single-speaker, single word utterances and small vocabularies, but after researchers started using Hidden Markov Models (HMMs) for speech recognition in the 70's [9], vocabularies increased to the thousands, with IBM's 1984 typewriter system "Tangora" boasting a trainable vocabulary of 20.000 words [10]. Progress was limited by the cost of computers and storage space, but as technology improved, so did speech recognition. In 1992, AT&T started using speech recognition to route telephone calls [11] and for customer service [12]. As computational power increased and costs decreased, more advanced speech recognition systems were developed, mostly based on HMMs. The 2000s saw the rise of neural networks and were soon deployed in speech recognition. Early systems used HMMs alongside neural networks, but in recent years the focus has shifted to primarily using neural networks.

Today, speech recognition platforms have mostly shifted from HMMs to neural networks, using either Convolutional Neural Networks (CNNs) or Recurrent Neural Networks (RNNs). These models are often deployed on servers using Graphical Processing Units (GPUs) for acceleration, using edge-devices for detecting speech commands, also known as keyword spotting, to create an uplink when a keyword is detected.

While previously limited to specific devices, today, speech recognition is available on most computer platforms, from home computers to smart-phones. The most notable

2.3. PREVIOUS WORK 7

example is Apple's Siri, recognising and answering questions from the user. Most major electronic brands have their own speech recognition system, such as Apple's Siri and Microsoft's Cortana. Speech recognition is still being used for customer service, voice-controlled applications and are a significant part of the "smart home" concept.

### 2.3 Previous work

#### 2.3.1 Google Speech Commands dataset

The Google Speech Commands dataset is a dataset consisting of speech samples for up to 35 different words. Initially released in 2017, the dataset featured 30 different words, each word featuring 1600 to 4000 different variations [13], and has since been updated to include over 100.000 samples for 35 words. The dataset is targeted towards developers of edge-deployed Keyword Spotting (KWS) neural networks as a toolset to train and verify the functionality of the networks, while another target audience is hardware manufacturers. By having a common dataset, manufacturers can demonstrate their products by using networks trained with the toolkit, in addition to creating specialised hardware or optimisations to cater to KWS neural networks.

All recordings in the dataset have the same file properties: Recorded at 16 kHz with a bit-rate of 16 bits, all clips are 1 s long and stored as .wav-files. The recordings were selected based on specific criteria, such as intelligibility and loudness, initially using file size and average loudness levels to filter unsuitable samples, followed by manual verification to check that the pronounced word is the same as the label. The words in the dataset were chosen based on commonness, such as "yes" and "no", the number of phonemes, such as "Marvin" and "Sheila", or their similarity to other words in the dataset, such as "tree" and "three". The recordings were collected through a website where users could record themselves pronouncing words from the dataset. No specific guidelines were set, ensuring different recording qualities and background noises for the recorded samples, creating a more realistic dataset.

#### 2.3.2 The Kaggle TensorFlow Speech Recognition Challenge

The Kaggle TensorFlow Speech Recognition Challenge was a neural network design competition issued by Google Brain in January 2018 on the Kaggle platform. The challenge consisted of designing and training a CNN using TensorFlow to recognise 12 words from the Google Speech Commands dataset, with a special extra competition which required the network to run on a Raspberry Pi 3 with specific requirements [14]. The Google Speech dataset consists of 30 different words, each recorded 2000 times resulting in a data set of 60.000 samples, in addition to 6 background noise samples. To reduce network size and scope, the Kaggle challenge selected 10 words from the dataset: *yes, no, up, down, left, right, on, off, stop, go, silence* and *unknown. Unknown* is one of the remaining words in the dataset, selected by the user, used to represent any word other than the ones listed, while *silence* represents no sound.

After designing and training the network, contestants could test their network on a test-dataset by uploading it to the Kaggle website and afterwards submitting it as an entry in the competition. The top three networks were able to achieve a classification accuracy of 91% using CNNs. Afterwards, the winning entries explained how they were able to achieve these results on the discussion pages for the challenge. The winning submission, achieving a classification accuracy of 91.06%, used log-mel-filterbanks as the input data to a CNN-based network, with several networks running simultaneously in ensemble-form to achieve higher accuracy.

#### 2.3.3 Kaggle Speech Challenge neural networks

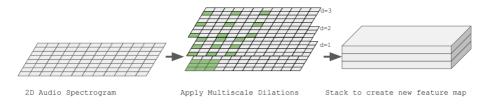

Though the techniques used by the winners were explained, the neural networks themselves were not released. Still, several papers have used the challenge and dataset as a metric for measuring the accuracy of their networks. McHahan et al. [15] used the dataset to evaluate pre-trained speech recognition models as well as "fresh" models, using two different input techniques. One set of models used regular input, a 2D-matrix of mel-filterbank data, and another using multiscaling. Multiscaling is the technique of performing several dilated convolutions on the same set of data. Dilation is a relatively new parameter in convolutions, introduced in 2015 by Yu et al. [16], in addition to

2.3. PREVIOUS WORK 9

stride and kernel size, which increases the stride length by skipping spaces of data. Performing dilated convolutions 2D input data creates 3D output data, as illustrated by figure 2.1.

Figure 2.1: Example of dilated convolutions, converting a 2D data matrix into a 3D data cube

The networks using dilated convolutions achieved a classification accuracy of 82.22% and 85.52% for fresh and pre-trained, respectively, compared to 81.32% and 82.84% for non-multiscale networks for 20 words.

In 2018, de Andrade et al. [17] used the dataset to evaluate the classification accuracy of three networks: A CNN, an LSTM network and an Attentive LSTM (att-LSTM) network. The att-LSTM network used an attention model to detect parts of the data which were of interest, such as ignoring periods of silence and increasing attentiveness when speech information was present. Also illustrated by Bahdanau et al. [18] and Vaswani et al. [19], neural attention models increase performance on long sequence-to-sequence models, such as speech recognition. In addition to accuracy, de Andrade et al. [17] focused on developing network models with relatively few parameters, around 200K, to make the networks more suitable for edge deployment. Similar to McHahan et al. [15], the networks used 2D mel-filtered data as the input, though logarithmised. The final att-LSTM network had 202K trainable parameters, compared to 185K and 3060K for the LSTM network and CNN, respectively. The att-LSTM network achieved a classification accuracy of 94.5% for 20 words and 96.9% for 12 words, as used for the Kaggle Speech Challenge. The final network models were uploaded to GitHub under no specific license.<sup>1</sup>

$<sup>^{1}</sup> https://github.com/douglas125/SpeechCmdRecognition \\$

#### 2.3.4 Keras

Keras<sup>2</sup> is an open-source neural network library for Python. Originally released in March 2015, Keras aims at providing a high-level interface towards machine learning frameworks such as TensorFlow and MXNet and features GPU support along with the standard CPU support. Keras describes a neural network model as a sequential structure of layers, allowing for rapid prototyping and modularity.

#### 2.3.5 Microsoft MMdnmn

MMdnn³ is a toolkit developed by Microsoft to convert models between frameworks, i.e. convert TensorFlow-models to MXNet-models. As of 2019-06-03, the framework supports conversion between Caffe, Keras, TensorFlow, CNTK, MXNet, PyTorch, CoreML and ONNX. The toolkit converts between the frameworks by initially converting the model into an intermediate representation before converting it into the target framework. The toolkit also features a graph visualiser for visualising the neural network structure.

#### 2.3.6 Semester project

During autumn 2018, a semester project was conducted examining FPGA acceleration of a KWS neural network using OpenVINO for Cisco [20]. The neural network was a binary classifier performing keyword spotting for the phrase "Hey Spark" on a 0.9 s input recording, either performed live using a microphone or a pre-recorded sample. The network was accelerated on a server at NTNU on an Intel Arria 10 GX Development Kit, achieving a classification time of 5.85 ms and 3.10 ms for CPU and FPGA, respectively. The network was inferred on the CPU/FPGA using a C++-program integrating the Inference Engine with the live audio recording or sample loading. The program was partially based on a master's thesis from Spring 2018, where the same network was accelerated using OpenCL and the Arria 10 GX Development Kit. The semester project C++ program used the same pre-processing, live recording technique

<sup>&</sup>lt;sup>2</sup>https://keras.io/

$<sup>^3</sup>$ https://github.com/microsoft/MMdnn

and sample loading as the program from the master's thesis. The pre-processing was a pre-compiled binary file supplied by Cisco which generated Mel-Frequency Cepstrum Coefficient (MFCC) values for the input sample. The neural network was designed and trained using Caffe. The project report is available along with the associated code on GitHub<sup>4</sup>.

#### 2.4 Neural Networks on FPGA

FPGAs offer high performance per watt, making it a strong candidate for neural network computations and inference. Neural networks deployed on an FPGA can also be sped up when the inferred algorithm uses low numeric precision in calculations, e.g. using fixed point weighting and quantisation data instead of 32-bit floating point. These optimisations can provide substantial speedup while maintaining reasonable accuracy [21][22].

Due to this, FPGAs are a preferred platform for running inferred artificial neural networks. One of the main problems reducing the adoption rate is, and has been for many applications, how they are programmed. FPGAs are not programmed in the same way as MCUs or computer programs using a programming language such as C++ or C which is assembled into machine-level instructions. An FPGA is "programmed" by describing the functionality using a Hardware Description Language (HDL), such as VHDL or Verilog. The HDL code is then synthesised into a netlist which is mapped onto the FPGA. This way of programming differs from regular programming and increases the difficulty of writing effective and quality HDL-code, in most cases requiring specialised engineers. To reduce the difficulty of programming FPGAs, several tools exist to synthesise high-level programming languages, such as C, C++ and Python, into HDL code. This is called High-level Synthesis (HLS), and can be utilised in conjunction with Artificial Neural Networks (ANNs) to allow for inference of C++ code using OpenCV, TensorFlow, Caffe and other frameworks to FPGA without the need for the designer to write HDL-code.

$<sup>^4</sup> https://github.com/andernil/OpenVINO\_project$

#### 2.4.1 FPGA acceleration frameworks

#### 2.4.1.1 OpenCL

Open Computing Language (OpenCL) [23] is a platform heterogeneous framework for writing and running programs on several computing platforms, including CPUs, GPUs, FPGAs, Digital Signal Processors (DSPs) and other hardware accelerators. OpenCL was launched in 2009 by Apple to utilise the acceleration possibilities of on-board GPU. A collaborative group, the Khronos Compute Working Group, was created featuring representatives from several CPU, GPU, embedded-processing and software companies to maintain and improve the framework. As of this report, the newest version was 2.2, which incorporated more C++ features to the language.

The OpenCL framework is officially available for C and C++, but is unofficially available for Python, Java, Perl and .NET. An OpenCL implementation of a program is based around a host containing several compute devices, such as a CPU and a GPU, which is further divided into multiple processing elements. A function which is executed using OpenCL is called a kernel and can run in parallel on all processing elements. A programmer can utilise the acceleration capabilities available on a system by getting the device information from the computer the program is running on.

While OpenCL provides good possibilities for acceleration and resource usage, it is limited by its low-level nature. While it has functions for standard operations like FFT, neural networks have to be manually declared unless the frameworks used to generate the network have OpenCL-branches. Caffe has such a branch [24], but it is currently under development. TensorFlow has an OpenCL-branch on its roadmap. The lack of neural network framework support limits its adoption. A more supported and similar framework to OpenCL is Nvidia's CUDA, although this only runs on Nvidia GPUs.

#### 2.4.1.2 Intel OpenVINO

The OpenVINO toolkit is Intel's solution for running neural networks on FPGAs, and aims to simplify the process compared to existing solutions. The OpenVINO toolkit was launched in 2018 by Intel, and allows users to program applications where neural networks can be accelerated on Intel processors, GPUs, FPGAs and Vision Processing

Units (VPUs) [25]. The toolkit is available for Windows 10, CentOS, Ubuntu and Yocto Project Poky Jethro, but compatibility with different inference targets varies between platforms. As of this report, FPGA acceleration with OpenVINO works on the Altera Arria 10 GX development kit and the Intel Vision Accelerator Design with Intel Arria 10, with a retail price of \$4,495, while there is no publicly available retail price for the Vision Accelerator. These FPGAs have a PCI-Express connector which allow them to easily be integrated into a computer.

OpenVINO is mainly used for accelerating image recognition CNNs, but can be used for other purposes such as speech recognition. It supports frameworks such as Caffe and TensorFlow and deep learning architectures such as AlexNET and GoogleNET. It supports a set amount of layers for each framework out of the box, with custom layer support available for developers.

To use OpenVINO in a project, the neural network model is optimised using the model provided by the neural network framework, such as a .caffemodel (from Caffe), with the calculated weights with the Model Optimizer. The default model precision is single-precision floating point, while quantisation to half-precision floating point is available in the Optimizer. 8-bit integer quantisation is also available. The Optimizer provides an optimised intermediate representation which is loaded into the code using the Inference Engine API. The API prepares and infers the network to the target device and runs the network with the supplied input data. All pre- and post-processing is done in C++, so the only part which has to be replaced is the inference or prediction process. On FPGA, OpenVINO uses a pre-loaded bitstream programmed onto the FPGA to accelerate instructions. It does not utilise HLS, but uses the FPGA as a specialised processor for performing mathematical operations found in neural networks, such as convolutions and activations. The OpenVINO bitstreams utilise all available space on the FPGA, leaving no room for additional HDL code.

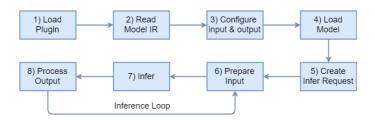

Figure 2.2 show the program flow when using the Inference Engine:

1. Load Plugin - The appropriate plugin for the deployment target is selected, such as FPGA and CPU, or for multiple targets, Hetero, which runs the network on the CPU if it is unsupported on the primary targeted device.

Figure 2.2: Program flow for the Intel OpenVINO Inference Engine

- Read Model IR The Intermediate Representation of the target neural network is loaded into the Inference Engine. If Hetero-execution is selected, the network layers are split between the target device and the CPU depending compatibility.

- Configure input and output The input and output accuracies are specified, as well as the input layout.

- 4. Load Model The model is loaded from the IR into the system memory

- 5. Create Infer Request An inference request is sent to the Inference Engine to ready for inference onto the target device(s).

- 6. Prepare input The input data is loaded into the network.

- 7. Infer The network is inferred onto the target device(s) along with the input data. The layers are executed in order and an output is generated.

- 8. Process Output The output is loaded from the Inference Engine.

As illustrated by figure 2.2, it is recommended to repeat steps 6 through 8 when the network is used multiple times in one session.

Several network topologies are supported by OpenVINO, such as CNN and LSTM; however, LSTM support is limited to only the Kaldi-framework and partially for MXNet.

#### 2.4.1.3 Xilinx DNNDK

To compete with OpenVINO, Xilinx acquired Chinese developer DeePhi in 2018 and their neural network FPGA acceleration SDK, the Deep Neural Network Development Kit (DNNDK). The DNNDK SDK features model pruning, quantisation and deployment on Xilinx FPGA development kits such as the Xilinx ZCU102 (\$2800), ZCU104 (\$1000) and Avnet Ultra96 (\$250) along with some of DeePhi's development kits. Along with FPGAs, the systems have embedded MCUs, on the Xilinx devices called Multi-Processor System-on-Chip (MPSoC), with FPGA as Programmable Logic and MCU as Processor System (PS). According to DeePhi, the SDK is capable of accelerating CNNs as well as RNNs, achieving a throughput speedup of 1.8x and 19x when compared to Application Specific Integrated Circuit (ASIC) and HLS-implementations of the same network, using 56x less power than the HLS implementation [26]. The SDK is divided into three main programs: DECENT, DNNC and the C++-API.

DeePhi's solution to running neural networks on an FPGA is to accelerate them using a soft-core processor, the Deep-learning Processor Unit (DPU). The DPU is designed to support and accelerate common neural network designs, such as AlexNET, SSD and SqueezeNet, as well as custom networks. In contrast to OpenVINO, the FPGA image does not occupy the whole FPGA, leaving space for custom HDL-code to run alongside the SDK.

DECENT performs quantisation on the weights and activations in the SDK, from 32-bit floating point to 8-bit signed integer precision, optimising mathematical functions and memory usage. DECENT also performs pruning, removing unnecessary connections and neurons.

DNNC splits the neural network into smaller kernels for either deployment on main parts of the MPSoC, the PS or FPGA/DPU, depending on the network type, which are then loaded and used using a C++-program to interface with the target devices.

# 2.5 High level synthesis

#### 2.5.1 Vivado HLS

Vivado HLS is Xilinx' HLS tool for HDL synthesis of C, C++ and SystemC. Initially a paid upgrade to the standard Vivado package, Vivado HLS has since been included for free alongside the core Vivado package. The program allows for any of the supported

programming languages to be loaded into the program, simulated and synthesised into HDL and exported either as HDL or as a Vivado IP Core. The program has several features, such as specialised HLS libraries, IP cores such as FFT and FIR-filters, C-simulation and software/hardware co-simulation. Vivado HLS is integrated with other Xilinx programs, using Vivado XSim for HDL debugging and waveform analysis, in addition to Vivado's IP Block Design tool. Vivado HLS also features the use of pragma directives to perform optimisations to the synthesised code, such as loop unrolling, parallelisation and interface optimisation. Figure 2.3 shows an example of pragmas for specifying loop-unrolling and partitioning.

```

template<class TI, class TO, class TC, int SZ, win_fn_t FT, int UF>

void window_fn(TI *indata, TO *outdata)

{

TC coeff_tab[SZ];

init_coef_tab<rr/>

init_coef_tab<rr/>

#pragma HLS ARRAY_PARTITION variable=coeff_tab cyclic factor=UF

apply_win_fn:

for (unsigned i = 0; i < SZ; i++) {

#pragma HLS URROLL factor=UF

#pragma HLS DIPELINE rewind

outdata[i] = coeff_tab[i] * indata[i];

}

}</pre>

```

Figure 2.3: Code example showing the use of pragmas in Vivado HLS

The code to be synthesised is defined by selecting a "top-function", the function from which all code within shall be synthesised. This requires all functionality of the program to be divided into subfunctions, and only one function can be selected as the top function. If several independent parts of the code are to be synthesised, the functions have to be synthesised separately.

# **Chapter 3**

# Theoretical background

This chapter explores some of the theory behind Artificial Neural Networks (ANNs), High-level Synthesis (HLS) and digital signal processing for speech recognition. Chapter 3.1.1 was originally written for the semester project.

### 3.1 Neural networks

#### 3.1.1 Neural network basics

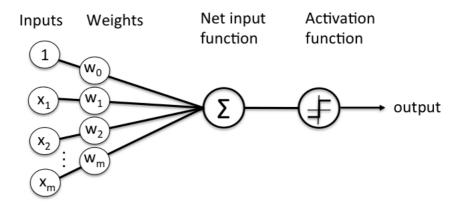

Machine learning uses Artificial Neural Networks (ANNs) to perform calculations and predict or classify an output based on a set of input data, attempting to emulate the functionality of the neural networks found in the human brain. Although computers are more efficient at performing mathematical computations and storing data, humans are better at learning tasks. Learning a new skill, recognising faces and voices and decision making are tasks which humans are better at, and which computers struggle with performing. These actions are, in humans, performed by a neural network in the brain. This neural network consists of approximately 10<sup>11</sup> neurons which are interconnected into a decision tree [27]. The desire to mimic the human neural network motivated scientists to create a mathematical model of a neuron called a perceptron. A model of

the perceptron was described by Frank Rosenblatt in 1958.

# Schematic of Rosenblatt's perceptron.

Figure 3.1: Perceptron model as described by Frank Rosenblatt [28]. The activation function is an adjustable threshold for deciding whether the result of the input function is 1 or 0

Figure 3.1 shows a block diagram of the model proposed by Rosenblatt. The diagram served as a basis for further computational models and was implemented in software by IBM in 1958 to perform image recognition, though limited to only one pattern. The limitation was due to the network having only one layer. The solution to this limitation was to implement a feed-forward, multi-layered neural network consisting of perceptrons, as suggested by Stephen Grossberg in 1973 [29]. This type of network is called a Deep Neural Network (DNN), while networks with a single hidden layer are traditionally called a Artificial Neural Network (ANN).

These new types of networks consist of several different types. The most common

network types are shown in figure 3.2. The network types can be divided into several categories: Feed-forward, recurrent, competitive and self-organising. Feed-forward networks, such as figure 3.2a and 3.2b, can be compared to combinatorial logic circuits. Recurrent networks, such as figure 3.2c and 3.2d, are more akin to sequential circuits with the recursive connections acting as a short-term memory. Competitive neural networks and self-organising networks, such as figure 3.2e and 3.2f, allow the networks to self-organise and build input feature maps, a feature used during network training.

Figure 3.2: Types of artificial neural networks [30]

The neural network type to use depends on the task of the network. For image recognition, convolutional neural networks can be used, while for handwriting and speech recognition, recursive neural networks can be used. After selecting a network

type, the weighting of the connection between the nodes has to be calculated. This is performed by training the network.

### 3.1.1.1 Network design

Neural network design is a complex field, with several layer types to choose from to perform different functions. The only standard, go-to layers are the input and output layers. The input layer is usually some form of pre-processing, such as normalisation or re-ordering. The output layer represents the result of the network, often in one-hot encoding or integer values. Neural networks can be further divided into smaller "networks" for each layer, as they might contain convolutions, activations and poolings to perform a function, such as a deep convolution network layer as shown in figure 3.3. Several layers exist, such as:

**Activation functions:** Activation functions are used to perform gating and weighting on the input values of the function, adding a non-linear property to the neural networks. Several activation function types exist with different mathematical properties. Linear activation uses a linear scaling factor on the input value, while the step function is zero for negative values and one for positive values. Table 3.1 shows some common activation functions.

**Pooling:** Pooling layers are used to reduce the spatial dimension without reducing the depth of the data, e.g. if the data has the dimensions  $H \times W \times Depth$ , pooling reduces the dimensions to  $H' \times W' \times Depth$ . Reduction can be done in several ways, either downsampling using algorithms such as skipping or averaging, leading to several different variations of the pooling function. One such variation of pooling is max-pooling, where a window "slides" over an area of the input data and selects the highest value. Pooling reduces the amount of data in the neural network, increasing computation performance and decreasing the number of tunable parameters, further improving performance and reducing the risk of overfitting.

Figure 3.3: Convolutional neural network layer containing several layer types to form one deep convolution layer, starting at 2DConv 1 and ending at Dropout 1

**Dense:** Dense layers are fully connected layers, i.e. each input node is connected to each output node with adjustable weights for each connection. These layers are computationally heavy as they involve multiple Multiply–Accumulate Operations (MACs) for each connected node.

**Dropout:** Dropout is similar to dense, but will randomly "drop" a neuron, i.e. remove the neuron from the computation. Random neuron removals force the neural network to be more versatile and robust, reducing the chance of overfitting the neural network to a particular dataset.

| Name    | Function                                                                                                                         |

|---------|----------------------------------------------------------------------------------------------------------------------------------|

| Linear  | f(x) = ax                                                                                                                        |

| Step    | $f(x) = \begin{cases} 0 & \text{for } x < 0 \\ 1 & \text{for } x \ge 0 \end{cases}$ $f(x) = \frac{1}{1 + e^{-x}}$                |

| Sigmoid | $f(x) = \frac{1}{1 + e^{-x}}$                                                                                                    |

| Tanh    | $f(x) = tanh(x) = \frac{2}{1 + e^{-2x}} - 1$                                                                                     |

| ReLu    | $f(x) = tanh(x) = \frac{2}{1 + e^{-2x}} - 1$ $f(x) = \begin{cases} 0 & \text{for } x < 0 \\ x & \text{for } x \ge 0 \end{cases}$ |

Table 3.1: List of common neural network activation functions

**Convolution:** Convolution layers perform convolution functions on the input data, sliding a fixed-size window across the 2D input data matrix, similar to pooling. The fixed-size window is called a kernel and contains adjustable weight values in the matrix which are multiplied with the input data. Mathematically, a convolution produces a function expressing how one function is modified by another. Figure 3.4 shows a simple 2D-convolution. Convolutional layers excel with matrix-shaped data, such as image data [31], but as a result, are computationally intensive with a large amount of MACs.

**Batch normalisation:** Batch normalisation is the process of normalising values between layers to reduce "internal covariate shift". Internal covariate shift is a byproduct of adjusting weights during the training phase, where the input data of the next layer is affected to the prior layer, causing a varying offset during training. Batch normalisation deals with this by always normalising values before the next layer's input, resulting in increased learning rate and reducing the number of learning steps required [32].

Figure 3.4: Simple 2D-convolution of a 3x3 matrix with a 2x2 kernel producing a 2x2 output matrix

Long short-term memory: Memory cells are used as temporary storage in neural networks, and can "remember" previous input values, i.e. in a video input, it can "remember" previous frames. This memory feature makes the networks recursive, which are classified as a RNN These form the building blocks for Long Short-Term Memory (LSTM) layers. LSTM layers consist of memory cells and activation functions combined in a single block [33], along with the ability to bypass the memory cells. Their depth, or memory length, can be defined by the task and requirements. Smaller memories have less trainable parameters and require less storage. LSTMs layers are one of the main components of recurrent neural networks.

Figure 3.5: An LSTM layer for three discrete time steps [34]

Figure 3.5 shows an unrolled LSTM layer with three states. The key to the LSTM layer functionality is the top line shown in the figure, the cell state. It functions similarly to a conveyor belt, where each stage has the ability to modify the cell data passing through the stage. Whether to adjust or not is decided by the activation layers, illustrated as the four square boxes with sigmoid and tanh activation functions. These four activation layers are the trainable parameters of the LSTM block. These activation functions are based on the input data, X, which is multiplied with the cell state after the cell state has passed a static tanh activation function. The output, h, is passed to the next time the LSTM layer is called. The depth of the LSTM layer decides how many of the previous cell state and output values are kept in memory and used for the calculation of h.

LSTM layers can have an additional bidirectional property, allowing for future and past values to be used in computations [35]. This differs from traditional RNN and LSTM layers as they require future values to be delayed, shown in figure 3.6 comparing an RNN and a BRNN.

Figure 3.6: Comparison of a RNN and BRNN layer functionality [36]. In an LSTM network, the LSTM layers are used for the squared circles of the figure

#### 3.1.1.2 Training

Neural network training can be performed in several ways but is generally performed by loading testing data, which has been manually classified, into the network and verifying the output. The prediction error is measured using a cost function, and the goal of training is to find the global minimum for this function. This is performed by tuning the weights of the network until this value is reached, or is as low as achievable. All weights in a layer can be expressed as a gradient, and the optimisation algorithms focus on tuning the values of the gradients for each layer to reduce loss. Gradient tuning can be done using several optimisation algorithms, such as gradient descent. Gradient descent is an optimisation algorithm which attempts to find the local minimum by finding the steepest descent for a function using backpropagation. Backpropagation is an algorithm which steps backwards through the different layers and gradients of the network. One cycle of sample input and weight adjustment is called an "epoch".

During training, callback functions can be used to perform specific actions after the end of an epoch. In theory, any function can be called, but these functions are usually reserved for training functions, such as:

- Model Checkpointer Saves the neural network configuration with weights when a specified training metric improves.

- CSV Logger Saves epoch results to a .csv-file.

- Early Stopping Stops the training process if the specified training metric, such as validation accuracy, fails to improve for a specified number of epochs.

- Learning rate adjustment Adjusts the learning rate if the specified training metric fails to improve for a specified number of epochs.

- Terminate on NaN Terminates the training if the loss of the network is calculated to be NaN. Usually indicates an error in the training data.

Using callback functions helps reduce unnecessary time spent training, though some should be used with caution. Terminating training too early, due to a strict early

stopper, can result in a sub-par neural network as it is based on a local minimum.

Training a neural network is a resource intensive process, both in data and computational power. To properly train a neural network, training-, testing- and validation data is required, usually combined in a dataset. First, the dataset has to be related to the desired output of the data. To achieve good classification accuracy across different classification scenarios, the dataset has to be diverse and plentiful. Though the size of the dataset depends on the problem, research indicates that a data set of over 500 samples per class [37] is sufficient for some classification tasks, while others recommend datasets of 10 to 50 times the amount of weights in the network [38].

After finding or creating a varied and large dataset, the network can be trained. Training requires the calculation and adjustment of up to several million weights. Also, the dataset and the number of epochs required to achieve optimal loss can be high, leading to long training times. Therefore, training is often accelerated on GPUs, either locally or on servers.

#### 3.1.1.3 Verification

To verify a trained neural network, verification data is loaded into the network, and the outputs analysed. The verification data is usually unused data from the dataset, split before the network training. The split-ratio can vary, but a common ratio is 60/30/10 for training, validation and verification, respectively. The output of the network is compared with the reference, and the results can be analysed in several ways, such as overall accuracy, precision and recall.

Overall accuracy is the most straightforward metric, illustrating how many of the predictions were correct. Overall accuracy, though, can be an inaccurate metric as many predictions might be to "large" labels, such as "unknown" words. Precision and recall is a more detailed metric, illustrating two similar aspects. Precision represents, for a given class, how many of the predicted labels for that category were correct, while recall represents, for a given label, how many of the possible labels were predicted. E.g., if class A was predicted 20 times out of a possible 40 times, but label A was used 80 times, class A would have a precision of 0.5 and a recall of 0.25. For multiclass predictions, such as the Kaggle challenge, the precision and recall of a model can be

found by calculating the average of the precision and recall for the individual words.

Precision and recall requires the definition of four classification categories: True positive, false positive, false negative and true negative. These can be explained using the following analogies: True positive, a pregnant woman is diagnosed as pregnant; false positive, a non-pregnant woman is diagnosed as pregnant; false negative, a pregnant woman is diagnosed as not pregnant; and true negative, a non-pregnant woman is diagnosed as not pregnant. These four categories are used to calculate precision based on equations 3.1 and 3.2.

$$Precision = \frac{tp}{tp + fp} \tag{3.1}$$

$$Recall = \frac{tp}{tp + fn} \tag{3.2}$$

Both of these metrics can be used to help increase the robustness of the network by serving as reference metrics when performing adjustments to the network, or when performing post-processing such as thresholding and weighting. By setting a threshold for prediction values, false positives can be reduced when the prediction value is low. Weighting can be performed on the prediction values to compensate for the uncertainty in the model's predictions.

## 3.1.2 Topologies

Though several topologies exist, the most common are Convolutional Neural Network (CNN) and Recurrent Neural Network (RNN).

#### 3.1.2.1 Convolutional Neural Networks

Convolutional Neural Networks (CNNs) mainly feature convolutional layers to perform classification and other machine learning tasks. As convolution layers work well with 2D-matrices, CNNs are commonly deployed for image and video recognition purposes; however they can serve as the basis for small and effective networks [39], CNNs usually have thousands to millions of parameters [40], making them susceptible to long training

times and high memory usage. Still, CNNs are the standard for image recognition, forming the backbone for popular neural network designs such as SqueezeNet [39] and YoloNet [41].

#### 3.1.2.2 Recurrent Neural Networks

Recurrent Neural Networks (RNNs) are an alternative to CNNs, and instead of primarily using convolution layers, utilise memory cell layers, often in the form of an LSTM layer, to remember and sequence input data. The memory property enables the network to remember input sequential patterns, making it ideal for speech recognition, while having relatively few parameters [42] and of smaller sizes.

## 3.1.3 Neural network optimisations

After training, a neural network often has redundant layers and neurons which can be optimised away. Also, networks are often trained using floating point data types for weights and activations, which can be optimised to fixed-point representation. Together, these optimisations can reduce the size of the network and computational power required to run the network. These optimisations can be divided into two categories: Pruning and quantization. These functions are often run during the inference, the process of tuning and optimising the network to run on a target device, such as a phone or an edge device.

#### 3.1.3.1 **Pruning**

Pruning is the process of removing unnecessary layers, neurons and connections between them to reduce network size and computational demand. The removal process can be done by using pruning algorithms which search through the network, removing unnecessary parts and connections [43]. Pruning might come with the cost of reduced network accuracy, but this is of negligible and in some cases none [44].

#### 3.1.3.2 Quantisation

Quantisation converts weights and activation values from floating-point or fixed-point notations to smaller fixed-point notations and even binary values. Mathematical functions on computers and in processors are performed faster when the data width is decreased. Quantisation, therefore, reduces the computations required to calculate the output of a neural network.

#### 3.1.3.3 Inference

Inference combines pruning and quantisation to optimise the network for deployment on a target device such as a phone or an edge device. The inference process can be done manually but is often performed using a neural network acceleration framework such as Intel OpenVINO.

# 3.2 High level synthesis

High-level Synthesis (HLS) is the term used to describe the process of converting and compiling high-level language code, such as C++ or SystemC, to Hardware Description Languages (HDLs) such as VHDL and Verilog. One of the main goals of HLS is to accelerate product development, allowing complex functions to be written and tested in C before being synthesised to HDL. HDL-programming has traditionally required specialised skill as the fundamentals are different from traditional object-oriented and functional programming. One of these fundamental differences is that HDL is a descriptive language, as the code is synthesised into logic gates and functions. Formal programming languages, on the other hand, are compiled into instructions for execution on a processor. In addition, HDL is executed in parallel on an FPGA while formal programming languages are sequential, though parallelisation is possible through the use of multi-core processors.

While HLS has been a concept for several decades [45], it has recently progressed to the point of being adopted and used in industry and academia [46], with languages such as SystemC and HLS-tools like Vivado HLS being popular choices.

# 3.3 Speech recognition

Speech recognition is usually performed on computers by sampling and converting a speech symbol from acoustic waves into uncompressed data, such as Pulse-Code Modulated (PCM) data, and then analysed in a neural network. Though raw PCM data can be used [47], the data is often processed in some form, such as filtering and Fourier-transformation, to reduce noise and extract the most relevant information.

## 3.3.1 Speech recognition fundamentals

Speech recognition is based on the analysis of speech signals, attempting to convert audio to text for further use in a computer program or system. It can be described as oral communication; the use of vowel and consonant sounds to generate words. As such, words, and the speech recognition used to detect them can be split into individual sounds. These individual sounds are called "phonemes", and one goal of speech recognition is to recognise the individual phonemes in a recorded phrase and assemble these into a word. This method, however, has proven challenging to utilise as phonemes can be hard to differentiate. The most common method is to divide the speech signal into smaller frames for analysis, mapping the analysed frames to vectors and inputting them into a neural network or an HMM.

### 3.3.2 Hidden Markov Models

A Hidden Markov Model (HMM) is a statistical system used to model sequences such as speech and handwriting by modelling them as hidden states connected by weighted connections. The weights describe the probability of the next member of the sequence. Figure 3.7 shows an example HMM for activities based on the current weather. HMMs were the standard for speech recognition until neural networks were adopted for the same purpose, though both have been used in combination to perform speech recognition [48].

Figure 3.7: HMM showing the probability of different activities occurring based on the current weather [49]

# 3.4 Speech pre-processing

The speech signal is processed to reduce noise, remove unnecessary information and filter it for analysis. Pre-processing can be performed in several ways, but the most common method is to frame the signal into smaller frames, perform DFT and possibly calculate MFCC values.

### 3.4.1 Fast Fourier Transform