Viljar Fjellanger

# On-line Voltage Estimation during Sensorless Control of an Induction Machine Drive

Master's thesis in Electric Power Engineering Supervisor: Roy Nilsen June 2019

Master's thesis

NTNU Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

Viljar Fjellanger

# On-line Voltage Estimation during Sensorless Control of an Induction Machine Drive

Master's thesis in Electric Power Engineering Supervisor: Roy Nilsen June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Electric Power Engineering

# **Problem Description**

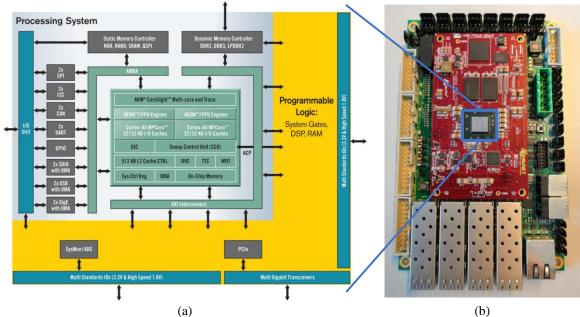

In the research group Power Electronics System and Components (PESC) at the department of Electric Power Engineering a new Control-platform is developed. This control platform is based on a picoZed - board with a Xilinx Zynq7030 System-on-Chip (SoC) with two floating point processors and a Field Programmable Gate Array (FPGA). The tools used are Vivado for FPGA programming, System Generator and Simulink for developing IP-cores for the FPGA and finally SDK for C++ programming.

One of the applications of this Control-platform is Sensorless control of Electric Machines. This thesis shall be focused on a 3-phase Induction Motor drive. The tasks to be performed are:

- Derive mathematical models and present the control theory for Induction Motor Drives.

- Discuss the most commonly used flux models: Current Model and Voltage Model.

- Evaluate the sources of error in these models; especially voltage errors.

- Present the theory for the effect on dead-times and blanking times on in the pulse pattern in a 2-level 3-phase inverter.

- Develop a voltage-estimator to be used in a flux model. The estimator should be implemented in the FPGA by help of Simulink and the System Generator package from Xilinx.

- Methods and Workflow for how to test this in Simulink and on the Control Platform should be presented if sufficient time is available.

Supervisor: Prof. Roy Nilsen

## Preface

This thesis was submitted to the Department of Electric Power Engineering at NTNU and concludes the 2-year master program "Electric Power Engineering". The work has been challenging and motivating and really widened my horizon in the exiting world of programming. I am very grateful for the new acquired knowledge.

I want to thank my supervisor Prof. Roy Nilsen for all his guidance throughout the project. His theoretical knowledge, constructive feedback and passion for the field of study has been very valuable during this work. I would also give a special thanks to PhD candidate Anirudh Budnar Acharya for sharing his knowledge in FPGA programming and his invaluable assistance with the FPGA design. Lastly, I want to thank the participants in the PESC group for all the interesting and fruitful discussions.

Trondheim, June 11, 2019

iljor Jjellanger

Viljar Fjellanger

# Abstract

Sensorless control of electrical machines can increase reliability and reduce cost of high-performance drives. The sensorless control can be achieved by using *field-oriented control*, where voltage and current measurement are used as inputs to a flux model called *voltage model*. However, it is well known that errors in input variables, such as stator voltage, can lead to *drifting* in the flux linkage estimation. It is possible to give an estimate of the stator voltage using control signal for the inverter's IGBTs and correcting for turn-on and turn-off delays of the IGBTs and blanking time.

The main purpose of this thesis was to design and test an on-line voltage estimator using Xilinx's System Generator DSP tool together with Xilinx SDK. The voltage estimator was tested using an open loop V/f-controller with the future goal of implementing it in a field-oriented control. Tests were performed purely on the control board without a physical inverter connected. Test results were compared to simulations and the expected results deducted in the theoretical study. Modelling, scaling and control strategies of the induction machine was thoroughly reviewed with updated concepts and notations and a non-ideal inverter model was presented and analysed in order to design the voltage estimator.

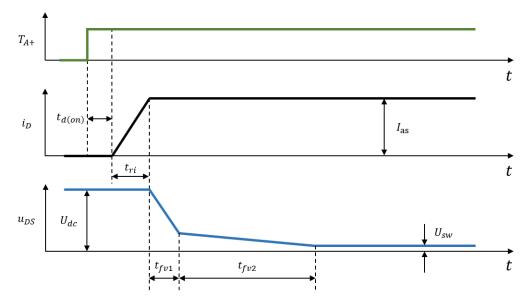

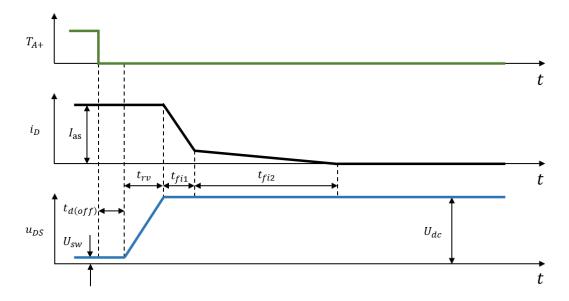

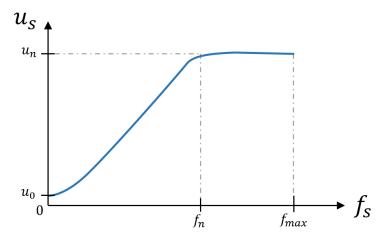

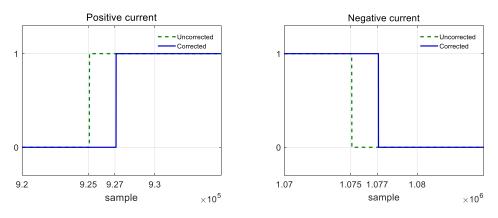

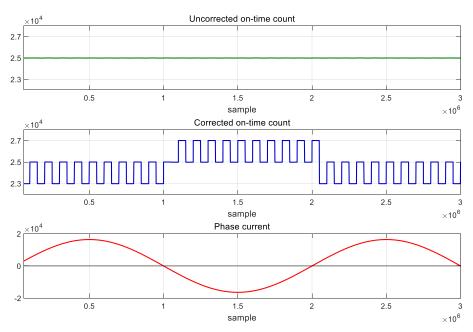

The voltage estimator used the CPU for mathematical computations and the FPGA to estimate the time period to which the inverter outputs had same voltage potential as DC-link voltage. Theoretical analysis showed that blanking time and difference in turn-on and turn-off time in the IGBTs introduced a time delay to the output voltage pulse, compared to control signal of the IGBT. It was also shown that the time delay was dependent on current direction. The voltage estimator's ability to introduce this time delay was initially tested. The test was performed by using one bridge leg as a half-bridge converter and monitoring the on-time counter value. Results from tests with a constant control voltage and a switch in current direction, showed correct time delays in on-time estimation.

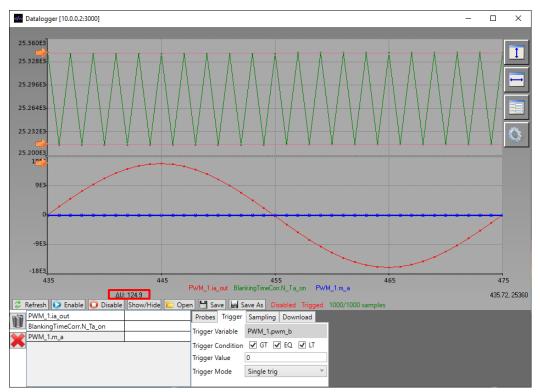

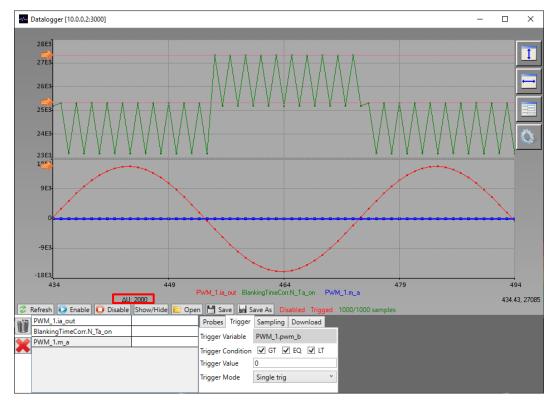

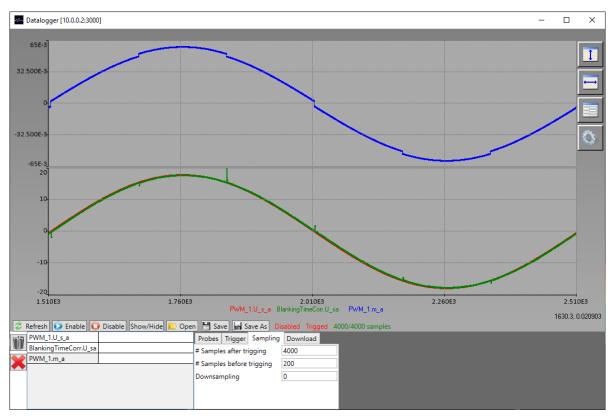

Phase voltage estimation was tested during low speed V/f-control. The test was performed with and without blanking time. Results without blanking time showed an estimated phase voltage equal to the control voltage and test with blanking time showed estimation of a distorted output voltage. The distorted waveform of estimated output voltage was in accordance with the theoretical analysis.

An expression for the non-linear voltage drop imposed by the inverter was deducted in the non-ideal inverter model. The expression was used to create a correction to the control voltage with the intention to remove the distortion of output voltage. The estimator was tested similarly as for the initial phase-voltage test. The result showed an estimated output voltage equal to the sinusoidal reference voltage from the controller. From this it could be verified that the non-linear voltage drop equation given by the inverter model was correct. Furthermore, similarities between results from the compensated V/f-control and the expected results from a FOC, showed that the estimator could work independently of control strategy.

From the results it was concluded that the new IP-core that was integrated in the FPGA design was able to recognise current direction and insert the correct time delay to the on-time count. It was also concluded that voltage estimator was able to estimate correct output voltage, independent of control strategy. This verified the equations for output voltage and distorted voltage deducted in non-ideal inverter model.

Finally, Xilinx System Generator DPS tool was proven to an efficient way of programming complex FPGA programs. The tool allowed for design, testing and implementation of new IP-cores without knowledge of VHDL programming.

## Sammendrag

Sensorløs kontroll av elektriske maskiner kan bidra til økt pålitelighet samt kostnadsreduksjon på motordrifter med krav til høy-presisjon. Kontrollstrategien *feltorientert kontroll* kan brukes for å oppnå sensorløs kontroll ved at strøm- og spenningsmålinger brukes i en fluksmodell som kalles *spennings-modellen*. Det er videre et kjent problem at unøyaktige inputvariabler i spenningsmodellen, som for eksempel spenningsmålinger, kan føre til feil i fluksestimeringen. I litteraturen kalles denne feilen for *drifting*. Det er mulig å estimere statorspenningen ved hjelp av styresignalene til IGBTene i omformeren. Ved slik estimering er det viktig å korrigere for tidsforsinkelser i forbindelse med svitsjeforløpet til IGBTene samt dødtid i omformeren.

Hovedformålet med oppgaven har vært design og testing av en on-line spenningsestimator. Estimatoren er designet ved hjelp programmene System Generator DSP og SDK, begge utviklet og laget av Xilinx. Spenningsestimatoren er testet ved hjelp av en åpen sløyfe V/f-kontroller med et framtidig mål om å implementere den i en feltorientert kontroller. Testene i denne masteroppgaven ble gjort på et kontrollbrett uten tilkobling til en fysisk omformer. Resultatene ble sammenlignet med simuleringer og sett i sammenheng med de forventede resultatene fra teoristudiet. Modellering, skalering og kontrollstrategier for induksjonsmaskinen ble nøye gjennomgått. Likningene ble presentert med oppdatert notasjon i henhold til motordrift faget på fakultetet. En ikke-ideell omformermodell ble også presentert og analysert for å forstå hvordan spenningsestimatoren skulle designes.

Matematiske beregninger til estimatoren ble gjort i prosessoren mens estimatet av tidsintervallet, hvor spenningen på omformerens utgangsterminaler var lik DC-spenningen, ble gjort i FPGAen. Analysen av omformeren viste at differansen i av og på forsinkelsen i IGBTene samt dødtiden, introduserte en tidsforsinkelse i spenningspulsen fra omformeren i forhold til kontrollsignalet til IGBTen. Det ble også vist at tidsforsinkelsen var avhengig av strømretningen i brogrenen. For å teste FPGA-programmets evne til å estimere riktig tidsintervall, ble den ene brogrenen brukt som en halvbro-omformer og påtrykt en konstant kontrollspenning. Strømretningen ble også endret under testen. Testresultatene viste at estimatoren var i stand til å gi korrekte resultater.

Fasespenningsestimat ble testet ved bruk av en V/f-kontroller innstilt for lav utgangshastighet. Testen ble gjennomført med og uten dødtid. Resultatet fra testen uten dødtid vise et fasespenningsestimat likt kontrollspenningen. Resultatet med dødtid viste en forvrenging i den estimerte utgangsspenningen, helt i samsvar med teoristudiet.

Et utrykk for det ulineære spenningsfallet fra omformeren ble utledet i den ikke-ideelle omformermodellen. Uttrykket ble brukt til å korrigere kontrollspenningen med mål om fjerne det ulineære spenningsfallet. Testresultatene viste at den estimerte utgangsspenningen hadde samme fase og amplitude som den sinusformede referansespenningen fra omformeren. Resultatet viste at det utledede utrykket som beskriver spenningsfallet var korrekt. Resultatene fra testen var også lik det man kunne forventet seg ved bruk av feltorientert kontroll. Dette viste at estimator ikke var begrenset til en kontrollstrategi.

Fra resultatene konkluderes det at den nye IP-kjernen som ble integrert i det ferdige FPGA-designet, evnet å estimere riktig tidsintervall for utgangsspenningen. Det ble også konkludert at spenningsestimatoren klarte å estimere riktig utgangsspenning i de forskjellige testene og at estimering var uavhengig av kontrollstrategien. Dette ga grunnlaget for verifisering av likningene som ble funnet i den ikke-ideelle omformermodellen.

Xilinx System Generator DPS-verktøy har vist seg å være en svært effektiv måte å programmere komplekse FPGA-programmer på. Verktøyet muliggjorde design, testing og implementering av en ny IP-kjerne uten inngående kunnskap om VHDL programmering.

# Table of Content

|   | LIST OF FIGURESVI   |                                                           |        |

|---|---------------------|-----------------------------------------------------------|--------|

|   | LIST OF CODE        |                                                           | VII    |

|   | ACRONY              | MS                                                        | . VIII |

|   | Νοτατις             | NS                                                        | IX     |

| 1 | INTR                | ODUCTION                                                  | 1      |

|   | 1.1                 | BACKGROUND AND MOTIVATION                                 | 1      |

|   | 1.2                 | SCOPE OF WORK                                             | 2      |

|   | 1.3                 | ORGANIZATION OF THE REPORT                                | 2      |

| 2 | мо                  | DELLING AND SCALING OF THE INDUCTION MACHINE              | 3      |

|   | 2.1                 | INTRODUCTION TO THE IM MACHINE                            | 3      |

|   | 2.2                 | MODELLING OF THE INDUCTION MACHINE                        |        |

|   | 2.2.1               |                                                           |        |

|   | 2.2.2               | ,                                                         |        |

|   | 2.2.3               | •                                                         |        |

|   | 2.3                 | PU SYSTEM                                                 |        |

| 3 | CON                 | TROL OF THE INDUCTION MACHINE                             |        |

| 5 | 3.1                 | V/f-Control                                               |        |

|   | 3.1<br>3.2          | ROTOR-FLUX ORIENTATED CONTROL                             |        |

|   | 3.2<br>3.2.1        |                                                           |        |

|   | 3.2.1               |                                                           |        |

|   | 3.2.3               | -                                                         |        |

|   | 3.3                 | Drifting in Voltage Model                                 |        |

| 4 |                     | TAGE AND CURRENT MEASUREMENT                              |        |

| • |                     |                                                           |        |

|   | 4.1                 | Non-ideal Inverter Model                                  |        |

|   | 4.1.1               | 5                                                         |        |

|   | 4.1.2               | 5 , - , 5                                                 |        |

|   | 4.1.3               |                                                           |        |

|   | <i>4.1.4</i><br>4.2 | Consequences of the Non-Linear voltage drop               |        |

|   | 4.2<br>4.3          | CURRENT MEASUREMENT                                       | -      |

|   | -                   |                                                           | . 33   |

|   | 4.3.2               |                                                           |        |

|   | 4.3.3               |                                                           |        |

| 5 |                     | GRAMMING STRUCTURE AND SOFTWARE                           |        |

| 5 |                     |                                                           |        |

|   | 5.1                 |                                                           |        |

|   | 5.2                 | PROGRAMMING STRUCTURE IN SDK                              |        |

|   | 5.3                 | IP-CORE GENERATION USING SYSTEM GENERATOR DSP IN SIMULINK |        |

| 6 | CPU                 | AND FPGA PROGRAMMING                                      |        |

|   | 6.1                 |                                                           | -      |

|   | 6.2                 | V/f-Control (Controller)                                  |        |

|   | 6.3                 | PWM (Modulator)                                           |        |

|   | 6.4                 | VOLTAGE ESTIMATION WITH BLANKING TIME CORRECTION          |        |

|   | 6.5                 | DISTORTION VOLTAGE CORRECTION                             | . 61   |

| 7  | PRO                           | GRAM VERIFICATION THROUGH SIMULATION AND TESTING | 62 |

|----|-------------------------------|--------------------------------------------------|----|

|    | 7.1                           | INTRODUCTION                                     | 62 |

|    | 7.2                           | DC-VOLTAGE TEST                                  | 63 |

|    | 7.3                           | AC-VOLTAGE TEST                                  |    |

|    | 7.4                           | AC-VOLTAGE TEST WITH CORRECTION                  |    |

| 8  | 8 DISCUSSION                  |                                                  | 72 |

| 9  | 9 CONCLUSION AND FURTHER WORK |                                                  | 75 |

|    | 9.1                           | CONCLUSION                                       |    |

|    | 9.2                           | Further Work                                     | 76 |

| RI | REFERENCES                    |                                                  |    |

# List of figures

| FIGURE 2.1: PRINCIPLE DRAWING OF THE THREE-PHASE INDUCTION MACHINE                                               | 3     |

|------------------------------------------------------------------------------------------------------------------|-------|

| FIGURE 2.2: SCHEMATIC REPRESENTATION OF THE THREE-PHASE INDUCTION MACHINE                                        | 4     |

| FIGURE 2.3: THREE-PHASE INDUCTION MACHINE                                                                        | 6     |

| FIGURE 2.4: EQUIVALENT TWO-PHASE INDUCTION MACHINE                                                               | 6     |

| FIGURE 2.5: CLARKE TRANSFORMED MODEL                                                                             | 8     |

| Figure 2.6:Park transformed model                                                                                | 8     |

| Figure 3.1: $V/f$ curve without voltage boost                                                                    | 14    |

| FIGURE 3.2: TORQUE/SPEED CURVE WITHOUT VOLTAGE BOOST                                                             |       |

| Figure 3.3: $V/f$ curve with voltage boost                                                                       |       |

| FIGURE 3.4: TORQUE/SPEED CURVE WITH VOLTAGE BOOST                                                                |       |

| FIGURE 3.5: VECTOR DIAGRAM FOR USED IN VOLTAGE MODEL                                                             |       |

| FIGURE 3.6: DRIFTING OF STATOR FLUX                                                                              |       |

| Figure 4.1: Inverter circuit                                                                                     |       |

| FIGURE 4.2: TURN-ON VOLTAGE AND CURRENT WAVEFORM                                                                 |       |

| Figure 4.3: Turn-off voltage and current waveform                                                                |       |

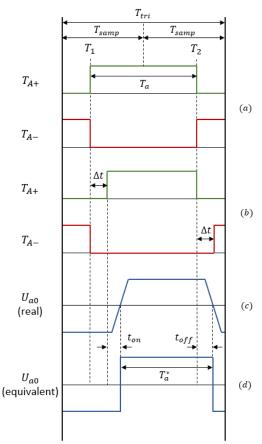

| Figure 4.4: Switching patterns for a two level three-phase inverter with current flowing to the load. (A) Ideal  | . – . |

| switching. (b) Switching this blanking time. (c) Actual phase to 0 voltage. (d) equivalent phase to 0 voltage    | 25    |

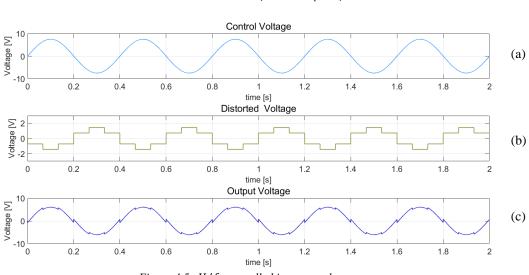

| Figure 4.5: $V/f$ -controlled inverter voltages                                                                  |       |

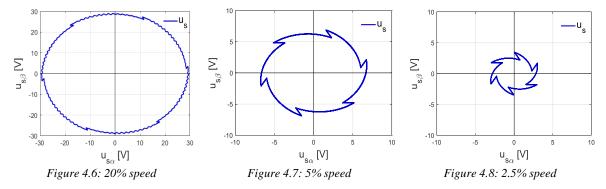

| Figure 4.6: 20% speed                                                                                            |       |

| Figure 4.7: 5% speed                                                                                             |       |

| Figure 4.8: 2.5% speed                                                                                           |       |

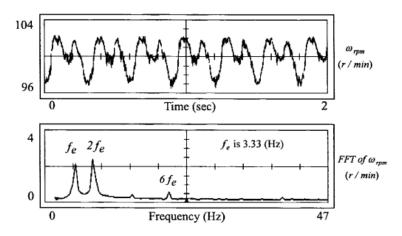

| FIGURE 4.9: MECHANICAL SPEED AND FFT ANALYSIS OF MECHANICAL SPEED WITH MEASUREMENT ERRORS [18].                  |       |

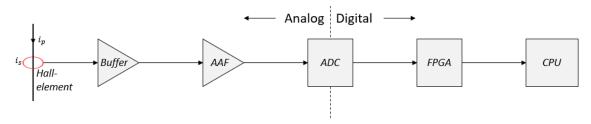

| FIGURE 4.10: CURRENT MEASUREMENT CIRCUIT                                                                         |       |

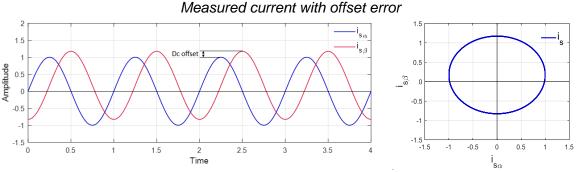

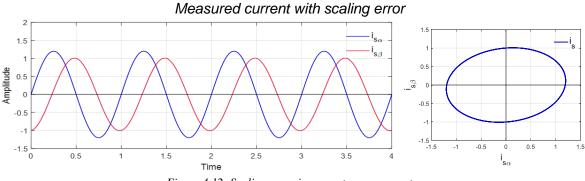

| Figure 4.11: Offset error in current measurement                                                                 |       |

| Figure 4.12: Scaling error in current measurement                                                                |       |

| FIGURE 5.1: (A) SCHEMATIC REPRESENTATION OF THE ZYNQ-PROCESSOR [26]. (B) PHOTO OF THE CONTROL BOARDS.            |       |

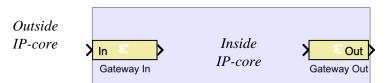

| FIGURE 5.2: INPUT AND OUTPUT GATES                                                                               |       |

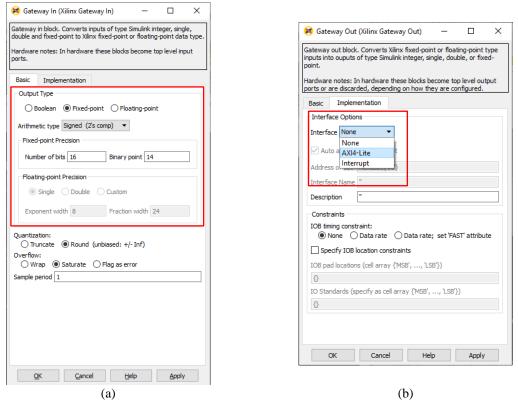

| FIGURE 5.3: BLOCK SPECIFICATION FOR GATEWAY PORTS                                                                |       |

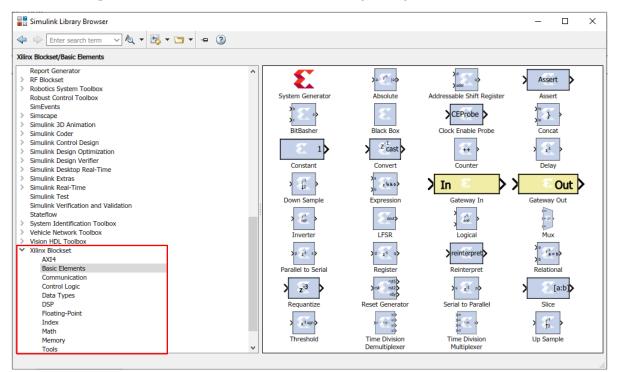

| FIGURE 5.4: BASIC BLOCK LIBRARY FOR THE XILINX TOOL                                                              |       |

| FIGURE 5.4. DASIC BLOCK LIBRART FOR THE AILINA TOOL                                                              |       |

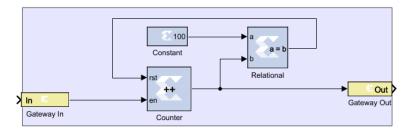

| FIGURE 5.6: SIMULATION OF COUNTER                                                                                |       |

| FIGURE 5.0: SIMULATION OF COUNTER                                                                                |       |

| FIGURE 5.7: SCOPE OUTPUT                                                                                         |       |

| FIGURE 5.8: SYSTEM GENERATOR SETUP<br>FIGURE 5.9: (A) COUNTER EXAMPLE IN SIMULINK. (B) COUNTER EXAMPLE IN VIVADO |       |

|                                                                                                                  |       |

| FIGURE 5.10: LINK BETWEEN HARDWARE PLATFORM, BSP AND PROJECT                                                     |       |

| FIGURE 6.1: OBJECTS AND ELEMENTS IN THE CONTROL SOFTWARE                                                         |       |

| FIGURE 6.2: $V/f$ -CURVE                                                                                         |       |

| FIGURE 6.3: SWITCHING BEHAVIOUR WITH BLANKING TIME, POSITIVE CURRENT                                             |       |

| FIGURE 6.4: SWITCHING BEHAVIOUR WITH BLANKING TIME, NEGATIVE CURRENT                                             |       |

| FIGURE 6.5: BLANKING TIME COMPENSATOR                                                                            |       |

| FIGURE 6.6: RISING AND FALLING EDGE DETECTOR                                                                     |       |

| FIGURE 6.7: SIGN OF CURRENT                                                                                      |       |

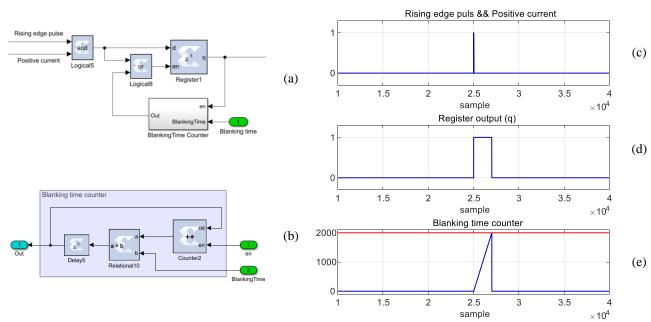

| FIGURE 6.8:BLANKING TIME COUNTER                                                                                 |       |

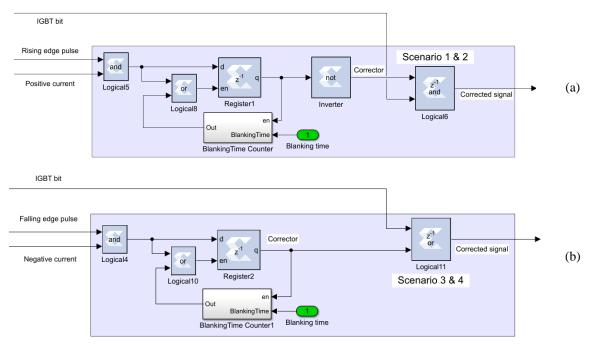

| FIGURE 6.9: BLANKING TIME CORRECTION OF IGBT BIT. (A) POSITIVE CURRENT. (B) NEGATIVE CURRENT.                    |       |

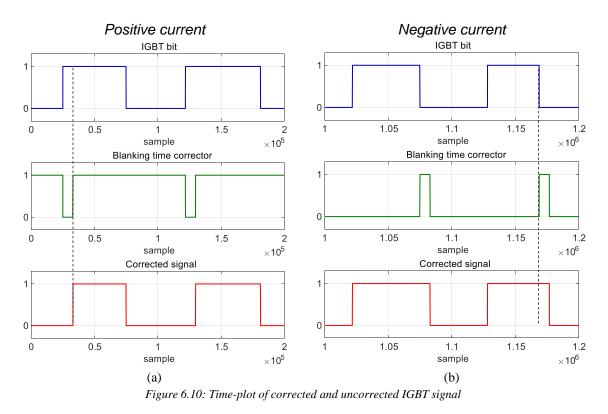

| FIGURE 6.10: TIME-PLOT OF CORRECTED AND UNCORRECTED IGBT SIGNAL                                                  |       |

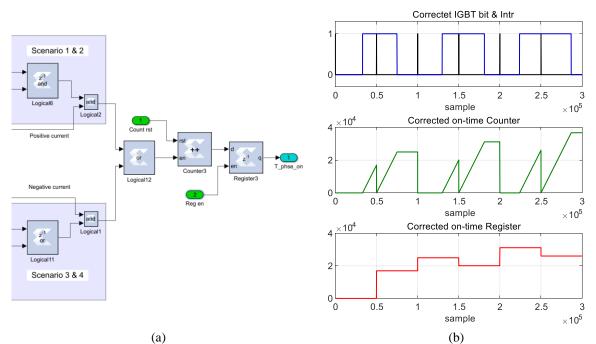

| FIGURE 6.11: (A) COUNTER AND REGISTER LOGIC. (B) CORRECTED SIGNAL, ON-TIME COUNTER AND ON-TIME REGISTER          |       |

| FIGURE 6.12: COMPLETE BLOCK DESIGN OF THE BLANKING TIME CORRECTOR IP-CORE                                        |       |

| FIGURE 6.13: SEQUENCER BLOCK                                                                                     |       |

| FIGURE 7.1: PWM MODEL                                                                                            |       |

| FIGURE 7.2: ILLUSTRATION OF CORRECTED AND UNCORRECTED IGBT BIT                                                   |       |

| FIGURE 7.3: CLOSE-UP PICTURE OF TURN-ON AND TURN-OFF DELAY IMPOSED BY BLANKING TIME                              | 64    |

| FIGURE 7.4: SIMULATION - ON-TIME COUNT FOR DC-TEST WITH AND WITHOUT BLANKING TIME | 64 |

|-----------------------------------------------------------------------------------|----|

| FIGURE 7.5:CONTROL BOARD - ON-TIME COUNT FOR DC-TEST WITHOUT BLANKING TIME        | 65 |

| FIGURE 7.6 CONTROL BOARD - ON-TIME COUNT FOR DC-TEST WITH BLANKING TIME           | 66 |

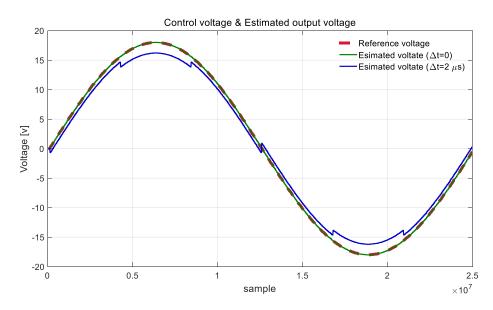

| FIGURE 7.7: SIMULATION – VOLTAGE ESTIMATION WITH AND WITHOUT BLANKING TIME        | 67 |

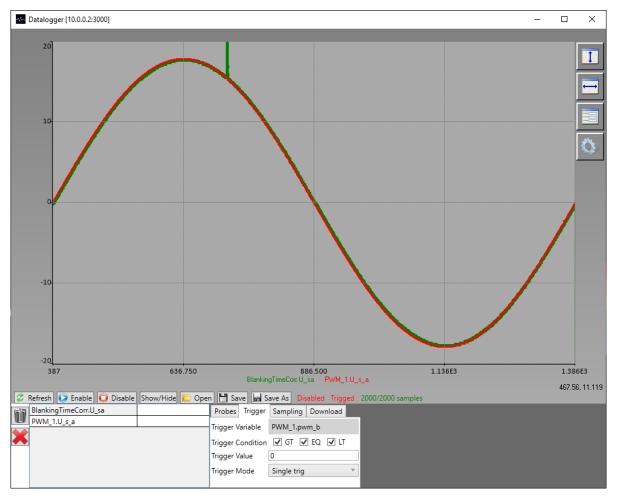

| FIGURE 7.8: CONTROL BOARD – VOLTAGE ESTIMATION WITHOUT BLANKING TIME              | 68 |

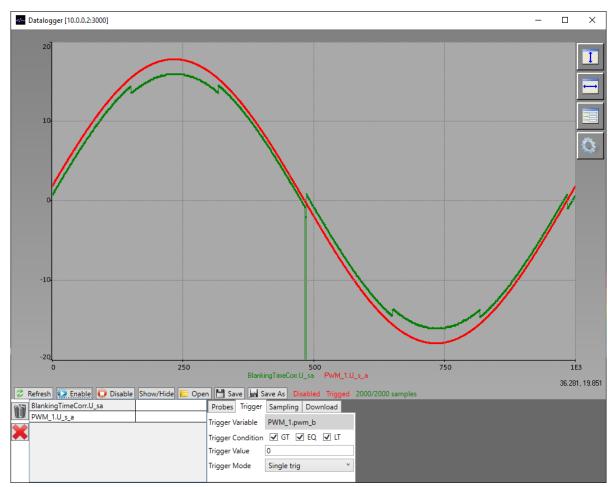

| FIGURE 7.9: CONTROL BOARD – VOLTAGE ESTIMATION WITH BLANKING TIME                 | 69 |

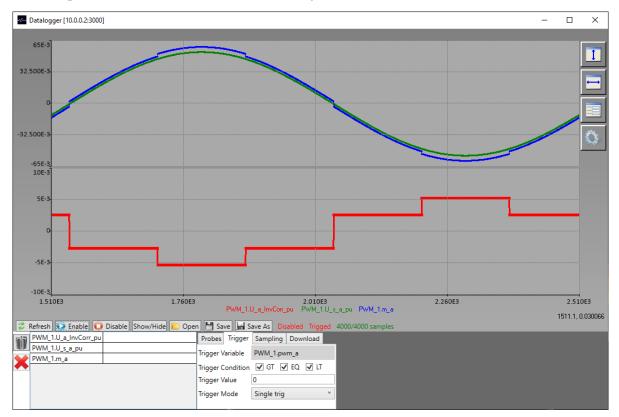

| FIGURE 7.10: CONTROL BOARD – CONTROL VOLTAGE COMPENSATION                         | 70 |

| FIGURE 7.11: CONTROL BOARD – VOLTAGE ESTIMATION WITH COMPENSATED CONTROL VOLTAGE  | 71 |

## List of code

| CODE 5.2: DRIVEROUTINEFAST.CPP41CODE 5.3: EXAMPLECLASS.HPP42CODE 5.4: EXAMPLECLASS.CPP42CODE 5.5: INITIALIZATION OF A NEW IP-CORE47CODE 5.6: READING AND WRITING TO AND FROM THE IP-CORE48CODE 6.1: SCALAR CONTROL INITIALIZATION CODE50CODE 6.2: SCALAR CONTROL RUN CODE51CODE 6.3: PWM RUN CODE52CODE 6.4: VOLTAGEESTIMATOR CODE60CODE 6.5: DISTORTEDVOLTAGECORRETION CODE61 | CODE 5.1: MAIN.CC                                     | 40 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----|

| CODE 5.4: EXAMPLECLASS.CPP42CODE 5.5: INITIALIZATION OF A NEW IP-CORE47CODE 5.6: READING AND WRITING TO AND FROM THE IP-CORE48CODE 6.1: SCALAR CONTROL INITIALIZATION CODE50CODE 6.2: SCALAR CONTROL RUN CODE51CODE 6.3: PWM RUN CODE52CODE 6.4: VOLTAGEESTIMATOR CODE60                                                                                                       | CODE 5.2: DRIVEROUTINEFAST.CPP                        |    |

| CODE 5.5: INITIALIZATION OF A NEW IP-CORE47CODE 5.6: READING AND WRITING TO AND FROM THE IP-CORE48CODE 6.1: SCALAR CONTROL INITIALIZATION CODE50CODE 6.2: SCALAR CONTROL RUN CODE51CODE 6.3: PWM RUN CODE52CODE 6.4: VOLTAGEESTIMATOR CODE60                                                                                                                                   | CODE 5.3: EXAMPLECLASS.HPP                            | 42 |

| CODE 5.6: READING AND WRITING TO AND FROM THE IP-CORE       48         CODE 6.1: SCALAR CONTROL INITIALIZATION CODE       50         CODE 6.2: SCALAR CONTROL RUN CODE       51         CODE 6.3: PWM RUN CODE       52         CODE 6.4: VOLTAGEESTIMATOR CODE       60                                                                                                       | CODE 5.4: EXAMPLECLASS.CPP                            | 42 |

| CODE 6.1: SCALAR CONTROL INITIALIZATION CODE50CODE 6.2: SCALAR CONTROL RUN CODE51CODE 6.3: PWM RUN CODE52CODE 6.4: VOLTAGEESTIMATOR CODE60                                                                                                                                                                                                                                     | CODE 5.5: INITIALIZATION OF A NEW IP-CORE             | 47 |

| CODE 6.2: SCALAR CONTROL RUN CODE         51           CODE 6.3: PWM RUN CODE         52           CODE 6.4: VOLTAGEESTIMATOR CODE         60                                                                                                                                                                                                                                  | CODE 5.6: READING AND WRITING TO AND FROM THE IP-CORE | 48 |

| CODE 6.3:PWM RUN CODE                                                                                                                                                                                                                                                                                                                                                          |                                                       |    |

| CODE 6.4: VOLTAGEESTIMATOR CODE                                                                                                                                                                                                                                                                                                                                                | CODE 6.2: SCALAR CONTROL RUN CODE                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                | CODE 6.3:PWM RUN CODE                                 |    |

| CODE 6.5: DISTORTEDVOLTAGECORRETION CODE                                                                                                                                                                                                                                                                                                                                       | CODE 6.4: VOLTAGEESTIMATOR CODE                       | 60 |

|                                                                                                                                                                                                                                                                                                                                                                                | CODE 6.5: DISTORTEDVOLTAGECORRETION CODE              | 61 |

## Acronyms

| AC   | Alternating Current               |

|------|-----------------------------------|

| ADC  | Analog Digital Controller         |

| CPU  | Central Processor Unit            |

| DC   | Direct Current                    |

| DSP  | Digital Signal Processors         |

| pu   | Per unit                          |

| PWM  | Pulse Width Modulation            |

| FOC  | Field-Oriented Control            |

| SDK  | System Development Kit            |

| MMF  | Magnetomotive Force               |

| IGBT | Insulated-Gate Bipolar Transistor |

| FFT  | Fast Fourier Transform            |

| AAF  | Anti-Aliasing Filter              |

| BSP  | Board Support Package             |

|      |                                   |

## Notations

| Symbol             | Explanation                                                      |

|--------------------|------------------------------------------------------------------|

| U                  | Voltage                                                          |

| Ι                  | Current                                                          |

| R                  | Resistance                                                       |

| L                  | Inductance                                                       |

| Ψ                  | Flux linkage                                                     |

| S                  | Apparent power                                                   |

| <u>α</u>           | Alpha-axis                                                       |

| <u>β</u>           | Beta-axis                                                        |

| arphi              | Current angle                                                    |

| δ                  | Voltage angle                                                    |

| ε                  | Flux linkage angle                                               |

| <u>U</u>           | Column matrix of voltages                                        |

| <u>I</u>           | Column matrix of currents                                        |

| $\underline{\Psi}$ | Column matrix of flux linkages                                   |

| R                  | Resistance matrix                                                |

| L                  | Inductance matrix                                                |

| $R_s$              | Stator resistance                                                |

| $R_r$              | Rotor resistance                                                 |

| $L_{s\sigma}$      | Stator leakage inductance                                        |

| $L_{r\sigma}$      | Rotor leakage inductance                                         |

| $L_{sm}$           | Peak value of mutual inductance between stator windings          |

| $L_{rm}$           | Peak value of mutual inductance between rotor windings           |

| L <sub>srm</sub>   | Peak value of mutual inductance between stator and rotor winding |

| x <sub>s</sub>     | Stator reactance                                                 |

| x <sub>r</sub>     | Rotor reactance                                                  |

| $x_{\sigma}$       | Leakage reactance                                                |

| $x_{s\sigma}$      | Stator leakage reactance                                         |

| $x_{r\sigma}$      | Rotor leakage reactance                                          |

| $x_m$              | Mutual reactance                                                 |

| $x_M$              | Equivalent mutual reactance                                      |

| $T_r$              | Rotor rime constant                                              |

| n                  | Rotor speed [pu]                                                 |

| f                  | Frequency                                                        |

| ω              | Angular frequency                                 |

|----------------|---------------------------------------------------|

| θ              | Angle of rotor                                    |

| $	heta_k$      | Angle of fictitious system with respect to stator |

| $	heta_r$      | Angle of fictitious system with respect to rotor  |

| T <sub>e</sub> | Electrical torque                                 |

| τ <sub>e</sub> | Electrical torque in pu                           |

| p              | Pole pairs                                        |

| Τ              | Transformation matrix                             |

| J              | Rotation matrix used in transformation            |

Small letters indicate pu values

| Superscript | Explanation                                               |

|-------------|-----------------------------------------------------------|

| S           | Stator quantities in stator coordinates                   |

| R           | Rotor quantities in rotor coordinates                     |

| SR          | Stator and rotor quantities in their original coordinates |

| S           | Referred to stator                                        |

| r           | Referred to rotor                                         |

| k           | Referred to transformed frame                             |

| $\psi_s$    | Referred to stator flux linkage axis                      |

| $\psi_r$    | Referred to rotor flux linkage axis                       |

| ۸           | Estimated value                                           |

| *           | Actual value                                              |

| ,           | Distorted value                                           |

| <b>A</b> 1 | • 4   |

|------------|-------|

| Sinhe      | crint |

| Subs       | ιιpι  |

|            |       |

| bscript | Explanation             |

|---------|-------------------------|

| a, b, c | Phases in the machine   |

| α       | $\alpha$ -axis quantity |

| β       | $\beta$ -axis quantity  |

| S       | Stator quantity         |

| r       | Rotor quantity          |

| e       | Electrical quantity     |

| Ν       | Rated value             |

| n       | Reference value         |

| _       | Vector                  |

# 1 Introduction

### 1.1 Background and Motivation

Ever since the introduction of variable speed drives, pioneered in the late 70's, AC machines have taken over more and more of the variable speed applications previously dominated by DC machines [1]. Throughout the years, different control strategies have been developed to fulfil different needs in the market. These are typically divided into high-performance and low-performance drives. Traditionally, high-performance drives have required position measurements in the control scheme. However, during the last decades extensive research has been carried out in order to remove the dependency of position measurement, also known as sensorless control. Position sensor itself and wiring between sensor and controller represent a reliability issue, increased maintenance work, increased weight and unnecessary cost [2].

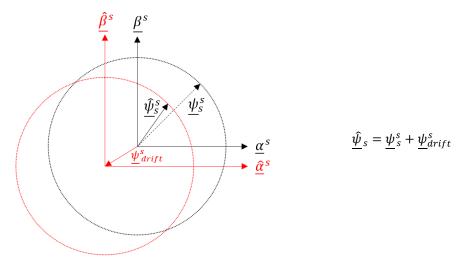

High-performance sensorless drives require estimation of rotor position. Position estimation can be achieved with the knowledge of flux linkages in the machine. This is exploited by the control strategy *field-oriented control* (FOC), where flux linkages are calculated using current and voltage measurements in the so-called *voltage model*. It is known that the open integrator used in the voltage model can cause a DC-offset in the flux linkage estimation if subjected to errors in parameter estimation or measurements. In literature, this phenomenon is referred to as *drifting* and the implications it causes has grates impact during low speed operation or slow runs through zero speed. Today it exists numerus methods, so-called observers, that tackles the challenges caused by drifting [3-5]. For several years, sensorless control has also been a field of interest at the Department of Electric Power Engineering at NTNU, where project, master and doctor theses have been written about the subject [6-9].

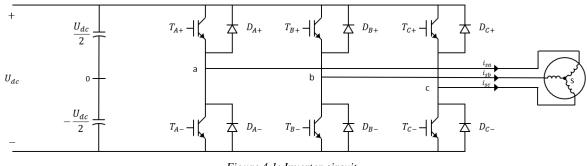

To avoid drifting it is important to apply accurate voltage and current measurements. Direct voltage measurements on inverter terminals are the most accurate, however high rise-times and high output voltage require special measuring equipment with adequate bandwidth and insulation [10]. Moreover, the analog signal processing may introduce offset errors. Expensive measuring hardware and analog signal processing can be avoided by estimating the inverter voltage output with help of the IGBTs control signal. However, semiconducting components in the inverter cause a non-linear voltage drop that has to be taken into account in order to achieve desired estimation accuracy.

To facilitate further research and development in fields like sensorless FOC, a R&D group at the department of Electrical Power Engineering has since the beginning of 2019 worked on establishing a common NTNU Control Platform. The complete drive setup uses a control board from Avnet and a process interface board developed by SINTEF Energy. The setup also uses release and monitoring tools provided by The Switch Marine Drives. The control platform will act as the foundation for future research and a starting point for master and doctor theses in the years to come.

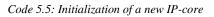

The NTNU control platform consists of a CPU routine and a complete FPGA design. The CPU routine is written in C++ and developed in Xilinx's *System Development Kit* (SDK). FPGA design is constructed out of a network of IP-core using another Xilinx program called *Vivado*. Previously, IP-cores have been written using the language VHDL and development of IP-cores has required specialist knowledge. However, in today's market there exists development tools that can make this work significantly easier and allow a broader range of electrical engineers to participate in FPGA design. This thesis will use *Xilinx System Generator DSP* together with MATLAB *Simulink* in the development of a new IP-core. The IP-core will be a part of the output voltage estimator.

### 1.2 Scope of work

This thesis focuses on modelling and control of an induction machine drive. It also focuses on implementation of an on-line voltage estimation technique for a two-level three-phase inverter. IP-core development using *Xilinx System Generator DSP* at the department of Electrical Power Engineering has previously only been done to a small extent. This thesis present and explain the tool in detail with the intention of being an example for future development.

The scope of the work includes:

- Modelling, control and scaling of the induction machine according to the concepts and notations presented in the course Electrical Drives (TET4120).

- Modelling of a two-level three-phase inverter.

- Development of an on-line voltage estimator and an open loop V/f-controller.

- Analysis of simulation and test results with the goal of validating the estimation technique.

Limitations of the work includes:

- Tests of voltage estimator are not done on a physical drive.

- Current measurements are emulated from the CPU and not form a running machine.

- FOC is not implemented in the control routine.

There are also a number of simplifications and approximations in the induction machine model, inverter model and output voltage estimator. These are explained in the receptive chapters.

### 1.3 Organization of the report

The report is divided into eight main chapters: Physical modelling of the induction machine, Clark and Park transformation and pu scaling of voltage and flux linkage equations are presented in chapter 2. Open loop V/f-control and closed loop FOC alongside with the phenomenon drifting are presented in chapter 3. A non-ideal inverter model and consequences of errors in current measurements are analysed in chapter 4. Chapter 5 introduces the programming structure for the NTNU Control Platform and gives an example of how to generate an IP-core using Xilinx's System Generator tool in MATLAB Simulink. A summary of CPU routines for the drive and voltage estimator, together with a thorough explanation of the developed IP-core, is presented in chapter 6. Chapters 7 presents simulation and control board tests. A discussion of the thesis is given in chapter 8. Finally, the conclusions and suggestion for further work are given in chapter 9.

## 2 Modelling and Scaling of the Induction Machine

### 2.1 Introduction to the IM machine.

The asynchronous machine is a type of AC machine and is the most commonly used electrical machine in the industry. This is because of its simple construction, easy maintenance, robustness and versatile area of application. The output power of the asynchronous machine can range from a few watts up towards 10 MW [11]. The operating principles of the machine are described by Faraday's law of induction and Lorentz force on the conductors in the rotor. Alternating currents in the stator windings set up a magnetic field in the machine's stator and rotor. When the alternating field crosses the rotor conductors a current is induced within the conductor, thus creating a force perpendicular to the field and current.

Asynchronous machines come with two different types of rotors, wounded and squirrel-cage rotor. Asynchronous machines with a wounded rotor, also called double fed asynchronous machines, have isolated windings in both stator and rotor. The winding has the same number of poles and phases as the stator and each phase is connected to its own isolated slipring. Additional resistance can be connected in series with the rotor winding during start-up to increase the starting torque. As the machine accelerates, the resistances are short circuited to increase the torque at higher speeds and to reduce conduction losses [12]. The other and more commonly used asynchronous machine is the one using a squirrel-cage rotor. This machine is commonly called *Induction Machine* (IM). The squirrel-cage rotor is made out of multiple aluminium or copper rods that are moulded in slots of the rotor and short circuited at both ends. Lack of rotor windings and slipring with brushes makes the induction machine. In this master thesis, modelling and control will be based on the induction machine.

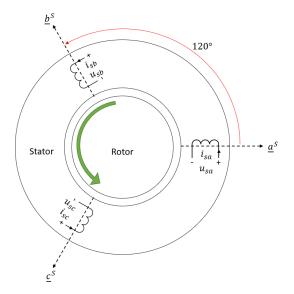

An illustration of the three-phase induction machine is presented in Figure 2.1. Each distributed phase winding is represented by an equivalent concentrated coil aligned with its respective magnetic axis. The three magnetic axes are shifted 120° in space and is shown as  $\underline{a}^{S}, \underline{b}^{S}, \underline{c}^{S}$  in the figure.

Figure 2.1: Principle drawing of the three-phase Induction Machine

### 2.2 Modelling of the Induction Machine

There are several different reasons why it is important to make equivalent models of the induction machine. Different control strategies use different transformed models of the physical machine in order to simplify the analysis and equations [11]. The models also allow the machine and control strategies to be tested using simulation tools.

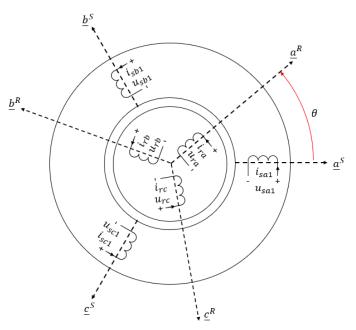

The control and analysis used in this master thesis require two different transformed models. Stator oriented model and rotor-flux oriented model. Both models have fictitious stator and rotor windings located at the same magnetic axis. The transformed models are presented in detail in this subchapter. However, before deducting the different transformed models, it is necessary to make a physical model representing the real currents, voltages, impedances and fluxes in the machine. Moreover, to simplify the transformations it is possible to make a two-phase representation of the physical three-phase system.

For all the models presented in this thesis, direction and polarity of currents and voltages are defined according to a machine running in motor operation. Capital symbols are used for physical values and lower-case letters are used for pu-values. The superscript *S* and *R* indicate that the vector is in its original frame of reference, i.e. stator quantiles in stator frame and rotor quantiles in rotor frame. Lower case superscript indicates what reference frame the windings are fixed to, i.e. *s* is fixed to stator, *r* is fixed to rotor or *k* is fixed to an unspecified system. Subscript *s* and *r* indicate where the winding is located. Furthermore, subscript *a*, *b*, *c* or  $\alpha$ ,  $\beta$  specify the stator or rotor winging in question.

The physical machine model presented is based on the work done in [11] and [13] and both Clarke and Park transformations are based on the work done in [11].

Figure 2.2: Schematic representation of the three-phase Induction Machine

The following five assumptions are taken into account when modelling the machine:

- 1. The stator windings only give a sinusoidal distributed field in the air gap.

- 2. All the stator windings are equal and have their unique orientation.

- 3. Resistance and inductances are assumed independent of temperature and frequency.

- 4. Magnetic saturation, hysteresis and eddy currents are neglected.

- 5. The squirrel-cage rotor is equivalent to a wounded rotor.

#### 2.2.1 Physical model

The physical model is based on the so-called Co-energy concept and can be constructed by using the voltage balance equations for each of the equivalent stator and rotor winding [11]. Eq.(2.1) shows voltage equation for the windings in the induction machine given in matrix form. The six windings in question are presented in Figure 2.2. Flux linkage in the voltage equation can be expressed by eq.(2.2).

$$\underline{U}^{SR} = \mathbf{R}^{SR} \cdot \underline{I}^{SR} + \frac{d\underline{\Psi}^{SR}}{dt}$$

(2.1)

$$\underline{\Psi}^{SR} = \boldsymbol{L}^{SR} \cdot \underline{I}^{SR} \tag{2.2}$$

Where the voltage, current and flux linkage vectors are:

$$\underline{U}^{SR} = \begin{bmatrix} U_{sa} & U_{sb} & U_{sc} & U_{ra} & U_{rb} & U_{rc} \end{bmatrix}^{T}

\underline{I}^{SR} = \begin{bmatrix} I_{sa} & I_{sb} & I_{sc} & I_{ra} & I_{rb} & I_{rc} \end{bmatrix}^{T}

\underline{\Psi}^{SR} = \begin{bmatrix} \Psi_{sa} & \Psi_{sb} & \Psi_{sc} & \Psi_{ra} & \Psi_{rb} & \Psi_{rc} \end{bmatrix}^{T}$$

(2.3)

The resistance matrix containing the physical stator and rotor resistance has the shape of a  $I_4$  identity matrix and can be expressed as:

$$\boldsymbol{R}^{SR} = diag[\boldsymbol{R}_{S} \quad \boldsymbol{R}_{S} \quad \boldsymbol{R}_{S} \quad \boldsymbol{R}_{r} \quad \boldsymbol{R}_{r} \quad \boldsymbol{R}_{r}]$$

(2.4)

The inductances used to calculate the flux linkages in the machine can be expressed with help of submatrices.  $L_{ss}^S$  and  $L_{rr}^S$  are the self and mutual inductances of stator and rotor with respect to itself. The air gap between stator and rotor is assumed to be constant since the rotor is assumed to be symmetrical, thus making both submatrices independent of rotor angle,  $\theta$ .  $L_{sr}^S(\theta)$  and  $L_{rs}^R(\theta)$  are the mutual inductance between stator and rotor and vice versa, both with a rotor angle dependency.

$$\boldsymbol{L}^{SR} = \begin{bmatrix} \boldsymbol{L}_{Sr}^{S} & \boldsymbol{L}_{Sr}^{S}(\boldsymbol{\theta}) \\ \boldsymbol{L}_{rs}^{R}(\boldsymbol{\theta}) & \boldsymbol{L}_{rr}^{S} \end{bmatrix}$$

(2.5)

Submatrices  $L_{ss}^{S}$  are written in detail in eq.(2.6). The diagonal elements show the self-inductance of each winding. Self-inductance is given by stator leakage induces,  $L_{s\sigma}$  (i.e. inductance in the end windings etc.) and mutual inductance of the winding with respect to itself (i.e.  $L_{sm} \cdot \cos(0)$ ). The off-diagonal elements give the mutual inductance between two different windings. From Figure 2.2 it can be seen that the stator windings are located 120° from each other, thus making the off-diagonal elements equal  $L_{sm} \cdot \pm \cos(2\pi/3)$ .

$$\boldsymbol{L}_{SS}^{S} = \begin{bmatrix} L_{sa} & L_{sasb} & L_{sasc} \\ L_{sbsa} & L_{sb} & L_{sbsc} \\ L_{scsa} & L_{scsb} & L_{sc} \end{bmatrix} = L_{s\sigma} \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} + L_{sm} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ -\frac{1}{2} & 1 & -\frac{1}{2} \\ -\frac{1}{2} & -\frac{1}{2} \\ -\frac{1}{2} & -\frac{1}{2} \end{bmatrix}$$

(2.6)

Same goes for self and mutual inductances in the equivalent rotor windings,  $L_{rr}^{R}$ .

$$\boldsymbol{L}_{rr}^{R} = \begin{bmatrix} L_{ra} & L_{rarb} & L_{rarc} \\ L_{rbra} & L_{rb} & L_{rbrc} \\ L_{rcra} & L_{rcrb} & L_{rc} \end{bmatrix} = L_{r\sigma} \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} + L_{rm} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ -\frac{1}{2} & 1 & -\frac{1}{2} \\ -\frac{1}{2} & -\frac{1}{2} \\ -\frac{1}{2} & -\frac{1}{2} \end{bmatrix}$$

(2.7)

The mutual inductance between stator and rotor given by  $L_{sr}^S$  is presented in the matrix below. The mutual inductances are dependent on rotor position and is given by the peak inductance between a stator and rotor winding,  $L_{srm}$ , and the physical angle between the two windings at a given time in space.

$$L_{sr}^{S}(\theta) = L_{srm} \begin{bmatrix} \cos(\theta) & \cos\left(\theta + \frac{2\pi}{3}\right) & \cos\left(\theta + \frac{4\pi}{3}\right) \\ \cos\left(\theta - \frac{2\pi}{3}\right) & \cos(\theta) & \cos\left(\theta + \frac{2\pi}{3}\right) \\ \cos\left(\theta - \frac{4\pi}{3}\right) & \cos\left(\theta - \frac{2\pi}{3}\right) & \cos(\theta) \end{bmatrix}$$

(2.8)

The mutual inductance between rotor and stator,  $L_{rs}^{R}(\theta)$ , is simply the transposed matrix of  $L_{sr}^{S}(\theta)$ .

$$\boldsymbol{L}_{rs}^{R}(\theta) = \left(\boldsymbol{L}_{sr}^{S}(\theta)\right)^{T}$$

(2.9)

The different constants used in the inductance matrices are summarised below

$L_{s\sigma}$  – Leakage inductance of each stator winding  $L_{r\sigma}$  – Leakage inductance of each rotor winding  $L_{sm}$  – Peak value of mutual inductance between two stator windings  $L_{rm}$  – Peak value of mutual inductance between two rotor windings  $L_{srm}$  – Peak value of mutual inductance between a stator and rotor winding

#### 2.2.2 Clarke Transformation

The sinusoidal phase currents, voltages and flux linkages in the machine can be represented as three vectors, shifted 120° in space, in the two-dimensional plane. The sum of the phase vectors will be a rotating vector with constant amplitude. This rotating space vector can also be represented by a two-phase winding where the windings are shifted by 90 electrical degrees. The transformation from a three-phase system to a two-phase system is usually called Clark transformation, after professor Edith Clark, or  $\alpha$ ,  $\beta$ ,  $\gamma$  transformation. Preforming a Clark transformation will simplify both equations and analysis of the system.

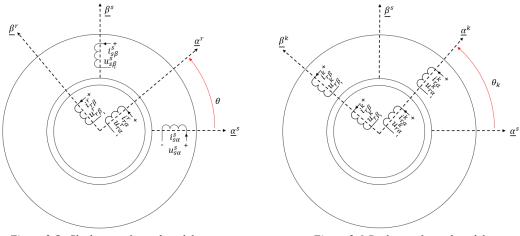

The old three-phase system and the transformed two-phase system are presented in Figure 2.3 and Figure 2.4, respectively. It can be seen that the new  $\alpha$ -axis is located similar to the old  $\alpha$ -axis.  $\beta$ -axis is leading  $\alpha$ -axis with 90 electrical degrees. The angle  $\theta$  are the same in both models.

$\underline{\beta}^{r}$

Figure 2.3: Three-phase induction machine

Figure 2.4: Equivalent two-phase induction machine

Two-phase transformation of stator and rotor current can be done using the equations presented in (2.10). The two-phase representation of the three-phase system as shown in Figure 2.4 and given by the equations are only valid if it is assumed that the sum of current in the three-phase system is equal to zero. However, this will not limit the model since the drive will be tripped if current starts returning through earth, thus making the sum of phase current different from zero.

$$Stator currents \qquad Rotor currents \\ I_{s\alpha}^{s} = \frac{2}{3} \left( I_{sa} - \frac{1}{2} \cdot I_{sb} - \frac{1}{2} I_{sc} \right) = I_{sa} \qquad I_{r\alpha}^{r} = \frac{2}{3} \left( I_{ra} - \frac{1}{2} \cdot I_{rb} - \frac{1}{2} I_{rc} \right) = I_{ra} \\ I_{s\beta}^{s} = \frac{2}{3} \left( \frac{\sqrt{3}}{2} \cdot I_{sb} - \frac{\sqrt{3}}{2} I_{sc} \right) = \frac{\sqrt{3}}{3} (I_{sb} - I_{sc}) \qquad I_{r\beta}^{r} = \frac{2}{3} \left( \frac{\sqrt{3}}{2} \cdot I_{rb} - \frac{\sqrt{3}}{2} I_{rc} \right) = \frac{\sqrt{3}}{3} (I_{rb} - I_{rc})$$

(2.10)

Equations needed to transform currents in the two-phase system back to a three-phase system are presented in (2.11).

Stator currentsRotor currents

$$I_{sa} = I_{sa}^s$$

$I_{ra} = I_{ra}^r$  $I_{sb} = -\frac{1}{2} \cdot I_{sa}^s + \frac{\sqrt{3}}{2} \cdot I_{s\beta}^s$  $I_{rb} = -\frac{1}{2} \cdot I_{ra}^r + \frac{\sqrt{3}}{2} \cdot I_{r\beta}^r$  $I_{sc} = -\frac{1}{2} \cdot I_{sa}^s - \frac{\sqrt{3}}{2} \cdot I_{s\beta}^s$  $I_{rc} = -\frac{1}{2} \cdot I_{ra}^r - \frac{\sqrt{3}}{2} \cdot I_{r\beta}^r$

Voltages and flux linkages can be transformed from a three-phase to a two-phase representation and vice versa using the same relations as shown in (2.10) and (2.11). As for currents, the transformed voltage and flux linkage model is only valid if the sum of phase voltages is zero.

After the Clark transformation, voltage and flux linkage equations can be expressed in matrix form by eq.(2.12) and (2.13), respectively.

$$\underline{U}^{sr} = \mathbf{R}^{sr} \cdot \underline{I}^{sr} + \frac{d\underline{\Psi}^{sr}}{dt}$$

(2.12)

$$\underline{\Psi}^{sr} = \boldsymbol{L}^{sr} \cdot \underline{\boldsymbol{I}}^{sr} \tag{2.13}$$

Where the voltage, current and flux linkage vectors are:

$$\underline{U}^{sr} = \begin{bmatrix} U_{s\alpha}^{s} & U_{s\beta}^{s} & U_{r\alpha}^{r} & U_{r\beta}^{r} \end{bmatrix}^{T}

\underline{I}^{sr} = \begin{bmatrix} I_{s\alpha}^{s} & I_{s\beta}^{s} & I_{r\alpha}^{r} & I_{r\beta}^{r} \end{bmatrix}^{T}

\underline{\Psi}^{sr} = \begin{bmatrix} \Psi_{s\alpha}^{s} & \Psi_{s\beta}^{s} & \Psi_{r\alpha}^{r} & \Psi_{r\beta}^{r} \end{bmatrix}^{T}$$

(2.14)

The resistance matrix is given by the diagonal matrix shown in (2.15). The components of the matrix are the physical resistance in stator and rotor windings.

$$\boldsymbol{R}^{sr} = diag[\boldsymbol{R}_s \quad \boldsymbol{R}_s \quad \boldsymbol{R}_r \quad \boldsymbol{R}_r] \tag{2.15}$$

In order to use the same inductances as in the physical model, a scaling factor of 3/2 must be introduced to the elements that produces flux in the air gap. This is done to compensate for the MMF produced by the two-phase system that would otherwise be 2/3 smaller than the real MMF [11].

The new inductance matrix for the two-phase system is presented in (2.16). Comparing  $L^{sr}$  with  $L^{SR}$  from the physical model, it can be seen that the matrix is reduced from a 6x6 to a 4x4 matrix. Moreover, since the new stator and rotor windings are shifted by 90°, mutual inductance between the two windings in stator or rotor is zero. Mutual inductance between a stator and rotor winding is still dependent on rotor position.

$$\mathbf{L}^{sr}(\theta) = \begin{bmatrix} L_{saa} & 0 & L_{sara}(\theta) & L_{sar\beta}(\theta) \\ 0 & L_{s\beta\beta} & L_{s\betara}(\theta) & L_{s\betar\beta}(\theta) \\ L_{rasa}(\theta) & L_{ras\beta}(\theta) & L_{raa} & 0 \\ L_{r\betasa}(\theta) & L_{r\betas\beta}(\theta) & 0 & L_{s\beta\beta} \end{bmatrix}$$

$$= \begin{bmatrix} L_{s\sigma} + \frac{3}{2}L_{sm} & 0 & \frac{3}{2}L_{srm}\cos\theta & -\frac{3}{2}L_{srm}\sin\theta \\ 0 & L_{s\sigma} + \frac{3}{2}L_{sm} & \frac{3}{2}L_{srm}\cos\theta & \frac{3}{2}L_{srm}\cos\theta \\ \frac{3}{2}L_{srm}\cos\theta & \frac{3}{2}L_{srm}\sin\theta & L_{r\sigma} + \frac{3}{2}L_{rm} & 0 \\ -\frac{3}{2}L_{srm}\sin\theta & \frac{3}{2}L_{srm}\cos\theta & 0 & L_{r\sigma} + \frac{3}{2}L_{rm} \end{bmatrix}$$

$$(2.16)$$

Where:

$L_{s\sigma}$  – Leakage inductance of each stator winding  $L_{r\sigma}$  – Leakage inductance of each rotor winding  $L_{sm}$  – Peak value of mutual inductance between two stator windings  $L_{rm}$  – Peak value of mutual inductance between two rotor windings  $L_{srm}$  – Peak value of mutual inductance between a stator and rotor winding

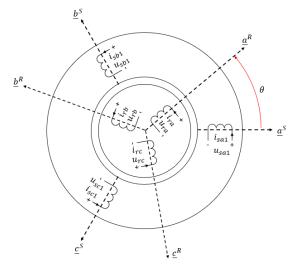

#### 2.2.3 Park Transformation

From last section, it was shown that the inductance matrix,  $L^{sr}$ , was dependent on rotor position. This dependency occurs because stator and rotor windings are fixed to different axis in the model. By modelling both stator and rotor winding in the same axis system, inductance becomes independent of position. This will simplify the model even further.

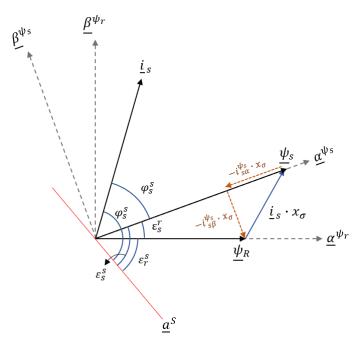

The transformation from the two-phase equivalent system to the new system with stator and rotor windings rotating in the same axis system is called Park transformation. The Park transformed system is show in Figure 2.6. The figure shows the new fictitious stator and rotor winding fixed to the same axis.

Figure 2.5: Clarke transformed model

Figure 2.6:Park transformed model

The transformation matrix and the inverse transformation matrix used in Park transformation are presented in (2.17).

$$\boldsymbol{T}^{k} = \begin{bmatrix} \boldsymbol{T}_{ss}^{k} & \boldsymbol{0} \\ \boldsymbol{0} & \boldsymbol{T}_{rr}^{k} \end{bmatrix} \qquad \qquad \boldsymbol{T}^{-k} = \begin{bmatrix} \boldsymbol{T}_{ss}^{-k} & \boldsymbol{0} \\ \boldsymbol{0} & \boldsymbol{T}_{rr}^{-k} \end{bmatrix}$$

(2.17)

Where the different elements of the transformation matrices are:

$$\boldsymbol{T}_{ss}^{k} = \begin{bmatrix} \cos\theta_{k} & \sin\theta_{k} \\ -\sin\theta_{k} & \cos\theta_{k} \end{bmatrix} \qquad \qquad \boldsymbol{T}_{ss}^{-k} = \begin{bmatrix} \cos\theta_{k} & -\sin\theta_{k} \\ \sin\theta_{k} & \cos\theta_{k} \end{bmatrix}$$

(2.18)

$$\boldsymbol{T}_{rr}^{k} = \begin{bmatrix} \cos\theta_{r} & \sin\theta_{r} \\ -\sin\theta_{r} & \cos\theta_{r} \end{bmatrix} \qquad \qquad \boldsymbol{T}_{rr}^{-k} = \begin{bmatrix} \cos\theta_{r} & -\sin\theta_{r} \\ \sin\theta_{r} & \cos\theta_{r} \end{bmatrix}$$

(2.19)

Where:

$\theta_r = \theta_k - \theta$

The relation between voltages, currents and impedances between Park and Clarke transformed systems are given by:

$$\underbrace{\underline{U}^{k} = \mathbf{T}^{k} \cdot \underline{U}^{sr}}_{\mathbf{I}^{k} = \mathbf{T}^{k} \cdot \underline{I}^{sr}} \qquad \qquad \underbrace{\underline{U}^{sr} = \mathbf{T}^{-k} \cdot \underline{U}^{k}}_{\mathbf{X}^{k} = \mathbf{T}^{k} \cdot \mathbf{X}^{sr} \cdot \mathbf{T}^{-k}} \qquad \qquad \underbrace{\underline{I}^{sr} = \mathbf{T}^{-k} \cdot \underline{I}^{k}}_{\mathbf{I}^{sr} = \mathbf{T}^{-k} \cdot \underline{I}^{k}} \qquad (2.20)$$

An expression for the flux linkage can be found by multiplying both sides of eq. (2.13) with  $T^k$  and using the relations given in (2.20).

$$\underline{\Psi}^{k} = \boldsymbol{T}^{k} \cdot \underline{\Psi}^{\mathrm{sr}} = \boldsymbol{T}^{k} \cdot \boldsymbol{L}^{\mathrm{sr}} \cdot \boldsymbol{T}^{-k} \cdot \underline{I}^{k} = \boldsymbol{L}^{k} \cdot \underline{I}^{k}$$

(2.21)

Voltage equations in the new transformed system can be found by multiplying both sides of the voltage equation, eq.(2.12), with the transformation matrix,  $T^k$ , and using the relations between the two systems.

$$T^{k} \cdot \underline{U}^{sr} = T^{k} \left( R^{sr} \cdot \underline{I}^{sr} + \frac{d\underline{\Psi}^{sr}}{dt} \right)$$

$$\underline{U}^{k} = T^{k} \cdot R^{sr} \cdot T^{-k} \cdot \underline{I}^{k} + T^{k} \cdot \frac{d(T^{-k} \cdot \underline{\Psi}^{k})}{dt}$$

$$\underline{U}^{k} = R^{k} \cdot \underline{I}^{k} + \frac{d\underline{\Psi}^{k}}{dt} + T^{k} \cdot \frac{dT^{-k}}{dt} \cdot \underline{\Psi}^{k}$$

(2.22)

It can be seen that the inverse transformation matrix,  $T^{-k}$ , is a function of  $\theta_r$  and  $\theta_k$ . The derivative of  $T^{-k}$  can be expressed as:

$$\frac{d\boldsymbol{T}_{(\theta_r,\theta_k)}^{-k}}{dt} \cdot \frac{(\partial\theta_r \cdot \partial\theta_k)}{(\partial\theta_r \cdot \partial\theta_k)} = \frac{\partial\theta_r}{dt} \cdot \frac{\partial\boldsymbol{T}^{-k}}{\partial\theta_r} + \frac{\partial\theta_k}{dt} \cdot \frac{\partial\boldsymbol{T}^{-k}}{\partial\theta_k} = \omega_n \cdot f_r \cdot \frac{\partial\boldsymbol{T}^{-k}}{\partial\theta_r} + \omega_n \cdot f_k \cdot \frac{\partial\boldsymbol{T}^{-k}}{\partial\theta_k}$$

(2.23)

By substituting eq.(2.23) in eq.(2.22) and introducing the coupling matrices  $J_r$  and  $J_k$ , the voltage equation can be expressed as:

$$\underline{U}^{k} = \mathbf{R}^{k} \cdot \underline{I}^{k} + \frac{d\underline{\Psi}^{k}}{dt} + \omega_{n} \cdot f_{r} \cdot \mathbf{J}_{r} \cdot \underline{\Psi}^{k} + \omega_{n} \cdot f_{k} \cdot \mathbf{J}_{k} \cdot \underline{\Psi}^{k}$$

(2.24)

Where:

Voltage, current and flux linkage vectors in the new system become:

$$\underline{\underline{U}}^{k} = \begin{bmatrix} U_{s\alpha}^{k} & U_{s\beta}^{k} & U_{r\alpha}^{k} & U_{r\beta}^{k} \end{bmatrix}^{t}$$

$$\underline{\underline{I}}^{k} = \begin{bmatrix} I_{s\alpha}^{k} & I_{s\beta}^{k} & I_{r\alpha}^{k} & I_{r\beta}^{k} \end{bmatrix}^{T}$$

$$\underline{\underline{\Psi}}^{k} = \begin{bmatrix} \Psi_{s\alpha}^{k} & \Psi_{s\beta}^{k} & \Psi_{r\alpha}^{k} & \Psi_{r\beta}^{k} \end{bmatrix}^{T}$$

(2.25)

The resistance matrix becomes equal to that used in previous section.

$$\boldsymbol{R}^{k} = diag[\boldsymbol{R}_{s} \quad \boldsymbol{R}_{s} \quad \boldsymbol{R}_{r} \quad \boldsymbol{R}_{r}]$$

(2.26)

As mention earlier, one of the main motivations of preforming a Park transformation is the inductance matrix's independency of rotor position. Since stator and rotor winding are fixed to the same axis system, the new inductance matrix simply becomes  $L^{sr}(\theta = 0)$ .

$$\boldsymbol{L}^{k} = \boldsymbol{L}^{sr}(0) = \begin{bmatrix} L_{s\sigma} + \frac{3}{2}L_{m} & 0 & \frac{3}{2}L_{m} & 0\\ 0 & L_{s\sigma} + \frac{3}{2}L_{m} & 0 & \frac{3}{2}L_{m}\\ \frac{3}{2}L_{m} & 0 & L_{r\sigma} + \frac{3}{2}L_{m} & 0\\ 0 & \frac{3}{2}L_{m} & 0 & L_{r\sigma} + \frac{3}{2}L_{m} \end{bmatrix}$$

(2.27)

Where:

$L_{s\sigma}$  – Leakage inductance of each stator winding  $L_{r\sigma}$  – Leakage inductance of each rotor winding  $L_m$  – Mutual inductance between two windings

#### Orientation of axis system

For a synchronous machine with salient poles, Park transformed system is always oriented to the rotor in order to achieve an inductance matrix independent of the position. In an asynchronous machine however, axis orientation does not have the same constraints. The symmetrical rotor ensures a position independent inductance matrix as long as the equivalent stator and rotor windings are orientated to the same magnetic axis.

There are several different alternatives on how to orient the Park transformed system. The desired orientation is dependent on application, control and measurement available of the machine. Commonly used orientations include: Stator-oriented model, rotor-oriented model and space-vector oriented model. In this thesis, stator-oriented model and rotor-flux (space-vector) oriented model will be used.

#### Stator-oriented model

In stator-oriented model,  $\underline{\alpha}^k$ ,  $\underline{\beta}^k$  is fixed to the  $\underline{\alpha}^s$ ,  $\underline{\beta}^s$ -axis, thus making the new axis system stationary. Currents and voltages are alternating with stator frequency,  $f_s$ , in both equivalent stator and rotor windings. This can for example be beneficial when using a hysteresis controller.

$$\theta_k = 0 \qquad \qquad \theta_r = -\theta \qquad \qquad f_k = 0 \qquad (2.28)$$

#### Rotor-flux oriented model

In rotor-flux oriented system,  $\underline{\alpha}^k$  is fixes to the rotor flux  $\underline{\psi}_r$ . The rotor flux rotates with the same frequency as the stator frequency i.e. synchronous frequency. The synchronous rotating model result in DC-quantities of currents and voltages in steady state operation. This can be beneficial when using PI-controllers.

$$\theta_k = \theta_{\psi_r}$$

$\theta_r = \theta_{\psi_r} - \theta$   $f_k = f_{\psi_r} = f_s$  (2.29)

#### Electrical torque

The electrical torque of the machine in the Park transformed model can be expressed as [11]:

$$T_e = \frac{p}{2} \cdot 3 \cdot L_m \cdot (I_{s\beta}^k \cdot I_{r\alpha}^k - I_{s\alpha}^k \cdot I_{r\beta}^k)$$

(2.30)

By realizing that  $\Psi_s = L_m \cdot I_r$ , the torque equation can be expressed in terms of stator quantities

$$T_e = \frac{p}{2} \cdot 3 \cdot \left(\Psi_{s\alpha}^k \cdot I_{s\beta}^k - \Psi_{s\alpha}^k \cdot I_{s\alpha}^k\right)$$

(2.31)

Where: *p* is the number of pole pairs in the motor

### 2.3 Pu system

Once the proper transformation model has been established, it is possible to scale the values according to a pu-system. The base values are often chosen to be related to the rated value of the machine. There are many reasons why a pu-scaled model can be beneficial. Since the values are scaled according to the rated limits, it becomes easy to detect if the machine is running in overload regardless of the power rating. The scaling also makes it easier to utilize experiences with machines of other power rating. Moreover, proper pu-scaling can also simplify machine model, thus simplifying the equations [11].

Base values for stator quantities in the pu-model are shown in (2.32).

$$U_{s,basis} = \hat{U}_{n} \qquad I_{s,basis} = \hat{I}_{n}$$

$$Z_{s,basis} = \frac{\hat{U}_{n}}{\hat{I}_{n}} \qquad S_{s,basis} = \frac{3}{2} \cdot \hat{U}_{n} \cdot \hat{I}_{n} \qquad (2.32)$$

$$L_{s,basis} = \frac{\Psi_{s,basis}}{\hat{I}_{n}} \qquad \Psi_{s,basis} = \frac{\hat{U}_{n}}{2\pi \cdot f_{n}}$$

An important simplification that can be achieved when scaling the model is the simplified inductance matrix. By properly selecting the rotor base values, inductance matrix becomes [14]:

$$\boldsymbol{x}^{k} = \boldsymbol{\Psi}_{sr,base}^{-1} \cdot \boldsymbol{X}_{sr}^{k} \cdot \boldsymbol{\hat{I}}_{sr,basis} = \begin{bmatrix} x_{s} & 0 & x_{m} & 0\\ 0 & x_{s} & 0 & x_{m} \\ x_{m} & 0 & x_{r} & 0 \\ 0 & x_{m} & 0 & x_{r} \end{bmatrix}$$

(2.33)

Where

$$\begin{aligned} x_s &= x_m + x_{s\sigma} \\ x_r &= x_m + x_{r\sigma} \end{aligned}$$

The base value for the torque is given as:

$$T_{basis} = \frac{S_n}{\Omega_n} = \frac{3}{2} \cdot p \cdot \frac{\hat{U}_n \cdot \hat{I}_n}{\omega_n} = \frac{3}{2} \cdot p \cdot \Psi_n \cdot \hat{I}_n$$

(2.34)

By scaling the voltage equations, (2.24), and flux linkage equations (2.21) according to (2.32) and introducing the scaled inductance matrix, pu-equation for voltage and flux linkage can be expressed by (2.35) and (2.36), respectively.

$$u_{s\alpha}^{k} = r_{s} \cdot i_{s\alpha}^{k} + \frac{1}{\omega_{n}} \cdot \frac{d\psi_{s\alpha}^{k}}{dt} - f_{k} \cdot \psi_{s\beta}^{k} \qquad u_{r\alpha}^{k} = r_{r} \cdot i_{r\alpha}^{k} + \frac{1}{\omega_{n}} \cdot \frac{d\psi_{r\alpha}^{k}}{dt} - (f_{k} - n) \cdot \psi_{r\beta}^{k}$$

$$u_{s\beta}^{k} = r_{s} \cdot i_{s\beta}^{k} + \frac{1}{\omega_{n}} \cdot \frac{d\psi_{s\beta}^{k}}{dt} + f_{k} \cdot \psi_{s\alpha}^{k} \qquad u_{r\beta}^{k} = r_{r} \cdot i_{r\beta}^{k} + \frac{1}{\omega_{n}} \cdot \frac{d\psi_{r\beta}^{k}}{dt} - (f_{k} - n) \cdot \psi_{r\alpha}^{k}$$

$$(2.35)$$

Flux linkage equations

$$\psi_{s\alpha}^{k} = x_{s} \cdot i_{s\alpha}^{k} + x_{m} \cdot i_{r\alpha}^{k} \qquad \qquad \psi_{r\alpha}^{k} = x_{r} \cdot i_{r\alpha}^{k} + x_{m} \cdot i_{s\alpha}^{k}$$

$$\psi_{s\beta}^{k} = x_{s} \cdot i_{s\beta}^{k} + x_{m} \cdot i_{r\beta}^{k} \qquad \qquad \psi_{r\beta}^{k} = x_{r} \cdot i_{r\beta}^{k} + x_{m} \cdot i_{s\beta}^{k}$$

(2.36)

The electrical torque in pu can be expressed as follows:

$$\tau_e = \frac{T_e}{T_{basis}} = \frac{3/2 \cdot p \cdot \left(\Psi_{s\alpha}^k \cdot I_{s\beta}^k - \Psi_{s\beta}^k \cdot I_{s\alpha}^k\right)}{3/2 \cdot p \cdot \Psi_n \cdot \hat{l}_n} = \psi_{s\alpha}^k \cdot i_{s\beta}^k - \psi_{s\beta}^k \cdot i_{s\alpha}^k \tag{2.37}$$

## 3 Control of the Induction Machine

### 3.1 V/f-Control

Scalar control or more commonly known V/f-control, is the most used control strategy in the industry when controlling an induction motor. V/f-control offers a low-performance control of the machine, i.e. ability to control steady state speed but not dynamic processes between two steps in speed reference. This behaviour makes V/f-control suitable for applications with little requirement with regard to dynamic processes like fans and pumps [15].

V/f-control can be performed using both open and closed loop. The difference between the two setups is usage of position sensor. Closed loop control is able to adjust the mechanical speed to the reference value, while the open loop control regulates the synchronous rotating field according to a reference, thus giving a small steady state deviation between reference and actual speed. Both control methods use current measurements to protect the machine for overload.

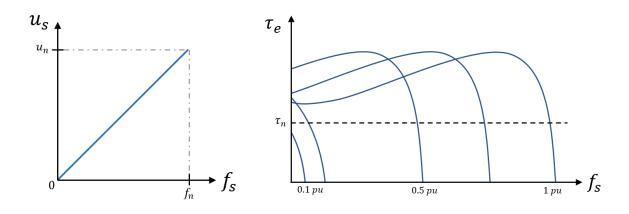

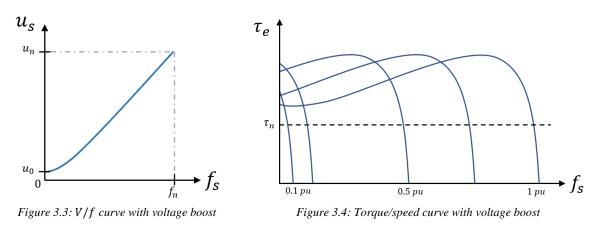

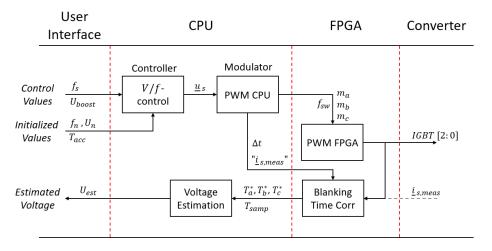

The reason why the control strategy is called V/f-control is simply because the relation between stator voltage and frequency is kept constant during different operation speeds. Equations for steady state stator voltage and stator flux for low-, medium- and high-speed operation are presented in (3.1). Looking at stator flux during medium- and high-speed operation, it is evident that stator flux is proportional with stator voltage and inverse proportional with stator frequency. Consequently, by keeping the V/f ratio constant, stator flux is also kept constant. This constant relationship is shown in Figure 3.1.

A classical torque speed curve of an induction motor is presented in Figure 3.2. If the stator flux is kept at its rated value, hence constant V/f ratio, the familiar torque characteristic will be shifted along the frequency axis with more or less the same shape. This behaviour enables the machine to deliver nominal torque in large area of the nominal speed range. The slip rate of the machine is also kept low, giving good efficiency and low reactive power consumption during lower speed operation [16].

However, looking at voltage and flux equations during low speed operation, it is seen that resistive voltage drop starts to make an impact on the flux amplitude. The reduced flux amplitude result in a lower torque. This effect is also illustrated in Figure 3.2, where the torque at low speeds becomes lower than the nominal torque. If the machine has a high load-torque during start up, this behaviour may prove to be problematic [15].

Figure 3.1: V/f curve without voltage boost

Figure 3.2: Torque/speed curve without voltage boost

One method of avoiding the problem at lower speed operation and especially when the stator frequency is close to zero is to introduce a so-called voltage boost. The voltage boost compensates for the resistive voltage drop, ensuring a stator flux at 1 pu, thus making the machine able to produce the same torque throughout the nominal speed operation range. The voltage boost and the new torque/speed characteristic are presented in Figure 3.3 and Figure 3.4, respectively [16].

### 3.2 Rotor-Flux Orientated Control

Some applications of the induction machines, like ship propulsion or electrical cars, may require the ability to control dynamic processes as well as steady state values of speed and torque. Such drives are called high-performance drives. A control strategy that falls under this is the so-called *field-oriented control* (FOC). FOC allows the magnitude, frequency and phase shift of the different phase-voltages in the machine to be controlled individually, thus allowing the torque and flux to change separately [13]. There are at least three different control strategies of field oriented control [11]:

- 1. Stator oriented field control

- 2. Rotor oriented field control

- 3. Rotor-flux oriented field control

This thesis will only present and analyse benefits and challenges regarding the rotor-flux oriented control

The rotor-flux oriented control is an attractive control strategy because the control becomes very similar to the simple DC-machine control. Since the rotor-flux oriented system is rotating with stator frequency, all steady state values of currents, voltages and fluxes become DC-quantities in steady state. Furthermore, by definition,  $\alpha^k$ -axis is fixed to the rotor flux vector, thus  $\underline{\psi}_r = \psi_{r\alpha}$  and  $\psi_{r\beta} \equiv 0$ . Looking at the scaled rotor-flux eq. (2.36) it becomes evident that the length of the flux is determined by  $i_{s\alpha}^{\psi_r}$ .

$$\psi_R = \psi_{R\alpha} \qquad \qquad \psi_{R\beta} \equiv \frac{d\psi_{R\beta}}{dt} \equiv 0 \qquad (3.2)$$

Flux linkage vectors are not a physical quantity and cannot be measured. Therefore, in order to control the machine according to a flux vector it is necessary to calculate/estimate the flux vector using a flux model. Different models use different input parameters, thus making them suitable for different applications. The two estimation models presented in this thesis is called *Voltage model* and *Current model*. Usually, current model is the preferred estimation model if there is a position sender mounted on the shaft of the machine and voltage model can be used if the machine is running in sensorless control.

#### 3.2.1 Current Model

Current model uses measurements of stator current and rotor position as input parameters. Precise position measurement and the knowledge of stator frequency allows for a Park transformed system that is fixed to the rotor flux space vector. As stated earlier, fixing the new stator and rotor winding to a system that rotates with the same frequency as stator frequency yields DC-quantities of voltage, current and flux vectors in steady state. It will be shown in the derived current model below that control of the decomposed induction machine becomes very similar to that of a DC-machine. The model presented is based on the work done in [11].

Current model is derived from the rotor voltage and rotor-flux equations presented in eq.(2.35) and (2.36). Rotor voltage vector and rotor flux vector can be presented as follows:

$$\underline{u}_{r}^{k} = r_{r} \cdot \underline{i}_{r}^{k} + \frac{1}{\omega_{n}} \cdot \frac{d\underline{\psi}_{r}^{k}}{dt} + j \cdot f_{r} \cdot \underline{\psi}_{r}^{k}$$

$$(3.3)$$

$$\underline{\psi}_r^k = \underline{i}_r^k \cdot x_r + \underline{i}_s^k \cdot x_m \tag{3.4}$$

With help of eq.(3.4), it is possible to express the rotor voltage with stator current and roto flux as state variables. Substituting for  $\underline{i}_{r}^{k}$  in eq.(3.3) and rearranging the equations with the two state variables gives:

$$\underline{u}_{r}^{k} = \frac{1}{\omega_{n}} \cdot \frac{d\underline{\psi}_{r}^{k}}{dt} + \left(\frac{r_{r}}{x_{r}} + j \cdot f_{r}\right) \cdot \underline{\psi}_{r}^{k} - \frac{x_{m}r_{r}}{x_{r}} \cdot \underline{i}_{r}^{k}$$

(3.5)

It is possible to simplify the equations by introducing the following set of parameters.

$$\underline{\psi}_{R}^{k} = \frac{\underline{\psi}_{r}^{k}}{1 + \sigma_{r}} \qquad \sigma_{r} = \frac{x_{r}}{x_{m}} - 1 \qquad r_{R} = \left(\frac{x_{m}}{x_{r}}\right)^{2} r_{r} = \frac{r_{r}}{(1 + \sigma_{r})^{2}} \qquad T_{r} = \frac{x_{r}}{\omega_{n} r_{r}}$$

(3.6)

Since the induction machine has a rotor that is short circuited in both ends,  $\underline{u}_r^k$  will always be zero. Multiplying eq.(3.5) with  $1/(1 + \sigma_r)$  and using the new parameters presented in (3.6), a simplified voltage equation can be expressed as:

$$\frac{\underline{u}_{r}^{k}}{1+\sigma_{r}} = \frac{1}{\omega_{n}} \cdot \frac{d\underline{\psi}_{r}^{k}}{dt} \cdot \frac{1}{1+\sigma_{r}} + \left(\frac{r_{r}}{x_{r}}+j\cdot f_{r}\right) \cdot \frac{\underline{\psi}_{r}^{k}}{1+\sigma_{r}} - \frac{x_{m}r_{r}}{x_{r}} \cdot \frac{1}{1+\sigma_{r}} \cdot \underline{i}_{r}^{k}$$

$$0 = \frac{1}{\omega_{n}} \cdot \frac{d\underline{\psi}_{R}^{k}}{dt} + \left(\frac{1}{T_{r}\cdot\omega_{n}}+j\cdot f_{r}\right) \cdot \underline{\psi}_{R}^{k} - r_{R} \cdot \underline{i}_{r}^{k}$$

(3.7)

By decomposing the equation above and aligning the fictitious system with the rotor-flux, eq.(3.7) can be expressed in terms of  $\alpha$  and  $\beta$  components as follows:

$$0 = \frac{1}{\omega_n} \cdot \frac{d\psi_R^{\psi_r}}{dt} + \frac{\psi_R^{\psi_r}}{(\omega_n T_r)} - r_R \cdot i_{s\alpha}^{\psi_r}$$

(3.8)

$$0 = \frac{1}{\omega_n} \cdot \frac{d\psi_{R\beta}^{\psi_r}}{dt} + jf_r \cdot \psi_R^{\psi_r} - r_R \cdot i_{s\beta}^{\psi_r}$$

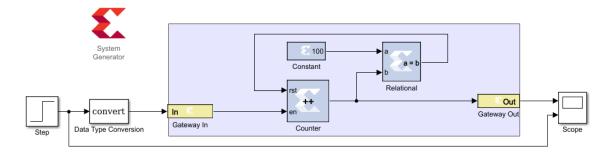

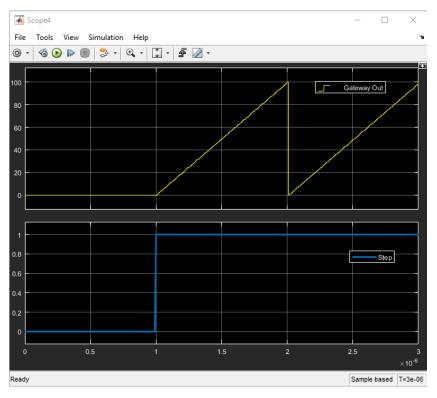

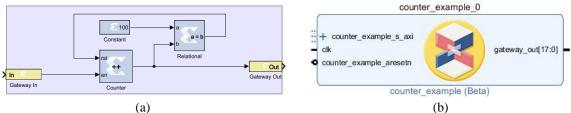

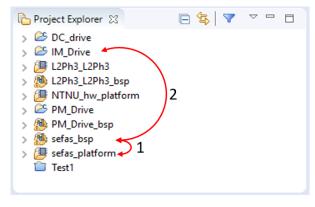

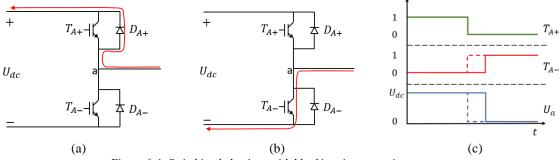

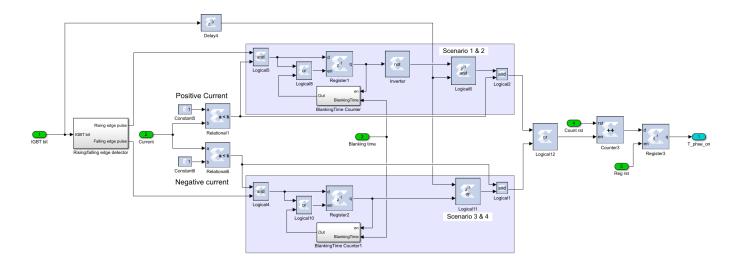

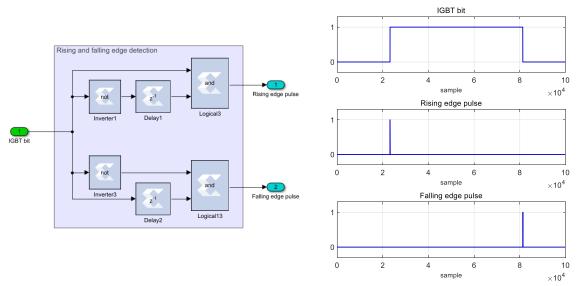

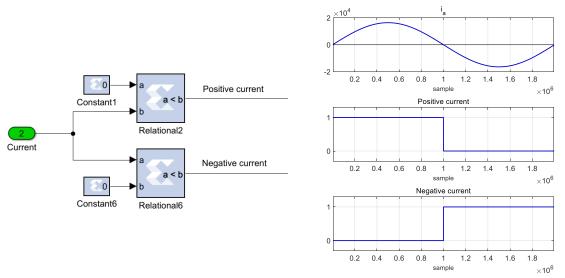

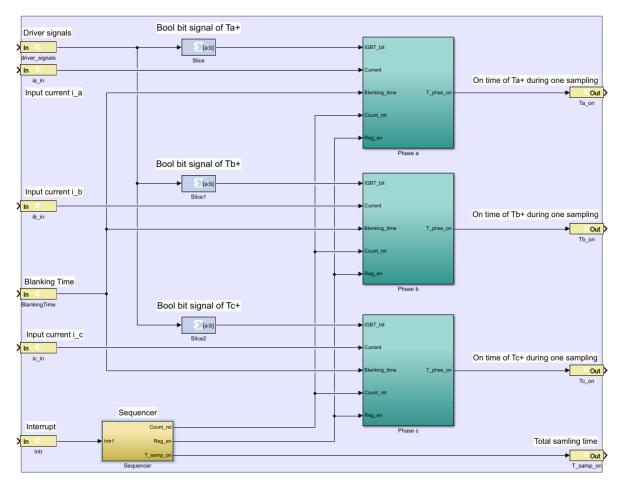

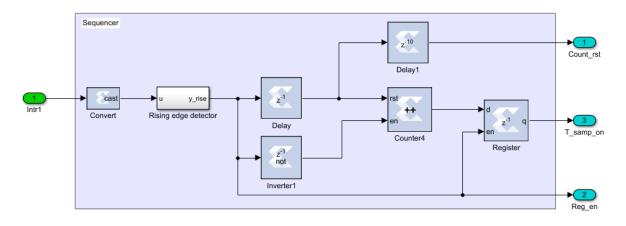

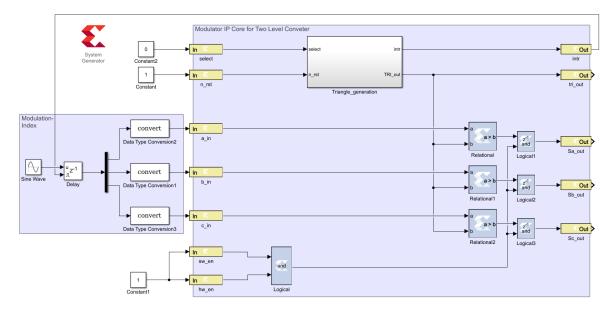

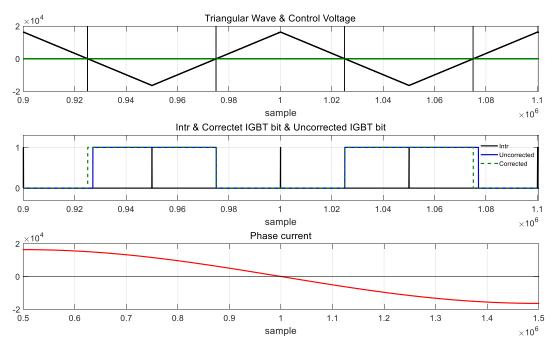

(3.9)