Master Thesis

Spring 2019

# Strict Memory Protection for Microcontrollers

**Erlend Sveen**

Supervisor: Jingyue Li Co-supervisor: Magnus Själander

Sunday 17<sup>th</sup> February, 2019

# Abstract

Modern desktop systems protect processes from each other with memory protection. Microcontroller systems, which lack support for memory virtualization, typically only uses memory protection for areas that the programmer deems necessary and does not separate processes completely. As a result the application still appears monolithic and only a handful of errors may be detected.

This thesis presents a set of solutions for complete separation of processes, unleashing the full potential of the memory protection unit embedded in modern ARM-based microcontrollers. The operating system loads multiple programs from disk into independently protected portions of memory. These programs may then be started, stopped, modified, crashed etc. without affecting other running programs. When loading programs, a new allocation algorithm is used that automatically aligns the memories for use with the protection hardware. A pager is written to satisfy additional run-time demands of applications, and communication primitives for inter-process communication is made available.

Since every running process is unable to get access to other running processes, not only reliability but also security is improved. An application may be split so that unsafe or error-prone code is separated from mission-critical code, allowing it to be independently restarted when an error occurs. With executable and writeable memory access rights being mutually exclusive, code injection is made harder to perform.

The solution is all transparent to the programmer. All that is required is to split an application into sub-programs that operates largely independently. An added benefit of this modularity is that code may also be developed and tested as independent programs. The standard POSIX API is used as the programming interface, allowing programmers to use existing knowledge and code when designing applications. For programs that do not depend on specific hardware, development may be done and tested on a regular desktop system entirely before running it on a microcontroller.

# Acknowledgements

Thanks to supervisors Jingyue Li and Magnus Själander for helping with all the formalities surrounding the thesis, and giving valuable feedback on the thesis work. The work presented in this thesis would not have been possible without supervision.

Also thanks to the students at the Orbit satellite program, which have helped by providing an environment for the thesis in the first place. The satellite program was in need of someone to work on the software, which resulted in both the pre-thesis project and the thesis itself. Students working on the satellite software has provided valuable feedback when using the operating system, helping to improve it.

# Contents

| Lis | List of Figures viii                          |                     |                                               |                   |  |  |  |  |  |

|-----|-----------------------------------------------|---------------------|-----------------------------------------------|-------------------|--|--|--|--|--|

| Lis | List of Tables ix                             |                     |                                               |                   |  |  |  |  |  |

| 1.  | Intro<br>1.1.<br>1.2.<br>1.3.<br>1.4.<br>1.5. | Solu<br>Test<br>Sum | <b>n</b> Earch Drivers                        | . 2<br>. 3<br>. 3 |  |  |  |  |  |

| 2.  | Bac                                           | kground             | d                                             | 5                 |  |  |  |  |  |

|     | 2.1.                                          | Men                 | nory Protection in Desktop Processors         |                   |  |  |  |  |  |

|     |                                               | 2.1.1.              | Overview                                      | . 5               |  |  |  |  |  |

|     |                                               | 2.1.2.              | History                                       |                   |  |  |  |  |  |

|     |                                               | 2.1.3.              | Memory Architecture As Seen By Software       |                   |  |  |  |  |  |

|     |                                               | 2.1.4.              | Challenges                                    |                   |  |  |  |  |  |

|     | 2.2.                                          |                     | nory Protection in Microcontrollers           |                   |  |  |  |  |  |

|     |                                               | 2.2.1.              | History                                       |                   |  |  |  |  |  |

|     |                                               | 2.2.2.              | Microcontroller Memory Protection             |                   |  |  |  |  |  |

|     |                                               | 2.2.3.              | Table Size and Table Entry Restrictions       |                   |  |  |  |  |  |

|     |                                               | 2.2.4.              | Allocation Example                            | . 11              |  |  |  |  |  |

| 3.  | Rela                                          | ted Wo              | ork                                           | 13                |  |  |  |  |  |

|     | 3.1.                                          | Stat                | e of the Art                                  | . 13              |  |  |  |  |  |

|     | 3.2.                                          | Shar                | ed vs Non-Shared Memory Architecture          | . 15              |  |  |  |  |  |

|     |                                               | 3.2.1.              | Microcontroller Shared Memory Problem Example | . 17              |  |  |  |  |  |

|     |                                               | 3.2.2.              | MPU Setup                                     | . 17              |  |  |  |  |  |

|     |                                               | 3.2.3.              | Shortcomings                                  | . 18              |  |  |  |  |  |

|     |                                               | 3.2.4.              | Privilege Escalation                          | . 18              |  |  |  |  |  |

|     |                                               | 3.2.5.              | Summary                                       | . 19              |  |  |  |  |  |

|     | 3.3.                                          | Rese                | earch Motivation                              | . 20              |  |  |  |  |  |

|     |                                               | 3.3.1.              | Previos Project Work                          | . 21              |  |  |  |  |  |

| 4.  | Proi                                          | ect Sco             | ope                                           | 23                |  |  |  |  |  |

|     | 4.1.                                          |                     | blem Summary                                  |                   |  |  |  |  |  |

|     |                                               | 4.1.1.              | Memory Protection Schemes                     |                   |  |  |  |  |  |

|     |                                               | 4.1.2.              |                                               |                   |  |  |  |  |  |

|    |      | 4.1.3.  | Benefits                                                                  | 24 |

|----|------|---------|---------------------------------------------------------------------------|----|

|    |      | 4.1.4.  | Hardware Popularity and Generalization                                    | 24 |

|    | 4.2. | Rese    | earch Questions                                                           | 25 |

|    |      | 4.2.1.  | Question 1: How may memory contents be protected during vari-             |    |

|    |      |         | ous failure modes?                                                        | 25 |

|    |      | 4.2.2.  | Question 2: How may the improvements be made without harming              |    |

|    |      |         | performance?                                                              | 25 |

|    |      | 4.2.3.  | Summary                                                                   | 26 |

|    | 4.3. | Solu    | tion Roadmap                                                              | 26 |

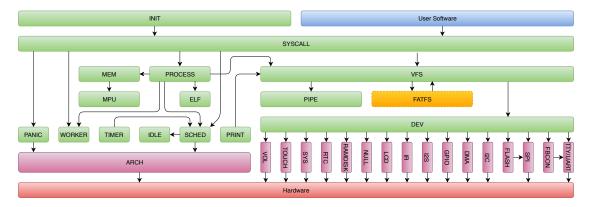

|    | 4.4. | Arch    | nitecture Overview                                                        | 27 |

|    |      |         |                                                                           |    |

| 5. | Men  | nory Al | location                                                                  | 29 |

|    | 5.1. | Allo    | cation Rules                                                              | 29 |

|    |      | 5.1.1.  | Allocation Rule Summary                                                   | 30 |

|    | 5.2. | Met     | adata Structures and Multibanking                                         | 31 |

|    | 5.3. | Allo    | cation Algorithm                                                          | 33 |

|    |      | 5.3.1.  | Algorithm Without MPU Support                                             | 33 |

|    |      | 5.3.2.  | Algorithm With MPU Support                                                | 36 |

|    |      |         |                                                                           |    |

| 6. | Prog | gram Lo | 5                                                                         | 41 |

|    | 6.1. | C C     | gram Structure                                                            | 41 |

|    | 6.2. | The     | ELF file format                                                           | 42 |

|    | 6.3. | Relo    | $cation  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 44 |

|    | 6.4. | Load    | d API Selection                                                           | 45 |

|    | 6.5. | Load    | l Procedure                                                               | 46 |

|    | 6.6. | Con     | text Switching                                                            | 48 |

|    |      |         |                                                                           |    |

| 7. | Add  | ing Pag |                                                                           | 50 |

|    | 7.1. | 0       | ng without Virtualization                                                 | 50 |

|    | 7.2. |         | ing Paging                                                                | 50 |

|    |      | 7.2.1.  |                                                                           | 51 |

|    |      | 7.2.2.  |                                                                           |    |

|    |      | 7.2.3.  |                                                                           |    |

|    |      | 7.2.4.  | Page Fault Handler                                                        | 57 |

|    |      | 7.2.5.  | Table Walking Algorithm                                                   | 58 |

|    |      | 7.2.6.  | Replacement Policy                                                        | 60 |

|    |      | 7.2.7.  | Miscellaneous Page Table Functions                                        | 60 |

| •  |      |         |                                                                           | ~~ |

| 8. |      |         | d Verification                                                            | 62 |

|    | 8.1. |         | nory Allocation                                                           | 62 |

|    |      | 8.1.1.  | Performance Considerations                                                | 62 |

|    |      | 8.1.2.  | Functionality Testing                                                     | 63 |

|    |      | 8.1.3.  | Test Subjects                                                             | 64 |

|    |      | 8.1.4.  | Methodology                                                               | 64 |

|    |      | 8.1.5. | Expected Results                                                                                                 |

|----|------|--------|------------------------------------------------------------------------------------------------------------------|

|    |      | 8.1.6. | Test Execution                                                                                                   |

|    |      | 8.1.7. | Discussion                                                                                                       |

|    |      | 8.1.8. | Conclusion                                                                                                       |

|    | 8.2. | Prog   | gram Loading                                                                                                     |

|    |      | 8.2.1. | Performance Considerations                                                                                       |

|    |      | 8.2.2. | Test Subjects                                                                                                    |

|    |      | 8.2.3. | Methodology                                                                                                      |

|    |      | 8.2.4. | Expected Results                                                                                                 |

|    |      | 8.2.5. | Test Execution                                                                                                   |

|    |      | 8.2.6. | Discussion                                                                                                       |

|    |      | 8.2.7. | Conclusion                                                                                                       |

|    | 8.3. | Pagi   | ng and Memory Protection                                                                                         |

|    |      | 8.3.1. | Performance Considerations                                                                                       |

|    |      | 8.3.2. | Test Subjects                                                                                                    |

|    |      | 8.3.3. | Methodology                                                                                                      |

|    |      | 8.3.4. | Expected Results and Test Execution                                                                              |

|    |      | 8.3.5. | Discussion                                                                                                       |

|    |      | 8.3.6. | Conclusion                                                                                                       |

|    | 8.4. | Sma    | ll System Use Case Example                                                                                       |

|    |      | 8.4.1. | Methodology                                                                                                      |

|    |      | 8.4.2. | Test Execution                                                                                                   |

|    |      | 8.4.3. | Results                                                                                                          |

|    |      | 8.4.4. | Discussion and Conclusion                                                                                        |

|    | 8.5. | Men    | nory Copy Speed Test                                                                                             |

|    |      | 8.5.1. | Methodology                                                                                                      |

|    |      | 8.5.2. | Expected Results                                                                                                 |

|    |      | 8.5.3. | Test Execution                                                                                                   |

|    |      | 8.5.4. | Discussion and Conclusion                                                                                        |

|    | 8.6. | Add    | ed Context Switching Overhead                                                                                    |

|    | 8.7. | Syst   | em Call Interface Overhead                                                                                       |

|    |      | 8.7.1. | System Calls                                                                                                     |

|    |      | 8.7.2. | Benefits and Limitations                                                                                         |

|    |      | 8.7.3. | Performance Study                                                                                                |

|    |      | 8.7.4. | Summary                                                                                                          |

|    |      |        |                                                                                                                  |

| 9. | Disc | ussion | 94                                                                                                               |

|    | 9.1. | Solu   | tion Discussion $\ldots \ldots $ 94 |

|    |      | 9.1.1. | Memory Allocation                                                                                                |

|    |      | 9.1.2. | Program Loading                                                                                                  |

|    |      | 9.1.3. | Paging Mechanism                                                                                                 |

|    | 9.2. | Rese   | earch Question Discussion                                                                                        |

|    |      | 9.2.1. | Research Question 1                                                                                              |

|    |      | 9.2.2. | Research Question 2                                                                                              |

| 10  | <b>~</b> | • •    |

|-----|----------|--------|

| 10. | Conc     | lusion |

|     |          |        |

| 11 | . Future     | Work 9                                                                                                                    | 9        |

|----|--------------|---------------------------------------------------------------------------------------------------------------------------|----------|

|    | 11.1.        | Memory Allocation Improvements                                                                                            | 9        |

|    | 11.2.        | Paging Improvements                                                                                                       | 9        |

|    | 11.3.        | Memory Sharing Schemes                                                                                                    | 9        |

|    | 11.4.        | Improved Standards Compliance                                                                                             | 0        |

|    | 11.5.        | Hardware Error Handling                                                                                                   | 0        |

|    | 11.6.        | Syscall Data Access Checking                                                                                              | 0        |

|    | 11.7.        | Moving Data Back Into Flash                                                                                               | 0        |

|    | 11.8.        | Test Procedures                                                                                                           | 1        |

|    | 11.9.        | Build Automation                                                                                                          | 1        |

|    | 11.10.       | Power Management                                                                                                          | 1        |

|    | 11.11.       | Kernel Security                                                                                                           | 1        |

|    | 11.12.       | General Operating System Development                                                                                      | 1        |

| Re | ference      | ns 10                                                                                                                     | 2        |

| Ар | pendice      | es 10                                                                                                                     | 4        |

| Α. | Supplie      | ed Archive 10                                                                                                             | 5        |

|    | A.1.         | Supplied Archive Structure                                                                                                | 5        |

|    | A.2.         | Code Licensing                                                                                                            |          |

| В. | Code I       | Listings 10                                                                                                               | 7        |

|    | B.1.         | Memory Allocation Test Code                                                                                               | 7        |

|    | DО           |                                                                                                                           |          |

|    | B.2.         | Shell Function for Program Execution                                                                                      | 0        |

|    | В.2.<br>В.3. | Shell Function For Program Execution10Crash Test Code10                                                                   |          |

|    |              | Sheh Function For Program Execution       10         Crash Test Code       10         Example Use Case Test Code       11 | 9        |

|    | В.З.         | Crash Test Code                                                                                                           | $9 \\ 3$ |

# List of Figures

| 2.1. | Overview of the address translation process                   | 6  |

|------|---------------------------------------------------------------|----|

| 2.2. | Overview of the address translation in a multi-process system | 8  |

| 2.3. | Memory allocation regions available                           | 12 |

| 2.4. | Memory allocation sub-regions available                       | 12 |

| 3.1. | Desktop vs. microcontroller memory systems                    | 16 |

| 4.1. | Overview of the system architecture                           | 27 |

| 5.1. | Fragmented memory due to allocation metadata                  | 30 |

| 5.2. | Memory fragmentation avoided by moving metadata               | 30 |

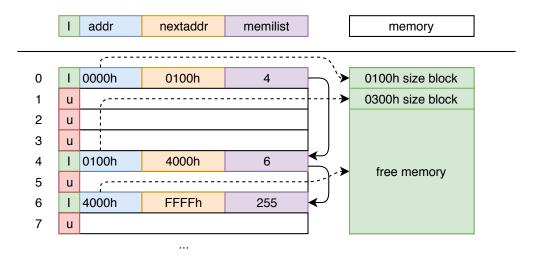

| 5.3. | Example of the memory list layout in memory                   | 32 |

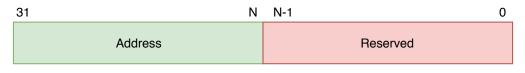

| 5.4. | Simplified Region Base Address Register                       | 36 |

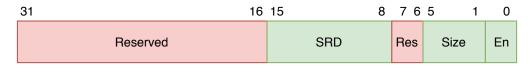

| 5.5. | Simplified Region Attribute and Size Register                 | 36 |

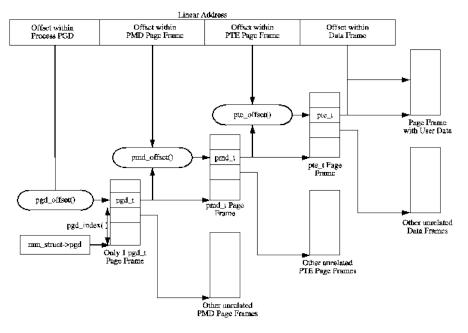

| 7.1. | Linux Page Table Layout $[1]$                                 | 51 |

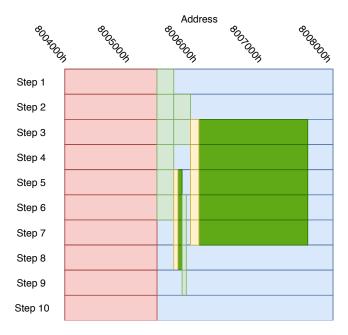

| 8.1. | Memory Allocation Test Progress                               | 67 |

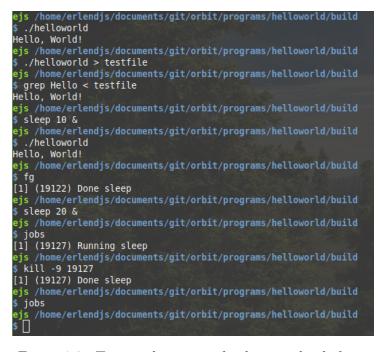

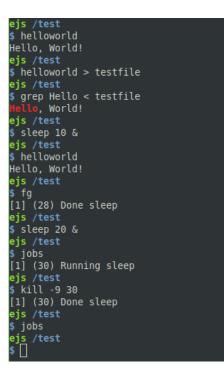

| 8.2. | Testing the process loading on the desktop                    | 71 |

| 8.3. | Testing the process loading on the microcontroller            | 72 |

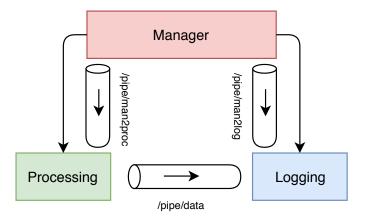

| 8.4. | Example Application Setup                                     | 80 |

# List of Tables

| 3.1. | Comparison of advantages in shared and non-shared memory systems | 15 |

|------|------------------------------------------------------------------|----|

| 3.2. | Allocated memory protection regions                              | 18 |

# List of Algorithms

| 1. | Top-level algorithm outline: MemAlloc    | 34 |

|----|------------------------------------------|----|

| 2. | Entry allocator: MemAllocEntry           | 35 |

| 3. | Memory deallocator: MemFree              | 35 |

| 4. | Top-level algorithm outline: MemAllocMPU | 40 |

| 5. | Simplified process loading procedure     | 47 |

| 6. | Memory management: SvcMemmanHandleMmap   | 55 |

| 7. | Memory management: SvcMemmanHandleMunmap | 57 |

| 8. | Memory management: PagerWalkHandle       | 60 |

# List of Listings

| 1.  | The dangerous vTaskDelay function                        | 19 |

|-----|----------------------------------------------------------|----|

| 2.  | Privilege escalation function                            | 19 |

| 3.  | The memory bank structure                                | 32 |

| 4.  | The structure used for MPU allocations                   | 37 |

| 5.  | The structures of the ELF file format                    | 43 |

| 6.  | Example structure of a program                           | 44 |

| 7.  | The posix_spawn function prototype                       | 46 |

| 8.  | The beginning of the ThreadControl structure             | 49 |

| 9.  | Restoring the MPU registers in assembly                  | 49 |

| 10. | The page table structures                                | 52 |

| 11. | The memory mapping functions $[2, 3]$                    | 53 |

| 12. | The PagerAddEntry and PagerCalculateMaxAddress functions | 56 |

| 13. | The DataAbort function                                   | 58 |

| 14. | The PagerWalk function                                   | 59 |

| 15. | The C copy function                                      | 85 |

| 16. | C Library implementation of the write function           | 89 |

| 17. | Assembly handler for the svc instruction                 | 89 |

| 18. | Kernel mode write call handler                           | 90 |

| 19. | Virtual file system write call handler                   | 91 |

| 20. | Device file system write call handler                    | 91 |

| 21. | Write function of /dev/null                              | 92 |

# Glossary

- **ABI** Application Binary Interface. 27

- **API** Application Programmer Interface. 19, 26, 27, 45, 46, 53, 70, 94–96, 98–100

- **CCM** Core-Coupled Memory. 31

CIA Confidentiality, Integrity, Availability. 14

CPU Central Processing Unit. 36, 42, 43

DFAR Data Fault Address Register. 77

**DFSR** Data Fault Status Register. 59

- DMA Direct Memory Access. 99

- **ECC** Error Correcting Code. 22

- **ELF** Executable and Linkable Format. 42

- GCC GNU Compiler Collection. 19

- **GNU** GNU is Not Unix. 42

- **IO** Input-Output. 69, 75

- **IoT** Internet of Things. 24

- **ISR** Interrupt Service Routine. 19

- **MMU** Memory Management Unit. 11, 46

- MPU Memory Protection Unit. 2, 10, 11, 13, 14, 16–18, 20, 21, 23, 24, 26, 28, 29, 33, 35–38, 48–54, 57, 59, 63–68, 73, 75, 78, 86, 87, 97

- **OS** Operating System. 27

- **PGD** Page Global Directory. 51

- **PID** Process ID. 46, 48, 52, 54, 58, 61, 74

- **PMD** Page Middle Directory. 51

- **POSIX** Portable Operating System Interface. 2, 13, 45, 46, 53, 69, 72, 94, 98

- **PTE** Page Table Entries. 51

**RAM** Random Access Memory. 18, 31, 75

**RASR** Region Attribute and Size Register. 36, 38, 53, 55, 64, 67

- **RBAR** Region Base Address Register. 36, 38, 49, 67

- **SRD** Sub-Region Disable bits. 36

- ${\sf SVC}$  Service Handler. 27

- **TLB** Translation Lookaside Buffer. 5

# 1. Introduction

In modern desktop and high-end embedded systems, application address spaces are separated from each other using memory protection hardware. The protection mechanisms are managed by the operating system, and applications may explicitly agree to share memory when desired. Hardware registers are only accessible to drivers that are given access by the Operating System. The hardware implements memory virtualization that enables each process to see the entire processor address space as its own, preventing them from accessing other applications memories. Paging is used to split the memory into smaller blocks called pages, which are assigned by the Operating System. Combined with virtualization, pages may be allocated, freed, moved, and swapped to slower storage as desired.

Microcontrollers are devices that embed the processor, memories and peripherals in a complete and small package. They power a large range of applications from alarm clocks to automotive entertainment systems and more. Due to their history in simple applications, memory management has been simple and memory protection unnecessary. As technology has evolved, however, both the microcontrollers and the software they run has grown. Modern microcontrollers typically embed a Memory Protection Unit, that enables protection for a few selected memory areas. Due to hardware complexity and cost, virtualization is typically not supported, and memory management is tedious. As a consequence protection is only used to protect programmer selected memory areas: good enough to detect serious faults, but not good enough to guarantee that a system will remain stable after a fault. Data loss is still likely, and due to the effort required to leverage the hardware, the protection features often remain unused.

# 1.1. Research Drivers

There are two main questions driving the research presented in this thesis. The first is about memory protection itself: how may the contents of a memory be protected during different failure modes? A memory may not just be different physical memories, but also logical blocks of memory within the same physical devices. Computer systems experience many different failures, with causes ranging from simple programmer errors to intentional security breaches or even hardware failures. The second research question relates to performance. How may improvements be made without harming performance? While performance impact may be measured, it is up to the application programmer to decide the acceptable limits of performance loss.

In the world of embedded operating system software, an overwhelmingly large majority of the systems that are certified to any notable safety standards are also proprietary and much too expensive for most applications. During the research phase of this thesis, no open source operating system that implements a restrictive memory protection scheme while also fitting inside the internal memories of the typical microcontroller were found, at least not in marketing material. Strict protection features appear to be a feature reserved for larger systems.

It is assumed that strict memory protection for Memory Protection Unit (MPU)enabled microcontrollers with less than a megabyte of memory is a new addition especially in the world of open-source software. This thesis continues with an implementation of a strict memory scheme using techniques borrowed from the desktop world, adapted for use in small systems where memory constraints, time to market, and predictability are important.

The work presented is mainly built upon techniques found in major open-source software such as the Linux kernel and open-source standards such as Portable Operating System Interface (POSIX) [4]. Using standards for application interfaces enables programmers to use existing knowledge, allowing for much quicker adaptation of the solution. It is also the intention for the solution to remain open-source so that it will be available to anyone that desires to use it.

# 1.2. Solutions

This thesis presents a solution that enables programs running on a microcontroller to be completely separated without added developer effort. In chapter 5, a memory allocator and deallocator is invented that manages memory at run-time while respecting the challenging limitations of the hardware. This allocator is the fundamental building block that enables the hardware protection features to be fully utilized at all times. Developers do not have to concern themselves with address calculations, alignment and register values any longer since the allocator handles everything seamlessly. This allocator provides the foundation for the other subsystems that build upon it, and makes it possible to answer the first research question.

A program loader is written and then presented in chapter 6 which is able to load multiple programs into memory and starts their simultaneous execution, using the allocator to ensure that they are separated. This ensures that the allocator and memory protection features are used at all times. By doing this at run-time, programs may be started, stopped, changed etc. at any time without interfering with other programs. Most importantly it enables a program to crash without compromising the system and other applications integrity. A monitoring program may then decide to act on the program crash and handle the error, for instance by restarting the problematic program and alerting the user. The loader follows the POSIX standard where possible providing a known programming interface for both starting programs and managing them.

At last a paging mechanism is invented which enables running software to allocate additional protected memory at run-time. The solution pushes the protection hardware to its limit by using free protection registers to implement a manually managed paging scheme. Since the pager pushes beyond what most microcontroller hardware is intended for, a very simple paging scheme is presented, sacrificing performance for simplicity. Using the pager is made completely optional ensuring that no performance is lost when it is not used.

# 1.3. Testing and Evaluation

Once all the sub-systems are described, testing and evaluation commences. The goals of the functional and performance testing is to assess how well the implementation satisfies the research questions, and how improvements may be made with continued work.

Performance of the various systems are evaluated with mathematical analysis, functional testing and discussion of the selected solution(s). The allocation subsystem is evaluated by looking at its time complexity properties, which is how it scales with the number of allocations. The design of the loader is evaluated by looking at its time characteristics. At last, some basic performance tests are made to see how the system fulfills its design goals and how it performs in practice.

# 1.4. Summary

Evaluation of the solutions show that the system is indeed able to accomplish strict memory protection with a limited performance impact. Software error may occur in one program without affecting unrelated programs and the system remains stable. Performance depends on the characteristics of the application: those that spend most of the time computing local data will experience very little performance loss, while those that make many system calls will experience more. This performance loss is inherent to the system call interface used as the bridge between individual programs. Programs making frequent system calls are tested to experience a 21 % to 28 % performance penalty depending on use of the pager.

The end solution is suitable for applications with needs that fall between high end microcontrollers and low end embedded Linux systems: where the basic features of a Linux system is often desired, but the hardware cost is not justifiable. By leveraging the solutions presented in this thesis high end microcontrollers will be able to serve these applications in a convenient and robust manner.

## 1.5. Thesis Structure

The thesis is structured into three main portions: getting a good understanding of the background material, the solutions themselves, and at last testing and evaluation of the presented solutions.

The first chapter is intended to bring a fundamental understanding of memory protection in current, competing and historical systems. This is contained in chapter 2, the background chapter.

Next, the related work chapter documents current software systems and their limitations. Since most of the systems that are likely to implement solutions comparable to the ones presented in this thesis are closed systems, and very expensive, making the scope of this background research somewhat limited. It is in any case assumed that an open source implementation is a great contribution to the world of microcontroller software, and so the work presented in this thesis is also open.

Chapter 4 formally describes the questions driving the research in the thesis. These are then referenced in the testing chapter in order to check how well they have been satisfied.

The second portion of this thesis are the chapters describing the solutions: Memory allocation in chapter 5, program loading in chapter 6 and at last paging in chapter 7. These all build upon each other creating an easy to use system that enforces strict memory protection between processes.

The last main portion of the thesis consists of testing, verification, evaluation and discussion of the solutions. Testing is mainly done to verify that the systems work according to intention and to check against the driving research questions. The tests also function as a showcase of what the system is able to accomplish in practical usage. At last a general discussion is made, potential improvements are suggested and a conclusion is made.

# 2. Background

In this section, we introduce the solutions employed in current systems. The various memory schemes used in desktop, mobile and microcontroller systems are briefly discussed. The challenges related to memory protection in microcontrollers are then discussed.

# 2.1. Memory Protection in Desktop Processors

In desktop computer systems, multiple programs are run at the same time sharing the processing units and available memories. Separating the memory accessible to these programs improves the stability, reliability and security of the system. This section provides a brief overview of how this is accomplished and the related challenges.

## 2.1.1. Overview

In modern desktop processors, process separation is achieved through memory virtualization and paging [5]. These two technologies are often used together but must not be confused: paging is a memory allocation scheme where memory is organized into blocks called pages, while virtualization is the translation of memory addresses.

When the modern processor needs to access memory the address is checked against a page table, which is cached by the processor in a Translation Lookaside Buffer (TLB). This table contains translation entries for translating virtual addresses that the processor uses to real memory addresses where the data is. With this technique each process sees the entire processor address space as its own, free of conflict, since the table is also swapped along with the process. Sharing memory can be achieved through setting an entry in multiple programs to the same physical address. Page sizes on modern x86 systems are usually a mix of 4KiB, 1MiB and even 1GiB.

Each entry in the table is marked as residing in real memory or not. If the running program accesses memory that is not located in real memory, the access triggers an exception that invokes the page supervisor. The page supervisor is part of the operating system and is responsible for fetching the data into memory from an indirectly accessible medium such as a hard drive, changing the table entry and resuming the program execution. With this technique it is possible to "simulate" more memory than what is physically installed. A similar exception occurs when the processor does not have the correct entry cached in the TLB. In those cases the supervisor will have to fetch the entry for it.

If the memory access was invalid, the operating system will not find the correct page neither on disk nor in main memory. An exception is then raised so that the offending program may handle the error gracefully or terminate.

In addition to virtualization the page table entries also contain the access rights of the page. Typical access rights are execute, read and write flags. Violating these rights will also trigger an exception similar to accessing invalid pages, allowing the fault to be handled.

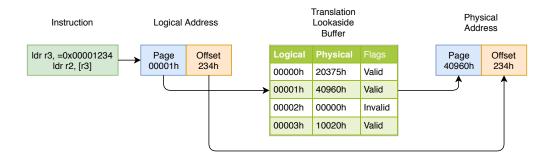

A simplified schematic of how the translation is performed is illustrated in figure 2.1. In this case the user program loads the address 0001234h into register R3 and loads the data word located at that address into register R2. Since the memory is virtualized, the address specified is not used directly. Instead, the address is divided into two parts: the page index and the page offset. The number of bits used in each directly correlates to the page size used which in this case is 4KiB. This gives the 12 bits for the offset and 20 bits for the page index which is used as input into the table. The physical page index is then taken from the table and used to assemble the final physical address with the original offset. Simultaneously, the access flags in the table is checked for any violations. In this example only the valid flag is shown.

Figure 2.1.: Overview of the address translation process

## 2.1.2. History

Memory virtualization goes back to the mainframe era of computing, when the main memory was composed of very expensive core memory. The size of these memories was in the thousands of words size range. Memory virtualization was then introduced as a means of simulating more memory through disk swapping, allowing machines configured with less memory to run more demanding programs. The NORD-1 made by Norsk Data was the first minicomputer to offer memory virtualization in the early 70s [6].

For the x86 processor architecture that is used in personal computers today, virtualized memory was first introduced with the Intel 80286 processor. The design used memory segmentation where each memory address was composed of a segment index and an offset into that segment. Multiple segments were used in the processor for program text, data, stack and 'extra' segment.

The Intel 80386 introduced paging in addition to segmentation. This added an additional level of address translation from the segmentation addresses to the real addresses providing virtualized memory like it is known today. With the 64-bit version of the x86 architecture, the segmentation is removed, providing a flat memory space with only paging and address translation.

## 2.1.3. Memory Architecture As Seen By Software

With virtualized memory, each process running on the system has its own address space. It can not see any data belonging to other processes. In order to communicate with the outside world the process uses system calls, a kind of software interrupt, to make the operating system perform simple tasks on behalf of the process. Examples of such tasks are reading key presses from the keyboard, writing a file or sending a packet on the network.

The operating system on the other hand has components that always operates in a privileged state. These software components are allowed to access all memory, which is necessary in order to perform system calls on behalf of processes among other tasks. The core component of the operating system which performs these tasks is often called the Kernel. The Kernel is responsible for starting the system and provide all the basic communication and cooperation primitives to build a functioning system. Examples are processor time scheduling, memory management, device drivers and file systems. Kernels are carefully written so that a process with malicious intent can not gain access to objects it should not have access to.

In some cases it is beneficial for programs to share memory directly, allowing communication to take place at the highest performance. The processes involved will then set up a shared piece of memory with the help of the Kernel, and the Kernel will then set entries in the page tables of both programs to the same piece of physical memory.

This kind of memory sharing is not always explicit. Since many programs often share the same code libraries, such as the standard C library and various graphics libraries, code segments may be shared between processes. In order to prevent one program from affecting another this code is then set to read-only execute permissions. The Kernel may also employ a copy-on-write scheme where an actual copy of the data is only made when the process with the intended copy does its first write. This approach helps making some operations significantly faster, such as 'fork'.

Desktop memory architecture is, therefore, non-shared by default, and sharing is then applied when desired. This may also be referenced to as a mixed memory architecture.

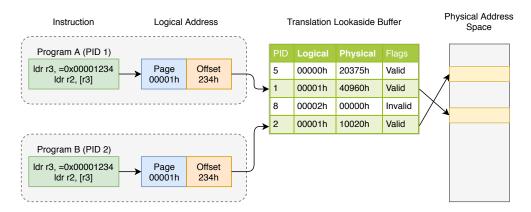

Figure 2.2 illustrates how the address translation takes place in a multi-process system. Here, two identical programs are run in parallel, each thinking it has the processor as its own using the same addresses. In reality the page table has different entries for the two program instances pointing the memory accesses to different parts of memory, allowing these initially conflicting programs to coexist.

Figure 2.2.: Overview of the address translation in a multi-process system

## 2.1.4. Challenges

In this section the quirks and challenges associated with paged memory are briefly discussed.

#### **Memory Fragmentation**

Memory fragmentation is a problem that may appear in systems where memory is frequently allocated and freed in various sizes, causing small fragments of free memory to reside between blocks that are in use. If these fragments can not be collected into continuous blocks when needed, new allocations may fail despite having enough memory since there is no continuous block large enough to satisfy the request.

The process of collecting these fragments is called *defragmentation*. In systems without virtualized memory, free or used blocks cannot be moved without direct cooperation with the programs that uses them. In systems *with* virtualized memory, physical memory may be defragmented by copying data to a new location and changing the translation in the page table. In the virtual address space holes may be present without any actual memory usage by simply not having entries in the page table for it. This memory is often referenced as reserved or committed memory by software tools.

Virtualization and paging provide a great deal of flexibility when dealing with fragmentation issues. For systems that support multiple page sizes, smaller pages may even be combined into larger ones for smaller page tables and more efficient cache usage.

#### Not Enough Memory

As previously discussed, having a small main memory may be compensated for by swapping pages to slower but larger storage. Swapping enables computers with too little memory to complete its task at the cost of performance. Disk swapping requires a form of virtualized memory with paging allowing the swapping to appear transparently to the affected program. Without virtualization, the capacity of the computer's main memory will impose a hard limit on the software memory usage. Since memory fragmentation is likely to occur without virtualization, out-of-memory errors may even occur before the memory resources are exhausted.

#### **Non-Deterministic Performance**

With paged virtualized memory the translation vectors has to be stored somewhere. Since the page tables are often large, the processor itself only contains a small cache of the most recently used entries. This cache is called the Translation Lookaside Buffer (TLB). When a program accesses some memory that is not in the cache the operating system is invoked so that it may fill the table with the correct entries. Fetching these entries takes time. If the requested memory was in real memory but not in the cache, the penalty may only be in hundreds of cycles. If the memory was swapped to disk however the penalty may be in millions of cycles, as hard drives have to position the read and write mechanism physically on the platters before reading data.

This introduces some randomness into the fine timings of the programs as the times when these events occur are hard to predict. In larger systems where bulk computing performance is what matters and some timing jitter is accepted, other benefits outweigh that of deterministic performance.

Some systems, such as the Xilinx Zynq UltraScale+ [7], combine processors with and without virtualized memory to gain the benefits of both. Timing sensitive software is then run on the processor without virtual memory while general higher-throughput computing is done with processors that offer virtual memory.

#### Page and Disk Thrashing

Thrashing is a phenomenon that happens when a page is evicted from either the page cache or main memory only to be brought back in again shortly after. The underlying cause is if the cache or memory is way too small causing most of the processing time to be spent on solving page faults.

Such problems are usually solved by upgrading the machine with more memory or a larger page cache. In some cases the running program may be altered so that its memory accesses are more suitable, however this is often not possible or too difficult. Thrashing often indicates that a machine is running programs with requirements beyond its capabilities.

## 2.2. Memory Protection in Microcontrollers

In this section, the memory protection hardware found in microcontrollers is discussed briefly. This provides a basis for comparison against the desktop methods and an understanding of its limitations.

## 2.2.1. History

The first microprocessors developed in the early 70s required multiple external components to function, such as memories and input-output devices. The increased cost made the microprocessor unsuitable for use in many simple appliances.

The microcontroller integrates a simple processor and all the required components in a single chip. A typical configuration in an early chip would be an 8-bit processor, a few kilobytes of read-only program memory and a handful of bytes for the working memory. This small configuration is sufficient for simple applications such as alarm clocks, microwave ovens and computer keyboards. The 8-bit microcontrollers still hold a significant market share, as they are the simplest to produce for use in simple appliances.

Other uses, such as audio/video processing and advanced control systems in cars and industry equipment has provided a market for more advanced microcontrollers as well. In 2011, the market share of 16-bit microcontrollers grew past the 8-bit market share for the first time [8]. Increased demand for Internet connectivity in many applications as well as intelligent car systems has also given rise to 32-bit microcontrollers. These 32-bit parts share many architectural aspects with their desktop counterparts, with the main differences now being computer power and memory capacity.

The early microcontroller applications did not require any memory protection or special safety hardware due to the low software and application complexity. With the increased use in automobile, industrial and internet-enabled applications, attention has shifted towards security-, reliability- and safety-features. As desktop and embedded processors converge, microcontroller processors has been enhanced with basic memory protection features.

### 2.2.2. Microcontroller Memory Protection

Memory protection in Cortex-M [9] and Cortex-R [10] microcontroller processors are implemented in a special MPU. The MPU monitors all memory accesses done by the CPU and checks that they are legal by looking in a table initialized by the programmer. Each table entry contains the address range and access rights of a memory "region". The memory address to be accessed is used as the table key, and the access type is compared to the table entry. The access type specifies if the access is part of an instruction fetch or a regular data load/store, and the privilege level of the access. If the table entry is in conflict with the access type, an instruction abort exception is triggered in case of an instruction fetch, or a data abort exception is triggered in case of data accesses.

#### 2.2.3. Table Size and Table Entry Restrictions

The table inside the MPU has a fixed size which depends on the options selected by the silicon manufacturer. Typical configurations are either 8, 12 or 16 table entries. The application programmer may choose to use less than the available number of entries, however if more is desired, a software mechanism that swaps regions on an abort exception has to be implemented.

Furthermore, each table entry has limits on the size and alignment of a memory region. The MPU hardware used in Cortex-M/R processor requires that the size of the region is in a power of two and that the base address of the region is aligned to the same power of two. Each region has eight sub-regions that is one-eight the size of the full region, each with a sub-region disable bit, allowing some flexibility during region allocation.

The most significant difference between the MPU and the desktop Memory Management Unit (MMU) counterpart is the lack of virtualized memory. That is, there is no translation of addresses allowing each process to see its own memory address space. They all have to coexist within the same address space, and must not be dependent on being located at a specific address.

As discussed in section 2.1.4 virtualized memory may be used to simulate more memory via disk swapping. In embedded systems without virtualized or paged memory, it is not possible to pretend to have more memory than one already has without extreme performance penalties. When the software reaches the point where the main memory is full or too fragmented no further requests can be fulfilled. The software will then have to manage its memory more carefully or terminate.

It is also not possible to defragment memory after allocation, or to have smaller fragments appear as a continuous page by using multiple translation entries as discussed in section 2.1.4. The effect is that software may run out of memory despite enough being technically available, since there is no single portion large enough to fulfill the request.

As discussed in section 2.1.4, virtualized memory is likely to add randomness to the fine timings of a program. Embedded software that has to respond and act on interrupts within a small set of machine cycles can not accept such non-deterministic performance, which is one of the reasons why virtualized or paged memory is not used for such systems.

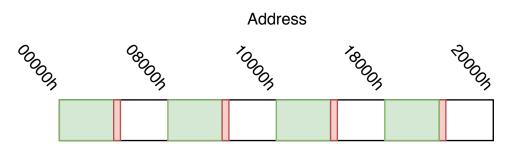

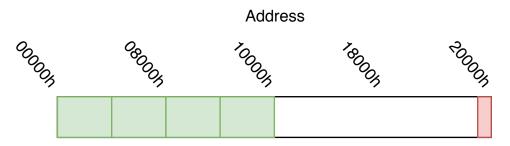

### 2.2.4. Allocation Example

In this section, an example is provided for an allocation of 35000 bytes. A memory allocation of 35000 bytes requires a region allocated to the nearest power of two, rounded up. This resolves to  $2^{16} = 65,536$  bytes, an over-allocation of 30,536 bytes or 87%. The eight sub-region disable bits may be used to reduce the amount of wasted space. With a region size of  $2^{16}$  bytes a sub-region is  $2^{13} = 8192$  bytes. Now using the sub-region size, a total of five continuous sub-regions is required to fulfill the request. The allocation is now 40,960 bytes, an over-allocation of 17%.

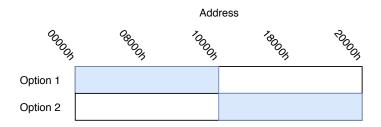

Figure 2.3.: Memory allocation regions available

Figure 2.4.: Memory allocation sub-regions available

Figure 2.3 illustrates the two regions that may be used for a region size of  $2^{16}$  bytes and a total memory size of  $2^{17}$  bytes. The blue marked area represents a region while the white area is untouched memory. Figure 2.4 illustrates the set of working subregion configurations that may be used, enhancing the detail of figure 2.3. The blue fill is replaced by eight blocks representing the sub-regions where green is the active subregions and red is the disabled sub-regions. The allocation algorithm must then find a free memory block that can be protected using any one of these configurations. In order to prevent unintended access from later allocations, the entire 40,960 byte block must be reserved despite only needing 35,000 bytes.

As made clear by figure 2.4 there are some missing combinations, where the green blocks would span the center of the memory box. This would however require either two 64KiB regions with the sub-regions split among them, or one 128KiB region spanning the entire memory. The trade-off in the first case is that two regions are used on a system that may only have eight regions available. In the second case, the sub-region size is now twice as large, causing an even greater over-allocation.

# 3. Related Work

Existing operating systems in the desktop world has made heavy use of memory protection schemes since the Intel 386 processor launched, although adaptation was rather slow. Certain systems such as Linux has been built with these features incorporated from the very beginning [11]. Mainframe systems have used such techniques from even earlier on. Aggressive memory protection in itself is, therefore, nothing new. This provides a huge amount of material that may be used to understand the techniques involved and ways to solve the problems of memory management.

Deeply embedded systems is however much different. As detailed later in section 4.1, the hardware necessary for the high-performance solutions often associated with desktop systems is too expensive for deeply embedded systems. The hardware is however able to perform many tasks just like its bigger brothers, but due to the complexity of getting around the hardware limitation, it is rarely used to its fullest.

In the world of embedded operating system software, an overwhelmingly large majority of the systems that are certified to any notable safety standards are also proprietary and much too expensive for most applications. During the research phase of this thesis, no open source operating system that implements a restrictive memory protection scheme while also fitting inside the internal memories of the typical microcontroller were found, at least not in marketing material. Strict protection features appear to be a feature reserved for larger systems. However, systems that takes different approaches to memory protection does exist, such as [12], [13] and [14].

It is assumed that strict memory protection for MPU-enabled microcontrollers with less than a megabyte of memory is a new addition especially in the world of open-source software. This thesis continues with an implementation of a strict memory scheme using techniques borrowed from the desktop world, adapted for use in small systems where memory constraints, time to market, and predictability are important.

The work presented is mainly built upon techniques found in major open-source software such as the Linux kernel and open-source standards such as POSIX [4]. Using standards for application interfaces enables programmers to use existing knowledge, allowing for much quicker adaptation of the solution. It is also the intention for the solution to remain open-source so that it will be available to anyone that desires to use it.

# 3.1. State of the Art

Microcontroller software and tools are still made and used much like in their 8-bit days. By default, a software package is compiled as a monolithic application using trusted software libraries and stored entirely in the internal ROM. The memory protection hardware is not used in these applications, and in the case of internet connected applications, this may pose a security threat. One example of a product hacked through memory exploits is the hack of the Amazon Dash Button, which allowed code to be injected and executed for a complete memory dump [15]. The hack was done by exploiting a buffer overflow bug that allowed arbitrary fragments of code to be executed from the buffer. By performing a complete memory dump using injected code, an attacker is then able to fully reverse engineer the application and uncover any secrets located in internal memory such as cryptographic keys and any other valuable information.

In applications that require a higher degree of security, reliability or safety, the MPU is used to protect selected sensitive areas in memory. This protects these areas from unintended or unauthorized access and enables any occurrences of such to be handled as any other invalid access and trigger an interrupt. Security (Confidentiality, Integrity, Availability (CIA)) is improved by restricting access by unauthorized code to certain areas. Code that attempts the access may be stopped and the user may be alerted. Reliability is improved as accidental errors are caught and handled. By preventing the fault from escalating into undefined behaviour, important data may be salvaged before a reboot, or the application may even be able to continue normally. Safety is improved in a much similar way by preventing undefined behaviour. In safety-critical applications, unexpected or unknown errors are often handled by entering a special safe mode to prevent any damages.

The end result is a mostly shared memory architecture combined with non-shared memory architecture where desired. This mix is due to the program instructions residing in a single block of memory without strict separation between tasks by default, and then applying access restrictions selectively in desired areas. This use of the MPU is a joint effort between the threading library providing any default protection and the end application programmer setting up additional protection regions as desired. An example is discussed in section 3.2.1. The main advantage of this setup is that errors causing malicious or unintended access to the enabled regions will be caught by the hardware which will trigger an interrupt. By handling this interrupt properly, a graceful restart may be executed or the product may enter a special safe mode.

On the other hand, setting up regions selectively in bare-metal applications requires much more effort by the application programmer for it to have any good effect. In particular, separating stacks and individual instruction memories for different threads pose a big challenge due to the limitations of the MPU as discussed in section 2.2.3. For each group of memory that is to be accessed by the same executing thread with the same privilege, an aligned memory containing the data has to be set up, and the table has to be altered properly when changing threads. If a thread is allowed write access to another threads memory through shared regions, a bug in one may appear as a crash in another or go completely unnoticed. For security applications, even read only access may pose a significant threat. These disadvantages are inherent to shared memory architecture. Developing with explicitly set memory protection involves a tradeoff between development cost and benefits.

# 3.2. Shared vs Non-Shared Memory Architecture

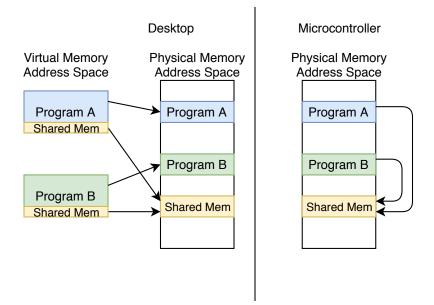

In this section, the virtualized memory approach used in desktop processors and the shared memory system typical to microcontrollers is compared directly. The shared memory architecture for the microcontroller used in this comparison is the architecture typically found in FreeRTOS ports, in particular the port for the Texas Instruments TMS570 microcontroller. The virtualized memory approach for the desktop is the type found in Linux and Windows systems.

It is important to note that a shared memory architecture in the microcontroller is typically system wide, and not just between individual programs that explicitly agreed upon the sharing. In the desktop world, each process is given its own non-shared address space using memory virtualization technology, with sharing applied when needed. Note that virtualization is not the same as shared or non-shared memory architecture, but a means to achieve it with relative ease and automation by the operating system.

Table 3.1.: Comparison of advantages in shared and non-shared memory systems

|                                                              | Desktop | Microcontroller |

|--------------------------------------------------------------|---------|-----------------|

| Shared instruction memory between user programs <sup>1</sup> | Yes     | No              |

| Crash detection rate                                         | Strong  | Weak            |

| Crash recovery success rate                                  | High    | Medium          |

| Protection of hardware registers                             | Yes     | Yes             |

| $TLB/Memory region entries^2$                                | 64 +    | 8 - 16          |

| Virtualized memory <sup>3</sup>                              | Yes     | No              |

| Live memory defragmentation possible                         | Yes     | No              |

| Simulation of more memory possible                           | Yes     | No              |

|                                                              |         |                 |

<sup>1</sup> Shared memory can be explicitly agreed upon in desktop systems. In some cases, such as with shared software libraries, code memory is shared by the operating system automatically.

<sup>2</sup> Processors store the entries in a cache that is managed by the operating system. Although technically possible in microcontrollers, this is not done.

<sup>3</sup> Enables memory defragmentation and simulating more memory.

In table 3.1, crash detection rate and crash recovery success rate relates to the ability of recovering from bugs causing undefined behaviour. These are typical programmer errors and in the case of memory management a runaway program may end up accessing memory it is not allowed to. Because memory is normally non-shared in the desktop memory architecture, the potential damages are limited. The detection and recovery rate is high. In the typical microcontroller implementation, however, the memory is by default shared. This opens up small windows where a bug may go undetected and cause damage to other programs or tasks. Protection of hardware registers refers to the ability to protect the hardware accesses itself, which is in direct control of sensors and actuators. In both systems these registers are often the most important asset to protect since modifications will affect the real world directly.

The number of memory region entries is the size of the table physically located in the processor. In desktop systems, this table is a cache for a much bigger table located in main memory. This is not the case for microcontroller systems, usually only a few of the regions are set permanently for the entire run-time of the application and then some are swapped during context switches. Although it is technically possible to use microcontroller hardware as a software-managed cache, this is not done.

Having memory virtualization technology or not is the main architectural difference between desktop systems and microcontroller systems. Although virtualization is not synonymous with shared or non-shared memory architecture, it enables the memory architecture in desktop systems by providing the necessary hardware mechanisms for an efficient implementation. In addition it makes live memory defragmentation and simulation of more memory possible. Despite its usefulness it is not implemented in microcontrollers due to hardware cost and complexity reasons. Most applications does not strictly need it either since they are still of low complexity when compared to most desktop software.

Many embedded applications does, however, benefit from memory protection. The MPU hardware implements protection mechanisms without virtualization, which is then used in applications where this is important.

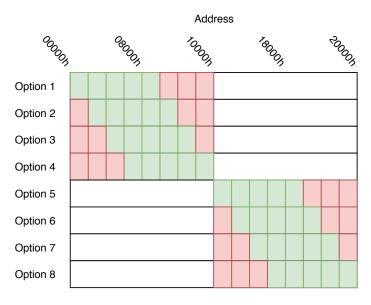

Figure 3.1.: Desktop vs. microcontroller memory systems

Figure 3.1 illustrates how the memory addressing is different in the two systems. The desktop system employs virtual memory and each of the programs reside in their own

virtual world, which is translated to the physical address space. The shared piece of memory is stored only once in the physical memory but mapped to each virtual memory space. In the microcontroller system both programs and data are located in the same address space and accesses the shared block using the same addresses.

Note that figure 3.1 does not show memory *protection*, which applies to both the left and right part of the illustration: In the desktop version it comes with the virtualization, while in the microcontroller version three MPU protection regions may be set for the memory blocks.

#### 3.2.1. Microcontroller Shared Memory Problem Example

As previously discussed, the default shared memory architecture with selective restrictions applied in microcontroller applications has weaknesses due to the sharing. In this section, the memory protection scheme implemented in a known microcontroller software is discussed as a practical example. The software is the TMS570 Cortex-R port of FreeRTOS. Although the port applies to only this line of processors, the weaknesses discussed are relevant to all software designed for the Cortex-M and Cortex-R processors that also makes use of memory protection in a similar fashion.

## 3.2.2. MPU Setup

In the TMS570 Cortex-R port of FreeRTOS, the kernel functions are put in a special section called kernelTEXT, placed in the first 32 kilobytes of persistent flash memory. This makes it extremely easy to allocate an MPU region to protect it against illegal accesses: the code is aligned to the first 32 kilobytes and the size is a power of two. This region is set up this way regardless of how much memory is actually required. It may be tweaked by the application programmer for efficiency. When a new task is set up, regions are initialized as in table 3.2. Regions 0 - 3 and 11 are set once on startup as default regions, while regions 5 and 6 are set in context switches and are per-task specific.

The memory type refers to the kind of memory protected: flash for the internal persistent flash storage where the program and read-only data is stored, RAM for the volatile storage, peripheral for the microcontroller peripherals and system for internal system hardware such as clock generators.

The address and size is the absolute physical address in memory where the region is allocated.

The user, privileged and execute columns describe the access rights for the regions. User refers to the execution of software with the lowest execution privilege while privileged refers to privileged software such as the operating system. The execute column decides if the contents is executable or not and applies to both execution contexts.

| Region number | Type       | Address    | Size              | User | Privileged | Execute |  |  |

|---------------|------------|------------|-------------------|------|------------|---------|--|--|

| 0             | Flash      | 0x00000000 | 4MB               | RO   | RO         | Yes     |  |  |

| 1             | Flash      | 0x00000000 | 32 KB             | NA   | RO         | Yes     |  |  |

| 2             | RAM        | 0x0800000  | $512 \mathrm{KB}$ | RO   | RW         | Yes     |  |  |

| 3             | Peripheral | 0xF0000000 | $256 \mathrm{MB}$ | RW   | RW         | No      |  |  |

| 5             | RAM        | 0x0800000  | 512KB             | RW   | RW         | Yes     |  |  |

| 6             | RAM        | 0x0800000  | 4KB               | NA   | RW         | No      |  |  |

| 11            | System     | 0xFFF80000 | 512KB             | RO   | RW         | No      |  |  |

Table 3.2.: Allocated memory protection regions

Legend: RO - Read Only, RW - Read and Write, NA - No Access

In short, a normally created task will have read/execute permissions to flash and read/write/execute permissions to Random Access Memory (RAM), excluding the regions allocated to the kernel. It will also have read/write access to all peripherals and read access to system modules, as well as all other threads and processes running on the system. Since the FreeRTOS kernel is extremely simple, access to all drivers, file systems etc. is also shared.

#### 3.2.3. Shortcomings

There are some shortcomings with the memory protection approach used in the port. Most importantly, individual tasks are not separated from each other as they have exactly the same permissions. The most dangerous problems are read/write access to all peripherals by all tasks and each others memories. The problem of individual task separation is possible to address by some extent by removing region 3 from the table and using xTaskCreateRestricted for specifying region 5 and 6 manually. Unfortunately region 5 is reserved for stack usage leaving only one region to the user for either peripherals or normal memory. Overcoming this limitation would require modification of the context switch. By default, the MPU is not used to detect stack overflows.

#### 3.2.4. Privilege Escalation

Since all FreeRTOS functions are located in the protected kernelTEXT section, precautions have to be taken in order to call them. This constraint applies to all FreeRTOS functions including the very basic delay function vTaskDelay. In order to perform such function calls, the privilege of the calling task is temporarily escalated by the use of a special system call called prvRaisePrivilege, permitting it to call into the protected kernelTEXT section. This system call sets the processor mode in the Saved Program Status Register and returns the old state, which is restored after calling into the protected section by using a separate system call. This is implemented as a macro called portRESET\_PRIVILEGE which internally calls portSWITCH\_TO\_USER\_MODE. The code for the delay function is shown in listing 1.

```

1 void MPU_vTaskDelay( const TickType_t xTicksToDelay )

2 {

3 BaseType_t xRunningPrivileged = prvRaisePrivilege();

4 vTaskDelay( xTicksToDelay );

5 portRESET_PRIVILEGE( xRunningPrivileged );

6 }

```

#### Listing 1: The dangerous vTaskDelay function

This example code overrides the original vTaskDelay using a macro to implement privilege escalation before calling the actual vTaskDelay

The privilege escalation handler does not check that the caller is indeed allowed to do so. From a security perspective this is extremely bad as any code could call it and even escalate its privilege permanently. In the ideal state the protected functions would have to be called from within the service call handler and check that the operation is permitted before performing any actions. The current approach, although flawed, is still useful as it will help detect programming errors and failures when used properly since it can detect accidental memory violations but not deliberate ones. The use of privilege escalation instead of system calls relates to FreeRTOS not accepting calls from within Interrupt Service Routine (ISR)s, as it will not be able to context switch in that state.

Since the privilege functions may be called from anywhere, it is possible to use it in user code as shown in listing 2.

```

1 void DoEvil (void)

2 {

3 prvRaisePrivilege ();

4 ApplyFullCarThrottle ();

5 }

```

#### Listing 2: Privilege escalation function

If an attacker is able to inject code that calls into the prvRaisePrivilege function the attacker will have access to the entire system. This assumes that the location of the injected code is executable, which also is the case in the discussed port.

## 3.2.5. Summary

Denying access to other tasks memory is possible using the FreeRTOS Application Programmer Interface (API). All memory used by a specific task would have to be placed either on the stack or in a separate and aligned section using the GNU Compiler Collection (GCC) \_\_attribute\_\_ mechanism. Region 6 would then be set to this section with region 5 for the stack. Tasks would then only have write permissions to their own memories. Using this approach would introduce additional requirements to the end application programmer, forcing everyone to understand and use the MPU, a great disadvantage. Additionally every task would still have read and execute permissions to most memory locations.

Overcoming all of these obstacles would require all tasks to have their code and data in separate and properly aligned memory sections. An implementation of such separation in a completely custom OS by the use of process loading and relocation is discussed in chapter 5 and onwards.

# 3.3. Research Motivation

The Orbit student organization at NTNU intends to build a small CubeSat satellite and launch it into orbit. Its purpose will be to display images on a small screen and then take pictures of the screen with the earth in the background. Although this task may seem simple enough, robust and fault tolerant systems are needed due to space radiation effects causing spurious faults. Furthermore, the lack of physical access once launched requires a robust solution since loss of communication may cause total loss of the satellite.