Magnus Øverbø

# Cryptanalysis of Irregularly Clocked LFSR

using approximate RBP search on FPGA

Master's thesis in Masters of Science Information Security: Technology

Supervisor: Prof. Slobodan Petrovic

June 2019

### Magnus Øverbø

## Cryptanalysis of Irregularly Clocked LFSR

using approximate RBP search on FPGA

Master's thesis in Masters of Science Information Security: Technology Supervisor: Prof. Slobodan Petrovic June 2019

Norwegian University of Science and Technology Faculty of Information Technology and Electrical Engineering Department of Information Security and Communication Technology

#### **Preface**

This Master's thesis in AIMT at NTNU was carried out during the spring semester of 2019 with Prof. Slobodan Petrovic as supervisor. Prof. Petrovic started this research[1] on the theoretic background of using approximate search as a method for obtaining the Levenshtein distance between two bit sequences of unequal lengths. Then utilise this in the generalised correlation attack[2] to recover the initial state of the irregularly clocked Linear Feedback Shift Register (LFSR).

The topic of this thesis is to assess the practical implementation of this method on Central Processing Unit (CPU) and Field-Programmable Gate Array (FPGA) using an unconstrained Approximate Row-wise Bit-Parallel (ARBP) search[1] using the shift-AND algorithm developed by Baeza-Yates and Gonnet[3].

The reader's background in this thesis is assumed to be familiar with computer architecture and logic operations in electronic circuitry. These aspects are explained, but familiarity is still expected.

Magnus Øverbø 2019-06-01

## Acknowledgement

A special thanks to Prof. Slobodan Petrovic for the guidance, supervision and feedback provided throughout the thesis.

Thanks to Mr. Høgli for reviewing my draft.

Magnus Øverbø

#### **Abstract**

Cryptanalysis on a cipher system the utilising 0/1 clocking Binary Rate Multiplier (BRM) as the keystream generator renders Siegenthaler's classical correlation attack[4] unusable since the output sequence and the undecimated bit sequence generated by the irregularly clocked Linear Feedback Shift-Register (LFSR) are of different lengths. Instead, by utilising the generalised correlation attack developed by Golic and Mihaljevic[2] the Levenshtein distance between the two sequences can be utilised as the basis for correlation.

In this thesis, we explore the application of implementing an unconstrained Approximate Rowwise Bit-Parallel (ARBP) search, using Wu and Manber's shift-AND algorithm[5], to obtain the Levenshtein distance between the ciphertext and the undecimated bit sequence of the irregularly clocked LFSR as the correlation metric. Our findings shows that the FPGA will perform better than a Central Processing Unit (CPU) implementation, as it operates with constant mean execution time, estimated by  $T_{tot} = R_{ops} \times 4f$ . Where  $R_{ops}$  represents the number of search state values which must be updated throughout the search, and f is the FPGA designs clock rate.

The CPUs processing time is shown to be of linear growth, based on the length of the search word as given by its periodic increase by a factor of  $\lceil \frac{M}{w} \rceil$ , where M is the search word length, and w is the size of the CPUs machine word.

However, overall the time required for processing a real-world cipher system using Field-Programmable Gate Array (FPGA) requires a large amount of resources. Even a feedback polynomial of L=32, with M=1024 and a clock rate of f=2.39GHz will require 43 days to complete, while M=4096 would require 695 days to complete. Even so, given 700 FPGAs running simultaneously a search can be completed within a day at the cost of the additional FPGAs needed, making it possible given enough resources are available.

#### **Contents**

| Pr  | eface   | !                                                                                                             | ii |

|-----|---------|---------------------------------------------------------------------------------------------------------------|----|

| Ac  | knov    | <b>vledgement</b> i                                                                                           | ίv |

| Ab  | strac   | <b>2t</b>                                                                                                     | v  |

| Co  | nten    | ts                                                                                                            | vi |

| Lis | st of l | Figures                                                                                                       | ix |

| Lis | st of ' | Tables                                                                                                        | X  |

| Lis | stings  | S                                                                                                             | хi |

| 1   | Intr    | oduction                                                                                                      | 1  |

|     | 1.1     | Background                                                                                                    | 1  |

|     | 1.2     | Related Research                                                                                              | 1  |

|     | 1.3     | Scope of the thesis                                                                                           | 3  |

|     | 1.4     | Contributions                                                                                                 | 3  |

|     | 1.5     | Research Questions and Hypothesis                                                                             | 3  |

|     | 1.6     | Thesis Outline                                                                                                | 4  |

| 2   | Cry     | ptanalysis of irregularly clocked LFSR using ARBP search                                                      | 5  |

|     | 2.1     | Stream Ciphers                                                                                                | 5  |

|     | 2.2     | Linear Feedback Shift Registers                                                                               | 5  |

|     |         | o de la companya de | 6  |

|     | 2.3     | Cryptanalysis                                                                                                 | 7  |

|     |         | 2.3.1 The Brute-Force Attack                                                                                  | 8  |

|     |         | 2.3.2 Generalised Correlation Attack                                                                          | 8  |

|     | 2.4     | Search                                                                                                        | 9  |

|     |         | 2.4.1 Bit-Parallelism and Bit-operations                                                                      | 9  |

|     |         | 2.4.2 Finite Automaton                                                                                        | 0  |

|     |         | 2.4.3 Bit-Parallel Search                                                                                     | 1  |

|     |         | 2.4.4 Exact Bit-Parallel Search using Shift-AND                                                               | 3  |

|     |         | 2.4.5 Approximate Row-wise Bit-Parallel Search                                                                | 3  |

|     |         | 2.4.6 Constrained vs Unconstrained Search                                                                     | 4  |

|     | 2.5     | Central Processing Unit                                                                                       | 5  |

|     | 2.6     | Field-Programmable Gate Array                                                                                 | 6  |

|     |         | 2.6.1 FPGA Development Methodology                                                                            | 8  |

|     |         | 2.6.2 FPGA Design Debugging                                                                                   | 9  |

|     | 2.7     | Universal Asynchronous Receiver-Transmitter                                                                   | 9  |

| 3   | Met     | hodology                                                                                                      | 2  |

|    | 3.1   | Research methodology                       | 22        |

|----|-------|--------------------------------------------|-----------|

|    | 3.2   | Experiment                                 | 22        |

|    | 3.3   | Data analysis                              | 23        |

|    | 3.4   | Software Development                       | 23        |

|    | 3.5   | Problems and Limitations                   | 24        |

|    |       | 3.5.1 Bias                                 | 24        |

| 4  | Imp   | lementation                                | 25        |

|    | 4.1   | CPU Implementation                         | 25        |

|    | 4.2   | FPGA implementation                        | 28        |

|    |       | 4.2.1 BRAM module                          | 28        |

|    |       | 4.2.2 UART module                          | 29        |

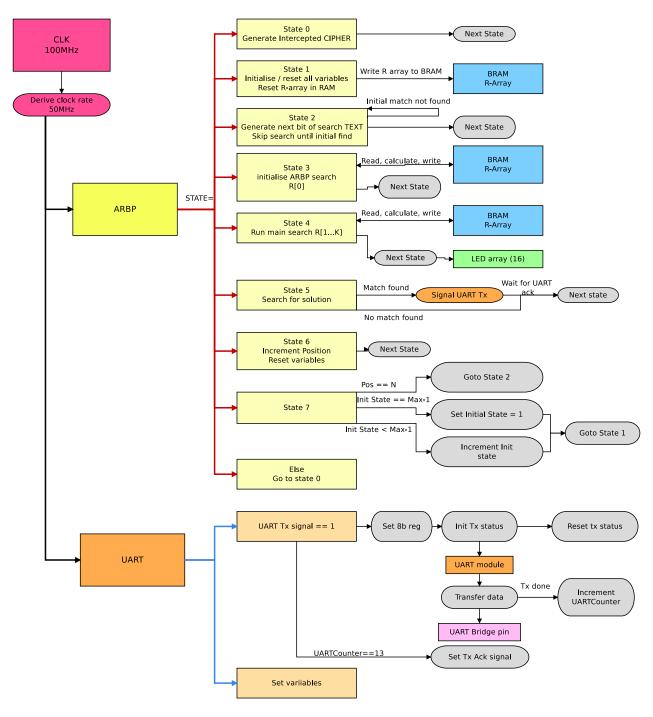

|    |       | 4.2.3 Ciphersearch Module                  | 30        |

|    | 4.3   | Testing methodology                        | 33        |

|    |       | 4.3.1 FPGA                                 | 33        |

|    |       | 4.3.2 CPU                                  | 34        |

|    | 4.4   | Assessment of variables in data collection | 34        |

|    |       | 4.4.1 Data transfer / Output timing issue  | 35        |

|    |       | 4.4.2 Preamble generation                  |           |

| 5  | Resu  | ılts                                       | 38        |

|    | 5.1   | Data gathering                             | 38        |

|    | 5.2   | Data set                                   | 39        |

|    |       | 5.2.1 Data set Internal validity           |           |

| 6  | Ana   | lysis                                      | <b>42</b> |

|    | 6.1   | Foundation for analysis                    | 42        |

|    |       | 6.1.1 Further analysis                     | 42        |

|    | 6.2   | Initial analysis of data                   | 43        |

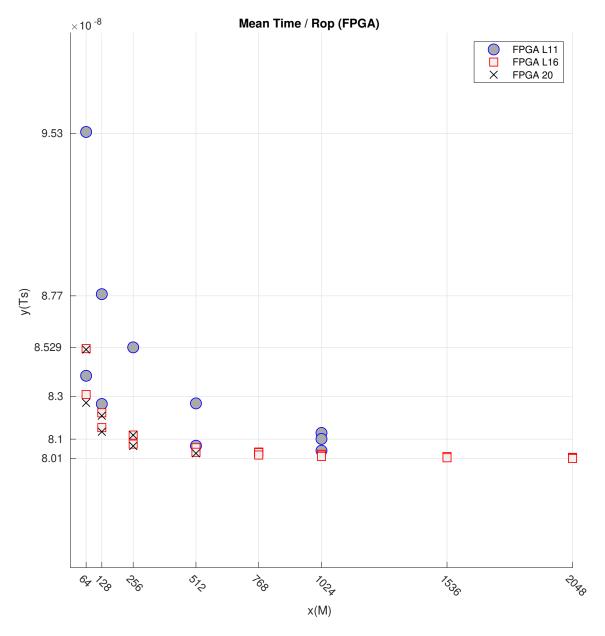

|    | 6.3   | FPGA runtime analysis                      | 45        |

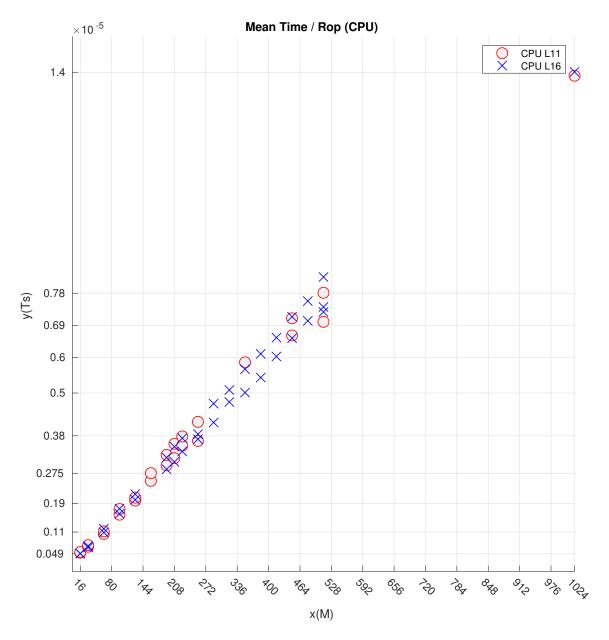

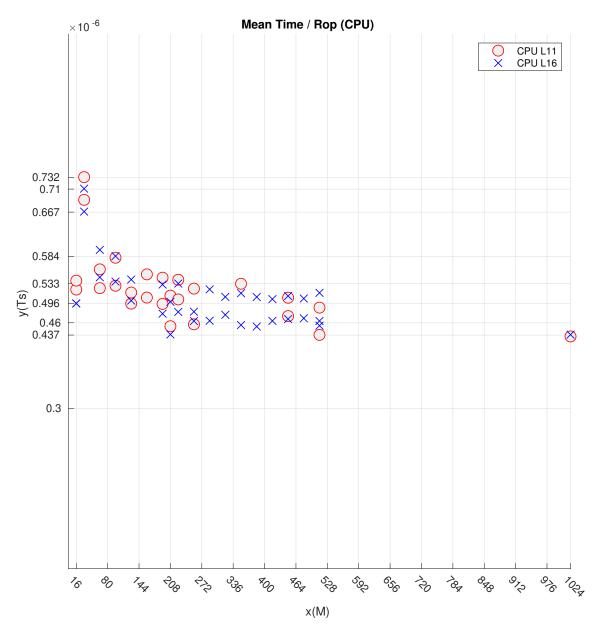

|    | 6.4   | CPU runtime analysis                       | 47        |

|    | 6.5   | Normalised clock comparison                | 50        |

|    | 6.6   | FPGA Estimated Runtime                     | 52        |

|    | 6.7   | Issues and Obstacles                       | 54        |

|    |       | 6.7.1 GMP                                  | 54        |

|    |       | 6.7.2 FPGA External communication          | 54        |

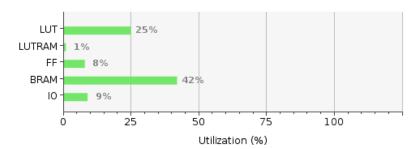

|    |       | 6.7.3 FPGA utilisation                     | 54        |

| 7  | Con   | clusion                                    | 56        |

|    | 7.1   | Answers to research questions              | 56        |

|    | 7.2   |                                            | 58        |

|    |       | 7.2.1 Improvement of CPU implementation    | 58        |

|    |       |                                            | 58        |

| Bi | bliog |                                            | 59        |

|    | _     |                                            |           |

| A | Data       | n sets                                                    | 53 |

|---|------------|-----------------------------------------------------------|----|

|   | <b>A.1</b> | FPGA Measurements                                         | 63 |

|   | A.2        | CPU Measurements                                          | 64 |

|   | A.3        | Estimation                                                | 66 |

| В | Sour       | rce Code                                                  | 58 |

|   | B.1        | CPU Implementation in C                                   | 68 |

|   | B.2        | FPGA Implementation and Design in Verilog                 | 79 |

|   |            | B.2.1 Testbench                                           | 79 |

|   |            | B.2.2 ARBP search FPGA (main program)                     | 30 |

|   |            | B.2.3 Block Ram Module (Verilog)                          | 90 |

|   |            | B.2.4 UART communication FPGA (shortened version Verilog) | 91 |

|   |            | B.2.5 Data receiver script                                | 93 |

## List of Figures

| 1  | Encryption using LFSR                                                                                                 | 6    |

|----|-----------------------------------------------------------------------------------------------------------------------|------|

| 2  | Cipher system using the 0/1-clocking BRM as keystream generator                                                       | 7    |

| 3  | Automaton, NFA on the left, and DFA on the right                                                                      | 10   |

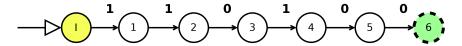

| 4  | NFA for exact search of pattern 001011                                                                                | 11   |

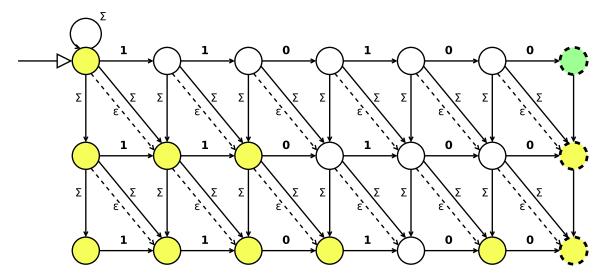

| 5  | Non-Deterministic Finite Automaton, allowing two errors                                                               | 12   |

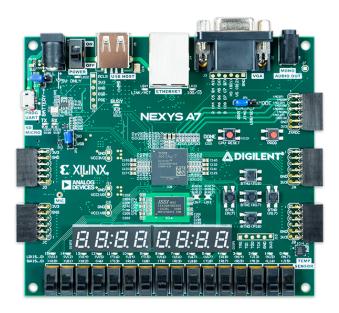

| 6  | Nexys A7 100T XC7A100T CSG324C Xilinx chip                                                                            |      |

|    | Source: https://reference.digilentinc.com/_media/reference/programmable-leadings.                                     | ogic |

|    | nexys-a7/nexys-a7-top-600.png                                                                                         | 16   |

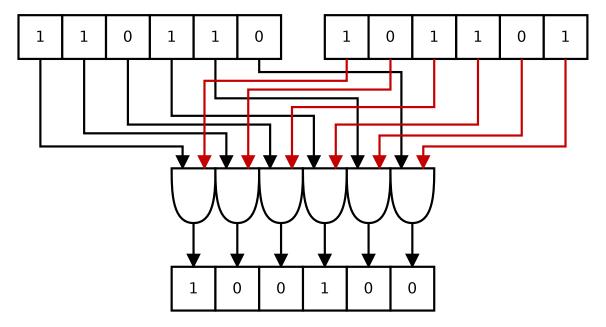

| 7  | AND operation on two registers                                                                                        | 17   |

| 8  | UART protocol                                                                                                         | 20   |

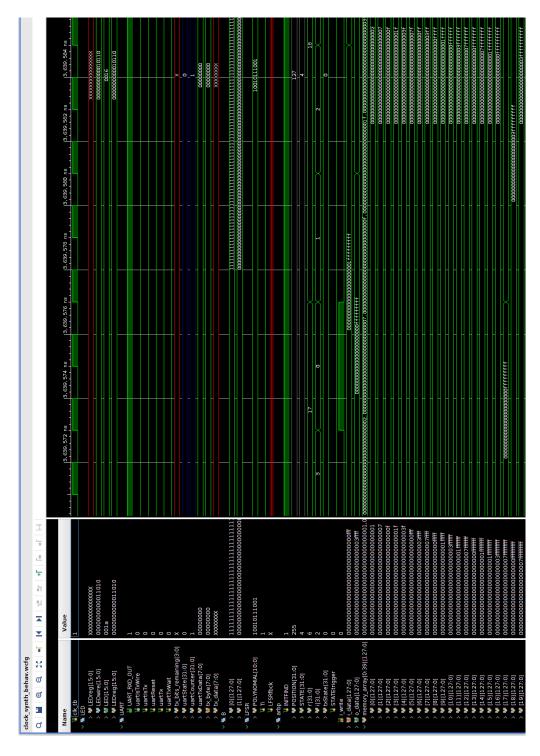

| 9  | Vivado simulation view. Source: Magnus Øverbø                                                                         | 21   |

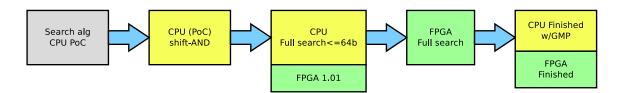

| 10 | Software development progression                                                                                      | 24   |

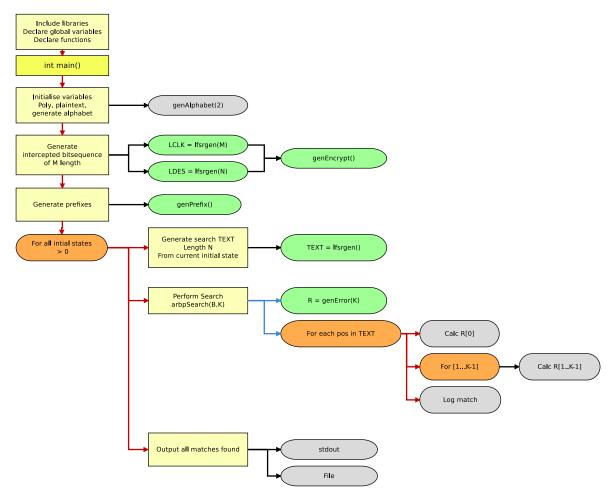

| 11 | Logic flow diagram of Central Processing Unit (CPU) implementation, written in C .                                    | 26   |

| 12 | Logic flow diagram of Field-Programmable Gate Array (FPGA) design                                                     | 31   |

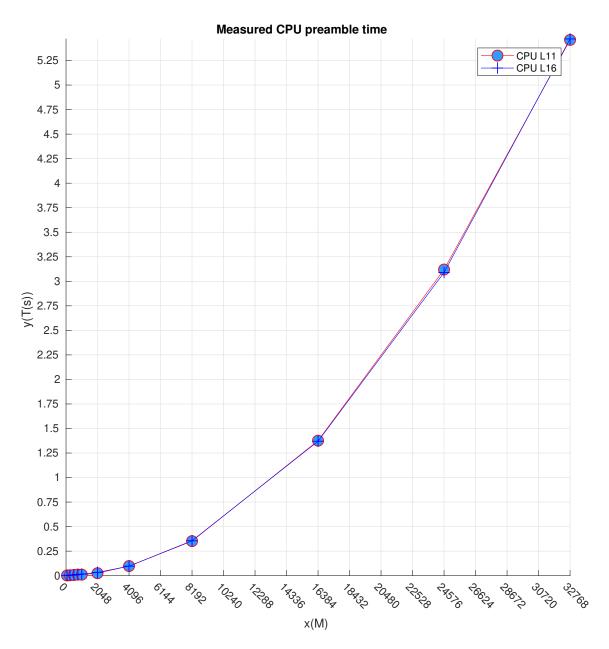

| 13 | Time required for generating the preamble on CPU                                                                      | 37   |

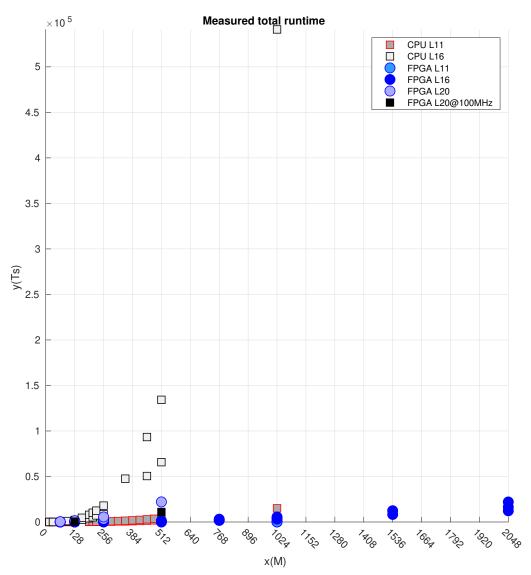

| 14 | Total processing time plotted by architecture and polynomial degree. With search                                      |      |

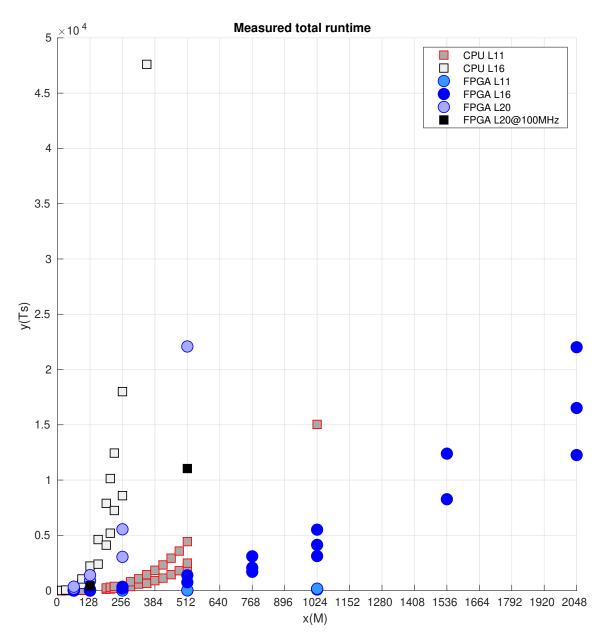

|    | word length $M$ on the X-axis, with multiple errors $K$                                                               | 40   |

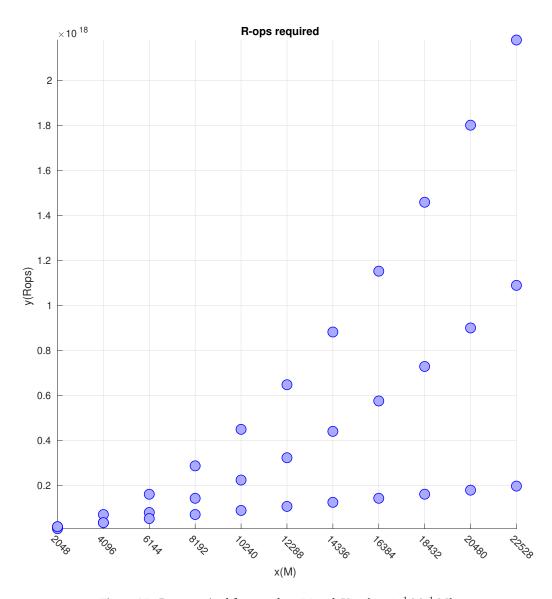

| 15 | $R_{ops}$ required for search w/M and $K \in \{1024, \frac{1}{4}M, \frac{1}{2}M\}$                                    | 43   |

| 16 | Entire runtime for FPGA and CPU with M bit search word and K bit allowed errors                                       | 44   |

| 17 | Mean time for FPGA to perform each $R_{op}$ calculation based on an M bit search word                                 | 46   |

| 18 | Mean time for CPU to perform each $\mathcal{R}_{op}$ calculation based on an M bit search word $% \mathcal{L}_{op}$ . | 48   |

| 19 | Adjusted mean time for CPU to perform each $R_{op}$ calculation based on an M bit                                     |      |

|    | search word                                                                                                           | 49   |

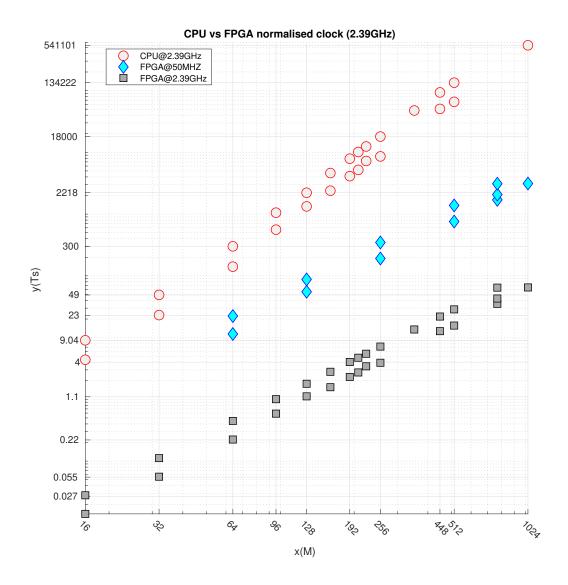

| 20 | Normalised FPGA clock rate vs CPU (log,log)                                                                           |      |

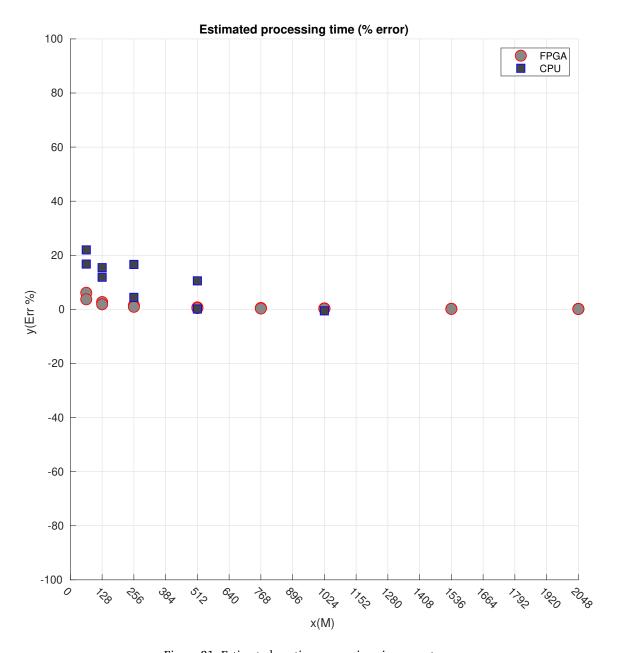

| 21 | Estimated runtime error given in percentage                                                                           | 53   |

| 22 | Device utilisation summary, L(16), M(2048), K(1024). Source: Magnus Øverbø                                            | 55   |

## List of Tables

| 1  | Within-Subject Experimental design                  | 23 |

|----|-----------------------------------------------------|----|

| 2  | Parameters used for preamble and search             | 39 |

| 3  | Time estimation for hypothesised circuit            | 56 |

| 4  | Data set collected from FPGA with 50MHz clock rate  | 63 |

| 5  | Data set collected from FPGA with 100MHz clock rate | 64 |

| 6  | Data set collected from 2.39GHz CPU                 | 64 |

| 7  | Timing of preamble generation on 2.39GHz CPU        | 65 |

| 8  | Estimation of runtime processing for FPGA           | 66 |

| 9  | Estimation error FPGA                               | 67 |

| 10 | Estimation error CPU                                | 67 |

## Listings

| 4.1        | Calculation of $R_0$ . Exact search         | 26 |

|------------|---------------------------------------------|----|

| 4.2        | Calculation of $R_1^K$ . Approximate search | 27 |

| 4.3        | Calculation of $R_0$                        | 32 |

| 4.4        | Calculation of $R_{k=1}^K$                  | 32 |

| B.1        | C ARBP source code                          | 68 |

| <b>B.2</b> | Verilog Testbench source code               | 79 |

| <b>B.3</b> | Verilog ARBP module source code             | 80 |

| <b>B.4</b> | Verilog BRAM module                         | 90 |

| B.5        | Verilog UART module                         | 91 |

| <b>B.6</b> | Python data logging script                  | 93 |

#### 1 Introduction

#### 1.1 Background

Large number calculations on a Central Processing Unit (CPU) is not possible without a library providing a layer of abstraction, as CPUs can maximum hold 64b in a single register. This limitation is a problem for cryptography requiring fast computations of large numbers since it creates latency. A Field-Programmable Gate Array (FPGA) is a stateless system consisting of a large amount of interconnectable Configurable Logic Block (CLB), Random Access Memory (RAM) module and several interfaces. FPGA is perfect for constructing logical circuits and performing logical operations as it generates a circuit with programmable logic without having a fixed register size like CPUs. Applications for FPGAs are among others, signal processing, string matching and cryptanalysis as explored in this thesis. It has already been shown to outperform CPUs in spam filtering by Borgund[6], and in text searching, as studied by Irwin et. al[7] and Michailidis and Margaritis[8]. The downside is that the clock frequency on a consumer-grade FPGA is much slower than a CPU, but its primary strength is that it performs operations in parallel and concurrently.

The theoretical application of performing cryptanalysis using a constrained approximate bit-parallel search algorithm is given in [1]. It details a cipher system built on the 0/1-clocking Binary Rate Multiplier (BRM) which generates the irregularly clocked keystream to encrypt the plaintext. The paper discusses the general correlation attack[2] and utilising a constrained Approximate Rowwise Bit-Parallel (ARBP) search to recover the initial state of an irregularly clocked Linear Feedback Shift Register (LFSR).

This thesis investigates the applicability of performing cryptanalysis of irregularly clocked LFSRs by employing an unconstrained ARBP search on an FPGA. It evaluates the Levenshtein distance[2] between the intercepted ciphertext and all undecimated bit sequences generated by the initial states of the clocked LFSR. The thesis uses an unconstrained ARBP search with the shift-AND algorithm developed by Wu and Manber[5], based on Baeza-Yates and Gonnets previous work[3], to obtain the Levenshtein distance.

Approximate search requires processing the M bit search word and the ciphertext sequence, which is tried embedded into the N bit search text allowing for K errors, where the search text is the undecimated keystream sequence of length N=2M bit. Given the limitation on a CPUs register size w is mainly 64b, this thesis sought to determine if an FPGA could perform an unconstrained ARBP search faster than a standard CPU, and what limitations occurs in relation to cryptanalysis.

#### 1.2 Related Research

Petrovic[1] explore the theoretical applicability of using a version of the unconstrained approximate, bit-parallel search algorithm developed by Wu and Manber[5], to calculate the constrained

Levenshtein distance between two bit sequences. This distance metric has been explored in the past by Golic and Mihaljevic[2] to perform cryptanalysis of a cipher system which utilises BRM as its keystream generator. More specifically, a 0/1 clocking generator, based on two separate LFSRs. Golic and Mihaljevic[2] proposed a generalised correlation attack based on the constrained Levenshtein distance as Siegenthaler's[4] classical correlation attack, using Hamming distance, is not possible with irregular clocked LFSR as the sequences are of different length.

This thesis seeks to build on Golic and Mihaljevic work regarding the estimation of Levenshtein distance between an output sequence of length M and an undecimated LFSR sequence of N=2M. The thesis implements an unconstrained ARBP search as developed by Wu and Manber[5]. The thesis also seeks to implement this algorithm on both a standard CPU architecture and using a specialised hardware, FPGA. which is capable of generating large complex circuits with programmable logic. The reason for this is that FPGAs do not have constraints on register size, w, as opposed to CPUs with w=64b. Given this advantage, it was desirable to determine how efficient the implementation of this algorithm would be on an FPGA in the setting of cryptanalysis.

The topic of efficiency in bit-parallel searches on CPU and FPGA is well researched. Irwin et.al[7] focused on exact string matching on an FPGA to improve the searching within an IDS. He utilised the exact bit-parallel matching as developed by Baeza-Yates and Gonnet[3]. Their tests based itself on searching a set of texts, given a set of search words where M=32b. It evaluated its findings against the same application run inside MatLab, which is not an ideal comparison as MatLab is a scripting language. However, their result showed that FPGAs were 160 times faster than MatLab.

Borgund[6] explored a similar project to Irwin et.al[7], and tested the increased efficiency of pattern recognition in spam email using an FPGA. The test performed was trying to match multiple search words within the text of emails using the Levenshtein distance and approximate bit-parallel search on FPGA. Borgunds results were evaluated against the same test on CPU, finding the FPGA was 55 times faster.

A different paper details the same discovery, using the approximate bit-parallel search algorithm as developed by Wu and Manber[5]. Michailidis and Margaritis[8] research is more closely related to this thesis because their tests used long patterns testing. They found that the FPGA was 9-340 times faster than a CPU given M=1024b. One difference between this thesis and Michailidis and Margaritis is the implementation. Michailidis and Margaritis preloaded the FPGA with all data required for the search, meaning it only had to handle the searching of fixed strings which is very efficient. In this thesis, an entire system was implemented to automate the search in relation to cryptanalysis, generate the data sets and transfer data.

In regards to specific hardware, Tran, Schindel, Liu and Schmidt[9] implemented approximate bit-parallel search of M=512b on a CPU capable of running a 512b register per CPU core. Although achieving excellent results in regards to CPU implementation and multithreading solutions, their problem arises when M>512b as the physical limits result in degraded performance. The cost of these CPUs is also a consideration, even though they will not have an application for cryptanalysis given its the limitation of M=512b.

Even though the efficiency of searching on FPGA is researched, its focus has been on sequences

shorter than w. Testing of search words longer than w is avoided on the background that the search will lose efficiency. In this thesis, it is sought to verify this and test how long search words can be processed, allowing  $K \ge \frac{1}{4}M$  errors.

This thesis implement a complete system for automated search with cryptanalysis as the focus, on both CPU and FPGA. It performs an unconstrained ARBP search for all initial states of an irregularly clocked LFSR and is further used to obtain the search speed of both CPU and FPGA. Because of this, the system must be capable of generating the search word and the search text automatically. The search algorithm then tries to embed the search word into the search text, and report matches to the host, allowing K errors to occur.

#### 1.3 Scope of the thesis

For the scope of this thesis, the implementations must simulate the cipher system and generate an arbitrary length search word, generate the search text, search all initial states of an LFSR given its degree and polynomial, and record matches of interest. Part of the thesis is to implement this search on both CPU and FPGA where most aspects of the information system are known. Meaning the LFSRs feedback polynomials, ciphertext and the BRM are known. Then perform the cryptanalysis by searching all undecimated bit sequences produced by the irregularly clocked LFSR, provided by the set of possible initial states, and logging the correlation metrics obtained from the search.

Further cryptanalysis of the cipher system is out of scope for this thesis. Meaning the one-to-one search for the combination of plausible undecimated bit sequences and *clocking* LFSR is out of the scope of this thesis.

#### 1.4 Contributions

This thesis seeks to evaluate how efficient FPGAs are in relation to CPUs for searching of N bit long binary sequences using  $\frac{1}{2}N$  long search words in the application of cryptanalysis. The reasoning for this is to evaluate the FPGAs applicability as a platform for obtaining the Levenshtein distance between two sequences and use it as the basis for cryptanalysis with the general correlation attack by Golic and Mihaljevic[2]. The search implemented in this thesis is the unconstrained, approximate row-wise bit-parallel search, using the shift-AND[3, 5] algorithm.

#### 1.5 Research Questions and Hypothesis

The thesis objective is to perform and evaluate the application of running an unconstrained ARBP shift-AND search on both FPGA and CPU. In doing so, the following hypothesis is developed based on past research and the thesis problem.

FPGA will perform an unconstrained ARBP search faster than a CPU, given a normalised clock rate.

The following research questions are posed based on the hypothesis to prove or disprove the hypothesis.

• How long search words can practically be processed.

- How fast is the search performing.

- How do changes to polynomial, search word length and error threshold affect the performance.

- How do the FPGA and CPU compare, given a normalised CPU clock speed.

- What are the limitations given each architecture.

#### 1.6 Thesis Outline

The thesis consists of three main chapters. Chapter 2 goes through and explains the background theory behind cryptanalysis, searching, and the system architectures used in the thesis project. Chapter 4 goes through both system architectures and explains how the implementations designs, discovered issues, and testing is also analysed to ensure the data collected would be valid. Chapter 6 discusses the results collected and the subsequent data analysis.

Chapter 1 entails the problem, defines the scope, discuss past research and poses the research questions. Chapter 2 explores the background theory and concepts which the thesis bases itself on. Some key aspects are Non-Deterministic Finite Automaton (NFA), unconstrained ARBP search, and Golic and Milosevic's proposed generalised correlation attack[2] and FPGAs. The background theory provides the reader with knowledge of the required topics for this thesis.

The research methodology is discussed in chapter 3. It discusses the methods used for research, experiment, software development and data analysis. In chapter 4, the implementation is explained for both CPU and FPGA. It discusses the considerations made during the design and implementation, and analyses implementations to ensure they do not provide data which would be considered tainted or incorrect.

Chapter 5 lists and explains the exact setup for the experiment and data collection. It presents the overview of the data sets along with initial assumptions and assessments. Following this chapter, it discusses the analysis of the gathered data, in chapter 6. Based on the obtained data sets, it compares the implementations using a common factor before analysing the data sets behaviour to draw a conclusion based on the characteristics and comparative analysis.

Lastly, chapter 7, summarises the findings and concludes this thesis before providing suggestions for future work. The attached appendices list the data sets collected and the final set of source code for both implementations.

#### 2 Cryptanalysis of irregularly clocked LFSR using ARBP search

In this thesis, all binary registers and sequences are depicted with the Most Significant Bit (MSB) as the left-most bit and Least Significant Bit (LSB) as the right-most bit. Bit-wise shift operations are left-shift operations, and numbering of registers and sequences are from right to left.

#### 2.1 Stream Ciphers

A stream cipher is a class of encryption algorithms, which operates on the individual characters or bits of a plaintext using an encryption transformation which varies with time. – Chapter 6.1, Handbook of Applied Cryptography, Menezes et al. [10]

The stream cipher system in this thesis is a symmetric cipher, meaning the same key is used for both encryption and decryption. The cipher system in this thesis is also a synchronous stream cipher since the keystream is produced independently of the plaintext and ciphertext.

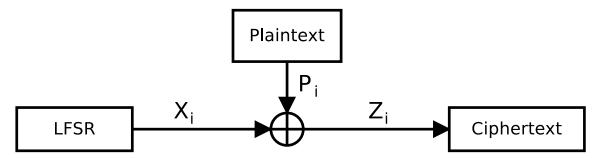

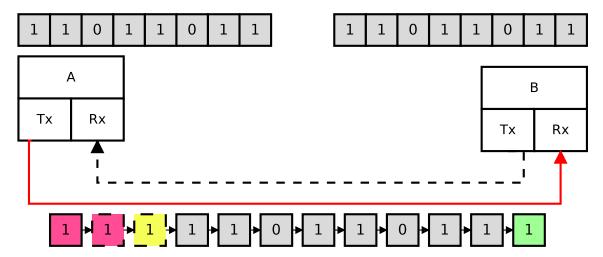

The cipher system in figure 1 operates in such a way that each bit of a plaintext(P) is encrypted by bit from a pseudorandom bit sequence(X), the keystream. The ciphertext is generated as  $X_i \oplus P_i = Z_i$ , by performing the bit-wise operation XOR on each pair of plaintext and keystream bits, denoted by the i-th bit. To recover the plaintext, the same procedure using the bit-wise XOR operation is employed, but on each pair of ciphertext and keystream bits, as  $X_i \oplus Z_i = P_i$ .

#### 2.2 Linear Feedback Shift Registers

A Linear Feedback Shift Register (LFSR) is a binary shift-register, *S*, where a polynomial denotes the feedback function and all bits are shifted each time it is clocked. Given the polynomial, the shift-register produces a pseudorandom output bit sequence, which is used as the stream cipher's keystream. This operation is detailed in, for example, [11].

The LFSR is represented by its current state and its feedback polynomial, C(D), of degree L, which is also the size of the binary shift-register. Church[12] represents polynomials as L+1 long bit sequences, which is not applicable in software or hardware. To compute a polynomial it has to be represented as a L bit long register, e.g. the polynomial  $C(D) = x^3 + x + 1$  is represented by a 3b register as;  $1 \ 0 \ 1 \rightarrow x^3 + x$ .

A LFSR computes its next state by the following method and is calculated each time the LFSR is clocked. Store the MSB  $S_L$ , calculate the feedback value using the polynomial and current state, shift the register and discard the current MSB. Insert the feedback value as the LSB,  $S_1$ .

First, the MSB is temporarily stored because it is the current states output bit, and is discarded by the future shift-operation. The feedback value, F(S), is calculated using the feedback polynomial and the current state, as shown below. It produces a single bit output, which is assigned as the LSB,

$S_1$  after the shift operation occurs.

$$F(S) = (\sum_{i=1}^{L} C(D)_i \wedge S_i) \mod 2$$

(2.1)

Following obtaining the feedback value, the next LFSR state is set by shifting the current state by a single bit. The shift results in discarding the MSB, which is why it is temporarily stored, and after the shift occurs, the LSB is set to the feedback value.

$$S_i = S_{i-1}$$

for  $i \in \{2, .., L\}$

$S_1 = F(S)$  (2.2)

When the LFSR is clocked n number of times the resulting pseudorandom output bit sequence, X, produced will be n bit long. X is then further used to produce the ciphertext Z, as illustrated in figure 1, by XOR-ing the X with plaintext P as denoted below.

$$Z_i = P_i \oplus X_i \quad \text{ for } i \in \{1, ..., n\}$$

(2.3)

An important factor regarding the feedback polynomials used for an LFSR is that they should be primitive polynomials. Utilising these polynomials will ensure that the maximum length period,  $2^L - 1$ , is generated. This is because these polynomials generate all possible states of the LFSR and the maximum output, except for the 0 state, before it repeats itself. A list of primitive polynomials for  $GF(2^L)$  is, for example, provided by [13], which is derived from [12].

Figure 1: Encryption using LFSR

#### 2.2.1 Clock Controlled Generators: Irregularly Clocked LFSR

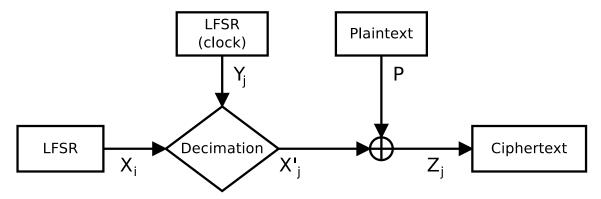

In this thesis, the pseudorandom bit sequence is generated by an irregularly clocked LFSR, which produces a decimated bit sequence of greater linear complexity. The method employed is a Binary Rate Multiplier (BRM) called 0/1-clocking, see, for example, [14].

The BRM used in this thesis operates as shown in figure 2. It depicts two LFSR producing two separate bit sequences, X and Y. These are fed into the decimation function producing the X' keystream bit sequence. This bit sequence is then XOR-ed with the plaintext, P, producing the ciphertext, Z.

The decimation function operates by clocking both LFSRs, X and Y simultaneously generating the bits  $X_i, Y_j$ . If  $Y_j = 1$  LFSR X is clocked once more, producing  $X_{i+1}$ .  $X_{i+1}$  is then added to the irregularly clocked bit sequence X' as  $X'_j$ . If  $Y_j = 0$ ,  $X_i$  is just forwarded to X' as bit  $X'_j$ . The resulting bit sequence X' is then used as the keystream and is XOR-ed with P producing the ciphertext Z.

The maximum number of deletions between X and X' is equal to the length M of the decimated bit sequence, given that the probability  $Pr(Y_j=1)=1$ . The minimum number of deletions is 0 given that the  $Pr(Y_j=1)=0$ , which occurs if the clocking LFSR is initialised with the 0 state. The clocking LFSR should produce a sequence of independent identically distributed binary variables, Y, with  $Pr(Y_j=1)=0.5$  for all initial states of the LFSR.

Figure 2: Cipher system using the 0/1-clocking BRM as keystream generator

The LFSRs in this thesis utilise primitive feedback polynomials for two reasons. First, using primitive polynomials of the same degree L in a BRM pseudorandom generator results in a linear complexity of  $L(2^L - 1)$ [15]. Secondly, the overall period is  $(2^L - 1)^2$ . The primitive polynomials used in this thesis were selected from [13, 12] for  $GF(2^L)$ , where 2 < L < 32.

The linear complexity is based on the shortest period it generates, and the linear complexity is defined as the shortest LFSR capable of generating the given sequence of bits.

#### 2.3 Cryptanalysis

Given the cipher system, there are requirements for the generation of keystreams to ensure it has adequate security. Regarding the statistical properties of the generated sequence, Golomb's postulates, as listed in [16], have to be satisfied and can be tested through various statistical tests and autocorrelation. The linear complexity must be high, and the BRM 0/1-clocking LFSR used in this thesis has a linear complexity of  $L(2^L - 1)$ [15]. Lastly, the periods generated must be long, and in this case, the overall period is  $(2^L - 1)^2$ [15].

Given these requirements, a keystream generator can be seen as adequately secure and resistant against attacks. The cryptanalysist's job then becomes to find a scientific method to break the cipher system. In this case the task is to recover the initial states of the two LFSRs, X and Y, used to gen-

erate the ciphertext, on the premise that the following parameters are known, the LFSRs feedback polynomials,  $C(D_X)$  and  $C(D_Y)$ , and the ciphertext Z of length M.

#### 2.3.1 The Brute-Force Attack

Given the cipher system used in this thesis, recovering the initial state of both LFSR using a brute force attack would require evaluating all combinations of initial states of X and Y. The search scope would consist of  $(2^L-1)^2$  decimated keystreams X', which must be evaluated against the ciphertext to recover the plaintext. Such a search quickly becomes infeasible to complete, e.g. given a polynomial of degree 100, the search scope would consist of approximately 1.606E+60, as opposed to a single LFSR with only approximately 1.267E+30.

Even though a brute-force method will find the correct solution eventually, the time requirements are usually well beyond the acceptable ones. Besides, there is a possibility of many possible solutions that could be found given that the plaintext is too short or too generic.

#### 2.3.2 Generalised Correlation Attack

Given Siegenthalers classical correlation attack[4] is based on the Hamming distance of two equal length bit sequences, it is not usable given the cipher system in this thesis. When a BRM-based generator generates the pseudorandom sequence, the undecimated sequence and the output sequence will be of different lengths, and Hamming distance is rendered unusable.

Golic and Mihaljevic[2] explored and developed a generalised correlation attack, which is based on a constrained Levenshtein distance between two bit sequences of different lengths. The two lengths must be of non-negative difference when calculating the correlation. Which in this case is always positive. Golic and Mihaljevic propose the same cipher system, as illustrated in figure 2. Where  $Pr(Y_j=1)=0.5$ , and the  $Pr(P_j=1)=p\neq 0.5$  for all j. These parameters generate the binary sequence Z, the ciphertext.

To evaluate the distance between a LFSR generated bit sequence and the ciphertext,  $2^L-1$  initial states must be evaluated and subsequently added to either of the possible hypotheses,  $H_0$  and  $H_1$ . Where the resulting Levenshtein distance d of the variable D is used for classifying the evaluations,  $H_0$  a representing a plausible solution, and  $H_1$  representing a non-match. After evaluation two sets of probability distributions are generated  $Pr(D|H_0)$  and  $Pr(D|H_1)$ .

The evaluation is based on the length of the ciphertext, M and the selected threshold value, t, which is set to achieve the desired probabilities for false-negatives  $P_m = 10^{-3}$  and false-positives  $P_f \approx 2^{-L}$ .

Following the initialisation, the Levenshtein distance between the generated undecimated bit sequence for each initial state of X is calculated using constrained search, explained in section 2.4.6. This constrained search allows match, substitution and deletions to occur, with the additional requirement of only allowing a run of one deletion. The resulting Levenshtein distance d is then classified as  $H_0$  or  $H_1$  according to t. The resulting set of  $Pr(D|H_0)$  will contain the most plausible initial states which could generate the solution.

#### 2.4 Search

Efficient searching algorithms is a well-researched topic, and for this thesis, the method employed for searching is Wu and Manbers Approximate Row-wise Bit-Parallel (ARBP) search algorithm[5]. This search is built on the work regarding the exact search by Baeza-Yates and Gonnet[3] using a bit-parallel algorithm. Baeza-Yates and Gonnet was the first to release the bit-parallel search for exact pattern matching, which was based on finite automata theory, like Knuth, Morris and Pratts algorithm[17], and it exploits the finite alphabet as Boyer and Moores algorithm[18] do.

A general problem in searching is the handling of large patterns as a Central Processing Unit (CPU) loses efficiency when handling data larger than a single machine word, w. Several methods for performing approximate search have been implemented, and the unconstrained approximate row-wise bit-parallel search algorithm based on Wu and Manbers shift-AND algorithm is explained in the following sections. The following sections details the concepts of the Non-Deterministic Finite Automaton (NFA)[3, 5], bit-parallel search[3, 5], the shift-AND algorithm and the difference between constrained and unconstrained search.

An exact search is defined as the search word, or pattern, P exists as a direct subset of the search text  $T, P \subset T$ . An approximate search is defined as, P is of distance k to Q, if it can be transformed through k number of insertions, deletions or substitutions[5]. This is explained further in section 2.4.2, finite automata, and section 2.4.3, bit-parallel search.

#### 2.4.1 Bit-Parallelism and Bit-operations

Bit-Parallelism, as explained by Navarro [19], chapter 1.3.1, is the representation of bit sequences and processing of bit-wise operations in a computer and hardware. In hardware, many bits can be represented as a single register of size w, which then can be updated in a single operation, e.g. given the logical AND operation in figure 7, two registers of w size can be processed as a single operation of parallel logic operations reducing the number of operations by w. This parallelism is the aspect referred to and allows for high-speed processing of complete registers.

For a standard CPU w is 64b, but on an Field-Programmable Gate Array (FPGA) w can be set to an arbitrary size given the FPGA has allocatable space for it. This ability is the reason why FPGAs are more efficient in performing bit-wise operations, as CPUs must perform the same task repeatedly until the entire value is processed.

Given this thesis uses bit-wise operations frequently, especially in the case regarding implementation, the used bit-wise operations are explained below. Arithmetic operations are not used in the search, besides incrementing counters, so these concepts are not explained.

#### Bitwise shift

This operation is denoted by "« n" or "» n", which produces a left or right shift of n positions. The operation will move all bits in the register n positions the declared direction, which results in discarding 1101101 << 3 = 1101000the n outermost bits and insert n 0-values at the shifted positions in the register. An example of a left-shift of three is given to the right.

#### Logical AND

This operation is denoted by "&". Given two registers, only the positions where a bit is set in both registers produce a set bit in the resulting register, figure 7. This produces the truth table on the right for each bit in the register.

# $\begin{array}{c|cccc} 0 & 0 & 0 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \end{array}$

#### Logical Inclusive OR / Logical OR

This operation is denoted by "|". Given two registers, all positions with a set bit, regardless of the register, will produce a set bit in the resulting register. This produces the truth table on the right for each bit in the register.

|   | 0 | 0 | 0 |

|---|---|---|---|

| ١ | 0 | 1 | 1 |

| İ | 1 | 0 | 1 |

|   | 1 | 1 | 1 |

#### Exclusive OR (XOR)

This operation is denoted by " ^ ". Given two registers only positions with a bit set in one of the register, will produce a set bit in the resulting. This produces the truth table on the right for each bit in the register.

| 0 | 0 | 0 |

|---|---|---|

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

#### 2.4.2 Finite Automaton

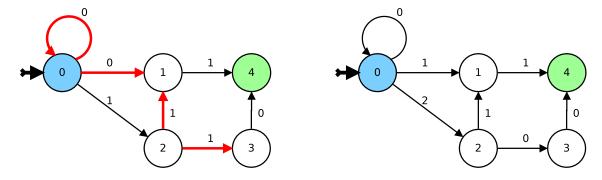

As described by Navarro[19], an automaton is a directed cyclic or acyclic graph where every vertex depicts a state  $q \in Q$ , and edges represent functional transitions  $D(q_i, \alpha_j)$  between states and are labelled by  $\alpha \in \Sigma \cup \{\epsilon\}$ . D associate each state  $q \in Q$  with a set  $Q' \subset Q$  for its set of edges,  $\alpha \in \Sigma \cup \{\epsilon\}$ . In the automaton there exists an initial state,  $I \in Q$ , regular states and final states  $F \subseteq Q$ . Given this, the automaton is defined by  $A = (Q, \Sigma, I, F, D)$ .

The automaton is a non-deterministic finite automaton, if there exist more than one transitions from  $q \in Q$ , given a single label  $\alpha$ . If there for every  $q \in Q$  exist only one transition for every  $\alpha$  it is said to be a deterministic finite automaton. Given figure 3, the left is an NFA, because  $D(q_0,\alpha_0)=q_0,q_1$  and  $D(q_2,\alpha_1)=q_1,q_3$ . Given the Deterministic Finite Automata (DFA), every state  $q \in Q$  have only one transition with the same  $\alpha$ .

Given an exact searching algorithm, each state has two transitions *D*. Either a horizontal match transitioning it to the next state, or a mismatch returning the search to *I*, while the final value of

Figure 3: Automaton, NFA on the left, and DFA on the right

the search pattern denotes a final state F marking a match.

In both Non-Deterministic Finite Automaton (NFA) and DFA, transitions from one state to another will set the new state active. In a DFA only one state is active at a time because only one transition exists from any state given a specific  $\alpha$ . In NFA, multiple states can be active at the same time, as there can exist more than one transition for  $\alpha$  given a current state.

#### 2.4.3 Bit-Parallel Search

Both Baeza-Yates and Gonnet's[3], and Wu and Manber's[5] proposed bit-parallel search algorithms that are based on NFAs. Gonnets search is an exact pattern matching which is given by the NFA in figure 4. Wu and Manber[5] proposed an approximate search based on Baeza-Yates and Gonnets exact search algorithm, giving the NFA in figure 5.

Given the exact search by Baeza-Yates and Gonnet[3] only horizontal transitions are allowed, indicating a direct match from the current state to the next value in the pattern. As shown in figure 4. In this event, both the pattern and search text is incremented, so the next state in the NFA is evaluated against the next  $t \in T$ .

Figure 4: NFA for exact search of pattern 001011

When the search state reaches the end, state 6 in figure 4, a full match is registered. The state of the search is represented as an M bit register R, the pattern length, and based on the algorithm, the currently active states are represented by a set bit or unset bit. Eg. R=001001, represent two partial matches are occurring, and have reached position one of the pattern and position four of the pattern. Example of exact search is shown in section 2.4.4 for a short example of the shift-AND algorithm for exact search, but the update function for the search state is given below.

$$R'_0 \leftarrow ((R_0 << 1)|0^{m-1}1)\&B[t_i]$$

Exact search utilises a single transition representing a direct match. Approximate search implements four transitions to allow K errors to occur. The NFA by Wu and Manber[5] has four transitions from every state until the  $F \subseteq Q$  states denoting a match with k errors. The transitions are defined as, match (horizontal), insertion (vertical), substitution (diagonal) and deletion (dashed diagonal).

Given the NFA for approximate search with K=2, figure 5, the marked transitions are defined as follows by Wu and Manber[5], and described by Navarro[19]. Horizontal transitions for a match are the same as for exact search, and both the search text and pattern is advanced. A vertical transition represents an insertion of a symbol into the pattern, and only the text advances. Solid diagonal lines represent substitutions, and both the search text and pattern is advanced. Dashed diagonal lines,  $\epsilon$ , mean that a character of the pattern is deleted, the pattern is advanced, but not the search text. Finally, the state I allows for an arbitrary number of bits to be skipped until the first transition is made.

The search state of an exact search is represented by a single M bit register that is updated throughout the search. Approximate search organises this as a set of search states.  $R_{k=0}^K$ , where  $R_0$  denotes the search state without errors,  $R_1$  allows a single error, until  $R_{k=K}$  allowing K errors to occur during the search. The two update functions for calculating the new search states are given below, see, for example [20].

$$\begin{split} R'_0 &\leftarrow ((R_0 << 1)|0^{m-1}1) \& B[t_j] \\ R'_k &\leftarrow ((R_k << 1) \& B[t_j]) |R_{k-1}| (R_{k-1} << 1)|(R'_{k-1} << 1)|0^{m-1}1 \end{split}$$

Figure 5: Non-Deterministic Finite Automaton, allowing two errors

The horizontal transition for  $R_0$  is particular and updated the same way as an exact search, while the rest are updated using the second function above and described below. The second function implements all four transitions given for  $t_j \in T_j$  as created by Wu and Manber[5] and explained by Navarro[20]. In the list below,  $R'_{k-1}$  refers to the new search state value of the search state with one less error than is currently being updated.  $R_{k-1}$  Refers to the old value of the search state with one less error allowed.  $R_k$  is the non-updated value of current search state, and  $R'_k$  is the updated search state value.

- 1. The horizontal transition is given by  $((R_k << 1)\&B[t_j])$  which evaluates the next state for correct match. The shifted search state value is OR-ed with the bit-mask of character  $t_j$ . Any matching bits will denote the new search state,  $R'_k$ .

- 2. The vertical transition is given by  $R'_k|R_{k-1}$ , by adding any missing bits from the non-updated search state with one less error allowed. This represents inserting missing characters into the pattern by advancing the text, but not the pattern.

- 3. The diagonal substitution transition is given by  $R'_k|(R_{k-1} << 1)$ , by adding missing bits from

the shifted register representing a non-updated search state with one lower error. This is representing advancing the text and the pattern given the NFA.

- 4. The diagonal deletion of a character in the pattern is given by  $R'_k|(R'_{k-1} << 1)$ . This is done by adding any missing bits from the updated search state of one less error to the new search state, through a logical inclusive OR operation.

- 5. In addition, as given by [20], an additional OR operation is performed.  $R'_k|0^{m-1}1$  which accounts for an unrepresented initial state, and simply sets the Least Significant Bit (LSB) of  $R'_k$  to 1.

#### 2.4.4 Exact Bit-Parallel Search using Shift-AND

The search algorithm shift-AND by Baeza-Yates and Gonnet[3] for exact search is based on a NFA and utilise register of M length to represent the current search state. The search state represents all currently active states which have a partial or complete match. The NFA for the search is given in figure 4 which deletes all non-match values until an initial match is found.

First, the search word, P, is processed to get the set of prefixes in the alphabet,  $\Sigma = \{B[t_0], B[t_1]\}$ . Since  $\Sigma$  is binary, the prepossessing is given by,  $B[t_0] = P$ , the inverse of the pattern, and  $B[t_1] = P$ . For each  $t_j \in T$  being searched, the current search state is updated according to the shift-AND algorithm. Where the shift-AND calculation for an exact match is denoted below.

$$R' = ((R << 1)|0^{m-1}1)\&B[t_j]$$

Given the search text T=10010110 and search word P=001011, the exact shift-AND search updates the search values as follows. Given the initial search state is R=0, the updated search state value is R', with each set bit representing a match or partial match. This R' is then used as the R value for every  $t_j$  being searched.

$$(R << 1|1) = 000001 \\ B[t_1 = 0] = 110100 \\ p = 001011 \\ B[t_j = 0] = 110100 \\ B[t_j = 1] = 001011 \\ R = 000000 \\ R = 000001 \\ R = 000011 \\ R = 000000 \\ R = 000011 \\ R = 000000 \\ R = 000011 \\ R = 000000 \\ R = 000001 \\ R = 010000   \\ R = 0100000  \\ R = 0100000  \\ R = 0100000  \\ R = 0100000  \\ R = 01000000 \\ R = 01000000 \\ R = 010000000 \\ R = 01000000 \\ R = 01000000 \\ R = 01000000 \\ R = 01000000 \\ R = 01$$

#### 2.4.5 Approximate Row-wise Bit-Parallel Search

As shown in explained in section 2.4.3, the approximate search is built upon the bit-parallel shift-AND search by Wu and Manber[5]. Which is built on top of the exact bit-parallel search algorithm by Baeza-Yates and Gonnet[3]. It is implemented as two separate functions, one for the initial  $R_0$  state, which is calculated in the same manner as an exact search. From this value, the next error level is calculated using the second function which represent all transitions possible from the

current state allowing K errors.

$$R'_k \leftarrow ((R_k << 1) \& B[t_j]) | R_{k-1} | (R_{k-1} << 1) | (R'_{k-1} << 1) | 0^{m-1} 1$$

Even though this is a high-speed search at the hardware level, many calculations have to be performed as given by  $R_{ops}=N\times(K+1)$ , which represent the total number of search state updates needed to be performed for an entire approximate search. The example later in this section with T of length N=9 and K=2 errors allowed. This results in 27  $R_{ops}$  to complete the search.

Given the NFA in figure 5 with T=100101110, p=001011 and K=2 errors allowed, we get the following approximate search states.

| $\frac{B[t_1 = 0] = 110100}{R'_0 = 000000}$ | $\frac{B[t_4 = 1] = 001011}{R'_0 = 000011}$                                                                                                                                 | $\frac{B[t_7 = 0] = 110100}{R'_0 = 010000}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $R_1' = 000001$                             | $R_1' = 001111$                                                                                                                                                             | $R_1' = 111111$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $R_2' = 000111$                             | $R_2' = 0111111$                                                                                                                                                            | $R_2' = 111111$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\frac{B[t_2 = 1] = 001011}{R'_2 = 000001}$ | $\frac{B[t_5 = 0] = 110100}{R_0' = 000100}$                                                                                                                                 | $\frac{B[t_8 = 0] = 110100}{R'_0 = 100000}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $R_1' = 000011$                             | $R_1' = 011111$                                                                                                                                                             | $R_1' = 111111$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $R_2' = 001111$                             | $R_2' = 111111$                                                                                                                                                             | $R_2' = 111111$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\frac{B[t_3 = 1] = 001011}{R'_0 = 000011}$ | $\frac{B[t_6=1] = 001011}{R_0' = 001001}$                                                                                                                                   | $\frac{B[t_9 = 1] = 001011}{R_0' = 000001}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $R_1' = 000111$                             | $R_1' = 011110$                                                                                                                                                             | $R_1^{'} = 101011$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $R_2' = 001111$                             | $R_2' = 111111$                                                                                                                                                             | $R_2' = 111111$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                             | $R'_0 = 000000$ $R'_1 = 000001$ $R'_2 = 000111$ $B[t_2 = 1] = 001011$ $R'_0 = 000001$ $R'_1 = 000011$ $R'_2 = 001111$ $B[t_3 = 1] = 001011$ $R'_0 = 000011$ $R'_1 = 000111$ | $R'_0 = 000000 R'_0 = 000001 R'_1 = 000001 R'_1 = 001111 R'_2 = 000111 R'_2 = 011111 \frac{B[t_2 = 1] = 001011}{R'_0 = 000001} R'_1 = 000011 R'_2 = 001111 R'_2 = 001111 R'_2 = 001011 R'_1 = 001011 R'_2 = 001011 R'_1 = 0111111 R'_2 = 001011 R'_1 = 0111110 R'_2 = 0111110 R$ |

#### 2.4.6 Constrained vs Unconstrained Search

Given the previous sections on correlation attacks, section 2.3.2, the idea of the constrained search was introduced. This section briefly explains the idea of unconstrained and constrained search. These search methods are implemented when calculating the edit distance between two sequences and are used by Golic and Mihaljevic[2] when calculating the constrained Levenshtein distance.

In the NFA for approximate search method by Baeza-Yates and Gonnet[3] the set of operations consists of match, insert, substitute and delete. An unconstrained search using the Levenshtein distance calculates the number of operations required to transform sequence A into B using any number of operations. Restrictions are not imposed on the operations and allow any number of consecutive runs by a single operation.

As opposed to unconstrained search, constrained search can restrict the set of operations and how they are used in the search, with the same goal of transforming A into B. As discussed concerning cryptanalysis, in [2, 1], the constrained Levenshtein distance is calculated based on the constraints proposed. For cryptanalysis, only match, deletion and substitution are allowed operations, since insert operations do not occur in the cipher system and can be disregarded. Restrictions are also set on the number of consecutive runs of deletes to one since the 0/1 clocking BRM skips maximum one bit at a time.

#### 2.5 Central Processing Unit

A Central Processing Unit (CPU)[21] is in its most basic definition is an electronic circuit component which carries out the computer programs set of instructions, in order to complete the desired task. A CPU has a specific set of instructions available, and only a subset of these can be utilised by a computer program. This mapping is handled by the compilation process when generating the computer program from source.