### ImageCL 3D Extensions Targeting Adaptive Mesh Refinement Proxy Applications on GPUs

Even Olsson Rogstadkjærnet

Master of Science in Computer ScienceSubmission date:August 2018Supervisor:Anne Cathrine Elster, IDICo-supervisor:Jan Christian Meyer, IDI

Norwegian University of Science and Technology Department of Computer Science

# **Problem Description**

This project will build on the ImageCL work done in the fall, extending the ImageCL language and compiler with functionality guided by proxy applications, i.e. mini-applications with performance characteristics of larger applications that can be used for performance modeling. The project will evaluate one or more of the proxy applications worked on by the Mantevo Project and develop it/them or a new application further to take advantage of the GPU using ImageCL.

# Sammendrag

Mens adopsjonen av parallelle og heterogene systemer fortsetter, øker også programmerings-kompleksiteten i disse systemene. Rammeverk som Compute Unified Device Architecture (CUDA) og Open Computing Language (OpenCL) gir funksjonell portabilitet på tvers av støttede enheter. Men de er ikke i stand til å kjøre den samme koden optimalt over forskjellige arkitekturer, eller gi mulighet for å porte koden enkelt og effektivt til andre Graphics Processing Unit (GPU) arkitekturer. Denne utfordringen er kjent som ytelses portabilitet, og er viktig siden hardware arkitekturen for GPU-er kan variere mye mellom forskjellige enheter.

Ved å gjøre optimaliseringer om til tuning parametere som kan bli gjort automatisk av kompilatoren, kan en auto-tuner bli brukt til å velge den beste kombinasjonen av optimaliseringer for hver arkitektur. Denne strategien har tidligere blitt utforsket ved å bruke ImageCL språket, som abstraherer bort mye av kompleksiteten ved å gjøre mange manuelle optimaliseringer om til tuning parametere.

I denne oppgaven utvider vi ImageCL språket og kompilatoren for å kunne støtte et bredere spekter av applikasjoner. Disse utvidelsene vil bli styrt av miniAMR, en proxy applikasjon med ytelse-karakteristikken til en Adaptive Mesh Refinement (AMR) applikasjon. I tillegg genererer vi flere GPU stensil-kerneler fra ImageCL kode og integrerer dem i miniAMR applikasjonen, og klarer å få en betydelig ytelsesforbedring (opptil 6.78*x*) for kernelene i forhold til referanse-implementasjonen.

## Abstract

As the adoption of parallel and heterogeneous systems increases, programming such systems also becomes increasingly complex. Frameworks like Compute Unified Device Architecture (CUDA) and Open Computing Language (OpenCL) provides functional portability across their supported devices. However, having the same code run optimally across multiple devices with different architectures, including being able to port code fairly seamlessly and efficiently to other GPU device architectures, is not provided. This challenge, known as performance portability, is significant since Graphics Processing Unit (GPU) architectures tend to get updated and vary even more than Central Processing Unit (CPU) architectures.

By transforming optimizations into tuning parameters that can be applied statically by the compiler, an auto-tuner can be used to pick the best combination of optimizations for each architecture. This strategy has earlier been explored using the ImageCL language and compiler, which moves much of the complexity away from the programmer by abstracting away many optimizations which would normally have to be applied manually.

In this thesis, we extend the ImageCL language and compiler to support a broader range of applications. These extensions will be guided by miniAMR, a proxy application with the performance characteristics of an Adaptive Mesh Refinement (AMR) application. AMR is a computational method used for adapting the accuracy within certain regions of a domain, and is often used in scientific and engineering applications. We generate multiple GPU stencil kernels from ImageCL code and integrate them into the miniAMR application. We are able to show a considerable speedup (up to 6.78x) for many of the generated stencil kernels in miniAMR compared to the reference implementation.

## Acknowledgements

The work on this thesis has been done under the supervision of Dr. Anne C. Elster and Dr. Jan Christian Meyer, which I would like to thank for the help and guidance given during this thesis. Thanks to NTNU for supporting the HPC-lab and providing access to GPUs, and thanks to NTNU's HPC Center for access to the EPIC cluster. I would also like to thank my fellow students at the HPC Lab for making the time spent at the lab much more enjoyable. Finally, I would like to thank my family for the support and encouragement provided during this thesis and also throughout my years of study. Thank you.

En Onkop

Even Olsson Rogstadkjærnet

# **Table of Contents**

| Pr  | obler       | n Description                                                                 | i                       |

|-----|-------------|-------------------------------------------------------------------------------|-------------------------|

| Sa  | mme         | endrag                                                                        | ii                      |

| Ał  | ostrac      | ct i                                                                          | iii                     |

| Ac  | knov        | wledgements                                                                   | iv                      |

| Ta  | ble o       | f Contents                                                                    | v                       |

| Lis | st of [     | Tables                                                                        | x                       |

| Lis | st of ]     | Figures                                                                       | xi                      |

| Lis | st of ]     | Listings xi                                                                   | iii                     |

| Lis | st of A     | Abbreviations x                                                               | vi                      |

| 1   | 1.1         | oduction<br>Project Goal                                                      | 1<br>3<br>3<br>4        |

| 2   | Bacl<br>2.1 | kgroundParallel Computing2.1.1Classification of Parallelism2.1.2GPU Computing | <b>5</b><br>5<br>6<br>7 |

|     | 2.2         | The GPU Architecture                                                          | 8<br>8                  |

|   |                                                                                                       | 2.2.2 Streaming Multiprocessors                                                                                                                                                                                                                                                                                                                                   | 9                                                                                       |

|---|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|   |                                                                                                       | 2.2.3 Single Instruction Multiple Threads                                                                                                                                                                                                                                                                                                                         | 10                                                                                      |

|   |                                                                                                       | 2.2.4 The GPU Memory Hierarchy                                                                                                                                                                                                                                                                                                                                    | 11                                                                                      |

|   |                                                                                                       | 2.2.5 CUDA and OpenCL                                                                                                                                                                                                                                                                                                                                             | 12                                                                                      |

|   | 2.3                                                                                                   | Performance Portability                                                                                                                                                                                                                                                                                                                                           | 14                                                                                      |

|   |                                                                                                       | 2.3.1 Auto-Tuning                                                                                                                                                                                                                                                                                                                                                 | 14                                                                                      |

|   | 2.4                                                                                                   | ImageCL                                                                                                                                                                                                                                                                                                                                                           | 15                                                                                      |

|   |                                                                                                       | 2.4.1 The ImageCL Language                                                                                                                                                                                                                                                                                                                                        | 15                                                                                      |

|   |                                                                                                       | 2.4.2 The ImageCL Compiler                                                                                                                                                                                                                                                                                                                                        | 17                                                                                      |

|   |                                                                                                       | 2.4.3 Tuning Parameters                                                                                                                                                                                                                                                                                                                                           | 18                                                                                      |

|   |                                                                                                       | 2.4.4 Stencil Computations                                                                                                                                                                                                                                                                                                                                        | 20                                                                                      |

|   |                                                                                                       | 2.4.5 The ROSE Compiler Infrastructure                                                                                                                                                                                                                                                                                                                            | 21                                                                                      |

|   | 2.5                                                                                                   | Proxy Applications                                                                                                                                                                                                                                                                                                                                                | 23                                                                                      |

|   |                                                                                                       | 2.5.1 Co-Design of Architecture and Algorithms                                                                                                                                                                                                                                                                                                                    | 24                                                                                      |

|   |                                                                                                       | 2.5.2 The Mantevo Project                                                                                                                                                                                                                                                                                                                                         | 26                                                                                      |

|   |                                                                                                       | 2.5.3 Adaptive Mesh Refinement and miniAMR                                                                                                                                                                                                                                                                                                                        | 26                                                                                      |

|   | 2.6                                                                                                   | Related Work                                                                                                                                                                                                                                                                                                                                                      | 28                                                                                      |

|   |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                   |                                                                                         |

| 3 | 3D 3                                                                                                  | and Other Extensions to ImageCL                                                                                                                                                                                                                                                                                                                                   | 29                                                                                      |

|   |                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

|   | 3.1                                                                                                   | The Block Type                                                                                                                                                                                                                                                                                                                                                    | 30                                                                                      |

|   |                                                                                                       | 6                                                                                                                                                                                                                                                                                                                                                                 | 30<br>31                                                                                |

|   |                                                                                                       | The Block Type                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

|   |                                                                                                       | The Block Type                                                                                                                                                                                                                                                                                                                                                    | 31                                                                                      |

|   |                                                                                                       | The Block Type                                                                                                                                                                                                                                                                                                                                                    | 31<br>32                                                                                |

|   |                                                                                                       | The Block Type                                                                                                                                                                                                                                                                                                                                                    | 31<br>32<br>32                                                                          |

|   |                                                                                                       | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table                                                                                                                                                                                                                            | 31<br>32<br>32<br>33                                                                    |

|   | 3.1                                                                                                   | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset Operator                                                                                                                                                                                                    | 31<br>32<br>32<br>33<br>34                                                              |

|   | 3.1<br>3.2                                                                                            | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset OperatorKernel Wrapper                                                                                                                                                                                      | 31<br>32<br>32<br>33<br>34<br>36                                                        |

|   | 3.1<br>3.2<br>3.3                                                                                     | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset OperatorKernel WrapperGlobal Memory                                                                                                                                                                         | 31<br>32<br>33<br>34<br>36<br>37                                                        |

|   | 3.1<br>3.2<br>3.3<br>3.4                                                                              | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset OperatorKernel WrapperGlobal MemoryShared Memory                                                                                                                                                            | 31<br>32<br>33<br>34<br>36<br>37<br>38                                                  |

|   | <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li><li>3.5</li></ul>                                 | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset OperatorKernel WrapperGlobal MemoryShared MemoryTexture Memory                                                                                                                                              | 31<br>32<br>33<br>34<br>36<br>37<br>38<br>40                                            |

| 4 | <ul> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ul> | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset OperatorKernel Wrapper                                                                                                                                                                                      | 31<br>32<br>33<br>34<br>36<br>37<br>38<br>40<br>41<br>42                                |

| 4 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>App</b>                                           | The Block Type                                                                                                                                                                                                                                                                                                                                                    | 31<br>32<br>32<br>33<br>34<br>36<br>37<br>38<br>40<br>41<br>42<br>43                    |

| 4 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>App</b><br>4.1                                    | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset OperatorShared WrapperGlobal MemoryShared MemoryConstant MemoryRegister CachingOlying Code Generated by ImageCL into miniAMRMemory Management and Setup                                                     | 31<br>32<br>32<br>33<br>34<br>36<br>37<br>38<br>40<br>41<br>42<br>43<br>43              |

| 4 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>App</b>                                           | The Block Type                                                                                                                                                                                                                                                                                                                                                    | 31<br>32<br>32<br>33<br>34<br>36<br>37<br>38<br>40<br>41<br>42<br><b>43</b><br>43<br>43 |

| 4 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>App</b><br>4.1                                    | The Block Type3.1.1The idz keyword3.1.2The none Boundary Condition3.1.3Double Precision Floating Point Support3.1.4The Footprint Table3.1.5The Offset Operator3.1.5The Offset OperatorGlobal MemoryShared MemoryShared MemoryConstant MemoryRegister CachingConstant MemoryAlternal Management and SetupKernel Implementations4.2.1Using Single Read-Write Buffer | 31<br>32<br>33<br>34<br>36<br>37<br>38<br>40<br>41<br>42<br>43<br>43<br>45<br>46        |

| 4 | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>App</b><br>4.1                                    | The Block Type                                                                                                                                                                                                                                                                                                                                                    | 31<br>32<br>32<br>33<br>34<br>36<br>37<br>38<br>40<br>41<br>42<br><b>43</b><br>43<br>43 |

### TABLE OF CONTENTS

#### TABLE OF CONTENTS

|    | 4.3   | Generated Kernels        | 49 |

|----|-------|--------------------------|----|

| 5  | Rest  | ults and Discussion      | 51 |

|    | 5.1   | Methodology              | 51 |

|    |       | 5.1.1 Configurations     | 52 |

|    |       | 5.1.2 Validation         |    |

|    | 5.2   | Performance Measurements | 53 |

|    |       | 5.2.1 Execution Time     | 53 |

|    |       | 5.2.2 Memory Usage       | 54 |

|    | 5.3   | Discussion               | 60 |

| 6  | Con   | clusion and Future Work  | 63 |

|    | 6.1   | Conclusion               | 63 |

|    | 6.2   | Future Work              | 64 |

| Bi | bliog | raphy                    | 65 |

| A  | Ima   | geCL Kernels             | 73 |

| B  | Min   | iAMR configuration       | 77 |

| С  | Deta  | ailed Measurements       | 79 |

TABLE OF CONTENTS

TABLE OF CONTENTS

# List of Tables

| 2.1 | Difference between the CUDA and OpenCL API for index and dimension queries [25, 35].                                                           | 13 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Difference between the CUDA and OpenCL terminology [35, 20]                                                                                    | 13 |

| 4.1 | The configurations and tuning parameters used for each generated kernel.                                                                       | 50 |

| 5.1 | The specifications of the three systems used in the measure-<br>ments                                                                          | 52 |

| 5.2 | The default problem size in miniAMR                                                                                                            | 52 |

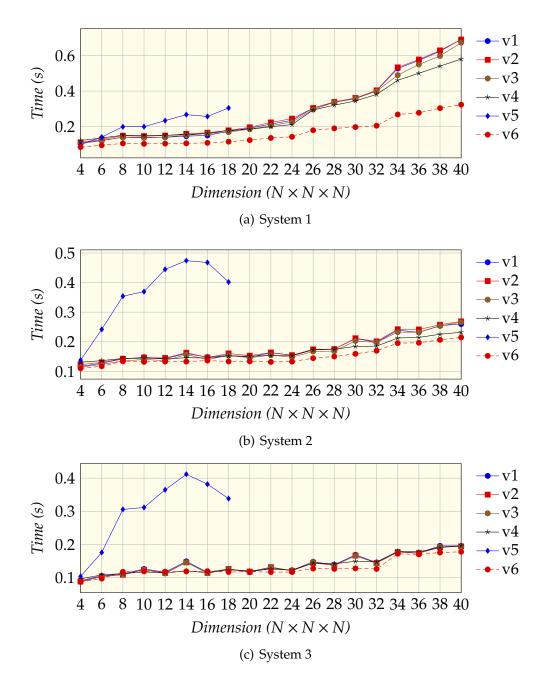

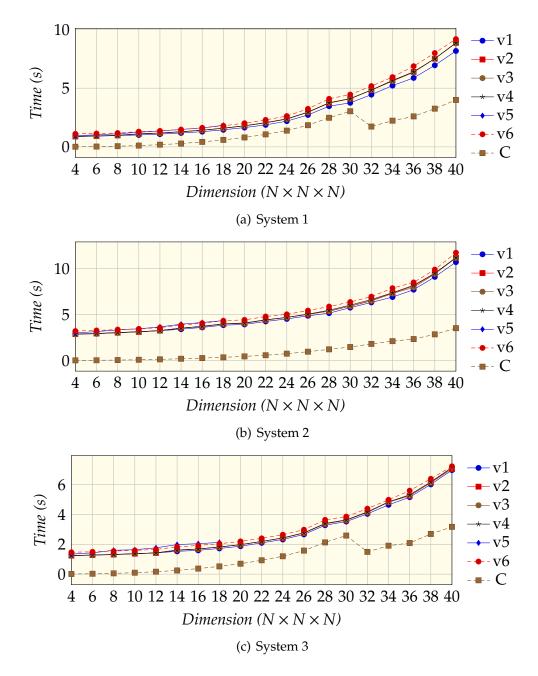

| C.1 | The time (in seconds) spent inside the kernel code for the GTX 980 system. Timed using CUDA events. This data is illustrated in Figure 5.1(a). | 80 |

| C.2 | 0                                                                                                                                              | 80 |

| C.3 | The time (in seconds) spent inside the kernel code for the<br>Titan V system. Timed using CUDA events. This data is                            | 00 |

| C.4 | illustrated in Figure 5.1(c)                                                                                                                   | 81 |

|     | local kernel setup for the GTX 980 system. Timed using gettimeofday. This data is illustrated in Figure 5.2(a)                                 | 81 |

| C.5 | 0                                                                                                                                              | -  |

|     | ing local kernel setup for the P100 system. Timed using gettimeofday. This data is illustrated in Figure 5.2(b).                               | 82 |

| C.6  | The time (in seconds) spent executing the kernel includ-         |    |

|------|------------------------------------------------------------------|----|

|      | ing local kernel setup for the Titan V system. Timed using       |    |

|      | gettimeofday. This data is illustrated in Figure 5.2(c)          | 82 |

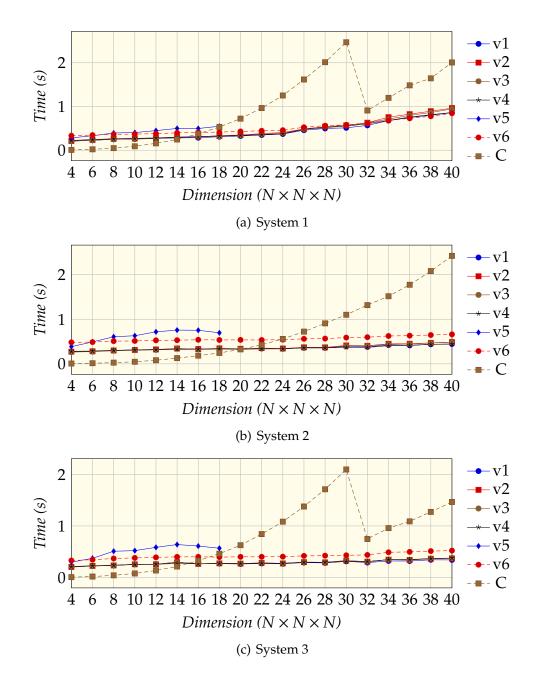

| C.7  | The total time (in seconds) spent on the GPU setup on the        |    |

|      | GTX 980 system. Timed using gettimeofday. This data is           |    |

|      | illustrated in Figure 5.3(a).                                    | 83 |

| C.8  | The total time (in seconds) spent on the GPU setup on the        |    |

|      | P100 system. Timed using gettimeofday. This data is illus-       |    |

|      | trated in Figure 5.3(b).                                         | 83 |

| C.9  | The total time (in seconds) spent on the GPU setup on the        |    |

|      | Titan V system. Timed using gettimeofday. This data is           |    |

|      | illustrated in Figure 5.3(c).                                    | 84 |

| C.10 | ) The total runtime (in seconds) of miniAMR on the GTX 980       |    |

|      | system. This data is illustrated in Figure 5.4(a)                | 84 |

| C.11 | The total runtime (in seconds) of miniAMR on the P100            |    |

|      | system. This data is illustrated in Figure 5.4(b)                | 85 |

| C.12 | The total runtime (in seconds) of miniAMR on the Titan V         |    |

|      | system. This data is illustrated in Figure 5.4(c)                | 85 |

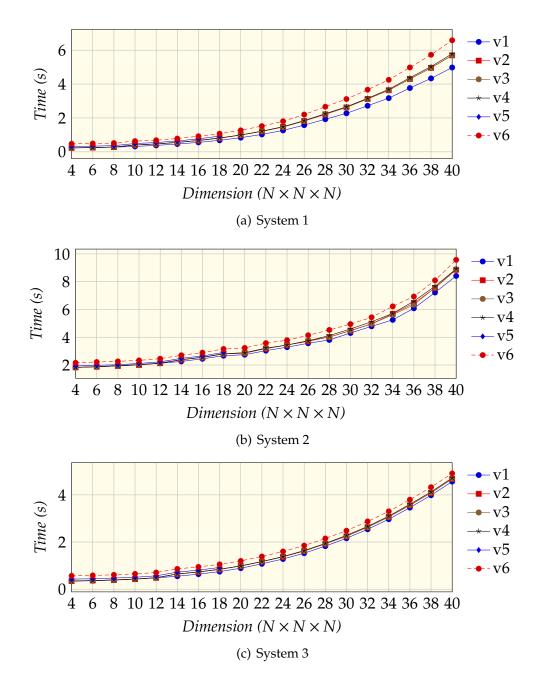

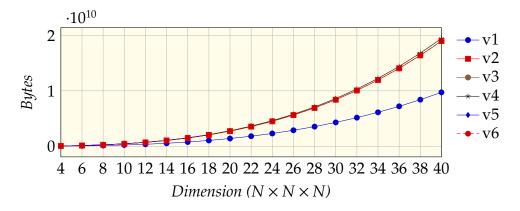

| C.13 | The amount of global memory allocated (in Bytes) on the          |    |

| _    | GPU. This data is illustrated in Figure 5.5.                     | 86 |

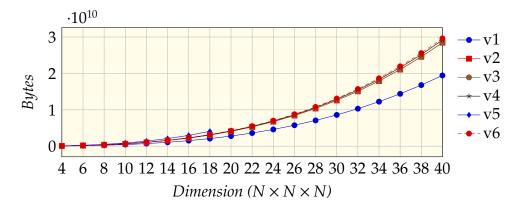

| C.14 | The amount of memory (in Bytes) copied from host to device       |    |

|      | and from device to host. This data is illustrated in Figure 5.6. | 86 |

# **List of Figures**

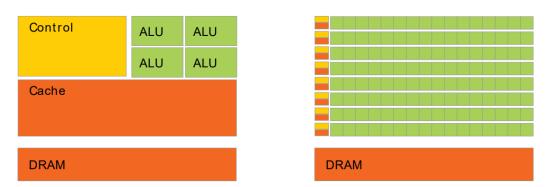

| 2.1 | The difference in hardware on the CPU and on the GPU, focusing on the distribution of DRAM, cache, control units, and ALUs for each device. From <i>CUDA C Programming</i> |          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|     | <i>Guide</i> [35] with permission.                                                                                                                                         | 9        |

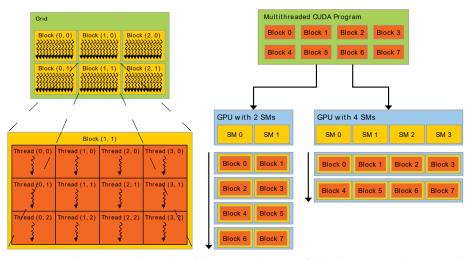

| 2.2 | Block layout and distribution. From CUDA C Programming                                                                                                                     |          |

|     | <i>Guide</i> [35] with permission.                                                                                                                                         | 10       |

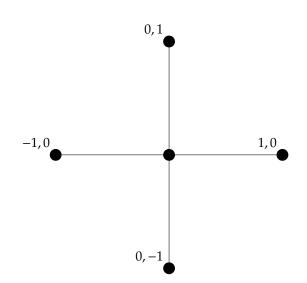

| 2.3 | A five-point stencil                                                                                                                                                       | 21       |

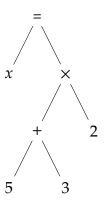

| 2.4 | The assignment $x = (5 + 3) \times 2$ represented in an AST                                                                                                                | 22       |

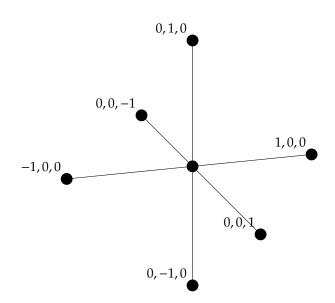

| 2.5 | The seven-point stencil used in miniAMR                                                                                                                                    | 27       |

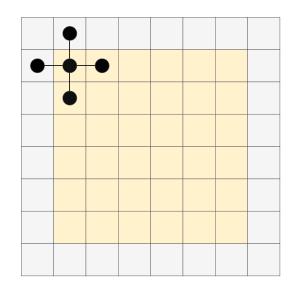

| 3.1 | A 5-point stencil calculation accessing the border memory.                                                                                                                 | 33       |

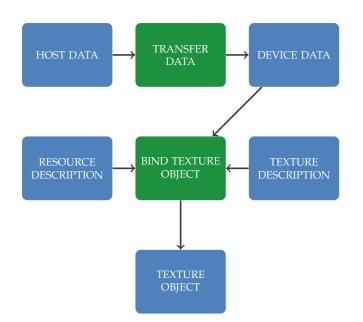

| 3.2 | Workflow for binding host data to a three-dimensional tex-                                                                                                                 |          |

|     | ture object in CUDA                                                                                                                                                        | 41       |

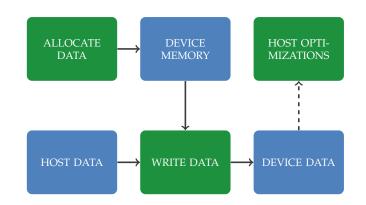

| 4.1 | General flow of device initialization in miniAMR                                                                                                                           | 44       |

| 5.1 | Time spent inside the kernel code for the GTX 980-, P100-, and Titan V-system. Timed using CUDA events.                                                                    | 55       |

| 5.2 | Kernel execution time including local kernel setup for the                                                                                                                 | 00       |

| 0.2 | GTX 980-, P100-, and Titan V-system. Timed using gettimeofda                                                                                                               | v. 56    |

| 5.3 | GPU total setup time on the GTX 980-, P100-, and Titan                                                                                                                     | <b>,</b> |

|     | V-system. Timed using gettimeofday                                                                                                                                         | 57       |

| 5.4 | Total time of miniAMR for the GTX 980-, P100-, and Titan                                                                                                                   |          |

|     | V-system.                                                                                                                                                                  | 58       |

| 5.5 | Amount of global memory allocated on the GPU                                                                                                                               | 59       |

| 5.6 | Amount of memory copied from host to device and from                                                                                                                       |          |

|     | device to host.                                                                                                                                                            | 59       |

LIST OF FIGURES

LIST OF FIGURES

# Listings

| 2.1 | An implementation of the rules of <i>Conway's Game of Life</i> [18] |    |

|-----|---------------------------------------------------------------------|----|

|     | in ImageCL.                                                         | 17 |

| 2.2 | The assignment $x = (5 + 3) \times 2$ built using the ROSE API      | 22 |

| 3.1 | Using the Block type to write a seven-point stencil in ImageCL.     | 30 |

| 3.2 | A 27-point stencil using loops in ImageCL.                          | 34 |

| 3.3 | A 27-point stencil using a single buffer to read and write          |    |

|     | using the + operator.                                               | 35 |

| 4.1 | Overview of miniAMR after integration of generated code             | 44 |

| 4.2 | Pseudo code of the reference implementation of the kernel           | 46 |

| 4.3 | Simplified ImageCL kernel using a single read-write buffer .        | 47 |

| 4.4 | Simplified ImageCL kernel using a read and write buffer             | 48 |

| 4.5 | ImageCL kernel using three-dimensional read and write               |    |

|     | buffers.                                                            | 49 |

| A.1 | ImageCL kernel using a single read-write buffer                     | 74 |

| A.2 | ImageCL kernel using read and write buffers                         | 75 |

| A.3 | ImageCL kernel using 3D read and write buffers                      | 76 |

|     |                                                                     |    |

## **List of Abbreviations**

ALU Arithmetic Logic Unit

AMR Adaptive Mesh Refinement

**API** Application Programming Interface

AST Abstract Syntax Tree

CPU Central Processing Unit

CUDA Compute Unified Device Architecture

FFT Fast Fourier Transform

FLOPS Floating Point Operations Per Second

GPU Graphics Processing Unit

HIP Heterogeneous-compute Interface for Portability

HPC High Performance Computing

ILP Instruction Level Parallelism

MIMD Multiple Instructions Multiple Data

ML Machine Learning

MPI Message Passing Interface

**OpenCL** Open Computing Language

SIMD Single Instruction Multiple Data

**SIMT** Single Instruction Multiple Threads

$\mathbf{SM} \ \text{Streaming Multiprocessor}$

SPMD Single Program Multiple Data

## Chapter 1

# Introduction

Since the end of Dennard scaling [9] around 2006, we have seen a shift from high frequency single-core systems to multi/many-core and heterogeneous systems. Multi/many-core systems takes advantage of parallelism to increase the performance of an application. This usually comes at the cost of the serial performance, as each core often comes with a lower frequency than in a single-core system [11]. Heterogeneous systems are able to provide both high single threaded performance and high parallel performance by combining a low latency CPU with a high throughput accelerator.

Although originally targeting graphics in computer games, GPUs provide a high level of parallelism and high memory bandwidth, which makes it well suited for data level parallelism. The GPUs thus have become some of the most popular accelerators used in heterogeneous systems, and can be found in both consumer and High Performance Computing (HPC) systems today.

The ability to get optimal performance of the same kernel across multiple devices, also known as *performance portability*, is a known problem for accelerators [46, 24, 43]. Frameworks such as CUDA and OpenCL provides functional portability across their supported devices. However, due to the wide range of available optimizations, devices, and architectural differences, these frameworks are not able to provide performance portability. Auto-tuning has been proposed as a solution to the performance portability issue. This involves automatically generating multiple different implementations from the same code and evaluation the performance of each version. The version with the greatest performance is then chosen as the final implementation. This can either be done with exhaustive search over the domain, which can be time-consuming, or by using a model driven approach that takes advantage of heuristics to find a subset of the domain to evaluate [14, 28].

ImageCL is a language designed by Falch and Elster (2016) [12], to provide performance portability and make it easier to write image and stencil based kernels for heterogeneous hardware. ImageCL abstracts away optimization features that would normally be required to do manually, *e.g.* the memory levels. These optimizations are instead turned into tuning parameters, which can be used to train a machine learning model that can be used as an auto-tuning model. This model can in turn be used to generate optimized device code based on the platform and device it compiles for [12, 15].

The ImageCL language provides the built-in Image type, which represents a two-dimensional grid of pixels. The Image type makes it possible to adapt stencils and other common image processing code that works on twodimensional problem domains, without restructuring the code. However, calculations that works on three-dimensional problem domains are often found in scientific and engineering code, and these are not easily adapted to the ImageCL language.

Earlier work on ImageCL includes a CUDA backend to ImageCL, and was added as part of the specialization project in the fall of 2017 [44]. This allows ImageCL to generate optimized CUDA code in addition to OpenCL code. In this thesis we will use this CUDA backend to generate our kernels from the ImageCL code.

### 1.1 **Project Goal**

In this thesis, we aim to extend the ImageCL language and its compiler to support a broader range of applications. We have decided to target miniAMR [51], an Adaptive Mesh Refinement (AMR) proxy application, because it contains a stencil computation which is well suited for ImageCL and AMR is often found in scientific and engineering applications. The miniAMR proxy application is used to guide the extensions we elect to make to ImageCL so that it can be use for a wider range of scientific applications. Our work will include investigating how well our code generated by the extensions to ImageCL is able to integrate with and improve the performance of the proxy application and its stencil kernel.

### **1.2 Contributions**

The contributions made in this thesis includes:

- The Block type extension to ImageCL, for representing three-dimensional data.

- The idz keyword extension to ImageCL, for finding the thread identity in the z-dimension.

- The none boundary condition in ImageCL, which allows for manual boundary handling.

- Extensions to the data analysis applied by ImageCL to support threedimensional optimizations.

- The offset operator in ImageCL, which allows for aliasing of Image or Block data with offset.

- The support for memory optimizations on the Block type. This includes shared memory, constant memory, and texture memory.

- Benchmarks of multiple miniAMR stencil kernels generated by ImageCL, including the ImageCL kernel code.

### **1.3** Structure of the Thesis

The remainder of this thesis is structured as follows:

**Chapter 2** presents the necessary background material and information, focusing on the GPU architecture, performance portability, and proxy applications.

**Chapter 3** presents the extensions added to the ImageCL language and compiler.

**Chapter 4** describes how the code generated from ImageCL has been integrated into the miniAMR proxy application.

**Chapter 5** presents and discusses the performance measurements of the miniAMR kernels generated by ImageCL.

Chapter 6 concludes the thesis and suggests areas suitable for future work.

**Appendix A** shows the full code of the ImageCL kernels that is used to generate the GPU kernels.

**Appendix B** illustrates the miniAMR configurations used in the performance measurements.

Appendix C presents the performance measurements in detail.

### Chapter 2

### Background

This chapter highlights some of the necessary background information in which the rest of the chapters are built on. Part of this chapter is based on the background chapter of the specialization project [44] of the author in the fall of 2017, where we extended the ImageCL compiler with a CUDA backend in addition to the register caching optimization for the CUDA backend. Section 2.1 gives a brief overview of different types of parallel computing, before Section 2.2 gives a detailed description of the GPU architecture and programming model. Section 2.3 explains the concept of performance portability and auto-tuning. Next, Section 2.4 describes the ImageCL compiler and language used to generate optimized GPU code from tuning parameters. Section 2.5 gives an overview of proxy applications and their use cases. Finally, Section 2.6 will briefly discuss earlier related work.

### 2.1 Parallel Computing

Present hardware is built to take advantage of parallelism. This requires developers to build software that is able to take advantage of this parallelism to achieve good performance. Traditionally, developers have used a serial model when designing and implementing software, but as the serial performance of hardware have stagnated, taking advantage of this parallelism have become increasingly important [11, 5, 27].

Hardware and compiler architects have tried to exploit Instruction Level Parallelism (ILP) which allows the CPU to execute multiple instructions in parallel, while still letting the user program using a serial model. However, it has shown to be difficult to take advance of ILP much further than we currently are, and ILP has reached a point of diminishing returns. Instead, more independent cores are added to the CPU that can be used to run multiple parts of the program in parallel [21].

While multi-core systems do not have the same restrictions as ILP when it comes to performance, it moves much of the complexity of parallelism on to the developers. Developers now have to represent the system using a parallel model instead of a serial model, giving more control to the developer at the cost of increasing the complexity of the software development.

#### 2.1.1 Classification of Parallelism

Parallelism is often classified as either being task-level based or data-level based. Task-level based parallelism is the simultaneous execution of individual tasks, *e.g.* execution of two independent functions in parallel. This means that separate instruction streams work on separate data streams in parallel, also known as Multiple Instructions Multiple Data (MIMD). While it is often easy to apply this kind of parallelism on separate tasks in the application, it is usually hard to find a large portion of the application that is well suited for this kind of parallelism since tasks are often dependent on each other. MIMD can also be applied as data parallelism, *e.g.* letting each thread work on on their own separate slice of an array [21].

Data level based parallelism, or data parallelism, is the simultaneous execution of an operation on chunks of data of the same workload, *e.g.* by letting each processing element work on its own part of an array. Single Instruction Multiple Data (SIMD) is one form of data parallelism which performs the same instruction on multiple items in parallel. The SIMD parallelism is exposed as special instructions that works on multiple elements, and provides a simple way for the programmer to take advantage of parallelism while still being able to use a serial model when implementing the software. However, as all elements being operated on needs to take the same instruction-path, the SIMD model can be limited in its functionality [21].

Single Program Multiple Data (SPMD) is a specialization of MIMD where the same program is executed on multiple processors with possibly different input data. This allows the control flow for each task to diverge, rather than being executed in lockstep as with the SIMD model. However, unlike SIMD, SPMD forces the programmer to use a parallel model when building the application, which increases the complexity. Message Passing Interface (MPI) [32, 48] is a standard that can be used to gain SPMD parallelism within an application. Recently, the Single Instruction Multiple Threads (SIMT) model has become popular as it is the dominant parallel model on the GPU. SIMT is a combination of SIMD and multithreading, and will be explained in more details in Section 2.2.3 [21, 42].

### 2.1.2 GPU Computing

The GPU was first introduced as a fixed pipeline accelerator for graphics that was meant to offload the compute heavy workload associated with the three-dimensional graphics rendering from the CPU [42]. However, as the GPU is particularly good at highly parallel and compute intensive workloads, it has now evolved into a more general highly parallel programmable processor. The result of this evolution is a processor like NVIDIA's GV100, based on the Volta architecture, with 5120 32-bits floating point cores, 2560 64-bits floating point cores, and a peak tera-Floating Point Operations Per Second (FLOPS) count of 15.7, which is a substantially greater amount than any CPU is able to provide. In addition, the Volta architecture introduces tensor cores that are designed specifically for deep learning [29].

The GPU is designed for a particular class of applications that provides certain characteristics that the GPU is able to take advantage of. As explained in Owens et al. (2008) [42], it needs to be an application where throughput is more important than latency, the computational requirements are large, and the opportunity for data-level parallelism is substantial. These requirements is a good fit for many scientific and high performance applications, as well as games and other graphics intensive applications [42]. Today it is common to use a heterogeneous system that combines the low-latency attribute of the CPU with the high-throughput attribute of the GPU. This provides a high value of performance, price and power usage.

The major GPU vendors, like NVIDIA, AMD, and Intel, have seen the potential of general purpose computing on the GPU and released vendor specific Application Programming Interfaces (APIs) like NVIDIA's CUDA platform [37] and AMD's Heterogeneous-compute Interface for Portability (HIP) [2], or supported open standards like OpenCL [26]. OpenCL provides functional portability to all devices that supports the OpenCL standard. This includes the majority of CPUs and GPUs, and many other specialized accelerators.

### 2.2 The GPU Architecture

This section describes the architecture of the GPU, and we will use the CUDA terms when explaining different components found in the GPU. However, you will find many of the same concepts in other vendors architecture under potentially different names, and many of the differences between CUDA and OpenCL will be explained in detail in Section 2.2.5. NVIDIA introduced the CUDA architecture in 2007 as a parallel computing platform and programming model for general computing on the GPU [38, 37].

Figure 2.1 illustrates the main structural difference between the CPU and the GPU. We can see that the CPU provides large caches and more advanced control units, while the GPU contains many simpler Arithmetic Logic Units (ALUs). This difference in architecture is the main reason the CPU excels at low-latency workloads, while the GPU excels at compute intensive, data-parallel workloads [35, 27]. In the follow sections, we will go into details of how the GPU architecture works.

#### 2.2.1 Thread Blocks

A thread block is an abstraction which represents a grouping of primitive threads that executes the same kernel. The number of threads within a

**Figure 2.1:** The difference in hardware on the CPU and on the GPU, focusing on the distribution of DRAM, cache, control units, and ALUs for each device. From *CUDA C Programming Guide* [35] with permission.

thread block is chosen based on the amount of resources desired by each thread and the desired occupancy on the Streaming Multiprocessor (SM). The threads can be organized in either a one-, two-, or three-dimensional layout within a single thread block, and the thread blocks are then organized into a grid in either a one-, two-, or three-dimensional layout [35, 21]. This is illustrated in Figure 2.2(a) where threads in a two-dimensional grid of two-dimensional blocks are organized.

This flexibility makes it easier to work with problems like multi-dimensional matrices. In addition, the thread blocks are executed independently of each other, which allows the thread blocks to be distributed across SMs differently depending on the amount of SMs available on the GPU. As illustrated in Figure 2.2(b), the GPU can distribute the workload across all available SMs, making the program scale across different devices.

### 2.2.2 Streaming Multiprocessors

The SMs are the hardware on the GPU that is able to execute the users GPU kernels. Each SM contains their own registers, caches, warp schedulers, and dispatch units, as well as execution cores for integers, and 32-bits and 64-bits floating point operations [36, 27]. In addition, the Volta architecture introduced the Tensor Core, which is a mixed-precision 16-bits and 32-bits execution core built for deep learning matrix arithmetic. The warp

(a) A two-dimensional grid of (b) Distribution of blocks on two devices with two-dimensional blocks. different amount of SMs available.

**Figure 2.2:** Block layout and distribution. From *CUDA C Programming Guide* [35] with permission.

scheduler and dispatch unit is responsible to schedule and switch contexts between warps, and to issue instructions to warps that are ready to execute, respectively. The Volta GV100 GPU from NVIDIA has 80 SMs that can execute blocks independently [29]. As seen in Figure 2.2(b), the thread blocks are mapped to the hardware by dividing them between available SMs. This asserts that each thread block gets the most resources available on each SM.

#### 2.2.3 Single Instruction Multiple Threads

The SM is able to execute hundreds of threads concurrently by taking advantage of SIMT. SIMT is an execution model where multiple threads are grouped together and executes the same instructions in lockstep on different data. In CUDA, these groups are called warps and consists of 32 threads. When a SM is given a block for execution, it partitions the threads in the block into warps that is scheduled by a warp scheduler [36].

Threads within a warp have their own instruction address counter and

register state which enables them to take different paths in the program. If threads within a warp take different paths, the warp executes each path while masking out threads not on the current path. This is called branch divergence and while this does not affect the correctness of the program, it causes the execution of branches to be serialized, leading to performance decrease [36].

Volta [29] introduced *Independent Thread Scheduling* which allows full concurrency between threads, regardless of warp. A *Schedule Optimizer* now instead groups active threads within a warp together into SIMT units, which enables the high throughput of earlier NVIDIA architectures in addition to increased flexibility as threads can diverge and reconverge at sub-warp granularity [36].

#### 2.2.4 The GPU Memory Hierarchy

There are two main groups of memory: memory located on-chip and memory located off-chip in DRAM. Memory located on-chip includes registers, shared memory, and cache. Registers are the fastest memory on the GPU and is local to each thread. The maximum amount of registers per thread in Volta is 255. However, this number will be limited by the occupancy on the SMs, and with a 100% occupancy each thread will only have access to 32 registers [29]. Shared memory is a user managed cache that is shared between all threads in the same thread block. Shared memory is divided into *banks* that can be accessed simultaneously, yielding a high memory bandwidth as long as no bank conflict happens [34, 27].

Off-chip memory includes global memory, local memory, constant memory, and texture memory. Global memory is the largest available memory on the GPU but is also one of the slowest, together with local and texture memory. Local memory is local to each thread and is used when threads does not have any available registers left or if the data is too big to fit in registers. Texture memory is read-only memory for the device and is cached so it only needs to be read from off-chip memory once. The texture cache is optimized for two-dimensional spatial locality. Constant memory is, like texture memory, read-only cached memory that can broadcast a single value to threads in a half-warp, leading to only a single memory access if all threads requests data from the same memory location. This will generate only  $\frac{1}{16}$  of the memory traffic as you would when reading from global memory [34, 27, 47].

#### 2.2.5 CUDA and OpenCL

The CUDA C language [37] is an extension of the C/C++ languages that exposes the GPU architecture to the user through an API that allows the user to create functions that can be executed on the GPU. These functions are called kernels and are executed once per thread in parallel. The CUDA API allows the user to decide the grid and block dimensionality when calling the kernels. Inside each kernel, the user is exposed to additional built-in variables and functions that interfaces with the GPU hardware. This functionality allows the user to identify the current running thread, both local to the thread block and globally in the grid, which allows the user to divide the work between the threads. In addition, the CUDA API exposes GPU specific functionality to the user, allowing optimizations not possible through regular C/C++. The memory levels are one of these, and the user can define what kind of memory the allocated data should be placed in through special keywords like \_\_shared\_\_ and \_\_global\_\_. The API also provides method to allocate, deallocate, and transfer data between the host and the device [35].

CUDA is specific to NVIDIA GPUs and is developed by the company that also designs the hardware. This allows the CUDA API to map closely to the underlying hardware architecture and computing characteristics of the NVIDIA GPU. However, this also limits the amount of devices the code can be run on. OpenCL is an open standard for accelerated computing which provides functional portability across all devices which supports the OpenCL standard. Since OpenCL needs to support a wide range of devices, the OpenCL API is more general than the CUDA API. The programming model for CUDA and OpenCL is still very similar, and while the two APIs uses different terms, they use the same grid and thread block model for execution on the GPU. Table 2.1 gives an overview of how the indexing and dimensionality is queried in each of the APIs, and Table 2.2 shows the terminology used in CUDA and OpenCL. **Table 2.1:** Difference between the CUDA and OpenCL API for index and dimension queries [25, 35].

| Description                    | CUDA (variables)                | OpenCL<br>(functions) |

|--------------------------------|---------------------------------|-----------------------|

| Amount of blocks in the grid   | gridDim                         | get_num_groups        |

| Amount of threads in the block | blockDim                        | get_local_size        |

| Index of the block             | blockIdx                        | get_group_id          |

| Local index of the thread      | threadIdx                       | get_local_id          |

| Global index of the thread     | blockIdx * blockDim + threadIdx | get_global_id         |

| Amount of threads in the grid  | gridDim * blockDim              | get_global_size       |

Table 2.2: Difference between the CUDA and OpenCL terminology [35, 20].

| CUDA                     | OpenCL          |

|--------------------------|-----------------|

| Streaming multiprocessor | Compute unit    |

| Thread                   | Work-item       |

| Thread block             | Work-group      |

| Shared memory            | Local memory    |

| Local memory             | Private memory  |

| Global memory            | Global memory   |

| Constant memory          | Constant memory |

| Texture memory           | Image memory    |

### 2.3 Performance Portability Across GPUs

While the programming models used for CUDA and OpenCL provides functional portability across all their supported devices, guaranteeing the same final outcome of a computation, the performance of said computation may vary from device to device [46, 24]. An application that is optimized for a specific device might therefore perform worse on other devices, based on the underlying hardware architecture and the resources available for each device [43]. Performance portability on the GPU is often worse than on the CPU, since the GPU architecture often changes more drastically than on the CPU. In addition, many of the optimizations on the GPU are more often exposed to the user, like shared memory and block dimensions, while on the CPU they are often done in the hardware or by the compiler, like caching and prefetching. While the block distribution, as seen in Section 2.2.1, mitigates this problem across GPUs, it does not solve it.

#### 2.3.1 Auto-Tuning

The responsibility of performance portability is thus on the user, which means it is often necessary to optimize the application for each device the application is meant to be executing on to achieve high-performance across devices. This work is not feasible for most programmers to do manually, as the amount of devices being targeted is often substantial. Additionally, the process of optimizing the application for each device itself is time consuming and prone to errors [14].

A proposed solution to the performance portability problem on the GPU is auto-tuning. Auto-tuning is the act of automatically generating implementation candidates, measuring the performance of these candidates, and then choosing the best one based on the measurements [14]. Auto-tuning has seen successful use in areas like Fast Fourier Transform (FFT) with the FFTW library [17], and linear algebra with the ATLAS library [7], among others. Auto-tuning can be done empirically, but as the amount of possible implementation candidates can be large it can be a time consuming and impractical solution.

A model-driven approach for auto-tuning is often a better solution, as it

narrows down the search space before it evaluates the implementation candidates. It achieves this by introducing a performance model that applies some heuristic or domain knowledge to find a subset of the implementation candidates that are most likely to be one of the optimal solutions. However, the accuracy of model-driven auto-tuning is dependent on the quality of the model, which usually requires a lot of time and high domainknowledge of the target architectures to implement. Machine Learning (ML) methods have been used to train the auto-tuning model instead of manually implementing it. This is done by generating implementation candidates that can be used to train an ML based performance model. This model can then be used to predict the subset of implementation candidates that is most likely to perform well, and then evaluate these [14, 28].

The ability to use ML to train a performance model, is one of the main driving factors for the development of ImageCL and its tuning parameters, which will be described in Section 2.4.

### 2.4 ImageCL

The OpenCL and CUDA languages exposes the user to many distinct and often complex optimization opportunities. However, while a certain combination of optimizations might lead to good performance on the device being targeted, it might lead to worse performance on another. This section describes the ImageCL language and compiler developed by Falch and Elster [12, 15]. ImageCL tries to make GPU programming easier by turning the optimization opportunities exposed in OpenCL and CUDA into tuning parameters which can be handled by an auto-tuner instead.

### 2.4.1 The ImageCL Language

ImageCL is a programming language designed to simplify the process of creating image processing kernels for heterogeneous hardware. The language is based on the same programming model used by OpenCL and CUDA. However, it makes some changes to the model to simplify the process. In contrast to OpenCL and CUDA, where the programmer works in a two-level thread hierarchy as seen in Subsection 2.2.1, ImageCL only defines a single flat thread space. The size and dimensionality of the thread blocks are turned into an implementation detail instead [12].

Like in OpenCL and CUDA, the ImageCL kernel represents the work performed by a single thread, but ImageCL defines the built-in variables idx and idy which represents the identity of the thread in x-, and ydirection, respectively. These built-in variables can be used to easily access the data element, also referred to as pixels, corresponding to each thread in the grid. This is in contrast to CUDA especially, where the user is exposed to the local thread identity within a thread block, in addition to the dimensionality and size of the thread blocks and the grid. This often forces the user to do the calculations manually to get the corresponding data element for a thread [12].

ImageCL also provides a custom datatype called Image that can be mapped to the grid, defining the size and dimensionality of the grid to be the same as the Image. The Image datatype allows for two-dimensional indexing, making it easy to apply idx and idy to access the pixels in the Image. In addition, the user is able to specify a boundary condition that enables outof-bounds accesses to be well defined on Images. This boundary condition can either be set to clamped, meaning that the accesses outside the image is set to the closest pixel within the image, or as a constant value specified by the user.

Listing 2.1 shows an implementation of the rules of *Conway's Game of Life* [18] in ImageCL. In the example we can see how the grid is mapped to the Image and how the boundary condition is set to a constant value, i.e 0. It also illustrates how the built-in variables idx and idy are used to access the Image in a stencil pattern.

As explained in Section 2.2.4, the GPU has multiple types of memory that is exposed to the user in both CUDA and OpenCL. This makes the memory mapping complex for the user, as each memory level can affect the performance of the application in some way. ImageCL abstract away these different memory levels and exposes the user to only a single flat address space [12].

```

#pragma imcl grid(v, o)

#pragma imcl boundary_cond(v:constant)

void conway(Image<int> v, Image<int> o){

int sum = v[idx - 1][idy - 1]

+ v[idx][idy - 1]

+ v[idx + 1][idy - 1]

+ v[idx - 1][idy]

+ v[idx + 1][idy]

+ v[idx - 1][idy + 1]

+ v[idx][idy + 1]

+ v[idx + 1][idy + 1];

if (v[idx][idy] == 1) {

if (sum == 2 || sum == 3) {

o[idx][idy] = 1;

} else {

o[idx][idy] = 0;

}

} else if (sum == 3) {

o[idx][idy] = 1;

} else {

o[idx][idy] = 0;

}

}

```

**Listing 2.1:** An implementation of the rules of *Conway's Game of Life* [18] in ImageCL.

### 2.4.2 The ImageCL Compiler

The ImageCL compiler is a source-to-source compiler, or transpiler, which currently is able to generate OpenCL and CUDA code. All the complexity that the ImageCL language abstracts away, like the memory levels and the thread hierarchy, are turned into tuning parameters that each corresponds to one possible implementation in OpenCL or CUDA, where each implementation will have a distinct optimization applied. While these tuning parameters could be given manually by the user, the ImageCL compiler is meant to be used together with an auto-tuner that is able to pick the best performing parameters for a given device. This tuning phase operates together with an auto-tuner to generate multiple implementation candidates. The source code is analyzed to find the possible parameter space, which is then fed into the auto-tuner. The auto-tuner generates the parameter values and the ImageCL compiler creates a candidate implementation that is benchmarked to find the execution time. The auto-tuner can repeat these steps multiple times until it is confident that the best implementation candidate has been found [12, 15].

#### 2.4.3 Tuning Parameters

This section describes the tuning parameters used in ImageCL. Since ImageCL is a programming language focusing on image computation, which includes stencil based computations, the tuning parameters will be most specific towards the types of optimizations which benefits stencil computations and other computations found mostly in image processing. The following tuning parameters are currently used in the ImageCL compiler [12, 15]:

- Thread block size: The thread block size can play a decisive role in the performance of the application. One reason is that communication between threads often happens through shared memory, which is local to each block. So dependent on the communication pattern in the application, the optimal thread block size might vary. Another reason is that the number of blocks needed will vary based on the size of the blocks, and the amount of scheduling done by the SMs will vary based on the number of blocks used, as illustrated in Figure 2.2(b) in Section 2.2.1. The grid size however, is mapped to the data and is therefore not a tuning parameter.

- **Thread coarsening:** Thread coarsening is how much work each thread will perform. While the GPU should use thousands of threads to fully utilize the hardware, the input data might be millions of elements long. In that case it might be better to let each thread perform more work instead of spawning millions of threads. This is done by

letting each thread work on a local block of pixels. The dimensionality of this local block is also part of the tuning parameter, since the access pattern of the kernel might give an performance impact based on it.

- **Thread mapping:** The thread mapping describes the access pattern used by the threads. For example, if a thread is assigned pixels in a contiguous block of memory, the access pattern could give good spatial locality. However, on the GPU this might give overall worse performance as the access pattern has poor coalescing [34, 35]. By instead using interleaved memory access it might be possible to get a performance increase as the memory access will be coalesced into fewer total memory accesses.

- The memory parameters: All the memory levels used as tuning parameters in ImageCL are described in Section 2.2.4 and each of them provides their own distinct benefits and drawbacks depending on the contexts they are used in. Additionally, not all memory types can be used depending on the kernel, like texture and constant memory, since they are read-only from device and can thus not be modified. By turning them into tuning parameters, ImageCL lets the auto-tuner predict if it is beneficial to use them instead of global memory in that particular case.

- Loop unrolling: Loop unrolling, or loop unwinding, is an optimization that repeats the loop body while adjusting the loop counter to match the total amount of work done. This can lead to reduced branch penalty from the loop, reduce the overall executed instructions, and potentially exposes more parallelism to the compiler. However, loop unrolling can also lead to increased program size which can potentially lead to an increase in instruction cache misses, hinder function inlining as the inlined code size would be multiplied with the degree of loop unrolling, and possibly lead to worse branch prediction if the iterations contained branching [33].

Since there are both significant benefits and disadvantages of applying loop unrolling, ImageCL turns it into a tuning parameter and lets the auto-tuner decide what to do.

• Register caching: Register caching is a CUDA specific optimization

that uses a warp-local cache built up from registers. Registers provide both higher bandwidth and lower access latency than shared memory, but using registers as a user managed cache instead of shared memory has historically not been an option due to their thread local lifetimes. However, NVIDIA's Kepler architecture introduced the shuffle instruction which made it possible for threads within a warp to share data without going through other memory levels, *e.g.* shared memory [39].

To apply register caching as an optimization, we need an access pattern which is well suited for manual caching, like stencil computations which provides a predictable access pattern at compile time. Usually, shared memory has been used for this kind of memory optimizations, but this is also a use-case well suited for register caching. Register caching also performs store-and-load operations in a single step, in contrast to shared memory, and eliminates the need for expensive thread block-wise synchronization. This provides register caching an additional performance advantage compared to shared memory as long as registers are not spilled into local memory [13].

## 2.4.4 Stencil Computations

Stencil computation is a kind of computation that involves determining the value of an element in a grid according to a fixed access pattern, called a stencil. Stencil computations are often found in scientific code like image processing, discretized differential equations, and adaptive mesh refinement. Stencils comes in many different variants, and Figure 2.3 shows a five-point stencil used to determine the value of a single element in a two-dimensional grid. Stencil computations are well suited for the GPU, as each element in the grid can be computed independently of each other. In addition, stencil computation uses a fixed access pattern which makes them particularly well suited for register caching since register caching needs to know the access pattern at compile time [13, 40].

The computing time and memory usage of stencil computations grows linearly with the amount of elements within an array. This means that parallel implementations of stencil computations are of high importance

Figure 2.3: A five-point stencil.

in areas like scientific computing, where the working sets are usually very large. Stencil computations are therefore one of the main targets for the ImageCL language, and provides easy abstractions for working with these sort of computations.

#### 2.4.5 The ROSE Compiler Infrastructure

The ImageCL compiler is implemented using ROSE [45]. ROSE is an open source compiler infrastructure to build source-to-source program transformation and analysis tools for large scale applications. It particularly targets custom tools for static analysis, program optimization, performance analysis, and cybersecurity. It consists of multiple different front-ends for different languages and currently supports C [6], C++ [16], FORTRAN [54], UPC [50], and OpenMP [41] for C, C++, and FORTRAN applications.

The intermediate representation used in ROSE is a high level Abstract Syntax Tree (AST) that is well suited for source-to-source transformations, which allows the user to do analysis, optimizations, and transformations on it. An example of a simple AST is illustrated in Figure 2.4. By modifying the AST we can insert and modify the necessary code to generate optimized GPU code which has been abstracted away and replaced by

**Figure 2.4:** The assignment  $x = (5 + 3) \times 2$  represented in an AST.

tuning parameters. When we have finished transforming the AST to represent valid OpenCL or CUDA code and applied the given optimizations, ROSE is able to traverse the AST and generate the corresponding source code. Listing 2.2 illustrates how the AST in Figure 2.4 would be built using the ROSE API.

```

auto *assignment = buildAssignStatement(

buildVarRefExp("x", scope),

buildMultiplyOp(

buildAddOp(

buildIntVal(5),

buildIntVal(3)

),

buildIntVal(2)

)

);

```

**Listing 2.2:** The assignment  $x = (5 + 3) \times 2$  built using the ROSE API.

The program analysis available includes call graph analysis, control flow analysis, data flow analysis, class hierarchy analysis, data- and systemdependence analysis, and MPI communication pattern analysis. The optimizations and translations functionality also includes partial redundancy elimination, constant folding, inlining, outlining, OpenMP directive lowering, automatic parallelization and loop transformations [45].

## 2.5 **Proxy Applications**