# Instruction Set for Bit-Banging Operations

Increasing flexibility for low power communication

# Henrik Olav Solvang

Master of Science in ElectronicsSubmission date:January 2016Supervisor:Kjetil Svarstad, IETCo-supervisor:Jan Frode Lønnum, Nordic Semiconductor ASA

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# PROBLEM DESCRIPTION

# Title:Instruction Set for Bit-Banging OperationsIncreasing flexibility for low power communication

Focus: Computer architecture, Processor design, Serial Communication.

Bit-banging techniques are being widely used by embedded programmers to emulate dedicated hardware in microcontrollers. Today a wide range of serial engines such as SPI, UART, UASRT, TWI, USB, I2S, MIPI etc. are required in a broad range ASIC targeted for high volume production. It is costly in terms of development time and chip area to make dedicated circuitry for these diverse communication protocols.

In order to increase the efficiency of communication protocols based on bitbanging methodology, this master thesis will propose a new core logic unit with an efficient instruction set for performing bit-banging operations. It is important that the architectural study on the instruction set is targeting efficient operations, high flexibility and the stringent timing requirements found in many communication peripherals. A more general use of the instruction set beyond serial engines should be considered. If time permits an example engine in C/SystemVerilog should be developed.

| Responsible professor: | Kjetil Svarstad, IET                   |

|------------------------|----------------------------------------|

| Supervisor:            | Jan Frode Lønnum, Nordic Semiconductor |

### ABSTRACT

A microcontroller can only offer a limited amount of communication interfaces. When designing an ASIC targeted for high volume production, flexibility must often give way to increased energy efficiency. The limitation in the number and types of communication interfaces may force embedded designers to use inefficient bit-banging techniques to communicate with various modules. Can a co-processor optimized for bit-banging provide this flexibility with an acceptable loss in power efficiency, compared to dedicated hardware modules?

A cycle-accurate instruction set simulator has been developed to support the design of instruction sets and optimization of the bit-banging programs. It is also used to determine the run/sleep ratio for these programs on the individual instruction sets. Complexity based power estimations, that make use of power and complexity measures from an ARM Cortex M0 implementation, are used to estimate the dynamic power consumption of the various instruction sets.

A new set of instructions, called the SOL-instructions, was developed to optimize the output and input of serial data. Together with the addition of the *REPEAT*-instruction, a 36% reduction in active time was achieved compared to a simple instruction set. Compared to dedicated modules the difference in dynamic power consumption vary with transmission frequency. The power consumption range from 6.7%(UART, 9.6kbps) to 529%(SPI, 1000kbps) of the dedicated hardware's power consumption.

Flexibility is added at the cost of reduced power efficiency for high speed transmissions. The bit-banging processor is perhaps best suited as an addition to existing modules. It can not completely replace dedicated modules for common protocols, but show very promising results as an alternative to bit-banging in the host processor.

### SAMMENDRAG (NORWEGIAN)

En mikrokontroller kan bare tilby et begrenset antall kommunikasjonsgrensesnitt. Når man designer en ASIC som skal produseres i høyt volum, må ofte fleksibilitet ofres for økt energieffektivitet. Begrensningen i antall kommunikasjonsgrensesnitt kan tvinge utviklere av innebygde systemer til å bruke inneffektive bit-banging-teknikker for å kommunisere med ulike moduler. Kan en coprosessor som er optimalisert for bit-banging tilby denne fleksibiliteten med et akseptabelt tap i energieffektivitet, sammenlignet med spesialiserte hardwaremoduler?

En syklus-nøyaktig instruksjonssett-simulator har blitt utviklet for å støtte designet av instruksjonssett og optimaliseringen av bit-banging-programmene. Den blir også brukt til å bestemme aktiv/inaktiv-forholdet for disse programmene for de individuelle instruksjonssettene.

Et nytt sett med instruksjoner, kalt SOL-instruksjoner, har blitt utviklet for å optimalisere utmating og innmating<sup>1</sup> av seriell data. Sammen med REPEATinstruksjonen ble den aktive kjøretiden redusert med 36% i forhold til et simpelt instruksjonssett. Sammenlignet med spesialiserte hardware-moduler så varierer forskjellen i dynamisk effektforbruk med overføringsfrekvensen. Effektforbruket varierer fra 6,7%(UART, 9.6kbps) til 529%(SPI, 1000kbps) av de spesialiserte hardware-modulenes effektforbruk.

Fleksibiliteten er økt på bekostning av redusert energieffektivitet for høyhastighets-kommunikasjon. Bit-banging-prosessoren er kanskje best egnet som et tillegg til eksisterende moduler. Den kan ikke erstatte spesialiserte hardwaremoduler for de mest brukte protokollene, men er et veldig lovende alternativ til bit-banging i vertsprosessoren.

<sup>1</sup> Output/Input

#### PREFACE

This thesis completes a Master of Science degree in Electronics, Design of Digital Systems. The assignment was given by Nordic Semiconductor in August 2015, and the thesis was delivered in January 2016.

While my studies have focused on the design of digital circuits, this thesis focuses on an architectural approach to a problem. With no accurate measurements of the chip power nor complexity available, and with no time to perform such measurements, a practical approach to power estimations was adopted. It was challenging to perform, and not nearly as satisfying as having more trustable results, but at an architectural level it is simply not practical to implement all solutions. It has been very educational to work at this level of abstraction, and I believe the work has given me valuable insight into the early stages of chip design. Insight that I will benefit from as an engineer.

I would like to thank my Professor Kjetil Svarstad for his advice during the design and writing processes. Jan Frode Lønnum, who has been my supervisor at Nordic Semiconductor, for advice and proofreading of the thesis. And finally I would like to thank Vemund Bakken for designing the problem, for very helpful advice in the starting phases of my work, and for input on the thesis.

Henrik Olav Sollesnes Solvang NTNU, IET Trondheim, January 24, 2016

# CONTENTS

|   | Abs | ract                                                                                            | iii |

|---|-----|-------------------------------------------------------------------------------------------------|-----|

|   |     | mendrag (Norwegian)                                                                             | v   |

|   |     |                                                                                                 | vii |

| 1 |     | RODUCTION                                                                                       | 1   |

| - | 1.1 | Motivation                                                                                      | 1   |

|   | 1.2 | Contributions                                                                                   | 2   |

|   | 1.3 |                                                                                                 | 2   |

|   | 1.4 | Method                                                                                          | 3   |

|   | 1.5 | Structure of the thesis                                                                         | 3   |

| 2 |     | KGROUND AND PREVIOUS WORK                                                                       | 5   |

| 2 | 2.1 | Bit-banging                                                                                     | 5   |

|   | 2.1 | Protocols                                                                                       | 5   |

|   | 2.2 | 2.2.1 Serial Peripheral Interface – SPI                                                         | 5   |

|   |     | 2.2.1       Serial Fempheral Interface = 511         2.2.2       Inter-Integrated Circuit – I2C | 8   |

|   |     |                                                                                                 | 11  |

|   |     |                                                                                                 | 11  |

|   | 2.3 |                                                                                                 | 13  |

|   | 2.4 |                                                                                                 | 13  |

|   | 2.1 | 7.8                                                                                             | 14  |

|   |     | I                                                                                               | 14  |

|   |     |                                                                                                 | 15  |

|   |     |                                                                                                 | 16  |

|   | 2.5 |                                                                                                 | 17  |

|   | 2.6 | , <u> </u>                                                                                      | 17  |

|   | 2.0 |                                                                                                 | 17  |

|   |     | J I I I I I I I I I I I I I I I I I I I                                                         | 19  |

|   |     |                                                                                                 | 19  |

|   | 2.7 |                                                                                                 | 19  |

|   | 2.8 |                                                                                                 | 20  |

|   | 2.9 |                                                                                                 | 21  |

| 3 | PRO |                                                                                                 | 23  |

| 4 |     |                                                                                                 | 27  |

| T | 4.1 |                                                                                                 | 27  |

|   | 4.2 |                                                                                                 | 28  |

|   | 4.3 | 0                                                                                               | 29  |

|   | 4.4 | -                                                                                               | 29  |

|   | 4.5 | -                                                                                               | 30  |

|   | 4.6 |                                                                                                 | 30  |

|   | 4.7 |                                                                                                 | 31  |

|   | ±•/ |                                                                                                 | ~ - |

|   | 4.8                                                                                      | A-programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 33                                                                                                                                                                                             |

|---|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.9                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 36                                                                                                                                                                                             |

| 5 | INS                                                                                      | TRUCTION SET ARCHITECTURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                                                                                                                                             |

|   | 5.1                                                                                      | Minimal Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                                                                                                                                             |

|   |                                                                                          | 5.1.1 Protocols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38                                                                                                                                                                                             |

|   |                                                                                          | 5.1.2 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 43                                                                                                                                                                                             |

|   | 5.2                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 43                                                                                                                                                                                             |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44                                                                                                                                                                                             |

|   | 5.3                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 44                                                                                                                                                                                             |

|   |                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 46                                                                                                                                                                                             |

|   |                                                                                          | 5.3.2 Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 47                                                                                                                                                                                             |

|   | 5.4                                                                                      | SOL instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48                                                                                                                                                                                             |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                                                             |

|   | 5.5                                                                                      | SOL and Repeat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50                                                                                                                                                                                             |

|   | 5.6                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                                                                                                                                                             |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                                                                                                             |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55                                                                                                                                                                                             |

|   | 5.7                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56                                                                                                                                                                                             |

|   | 011                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58                                                                                                                                                                                             |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                                                                                                                                             |

|   | 5.8                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                                                                                                                                             |

|   | 5.9                                                                                      | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 62                                                                                                                                                                                             |

| 6 | POW                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63                                                                                                                                                                                             |

| 0 | 100                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00                                                                                                                                                                                             |

|   | 61                                                                                       | Power estimation method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 63                                                                                                                                                                                             |

|   | 6.1<br>6.2                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 63<br>64                                                                                                                                                                                       |

|   | 6.2                                                                                      | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64                                                                                                                                                                                             |

|   |                                                                                          | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65                                                                                                                                                                                       |

|   | 6.2                                                                                      | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65<br>65                                                                                                                                                                                 |

|   | 6.2                                                                                      | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65<br>65<br>69                                                                                                                                                                           |

|   | 6.2                                                                                      | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65<br>65<br>69<br>70                                                                                                                                                                     |

|   | 6.2                                                                                      | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65<br>65<br>69<br>70<br>70                                                                                                                                                               |

|   | 6.2<br>6.3                                                                               | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65<br>69<br>70<br>70<br>71                                                                                                                                                               |

|   | <ul><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                            | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>64</li> <li>65</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> </ul>                                                                                     |

|   | 6.2<br>6.3                                                                               | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>64</li> <li>65</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> </ul>                                                                         |

| П | <ul><li>6.2</li><li>6.3</li><li>6.4</li><li>6.5</li></ul>                                | The Cortex M0 as a baselinePower estimate per functionality6.3.1Unused functions6.3.2Repeat6.3.3SOL6.3.4Conditionals6.3.5Parallel ExecutionDedicated modules6.5.1Equivalent power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>64</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> </ul>                                                                         |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>COM                                                          | The Cortex M0 as a baselinePower estimate per functionality6.3.1Unused functions6.3.2Repeat6.3.3SOL6.3.4Conditionals6.3.5Parallel ExecutionDedicated modules6.5.1Equivalent powerConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstructionConstruction< | <ul> <li>64</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> </ul>                                                             |

| 7 | <ul> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>COM</li> <li>7.1</li> </ul> | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65<br>69<br>70<br>70<br>71<br>71<br>72<br>73<br>75<br>75                                                                                                                                 |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>COM<br>7.1<br>7.2                                            | The Cortex M0 as a baseline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 64<br>65<br>69<br>70<br>70<br>71<br>71<br>72<br>73<br>75<br>75<br>76                                                                                                                           |

|   | 6.2<br>6.3<br>6.4<br>6.5<br>CON<br>7.1<br>7.2<br>7.3                                     | The Cortex M0 as a baseline       Power estimate per functionality         Power estimate per functionality       6.3.1         Unused functions       6.3.1         G.3.1       Unused functions         G.3.2       Repeat         G.3.3       SOL         G.3.4       Conditionals         G.3.5       Parallel Execution         Dedicated modules       Power         G.5.1       Equivalent power         GINED RESULTS       Inter-Integrated Circuit – I2C         Universal Asynchronous Receiver/Transmitter – UART       Serial Peripheral Interface – SPI                                                                                                                                                                                                                                                                          | 64<br>65<br>69<br>70<br>70<br>71<br>71<br>71<br>72<br>73<br>75<br>75<br>76<br>77                                                                                                               |

| 7 | 6.2<br>6.3<br>6.4<br>6.5<br>COM<br>7.1<br>7.2<br>7.3<br>DISC                             | The Cortex M0 as a baseline       Power estimate per functionality         Power estimate per functionality       6.3.1         Unused functions       6.3.2         6.3.2       Repeat       6.3.2         6.3.3       SOL       6.3.3         6.3.4       Conditionals       6.3.4         6.3.5       Parallel Execution       6.3.4         Dedicated modules       6.3.5       Parallel Execution         Estimation results       6.5.1       Equivalent power         6.5.1       Equivalent power       6.5.1         Inter-Integrated Circuit – I2C       12C         Universal Asynchronous Receiver/Transmitter – UART       6.5.1         Serial Peripheral Interface – SPI       6.5.1                                                                                                                                            | <ul> <li>64</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>76</li> <li>77</li> <li>79</li> </ul>                         |

|   | 6.2<br>6.3<br>6.4<br>6.5<br>COM<br>7.1<br>7.2<br>7.3<br>DISC<br>8.1                      | The Cortex M0 as a baseline       Power estimate per functionality         Power estimate per functionality       6.3.1         Unused functions       6.3.2         Repeat       6.3.2         6.3.2       Repeat         6.3.3       SOL         6.3.4       Conditionals         6.3.5       Parallel Execution         6.3.6       Parallel Execution         Dedicated modules       6.5.1         Estimation results       6.5.1         Equivalent power       6.5.1         Inter-Integrated Circuit – I2C       12C         Universal Asynchronous Receiver/Transmitter – UART       12C         Serial Peripheral Interface – SPI       12C         CUSSION       Power estimation                                                                                                                                                   | <ul> <li>64</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>75</li> <li>76</li> <li>77</li> <li>79</li> <li>79</li> </ul>             |

|   | 6.2<br>6.3<br>6.4<br>6.5<br>COM<br>7.1<br>7.2<br>7.3<br>DISC<br>8.1<br>8.2               | The Cortex M0 as a baseline         Power estimate per functionality         6.3.1       Unused functions         6.3.2       Repeat         6.3.3       SOL         6.3.4       Conditionals         6.3.5       Parallel Execution         Dedicated modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>64</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>76</li> <li>77</li> <li>79</li> <li>80</li> </ul>             |

|   | 6.2<br>6.3<br>6.4<br>6.5<br>CON<br>7.1<br>7.2<br>7.3<br>DISC<br>8.1<br>8.2<br>8.3        | The Cortex M0 as a baseline         Power estimate per functionality         6.3.1       Unused functions         6.3.2       Repeat         6.3.3       SOL         6.3.4       Conditionals         6.3.5       Parallel Execution         6.3.6       Parallel Execution         Dedicated modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>64</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>76</li> <li>77</li> <li>79</li> <li>80</li> <li>81</li> </ul> |

|   | 6.2<br>6.3<br>6.4<br>6.5<br>COM<br>7.1<br>7.2<br>7.3<br>DISC<br>8.1<br>8.2               | The Cortex M0 as a baseline         Power estimate per functionality         6.3.1       Unused functions         6.3.2       Repeat         6.3.3       SOL         6.3.4       Conditionals         6.3.5       Parallel Execution         6.3.6       Parallel Execution         Dedicated modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>64</li> <li>65</li> <li>69</li> <li>70</li> <li>70</li> <li>71</li> <li>71</li> <li>72</li> <li>73</li> <li>75</li> <li>76</li> <li>77</li> <li>79</li> <li>80</li> </ul>             |

|     | 8.6   | Voltage scaling                  | 82 |

|-----|-------|----------------------------------|----|

| 9   | CON   | ICLUSION                         | 83 |

|     | 9.1   | Recommendations for Further Work | 83 |

| Bil | oliog | raphy                            | 85 |

| Aŗ  | opend | lix                              | 89 |

| A   | CEL   | L LIST                           | 91 |

# LIST OF FIGURES

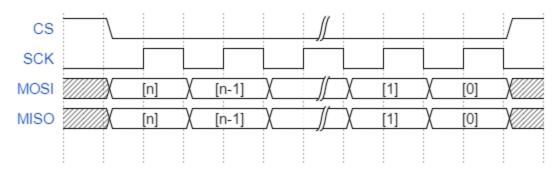

| Figure 2.1  | Simple SPI transaction                                          | 6  |

|-------------|-----------------------------------------------------------------|----|

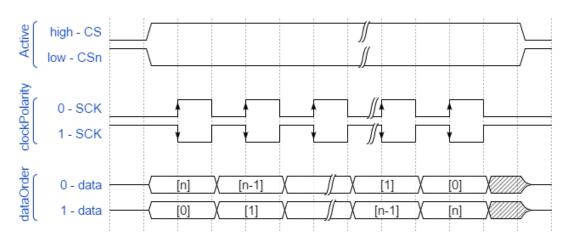

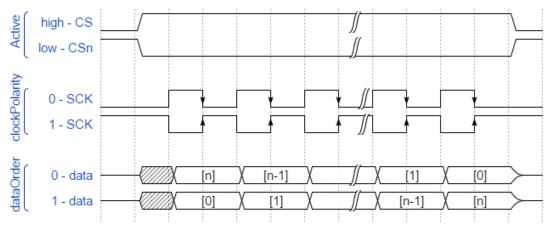

| Figure 2.2  | SPI configurations with sampling on the leading edge.           | 7  |

| Figure 2.3  | SPI configurations with sampling on the trailing edge.          | 7  |

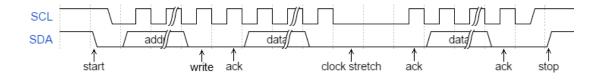

| Figure 2.4  | Typical transfer of two bytes on I2C                            | 9  |

| Figure 2.5  | Slave <i>clock-stretches</i> to catch up when master writes two |    |

| 0           | bytes of data.                                                  | 9  |

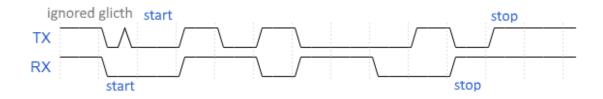

| Figure 2.6  | Glitch in start of UART TX.                                     | 12 |

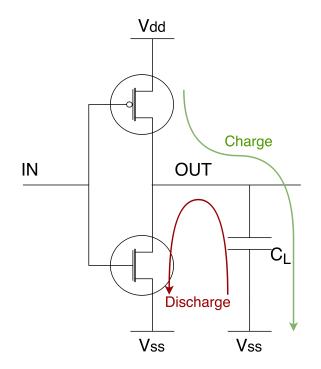

| Figure 2.7  | Switching power in a CMOS inverter                              | 18 |

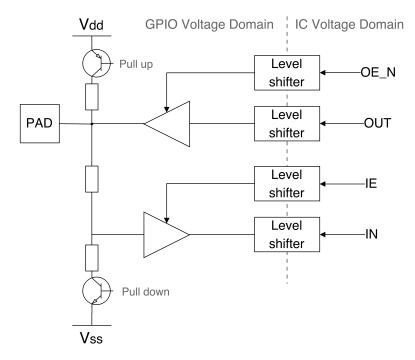

| Figure 2.8  | Nordic semiconductor input/output pad                           | 20 |

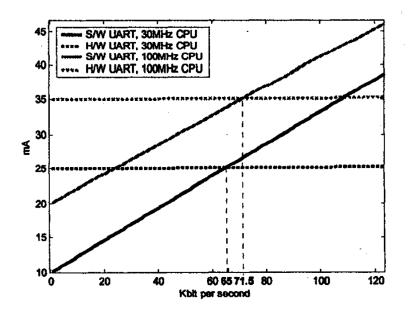

| Figure 2.9  | Power consumption of UART implemented on a CPU                  |    |

|             | compared to a dedicated hardware module[1]                      | 22 |

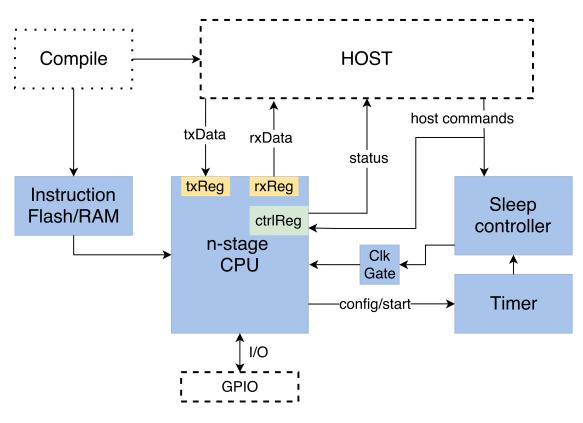

| Figure 3.1  | Bit-banging processor architecture illustration.                | 23 |

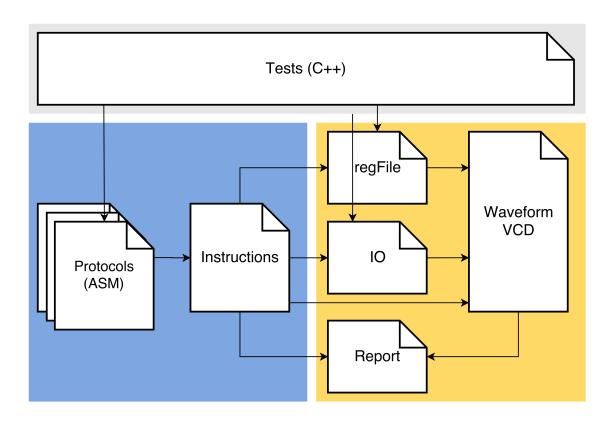

| Figure 4.1  | File structure and control flow of the instruction set sim-     |    |

|             | ulator                                                          | 28 |

| Figure 4.2  | VCD-file                                                        | 29 |

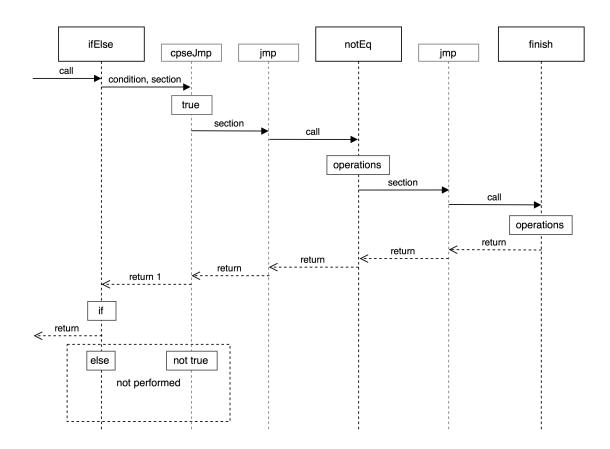

| Figure 4.3  | Flow graph of the algorithm shown in algorithm 4.12b.           | 35 |

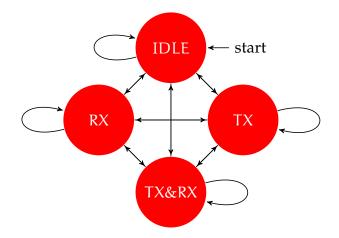

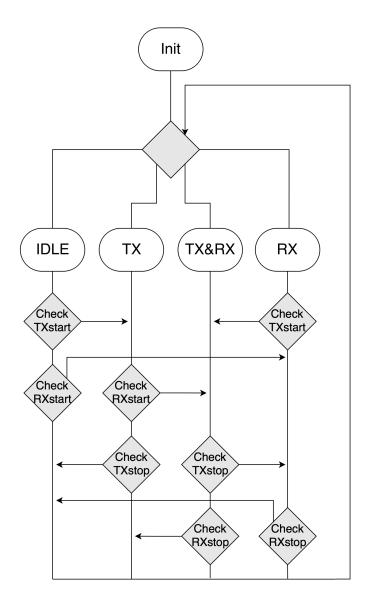

| Figure 5.1  | State chart for UART                                            | 42 |

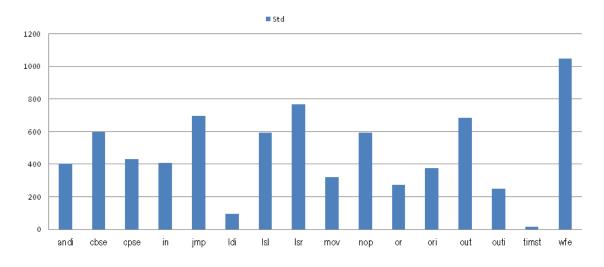

| Figure 5.2  | Simulation results for minimal ISA                              | 43 |

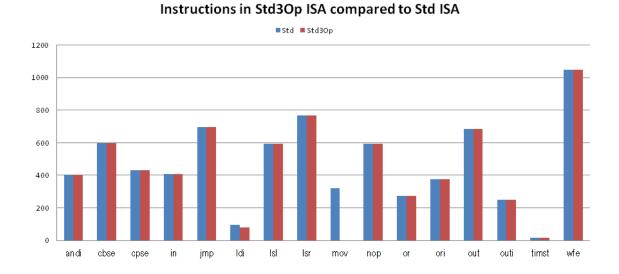

| Figure 5.3  | Simulation results for three operand ISA                        | 44 |

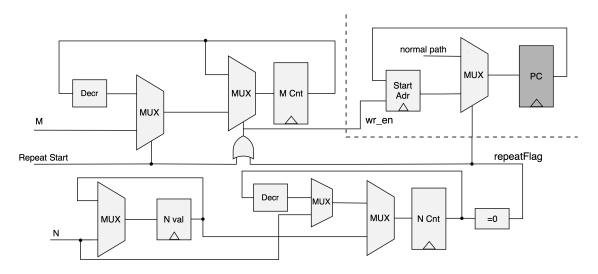

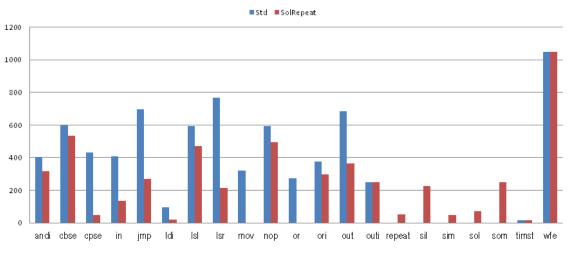

| Figure 5.4  | Illustration of hardware implementation of the REPEAT-          |    |

|             | instruction                                                     | 45 |

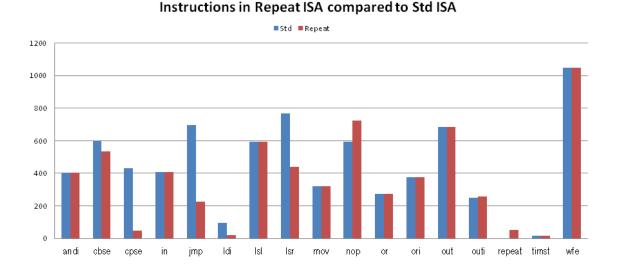

| Figure 5.5  | Simulation results for REPEAT ISA                               | 48 |

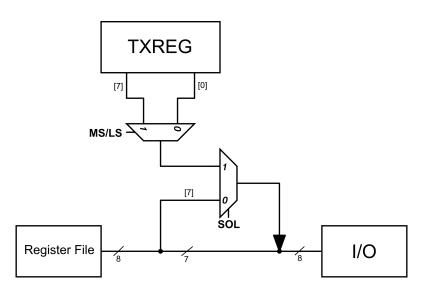

| Figure 5.6  | SOL TX instructions(SOL/SOM) in hardware                        | 50 |

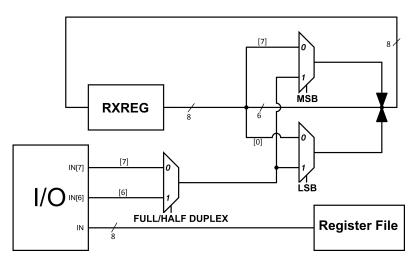

| Figure 5.7  | SOL RX instructions(SIL/SIM) in hardware                        | 51 |

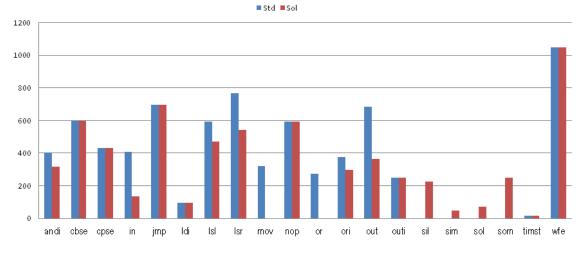

| Figure 5.8  | Simulation results for SOL ISA                                  | 51 |

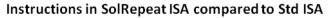

| Figure 5.9  | Simulation results for SOL and REPEAT ISA                       | 51 |

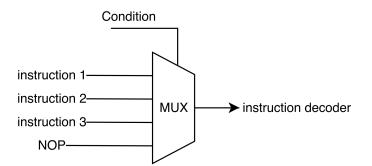

| Figure 5.10 | Illustration of conditional execution implementation            | 54 |

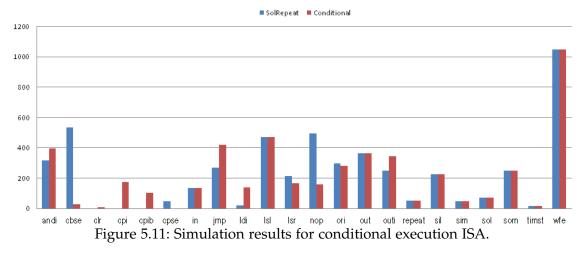

| Figure 5.11 | Simulation results for conditional execution ISA                | 55 |

| Figure 5.12 | Illustration of the UART program in the parallel execu-         |    |

|             | tion instruction set. Operations shown as horizontal ar-        |    |

|             | rows does not incur a pipeline flush                            | 57 |

| Figure 5.13 | Illustration of parallel execution implementation               | 57 |

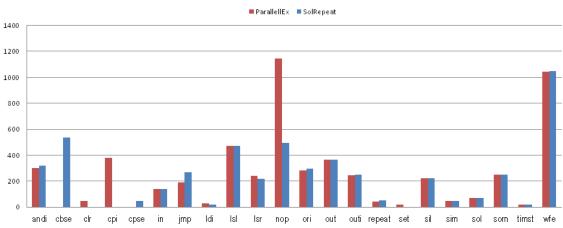

| Figure 5.14 | Simulation results for parallel execution ISA                   | 60 |

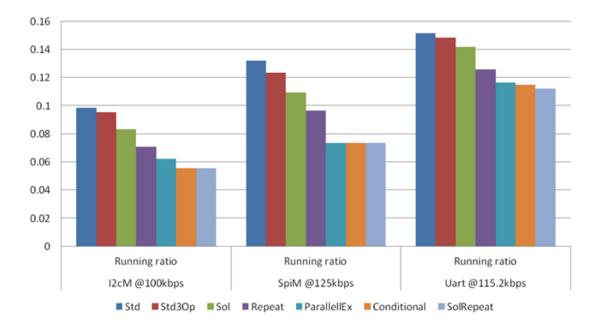

| Figure 5.15 | Running ratio for all instruction sets divided by protocol.     | 61 |

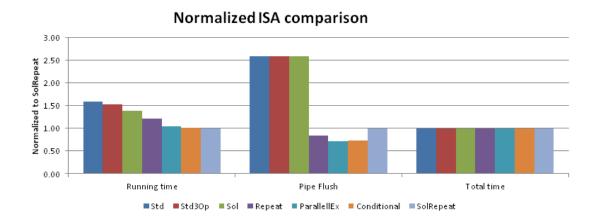

| Figure 5.16 | Running and total time of benchmark on all instruction          |    |

|             | sets, normalized to SolRepeat.                                  | 62 |

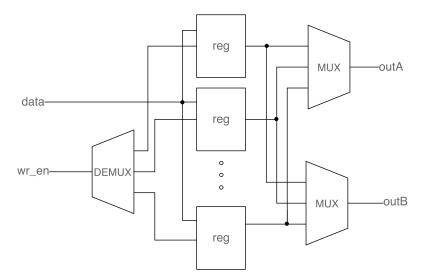

| Figure 6.1  | Simple register file model.                                     | 66 |

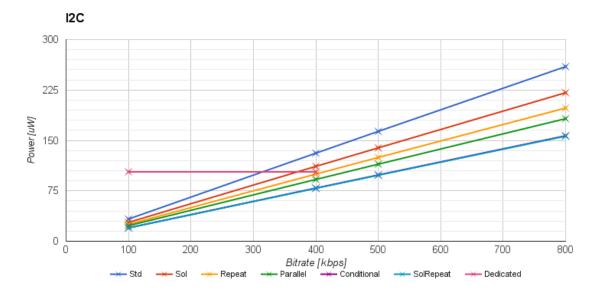

| Figure 7.1 | Power estimates for the I2C protocol divided by imple- |    |

|------------|--------------------------------------------------------|----|

|            | mentation.                                             | 75 |

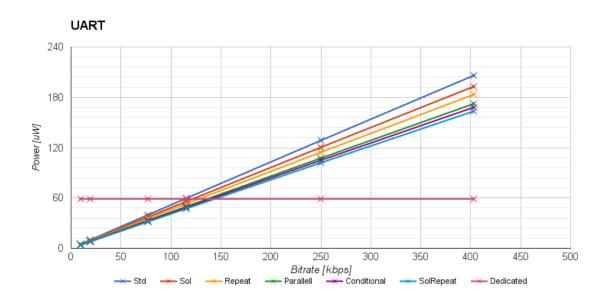

| Figure 7.2 | Power estimates for the UART protocol divided by im-   |    |

|            | plementation                                           | 76 |

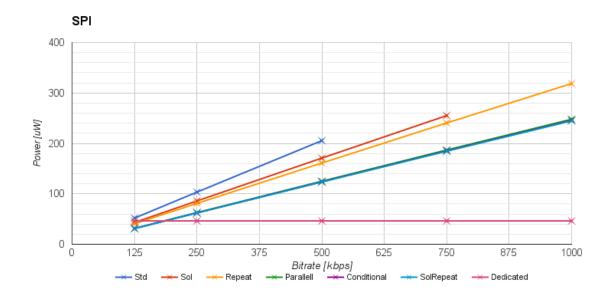

| Figure 7.3 | Power estimates for the SPI protocol divided by imple- |    |

|            | mentation.                                             | 77 |

# LIST OF TABLES

| Table 2.1  | Typical structure of SDA when transmitting two bytes.     | 9  |

|------------|-----------------------------------------------------------|----|

| Table 2.2  | UART frame                                                | 12 |

| Table 2.3  | Structure of an instruction with corresponding mnemonic   |    |

|            | assembly code                                             | 14 |

| Table 5.1  | Minimal Instruction set                                   | 37 |

| Table 5.2  | Condition register and condition checks                   | 53 |

| Table 5.3  | Maximum bitrates for SolRepeat ISA.                       | 62 |

| Table 6.1  | Cortex M0 area and dynamic power consumption              | 64 |

| Table 6.2  | Area and power estimates of register reduction            | 67 |

| Table 6.3  | Area and power estimates of addition/subtraction func-    |    |

|            | tionality                                                 | 67 |

| Table 6.4  | Area and power estimates of datapath width reduction      | 68 |

| Table 6.5  | Area and power estimates of multiplier                    | 68 |

| Table 6.6  | Area and power estimates of Repeat functionality          | 69 |

| Table 6.7  | Area and power estimates of SOL functionality             | 70 |

| Table 6.8  | Area and power estimates of Conditional functionality.    | 71 |

| Table 6.9  | Area and power estimates of Parallel Execution            | 71 |

| Table 6.10 | Power estimates of dedicated hardware modules             | 72 |

| Table 6.11 | Area and current estimates of unused Cortex M0 func-      |    |

|            | tionality, and reduced Cortex M0 core                     | 72 |

| Table 6.12 | Area and current estimates of each instruction set archi- |    |

|            | tecture                                                   | 73 |

|            |                                                           |    |

# LIST OF ALGORITHMS

| 2.1  | SPI master bit-banging                                           | 7          |

|------|------------------------------------------------------------------|------------|

| 2.2  | I2C master start bit and address transfer                        | 10         |

| 2.3  |                                                                  | 10         |

| 2.4  |                                                                  | 11         |

| 2.5  |                                                                  | 12         |

| 2.6  |                                                                  | 13         |

| 2.7  |                                                                  | 17         |

| 2.7  | Assembly pseudo-language example.                                | L          |

| 4.8  | I-functions used in the simulator                                | 32         |

| 4.9  |                                                                  | 32         |

| 4.10 |                                                                  | 33         |

|      |                                                                  | 34         |

|      |                                                                  | 35         |

| 1.12 |                                                                  |            |

| 5.13 | Start-up A-program for the SPI-protocol                          | 38         |

|      |                                                                  | <b>4</b> 0 |

|      |                                                                  | <b>4</b> 0 |

| 5.16 |                                                                  | 41         |

| 5.17 |                                                                  | 12         |

|      |                                                                  | 12         |

|      |                                                                  | 16         |

|      |                                                                  | 47         |

|      | Outputting single bit from a register without destroying data in | ~ .        |

| 0.21 |                                                                  | <b>1</b> 9 |

| 5 22 |                                                                  | 53         |

|      |                                                                  | 58         |

|      |                                                                  |            |

|      |                                                                  | 59         |

| 5.25 | UART RX parallel execution A-program                             | 50         |

# ACRONYMS

**BBP** Bit Banging Processor

- SPI Serial Peripheral Interface

- UART Universal Asynchronous Receiver/Transmitter

- 12c Inter-Integrated Circuit

- 12s Inter-Integrated Sound

- TWI Two Wire Interface

- ASIC Application-Specific Integrated Circuit

- RISC Reduced Instruction Set Computer

- **CISC** Complex Instruction Set Computer

1/0 Input/Output

- ISA Instruction Set Architecture

- PC Program Counter

- **RTL** Register Transfer Level

- CPU Central Processing Unit

- LSB Least Significant Bit

- мsв Most Significant Bit

- Aнв Advanced High-performance Bus

- VCD Value Change Dump

- ALU Arithmetic Logic Unit

- ASPR Application Program Status Register

- Instruction Acronyms: see table 5.1 and chapter 5.

# INTRODUCTION

Reducing power consumption in ASIC designs has been an important topic for research and development for many years. The innovations in low power has created, and continues to create, new markets as well as constantly improving existing product lines. Optimizing for battery life and performance is as important as ever, but in the process of doing so the complexity constantly increases. The market for low-power microcontrollers is changing. The bulk of the market is large companies with time and resources to design complex systems. However, small start-ups achieving rapid innovation through the use of off-the-shelf modules is an increasingly important group of users. To capture these markets, ease of use is an important factor, and this includes the ease of which a microcontroller can communicate with existing modules.

### 1.1 MOTIVATION

Communication with sensors, external memory, motors and other external onor off-chip modules is an intrinsic part of any microcontroller. There are several different communication protocols, where Inter Integrated Circuit(I2C), Serial Peripheral Interface(SPI) and Universal Asynchronous Receiver/Transmitter(UART) are among the most common. In serial communication, data is sent one bit at a time. If the microprocessor is used to transmit and receive these bits, known as bit-banging, it can have a severe impact on performance and power consumption. Traditionally, this is solved by adding peripheral modules that communicates on the bus with minimal interaction from the microprocessor. It is necessary to add one module for each open communication port, so the number of available ports is limited. In the Nordic Semiconductor chip *nRF52* there are in total one Inter-Integrated Sound(I2S), one UART, two Two Wire Interface(TWI, I2C-compatible) and three SPI modules. Some of these modules share resources so only five modules can be active simultaneously, where the two SPI-s and two TWI-s share resources. Although this selection of communication protocols may suffice in most cases, they still represent a limitation when the microcontroller is used in a larger system. Can an application specific processor designed to bit-bang protocols be a more flexible alternative, and what impact does it have on power? In this thesis the architecture of such a processor will be investigated. It is not expected that the power consumption will equal the consumption of dedicated hardware, but it is hoped that it can be well within an order of magnitude.

#### 1.2 CONTRIBUTIONS

A cycle-accurate instruction set simulator has been created in C. The simulator emulates timing and creates waveform-files which can be viewed in a waveform viewer. It is simple to add and remove features of the simulated instruction sets, and seven instruction set variations has been implemented. The simulator can handle conditional parallel execution, where one of three fetched instructions is performed. Finally, the simulator creates report files that can be used to compare different instruction set implementations.

A concept architecture for a bit-banging processor has been created, and power consumption for this processor has been estimated. The ARM Cortex M0 is used as a baseline for power estimates. Based on analysis, the size of some Cortex M0 features has been calculated to allow for more accurate power estimations. The hardware-cost of implementing some instructions has been calculated for the same reason. The simulation and hardware estimation results have been combined to compare the different bit-banging processor implementations to each other and to dedicated hardware.

Using the simulator and power estimates, an instruction set architecture with promising results in terms of power efficiency has been created. A processor based on the instruction set architecture can be added to a microcontroller to offer a flexible communication module at an acceptable reduction in power efficiency, compared to dedicated hardware. Suggestions to further improve the power consumption of the bit-banging processor is presented.

#### 1.3 LIMITATIONS

Time is the number one limiting factor when writing a thesis, and consequently it is important to limit the scope of the thesis to ensure that all tasks can be performed with the necessary depth. The main focus of this thesis is to develop an instruction set which is optimized for serial communication. It was decided that an RTL-implementation of the processor would not be feasible. Since there has been no RTL-implementation, the power estimates are based on an existing processor, the ARM Cortex M0. Although the Cortex M0 is a low-power processor, it is a larger and more powerful processor than the bit-banging processor. Through analysis and existing estimates, the size of Cortex M0 submodules that are not included in the bit-banging processor has been calculated and removed, but the accuracy of the power estimations are not expected to be high. Furthermore, complexity-based power estimation is not a very accurate method, and this further reduces the reliability of the power estimations. There has not been time to consider all aspects of the protocol implementations. Specifically, clockstretching in I2C and clock synchronization in UART, are not implemented.

# 1.4 METHOD

The instruction set simulator has been designed using an iterative design methodology with ad-hoc testing. Using testbenches in the instruction set simulator to verify the results, the instruction sets have been developed using an analysis based methodology to explore the major candidates for improving the power efficiency. The power estimation is performed using an analysis based gate equivalent model widely used in industry for fast, architectural, power estimations.

# 1.5 STRUCTURE OF THE THESIS