# Processing Core for Compressing Wireless Data

The Enhancement of a RISC Microprocessor

Eskil Viksand Olufsen

Master of Science in Electronics Submission date: June 2006 Supervisor: Einar Johan Aas, IET Co-supervisor: Tor Audun Ramstad, IET Robin Osa Hoel, Chipcon AS

Norwegian University of Science and Technology Department of Electronics and Telecommunications

# **Problem Description**

Compression of data in wireless systems is not a well-defined problem. Each application of compression needs to address different data types. This wide variety has made a single, efficient, compression technique hard to find. The only way to approach compression for this type of problem is to involve hybrid techniques or adapt different compression methods for different applications.

Today, most SoC solutions have an embedded microprocessor to handle complex control tasks, and Texas Instruments Norway has developed the NanoRisc microprocessor for this purpose. Texas Instruments Norway wishes to explore the NanoRiscs ability to process lossless data compression algorithms, and examine enhancements to improve its performance on these tasks.

The thesis should include an analysis of the NanoRiscs current ability to process different lossless data compression algorithms, and examine and implement area efficient enhancements to the NanoRisc core.

Assignment given: 16. January 2006 Supervisor: Einar Johan Aas, IET

## Abstract

This thesis explores the ability of the proprietary Texas Instruments embedded 16 bits RISC microprocessor, NanoRisc, to process common lossless compression algorithms, and propose extensions in order to increase its performance on this task.

In order to measure performance of the NanoRisc microprocessor, the existing software tool chain was enhanced for profiling and simulating the improvements, and three fundamentally different adaptive data compression algorithms with different supporting data structures were implemented in the NanoRisc assembly language. On the background of profiling results, some enhancements were proposed:

- Bit field instructions.

- New load and store instructions for table data structures.

- An instruction improving read and writes of variable length codewords from memory.

- An instruction improving CRC-16 checksum calculation.

- Non-blocking load behavior.

These new enhancements improved throughput of the three implemented algorithms by between 18% and 103%, and the code sizes decreased between 6% and 31%. The bit field instructions also reduced RAM access by up to 53%. The enhancements were implemented in the NanoRisc VHDL model and synthesized. Synthesis reports showed an increase in gate count of 30%, but the whole NanoRisc core is still below 7k gates. Power consumption per MIPS increased by 7%, however reduced clock cycle count and memory access decreased the net power consumption of all tested algorithms. It is also shown that data compression with the NanoRisc prior to transmission in a low power RF transceiver may increase battery lifetime 4 times.

Future work should include a comprehensive study of the effect of the proposed enhancements to more common applications for the NanoRisc microprocessor.

# Acknowledgements

I want to express my gratitude to Texas Instruments Norway for giving me the opportunity to write this thesis and providing me with a work place.

Special thanks goes to my supervisor Robin Hoel for his guidance, advices and encouraging comments.

Thanks also to Peder Rand for patient guidance when helping me understand the tools and behavior of the NanoRisc core.

I also want to thank the employees at Texas Instrument Norway for a pleasant and educational working environment.

# **Table of Contents**

| IN | NTRODUCTION                                                                                         | 1 |

|----|-----------------------------------------------------------------------------------------------------|---|

| 1  | THEORY                                                                                              | 2 |

|    | 1.1 Measures                                                                                        | 2 |

|    | 1.2 ENTROPY CODING                                                                                  |   |

|    | 1.2.1 Entropy Coding Schemes Used for Evaluation                                                    |   |

|    | 1.2.1.1 Rice Coding                                                                                 |   |

|    | 1.2.1.2 Huffman Coding                                                                              |   |

|    | 1.2.1.3 LZ77                                                                                        | 6 |

| 2  | RELATED WORKS                                                                                       | 8 |

|    | 2.1 Phillips Trimedia                                                                               | 9 |

|    | 2.2 ARM                                                                                             |   |

| 2  | THE NANORISC PROCESSOR                                                                              |   |

| 3  |                                                                                                     |   |

|    | 3.1 Architecture                                                                                    |   |

|    | 3.2 INSTRUCTION SET                                                                                 |   |

|    | 3.3 Tools                                                                                           |   |

|    | 3.3.1 Assembler                                                                                     |   |

|    | 3.3.2 Simulator                                                                                     |   |

| 4  | IMPLEMENTATION OF THE COMPRESSION ALGORITHMS                                                        |   |

|    | 4.1 IMPLEMENTATION OF RICE CODING                                                                   |   |

|    | 4.1.1 Calculating the K-value                                                                       |   |

|    | 4.1.2 Modeling Stage                                                                                |   |

|    | 4.2 IMPLEMENTATION OF HUFFMAN CODING                                                                |   |

|    | 4.2.1 Updating the Huffman tree                                                                     |   |

|    | 4.2.2 Implementing the Tree Data Structure                                                          |   |

|    | 4.3 IMPLEMENTATION OF LZ77                                                                          |   |

|    | 4.3.1 Simplified Deflate<br>4.3.2 Searching for Matches                                             |   |

|    | <ul><li>4.3.2 Searching for Matches</li><li>4.3.3 The Dictionary Data Structure</li></ul>           |   |

|    |                                                                                                     |   |

| 5  | ENHANCEMENTS OF EXISTING TOOLS                                                                      |   |

|    | 5.1 Profiling                                                                                       |   |

|    | 5.1.1 Profiling With the Assembler                                                                  |   |

|    | 5.1.1.1 Implementation                                                                              |   |

|    | 5.1.2 Profiling In the Simulator                                                                    |   |

|    | 5.1.2.1 Implementation                                                                              |   |

|    | 5.2.1 Adding New Instructions to the Assembler                                                      |   |

|    | 5.2.1 Adding New Instructions to the Assembler                                                      |   |

| 6  | FINDING ENHANCEMENTS FOR THE NANORISC PROCESSOR                                                     |   |

| 6  |                                                                                                     |   |

|    | 6.1 INSTRUCTION LEVEL PROFILING                                                                     |   |

|    | 6.1.1 Profiling Rice                                                                                |   |

|    | 6.1.2 Profiling Huffman                                                                             |   |

|    | <ul> <li>6.1.3 Profiling Deflate</li> <li>6.2 PROPOSALS FROM INSTRUCTION LEVEL PROFILING</li> </ul> |   |

|    | 6.2 PROPOSALS FROM INSTRUCTION LEVEL PROFILING<br>6.2.1 Instruction Level Enhancements              |   |

|    | 6.2.1 Instruction Level Enhancements<br>6.2.2 Adding Non-Blocking Load Behavior                     |   |

|    | 6.2.3 Estimating Speedup                                                                            |   |

|    | 6.3 ALGORITHMIC LEVEL PROFILING                                                                     |   |

|    | 6.3.1 Profiling Rice                                                                                |   |

|    | 6.3.2 Profiling Huffman                                                                             |   |

|    | 6.3.3 Profiling Deflate                                                                             |   |

|    | 6.4 PROPOSALS FROM ALGORITHMIC LEVEL PROFILING                                                      |   |

| 6.4.1 The Stream Function                           | 46 |

|-----------------------------------------------------|----|

| 6.4.2 The Hash Function                             |    |

| 6.5 PROPOSED ENHANCEMENTS FOR THE NANORISC          |    |

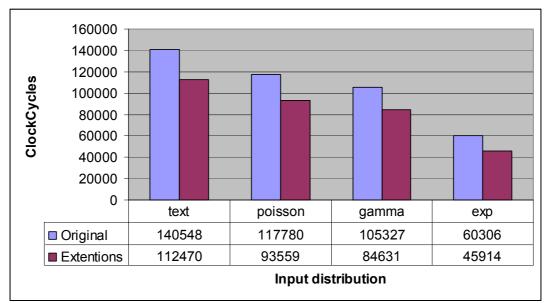

| 6.6 RESULTS OBTAINED FROM THE PROPOSED ENHANCEMENTS |    |

| 7 THE ENHANCED NANORISC PROCESSOR                   | 51 |

| 7.1 IMPLEMENTATION                                  |    |

| 7.1.1 Non-Blocking Load Behavior                    |    |

| 7.1.2 Bit Field Instructions                        | 53 |

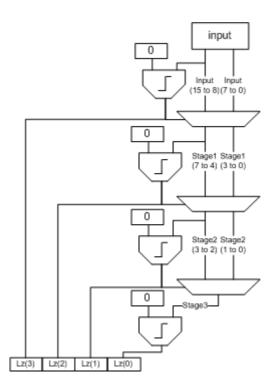

| 7.1.3 Clz Module                                    | 55 |

| 7.1.4 Crc Module                                    |    |

| 7.1.5 The Str Instruction                           |    |

| 7.2 Synthesis                                       |    |

| 7.2.1 Timing                                        |    |

| 7.2.2 Area                                          |    |

| 7.2.3 <i>Power</i>                                  |    |

| 7.3 Performance                                     |    |

| 7.3.1 Energy Savings                                |    |

| 7.3.2 Benchmarks                                    | 64 |

| 8 DISCUSSION                                        | 66 |

| 8.1 Enhancements                                    |    |

| 8.2 POWER                                           |    |

| 8.3 TIMING AND THROUGHPUT                           |    |

| 8.4 Assembly Source Code                            |    |

| 8.5 Area                                            |    |

| 8.6 A COMPARISON                                    |    |

| 8.7 FUTURE WORK                                     |    |

| 8.7.1 Processor Core                                |    |

| 8.7.2 Testing                                       |    |

| 8.7.3 Tools                                         |    |

| CONCLUSION                                          |    |

| REFERENCES                                          |    |

| APPENDIX                                            | 74 |

| A. NEW INSTRUCTIONS                                 |    |

| B. SYMBOL DISTRIBUTIONS                             |    |

| C. INSTRUCTION LEVEL PROFILING                      |    |

| D. ALGORITHMIC LEVEL PROFILING                      |    |

| E. Zip-File                                         |    |

# List of Figures

| Figure 2, video codec<br>Figure 3, phillips trimedia architecture [7].<br>Figure 4, ARM9E datapath [8]<br>Figure 5, simple overwiev of the NanoRisc architecture [reference 8].<br>Figure 6, memory set up.<br>Figure 7, NanoRisc data flow diagram.<br>Figure 8, Assembler command line syntax.<br>Figure 9, NanoRisc ISS screenshot.<br>Figure 10, the Rice algorithm flowchart.<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14]                                                                                                                                                                                                                                                                                                                                                                           | 9<br>11<br>12<br>13<br>14<br>16<br>17<br>19<br>20                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Figure 4, ARM9E datapath [8]<br>Figure 5, simple overwiev of the NanoRisc architecture [reference 8]<br>Figure 6, memory set up.<br>Figure 7, NanoRisc data flow diagram.<br>Figure 8, Assembler command line syntax.<br>Figure 9, NanoRisc ISS screenshot.<br>Figure 10, the Rice algorithm flowchart.<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14].                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ol> <li>11</li> <li>12</li> <li>13</li> <li>14</li> <li>16</li> <li>17</li> <li>19</li> <li>20</li> </ol> |

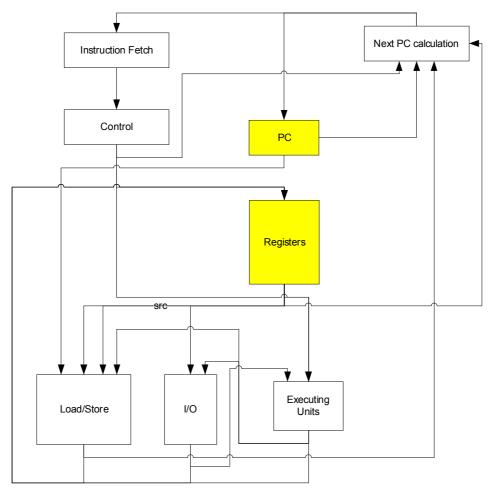

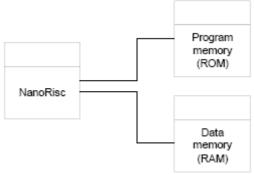

| Figure 5, simple overwiev of the NanoRisc architecture [reference 8]<br>Figure 6, memory set up<br>Figure 7, NanoRisc data flow diagram<br>Figure 8, Assembler command line syntax<br>Figure 9, NanoRisc ISS screenshot<br>Figure 10, the Rice algorithm flowchart<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12<br>13<br>14<br>16<br>17<br>19<br>20                                                                     |

| Figure 6, memory set up.<br>Figure 7, NanoRisc data flow diagram.<br>Figure 8, Assembler command line syntax.<br>Figure 9, NanoRisc ISS screenshot.<br>Figure 10, the Rice algorithm flowchart.<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13<br>14<br>16<br>17<br>19<br>20                                                                           |

| Figure 6, memory set up.<br>Figure 7, NanoRisc data flow diagram.<br>Figure 8, Assembler command line syntax.<br>Figure 9, NanoRisc ISS screenshot.<br>Figure 10, the Rice algorithm flowchart.<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13<br>14<br>16<br>17<br>19<br>20                                                                           |

| Figure 8, Assembler command line syntax.<br>Figure 9, NanoRisc ISS screenshot.<br>Figure 10, the Rice algorithm flowchart.<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16<br>17<br>19<br>20                                                                                       |

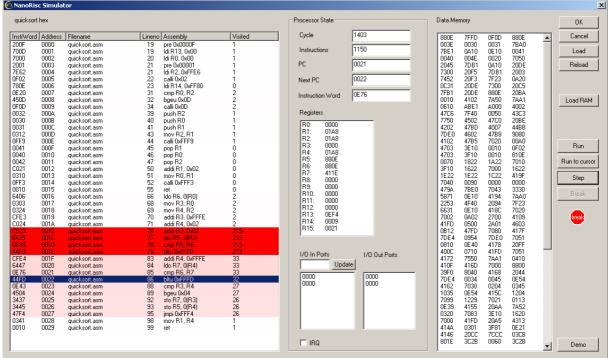

| Figure 9, NanoRisc ISS screenshot.<br>Figure 10, the Rice algorithm flowchart.<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17<br>19<br>20                                                                                             |

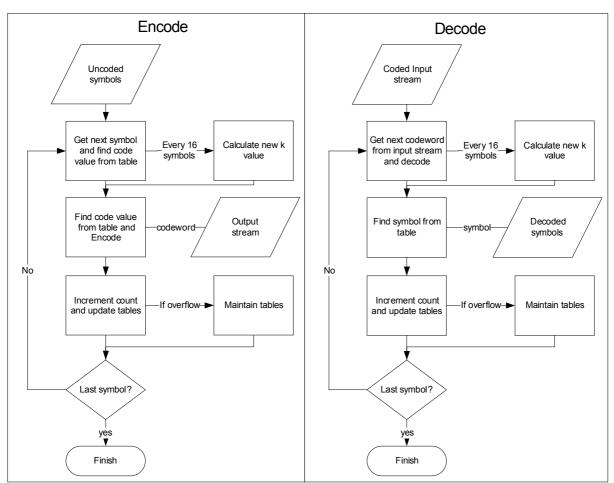

| Figure 10, the Rice algorithm flowchart<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19<br>20                                                                                                   |

| Figure 10, the Rice algorithm flowchart<br>Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the<br>alternative approach. (symbol count is 16) [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19<br>20                                                                                                   |

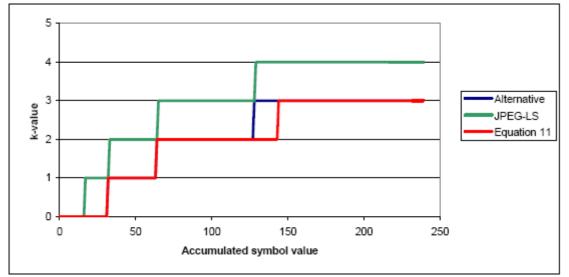

| Figure 11, calculation of the k-value using equation 6, the JPEG-LS method and the alternative approach. (symbol count is 16) [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 20                                                                                                         |

| alternative approach. (symbol count is 16) [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

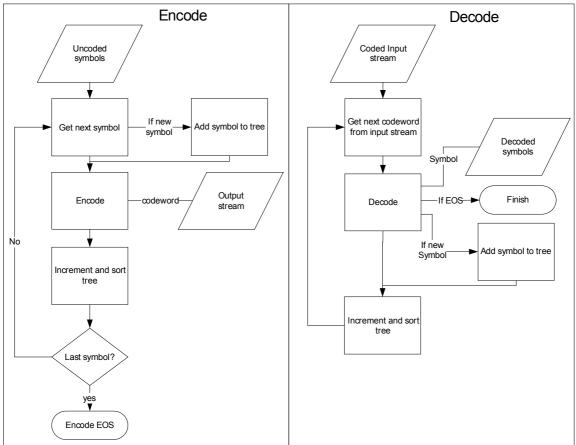

| Figure 13, Huffman tree showing the sibling property.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                            |

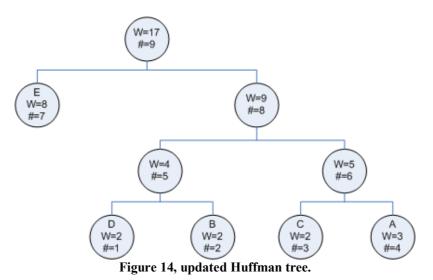

| Figure 14, updated Huffman tree.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                            |

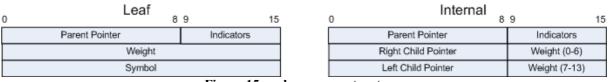

| Figure 15, node memory structure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

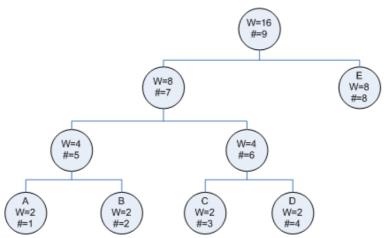

| Figure 16, initial Huffman tree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

| Figure 19, profile labels syntax.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

| Figure 20, enhanced NanoRisc ISS GUI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31                                                                                                         |

| Figure 21, Profile window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32                                                                                                         |

| Figure 22, new ISA dialog window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                            |

| Figure 23, example insertion of a bit field (6 clock cycles)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

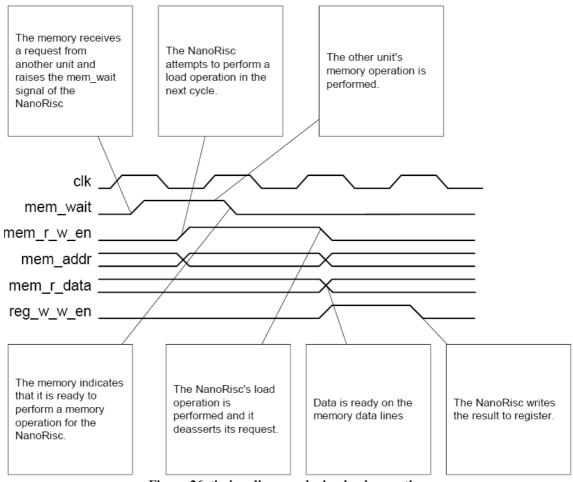

| Figure 26, timing diagram during load operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                            |

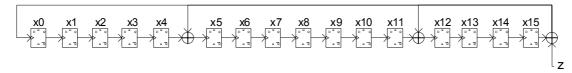

| Figure 27, old stream function for decoding algorithms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46                                                                                                         |

| Figure 28, new stream function for decoding algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                            |

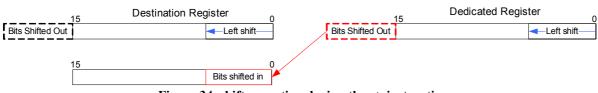

| Figure 34, shift operation during the <i>str</i> instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                            |

| Figure 35, clock cycles used to decode, switch nodes and inserting nodes during Huffman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 65                                                                                                         |

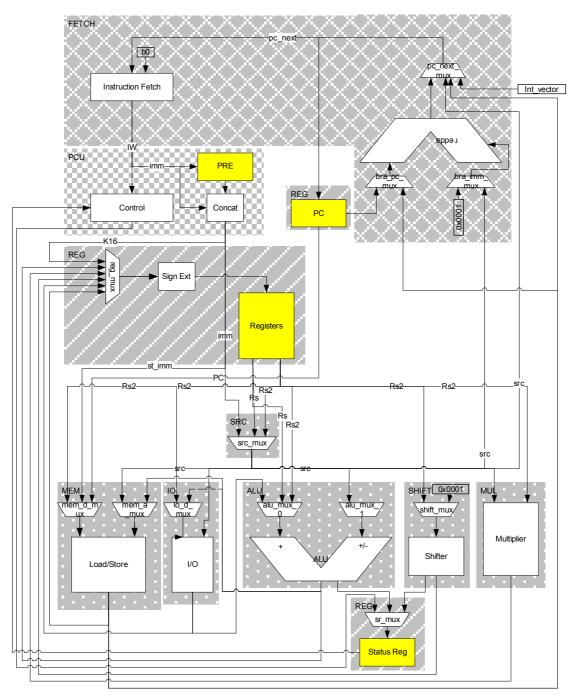

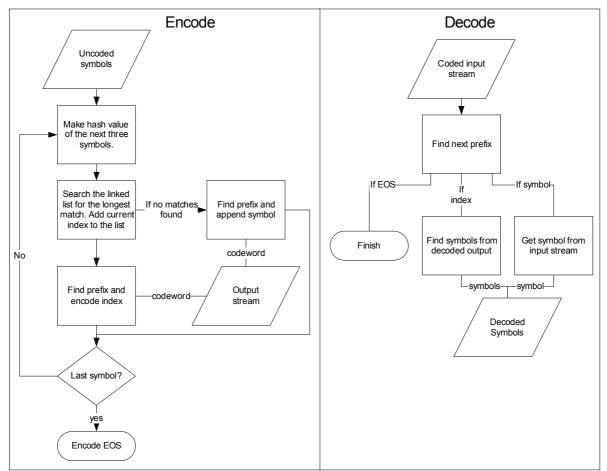

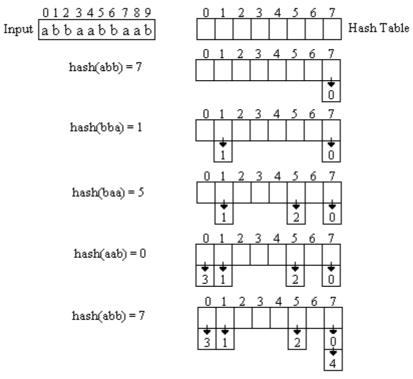

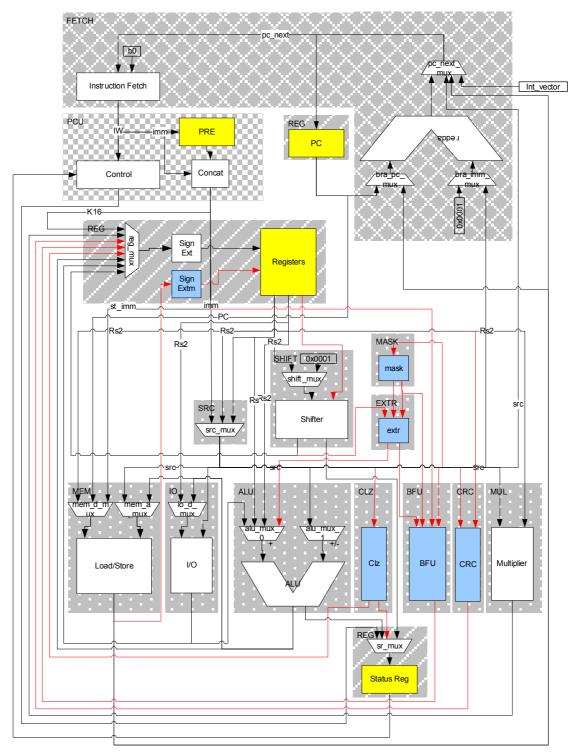

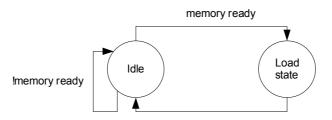

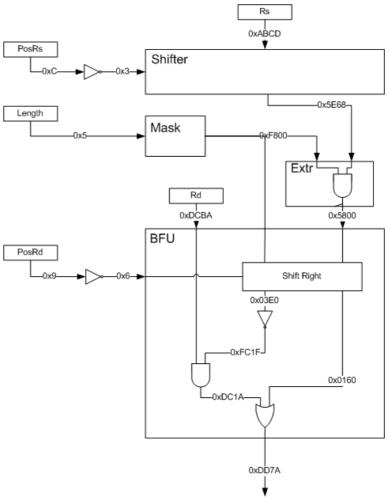

| Figure 17, the simplified Deflate flow chart.       Figure 18, hash table with linked lists         Figure 19, profile labels syntax.       Figure 20, enhanced NanoRisc ISS GUI.         Figure 21, Profile window       Figure 22, new ISA dialog window.         Figure 23, example insertion of a bit field (6 clock cycles).       Figure 24, example addition on a bit field (3 clock cycles).         Figure 25, example shift add operation for index storage (3 clock cycles).       Figure 27, old stream function for decoding algorithms.         Figure 29, the enhanced NanoRisc data flow diagram.       Figure 30, state machine during load instructions.         Figure 31, data flow in the bit field example.       Figure 32, CLZ data flow diagram.         Figure 34, shift operation during the str instruction.       Figure 34, shift operation during the str instruction. | 26<br>28<br>29<br>31<br>32<br>35<br>35<br>35<br>42<br>46<br>48<br>52<br>53<br>54<br>56<br>57<br>58         |

# List of Tables

| Table 1, Rice codes $(k = 2)$                                                               | 5     |

|---------------------------------------------------------------------------------------------|-------|

| Table 2, Encoding steps (LZ77 Example)                                                      | 6     |

| Table 3, Incomming symbols (LZ77 Example)                                                   | 6     |

| Table 4, original instruction encoding.                                                     |       |

| Table 5, "pre" types and their encoding.                                                    | 16    |

| Table 6, Table example for the implementation of the sorting method                         | 21    |

| Table 7, indicators for simplified Deflate                                                  |       |

| Table 8, instruction level profiling results from the Rice algorithm.                       | 36    |

| Table 9, instruction level profiling results from the Huffman algorithm.                    |       |

| Table 10, instruction level profiling results from the simple Deflate algorithm             | 38    |

| Table 11, undefined space in the original ISA                                               |       |

| Table 12, encoding of new instructions.                                                     |       |

| Table 13, default "pre" values                                                              |       |

| Table 14, operations that may be affected by the enhancements                               | 43    |

| Table 15, estimated speedup from new instructions and NBL behavior                          | 43    |

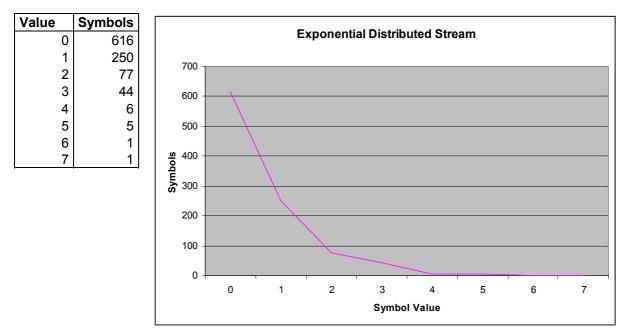

| Table 16, algorithmic profiling from the Rice decoding algorithm with exponential distribu  |       |

| input stream.                                                                               | 44    |

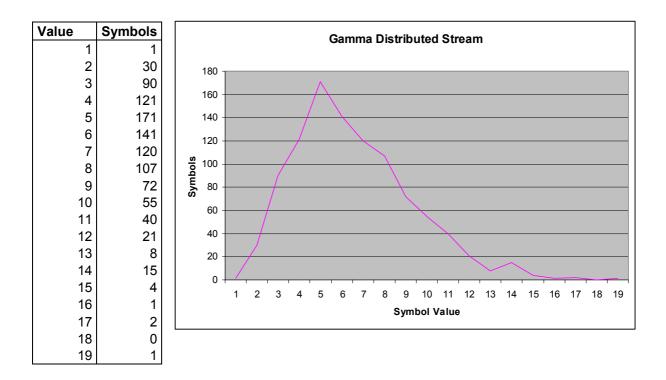

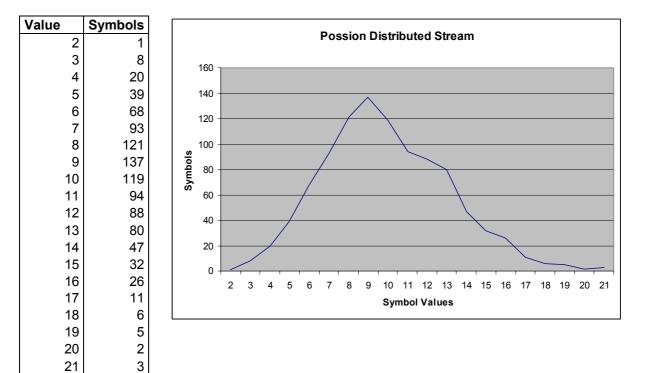

| Table 17, algorithmic profiling from the Huffman decoding algorithm with poisson            |       |

| distributed input stream.                                                                   | 44    |

| Table 18, algorithmic profiling from the Deflate decoding algorithm with text input stream  | ı. 45 |

| Table 19, algorithmic profiling from the Deflate encoding algorithm with text input stream  |       |

| Table 20, profiling results from the stream label when decoding the text stream.            |       |

| Table 21, encoding of the str instruction.                                                  |       |

| Table 22, profiling results from the stream label when decoding the text stream and using t |       |

| new str instruction.                                                                        |       |

| Table 23, encoding of the crc instruction.                                                  | 48    |

| Table 24, new Instructions.                                                                 | 49    |

| Table 25, new "pre" types                                                                   | 49    |

| Table 26, increase in throughput.                                                           |       |

| Table 27, RAM access reduction.                                                             | 50    |

| Table 28, reduction in code size due to new instructions.                                   | 50    |

| Table 29, compression ratios.                                                               | 50    |

| Table 30, Register contents in bit field example                                            | 54    |

| Table 31, gate count for the original NanoRisc.                                             |       |

| Table 32, contributions from each stage and module to the gate count at 25 MHz              | 60    |

| Table 33, contributions from each stage and module to the gate count at 62.5MHz             | 60    |

| Table 34, estimated power consumption at 25 MHz [mW]                                        | 61    |

| Table 35, estimated power consumption at 62.5 MHz [mW]                                      | 61    |

| Table 36, power consumption for 512x16 bits ROM and 2048x16 bits RAM [mW] (global           | l     |

| voltage 1.62, 25Mhz operation)                                                              | 61    |

| Table 37, power and energy consumption at 25 MHz                                            | 63    |

| Table 38, energy consumption per bit for the enhanced NanoRisc.                             | 63    |

| Table 39, energy reduction per bit for the enhanced NanoRisc                                |       |

| Table 40, reduction in energy consumption due to compression with the enhanced NanoRia      |       |

|                                                                                             | 63    |

| Table 41, summary of results from "Energy Aware Lossless Data Compression" [25]             | 69    |

| Table 42, results from the implemented algorithms in the enhanced NanoRisc at 25 MHz        | 69    |

|                                                                                             |       |

## List of Acronyms and Abbreviations

A list of acronyms and abbreviations that are not explicitly explained in the text.

- **ASCII:** American Standard Code for Information Interchange. Standard 8 bits code used in data communications.

- ASIC: Application Specific Integrated Circuit.

- **CCITT:** Consultative Committee on International Telephony and Telegraphy. The international standards-setting organization for telephony and data communications.

- **CCSDS:** Consultative Committee for Space Data Systems.

- **CPU:** Central Processing Unit. Programmable logic device that performs all the instruction, logic, and mathematical processing in a computer.

- **CRC:** Cyclic Redundancy Check. An error checking technique used to ensure the accuracy of transmitting digital data.

- **DCT:** Discrete Cosine Transform. Mathematical transform used to convert signals from time domain to frequency domain.

- **DEMUX:** De-Multiplexer. Splits a signal to pass over multiple signal paths.

- **DSP:** Digital Signal Processor.

- **GUI:** Graphical User Interface. A computer terminal interface, such as Windows, that is based on graphics instead of text.

- HW: Hard Ware.

- I/O: InOut

- **IP:** Internet Protocol. Used for communications across a packet-switced network.

- **JPEG:** Joint Photographic Experts Group. JPEG is a standards committee that designed a lossy image compression format.

- JPEG-LS: A lossless image compression format.

- LAN: Local Area Network.

- **Isb:** Least Significant Bit.

- **LSB:** Least Significant Byte

- **MPEG:** Motion Picture Expert Group. Group defining the framework for a wide range of video and audio compression standards.

- MS: Microsoft. Software company.

- msb: Most Significant Bit

- MSB: Most Significant Byte

- MUX: Multiplexer. Allows two or more signals to pass over one signal path.

- **NASA:** National Aeronautics and Space Administration. US agency which administer the American space program.

- **OPS:** Operations per Second.

- PC: Personal Computer.

- **RAM:** Random Access Memory. Volatile memory used for data storage during operation.

- **RISC:** Reduced Instruction Set Computing. Processor architectures where a low amount of instructions are needed to perform necessary tasks.

- **ROM:** Read Only Memory. Nonvolatile memory often used as program memory.

- **RTL:** Register Transfer Level. Describes logical operation in digital circuits.

- **SCSI:** Small Computer System Interface. Parallel interface standard used by Apple Macintosh computers, PCs, and many UNIX systems for attaching peripheral devices to computers.

- **SoC:** System on Chip. A chip which constitutes an entire system or major subsystem.

- VHDL: A hardware modeling language. Commonly used for RTL modeling and synthesis.

# Introduction

Lossless data compression has become a standard feature in most high-speed communications networks. Data compression chipsets have been important for this development, and the significance of the V.42bis compression standard in modems is an example of this. The question is if data compression will play the same role for small wireless networks. If data compression can double or triple network throughput or significantly increase battery lifetime without harmful side effects, then the added complexity is worthwhile.

Not all data types are compressible and there are potential dangers such as data expansion, error propagation and incompatible standards. However, most commonly transmitted data is highly compressible. The aim of data compression for radio transmission is to save power or reduce bandwidth. Bandwidth is a precious commodity, and it is closely related to the bit rate (R = bps). For ordinary binary-phase shift keying the null-to-null bandwidth is given by 1.0R. Thus, if the number of data bits were reduced by half, then one would need only half the bandwidth. With the increase in use of wireless technology, it becomes more and more important that the bandwidth must be used efficiently. However, power can be saved by keeping the bandwidth and reduce airtime. Wireless transmission of one bit typically requires over 1000 times more energy than a single 16 bits computation. It is therefore justifiable to perform significant computation to reduce the number of bits transmitted, but limitations such as memory requirements, area constraints and throughput must be considered.

Today, most SoC transceiver solutions have an embedded microprocessor to handle complex control tasks, and Texas Instruments Norway has developed the NanoRisc microprocessor for this purpose. This thesis will explore the NanoRiscs current ability to process lossless data compression algorithms, and examine enhancements to improve its performance on this task. The work and this report have been divided into five main stages:

- A study of lossless compression algorithms, related works and the NanoRisc microprocessor.

- Implantation of three lossless compression algorithms in the NanoRisc assembly language.

- Enhancements of existing tools in order to measure performance of the NanoRisc and simulate improvements.

- Profile resource use when processing the implemented compression methods and propose improvements based on these results.

- Implement the proposed improvements in the NanoRisc microprocessor core, and synthesize the core in order to estimate changes in area, timing and power due to the implemented improvements.

The scope of this thesis does not include finding suitable data compression methods for wireless data. Only computational requirements have been considered when choosing algorithms for evaluating the NanoRiscs performance on different compression algorithms. Lossy compression methods have also not been considered. The thesis will cover some fundamental information theory, but the reader should be familiar with data compression and integrated circuit design.

## 1 Theory

This chapter will first describe some fundamental measures and terms before entropy coding is briefly explained and three compression algorithms are chosen for evaluating the NanoRisc current ability to process compression algorithms.

#### 1.1 Measures

The field of mathematics concerned with data communications and storage is named information theory, and is generally considered to have been founded in 1948 by Claude E. Shannon [1]. He defined the information of a symbol  $x_n$  from the alphabet X to be:

Eq. 1

$$i(x) = -\log_2 P(x_n)$$

;[1]

Where P(x) is the probability of the symbol occurring in the data stream. This could be described as how much knowledge is gained due to the observation of the symbol  $X = x_n$ . The logarithmic function can have any base, but by choosing 2 the measure can be translated to bits. An estimation of the average information gained from observing a sequence of symbols  $x_n$  from the alphabet X is called the Shannon entropy (or just entropy):

Eq. 2

$$H(X) = E[i(X)] = -\sum_{x \in X} P(x_n) \log_2 P(x_n)$$

;[1]

This is an important measure when it comes to compression. For a lossless compression method, the Shannon entropy is the fundamental limit. This means that it is possible to compress the source in a lossless manner down to H(X)\*n, where n is the number of symbols in the data stream. It is mathematically impossible to do better than H(X)\*n. Equation 2 shows the first order model of the entropy. If there are statistical dependencies between symbols, higher order models can be used [1].

The redundancy of symbol  $x_n$  is:

Eq. 3

$$\rho(x) = l(x_n) - \log_2 \frac{1}{P(x_n)}$$

;[1]

Where  $l(x_n)$  is the length of the symbol  $x_n$  in bits. The expected redundancy of alphabet X in the data stream is:

Eq. 4

$$E[\rho(X)] = \sum_{x \in X} P(x)\rho(x) = E[l(X)] - H(X)$$

;[1]

There are several quantities used for compression performance. The quantity used in this thesis is the Compression Ratio:

Eq. 5

$$ComressionRatio = \left(1 - \frac{OutputSize}{InputSize}\right) * 100\%$$

When possible enhancements of the original NanoRisc processor are examined, some measures are needed in order to estimate the expected overall improvement. Amdahl's law [2] may be used for just that. This law is named after computer architect Gene Amdahl, and it is used to find the expected improvement to an overall system when only parts of the system are improved. It is often used in parallel computing to predict the theoretical maximum speedup using multiple processors. More technically, the law is concerned with the speedup achievable from an improvement to a computation that affects a proportion P of that computation where the improvement has a speedup of S. Ahmdal's law states that the overall speedup of applying the improvement will be:

Eq. 6

$$S_{system} = \frac{1}{(1-P) + \frac{P}{S}}$$

;[2]

If the result is e.g. 1.4, the improvement will make the system go 1.4 times faster.

### 1.2 Entropy Coding

Three compression algorithms are chosen to evaluate the NanoRisc processor. This section will give a short theoretical introduction to entropy coding and the coding schemes chosen. The details of the implementations are explained in chapter 4.

There are many known methods of data compression. Often they are suitable for different types of data, and produce different results. Any compression method is based on representing data in a way that reduces the redundancy as much as possible. To achieve this they exploit the statistical properties or the redundancy of the source data. The actual decrease of size is done by representing symbol values in a different way. A symbol that occurs often is encoded with a shorter codeword than a symbol that occurs rarely. Compression is only possible because data is normally represented in a format that is longer than necessary. Samples from a converter or instructions in a computer program often have a fixed length. This is done to make it easier to process data, since processing data is more common than compressing data.

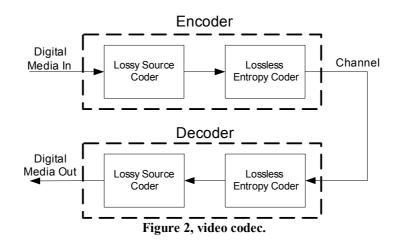

Some compression methods are lossy. They achieve compression by removing non-vital information from the source. Pictures and audio are often compressed with a lossy compression method, since the human eye or ear is still capable of interpreting the information with a reduction of quality. In contrast, a computer program cannot be compressed in a lossy way because the computer will not be able to understand instructions if something are missing. When loosing information is not acceptable, the data must be compressed with a lossless compression method. A lossless compression method will completely recover the original data from the compressed data. Entropy coding is defined as a coding scheme that assigns variable length codes to symbols so the code lengths match their probability. Lossless data compression methods are hence often called entropy coders. Entropy coding is often used as the last stage in lossy compression methods. After non-vital information is removed and complex methods have exposed statistical dependencies, entropy coding will make sure this is encoded in the shortest possible way (as close as possible to the entropy).

The process of entropy coding can often be split into modeling and coding. Modeling is a statistical analysis of the input data stream, and coding creates codewords from the statistics. These statistics may be frequencies of occurrence for different symbols, the existence of

repetitive sequences of symbols, dependencies in the frequency contents, etc. Modeling may be either static or adaptive. In static modeling, the same statistics is used every time coding is performed. Static modeling may be a good option if the source is well known and rigid. Adaptive modeling performs a statistical analysis every time coding is carried out. The method may be one-pass or two-pass. One-pass methods gather statistical information as the coding process goes forward and require thus only one pass of the input data stream. Two pass methods do one pass to gather statistical information, and another pass to do the coding. It is therefore necessary that the encoder in a two-pass method must pass the statistical information to the decoder. As established in Shannon's source coding theorem, there exists a relationship between the symbols probability and its shortest corresponding bit sequence. Since the statistical analysis is responsible for the evaluation of each symbols probability, modeling is one of the most important tasks in data compression. It is also important that the coding scheme is able to produce the shortest total output stream from the probability distribution found in the modeling.

### **1.2.1 Entropy Coding Schemes Used for Evaluation**

Three fundamentally different entropy coding schemes are chosen to evaluate the NanoRisc processors current ability to process data compression algorithms:

- **Rice Coding** makes codewords directly from a value. These codewords are optimal if the input data stream is modeled to fit a geometrical probability distribution.

- **Huffman Coding** generates codes from a codebook and may fit any probability distribution. The codebook is usually held in a binary tree called a Huffman tree.

- LZ77 detects patterns in the input stream and code lengths and pointers to where in the stream these patterns are found. (The actual algorithm implemented is called Deflate, and is a version of the LZ77 coding scheme.)

These three algorithms are chosen because they are fundamentally different from each other. Huffman and Rice coding are examples of statistical coding methods. They are heavily dependent on the quality of the modeling process or a precise static model. Even though Huffman and Rice are part of the same family of coding methods, they use very different methods. Huffman uses a codebook built on symbol probability in the data stream, while Rice produces codewords according to symbol value. It is important that the modeling stage produce low symbol values for the Rice encoder, while in Huffman only probabilities matter. The LZ77 coding method is a dictionary method. Dictionary methods utilize repetitive sequences of consecutive symbols in the input data stream. They build dictionaries of these sequences and encode where to find them. If the input stream consists of long and highly repetitive sequences, good compression ratios are achieved.

#### 1.2.1.1 Rice Coding

Rice coding is a selection of those Golomb codes that are easiest to produce in hardware. Golomb codes is a range of codes with a parameter m which encodes a positive integer n by encoding  $(n \mod m)$  in binary followed by encoding  $(n \dim m)$  in unary. When the parameter m is a power of two, the code is extremely efficient for use in computers since the division operation becomes a bitshift operation, and the remainder operation becomes a bitmask operation. This selection of Golomb codes is referred to as Rice codes. The disadvantage of the Rice coding is of course the restricted value of m, and therefore the compression may be

| Symbol | 4-bit  |          |           |          |

|--------|--------|----------|-----------|----------|

| Values | Binary | Quotient | Remainder | Code     |

| 0      | 0000   | 0        | 0         | 1 00     |

| 1      | 0001   | 0        | 1         | 1 01     |

| 2      | 0010   | 0        | 2         | 1 10     |

| 3      | 0011   | 0        | 3         | 1 11     |

| 4      | 0100   | 1        | 0         | 0 1 00   |

| 5      | 0101   | 1        | 1         | 0 1 01   |

| 6      | 0110   | 1        | 2         | 0 1 10   |

| 7      | 0111   | 1        | 3         | 0 1 11   |

| 8      | 1000   | 2        | 0         | 00 1 00  |

| 9      | 1001   | 2        | 1         | 00 1 01  |

| 10     | 1010   | 2        | 2         | 00 1 10  |

| 11     | 1011   | 2        | 3         | 00 1 11  |

| 12     | 1100   | 3        | 0         | 000 1 00 |

| 13     | 1101   | 3        | 1         | 000 1 01 |

| 14     | 1110   | 3        | 2         | 000 1 10 |

| 15     | 1111   | 3        | 3         | 000 1 11 |

less effective than that of Golomb codes. In Rice coding the term *k*-value is often used, where  $m = 2^k$ . An example of Rice codes with a *k*-value of 2 are shown in Table 1.

Table 1, Rice codes (k = 2)

When the entropy increases, it is usually the lsbs that becomes more and more random. To deal with this the Rice code just cuts off the lsbs and passes them through without coding, but the msbs that may be less random are coded. It is clear from the table that the Rice code achieves the best compression for an input stream of symbols that have a geometric probability distribution. Rice coding is a widely used technique for entropy coding in image and sound compression methods.

#### 1.2.1.2 Huffman Coding

Most variable-sized codes assume a given probability distribution of the symbols in the input data stream. The Huffman code is more general because it does not assume anything about the input symbol distribution, only that all probabilities are non-zero. Huffman was the first to develop an optimal algorithm for arbitrary probability distributions. This is achieved in the way the algorithm builds its codebook. Huffman first described this algorithm in a paper in 1952 [3]. The codebook is built in a binary tree structure (all nodes have only two children), and the algorithm follows these steps:

- 1. Consider all symbols as individual leaves with their probability as weight.

- 2. Find the two leaves with the lowest weight.

- 3. Make a new leaf with the weight of the two probabilities added together, and make the two found leaves children of the new leaf.

- 4. Repeat from step 2 as long as there are more than one leaf left.

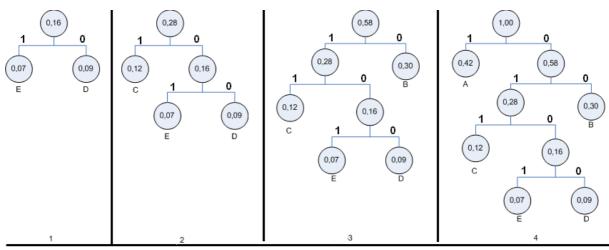

The following example will show the building of a Huffman tree. If the alphabet X consists of the symbols A, B, C, D and E, with a probability distribution P(A)=0,42, P(B)=0,3, P(C)=0,12, P(D)=0,09 and P(E)=0,07, the Huffman tree would be built as shown in Figure 1.

Figure 1, building of a Huffman tree.

When a symbol is read from the input stream, the code is created by traversing the tree from the leaf representing the code and to the root. By traversing right or left, the codeword is created with 1's or 0's. Decoding is done in similar matter, only the tree is traversed from the root to the leaf according to the code read. In the example from Figure 1, the codeword for E would be 0101.

#### 1.2.1.3 LZ77

This method uses previously observed input data as a dictionary. During encoding, the input stream encoded so far is called the search buffer. New symbols ready to be encoded is called the look-ahead buffer. The search buffer and the look-ahead buffer are often referred to as a window. When new symbols are to be encoded, the method tries to find matches in the search buffer for the pattern of symbols on the input. The window may have finite length, and the method is often called a sliding window (as data is being encoded, the window slide over the data stream). The LZ77 is part of a family of coding methods that is called dictionary methods. One may think of the search buffer as a dictionary of words (where pattern of symbols make up words) and the look-ahead buffer as words needed to be looked up in the dictionary. The method will always try to find the longest match, and when this is found a pointer to the beginning of the match in the search buffer and the length of the match is made. This pair, the pointer and length, is called an index. When encoding, this index together with the first symbol in the input stream that did not match is encoded. Encoding of an incoming data stream, Table 2, is shown in Table 3.

| Pos                                       | Symbol           |

|-------------------------------------------|------------------|

| 1                                         | А                |

| 2                                         | А                |

| 3                                         | В                |

| 4                                         | A<br>B<br>C<br>B |

| 5                                         | В                |

| 6                                         | В                |

| 7                                         | А                |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | B<br>A<br>B<br>C |

| 9                                         | С                |

| Pos | Match | Symbol | Output    |

|-----|-------|--------|-----------|

| 1   | None  | А      | (0,0) + A |

| 2   | A     | В      | (1,1) + B |

| 4   | None  | С      | (0,0) + C |

| 5   | В     | В      | (2,1) + B |

| 7   | AB    | С      | (5,2) + C |

Table 2, Incomming symbols (LZ77 Example)

Table 3, Encoding steps (LZ77 Example)

During decoding, the decoder will build up the same search buffer as the encoder. When the decoder reads a new index, it finds the beginning of the match in the search buffer and outputs the sequence according to its length. After that, it outputs the symbol following the index. The search buffer in the decoder consists of symbols decoded so far. It is evident from this description that looking up indexes (decoding) is much faster than searching for them (encoding), thus the LZ77 is an asymmetrical coding method.

## 2 Related Works

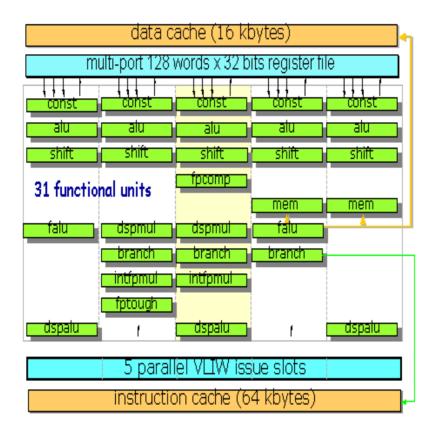

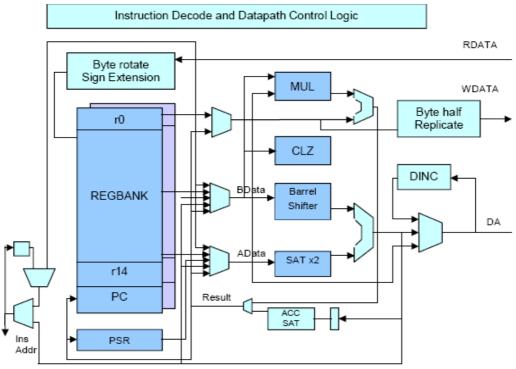

Since the original computer systems where designed for text processing and scientific applications, but not tasks such as audio and video compression, many enhancements of original computer systems have been towards multimedia applications. One of the most common solutions has been to include instructions that are optimized for typical multimedia applications. Almost all major processor manufacturers have developed their own set of media instructions. Examples include Motorola's AltiVec extensions to the PowerPC instruction set, and Intel's MMX, SSE, and SSE2 extensions to the x86 instruction set. The extensions differ in data path width, number and type of registers provided, as well as the availability of specific operations. Motorola's AltiVec and Intels SSE and SSE2 have 128 bits datapaths, floating point arithmetic, and they support in the region of over 100 instructions. The kinds of extensions these examples represent are of course farfetched for the enhancement of the NanoRisc processor, but the basic idea of adding special instructions and behavior in order to increase processing power for specific tasks is applicable.