# Efficient Verification with Portable Stimulus

Karianne Krokan Kragseth

Master of Science in ElectronicsSubmission date:June 2018Supervisor:Kjetil Svarstad, IESCo-supervisor:Isael Dias, Nordic Semiconductor

Norwegian University of Science and Technology Department of Electronic Systems

# Abstract

Portable Stimulus is an upcoming technique for increasing productivity and quality of verification of digital designs. A single test description shall be used to generate tests between multiple abstraction levels and platforms. Questa inFact is a tool that supports a subset of an upcoming standard from Accellera.

The thesis consisted of analyzing the current status and future development of Portable Stimulus. This included conducting a proof of concept through inFact. Generated code from a single description was proven to be used in simulation at IP-, sub-system- and SoC-level in UVM testbenches, as well as with C code running on a CPU. Only the stimulus was portable, meaning frameworks for driving the stimulus had to be created.

The current implementation of inFact is limited when compared to the Portable Stimulus specification, as a lot is not yet supported. It was possible to reuse the same test description, and through coverage driven simulation becomes verification more productive and the quality is increased. This is because of the shortened simulation time and the focus on what to test, rather than how. Thus, Portable Stimulus is heading in the right direction, but it still has a long way to go.

# Sammendrag

Portable Stimulus er en kommende teknikk for å øke produktiviteten og kvaliteten på verifikasjon av digitale design. En eneste testbeskrivelse skal brukes til å generere tester mellom flere abstraksjonsnivåer og plattformer. Questa inFact er et verktøy som støtter deler av en kommende standard fra Accellera.

Prosjektet besto av å analysere nåværende status og fremtidig utvikling av Portable Stimulus. Dette inkluderte et gjennomførbarhetsbevis (proof of concept) ved å benytte inFact. Kode generert fra en eneste beskrivelse har blitt bevist å kunne brukes ved simulering av IP-, subsystem- og SoC-nivå i UVM testbenker, i tillegg til ved kjøring av C kode i en CPU. Kun stimulansen er transporterbar, som betyr at rammeverk for å operere stimulansen også måtte skapes.

Den nåværende implementasjonen av inFact er begrenset sammenlignet med Portable Stimulus spesifikasjonen, da mye enda ikke er støttet. Det var mulig å gjenbruke den samme testbeskrivelsen, og gjennom "coverage" drevet simulering blir verifikasjonen mer produktivt og kvaliteten økes. Dette er på grunn av senket simuleringstiden og fokuset på hva som skal testes, fremfor hvordan. Dermed er Portable Stimulus på vei i riktig retning, men har fremdeles en lang vei å gå.

# Acknowledgements

I would like to thank my supervisors Isael Diaz and Vinodh Ravinath at Nordic Semiconductor and Kjetil Svarstad at NTNU for their guidance through weekly meetings. Their advice and feedback have been valuable. I would also like to thank Nordic Semiconductor by providing me with a place to work as well as tools and simulation frameworks required for conducting this thesis.

I also extend my gratitude to Staffan Berg at Mentor for demonstrating and teaching their tool Questa inFact, in addition to fast response when answering questions about inFact.

# Table of Contents

| Ab                      | Abstract i                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |    |  |  |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----|--|--|--|--|--|--|--|--|

| Sa                      | Sammendrag ii                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |    |  |  |  |  |  |  |  |  |

| Ac                      | Acknowledgements iii                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |    |  |  |  |  |  |  |  |  |

| Abbreviations viii      |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |    |  |  |  |  |  |  |  |  |

| 1 Introduc              |                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        | 1  |  |  |  |  |  |  |  |  |

|                         | 1.1                                               | Probler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | m Description                          | 1  |  |  |  |  |  |  |  |  |

|                         | 1.2                                               | Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | of the report                          | 2  |  |  |  |  |  |  |  |  |

| 2 Theory and Background |                                                   | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3                                      |    |  |  |  |  |  |  |  |  |

|                         | 2.1                                               | Univers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | sal Verification Methodology (UVM)     | 3  |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UVM Testbench                          | 3  |  |  |  |  |  |  |  |  |

|                         | 2.2                                               | What is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | s Portable Stimulus, and Why?          | 5  |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Verification on Different Platforms    | 6  |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | What One Wants to Test                 | 7  |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.2.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UVM vs. Portable Stimulus              | 7  |  |  |  |  |  |  |  |  |

|                         | 2.3 Portable Stimulus Specification Working Group |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                        |    |  |  |  |  |  |  |  |  |

|                         | 2.4                                               | Portable Stimulus Specification         Image: Contract of the state of the s |                                        | 8  |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Fundamentals                           | 8  |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Language                               | 9  |  |  |  |  |  |  |  |  |

|                         | 2.5 Portable Test and Stimulus Standard           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | le Test and Stimulus Standard          | 10 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Execution Semantic Concepts            | 10 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Components                             | 10 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Actions                                | 11 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Activities                             | 11 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Flow Objects                           | 12 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Resource Objects                       | 12 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pools                                  | 12 |  |  |  |  |  |  |  |  |

|                         |                                                   | 2.5.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Randomization Specification Constructs | 13 |  |  |  |  |  |  |  |  |

|   |      | 2.5.9    | Coverage Specification Constructs   | 3        |

|---|------|----------|-------------------------------------|----------|

|   |      | 2.5.10   | •                                   | 3        |

|   |      | 2.5.11   |                                     | 3        |

|   |      | 2.5.12   | •                                   | 3        |

|   |      |          |                                     | 4        |

|   |      |          |                                     | 4        |

|   | 2.6  |          | 1 1                                 | 6        |

|   |      | 2.6.1    | 11                                  | 6        |

|   |      | 2.6.2    |                                     | 8        |

|   |      | 2.6.3    | 8                                   | 9        |

|   | 2.7  |          | 6 6                                 | 21       |

|   | 2.7  | 155 10   |                                     |          |

| 3 | Port | able Sti | mulus Tool Questa inFact 2          | 23       |

|   | 3.1  | Choosi   | ng a PSS Tool                       | 23       |

|   | 3.2  |          |                                     | 23       |

|   |      | 3.2.1    | -                                   | 24       |

|   |      | 3.2.2    |                                     | 24       |

|   |      | 3.2.3    |                                     | 25       |

|   |      | 3.2.4    | 8 83                                | 25       |

|   |      | 3.2.5    | 1                                   | 25       |

|   | 3.3  |          | 8                                   | 25       |

|   | 0.0  | 3.3.1    | 5                                   | 26       |

|   | 3.4  |          |                                     | 27       |

|   | 3.5  |          | $\mathcal{O}$                       | 28       |

|   | 3.6  |          |                                     | 29<br>29 |

|   | 3.7  |          |                                     | 29       |

|   | 5.7  | iiii uot |                                     | .,       |

| 4 | Port | able Sti | mulus Verification Infrastructure 3 | 31       |

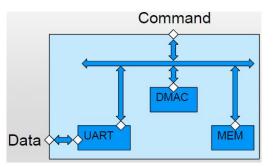

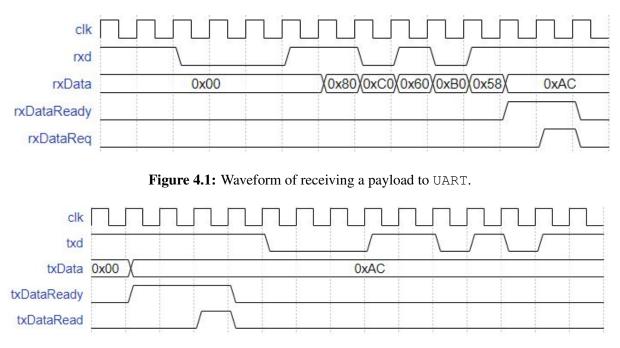

|   | 4.1  | UART     | Description                         | 31       |

|   | 4.2  | UVMI     | Framework                           | 32       |

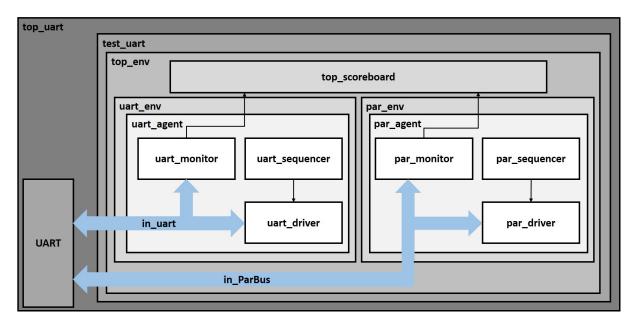

|   |      | 4.2.1    | UVM at UART IP Level                | 33       |

|   |      |          | 4.2.1.1 UART UVM Environment        | 35       |

|   |      |          | 4.2.1.2 PAR UVM Environment         | 39       |

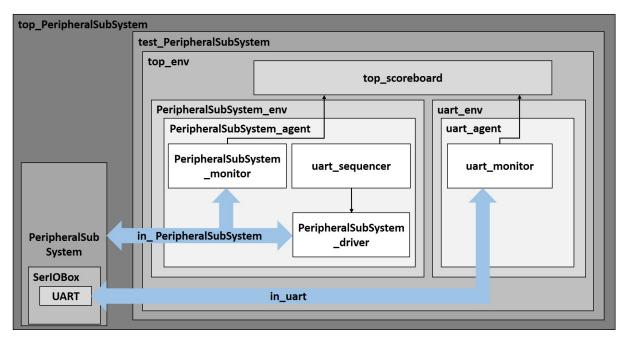

|   |      | 4.2.2    | UVM at UART Sub-System Level        | 10       |

|   |      |          |                                     | 13       |

|   |      | 4.2.3    |                                     | 14       |

|   |      |          |                                     | 15       |

|   | 4.3  | C Code   | 1                                   | 15       |

|   |      | 4.3.1    |                                     | 16       |

|   |      | 4.3.2    |                                     | 51       |

|   | 4.4  |          |                                     | 52       |

|   |      | 4.4.1    |                                     | 52       |

|   |      |          |                                     | 52       |

|   |      |          |                                     | 54       |

|   |      |          | 1                                   | 56       |

|   |      | 4.4.2    |                                     | 56       |

|   |      | 1.7.4    | e                                   | 58       |

|   |      |          |                                     | 0        |

|                 | Source Files 7'   |                                                      |                 |  |  |  |  |

|-----------------|-------------------|------------------------------------------------------|-----------------|--|--|--|--|

| Bibliography 73 |                   |                                                      |                 |  |  |  |  |

| 6               | <b>Con</b><br>6.1 | clusion<br>Future Work                               | <b>71</b><br>72 |  |  |  |  |

|                 | 5.5               | The Proof of Concept                                 | 69              |  |  |  |  |

|                 | 5.3<br>5.4        | Usability of inFact                                  | 67<br>68        |  |  |  |  |

|                 | 5.1<br>5.2        | Portable Stimulus                                    | 65<br>66        |  |  |  |  |

| 5               |                   | ussion                                               | 65              |  |  |  |  |

|                 |                   | <ul> <li>4.6.1 C Code Modifications</li></ul>        | 63<br>63        |  |  |  |  |

|                 | 4.6               | C Simulation with Generated Code                     | 62              |  |  |  |  |

|                 |                   | <ul> <li>4.5.1 UVM testbench Modifications</li></ul> | 61<br>62        |  |  |  |  |

|                 | 4.5               | 4.4.2.3 Creating a Coverage Strategy                 | 59<br>60        |  |  |  |  |

|                 |                   | 4.4.2.2 Generated Graph                              | 58              |  |  |  |  |

# Abbreviations

| API  | = | Application Programming Interface          |

|------|---|--------------------------------------------|

| DMA  | = | Direct Memory Access                       |

| DSL  | = | Domain-Specific language                   |

| EDA  | = | Electronic Design Automation               |

| HSI  | = | Hardware/Software Interface                |

| IDE  | = | Interactive Development Environment        |

| LSB  | = | Least Significant Bit                      |

| PI   | = | Procedural Interface                       |

| PPI  | = | Programmable Peripheral Interface          |

| PSS  | = | Portable Stimulus language Specification   |

| QoS  | = | Quality of Service                         |

| RAM  | = | Random Access Memory                       |

| RTL  | = | Register Transfer Level                    |

| RX   | = | Receive                                    |

| SDV  | = | Software Driven Verification               |

| SLN  | = | System Level Notation                      |

| SoC  | = | System on Chip                             |

| SUT  | = | System Under Test                          |

| TLM  | = | Transaction-Level Modeling                 |

| TX   | = | Transmit                                   |

| UART | = | Universal Asynchronous Reciver/Transmitter |

| UVM  | = | Universal Verification Methodology         |

| VIP  | = | Verification IP                            |

| WG   | = | Working Group                              |

|      |   |                                            |

# CHAPTER 1

# Introduction

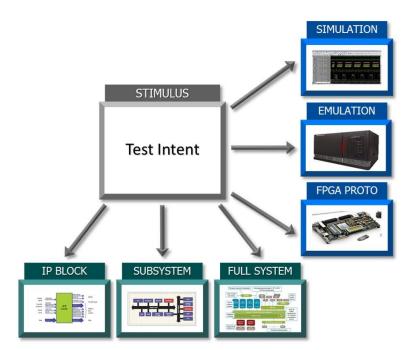

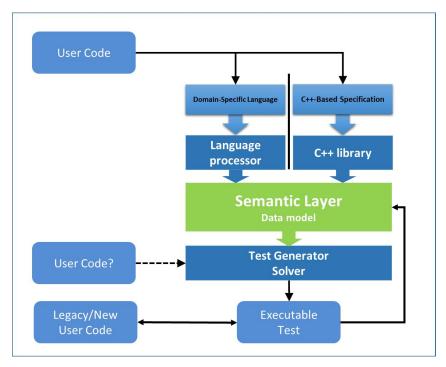

Development of techniques, such as constrained randomization, functional coverage and the UVM, for block level, have provided improvements in the productivity and quality of design verification. However, at the sub-system and SoC level's verification, challenges continue to grow. The complexity of SoC projects are increasing, making this even more challenging. Also, a lot of effort is put into writing the same kind of tests at different abstraction levels, IP-, sub-system and SoC-level, and at multiple platforms, simulation, emulation and silicon.

As a result, a new approach "Portable Stimulus" is being addressed. The goal is to have a single description of test intent that can generate stimulus for IP-, sub-system- and SoC-level. Portable Stimulus wants to increase verification productivity, and make reuse between abstraction levels as well as between different projects easier. Also, Portable Stimulus wants to increase the quality of design by making bug detection easier and more efficient.

During this thesis, a Portable Stimulus standard was being developed by Accellera, but an early adopter release was present. The first version is supposed to be released during the summer of 2018. A tool by Mentor, called "Questa inFact", is a contributor to this standard, and a subset of Portable Stimulus was supported. This thesis is about analyzing Portable stimulus, and conduct a proof of concept through inFact. It contains an explanation on how Portable Stimulus is achieved at the different abstraction levels, and between different platforms. This includes RTL simulation with UVM testbenches and C code running on an CPU. UVM is used because Portable Stimulus is specified to generated UVM sequences at RTL level. Nordic Semiconductor, an integrated circuits provider, has requested this thesis.

# **1.1 Problem Description**

The problem description states to do a investigation of existing proposal for universal stimulus, and compare them. However, only one proposal has been examined in this thesis, Portable Stimulus, as this is in the process of becoming a standard. Thus, most effort will be put towards this proposal, making it unnecessary to investigate other proposals. In addition, this standard is a collection on multiple proposals. A proof of concept, with a limited implementation of

Portable Stimulus, has been conducted as the problem description states. The methodology followed in this thesis is evaluation of a suggested standard. This through analyzing what it is good for and use it in a realistic example which, hopefully, exposes both strong and weak sides of language/notation/tool.

The work in this thesis include:

- Investigating Portable Stimulus, and supporting tools

- Proof of concept:

- Choosing a scenario: receive and transmit with UART

- Creating UVM frameworks, from scratch, for three different abstraction layers (IP, sub-system and SoC)

- Creating a C code framework

- Creating Portable Stimulus code by importing UVM transactions and sequences in inFact

- Creating Portable Stimulus code from scratch in inFact

- Integrating generated code from inFact into UVM frameworks and running it

- Integrating generated code from inFact into C code framework and running it

### **1.2** Layout of the report

Chapter 2 contains an explanation of UVM and Portable Stimulus, and what the idea behind Portable stimulus is and how it should work. Chapter 3 presents the tool, Questa inFact. The process on writing the UVM and the C code frameworks are explained in Chapter 4. The UVM frameworks consist of a separate testbench at IP-, sub-system and SoC-level. How the PSS code is created, both through an import function and from scratch, are also presented. Last, the frameworks and the PSS generated code are connected and simulated. Chapter 5 further discusses and analyses this.

# CHAPTER 2

# Theory and Background

### 2.1 Universal Verification Methodology (UVM)

Universal Verification Methodology (UVM) is a result from the UVM working group formed by Accellera, which involves standardization of verification[1]. UVM is a methodology for functional verification improving verification complexity and interoperability between verification components and environments[2]. UVM is also designed for reusability.

#### 2.1.1 UVM Testbench

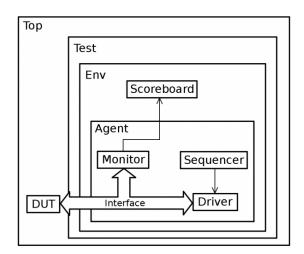

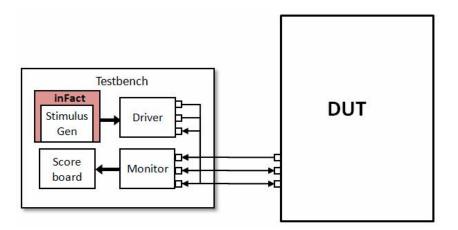

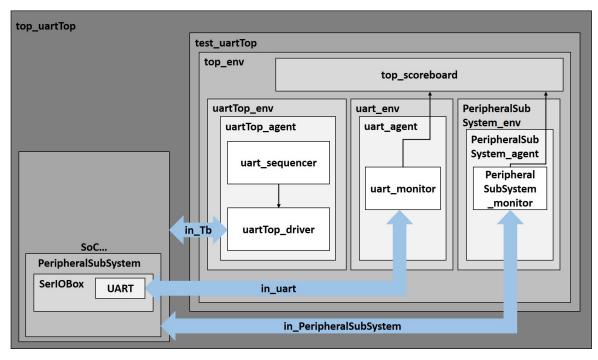

Figure 2.1 shows a typical UVM based testbench architecture. This include components with defined intent, such as generating stimulus, driving stimulus to the DUT, monitoring the outputs of the DUT, and comparing the inputs and outputs. Testbench top in this example is *top*, instantiating UVM framework[3].

Figure 2.1: Typical UVM testbench [4].

#### Transactions

UVM components are transaction based through transaction-level communication interfaces and channels[3]. A transaction in UVM is a class object that includes whatever information needed to model a unit of communication between two components. These objects usually include variables and constraints. They contain a model of inputs and outputs that are used for generating stimulus to the DUT and monitoring the DUT. A call to a transaction will randomize the input values, which can be limited through constraints. A transaction is defined by declaring a class that extends *UVM\_sequence\_item*.

#### **UVM Test**

The top-level UVM component is the UVM *Test*[3]. Here is the environment instantiated, configured (through factory overrides or the configuration database), and stimulus is applied through the environment to the DUT by invoking UVM *Sequences*. A UVM *Test* is defined by declaring a class that extends *UVM\_test*.

#### **UVM Environment**

The UVM *Environment* is a hierarchical component that groups together the UVM *Scoreboard* and UVM *Agent*, and sometimes other UVM *Environments*[3]. The top-level UVM *Environment* encapsulates all the verification components targeting the DUT. A UVM *Environment* is defined by declaring a class that extends *UVM\_environment*.

#### **UVM Scoreboard**

The UVM *Scoreboard* is used for checking the behavior of the DUT[3]. It receives transactions from the UVM *Monitor* analysis ports. The inputs of the transactions are run through a reference model, called *predictor*, which produces expected outputs, and compares this with the outputs in the received transactions. A UVM *Scoreboard* is defined by declaring a class that extends *UVM\_scoreboard*.

#### **UVM Agent**

The UVM *Agent* is also a hierarchical component that groups together the verification components that interact with the DUT interface[3]. These components typically include a UVM *Sequencer* managing stimulus flow, a UVM *Driver* applying stimulus to DUT, and a UVM *Monitor* monitoring the DUT interface. Examples of other components that can be included are coverage collectors, protocol checkers and a Transaction-Level Modeling (TLM) model. There are two different operation modes for a UVM *Agent*, active mode where it can generate stimulus, and passive mode where it can only monitor the interface and not control it. A UVM *Agent* is defined by declaring a class that extends *UVM\_agent*.

#### **UVM Sequencer**

The UVM *Sequencer* works as an arbiter for controlling transaction flow of UVM *Sequence Items* transactions generated by one or more UVM *Sequence*. A UVM *Sequencer* is defined by declaring a class that extends *UVM\_sequencer*.

#### **UVM Sequence**

A UVM *Sequence* is used for generating stimulus, and is not a part of the component hierarchy[3]. They can be transient or persistent, and come into existence for a single transaction, drive stimulus for the whole stimulation, or anywhere in-between. It is possible to create a hierarchy of UVM *Sequences*, starting with one sequence called a *parent sequence*, invoking one or more sequences called *child sequences*. All UVM *Sequences* needs to be bound to a UVM *Sequencer* to operate. Multiple UVM *Sequences* can be bound to a single UVM *Sequencer*. A UVM *Sequence* is defined by declaring a class that extends *UVM\_sequence*.

#### **UVM Driver**

The UVM *Driver* applies stimulus to the DUT interface based on received UVM *Sequence Item* transactions from the UVM *Sequencer*[3]. I.e. it converts transaction-level stimulus into pinlevel stimulus. Transactions are received through a TLM port. A UVM *Driver* is defined by declaring a class that extends *UVM\_driver*.

#### **UVM Monitor**

The UVM *Monitor* monitors the DUT interface, and collects the inputs and outputs into transactions that is set to rest of the UVM *Testbench* for further analysis, for example a scoreboard[3]. A typical monitor would covert a certain interface pin wiggles to transactions. The transactions are sent through a TLM analysis port. A UVM *Monitor* is defined by declaring a class that extends *UVM\_monitor*.

### 2.2 What is Portable Stimulus, and Why?

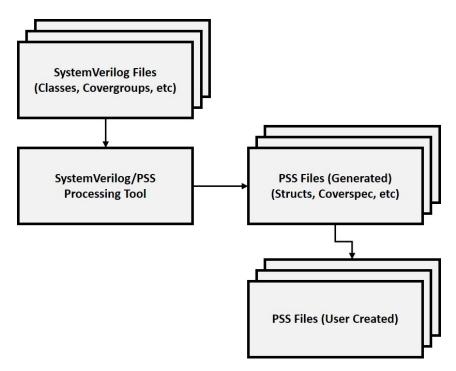

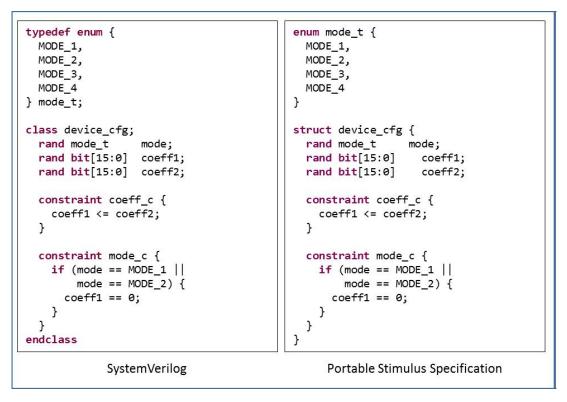

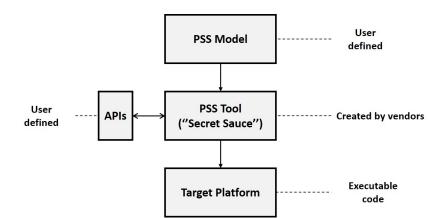

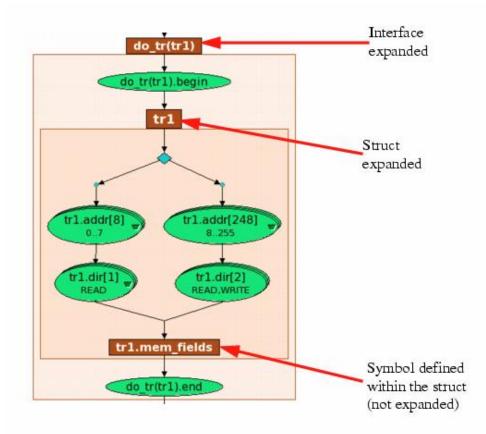

The complexity of SoC projects are increasing and verification productivity is not scaling with it[5]. A significant challenge is test intent reuse across vertical platforms - different phases of RTL design such as IPs, sub-systems, integration, chip and so on. To overcome reuse potential, an initiative is Portable Stimulus (PS), which try to address mainstream and methodical automation of test content reuse. The concept of PS is to only describe test intent and behavior once, and then target it for multiple abstraction layers, such as IP, sub-system and SoC[6]. This includes the verification platforms simulation, emulation and silicon. These platforms have separate requirements and use different languages, as well as different approaches when testing aspects of the system[7].