# Computational Materials: Experimental Platform

Ole Petter Skarre Lund

Master of Science in Computer Science

Submission date: June 2013

Supervisor: Gunnar Tufte, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# Problem Description

In this research project we try to exploit computational properties of unconventional materials (materials usually not considered as a computational substrate). Such materials may offer computation at extreme low cost and may also enable us to do computation that is hard (or impossible) on a von Neumann stored program machine. Currently we explore possible computational properties of carbon nano tubes.

In 2010 a first version of a platform was made. This system consists of a PCB, including an Atmel microcontroller and a Xilinx FPGA, that acts as an interface between a PC and a micro electrode array. The array interfaces the material under investigation.

In this project the experimental platform will be extended. There are several possible directions. As such there is a possibility for several students pursuing different directions. Possible directions:

- a) Extending the software, microcontroller and PC (mostly c-programming).

- b) Extending the FPGA interface to the material (VHDL and c-programming).

- c) Design of additional interface circuits between the FPGA and the micro electrode array (PCB-design, digital/analogue design).

# Abstract

The field of evolution in materio is a branch of unconventional computing that uses artificial evolution to manipulate materials so that the emergent properties can be used for computation. Some materials may have very complex properties and this could be utilized to do computation faster and/or more energy efficient than today's computers. The purpose of this master's thesis is to extend an already existing prototype system, called Mecobo, that is used for evolution in materio. The prototype system is currently only able to apply digital signals to the materials, i.e. high and low voltage, but with this new extension it will also be able to apply an arbitrary waveform in addition to reading the response from the materials. The main components of the extension are digital-to-analog converters that together with an FPGA functions as a frequency synthesizer. An analogto-digital converter is also used for sampling the response signal. Some initial experiments are presented, where the linearity/nonlinearity of the response signal is investigated when analog signals are applied to carbon nanotubes. The results shows that carbon nanotubes are able to influence the signals, as they pass through it.

# Sammendrag

Forskningsfeltet evolution in materio er en gren av feltet ukonvensjonell databehandling som bruker kunstig evolusjon for å manipulere materialer slik at egenskapene som oppstår kan benyttes til å gjøre signal- og databehandling. Noen materialer kan ha veldig komplekse egenskaper og dette kan bli utnyttet til å gjøre beregninger raskere og/eller mer energieffektivt enn hva dagens datamaskiner kan. Hensikten med denne masteroppgaven er å utvide et allerede eksisterende prototype-system, kalt Mecobo, som blir brukt til evolution in materio. Prototype-systemet er foreløpig bare i stand til å anvende digital signaler på materialer, med andre ord høy og lav spenning, men med den nye utvidelsen vil det bli mulig å andvende vilkårlige bølgeformer i tillegg til å kunne lese responsen fra materialet. Hovedkomponentene i den nye utvidelsen er digital-tilanalog konvertere som sammen med en FPGA fungerer som en frekvenssynthesizer. En analog-til-digital konverter blir brukt for å lese responssignalet fra materialet. Noen innledende eksperimenter presenteres, hvor lineæriteten/ikke-lineæriteten til responsen fra nanorør av karbon blir undersøkt, når analoge signaler blir andvendt. Resultatene viser at materialet er i stand til å påvirke signalene, idet de passerer gjennom det.

# Acknowledgments

I would like to thank my supervisor Gunnar Tufte. His knowledge in signal processing, analog/digital electronics and evolvable systems has been very helpful during the process of designing and evaluating the system and in analyzing the results of the experiments. Also, thanks to Odd Rune Strømmen Lykkebø for helping me with the various problems that I encountered.

# Contents

| Pr | oblei               | m Description                           | i                                |

|----|---------------------|-----------------------------------------|----------------------------------|

| Al | ostra               | $\operatorname{\mathbf{ct}}$            | iii                              |

| Sa | mme                 | endrag                                  | $\mathbf{v}$                     |

| A  | cknov               | vledgments                              | vii                              |

| Li | st of               | Figures                                 | xiii                             |

| Li | st of               | Tables                                  | $\mathbf{x}\mathbf{v}$           |

| A  | crony               | rms                                     | kvii                             |

| 1  | 1.1<br>1.2<br>1.3   | Oduction Unconventional Computation     | 1<br>1<br>3<br>4                 |

| 2  | Back 2.1 2.2        | kground Previous Work                   | 7<br>7<br>7<br>8<br>9<br>11      |

| 3  | Syst 3.1 3.2        | The Experimental Hardware               | 15<br>15<br>18<br>19<br>20       |

| 4  | <b>Desi</b> 4.1 4.2 | ign and Implementation  DA/AD Converter | 21<br>25<br>25<br>26<br>28<br>29 |

#### **CONTENTS**

|    |          | Phase accumulator                   | 30        |

|----|----------|-------------------------------------|-----------|

|    |          | Phase-to-Amplitude Converter        | 32        |

|    |          | Channel Grouping                    | 36        |

|    |          | 4.2.5 Wave Control                  | 37        |

|    |          | 4.2.6 Sample Register               | 38        |

|    |          | 4.2.7 User Module Changes           | 38        |

|    | 4.3      | Microcontroller                     | 39        |

|    |          | 4.3.1 Address Room                  | 39        |

|    |          | 4.3.2 Busy Line to Microcontroller  | 39        |

|    | 4.4      | libEMB                              | 41        |

|    | 4.5      | PCB                                 | 46        |

|    | 4.6      | Low-pass Filter                     | 47        |

|    | 4.7      | Error sources                       | 48        |

|    |          | 4.7.1 Phase Truncation              | 48        |

|    |          | 4.7.2 Quantization                  | 51        |

|    |          | v                                   |           |

| 5  | Test     | ting and Evaluation                 | <b>53</b> |

|    | 5.1      | System Tests                        | 53        |

|    | 5.2      | FPGA Tests                          | 53        |

|    | 5.3      | Digital/Analog Converter Evaluation | 54        |

|    |          | 5.3.1 Integral Nonlinearity         | 55        |

|    |          | 5.3.2 Differential Nonlinearity     | 57        |

|    |          | 5.3.3 Frequency Domain Analysis     | 59        |

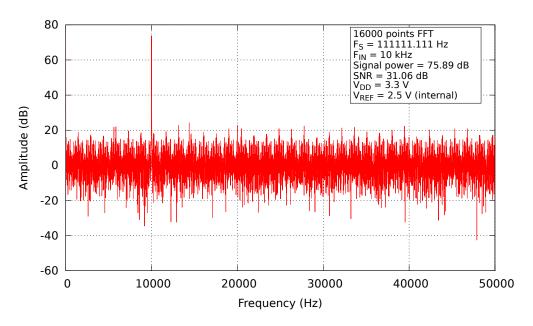

|    |          | Digital-to-analog Converter         | 61        |

|    |          | Analog-to-digital Converter         | 62        |

|    |          | Closed-loop                         | 63        |

|    |          |                                     |           |

| 6  | Exp      | periments                           | 67        |

|    | 6.1      | Trial and Error                     | 67        |

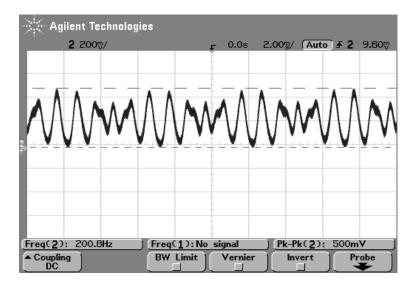

|    | 6.2      | ADC Adding Noise To The Output      | 68        |

|    | 6.3      | Frequency Response                  | 69        |

|    | 6.4      | Phase Response                      | 70        |

|    |          | 6.4.1 Experiment 1                  | 71        |

|    |          | 6.4.2 Experiment 2                  | 72        |

|    | 6.5      | Amplitude Response                  | 74        |

| 7  | <b>C</b> | a alvedora                          | 70        |

| 7  |          | nclusion Further Week               | <b>79</b> |

|    | 7.1      | Further Work                        | 80        |

| Bi | bliog    | graphy                              | 83        |

### **CONTENTS**

| Aı           | pend | dices                 |                             | 86  |

|--------------|------|-----------------------|-----------------------------|-----|

| $\mathbf{A}$ | Test | Plans                 |                             | 87  |

|              | A.1  | System                | Tests                       | 87  |

|              |      | A.1.1                 | libEMB                      | 87  |

|              | A.2  | $\operatorname{FPGA}$ | Design Tests                | 89  |

|              |      | A.2.1                 | SPI DAC Controller          | 89  |

|              |      | A.2.2                 | SPI ADC Controller          | 89  |

|              |      | A.2.3                 | Sine LUT                    | 90  |

|              |      | A.2.4                 | Sine LUT Wrapper            | 90  |

|              |      |                       | Configuration Register      | 90  |

|              |      |                       | Wave Configuration Register | 90  |

|              |      | A.2.7                 | Wave Memory                 | 91  |

|              |      |                       | Wave Generator              | 91  |

|              |      | A.2.9                 | Sample Register             | 92  |

|              |      | A.2.10                | Wave Controller             | 93  |

|              |      |                       | Wave Module                 | 93  |

|              |      |                       | Toplevel                    | 93  |

| В            | Fini | te Stat               | te Machines                 | 95  |

| $\mathbf{C}$ | Test | Equip                 | oment                       | 99  |

| D            | Bill | of Mat                | terials                     | 100 |

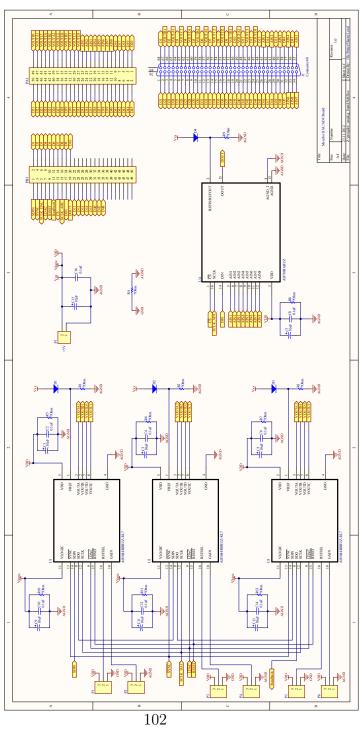

| $\mathbf{E}$ | Sche | ematics               |                             | 101 |

# List of Figures

| 1.1<br>1.2 | Visualization of evolution in materio |

|------------|---------------------------------------|

|            |                                       |

| 2.1        | Gordon Pask's schematic               |

| 2.2        | Adrian Thompson's experiment setup    |

| 2.3        | Evolvable motherboard                 |

| 2.4        | Liquid crystal evolvable motherboard  |

| 2.5        | Robot controller                      |

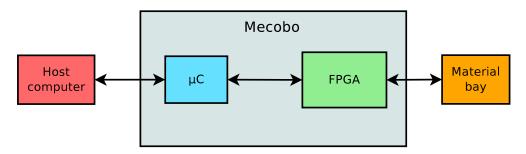

| 2.6        | System overview without the extension |

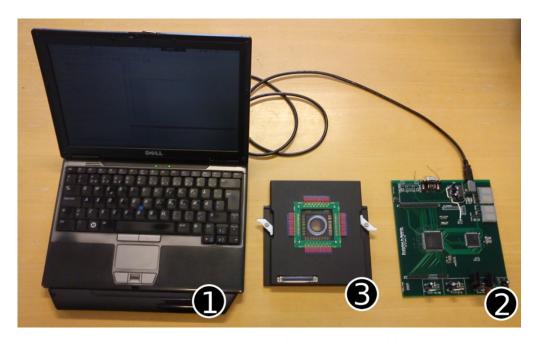

| 2.7        | Picture of Mecobo                     |

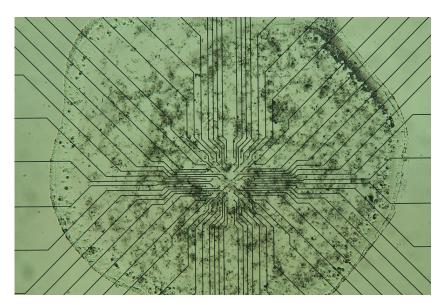

| 2.8        | Carbon nanotubes                      |

| 2.9        | Gold particles                        |

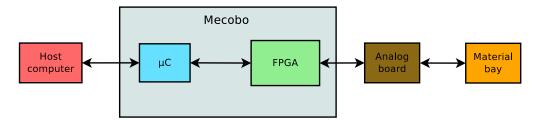

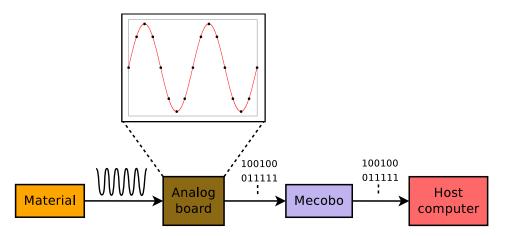

| 3.1        | System overview with the analog board |

| 3.2        | Mecobo interfacing                    |

| 3.3        | Prototype system                      |

| 3.4        | Experimental setup                    |

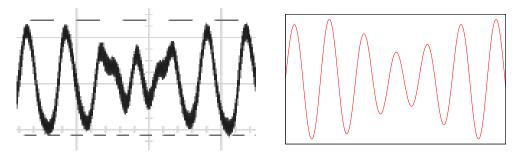

| 3.5        | Desired Waveforms                     |

| 3.6        | Sampling example                      |

| 3.7        | Direct digital synthesizer            |

| 4.1        | Analog board overview                 |

| 4.2        | DAC block diagram                     |

| 4.3        | ADC block diagram                     |

| 4.4        | Analog board with communication       |

| 4.5        | FPGA design overview                  |

| 4.6        | Extended FPGA design overview         |

| 4.7        | DAC SPI controller                    |

| 4.8        | ADC SPI controller                    |

| 4.9        | Wave module                           |

| 4.10       | Numerically controlled oscillator     |

| 4.11       | Phase accumulator output              |

|            | Sine symmetry                         |

|            | NCO wave output                       |

|            | Sawtooth to triangle wave             |

|            | DAC channels                          |

|            | Address rooms                         |

|            | Analog board ground                   |

|            | DAC schematic 47                      |

### LIST OF FIGURES

| 4.19 | DAC schematic                                            |

|------|----------------------------------------------------------|

|      | Picture of the analog board                              |

|      | Low-pass filter                                          |

|      | Phase truncation error                                   |

| 5.1  | Ideal vs. measured plot of DAC                           |

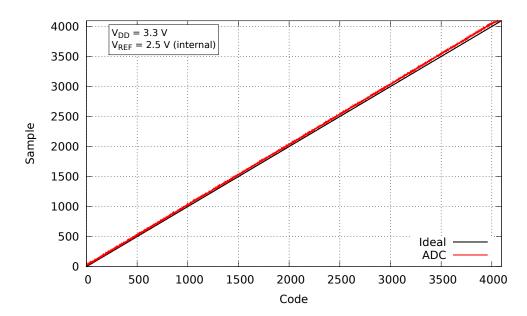

| 5.2  | Ideal vs. measured plot of ADC                           |

| 5.3  | DAC integral nonlinearity                                |

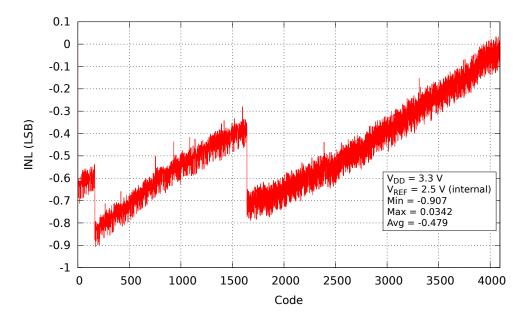

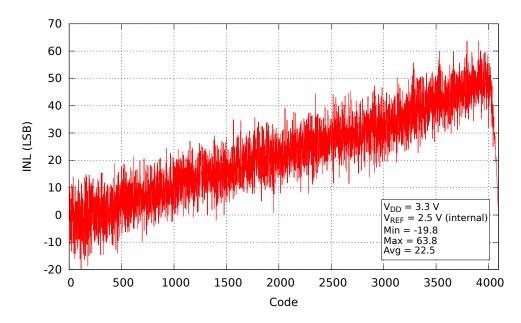

| 5.4  | ADC integral nonlinearity                                |

| 5.5  | DAC differential nonlinearity                            |

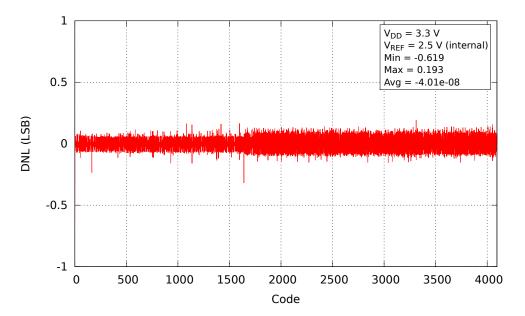

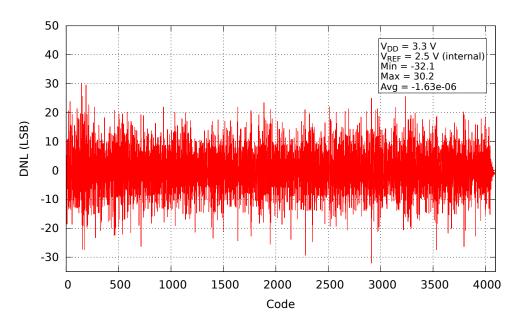

| 5.6  | ADC differential nonlinearity 60                         |

| 5.7  | DAC dynamic performance 61                               |

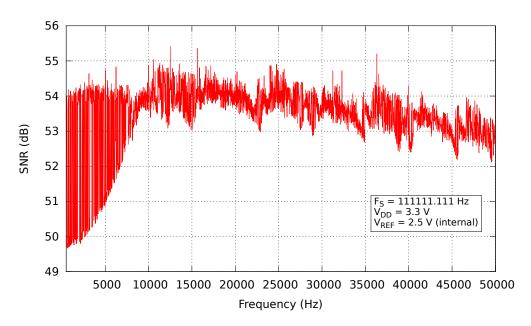

| 5.8  | DAC signal-to-noise ratio vs. input frequency 62         |

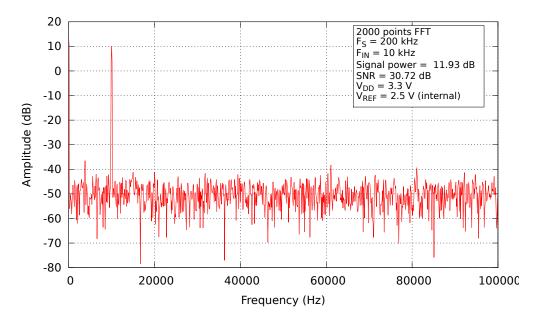

| 5.9  | ADC dynamic performance                                  |

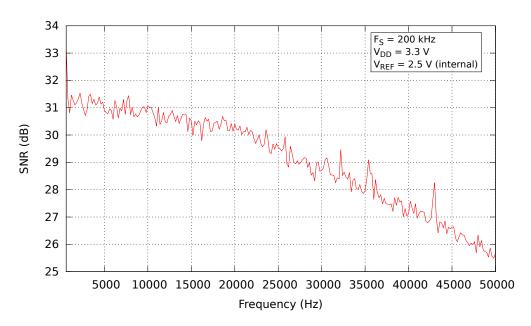

| 5.10 | ADC signal-to-noise ratio vs. input frequency 64         |

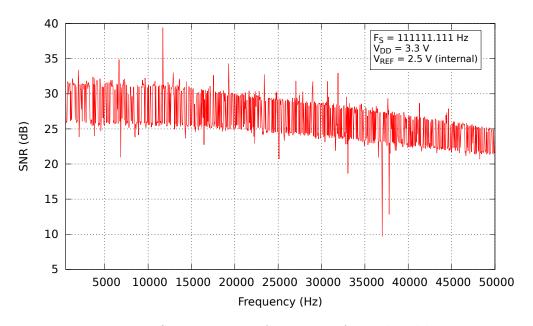

| 5.11 | Closed-loop dynamic performance                          |

| 5.12 | Closed-loop signal-to-noise ratio vs. input frequency 65 |

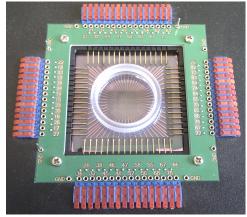

| 6.1  | Carbon nanotubes and MEA used in experiments 68          |

| 6.2  | Trial and error experiment setup                         |

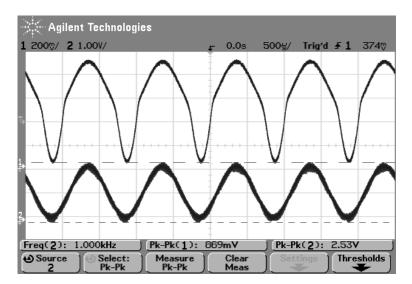

| 6.3  | 1000 Hz input                                            |

| 6.4  | 1000 Hz and 800 Hz as input                              |

| 6.5  | Weighted sum                                             |

| 6.6  | Material response without noise                          |

| 6.7  | Material response with noise                             |

| 6.8  | Frequency response experiment setup                      |

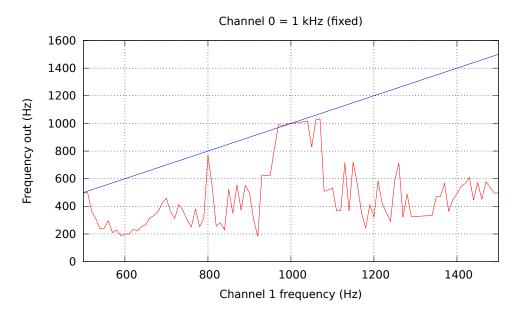

| 6.9  | Frequency in vs. frequency out                           |

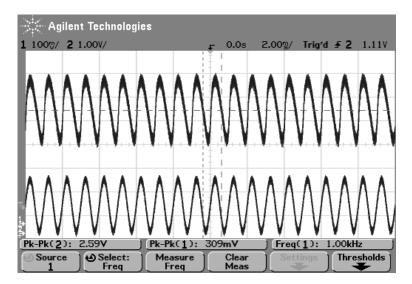

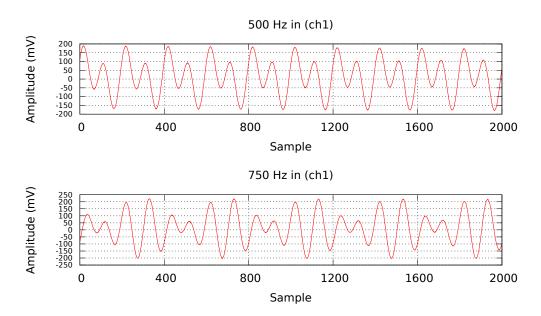

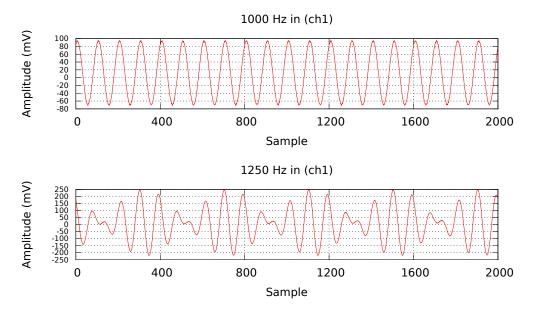

| 6.10 | Waveform plot at 500 Hz and 750 kHz                      |

| 6.11 | Waveform plot at 1000 Hz and 1250 Hz                     |

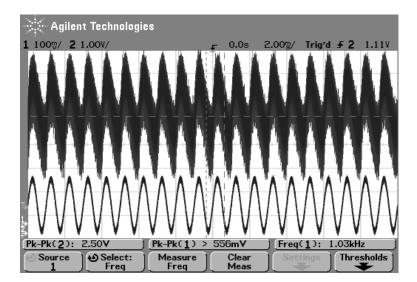

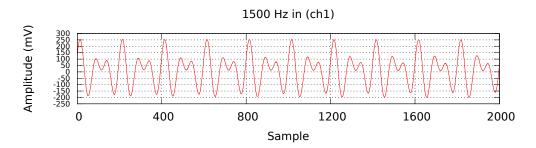

| 6.12 | Waveform plot at 1500 Hz                                 |

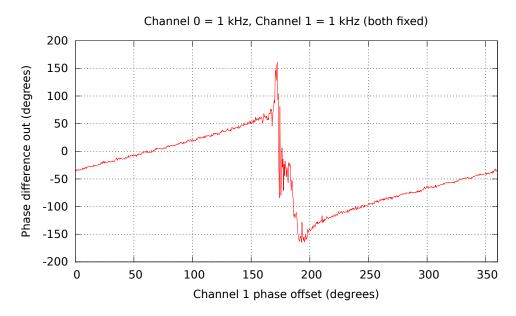

| 6.13 | Phase response 1                                         |

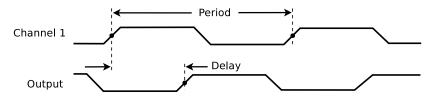

|      | Phase difference calculation                             |

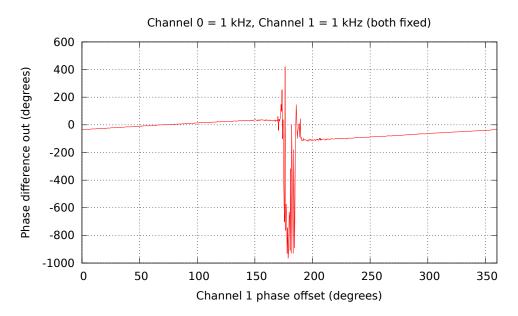

| 6.15 | Phase response 2                                         |

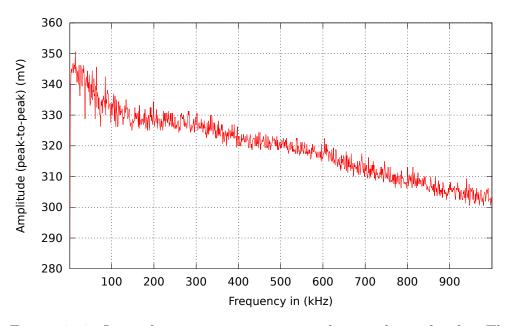

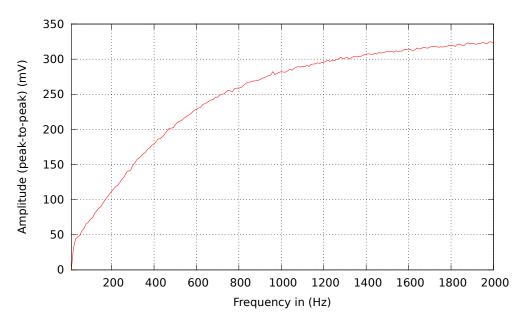

| 6.16 | Frequency (1 kHz - 1 MHz) vs. peak-to-peak amplitude 77  |

|      | Frequency (10 Hz - 1 kHz) vs. peak-to-peak amplitude 78  |

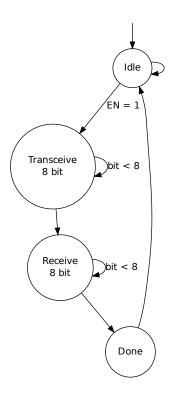

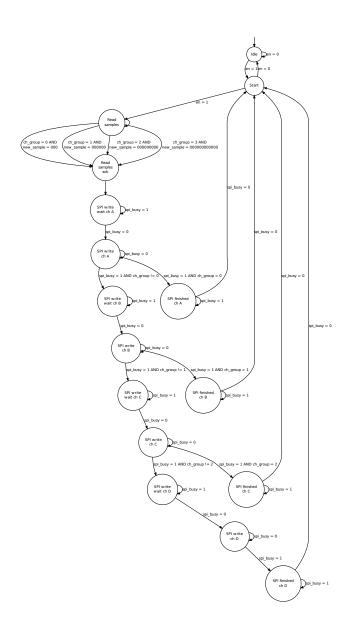

| B.1  | FSM of the ADC SPI controller                            |

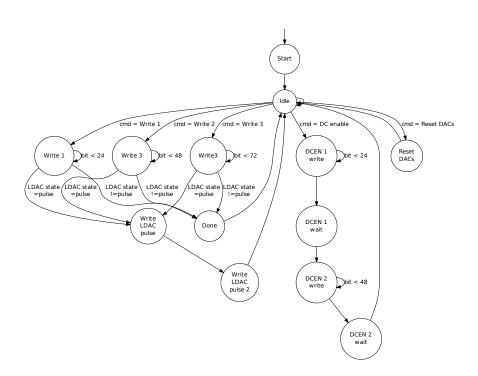

| B.2  | FSM of the DAC SPI controller                            |

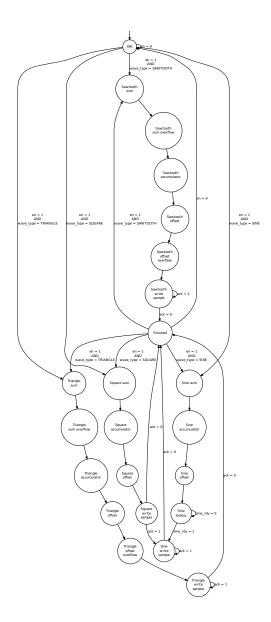

| В.3  | FSM of the NCO                                           |

| B.4  | FSM of the sample register                               |

| E.1  | Analog board PCB schematic                               |

# List of Tables

| 3.1  | EA genome example                          |

|------|--------------------------------------------|

| 4.1  | DAC SPI commands                           |

| 4.2  | DAC channel grouping                       |

| 4.3  | Channel group frequencies                  |

| 4.4  | New user module commands                   |

| 4.5  | New libEMB functions                       |

| 4.6  | Argument constraints                       |

| 4.7  | PCB design rules                           |

| A.1  | libEMB function tests                      |

| A.2  | SPI DAC controller tests                   |

| A.3  | SPI ADC controller test                    |

| A.4  | Sine look-up table test                    |

| A.5  | Sine look-up table wrapper test            |

| A.6  | Configuration register test                |

| A.7  | Wave configuration register test           |

| A.8  | Wave memory test                           |

| A.9  | Wave generator test                        |

| A.10 | Sample register tests                      |

| A.11 | Wave controller tests                      |

| A.12 | Wave module tests                          |

| A.13 | Toplevel tests                             |

| C.1  | Test equipment                             |

| D.1  | Bill of materials for the analog board 100 |

# Acronyms

FPGA field programmable gate array

PCB printed circuit board

**EA** evolutionary algorithm

${f SPI}$  serial peripheral interface

**DDS** direct digital synthesizer

${f NCO}$  numerically controlled oscillator

INL integral nonlinearity

**DNL** differential nonlinearity

DAC digital-to-analog converter

${f ADC}$  analog-to-digital converter

PA phase accumulator

PAC phase-to-amplitude converter

SNR signal-to-noise ratio

${f SFDR}$  spurious-free dynamic range

MSB most significant bit

LSB least significant bit

FSM finite state machine

LUT look-up table

**ROM** read-only memory

# Introduction

This master's thesis is a about unconventional computation and unconventional computational machines. It is a part of a Future and Emerging Technologies project called NAnoSCale Engineering for Novel Computation using Evolution (NASCENCE). This project is funded by EU's Seventh Framework Programme (FP7). From the projects website we can read that: "The aim of this project is to model, understand and exploit the behavior of evolving nanosystems (e.g. networks of nanoparticles, carbon nanotubes or films of graphene) with the long term goal to build information processing devices exploiting these architectures without reproducing individual components. With an interface to a conventional digital computer we will use computer controlled manipulation of physical systems to evolve them towards doing useful computation." [nas]

## 1.1 Unconventional Computation

As Moore's law is expected to collapse sometime in the future, we need a new way to do computation to be able to continue the increase in speed and energy efficiency that we see in computers today. In the past, most of the improvements came from new microarchitectures that exploited instruction-level parallelism and from higher clock speeds. Unfortunately, these improvements cannot continue indefinitely because of the serial nature of the uniprocessor and the heat it generates at high frequencies. So for the last ten years, the processor industry has shifted the focus from single-core processors towards multi-core processors to take advantage of data-level and thread-level parallelism [HP12]. Although this is an important step, it is not enough to overcome the ever-increasingly demand for more speed and energy efficiency. Projects like NASCENCE is hopefully

the start of a transition from conventional to unconventional computers in areas that needs the computational strength of a unconventional computer to solve difficult problems faster or where low energy consumption is crucial. The goal is not necessarily to replace all conventional computers, but instead be a supplement.

Today, the word computation is something that most people associate with the traditional electronic computer based on von Neumann's stored program machine, consisting of silicon transistors. However, a lot of physical processes can be viewed as a computational process. Maybe the most apparent one is the biological process where an organism is developed from a zygote to a fully grown individual [KB03]. Another example is the Belousov-Zhabotinsky reaction. This is a nonlinear oscillating chemical reaction that creates complex patterns. It is an example of non-equilibrium thermodynamics that can be used to manipulate and process information and it is a subject of study in the field of reaction-diffusion computing [JHJ10]. A common denominator for these physical processes is that there is no central control. The system where the computation takes place is distributed and consists of many small parts that interacts locally with the nearest neighbors [SLHR06]. The system is parallel by nature and it often exhibits complex and non-linear properties that emerges from this interaction. This could be very useful. For example, small perturbations may cause great effect on the system as opposed to a system with linear properties where the effect usually is proportional to the perturbation [JHJ10].

We want to exploit this computational capability to do computation much faster and/or more energy efficient than what is possible with a conventional computer. Problems that are considered impossible to solve on the traditional computer may be solvable using such an unconventional computer. These systems may also offer other desirable properties such as robustness and adaption because of its decentralized structure [Hey]. There is no central processor or control that needs to function correctly so that the rest of the system can work correctly. All the small parts contribute equally and if some of them are disturbed or destroyed, the rest of the system may continue to function properly together. This is an example of robustness. Adaption may help the system to function correctly in different environments, by reorganizing and stabilize in a new state while maintaining its original operation or function.

While a conventional computer can be controlled and programmed using a large number of different programming languages that works as digital ab-

straction layer for a processor that we know all about, this is not the case with unconventional computers. They are often distributed and consists of a vast number of processing elements that together creates the emergent computational properties. The implementation could be a number of different physical and distributed systems where there is no obvious way to specify the systems operation or function. In such a distributed system, the programming techniques can be separated into two categories [Sip02]. The first one is direct programming where the programmer completely specifies the interaction/connection between the parts and each parts function, etc. If we do not have any knowledge about the systems internal structure and we don't know how the desired properties emerges or if it is to complicated to use direct programming, we could use an adaptive method such as artificial evolution [Dow10]. In this method, the system is specified to a certain extent before the adaptive process of evolution develops or produces the functionality we want.

#### 1.2 Evolution In Materio

Evolution in materio is a field of research that uses artificial evolution to control or manipulate materials to do some form of computation. The material can be solid, liquid or gas. The idea is to use artificial evolution to change the physical or electrical configuration of the material and exploit the emergent properties to do the computation. The physical system, in this case some type of material, may have very complex and unpredictable properties. It may be very hard or even impossible for humans to understand how the system works and we therefore need a way to overcome this problem. The power of evolution is that it does not have to know anything about the problem it tries to solve. We can therefore use artificial evolution as tool to solve complex problems we humans have little or no knowledge about [Har06]. By mimicking nature, we can configure the system without knowing how it works internally. We can view it as a black box. The material we are currently experimenting with is carbon nanotubes. We now little about the internal workings of the material and how its properties emerges and therefore we use artificial evolution to investigate this.

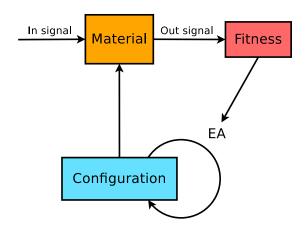

Figure 1.1 shows how one may visualize evolution in materio. The physical or electrical configuration of the material is changed and an input signal is processed by the material. The modified output signal is tested and its fitness is measured according to a fitness function. The fitness score

Figure 1.1: Visualization of evolution in materio.

is then used by the evolutionary algorithm to change the configuration using different genetic operators (such as mutation and crossover). The evolutionary algorithm moves through the solution space in search for a possible solution.

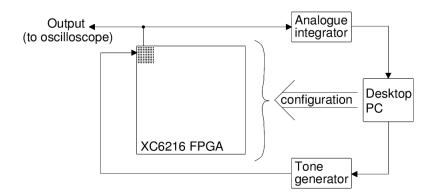

Evolution in materio has been successfully applied to several problems. For example, Simon Harding has used the technique to evolve a robot controller using liquid crystals as material [Har06]. Another example is Adrian Thompson's experiment where he evolved a tone discriminator circuit on a field programmable gate array (FPGA). The setup of the experiment is shown in figure 1.2. The FPGA acts as the material and the desktop PC runs the evolutionary algorithm and applies the different configurations to the FPGA. The tone generator is used to test the circuit and the integrator is for measurements that is used in the fitness calculation. The evolved circuit could discriminate between two different tones and it exploited the inherently analog nature of the silicon transistor [Tho96]. More about these experiments in chapter 2.

#### 1.3 Thesis Outline

This master's thesis describes an extension to the evolution in materio prototype system developed by Odd Rune Strømmen Lykkebø, as part of his master's thesis [Lyk10]. The system is currently only able to apply digital signals to the material, but we also want it to have the ability to apply dynamic signals, e.g. a sine wave or triangle wave, and sample the output response signal. The reason for this is simple; we are searching for an

Figure 1.2: Adrian Thompson's experiment setup. Illustration taken from [Tho96].

electrical configuration(s) that manipulates the material so that computational properties emerges. By extending to analog signals we get a much larger set of possible configurations. The extension is therefore a printed circuit board with digital-to-analog and analog-to-digital converters that connects to the material, in addition to necessary software and hardware needed for the communication between the prototype system and the new extension.

Chapter 2 describes some previous work done in this field and a brief overview of the work done by Odd Rune Strømmen Lykkebø. Chapter 3 gives and overview of the system, both the original system and the new extension. In chapter 4 we dive into the details of the system and look how it really functions, its capabilities and its limitations. The testing and evaluation is described in chapter 5. Chapter 6 presents initial experiments where we test the response of the material. Chapter 7 ends this master's thesis with a conclusion.

# 2 Background

This chapter presents background information on the earlier work done in the field of evolution in materio. In addition, it gives an overview of the existing platform that this thesis is an extension of.

#### 2.1 Previous Work

#### 2.1.1 Pioneer Work

The English cybernetician and psychologist Gordon Pask was a pioneer in the fields of evolvable and self-organizing systems. In the 1950's he conducted experiments where he tried to evolve a complex system that was capable of perceiving sound or magnetic fields. The system's parts was not fully specified and the thought was that the system was able to create its own "relevance criteria", meaning that it would discover on its own the observables that was required to perform a given task [Car93]. This was a very different engineering approach at the time. Usually, each component in a system has its position and behavior specified.

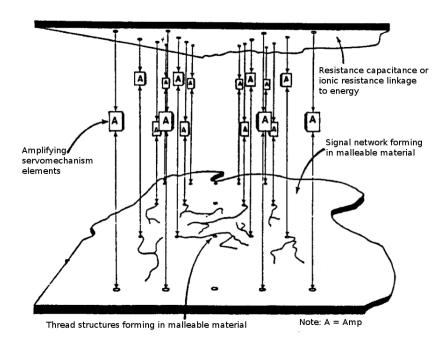

Gordon Pask used an electrode array that was suspended in a dish that contained an acidic aqueous metal-salt solution. This type of solution has the potential to behave in a very complex way [Car93]. By applying current on the electrodes, wires can self-assemble in the metal-salt solution. Figure 2.1 illustrates the experimental system with wires forming between electrodes in the chemical solution at the bottom. A network of these wires forms and together they can perform signal processing. Gordon Pask's system did manage to discriminate between 50 Hz and 100 Hz tones.

Figure 2.1: Schematic Gordon Pask's electrochemical system. Illustration taken from [Car93].

To train or program the system so that the desired behavior emerged, Pask used a set of resistors and changed their values using probabilities. This can be seen as a precursor to or a crude version of an evolutionary algorithm [Har06]. So in essence, what Gordon Pask did in his experiments is very similar to what we today call evolution in materio.

#### 2.1.2 FPGA Tone Discriminator

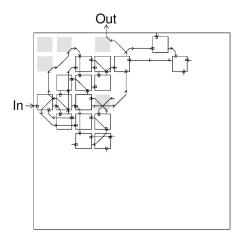

Closely related to evolution in materio is the field of *intrinsic hardware evolution*. It uses artificial evolution to evolve electronic circuits. Adrian Thompson was in the mid 90's the first to use artificial evolution to evolve an FPGA configuration that could discriminate between two square waves of 1 kHz and 10 kHz without any clock source [Tho96]. The evolved circuit consisted of  $10 \times 10$  logic cells that were connected together. A number of cells were removed without affecting the behavior of the circuit. Figure 2.2 shows the resulting functional part of the circuit. The gray boxes are cells that cannot be removed without affecting the behavior of the circuit. This is strange since these cells cannot influence the output via a connected path. These cells have some effect on the other cells, but

Figure 2.2: Functional part of the evolved circuit with gray cells that cannot be removed without affecting the behavior. Illustration taken from [Tho96].

not through wiring. Thompson suggested that this effect could come from power-supply wiring or electromagnetic coupling.

Even though we humans think of the FPGA as a digital device, under the hood it is analog, just as the rest of the world. The evolutionary algorithm don't care about this abstraction and exploits everything to find a candidate solution. In this way, Thompson's experiment can be viewed as evolution in materio since it exploited the analog properties of the silicon transistors in the FPGA to evolve a working circuit.

#### 2.1.3 Liquid Crystals

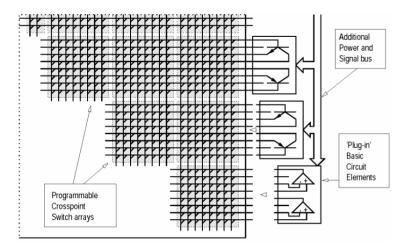

Another more recent example of evolution in materio is the work done by Simon Harding where he used liquid crystals as material [Har06]. The hardware platform he used for these experiments was a liquid crystal evolvable motherboard. It was based on previous motherboards that has been used for intrinsic hardware evolution. An example of such a previous motherboard is shown in figure 2.3. This motherboard was constructed by Paul Layzell. He was motivated by Adrian Thompson's work on intrinsic hardware evolution, but he wanted to be able to monitor the whole system during the evolutionary process. Since you cannot monitor signals inside an FPGA he developed a system where you can do that. The figure shows many switch arrays where each crosspoint can be controlled individually. At the sides, discrete components can be connected and thus it is possible

Figure 2.3: Evolvable motherboard constructed by Paul Layzell. Illustration taken from [Har06].

to monitor the evolutionary process. Several successful experiments were conducted.

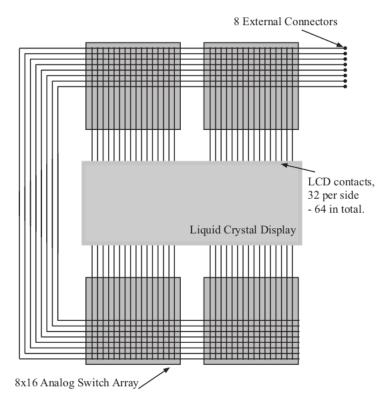

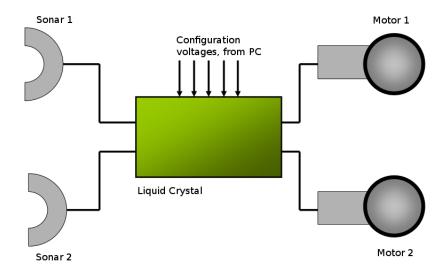

Simon Harding created his evolvable motherboard by connecting an offthe-shelf liquid crystal display to switch arrays as shown in figure 2.4. The switches are controlled by a computer and this computer also reads the response from the liquid crystal display. By using an evolutionary algorithm that applied voltages to the connections he was able to evolve complex material behavior. Among the successful experiments was the evolved real-time robot controller that could navigate around in a simulated environment. Signals from two sensors was fed to the liquid crystal and the response was used to control the robot using two motors as shown in figure 2.5. The sensors measured the distance to an obstacle and was instructed to output a square wave signal with a frequency that was proportional to the straight line distance. Then, the liquid crystal did some form of signal processing with the square wave signals coming from the sensors and controlled the motors by setting the voltage to high or low. According to [Har06], this is the first time liquid crystal has been used to control a robot.

Figure 2.4: Liquid crystal evolvable motherboard constructed by Simon Harding. Illustration taken from [Har06].

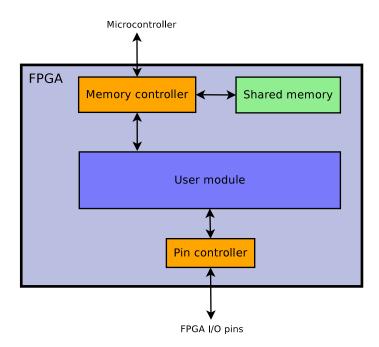

# 2.2 Existing Platform

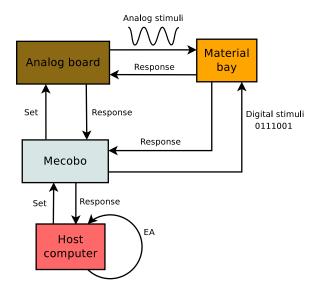

As stated in chapter 1, the work presented in this thesis is based on Odd Rune Strømmen Lykkebø's master's thesis. In his thesis, he designed and implemented a prototype system for evolution in materio. The overview of the system is shown in figure 2.6. It consists of a host computer, a microcontroller, an FPGA and a material bay for interfacing with the material. The main part in the system is called Mecobo, and this is where the microcontroller and the FPGA are located. It connects the host computer with the material bay. Figure 2.7 shows what Mecobo looks like. The laptop acts as the host computer where the evolutionary algorithm runs. On the right we have Mecobo and in the middle is the material bay that can contain different materials.

To communicate with Mecobo and set a voltage pattern on the electrodes in the material bay you have to use a C library specifically made for this system, called *libEMB*. This library contains different functions to

Figure 2.5: Setup for the evolved robot controller. Illustration taken from [Har06].

Figure 2.6: System overview without the new extension.

set and read the electrodes, in addition to other functions. Calling these functions will cause the host computer to communicate with the microcontroller on Mecobo which in turn will communicate with the FPGA. When Mecobo has done its work, the function that was called on the host computer returns. An example of how to use the setPattern function is shown in listing 2.1. The function has two arguments, where one (pinconfig\_t \*config) specifies which pins is output and the other argument (pattern\_t \*pattern) specifies the pattern to apply to the output pins. As we can see, the use of this function is fairly easy.

Listing 2.1: setPattern code example

```

// Create a pin configuration with 2 pins

// Set both as output

pinconfig_t *config = init_config(2);

```

Figure 2.7: 1: Host computer. 2: Mecobo. 3: Material bay. Picture taken from [Lyk10].

```

set_pin_mode(0, PIN_OUT, config);

set_pin_mode(1, PIN_OUT, config);

// Generate a random pattern

pattern_t *pattern = generate_random_pattern(2);

// Set pattern

setPattern(pattern, config);

```

The material currently used in experiments is carbon nanotubes and it is shown in figure 2.8 This material was constructed by spreading out the nanotubes using a probability distribution. This causes the nanotube density to be nonuniform. The idea is that the nonuniform density will provoke nonlinear properties in the material. There are also plans to use the gold particles, shown in figure 2.9, sometime in the future.

Figure 2.8: Nanotubes made of carbon. Electrodes for interfacing with the material is clearly visible as dark lines going towards the center.

Figure 2.9: Picture of gold particles that will be used as material under test in the future.

# System Overview

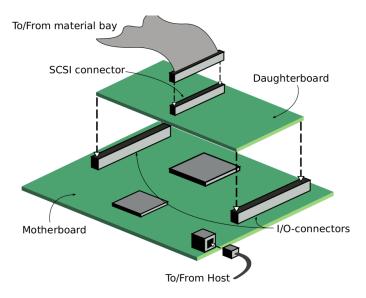

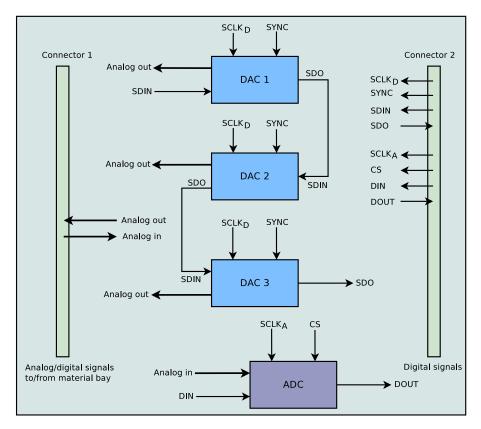

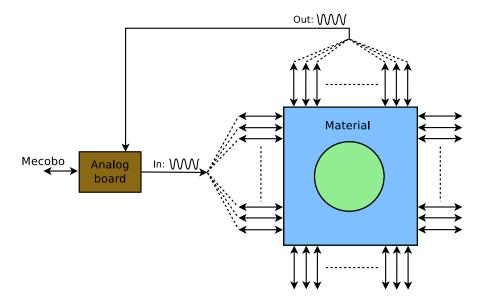

In this chapter we will explain the main parts of the original system and the new extension/daughterboard (just called analog board) and give an overview of its capabilities. Figure 3.1 shows where the analog board fits in the original system. As we can see from the figure, the analog board is connected to the FPGA on one side and to the material bay on the other side. This is illustrated in more detail in figure 3.2. The connectors shown in this figure is not necessarily what we actually use, but it gives us an idea of the connection between Mecobo and a daughterboard.

Figure 3.1: System overview, including the analog board.

## 3.1 The Experimental Hardware

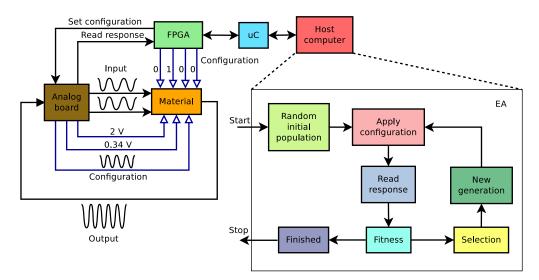

The purpose of Mecobo is to be able to apply electric current to some kind of material. Since the FPGA is a digital device it can only set the voltage on the electrodes in the material bay to digital high or low, which decreases the search space for the evolutionary algorithm (EA). With the analog board however, we can choose between many more voltage levels. This will greatly increase the search space of the EA. Figure 3.3 shows the system we want and how the information flows. Here, we are using

Figure 3.2: Mecobo and how it interfaces with the daughterboard. Picture taken from [Lyk10].

both analog and digital stimuli as the input signal or configuration. The stimuli is first set and then the response is read back and used as input to the fitness function in the EA that is running on the host computer. This is repeated until the EA terminates because of a predefined termination criterion that has been met, such as a fitness threshold, elapsed time or number of iterations or generations.

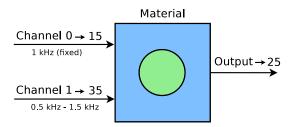

As a more detailed example, we can define two outputs from the analog board as input to the material and three outputs as a part of the configuration. We can also define one input to the analog board as the output from the material which we will use to measure the response from the material. Four pins on the FPGA might be define as the second part of the configuration. The goal could be to double the frequency of one of the input signals and sum the amplitude of the two input signals. Figure 3.4 illustrates this proposed experiment setup and its final configuration where the goal is met. We can see that the two input sine signals has the same fixed amplitude and frequency. The part of the configuration coming from the FPGA is expressed as a bit-pattern and in this case equal to 0100. The second part of the configuration is coming from the analog board. The two first signals is just static voltages. The third configuration signal is a regular sine wave. From the output signal we can see that the material has doubled the frequency of the input signals and summed their amplitude. To actually reach the goal function, we can use a (1+4)-ES (evolutionary

Figure 3.3: The prototype system and the main flow of information between the components.

strategy). This is a simple evolutionary algorithm with one parent and four children. The expanded view of the host computer in figure 3.4 shows the main steps in the EA. First, we generate a random population of 4 individuals. Each of these individuals has its own configuration that is applied to the the material. This configuration acts as the genome. An example of how it can be represented is shown in table 3.1. The configuration for the three analog inputs are expressed as the amplitude, frequency and phase of a sine wave. The configuration for the digital inputs are just a bit pattern. For each individual, the response from the material is read back and the fitness is calculated so that we can rank the individuals and select the best one to be the parent for the next generation. Choosing the right fitness function is often the hardest part in an evolutionary approach. It has to be defined properly so that it takes into account those parameters and properties that makes the algorithm converge to a good solution. After the selection process, the individual that was selected is now a parent and is used to generate four new individuals or children. This is done by using genetic operators to alter the parent's genome. The cycle continues until one of the individual's fitness value has reached a certain threshold.

Figure 3.4: One possible experiment setup.

|   | Analog stimuli |                |           | Digital stimuli |

|---|----------------|----------------|-----------|-----------------|

|   | Amplitude (V)  | Frequency (Hz) | Phase (°) | Bit pattern     |

| 1 | 1.23           | 100            | 0         |                 |

| 2 | 2.5            | 0              | 90        | 0001            |

| 3 | 0.34           | 587            | 245       |                 |

Table 3.1: Example genome for the evolutionary algorithm.

## 3.2 Extension

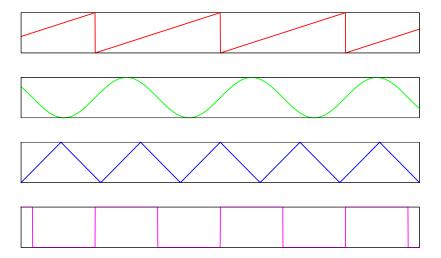

As already stated, we want to be able to apply multiple analog signals, both dynamic and static, and read the response from the material. We decided that 12 output signals together with 8 input signals are enough for now. We want four different wave types: sawtooth wave, sine wave, triangle wave and square wave. These waveforms are shown in figure 3.5. For these waves we want to control the frequency, amplitude and phase offset. This will greatly increase the search space since every new variable adds a new dimension to the search space. The frequency range requirement is quite loose, but a range from 0 Hz to several kilo hertz should be sufficient and the frequency resolution should be less than 10 Hz. The phase offset range should be from 0° to 360° with at least one degree resolution. The amplitude range should go from 0 V to a variable voltage level that we can change if we want to. The amplitude resolution should be high enough so that we get a smooth wave at high frequencies and amplitudes. Static

Figure 3.5: Waveforms we want the system to generate.

signals can be expressed as a sine wave of zero hertz and a phase offset. The sampling part of the system should be able to sample a dynamic signal with a frequency of several kilo hertz. Figure 3.6 illustrates the sampling of signals from the material. The response is converted from analog voltage to a digital code on request from the FPGA and then it is sent to the host computer via Mecobo. Because we don't know all the properties of the material or the configuration(s) needed to manipulate it, we define these somewhat loose requirements.

To reach the specified requirements, we need a suitable digital-to-analog converter (DAC) and a analog-to-digital converter (ADC). The converters are to be connected to the FPGA on Mecobo. Using the FPGA as a controlling unit gives us great flexibility in the design and it is easier to meet timing constraints. It also makes the pairing with the old design much easier. What we essentially want is an arbitrary waveform generator or a direct digital synthesizer (DDS).

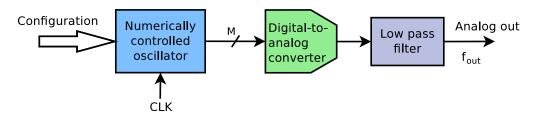

## 3.2.1 Direct Digital Synthesizer

A DDS is a type of frequency synthesizer that can create arbitrary waveforms with a wide range of frequencies and phase offsets, using a single fixed-frequency oscillator [dds]. The DDS consists of a numerically controlled oscillator (NCO), a digital-to-analog converter and a low-pass filter, as shown in figure 3.7. The NCO is implemented on the FPGA while the

Figure 3.6: Sampling the response from the material.

Figure 3.7: Main components of a direct digital synthesizer.

DAC is on the analog board. The low-pass filter is not on the analog board, but implemented as a separate part. By doing this, we can change the filter to another one with different characteristics. The next chapter will give a detailed explanation of the different components.

# 3.2.2 Signal Sampling

Generating waveforms is not enough. We also have to be able read the response from the material. So in addition to the DDS, we created a way to sample signals using an ADC. The design of such a system is less complicated than the DDS, but just as important. The FPGA controls the ADC and instructs it to send new samples, which the FPGA stores in a shared memory. The microcontroller can then read these samples and send them to the host computer.

4

# Design and Implementation

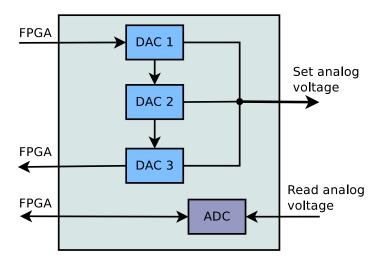

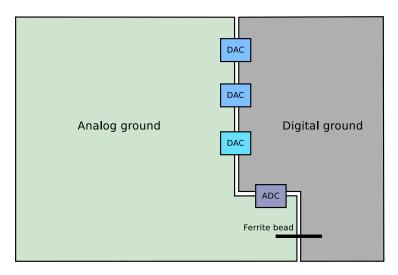

This chapter explains in detail how the system works. The system must be able to set and read analog signals and the main parts on the analog board are therefore three digital-to-analog converters (DAC) and one analog-to-digital converter (ADC), where the DACs sets the analog signals and the ADC reads the response. To control the analog board we use an FPGA which gives us great control and flexibility when it comes to the design of the DAC and ADC controllers and the design of the NCO. Communication between the FPGA and the analog board happens constantly during operation since the NCO always has a new wave sample for the DAC(s) and because the FPGA instructs the ADC to sample the response signal when the user of the system requests it.

First, we will describe the DA/AD converters in section 4.1. In section 4.2 comes an explanation of the FPGA design and especially the design of the parts that together makes up the NCO. Section 4.3 describes the changes in the microcontroller design while the new functions in the libEMB library is described in section 4.4. Then comes the PCB design section 4.5. After that, in section 4.6, comes a short description of the low pass filter that is used during testing and experimentation. In section 4.7, we will describe the most important known error sources of the system.

# 4.1 DA/AD Converter

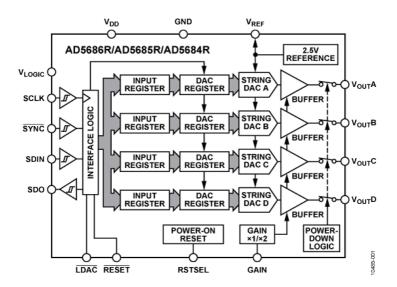

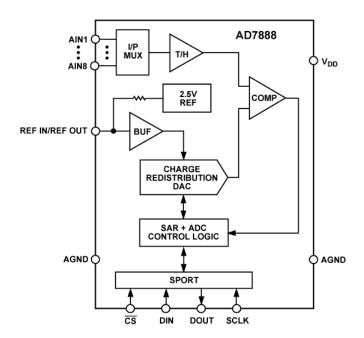

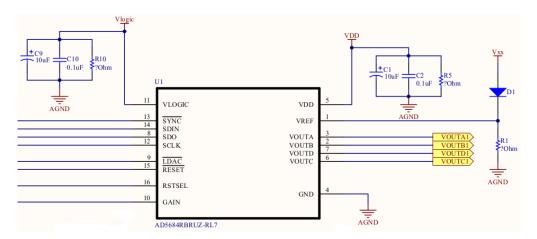

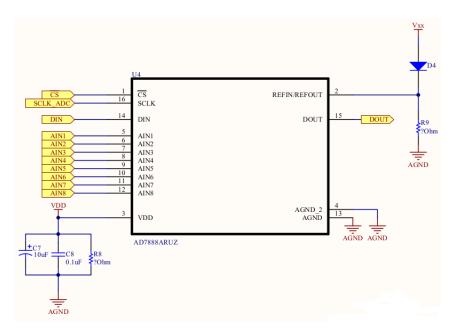

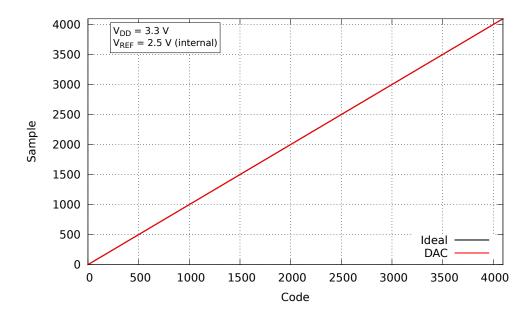

Figure 4.1 shows the analog board and its main components at a high level of abstraction. The exact chips used are AD5684R (DAC) and AD7888 (ADC) from Analog Devices. The block diagram of the DAC chip is shown in figure 4.2 and the block diagram of the ADC chip is shown in figure 4.3.

Figure 4.1: Analog board overview.

Each DAC has 4 channels and the board can therefore set 12 different signals. The ADC has 8 channels. Both DAC and ADC has a 12-bit resolution. Using 12-bit gives a sufficient resolution for our purposes. It means that the ADC can detect a voltage change of

$$\Delta V = \frac{V_{REF}}{4096} \tag{4.1}$$

where  $1.2 \text{ V} \leq V_{REF} \leq V_{DD}$ , when the reference source is external. Using the internal reference source gives  $V_{REF} = 2.5 \text{ V}$ . The external voltage reference pin is connected to  $V_{DD}$ , but an optional resistor can be used to adjust the external reference to the desired voltage. Each DAC has an output amplifier which is controlled by the gain pin. When the gain pin is tied to ground, the four output voltages can span between 0 V and  $V_{REF}$ . If it is tied to  $V_{DD}$ , the voltage span between 0 V and  $2 \times V_{REF}$ . The (ideal) output voltage is calculated using

$$V_{OUT} = V_{REF} \times Gain\left[\frac{D}{4096}\right] \tag{4.2}$$

where  $0 \text{ V} \leq V_{REF} \leq V_{DD}$  with an external reference or  $V_{REF} = 2.5$  V with the internal reference. As with the ADC, the external voltage reference pin on the DACs are connected to  $V_{DD}$  with an optional resistor for adjustment. Disabling of the internal voltage reference is done by writing to the configuration register, for both the DAC and ADC. Gain is 1 or 2 depending on whether it is tied to ground or  $V_{DD}$  (as stated above). The variable D is the base 10 converted binary value written to the DAC, and  $0 \leq D \leq 4095$ .

<sup>&</sup>lt;sup>1</sup>Not the same  $V_{REF}$  as the ADC uses.

Figure 4.2: Block diagram of the digital-to-analog converter (AD5684R). Source: http://www.analog.com/static/imported-files/images/functional\_block\_diagrams/AD5684R\_fbl.png.

Figure 4.4 shows the analog board at a more detailed level when it comes to the digital communication. Both the DACs and ADC uses serial peripheral interface (SPI) for communication. This is a full duplex synchronous serial communication interface, with only four signals. This means that it is relatively easy to implement an SPI controller on the FPGA that can communicate with these devices. The four signals are clock (SCLK<sub>D/A</sub>), slave select (DAC:  $\overline{\text{SYNC}}$ , ADC:  $\overline{\text{CS}}$ ), serial in (DAC: SDIN, ADC: DIN) and serial out (DAC: SDO, ADC: DOUT).

The DAC features a daisy-chain mode, which means that you can connect several DACs together by connecting the serial out pin on one DAC to the serial in pin on the next DAC. Data is first clocked into the first DAC. The command register is 24 bits and when more than 24 bits is clocked in, bits will be clocked out of the first DAC and into the second. So when there is three DACs the clock has to run for  $3 \times 24 = 72$  clock cycles so that all three DACs receives their command. This makes it easy to scale up and add more DACs since you only need one serial line for input and one for output. It is especially useful when I/O-pins on the FPGA are scarce, since no matter how many DACs you add, only two I/O-pins is needed for data transfer (you also need clock and select of course). The serial out pin on the last DAC provides readback for the FPGA.

All the DACs share the same select signal called SYNC. This signal is low

Figure 4.3: Block diagram of the analog-to-digital converter (AD7888). Source: http://www.analog.com/static/imported-files/images/functional\_block\_diagrams/AD7888\_fbl.png.

when bits are clocked into the configuration register, and then it is taken high to signal that a new command is in the register. This command is then executed. The LDAC signal is also shared. When you want to set a new output voltage on the DAC channels, you can use the  $\overline{\text{LDAC}}$  signal to specify when the channels should be updated. Each DAC channel has two registers where the digital voltage code is stored. One is called *input* register and the other is called DAC register. The output voltage is only update when the DAC register is updated. Holding  $\overline{LDAC}$  high during transfer will only update the addressed input register, while holding it low will update both registers. Holding it high during transfer, but taking it low at the end of the transfer (LDAC is pulsed low) will update all channels asynchronously regardless of which channel was addressed. So, for example writing a new voltage code to three of the DAC channels while holding  $\overline{\text{LDAC}}$  high and then write to the last channel and pulse  $\overline{\text{LDAC}}$ low when the transfer is finished will update all channels asynchronously. All three DACs also share the same reset signal. More information about the specifications can be found in the datasheets [dac, adc].

Figure 4.4: Block diagram of the analog board with communication lines.

## 4.2 FPGA

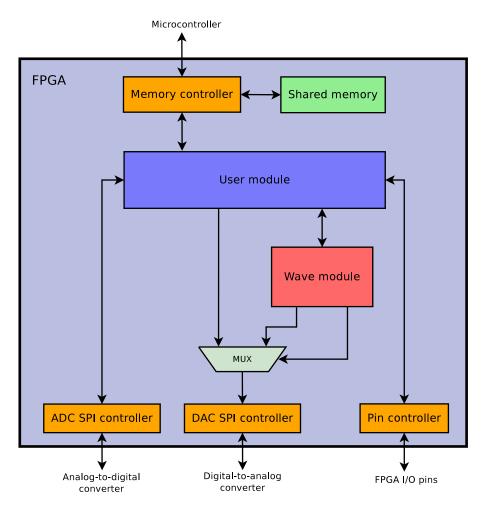

To be able to use the analog board we have to extend the FPGA design. Figure 4.5 shows the original FPGA design. In figure 4.6, we have added two SPI controllers, a wave module and a multiplexer. We have also extended the user module. Next, we will explain the new parts in detail. We will also give a brief explanation of the parts in the original design. Also, the new design is expecting an FPGA frequency of 50 MHz.

# 4.2.1 Original Design

The memory controller controls the access to the shared memory for both the microcontroller and the user module. The user module is implemented as a finite state machine (FSM) and its purpose is poll the shared memory to see if the microcontroller has written a new command to the command

Figure 4.5: FPGA design overview.

memory location. The command is either to configure the I/O pins (decide which one is input or output and set output pins to high or low) or read back the response from the material for those pins that are designated as input. More information on the original design can be found in [Lyk10].

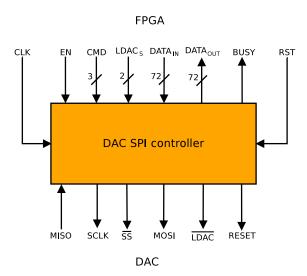

#### 4.2.2 DAC SPI Controller

The DAC SPI controller takes care of the communication with the three DACs. Figure 4.7 shows the block diagram. The controllers FPGA interface includes a clock (CLK), reset (RST), enable (EN) and busy (BUSY) signal. In addition we have a command signal that tells the controller which command it should execute when EN is asserted. The DATA in signal contains the data that is written to the DACs and the LDAC signal determines if the  $\overline{\text{LDAC}}$  pin should be high or low when writing to the DACs.

The DAC interface contains a serial clock (SCLK), slave select (SS), DAC reset (RESET), LDAC (LDAC), serial in (MISO) and serial out (MOSI). The serial in or MISO signal is currently not in use. The DAC supports a readback command which clocks the register content out on MISO, but the DAC SPI controller does not support this since it's a feature we actually don't need.

Figure 4.6: The extended FPGA design overview.

To prevent signal glitches, we added registers that works as buffers for the SPI output signals. The combinatorial logic in the finite state machine may cause glitches, but adding the registers (flip-flops) at the output prevents this glitches to propagate further. Adding these registers causes the signals to have a delay of one clock cycle.

Looking at table 4.1 we see that the controller has three write commands. It also has a daisy-chain enable implemented in hardware, that writes the daisy-chain command to the first two DACs. The last command is a reset command that resets the digital-to-analog converters. Their output voltage after a reset depends on whether RSTSEL is connected to ground or  $V_{DD}$ . The serial clock (SCLK) is running at a frequency of 25 MHz. The controllers finite state machine can be found in appendix B.

Figure 4.7: Block diagram of the DAC SPI controller.

| Command           | Description             |

|-------------------|-------------------------|

| CMD_SPI_NOOP      | No operation            |

| CMD_SPI_WRITE_1   | Write to DAC 1          |

| CMD_SPI_WRITE_2   | Write to DAC 1 and 2    |

| CMD_SPI_WRITE_3   | Write to DAC 1, 2 and 3 |

| CMD_SPI_ENABLE_DC | Enable daisy-chaining   |

| CMD_SPI_RESET     | Reset DACs              |

Table 4.1: Overview of DAC SPI commands.

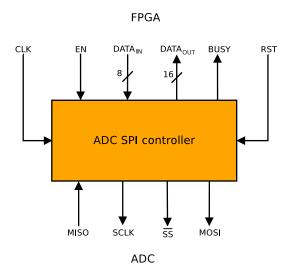

#### 4.2.3 ADC SPI Controller

The ADC SPI controller is less complicated than the DAC SPI controller. Figure 4.8 shows the input and output signals of the module. Just as the DAC SPI controller it has a clock (CLK), reset (RST), enable (EN) and busy (BUSY) signal. No command signal is needed since it only performs one command and that is to clock out 8 bits and clock in 16 bits. The DATA in signal provides the 8 output bits while the DATA out signal has the response ready when the controller goes idle and the BUSY signal is low. The 8 data bits being clocked out specifies the ADC channel to read next, enabling or disabling the internal reference voltage and power management. Since the voltage conversion is ready and clocked out on the next transfer, the first read after power up will always be zero. The ADC interface has the four standard SPI signals (serial clock, slave select, data in and data

Figure 4.8: Block diagram of the ADC SPI controller.

out) and the serial clock runs at frequency of 2 MHz. As with the DAC SPI controller, registers were added at the output to prevent glitches in the communication. The controllers finite state machine can be found in appendix B.

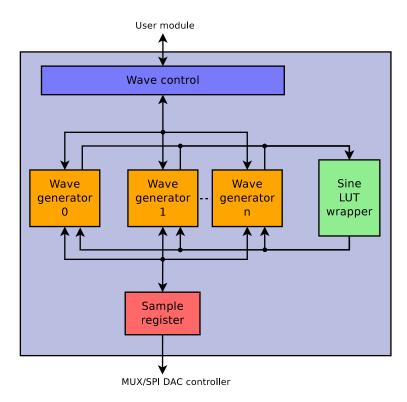

## 4.2.4 Numerically Controlled Oscillator

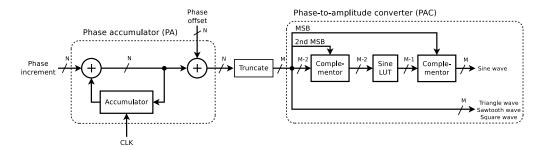

The NCO is the component that provides the DAC with samples. The NCO can be configured digitally, hence the name numerically controlled. The wave module shown in figure 4.9 consists of a wave control, several wave generators, a sine look-up table (LUT) and a sample register that communicates with the DAC SPI controller. The wave generators and the sine LUT is what actually makes up the NCO and there is one wave generator for each DAC channel. Figure 4.10 shows the block diagram of the NCO. This a very basic implementation of an NCO and it is based on the design in [Van96].

The first part is the phase accumulator (PA). At each clock cycle the phase increment (also called frequency control word) is added to the accumulator register. This produces a linearly increasing digital value or a sawtooth wave. Additionally, we can add a phase offset. Note that the phase offset is not accumulated like the phase increment. The accumulated value or phase, is then truncated and used in the phase-to-amplitude converter (PAC). The PAC outputs the phase value as it is for sawtooth waveforms

Figure 4.9: Block diagram of the wave module.

or converts the phase value into other waveforms by either using a lookup table or doing some calculations. The output value (amplitude) from the PAC is sent to the DAC, which converts this digital value/code to an analog voltage.

#### Phase accumulator

The accumulator register is N bits wide. At each clock cycle, the phase increment  $\Delta P$  is added to the accumulator register. When the register reaches  $2^N - 1$ , it overflows and starts from the beginning. Equation 4.3 gives the rate of overflow and thus also the frequency of the desired wave

$$f_{out} = \frac{f_{clk}}{2^N} \Delta P \quad \forall \quad f_{out} \le \frac{f_{clk}}{2}$$

(4.3)

where  $f_{clk}$  is the frequency of how often the FPGA is able to update the DACs. Remember that the DACs uses serial communication and the FPGA has to transfer  $3 \times 24 = 72$  bits when communicating with the three DACs. The FPGA will also add some overhead (e.g. starting and stopping

Figure 4.10: Block diagram of the numerically controlled oscillator.

a serial transfer), but the serial communication will be the limiting factor of  $f_{clk}$ . While the DAC SPI controller is busy transferring data, the wave generators will calculate the next sample and as long as the calculations take less time than the serial transfer, they will not limit  $f_{clk}$ . The limitation in equation 4.3 says that the equation is true for all  $f_{out}$  below or equal to the Nyquist frequency. From equation 4.3 we can derive

$$\Delta P = \frac{2^N}{f_{clk}} f_{out} \tag{4.4}$$

which is used to calculate the phase increment value based on the desired output frequency. By setting  $\Delta P = 1$  in equation 4.3, we get the minimum possible change in frequency, also called the frequency resolution

$$\Delta f_{out} = \frac{f_{clk}}{2^N} \tag{4.5}$$

The phase accumulator width in our system is set to N=16 bits which is the same as the shared memory word size. Higher N-value will give us better frequency resolution, but with N=16 we get around 5 Hz which is sufficient.

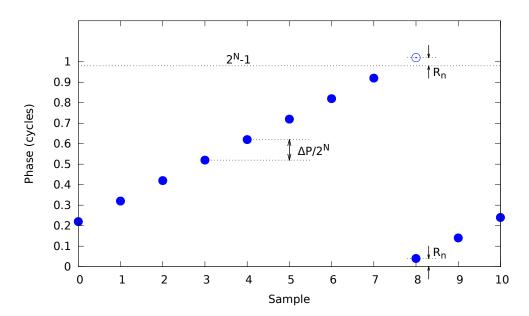

When the accumulator register overflows, the remainder  $R_n$  is stored in the register and the next cycle will then start at  $R_n$ . This is shown in figure 4.11. At sample seven, the accumulator register has almost reached the its highest value  $(2^N - 1)$  and at sample eight it overflows. The remainder  $R_n$  is now the starting value. Overflows may also occur when adding the offset, but the remainder  $R_n$  is not stored. After a certain number of cycles the initial remainder value  $R_0$  will be reached. The number of cycles it takes to reach  $R_0$  is called the numerical period or grand repetition rate. It is given by

$$Pe = \frac{2^N}{\text{GCD}(\Delta P, 2^N)} \tag{4.6}$$

Figure 4.11: Normalized phase accumulator output. Illustration inspired by http://en.wikipedia.org/wiki/File:Phase Accum Graph.png.

where  $GCD(\Delta P, 2^N)$  is the greatest common divisor of  $\Delta P$  and  $2^N$ . Since it does not take the exact same number of cycles each time to overflow the accumulator register for a given  $\Delta P$ , we are more interested in average overflow rate and this is what equation 4.3 tells us.

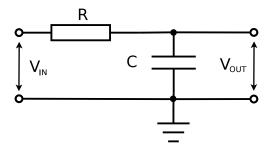

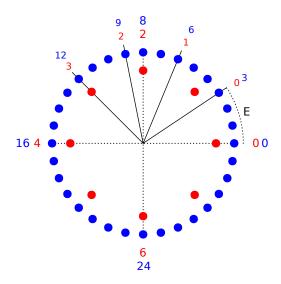

#### Phase-to-Amplitude Converter

While the PA determines the phase of the waveform, PAC determines the amplitude. This is done differently for different waveforms, but the truncation between the PA and PAC is common for them all. The width of the phase accumulator register is usually too large to be used directly as an index to a look-up table or directly as the amplitude of e.g. a sawtooth wave, because it may require too much memory space to store the look-up table in the first case and because it may be wider than the DAC resolution in the second case. Instead we use a fraction of the most significant bits. This means that the last W = N - M bits of the PA output has to be removed. We are then left with an M bit wide value as input to the PAC.

For the sine wave we use a LUT to find the right amplitude. This sine LUT is located on the FPGA and is implemented as a single port readonly memory (ROM). The memory requests from the wave generators are

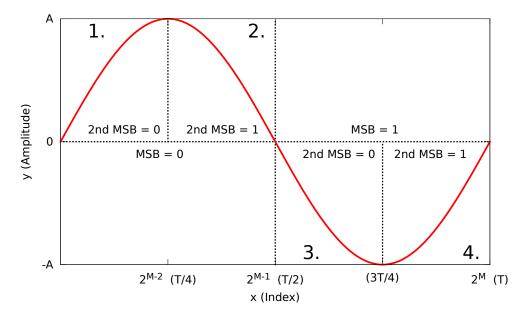

Figure 4.12: The four quadrants of a sine wave showing how the symmetry can be exploited.

processed sequentially and when all requests are handled, the values are presented to all wave generators at the same time. To save space we just store the first quadrant of the sine wave and exploit the sine wave symmetry to get the amplitudes for the second, third and fourth quadrant. Storing the whole period requires  $2^M \times K$  bits where M is the width of the index or address and K is the width of the amplitude. By storing only the first quadrant we will use  $2^{M-2} \times K$  bits which is four times less. We will have to add more logic to compensate for this, but smaller ROM means lower access time which is important since all the reads are handled sequentially.

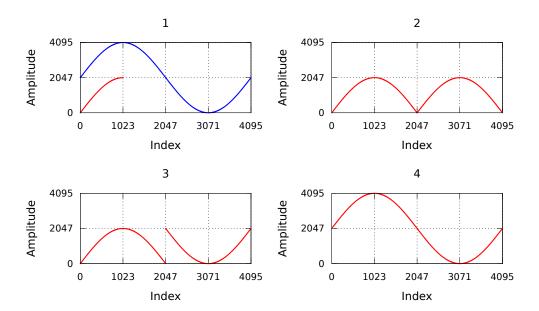

If we look at figure 4.12 we see the four quadrants and the value of the most significant bit (MSB) and the 2nd most significant bit of the index when indexing the different quadrants. Looking at figure 4.10 we see that the first complementor uses the 2nd MSB to decide the index. For the first and third quadrant it will go through the indexes from 0 to  $2^{M-2}-1$ , while for the second and fourth quadrant it will go from  $2^{M-2}-1$  to 0. This gives us a full rectified sine wave. The second complementor uses the MSB to decide the sign of the amplitude and invert the third and fourth quadrant to get a normal sine wave. In our implementation, the value of both M and K is set to 12 as this is the same as the DAC resolution. This gives us 4096 sine amplitude values that varies from 0 to 4095. Any wave will

Figure 4.13: 1: Stored quadrant and full period sine wave. 2: Full rectified sine wave out from the sine LUT. 3: Third and fourth quadrant inverted. 4: DC offset added to the first and second quadrant.

have a DC offset of 2048 and a peak-to-peak amplitude of  $2^{12} - 1 = 4095$ . So to further reduce the size of the sine LUT, we store the sine amplitude from 0 to 2047, instead of 2048 to 4095, using

$$2047 \times \sin\left(\frac{\pi}{2048}x\right) \tag{4.7}$$

where x goes from 0 to 1023 ( $2^{M-2}-1$ ). Numbers from 0 to 2047 takes 11 bits to represent, while 12 bits is needed when representing numbers from 2048 to 4095. This means that we can save 1 bit of space for each LUT entry. Figure 4.13, graph 1, shows the stored quarter sine wave and the full period sine wave that we want. Since we store the amplitude from 0 to 2047, we have to add the DC offset of 2048 to the amplitude for the first and second quadrant to get the correct wave form. This is done by the last complementor (in figure 4.10). Graph 2 shows the full rectified sine wave we get from the sine LUT. In graph 3, the third and fourth quadrant has been inverted and in graph 4 the DC offset has been added to the first and second quadrant. With this last storage reduction the sine LUT will use  $2^{M-2} \times (K-1)$  bits, and with M=K=12 we get  $2^{10} \times 11=11264$  bits.

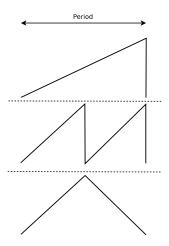

For the sawtooth wave we just truncate the PA value and use it as output from the PAC. The triangle wave is also quite easy to make since it's

Figure 4.14: Making a triangle wave from a sawtooth wave by frequency doubling and inverting the second sawtooth.

basically a sawtooth wave with double frequency and an inverted second sawtooth. This is illustrated in figure 4.14.

For the square wave, the amplitude depends on the value of the MSB as this indicates half a period. Equation 4.8 shows this.

$$A_{Square} = \begin{cases} 2^M - 1 & \text{if MSB} = 1\\ 0 & \text{if MSB} = 0 \end{cases}$$

(4.8)

Up till now we have assumed that the waveforms have a fixed peak-to-peak amplitude of  $2^M - 1$ . To change the amplitude of the sine wave we just shift the output value of the PAC n bits to the right. This is equivalent to dividing the value by  $2^n$  and it's the easiest way to change the amplitude since the values in the sine LUT are set to the highest possible amplitude and there is no division unit on the FPGA. There are of course downsides with this method. First of all, we get very coarse amplitude levels since we are halving the amplitude for each shift to the right. Secondly, we loose accuracy since we are doing division of integers. The quotient will be an integer only if the dividend is greater or equal to the divisor and if it is even.

Changing the amplitude of the square wave is just as easy. We just need to output the desired amplitude a when MSB equals 1, instead of  $2^M - 1$  as is done in equation 4.8.

For the sawtooth and triangle waves, it is a little bit different. Here we use the truncated PA value directly as output (amplitude) from the PAC. So to get the correct amplitude we have to substitute  $2^N$  in equation 4.3 and 4.4 with the desired amplitude a+1. For the triangle wave and sawtooth wave, we have to make sure that the offset is less than or equal to the amplitude. If not we will get an incorrect waveform since PA-value will overflow all the time. This check is done in software by the host computer. Note that this limitation does not apply to the square wave or the sine wave, since they map the PA value to amplitude and don't use the value directly as amplitude.

For more detail on how the NCO is implemented in VHDL, see figure B.3 in appendix B. This figure shows the finite state machine.

#### Channel Grouping

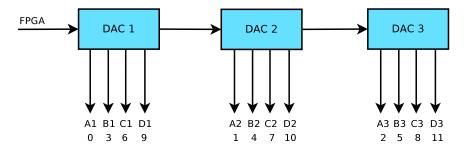

Since there are 12 DAC channel in total we have grouped them into 4 groups. Figure 4.15 shows the DAC channels and their identification. In table 4.2 we can see how the channels are grouped. The number of bits transferred for each group is

$$b = 3 \times 24 \times (g+1) \tag{4.9}$$

where g is the group number. So higher group number means lower  $f_{clk}$  which in turn means lower wave frequency  $(f_{out})$ . To always send data to all three DACs even though just one or two of them is in use may seem like a waste, but it is easier to implement. The maximum output frequency we get is high enough for our use, so that is not a problem.

To get the exact frequencies for each group we simulated the wave module design and counted how many FPGA clock cycles it took between each time the FPGA was ready to transfer a new set of samples. Using this information, equation 4.10 and  $f_{FPGA} = 50$  MHz we can calculate  $f_{clk}$  and maximum  $f_{out}$  (Nyquist frequency).

| Group | Channels                                       |

|-------|------------------------------------------------|

| 0     | A1, A2, A3                                     |

| 1     | A1, A2, A3, B1, B2, B3                         |

| 2     | A1, A2, A3, B1, B2, B3, C1, C2, C3             |

| 3     | A1, A2, A3, B1, B2, B3, C1, C2, C3, D1, D2, D3 |

Table 4.2: DAC channel grouping.

Figure 4.15: Overview of the channel identification numbers.

$$f_{clk} = \frac{1}{\frac{1}{f_{FPGA}} \times CC_{FPGA}} \tag{4.10}$$

The results is shown in table 4.3 and with channel group 0 we can output a waveform with a frequency of approximately 160 kHz which is the highest frequency, but wave frequencies over 70 kHz will probably look very distorted.

| Group | $CC_{FPGA}$ | $ m f_{clk}$      | Max f <sub>out</sub> |

|-------|-------------|-------------------|----------------------|

| 0     | 154         | 324675, 3247 Hz   | 162337 Hz            |

| 1     | 302         | 165562, 9139 Hz   | 82781 Hz             |

| 2     | 450         | 1111111, 11111 Hz | 55555 Hz             |

| 3     | 598         | 83612,04013 Hz    | 41806 Hz             |

Table 4.3: DAC channel group sample frequencies.

#### 4.2.5 Wave Control

The wave control in figure 4.9 has three tasks to do. The first is to enable the whole wave module. When the user module wants to enable the wave module it talks to the wave control which in turn forwards the enable signal to the rest of the modules inside the wave module. The second task is to store the wave group which is needed by the sample register to know how many channels it should send new samples to. The third task is to control the select line on the multiplexer (see figure 4.6). When the wave module is enabled, the multiplexer should select the signals coming from the wave module. Otherwise it should select the signals from the user module.

### 4.2.6 Sample Register

When the wave generators are ready with a new sample, the sample register reads the new samples and initiates a transfer to the DACs. While the sample register and DAC SPI controller are transferring data, the wave generators are calculating new sample values. The number of bits transferred depends on the selected channel group and even though not all channels may be in use, the wave generators corresponding to unused channels will still calculate new samples, but the sample register just don't transfer these samples to the DACs. To make sure that the DAC channels updates at the same time (but asynchronously), the sample register instructs the SPI DAC controller to pulse  $\overline{\text{LDAC}}$ , as described in section 4.1. Figure B.4 in appendix B shows the FSM of the sample register.

## 4.2.7 User Module Changes

To be able to use the new modules, we expanded the FSM of the user module. The new commands are shown in table 4.4. Except for the three

| Command      | Description                     |  |

|--------------|---------------------------------|--|

| Write 1      | Write to DAC 1.                 |  |

| Write 2      | Write to DAC 1 and 2.           |  |

| Write 3      | Write to DAC 1, 2 and 3.        |  |

| Read         | Read ADC voltage.               |  |

| DCen         | Enable daisy-chain              |  |

| Reset        | Reset DACs.                     |  |

| Enable wave  | Enable the wave module.         |  |

| Disable wave | Disable the wave module.        |  |

| Wave conf    | Write wave configuration to the |  |

|              | corresponding wave generator.   |  |

| Wave group   | Write wave group to the wave    |  |

|              | controller.                     |  |

Table 4.4: New user module commands.

write commands, there are a one-to-one correspondence between the user module commands and the commands/functions in the microcontroller and libEMB software.

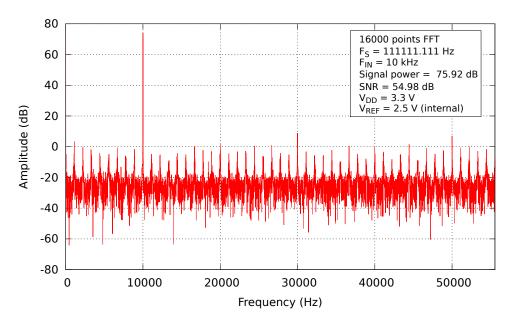

When one of the write commands are executed, the FSM will first read the DAC data to transfer, from the shared memory. Then it enables the DAC SPI controller and waits until the transferring is finished, before it clears the command register and returns to idle state. The DCen and reset commands will immediately enable the DAC SPI controller and execute the corresponding command. All four wave commands are similar to the write commands, except that the enable and disable wave commands does not involve reading from shared memory first. Also, none of the wave commands involves external communication. The read command will read the ADC data bits from memory in addition to the number of samples. Then it will repeatedly enable the ADC SPI controller and write the response to memory, until it has the number of sample we want. With an ADC serial clock frequency of 2 MHz and the current FSM, we get a sample frequency of 111111.111 Hz.

## 4.3 Microcontroller

The microcontroller software has been extended to be able to use the new FPGA commands. Since there is a one-to-one correspondence between the microcontroller functions and the libEMB functions, we will not explain the functions here, but instead explain other microcontroller changes and extensions. Section 4.4 will address the software changes.

#### 4.3.1 Address Room

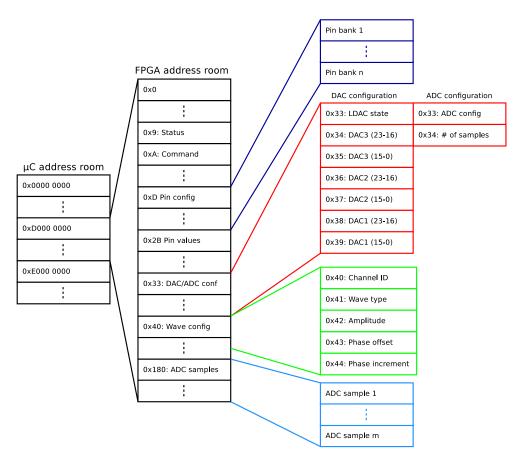

The original FPGA address space had  $2^{12} = 4096$  addresses. Since we want to be able to get a lot of samples from the ADC, we expanded the address space by two bits. This gives us  $2^{14} = 16384$ , where the first 384 addresses are reserved for command and configuration data and the last 16000 addresses are for ADC samples. The organization of the address space is shown in figure 4.16.

## 4.3.2 Busy Line to Microcontroller

When we want the ADC to convert the analog voltage on one of its channels, we have to have some way of knowing when the ADC and the FPGA are finished executing the command so that we can read back the voltage samples from memory. The time it takes may vary depending on how many samples we want. In the original Mecobo design there is no easy

Figure 4.16: Microcontroller and FPGA address rooms

way to signal the microcontroller that the FPGA is finished. We could for example let the FPGA write to a specific memory address and let the microcontroller read this memory address to see if the FPGA is finished, but the problem is that the shared memory controller gives priority to the microcontroller. This means that we cannot let the microcontroller poll the memory repeatedly as this would limit and in worst case stop the FPGA from accessing the memory (writing samples), depending on the clock frequency of the microcontroller and the FPGA. Adding a delay in the polling loop or just let the microcontroller wait some amount of time until we are certain that the FPGA is finished could work, but it is not a good solution. So what we did was to take the RS232 transmit pin on the FPGA and connect it to pin 0 on the microcontroller's PB header (PBH0). This works now as a busy line that signals when the FPGA is busy executing a command. Since neither the RS232 pin nor the PB header were in use, it causes no problem to use these pins for this purpose. The microcon-

troller can now poll this busy line as much as it wants without interrupting the FPGA's memory accesses.

#### 4.4 libEMB

To use the new functionality, we had to extend the libEMB software library. The new functions are listed in table 4.5. The first function is for reading the voltage level on one of the ADC channels. The number of samples can be between 1 and 16000. During testing we discovered some problems that causes the read\_voltage function to hang. The problem seems to depend on the number of samples and it may be related to the USB communication between the microcontroller and the host computer, since the debug communication (RS232) between the microcontroller and the host computer tells us that the FPGA has finished executing and the microcontroller reaches the point where it starts to send back data to the host computer. When it happens we have to use the reset-button on Mecobo. To avoid this problem altogether, it is best to set the number of samples to 16000 since we know that this works.

The read\_voltage function also has two arguments called ref and pm. The first one is used to enable (ref = 0) and disable (ref = 1) the internal reference. When using an external reference voltage, the internal reference should be disabled to obtain best performance [adc]. The second argument is used for power management. There are four different power modes and these are called normal operation, full shutdown, autoshutdown and autostandby. Every time a conversion is completed, the ADC enters the specified power mode and waits for the next command. The shutdown and standby modes needs some time to wake up and this is not taken into account when it comes to the FPGA implementation of the ADC SPI controller. Therefore, one should use the normal operation mode (pm = 0) to make sure that the system behaves correctly. The energy consumption of the prototype system is not our first concern so it should not be a problem that the ADC cannot enter power saving modes. An example of how to use the read\_voltage function is shown in listing 4.1.

Listing 4.1: Read voltage example

```

#include "emb.h"

void get_voltage(void)

{

```

| Function           | Arguments           | Description                                            |

|--------------------|---------------------|--------------------------------------------------------|

| read_voltage       | uint16_t channel    | Gets samples from                                      |

|                    | uint16_t samples    | ADC channel channel.                                   |

|                    | uint16_t * buf      | Stores them in buf. ref                                |

|                    | uint8_t ref         | turns on or off the internal                           |

|                    | uint8_t pm          | reference while $pm$ is the                            |

|                    |                     | power management.                                      |

| write_dac          | dac_config_t * conf | Write conf to the DACs and                             |

|                    | uint16_t ldac       | use the LDAC-state $ldac$ .                            |

| enable_daisy_chain | void                | Enable DAC daisy-                                      |

|                    |                     | chaining.                                              |

| reset_dac          | void                | Reset all DACs.                                        |

| enable_wave        | void                | Enable the wave module.                                |

| disable_wave       | void                | Disable the wave module.                               |

| set_wave_config    | uint16_t channel_id | Configure wave channel                                 |

|                    | uint16_t wave_type  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |

|                    | uint16_t amplitude  | amplitude, offset and freq.                            |

|                    | uint16_t offset     | channel_group is used                                  |