## A Comparative Analysis of Shared Cache Management Techniques for Chip Multiprocessors

Christian Vik Grøvdal

Master of Science in Computer Science Submission date: June 2013 Supervisor: Magnus Jahre, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# **Problem description**

Chip Multiprocessors (CMPs) or multi-core architectures are becoming increasingly popular, both in industry and academia. CMPs often share on-chip cache space between cores. When the CMP is used to run multiprogrammed workloads, different processes compete for cache space. Severe competition can lead to considerable performance degradation.

In recent years, a large number of shared cache management schemes have been proposed to alleviate this problem. The main aim of this project is shed some light on the relative strengths and weaknesses of the different cache management techniques.

The project must contain a review of recently proposed cache management techniques and identify similarities and differences. The student should also investigate how different memory system design choices impact performance and throughput with the SPEC2006 benchmarks and the gem5 simulator. The student should implement at least one cache management technique and compare its performance to a conventional LRU-managed cache and a statically partitioned cache. Additional cache management techniques should be implemented and evaluated if time permits.

#### Abstract

In this thesis we present a comparative analysis of shared cache management techniques for chip multiprocessors. When sharing an unmanaged cache between multiple cores, destructive interference can reduce the performance of the system as the cores compete over limited cache space. This situation is made worse by streamlike applications that exhibit low locality of reference but has high cache demands. Several schemes for dynamically adjusting cache space available to each core has been suggested, and in this work we evaluate 3 such schemes as well as static partitioning and conventional LRU.

We deploy a well defined simulation methodology to analyze the performance of the cache management techniques. The gem5 simulator is used to simulate the ARM ISA, and the SPEC2006 benchmark suite is used to create multi-programmed work-loads. The simulator has been extended to support cache management schemes and provide detailed simulation statistics. We implement UCP, PIPP, PriSM and static partitioning, and simulate dual core, quad core and 8 core workloads.

Our results show that destructive interference is a real issue in many workloads. Static partitioning can work well in scenarios where applications have similar cache demands, by creating private areas in the cache for each core. UCP improves on static partitioning by dynamically adjusting the size of each partition during runtime. PIPP performs decently by trying to maintain a specific cache occupation for each core without strictly enforcing a partition, but does not quite achieve the desired occupation and thus its performance suffers. PriSM fails to perform well, as its effort to determine a target cache allocation and maintain it does not work successfully for our workloads.

#### Sammendrag

I denne oppgaven presenterer vi en analyse av teknikker for å håndtere delt hurtigminne (cache) i flerkjerne prosessorer. Når man deler et hurtigminne mellom flere kjerner kan destruktiv interferens redusere ytelsen til systemet fordi flere prosesser konkurrerer om begrenset minneplass. Strømmende applikasjoner som har lav referanselokalitet men samtidig høyt hurtigminnebruk gjør dette problemet enda større. Det har blitt foreslått flere teknikker for å dynamisk justere hvor mye hurtigminne hver kjerne skal få, og i denne oppgaven har vi evaluert 3 slike teknikker opp mot konvensjonell LRU og statisk partisjonering.

Vi bruker en veldefinert simulasjonsmetodologi for å analysere ytelsen for hver av teknikkene. Vi bruker gem5 simulatoren til å simulere en ARM ISA, og SPEC2006 benchmark suite til å skape applikasjonsgrupper (workloads) som bruker flere kjerner. Simulatoren har blitt utvidet til å støtte håndteringsteknikker for hurtigminne, og presentere detaljert informasjon fra hver simulering. Vi implementerer UCP, PIPP, PriSM og statisk partisjonering, og simulerer 2, 4 og 8-kjerners arkitekturer med hver av disse teknikkene.

Våre resultater viser at destruktiv interferens er et reelt problem for mange applikasjonsgrupper. Statisk partisjonering kan fungere bra i tilfeller hvor applikasjonene har like store krav til hurtigminne, ved å skape private områder i hurtigminnet for hver kjerne. UCP forbedrer ytelsen til statisk partisjonering ved å dynamisk justere størrelsen til hver partisjon under kjøring. PIPP får grei ytelse, ved å prøve å beholde en gitt hurtigminnefordeling uten å strengt partisjonere hurtigminnet mellom hver kjerne, men klarer ikke helt å nå den riktige fordelingen og taper dermed litt ytelse. PriSM har dårlig ytelse, i stor grad fordi dens forsøk på å beregne en optimal hurtigminnefordeling og opprettholde denne ikke fungerer for våre applikasjonsgrupper.

# Acknowledgements

I would personally like to thank my advisor Magnus Jahre for excellent help and guidance with this thesis [11] .

I would also like thank the Department of Computer and Information Science (IDI) at the Norwegian University of Science and Technology (NTNU) for their help, and for providing resources used in this work.

Finally I would like to thank The Norwegian Metacenter for Computational Science (NOTUR) for providing the computational resources used, granting access to the supercomputer Stallo and 150,000 CPU hours [2]. The work has been performed under the project number NN4650K .

Christian Vik Grøvdal June 2013

# Contents

|          | Non  | nenclatu | ure                                                                                                                        |

|----------|------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 1        | Intr | oducti   | on 8                                                                                                                       |

|          | 1.1  | Chip I   | Multiprocessors (CMPs)                                                                                                     |

|          | 1.2  | CMP      | Memory Systems                                                                                                             |

|          | 1.3  | Resear   | ch questions $\ldots \ldots 11$ |

|          | 1.4  | Contri   | butions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $12$                                                                  |

|          | 1.5  | Outlin   | e                                                                                                                          |

| <b>2</b> | Bac  | kgrour   | nd 14                                                                                                                      |

|          | 2.1  | Cache    | 5                                                                                                                          |

|          | 2.2  | Cache    | Management Techniques                                                                                                      |

|          |      | 2.2.1    | Unmanaged caches                                                                                                           |

|          |      | 2.2.2    | Managed caches                                                                                                             |

|          |      | 2.2.3    | Shadow Tag Store 18                                                                                                        |

|          |      |          | 2.2.3.1 Auxiliary Tag Directories                                                                                          |

|          |      |          | 2.2.3.2 Recency hit counters $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 19$                                         |

|          |      |          | 2.2.3.3 Dynamic Set Sampling (DSS)                                                                                         |

|          |      | 2.2.4    | UCP: Utility based cache partitioning 21                                                                                   |

|          |      | 2.2.5    | PIPP: Promotion/Insertion Pseudo-Partitioning of Multi-Core         Shared Caches                                          |

|          |      | 2.2.6    | PriSM: Probabilistic Shared Cache Management 26                                                                            |

|          |      | 2.2.7    | Vantage                                                                                                                    |

| 3 | Mo  | deling | a CMP                                                       | 29 |

|---|-----|--------|-------------------------------------------------------------|----|

|   | 3.1 | ISA a  | nd multicore architecture                                   | 29 |

|   | 3.2 | Cache  | e and cache latency                                         | 30 |

|   | 3.3 | Main   | memory                                                      | 32 |

|   | 3.4 | Hardv  | vare and computational overhead of cache management schemes | 33 |

|   |     | 3.4.1  | Maintaining a partitioned cache                             | 33 |

|   |     | 3.4.2  | Allocation algorithms                                       | 34 |

|   |     | 3.4.3  | Enforcement algorithms                                      | 34 |

| 4 | Met | thodol | ogy                                                         | 36 |

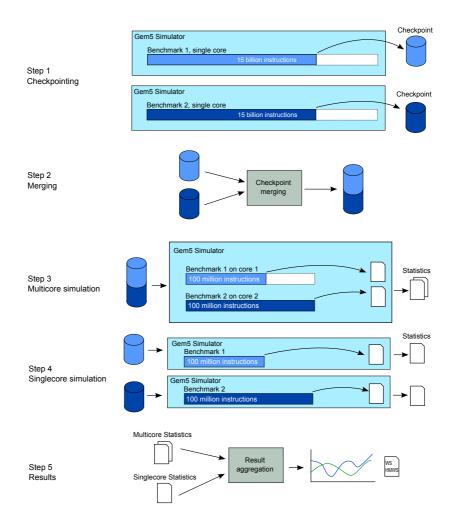

|   | 4.1 | Simul  | ation methodology                                           | 36 |

|   |     | 4.1.1  | Simulator                                                   | 36 |

|   |     | 4.1.2  | Single core checkpointing                                   | 36 |

|   |     | 4.1.3  | Multi core simulation                                       | 37 |

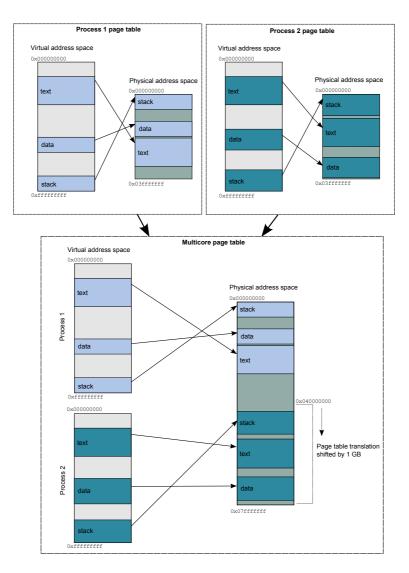

|   |     | 4.1.4  | Checkpoint merging details                                  | 38 |

|   |     | 4.1.5  | Computing resources                                         | 38 |

|   | 4.2 | Perfor | mance metrics                                               | 40 |

|   |     | 4.2.1  | Single core                                                 | 41 |

|   |     | 4.2.2  | Multicore                                                   | 41 |

|   | 4.3 | Bench  | ımarks                                                      | 42 |

|   |     | 4.3.1  | SPEC2006 benchmark suite                                    | 42 |

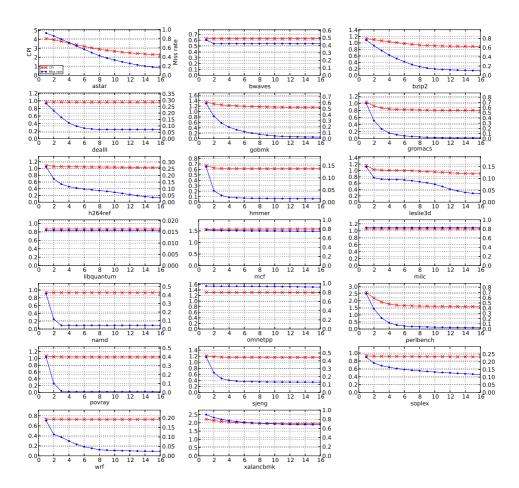

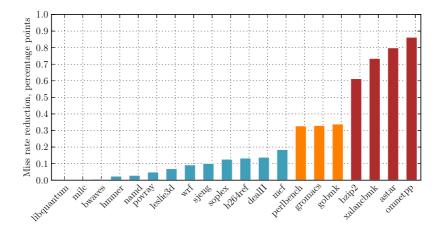

|   |     | 4.3.2  | Benchmark profiling                                         | 44 |

|   | 4.4 | Workl  | loads                                                       | 48 |

|   |     | 4.4.1  | Dual core workloads                                         | 48 |

|   |     | 4.4.2  | Quad core workloads                                         | 48 |

|   |     | 4.4.3  | 8 core workloads                                            | 49 |

|   | 4.5 | Imple  | mentation of cache management schemes                       | 49 |

|   |     | 4.5.1  | Overview                                                    | 49 |

|   |     | 4.5.2  | Shadow Tag Store                                            | 49 |

|   |     | 4.5.3  | UCP                                                         | 50 |

|   |     | 4.5.4  | PIPP                                                        | 50 |

|   |     | 4.5.5  | PriSM                                                       | 50 |

| <b>5</b> | $\mathbf{Res}$ | $\mathbf{ults}$ |                                                                                   | 52 |

|----------|----------------|-----------------|-----------------------------------------------------------------------------------|----|

|          | 5.1            | Introdu         | uction                                                                            | 52 |

|          | 5.2            | Dual co         | ore                                                                               | 53 |

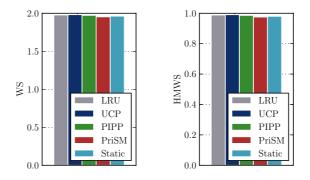

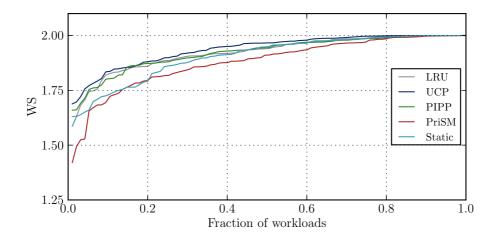

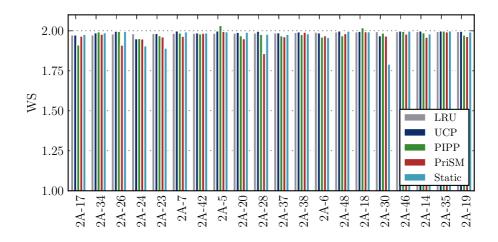

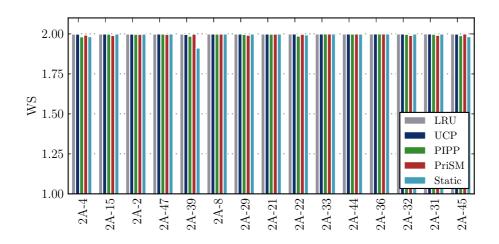

|          |                | 5.2.1           | Performance overview                                                              | 53 |

|          |                | 5.2.2           | UCP performance analysis                                                          | 55 |

|          |                |                 | 5.2.2.1 Case Study: Workload 2H-32                                                | 56 |

|          |                | 5.2.3           | PIPP performance analysis $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$      | 59 |

|          |                |                 | 5.2.3.1 Case Study: $2H-45 \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 60 |

|          |                | 5.2.4           | PriSM performance analysis                                                        | 62 |

|          |                |                 | 5.2.4.1 Case Study: Workload 2A-40                                                | 62 |

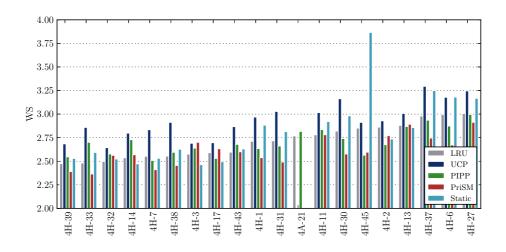

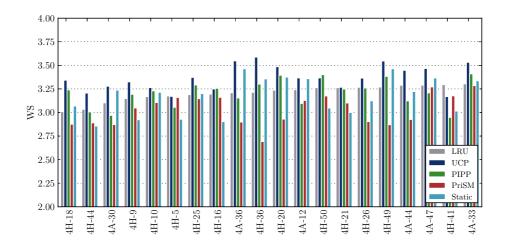

|          | 5.3            | Quad o          | core                                                                              | 65 |

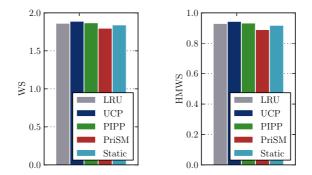

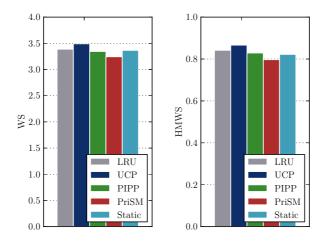

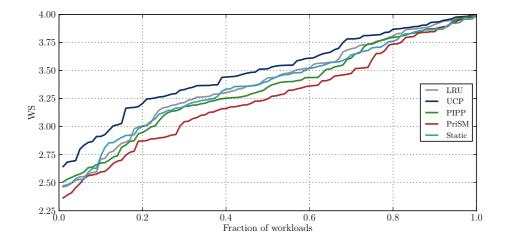

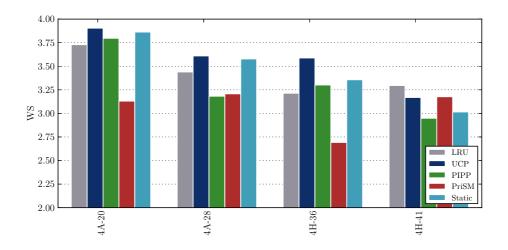

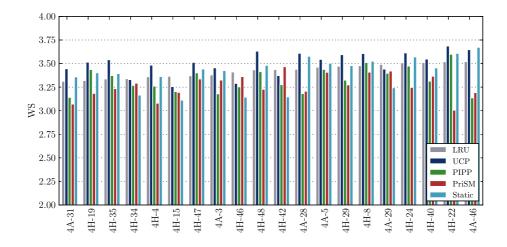

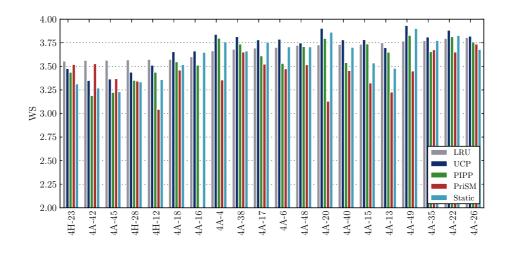

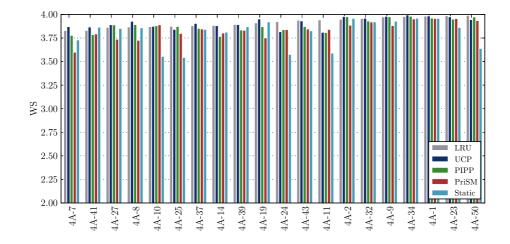

|          |                | 5.3.1           | Performance overview                                                              | 65 |

|          |                | 5.3.2           | UCP performance analysis                                                          | 67 |

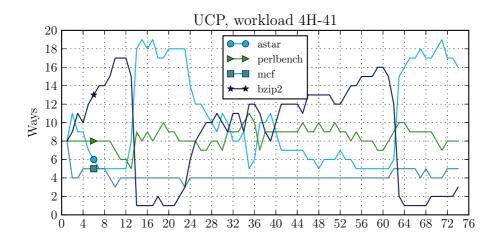

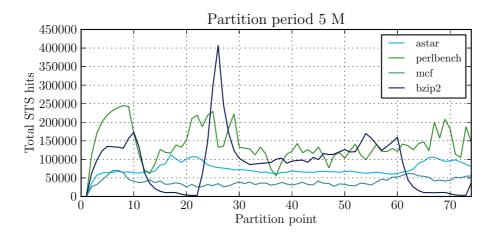

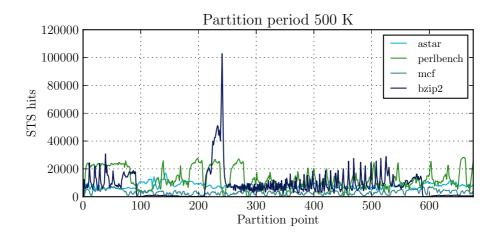

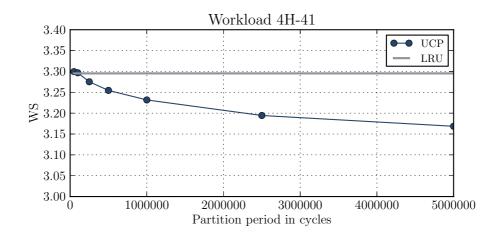

|          |                |                 | 5.3.2.1 Case study: Workload 4H-41 $\ldots$                                       | 67 |

|          |                | 5.3.3           | PIPP performance analysis $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$      | 70 |

|          |                |                 | 5.3.3.1 Case study: Workload 4A-28 $\ldots$                                       | 71 |

|          |                | 5.3.4           | PriSM performance analysis                                                        | 72 |

|          |                |                 | 5.3.4.1 Case Study: Workload 4H-36                                                | 72 |

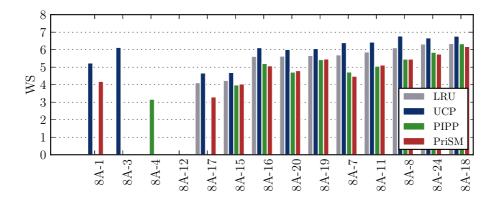

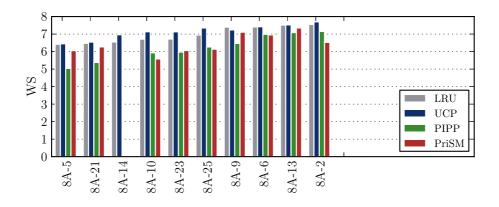

|          | 5.4            | 8 core          |                                                                                   | 75 |

|          |                | 5.4.1           | Performance overview                                                              | 75 |

| 6        | Dise           | cussion         |                                                                                   | 77 |

|          | 6.1            | Selection       | ng benchmarks and workloads                                                       | 77 |

|          | 6.2            | Limitir         | ng simulation to 8 cores                                                          | 78 |

|          | 6.3            | Perform         | nance of UCP                                                                      | 78 |

|          | 6.4            | Perform         | mance of PIPP                                                                     | 79 |

|          | 6.5            | Perform         | mance of PriSM                                                                    | 79 |

| 7        | Con            | clusion         | 1                                                                                 | 81 |

|          | 7.1            | Conclu          | sion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$      | 81 |

|          | 7.2            | Future          | work                                                                              | 82 |

| Α | Wor | kloads          | 85  |

|---|-----|-----------------|-----|

|   | A.1 | Dual core       | 85  |

|   | A.2 | Quad core       | 89  |

|   | A.3 | 8 core          | 92  |

| в | Sim | ulation results | 95  |

|   | B.1 | Dual Core       | 95  |

|   | B.2 | Quad Core       | 98  |

|   | B.3 | 8 Core          | 101 |

# Nomenclature

- **Application** a single threaded program running on a single core. The word application is used interchangeably with program and benchmark, describing the code running on the core.

- **ATD** Auxiliary Tag Directory. An extra tag store for each core in each set, which contains the tags of the data that would have been in the cache if the core had the entire cache to itself.

- **Benchmark** Synonym for application, but specifically referring to applications from the SPEC2006 benchmark suite.

- **CMP** Chip Multiprocessor. A single-chip processor with multiple processing cores, capable of simulataneous execution of several threads or processes.

- **Core** A single processing unit in a CMP, capable of running a single thread or process at a time.

- **CPU** A single processing core in a CMP, equivalent to a core.

- **DSS** Dynamic Set Sampling. A method to reduce storage overhead in Shadow Tag Stores (STS), by placing ATDs in a subset of the sets. This approximates cache usage by assuming some uniformity of the cache accesses across sets.

- LRU Least Recently Used. Refers to either A) A cache replacement policy,B) The least recently used block, equivalent to the lowest position on the stack.

- MRU Most Recently Used, refers to the last used block in a conventional LRU cache, or the highest priority position block in PIPP.

- **PIPP** Promotion/Insertion Pseudo-Partitioning. A shared cache management scheme used in this work.

- **PriSM** Probabilistic Shared Cache Management. A shared cache management scheme used in this work.

| STS      | Shadow Tag Store. A monitoring component used to gather informa-<br>tion about each cores use of a shared cache. Contains Auxillary Tag<br>Directories and recency counters. |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UCP      | Utility-based Cache Partitioning. A cache partitioning scheme used in this work.                                                                                             |

| UMON     | Utility Monitor. Equivalent to Shadow Tag Store (STS).                                                                                                                       |

| Wanklaad | A set of herebrashing acquirement in size to the number of cores on the                                                                                                      |

**Workload** A set of benchmarks, equivalent in size to the number of cores on the CMP. A workload defines what is run on each core.

## Chapter 1

# Introduction

This work aims to shed some light on the strength and weaknesses of proposed cache management techniques for chip multiprocessors. In particular we look at frequently cited cache partitioning schemes that claim to improve performance over the common LRU cache. In this Chapter we present the motivation behind this work, discussing the Chip Multiprocessor and the memory system. We introduce our research questions and list the contributions of this work, and outline the rest of the thesis.

### 1.1 Chip Multiprocessors (CMPs)

Chip Multiprocessors (CMPs) has become the norm for modern computing, leaving behind the single core era of the early 2000's and before. Up to the mid 2000's the improvement in performance mostly came as an effect of increased clock speeds made possible with shrinking transistor sizes. Eventually increasing clock speed further caused significant problems with heat and energy consumption, and hardware designers met the power wall, preventing further improvements using this technique. But as just as continued improvements following Moore's Law looked less likely, the focus shifted to adding multiple cores per processor [4]. This kept the aggregated performance and transistor counts increasing at a rate similar to what Moore's Law predicts. In 2013, quad cores are common (like Intels i7 series [6]), and the core count appears to be increasing. The introduction of multicore computing led to many new challenges in hardware architecture, amongst them how to perform cache management.

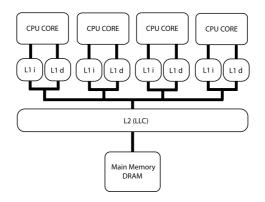

By CMP, we mean a single chip with several processing cores on it (Figure 1.1). It is also commonly known as a multicore processor, although CMP is a more precise term, indicating that the whole processor is located on a single chip. Having several processing cores allows it to run multiple programs or threads concurrently, increasing the amount of work that can be done per unit of time. A single process can be separated into several threads to provide simultaneous execution, or independent processes can share the cores between them.

Figure 1.1: An illustration of a Chip Multiprocessor with private and shared caches.

#### 1.2 CMP Memory Systems

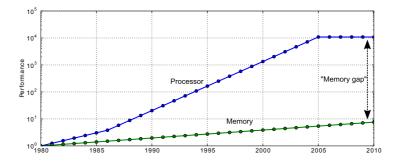

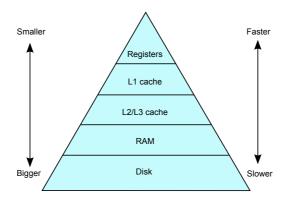

Caches are vital to todays high performance in CPUs. Processing power has increased at a much higher rate than memory speeds, and this has led to a performance difference called the memory gap [12]. Figure 1.2 shows the historic difference between processor and memory performance. The memory gap has been the cause of much research for a long time, as many techniques have been tried to help bridge the difference. One of the most important techniques to mitigate the memory gap is the memory hierarchy. Figure 1.3 shows the basic form of a memory hierarchy, where smaller and faster memories are placed closer to the CPU while larger and slower memories are used further down. The higher up the chain the data can be found, the lower the access time will be. After registers, caches are the fastest type of memory available, and deciding what data to place in the cache is crucial to the systems total performance.

When multiple applications in a CMP try to use the same cache resource simultaneously, they can have adverse effects on each others performance. Certain applications can take up large amounts of space in the cache without using it efficiently, whereas others may only require a few kilobytes but can have frequent accesses to it. The typical replacement policy is Least Recently Used (LRU), but this policy provides no isolation between applications. One application can cause the eviction of another applications cache lines, reducing the reuse of data stored in the cache. This is called destructive interference, and is the principal motivator behind the push for more utilization-aware shared caches.

Figure 1.2: The memory gap. Graph based on data from [12].

Figure 1.3: The memory hierarchy. A general memory hierarchy is shown, many more levels can be identified depending on the architecture.

In this work we will focus on the efforts of optimizing performance for shared caches in a CMP, in particular by preventing destructive interference between applications. We will look at selected cache management schemes for CMPs, that propose various forms of cache partitioning. Some schemes use strict isolation like UCP [18] or static partitioning, while others use probability distributions (PriSM [16]) or promotion/insertion strategies (PIPP [23]) to achieve their goals. These different strategies have varying strengths and weaknesses, improving or reducing performance depending on the workload. All the schemes except static partitioning depend on extra monitoring circuitry, that monitors the cache utilization and gives input to partitioning algorithms. We will also briefly evaluate the overhead of these circuits, making sure that a hardware implementation of the suggested scheme is feasible.

### 1.3 Research questions

The main research question that motivates this work is:

How can performance be improved when sharing a cache between multiple applications in a CMP?

This is a very broad question, spanning several aspects of computer architecture and design. In our work we focus on cache management schemes and how they impact the performance of a system. We are interested in evaluating the strengths and weaknesses of these schemes, and to see under what conditions they perform well or poorly. We will use simulation results to draw conclusions regarding each schemes performance and evaluate its usefulness. In particular, we are trying to answer the following questions:

- How much does LRU performance degrade when using multicore workloads, due to interference between the cores?

- What performance do the proposed schemes have in comparison to LRU and static partitioning?

- What are the limitations of each cache partitioning scheme, and how much impact does this have on its usefulness?

- What limitations are there in the simulation methodology, and can these skew the results in favor of any of the schemes?

### 1.4 Contributions

The main contributions of this work are:

- A comparison of several cache management schemes performance

- Several case studies to provide deeper understanding of each schemes strengths and weaknesses

- Multiple extensions to the gem5 simulator that enable shared cache management schemes and auxiliary functions

- A framework to perform multicore experiments on a distributed supercomputer

This thesis tries to take an impartial look at shared cache management schemes. Authors proposing new cache management schemes do include their own performance analysis, but these may not be directly comparable to other works. Usually the methodology differs significantly between each analysis, making comparisons unfair or impossible. Therefore it is useful to look at this topic in a unified sense, with the same methodology across the testing of all cache management schemes.

This thesis draws conclusions regarding the strengths and weaknesses of the individual cache schemes. We analyze outlier cases where performance is particularly good or poor for some of the schemes, to shed light on what makes the schemes respond differently. This supports the arguments presented about the cause of a schemes performance, and deepens the understanding of how each scheme works.

In addition, a framework for running multicore experiments using the gem5 simulator has been developed. The gem5 simulator has been extended to support CPUaware cache accesses, a prerequisite for all shared cache management techniques. The simulator has been extended with implementations of 4 cache partitioning schemes, and a general purpose Shadow Tag Store implementation. Additions to the simulator have been made to dump statistics multiple times during a single simulation.

We have developed tools for merging checkpoints from multiple applications to a combined checkpoint, allowing precise resuming of workloads with arbitrary combinations of applications. A framework for managing jobs on a supercomputer and triggering simulations have been created, based on previous work done at IDI, NTNU. Finally, multiple tools for aggregating data from a large number of experiments been developed, allowing rapid analysis of a massive amount of data. The framework and tools will be transferred to IDI, to serve as a starting point for future work.

### 1.5 Outline

The rest of this work is organized as follows: In Chapter 2 we present background information on caches, and some proposed cache management techniques. In Chapter 3 we talk about modeling the CMP and the details of our simulated architecture. Chapter 4 contains methodology, explaining our work with benchmarks and workloads, the simulation methodology, and how the results are produced. In Chapter 5 the results are presented, organized by number of cores. We also perform case studies of some workloads to show how the different cache schemes perform. A discussion of the results and our methods then follow in Chapter 6. We round off this work with a conclusion in Chapter 7, including a brief look at future work. Extra details about workloads and results are included in Appendix A and B.

## Chapter 2

# Background

In this chapter we will present some background information about caches and cache management schemes. We introduce a conventional LRU cache, and how this is used in an unmanaged way in shared caches. We then present methods of managing shared caches, using a variety of methods. Static partitioning, UCP, PIPP and PriSM are introduced as schemes we will perform experiments on, while Vantage is presented as a different scheme that we unfortunately did not include in our work.

### 2.1 Caches

This section describes a traditional cache structure, similar to an LRU cache. There are other cache structures that function differently, but they are less common and will be described where necessary.

Caches are used to store recently used data closer to the CPU so the data can be accessed faster than if they were located in main memory [12, 13]. To keep cache accesses fast, the caches need to be small. Larger caches have higher access latency, so the fastest caches have low capacity and are located close to the CPU. Although larger caches are slower, they have a greater probability of containing the data we are interested in. For this reason, caches are organized in hierarchies, named by their level, usually L1, L2 and sometimes L3. L1 is the first level cache, the fastest and closest to the CPU. If a piece of data is not found in the L1, the request goes to the L2 cache which is larger. Some systems also have another level of cache, the L3, which is even larger and slower. The Last Level Cache is referred to as LLC.

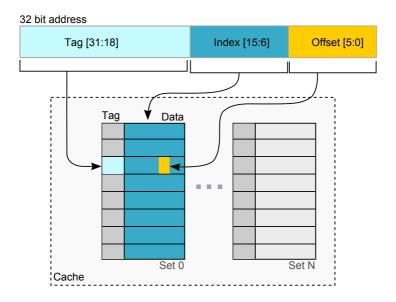

The mapping from an address to a cache location is illustrated in Figure 2.1. The storage available in a cache is split into a number of sets. Data with a given address can only reside in a single set, thereby limiting the number of places that needs to

Figure 2.1: Address mapping in caches. This cache has a block size of 64 bytes, 1024 sets and 8 way associativity.

be searched. The set is determined by the index bits of the address, so the number of index bits depend on the number of sets. Within a set, there are several cache ways, each of which contains one cache block of data. The number of cache ways per set is called the associativity of the cache, and tell us how many possible location a piece of data can be in. Each of these ways have to be searched for the correct tag, to determine if the data is present. A higher associativity allows us more flexibility of where to place data and what data to keep in the cache, but increases the access time since more searching is required. Finally, after determining the set and the way, the correct data is extracted from the cache block based on the offset bits in the address.

For caches with associativity larger than 1, in other words where we have more than one possible location for a block of data to be inserted, we require a replacement policy. This policy determines what block should be evicted to make room for the new data being requested if the set is already full. The most common policy is Least Recently Used (LRU). We visualize LRU as a stack, where the least recently used block is on the bottom, and the most recently used is on the top. In practice it is implemented using counters. The LRU policy always evicts the block in a set that is least recently used. When a block is accessed, it is moved to the top of the stack, moving the other blocks one step closer to the least recently used position. Other policies include Least Frequently Used (LFU) which takes the block with the lowest use frequency as the victim, and Pseudo-LRU which is cheaper to implement than true LRU but does not always select the least recently used as the eviction candidate.

| Cache Set Most recently used blog                                      | ck      |

|------------------------------------------------------------------------|---------|

| CPU 0 tag 0xAA                                                         |         |

| LRU block is CPU 1 tag 0x05                                            |         |

| evicted regardless CPU 0 tag 0xB2                                      |         |

| of owner CPU 0 tag 0xB6 New bloc                                       |         |

| CPU 1 tag 0x06 moved to                                                | MRU     |

| CPU 1 tag 0x0A                                                         |         |

| CPU 1 tag 0x02                                                         |         |

| Insert from CPU 0 $\rightarrow$ CPU 1 tag 0x01 $\rightarrow$ LRU block | evicted |

| Least recently used blo                                                | ck      |

#### LRU

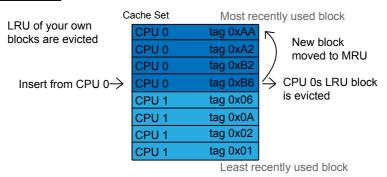

Figure 2.2: An unmanaged shared cache, with LRU as the eviction policy.

### 2.2 Cache Management Techniques

A vast number of cache management techniques for shared caches have been proposed. In this section we will provide a review of some recently proposed cache management techniques that are relevant for this work. Static partitioning, UCP, PIPP and PriSM are the management schemes evaluated later in this work. Vantage is introduced as additional background information.

#### 2.2.1 Unmanaged caches

The simplest management technique for shared caches is not to manage the cache at all. All cores can use the shared cache freely, just as it was their own cache. Cache accesses from the cores are serialized, and there is not control over how much of the cache each core can occupy. The core with the highest cache demand will occupy the largest portion of the cache, regardless of its ability to reuse any of the data. Figure 2.2 shows an unmanaged cache using LRU as the replacement policy.

The major problem with this approach lies in interference between the cores. When a core has a private cache, it can be fairly certain that a block will remain in the cache if the working set is small enough so it never gets evicted. In an unmanaged shared cache a core does not know how the other cores are using the cache. If their working sets are large, they could cause evictions of the first cores blocks. This would be detrimental to the first cores performance, and there is nothing it can do to limit this destructive interference.

However, there are benefits to unmanaged caches. They are significantly easier to implement since they require very few modifications from a standard private cache. There are also no extra overhead involved in cache management, neither in form of data gathering or enforcement methods to prevent interference. A single core can

#### Static way-partitioning

Figure 2.3: Static way-based partitioning.

also utilize the entire cache, without being limited by an allocation policy. All in all it is a more open approach, with fewer guarantees but more opportunities.

Whether it is beneficial to keep caches unmanaged is completely dependent on the workloads running on the system. As we will see later, certain types of workloads like those with rapidly changing characteristics or small working sets will achieve good performance with unmanaged caches, while applications with uneven cache needs may benefit from having stricter guarantees about the cache.

#### 2.2.2 Managed caches

Most CMP cache management schemes utilize cache partitioning in one way or another. Cache partitioning allocates areas of the cache to a specific process or core. The partitioning policies and implementations that decide the allocation and enforces it vary between the schemes suggested. Allocating areas to cores limits interference between the cores, and attempts to optimize the use of the available space.

One way of partitioning a cache is way-based partitioning, where each core is allocated a specific number of ways. The number of sets available to a core is then constant, but the associativity varies. The simplest way of doing way-based partitioning is by statically partitioning the cache as shown in Figure 2.3. A fixed number of ways is allocated to each core for the entire execution. This effectively creates a smaller private cache available for each core, but has no flexibility in rearranging the allocation based on utilization.

One can do better by changing the allocation of the ways during the execution. The cost of doing way-based partition individually for each set is usually prohibitive, so the common solution is to partition the ways globally. In other words, a core has the same number of ways available in all sets. The way that is allocated to a core

cannot be used by any other core. This is considered a coarse grained approach to cache partitioning. Since there are only small number of ways, the number of possible allocations is also low. And crucially, the number of cores must not exceed the number of ways, or else the cache will be unavailable to one or more of the cores. UCP [18] utilizes way-based partitioning.

To provide a finer grained partitioning, new techniques have been proposed that do not enforce a strict partitioning of the cache. The entirety of the cache is available to all cores, but the cache management scheme decides which fraction of the cache should be occupied by each core. It then tries to keep the occupancy close to the target allocation by using enforcement policies. PriSM [16] does this by choosing what block will be evicted based on an eviction probability for each core. By adjusting this eviction probability, the cache occupancy can be controlled without strictly enforcing an allocation. Similarly, PIPP[23] inserts blocks at lower priorities in the cache than the head, and uses a different promotion strategy to achieve the same goal.

Vantage [21] has been proposed as a shared cache management scheme, that uses a different sort of cache than the usual set/way based ones. ZCaches [20] is a cache design where extra associativity is achieved by increasing the potential number of eviction candidates past that which is possible with a standard type cache. It uses hashing to find potential candidates for eviction, and can chain a lookup to extend the associativity further. This makes Vantage a fine grained partitioning schemes that can provide strict partitioning of the cache.

#### 2.2.3 Shadow Tag Store

To decide on the target cache allocation, the management scheme needs information on how each core is utilizing the cache. By obtaining usage information from the cache, the allocation can be adjusted to meet specific performance criteria, such as minimizing the number of misses or maintaining fairness. The most common method of tracking cache usage is with a Shadow Tag Store [8].

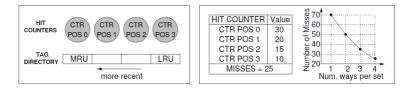

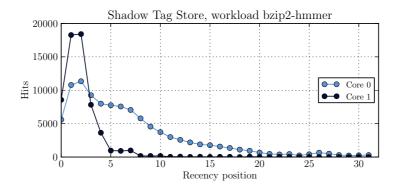

The Shadow Tag Store (STS)<sup>1</sup> is an extra monitoring circuit to maintain tag information and hit counters for shared caches. It is used in addition to the tags that identify the data in each set. Using the STS gives us useful information about the usage of the cache for each of the applications, by determining the number of hits in each recency position. There are two components to the STS; the Auxiliary Tag Directories (ATDs) and the recency hit counters. Depending on the desired accuracy of the cache monitoring, there may be one ATD and one set of recency hit counters for each set in the cache.

<sup>&</sup>lt;sup>1</sup>In UCP [18] terminology, the STS is called Utility Monitor (UMON). To stay consistent with other work, we refer to it as a Shadow Tag Store. We refer to a single tag store in one of the sets as an Auxiliary Tag Directory (ATD).

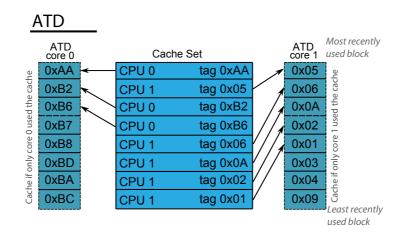

Figure 2.4: Two ATDs in a dual core system. Each ATD shows what the cache contents would have been if the core had the cache to itself.

#### 2.2.3.1 Auxiliary Tag Directories

The Auxiliary Tag Directory (ATD) is a LRU-managed list of the most recently accessed tags. It operates exactly as a private cache set, except it contains no data, only tags. When a new tag is used, the least recently used tag is removed and the new tag is inserted at the head of the stack. There is one ATD per core for each set of the cache. This is in contrast to the tag store of the data, of which there is only one per set. Having an ATD per core means we can determine what the contents of the cache would have been if the core had the entire cache by itself. Figure 2.4 shows a cache set and the corresponding ATD contents.

#### 2.2.3.2 Recency hit counters

A cache blocks recency position is its position in the LRU stack when a cache access causes a hit. A hit for the block in the most recently used position in the cache is a hit in the first recency position. And a hit for the block in the least recently used position is a hit in the last recency position. Consider a cache with only 1 set that is being accessed with the addresses 0xA, 0xB, 0xC, 0xA, 0xB, 0xC, 0xA... and so on, as shown in Figure 2.5. The first access to 0xA will insert it into the cache at the MRU position. The next access to 0xB will insert this to the MRU, pushing 0xA down to the second recency position. Inserting 0xC will bring 0xA down to the third recency position. The next access to 0xA will cause a hit, as we find 0xA in the third recency position.

A hit for 0xA causes the hit counter for the third recency position to be incremented. This tells us that this application requires 3 ways of cache to achieve a hit on this access. Notice how if this cache set only had 2 ways, 0xA would have

| Event      | Hit/miss | ATD content and hit counters |     |     |     | nters |     |

|------------|----------|------------------------------|-----|-----|-----|-------|-----|

| Access 0xA | miss     |                              | 0   | 0   | 0   | 0     | 0   |

|            |          |                              | 0xA |     |     |       |     |

| Access 0xB | miss     |                              | 0   | 0   | 0   | 0     | 0   |

|            |          |                              | 0xB | 0xA |     |       |     |

| Access 0xC | miss     | _                            | 0   | 0   | 0   | 0     | 0   |

|            |          |                              | 0xC | 0xB | 0xA |       |     |

| Access 0xA | hit      |                              | 0   | 0   | 1   | 0     | 0   |

|            |          |                              | 0xA | 0xC | 0xB |       |     |

| Access 0xB | hit      |                              | 0   | 0   | 2   | 0     | 0   |

|            |          |                              | 0xB | 0xA | 0xC |       |     |

|            |          | MR                           | U   |     |     |       | LRU |

|            |          |                              | ÷.  |     |     |       |     |

Figure 2.5: The content of the Shadow Tag Store and the hit counters. Notice that the hit counter is tied to the recency position, not the tag.

been evicted before it was accessed. The next access, 0xB, also hits in the third recency position, incrementing the counter to 2. In fact, this cyclic access pattern of 0xA, 0xB, 0xC, 0xA... will only cause hits in the third recency position. From this knowledge, the STS will know that there will be 0 hits unless this core gets at least 3 ways available to it.

#### 2.2.3.3 Dynamic Set Sampling (DSS)

Unfortunately, the storage overhead of keeping an ATD for each core per set makes an implementation of the naive Shadow Tag Store unfeasible. It would require significant amounts of data to store the tag information for so many ATDs. Doing this naively for a 16-way associative cache with a tag size of 40 bits and 16 bits of counter values would require (40 + 16) \* 16 = 896 bits for each core in a set. Using a common 64 bytes per line this set uses (40 + (64 \* 8)) \* 16 = 8232 bits for its data and tags. Each core would then add 11% on the storage requirements. For an 8 core system, half the storage necessary would be for ATDs, which is not feasible.

To avoid this issue, Dynamic Set Sampling (DSS) [17] is used. DSS is used to approximate cache utilization by sampling only a few of the sets in the cache. This reduces the storage overhead significantly, by allowing us to have ATDs in only a few of the cache sets. The accuracy of the estimate depends on the number of sets sampled and the uniformity of the accesses across sets. If each application accesses

UCP

Figure 2.6: Utility-based Cache Partitioning.

each set in the same pattern, a single set would be sufficient to determine the total utilization. But in practice, access patterns vary between sets, especially as the number of sets increase. UCP [18] samples 32 sets total. These are chosen by a simple static pattern, using an ATD on every N/32 cache set.

#### 2.2.4 UCP: Utility based cache partitioning

Utility Based Cache Partitioning[18] was proposed in 2006 by Moinuddin K. Qureshi and Yale N. Patt from the University of Texas at Austin. The original paper proposed solutions that have been used by later cache partitioning schemes, including the Utility Monitor (UMON) which is equivalent to the Shadow Tag Store [8].

The overall idea behind UCP is to partition the cache by ways. The number of ways allocated to each core depends on its cache utilization. The UMON circuits are used to monitor the utilization, and a partitioning algorithm allocates a number of ways to each core to minimize the number of cache misses. A way belongs exclusively to a core and cannot be evicted by any other core. This prevents interference between the cores that could lower the hit rate of the cache. The partitioning is illustrated in Figure 2.6.

The Shadow Tag Store tells the partitioning algorithm how many hits an application would have if it had N number of ways allocated to it, as illustrated in Figure 2.7. As the number of ways available is reduced, the number of misses increase. With multiple applications, there exists an optimal partitioning of ways between the applications, which minimizes the number of misses. This is equivalent to finding the partitioning that provides the maximum number of hits. Unfortunately, finding the optimal solution turns out to be NP-Hard [19]. The possible partitions increase with both the number of cores and number of ways, making it an exponential problem to evaluate them all. This exhaustive search, called EvalAll, is

Figure 2.7: Shadow Tag Store and hit counters. Any reduction in allocation will increase the number of misses according to the table. Illustration from [18].

```

Algoritme 2.1 Greedy Partitioning Algorithm, from [18]

```

```

balance = N # Num blocks to be allocated

allocations[i] = 0 for each competing application i

while(balance):

for i,a in enumerate(application): # get utility for next 1 block

alloc = allocations[i]

Unext[i] = get_util_value(i, alloc, alloc+1)

winner = application with maximum value of Unext

allocations[winner] += 1

balance -= 1

return allocations

def get_util_value(p, a, b):

U = change in misses for application p when the number

of blocks assigned to it increases from a to b

return U

```

unfeasible for anything but dual-core architectures, where it reduces to a trivial search.

The authors of UCP suggest two simpler partition algorithms that do no guarantee an optimal solution but have much better performance than EvalAll. A Greedy Algorithm (Algorithm 2.1) can be shown to be optimal if the utility curves of all UMONs are convex, in other words the number of hits for each cache way is decreasing for each step. The utility graph in Figure 2.7 is convex. If the utility curve is non-convex, the greedy algorithm will not give the correct partitioning. It will not consider the benefit of allocating one low-gain way in order to be able to allocate a high-gain way next, thereby not finding the optimal solution.

The second algorithm, called the Lookahead Algorithm (Algorithm 2.2), tries to improve on the Greedy Algorithm without adding too much computational complexity. It uses the notion of marginal utility (MU), defined as the difference in misses when it receives a and b ways, divided by the distance between a and b. This lets it look further ahead than the greedy algorithm. In our comparisons, the Lookahead Algorithm is used as the partitioning algorithm for UCP.

For each step of the Lookahead Algorithm, a number of ways are allocated to the application with the highest marginal utility. If the utility graph is convex we will

```

Algoritme 2.2 Lookahead Algorithm, from [18]

```

```

balance = N /* Num blocks to be allocated */

allocations[i] = 0 for each competing application i

while(balance):

foreach application i: /* get max marginal utility */

alloc = allocations[i]

max_mu[i] = get_max_mu(i, alloc, balance)

blocks_req[i] = min blocks to get max_mu[i] for i

winner = application with maximum value of max_mu

allocations[winner] += blocks_req[winner]

balance -= blocks_req[winner]

return allocations

def get_max_mu(p, alloc, balance):

max_mu = 0

for(ii=1; ii <= balance; ii++):</pre>

mu = get_mu_value(p, alloc, alloc+ii)

if( mu > max_mu ) max_mu = mu

return max_mu

def get_mu_value(p, a, b):

U = change in misses for application p when the number

of blocks assigned to it increases from a to b

return U/(b-a)

```

allocate 1 way at a time, reducing the lookahead algorithm to the greedy algorithm. Calculating the highest marginal utility can be done in parallel for each core, with complexity N each. In the worst case the main allocation part allocates only 1 way at a time, which gives a total time complexity of

$N + (N - 1) + (N - 2)... + 1 = N(N - 1)/2 \approx N^2/2.$

When evicting blocks from the cache, a check is made to see if this core fills its target allocation. If it is equal to or over its allocation, its least recently used block is selected for eviction. If it is below its target allocation, the least recently used block from one of the cores that exceed their quota is selected instead. The new block that is being inserted gets moved to MRU. This method prevents interference and makes the occupation always approach the allocation.

|                               | Cache Set | Most rece  | ntly used block       |

|-------------------------------|-----------|------------|-----------------------|

| Select LRU block for eviction | CPU 1     | tag 0xAA   |                       |

| then promote block            | CPU 1     | tag 0xA2   |                       |

| according to target           | CPU 0     | tag 0x02   | K                     |

| partition                     | CPU 0     | tag 0x04   |                       |

|                               | CPU 1     | tag 0xB6   | New block promoted    |

|                               | CPU 1     | tag 0xCA   | to insertion position |

|                               | CPU 1     | tag 0xA1   |                       |

| Insert from CPU 0 —           | > CPU 0   | tag 0x01   | ∕→LRU block evicted   |

|                               |           | Least rece | ently used block      |

|                               |           |            |                       |

| Target partitioning CP        | U 0 6     |            |                       |

###

Figure 2.8: Promotion/Insertion Pseudo-Partitioning.

2

CPU 1

(insertion position)

#### 2.2.5PIPP: Promotion/Insertion Pseudo-Partitioning of Multi-**Core Shared Caches**

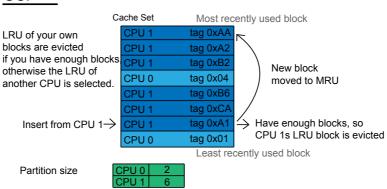

PIPP[23] was proposed in 2009 by Yuejian Xie and Gabriel H. Loh from Georgia Institute of Technology. In contrast to UCP that uses strict partitioning between the cores, PIPP implements an implicit partitioning by regulating where cache blocks are inserted in the LRU stack. Figure 2.8 shows how PIPP works for replacements.

When evicting blocks, PIPP works similar to LRU and evicts the least recently used block. However, the new block that is being inserted is not moved to the most recently used position in the LRU stack. Instead it inserts it according to the partition algorithm, as shown in Figure 2.9. The blocks of an application that is being allocated more of the cache will be inserted closer to the MRU. This means that it is less likely to be evicted soon, and thus increases this cores occupation of the cache. An application who gets a smaller allocation will have its blocks inserted closer to the LRU, and thus more likely to be evicted earlier. This leads to a pseudo-partitioning of the cache, where the occupancy of the cache regulates itself based on the insertions.

As the number of cores increase, the average partition size decreases. This causes the insertion positions to become closer to the least recently used position in the cache. Inserting close to LRU will in turn lead to quicker evictions, and is a known drawback with PIPP. Unless a new block is accessed very soon after insertion, it is highly likely that it will be quickly evicted.

On a cache hit, the block is promoted up the stack step-wise, not straight to the MRU position. At its basic form, this promotion is simply a shift 1 step towards

Figure 2.9: Insertion and promotion policy for PIPP. Figure from [23].

MRU. In addition to this, the block is only promoted with a specific probability  $p_{prom}$ . The probability can be tuned to adjust the rate of which blocks climb the stack, helping to maintain the target occupation.

PIPP relies on a Shadow Tag Store to determine the target partition sizes. The STS keeps track of each cores hit counters if it was allocated more or fewer ways. This information is then used as input to the partition algorithm to regulate insertions and promotions. The insertion position is set equivalent to the cache allocation. If a core is allocated 1 way, its blocks are inserted at the LRU position, and similarly if a core is allocated 5 ways, its blocks are inserted 5 steps above LRU.

PIPP also suggests a method for dealing with applications that exhibit low locality of reference, specifically those who have a stream-like behavior. If PIPP detects that an application would have more than  $m_i$  misses even with the whole cache available, it assumes the application is stream-like. This changes its insertion position for new blocks to  $\pi_{stream}$ , independent of its target partitioning. This  $\pi_{stream}$  is equal to the number of streaming applications, effectively inserting it very close to the LRU of the cache. In addition, promotion probability is reduced to  $p_{stream}$  which is significantly lower than  $p_{prom}$ . This combination tries to reduce the interference from streaming applications on applications that can utilize the cache better, by making it more likely that the streaming applications blocks are quickly evicted.

| PIISIVI                         |                      |             |                                            |

|---------------------------------|----------------------|-------------|--------------------------------------------|

| Ca                              | ache Set             | Most recer  | ntly used block                            |

| Randomly select CPU             | CPU 1                | tag 0xAA    | 5                                          |

| from eviction probability       | CPU 1                | tag 0xA2    |                                            |

| distribution, then evict        | CPU 1                | tag 0xB2    | New block                                  |

| its LRU block                   | CPU 0                | tag 0x04    | moved to MRU                               |

|                                 | CPU 1                | tag 0xB6    |                                            |

|                                 | CPU 1                | tag 0xCA    | /                                          |

| Insert from CPU 0 $\rightarrow$ | CPU 1                | tag 0xA1    | $\xrightarrow{/}$ CPU 1s LRU block evicted |

| CPU 1 selected                  | CPU 0                | tag 0x01    |                                            |

| for eviction                    |                      | Least recei | ntly used block                            |

| Eviction probability CP         | U 0 0.37<br>U 1 0.63 |             |                                            |

#### PriSM

Figure 2.10: Probabilistic Shared Cache Management.

#### 2.2.6 PriSM: Probabilistic Shared Cache Management

The article detailing PriSM[16] was published in 2012, by R. Manikantan, Kaushik Rajan and R. Govindarajan of the Indian Institute of Science, Bangalore, in cooperation with Microsoft Research India. It utilizes probabilities to maintain a cache occupation determined by a partitioning algorithm.

PriSM uses eviction probabilities to control the cache occupancy in each set. Each core has an eviction probability  $E_i$  such that  $\Sigma E_i = 1$ . When a miss occurs, this probability distribution is used to choose the victim block. First, a core is randomly selected according to the eviction distribution. A core may have an eviction probability of 0, which means it will never be selected for eviction unless all other options are out. After a core is selected, the LRU block of this core is chosen as the victim. If this core does not have any blocks in this set, the LRU block of any non-zero eviction probability core is selected. There is no change in hit policy from LRU, a hit causes the block to be moved to the most recently used position. The basics of PriSM is illustrated in Figure 2.10.

Adjusting the eviction probabilities is the job of the allocation policy. The authors of PriSM suggest three different policies depending on the desired functionality of the cache. The Hit Maximization policy does what the name suggests, it attempts to maximize the overall speed of the system by getting the highest number of cache hits. It will allocate more cache space to those cores than can best utilize it. PriSM uses a Shadow Tag Store without the recency hit counters to evaluate the cache utilization of the different cores. Instead of the recency counters it only stores the total hits per core in the ATD, a more coarse grained approach than PIPP and UCP uses.

The Fairness policy tries to equalize the slowdown between the cores when sharing a cache. If a core is slowed down more than the rest, this creates an unfairness even

though the total performance of the system might be better. To use this policy, PriSM requires access to the performance counters for CPI, instructions committed and cycles, in addition to the standard shadow tag information.

The final policy is Quality of Service, which tries to ensure a specified minimum level of performance for a given core. The authors use maximum slowdown in IPC as their target. This can be useful in situations with prioritized applications, for example applications that have specific timing needs.

PriSM changes the eviction probabilities at specific intervals, given in number of cache misses. Once the threshold has been passed, the allocation policy determines new eviction probabilities that will be used until the threshold is reached again.

#### 2.2.7 Vantage

Vantage[21] was proposed by Daniel Sanchez and Christos Kozyrakis from the Electrical Engineering Department at Stanford University in 2011. It breaks with the previous cache schemes we have seen, by using a different cache structure and allowing for a more fine grained partitioning and still having strict isolation between the cores.

Unlike LRU, UCP, PIPP and PriSM, Vantage uses a highly-associative cache type called ZCache [20]. It differs from ordinary caches in how it is organized. In an ordinary cache, the index bits of an address uniquely identifies the set, and then the associativity of that set determines the possible block candidates. ZCaches uses multiple hashing functions on the address to determine its possible location in the cache. On an insertion, the new block is inserted to the position given by one of the hash functions. If the block selected for eviction should not be evicted, we can hash its address, and move it to another location where we find a new eviction candidate. This process can be repeated until a desired block is found, which is then finally evicted. To keep the search finite, there is a depth limitation. The total number of potential eviction candidates is then

$$R = \sum_{d=0}^{D-1} (W-1)^d$$

where W is the number of hash functions and D is the max depth.

Vantage separates the cache into two parts, a managed region and a smaller unmanaged region that is about 15 % of the total cache size. A target allocation is given to each of the cores. The cores are then allowed to slightly outgrow their allocations by borrowing size from the unmanaged region. On average the partition should stay at its target allocation, by having an equal number of insertions and evictions. New blocks are inserted into the managed region, then demoted to the unmanaged region, and then either evicted from the cache or promoted back into the managed region if it gets a hit. The evictions, demotions and promotions are controlled by an eviction priority. Each block has an eviction priority, which changes while the cache is being used. This priority can be any ordering of the cache blocks, an LRU stack is a good example of such an ordering. In the LRU stack, the MRU has the lowest eviction priority while the LRU has the highest.

To keep the size of the managed and unmanaged regions under control, the number of promotions and demotions need to be equivalent on average. This is done by setting an eviction threshold called an Aperture on the managed region, causing every block in the top Aperture percent of eviction priorities to be demoted to the unmanaged region. The aperture is set to  $A = 1/(R \cdot m)$ , where R is the number of replacement candidates and m is the fraction of the cache desired as the managed region.

The partition size for each core is given by an allocation policy, typically UCP or a software policy. The allocation policy can have different performance targets, the common being hit maximization, but it can also try to optimize for other metrics such as fairness or Quality of Service.

Vantage and ZCaches are very different cache schemes than the others we have looked at. A deeper look at these is outside the scope of this work, in particular since we did not implement Vantage for our experiments.

### Chapter 3

# Modeling a CMP

#### 3.1 ISA and multicore architecture

We simulate a CMP with an architecture similar to what you would find being produced today, with 2 levels of cache and 2 GHz core clock speed. We use the ARM ISA because it is well supported in our simulator, and is an important ISA that is experiencing significant growth of use [15].

We chose a two level cache organization for two reasons. First, we want to exercise the shared cache as much as possible, thus we want few other caches between the CPU and the shared LLC. Modern Intel processors like the i7 have 3 levels of cache, where L1 and L2 are private and L3 is shared between the cores[6]. We do not use 3 levels of cache because it would require even more simulation time to reach a sufficient number of accesses to the LLC. A cache that is being underutilized by not being accessed enough provides very few insights into the performance of a cache scheme. Simulation time is valuable, and instead of simulating longer periods we can use a 2 level structure. 2 cache levels are also common for ARM based chips.

Second, the 2 level cache is in line with what the proposed cache schemes use in their evaluation [23, 16, 18]. Hence it is natural for us to maintain this, so we do not stray too far away from their methodology.

The architecture used is specified in Table 3.1. This is the baseline on which most of the experiments in the next section is based upon. We are interested in the performance benefits gained from using different schemes in the shared L2 cache, so the other parameters are kept the same as much as possible.

|            |                     | 2/4/8 (ARM)                                             |                                                                                                                                   |  |

|------------|---------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

|            | 2 GHz               |                                                         |                                                                                                                                   |  |

|            |                     | 2                                                       |                                                                                                                                   |  |

| 32  kB     | 8 way               | 6 MSHR                                                  | LRU                                                                                                                               |  |

| 32  kB     | 8 way               | 6 MSHR                                                  | LRU                                                                                                                               |  |

| 1/2/4/8 MB | 32 way              | 16 MSHR                                                 | [Various schemes]                                                                                                                 |  |

| 2/4/8  GB  | _                   | 64 rd/wr queue slots                                    | _                                                                                                                                 |  |

| -          | 32 kB<br>1/2/4/8 MB | 32 kB         8 way           1/2/4/8 MB         32 way | 2 GHz         2         32 kB       8 way         6 MSHR         32 kB       8 way         6 MSHR         1/2/4/8 MB       32 way |  |

Table 3.1: A typical architecture used. The L2 (LLC) is used with different cache schemes to evaluate performance.

| Cache Size      | $8 \mathrm{MB}$     |

|-----------------|---------------------|

| Line Size       | 64 bytes            |

| Associativity   | 16                  |

| Number of banks | 4                   |

| Technology node | 32  nm              |

|                 |                     |

| Access time     | $3.5 \ \mathrm{ns}$ |

| Response time   | $0.5 \ \mathrm{ns}$ |

|                 |                     |

Table 3.2: The cache parameters and corresponding access and response times.

#### **3.2** Cache and cache latency

In order to have as realistic simulations, we are using cache latency specifications from CACTI [14]. Cacti is an integrated cache and memory access model, both for timing, leakage and power estimation. In our work we are interested in the timing values for caches, which we can use in the simulation.

We obtain the cache latency parameters used for simulation by calculating them using CACTI for a baseline cache. This baseline cache is an 8 MB 16-way cache, with 4 banks. It has a line size of 64 bytes, and is on the 32 nm technology node. The CACTI output for this is shown in Table 3.2. This configuration gives us an access time of 3.5 ns, equivalent to 7 CPU cycles at 2 GHz. The additional response time for a miss notice to be sent back to the CPU is 0.5 ns.

The cache latencies will accentuate or limit the impact of cache hits and misses on the total performance. The optimal size-to-latency of a cache is very workload dependent, and is an additional variable to consider when optimizing cache systems

|                  | L1i      | L1d      |

|------------------|----------|----------|

| Hit Latency      | 1 cycle  | 2 cycles |

| Response latency | 1 cycle  | 2 cycles |

| Block size       | 64 bytes | 64 bytes |

| MSHRs            | 2        | 6        |

| Write buffers    | -        | 16       |

| Size             | 32  kB   | 32  kB   |

| Associativity    | 2        | 2        |

Table 3.3: Baseline parameters for the L1 caches. These values are defaults that come with the gem5 simulators ARM caches.

for multicore workloads. To keep the number of variables at a manageable level, we have decided to fix the cache latencies independent of the cache size. This is an obvious simplification, as a 1 MB cache will be faster than an 8 MB cache. The access time for a 1 MB cache is 2.9 ns, compared to 3.5 ns for 8 MB. But keeping the latencies fixed lets us compare experiments that would otherwise be incomparable. As these values will differ for every real implementation, it is more important that they are equal between experiments than completely accurate. This is also in line with previous work [16].

An unfortunate situation was discovered near the end of this work. As we started simulating our experiments, we used 32-way associative caches without updating the latency values from 16-way models. The access time for a 32-way 8 MB cache is 5.7 ns, compared to 3.5 ns for the 16-way cache. This error was not caught in time to redo all simulations, thus the results presented are using the latencies from a 16-way cache. The simulations are still fair as all experiments have had the same baseline, but the cache latencies do not match as closely to CACTI as they could have.

Baseline L1 specifications are shown in Table 3.3, and L2 specifications are shown in Table 3.4. The values are derived from the output of CACTI in Table 3.2.

The majority of the results presented will use 1 MB L2 cache for dual and quad core results, and 4 MB L2 for the 8 core results. This was chosen experimentally, to keep the cache small enough to ensure contention, yet large enough to have some impact on performance.

Connecting the caches are gem5s CoherentBus, which ensures that caches stay coherent during the simulation. It is 32 bytes wide, and has the same clock speed as the CPU core. The bus takes care of any concurrency issues during the simulation, and serializes accesses to the cache. This is the default bus in the gem5 simulator. Unfortunately there was no available information on what interconnect is used in

|                  | L2                |

|------------------|-------------------|

| Hit Latency      | 7 cycles          |

| Response latency | 2 cycles          |

| Block size       | 64 bytes          |

| MSHRs            | 16                |

| Write buffers    | 8                 |

| Size             | $1/2/4/8 { m MB}$ |

| Associativity    | 32                |

Table 3.4: Baseline parameters for an L2 cache.

similar work. But as the interconnect remains the same for all schemes, we consider this a fair approach.

## 3.3 Main memory

The main memory size is set to 1 GB per benchmark in the workload, to allow sufficient space for all SPEC2006 benchmarks. This means 2 GB for dual core workloads and 4 GB for quad core workloads. The size of the main memory does not affect its latency or any other specification other than size itself.

For the main memory model, we use the SimpleDRAM module from gem5. It is a single-channel single-ported DRAM controller model that aims to model the most important system-level performance effects of a DRAM without getting into too much detail of the DRAM itself. It will model row and column operation and refresh cycles, and other effects such as write-to-read switch delays. Some important specifications are shown in Table 3.5.

These specifications approximate a DDR3-1066 DRAM with 7-7-7 timing, with a 1 GHz main memory bus. DDR uses both rising and falling edge of the clock, giving an actual clock rate of 500 MHz. This results in a clock period of 2 ns. In a 7-7-7 timing, the numbers indicate clock cycles for tCAS (latency to access a certain column), tRCD (delay between an row address and a column address) and tRP (latency to open a row). A fourth parameter, rRAS (row active time) is not modeled in gem5. A 7 cycle latency means delays of  $2 ns \times 7 = 14 ns$ , which is equivalent to our timing parameters.

The DRAM parameters have a huge performance impact on the workloads throughput. If the RAM has to do a random memory access, it will take 2 cycles missing in L1, 9 cycles missing in L2 and then 28 ns from accessing the main memory. At 2 GHz clock speed this adds up to 67 cycles. In the same time you could access

|                           | Simple DRAM   |

|---------------------------|---------------|

| Write buffer size         | 32            |

| Read buffer size          | 32            |

| RAS to CAS delay          | 14 ns         |

| CAS delay                 | 14 ns         |

| Row precharge time        | 14 ns         |

| Refresh cycle time        | 300  ns       |

| Refresh command interval  | $7.8 \ \mu s$ |

| Write to read switch time | 1  ns         |

Table 3.5: DRAM model parameters.

L2 almost 7 times, and L1 a total of 67 times. Out-of-order execution help utilize this waiting period a bit better, but it still affects performance significantly. If we were to decrease the performance of DRAM, the performance difference in the results would increase. The main cost of a cache miss is due to the access latency to the DRAM, and thus a scheme that has fewer misses will benefit further when the DRAM is slower.

# 3.4 Hardware and computational overhead of cache management schemes

The suggested schemes all add hardware to perform cache partitioning and management. These additions monitor cache usage, calculates optimal use of the cache and enforce the partitioning schemes. However, all cache schemes claim that their implementation require a negligible overhead, and that no additional latency occur in the cache due to this overhead. In our simulations we maintain this assumption.

## 3.4.1 Maintaining a partitioned cache

The actual partitioning of the cache has a very low overhead. Depending on the number of cores N in the system, you will need  $log_2(N)$  bits per cache line to indicate ownership of the cache line. Cache lines already have this sort of information to mark valid data, dirty lines, and so on. With a common 64 byte cache line size, an 8-core CPU will require 3 extra bits per line to partition the cache. This is an increase of at most 0.4 %.

For a physically tagged cache, no additional circuitry needs to be added to perform

checks on data accesses, as the tag uniquely identifies the data and thus the owner core. Only on replacements is it necessary to know the owner of the data.

## 3.4.2 Allocation algorithms

UCP and PIPP depend on a target partitioning given by some allocation policy. This policy could come from many places, e. g. the operating system, but is commonly given by a hit maximization algorithm. This algorithm takes the hit information from the shadow tag store and computes the best partitioning of the cache. The optimal solution to this problem is unfortunately NP-hard [19], although trivial for dual core CMPs. To get a good but not necessarily optimal partitioning, the Lookahead Algorithm is used instead. This is easily implementable and is reasonably fast, having a worst case time complexity of  $N^2/2$ , where N is the number of ways.

For PriSM, the target partitioning algorithm is even simpler. It only uses the total number of hits in the shadow tag store to evaluate the potential gain if an application had the entire cache for it self. The target partition is then adjusted based on what application has the highest potential gain. It requires approximately 20 arithmetic operations to compute the new target partition for a 4 core system, and grows linearly with the number of cores. The arithmetic operations do include floating point, used when computing the eviction probabilities required by PriSM. Some of these can be implemented as fixed point arithmetic to reduce overhead. Despite this, PriSM has the lightest partitioning algorithm of the implemented cache schemes.

All three cache management schemes assume no additional latency to calculate the target partitions.

## 3.4.3 Enforcement algorithms

Enforcement of the allocation differ between cache schemes. In UCP, accesses work as in a LRU cache, the only difference is in replacement handling. When searching for an eviction candidate, UCP first has to see if it occupies the target amount of ways. If it does not, it needs to find a block from one of the other cores that exceeds its quota, preferably the one that exceeds it the most. A block is then selected, and the rest works as a normal eviction/replacement. This process requires a small counter and access to the target partition values, none of which produce a significant overhead.

Enforcing PIPP requires more computation, in particular on an access hit. Unlike LRU and UCP, a block is not promoted on a hit in all cases. PIPP needs a 4 bit random number, and promotes the block if the number is not 0, giving a 3/4 probability of promotion. In the case of a streaming application a 7 bit random number is required, and the block is promoted if it is equal to 0, giving a probability

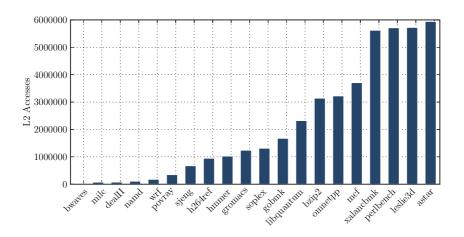

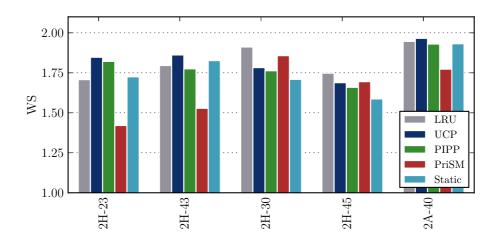

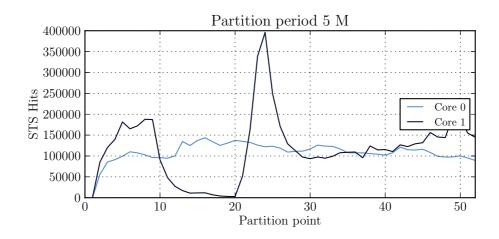

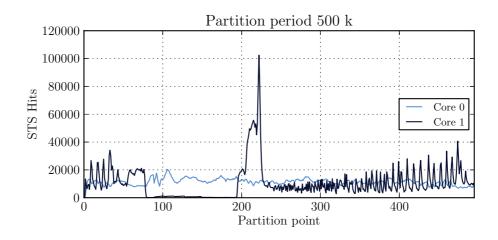

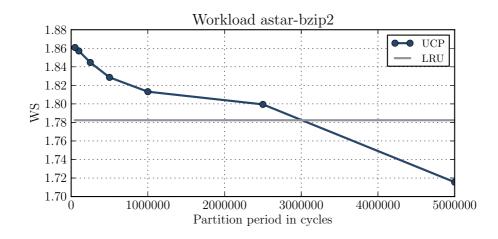

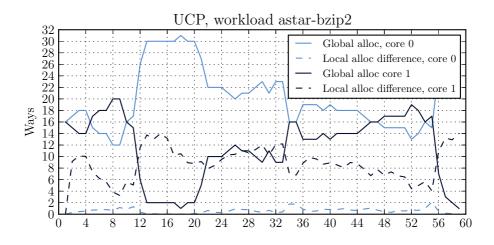

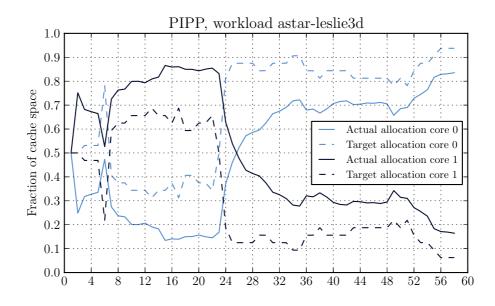

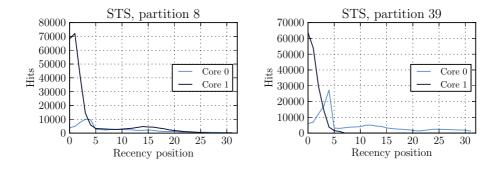

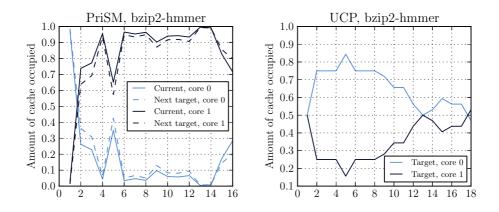

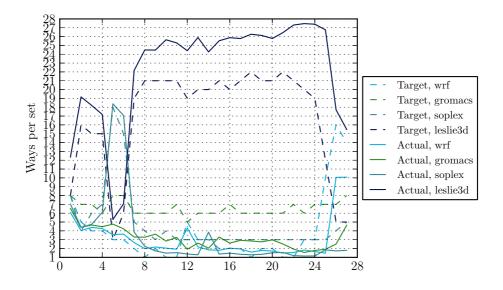

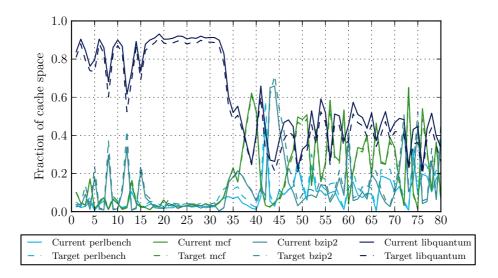

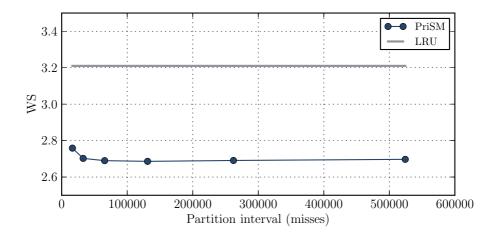

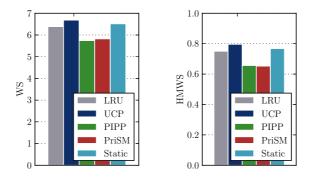

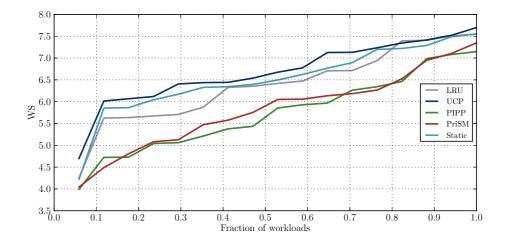

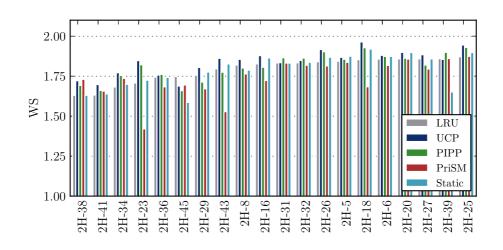

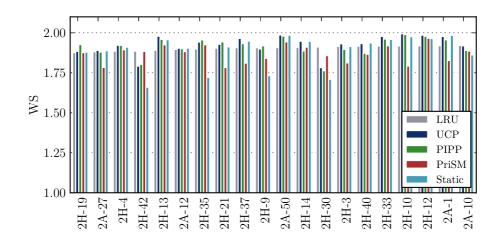

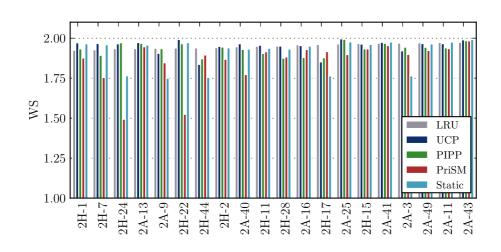

of 1/128. Random numbers may not be readily available, and as such could incur a small overhead. Evictions in PIPP add no extra overhead compared to LRU, the lowest priority block is always evicted.