## Implementing a Heterogeneous Multi-Core Prototype in an FPGA

Leif Tore Rusten Gunnar Inge Sortland

Master of Science in Computer ScienceSubmission date:July 2012Supervisor:Magnus Jahre, IDICo-supervisor:Gunnar Tufte, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

## **Problem Description**

#### Implementing a Heterogeneous Multi-Core Prototype in an FPGA

Current multi-core processors are constrained by energy. Consequently, it is not possible to improve performance further without increasing energy efficiency. A promising option for making increasingly energy efficient CMPs is to include processors with different capabilities. This improvement in energy efficiency can then be used to increase performance or lower energy consumption.

Currently, it is unclear how system software should be developed for heterogeneous multi-core processors. A main challenge is that little heterogeneous hardware exists. It is possible to use simulators, but their performance overhead is a significant limitation. In this thesis, the students should develop a framework for realizing heterogeneous multi-core processors in an FPGA. The minimum requirements of this thesis are two simple processor core implementations, a scalable interconnect and a memory interface. If time permits, a simple Task Based Parallelism (TBP) runtime engine can be implemented for the prototype architecture.

Supervisor: Magnus Jahre, IDI

#### Sammendrag (Norwegian Abstract)

Siden midten av 1980-tallet har ytelsesveksten for prosessorer vært formidabel, med en årlig vekst på om lag 52%. Denne veksten er gjort mulig blant annet grunnet arkitekturer som utnytter ILP og økende klokkefrekvenser. Disse fremgangsmåtene for ytelseøkning er derimot ikke lenger like effektive siden vi har nådd den praktiske grensen for effektforbruket til prosessorer. Ved å bruke heterogene prosessorer kan vi forbedre energieffektiviten, men dette krever forskning på åpne spørsmål vedrørende heterogen prosessering. Mangelen på heterogen maskinvare gjør det derimot vanskelig å drive effektiv forskning. I denne oppgaven har vi laget et svært modulært og konfigurerbart rammeverk for prototyperealiseringer av heterogene flerkjerneprosessorer. Rammeverket, som er planlagt brukt hos datamaskingruppen ved NTNU, består av to forskjellige prosessorfliser i tillegg til en rekke funksjonelle fliser. Disse flisene kan flislegges til forskjellige heterogene prosessorprototyper. Ved å bruke rammeverket vårt opp mot en Xilinx Virtex 6 fikk vi implementert prosessorer med opp til 40 heltallskjerner eller 16 flyttallskjerner.

#### Abstract

Since the mid-1980s processor performance growth has been remarkable, with an annual growth of about 52 %. Methods such as architectural enhancements exploiting ILP and frequency scaling have been effective at increasing performance, but are now limited by its diminishing returns and the power wall. Heterogeneous processors as an alternative source for continued growth looks promising, but research on heterogeneous software is made difficult as heterogeneous hardware is in low supply. This thesis cover the design and implementation of a heterogeneous processor called SHMAC and its framework. Flexibility of the delivered system allows rapid exploration of both hardware and software sides of heterogeneous processor research questions. The system is intended for research at CARD at NTNU. Two processor tiles and a set of additional tiles for extended functionality are provided, yielding a wide range of possible hardware setups in the delivered framework. Using a Xilinx Virtex 6 we were able to implement 40 integer cores or 16 floating-point cores.

## Preface

This thesis is submitted to the Norwegian University of Science and Technology for partial fulfillment of the requirements for a master's degree.

This work has been performed at the Department of Computer and Information Science, NTNU, Trondheim, with Magnus Jahre as supervisor and Gunnar Tufte as cosupervisor.

## Acknowledgment

We would like to thank our supervisors for good discussions and useful feedback. Without their continued support, eagerness and guidance this thesis would not have been possible. The weekly follow-up meetings have been a source for many great discussions guiding the progression of this thesis in a worthwhile direction.

We would also like to thank Nordic Semiconductor for providing us with a modern FPGA development board capable of large designs and with an easy host interface. We would not have done as well without it.

Gunnar Inge would also like to thank his wife Synne Agnete for all her extensive support.

The "Heterogeneous Multicorn" logo is built upon the work of Dee Dreslough with post-processing by Karl Johan Heimark.

## Contents

| Pr            | oble                                    | m Description                                                                                                                                          | i                                 |

|---------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Sa            |                                         | endrag<br>rwegian Abstract)                                                                                                                            | iii                               |

| Al            | bstra                                   | $\mathbf{ct}$                                                                                                                                          | $\mathbf{v}$                      |

| Pr            | r <b>efac</b> e<br>Acki                 | e<br>nowledgment                                                                                                                                       | <b>vii</b><br>vii                 |

| Co            | onter                                   | its                                                                                                                                                    | xii                               |

| $\mathbf{Li}$ | st of                                   | Figures                                                                                                                                                | xiv                               |

| $\mathbf{Li}$ | st of                                   | Tables                                                                                                                                                 | $\mathbf{x}\mathbf{v}$            |

| Li            | st of                                   | Listings x                                                                                                                                             | vii                               |

| Li            | st of                                   | Abbreviations                                                                                                                                          | xix                               |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4 | oduction         SHMAC Overview         Assignment Interpretation         1.2.1         Requirements         Main Contributions         Report Outline | <b>1</b><br>3<br>4<br>4<br>7<br>8 |

| 2             | <b>Bac</b><br>2.1                       | kgroundAnalytical Models of Computer Systems2.1.1Amdahl's law2.1.2Pollack's Rule                                                                       | <b>9</b><br>9<br>9<br>10          |

|               | 2.2                                     | Chip Multiprocessors                                                                                                                                   | 13                                |

|          |      | 2.2.2 TLP focused CMP                                                                                          |

|----------|------|----------------------------------------------------------------------------------------------------------------|

|          |      | 2.2.2.1 Tiled Chip Multiprocessors                                                                             |

|          |      | 2.2.3 Heterogeneous Chip Multiprocessors                                                                       |

|          | 2.3  | Software for Heterogeneous CMPs                                                                                |

|          |      | 2.3.1 Work Stealing                                                                                            |

|          |      | 2.3.2 Architecture-aware Task-scheduling                                                                       |

|          | 2.4  | Interconnect                                                                                                   |

|          |      | 2.4.1 Routing Algorithms                                                                                       |

|          |      | $2.4.1.1$ The Turn Model $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $19$                                     |

|          |      | 2.4.1.2 XY routing                                                                                             |

|          |      | 2.4.2 Wormhole Flow Control                                                                                    |

| 3        | The  | SHMAC 23                                                                                                       |

|          | 3.1  | Instruction Set Architecture                                                                                   |

|          | 3.2  | Tile Organization                                                                                              |

|          | 3.3  | Memory Layout                                                                                                  |

| 4        | Deta | ailed Design 29                                                                                                |

|          | 4.1  | Network Packets                                                                                                |

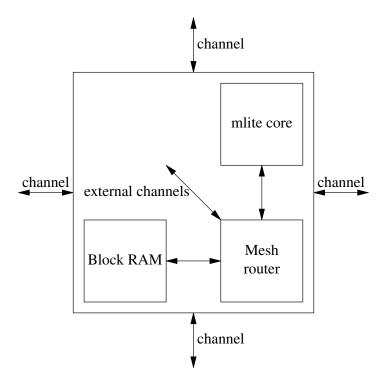

|          | 4.2  | Basic Tile Units                                                                                               |

|          |      | 4.2.1 On-chip Block RAM                                                                                        |

|          |      | 4.2.2 Dummy Slave                                                                                              |

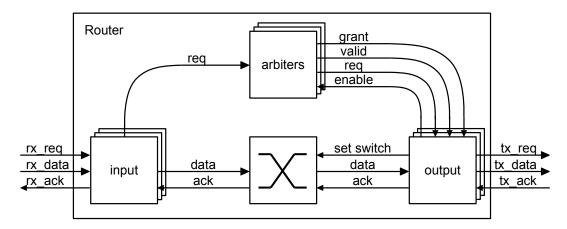

|          |      | 4.2.3 Mesh Router                                                                                              |

|          | 4.3  | Integer Processor Tile                                                                                         |

|          |      | 4.3.1 mlite                                                                                                    |

|          |      | $4.3.1.1  \text{Known Limitations}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  35$                |

|          | 4.4  | Floating Point Processor Tile                                                                                  |

|          |      | 4.4.1 FPU Module                                                                                               |

|          | 4.5  | RAM Tile                                                                                                       |

|          | 4.6  | LED Tile                                                                                                       |

|          | 4.7  | Clock Tile                                                                                                     |

|          | 4.8  | Jump Tile                                                                                                      |

|          | 4.9  | LL/SC Tile                                                                                                     |

|          | 4.10 | UART Tile                                                                                                      |

| <b>5</b> | SHN  | AC Software 45                                                                                                 |

|          | 5.1  | Configuration System                                                                                           |

|          | 5.2  | Run-time System                                                                                                |

|          | 5.3  | Writing SHMAC Software                                                                                         |

|          |      | 5.3.1 Accessing External Symbols                                                                               |

|          |      | 5.3.2 Access Memory from other Tiles                                                                           |

|          |      | 5.3.3 Locking Library $\ldots \ldots 50$ |

|          | 5.4  | Host Software                                                                                                  |

|          |      | 5.4.1 UART Utility Programs                                                                                    |

|          |      | 5.4.1.1 Program Loader                                                                                         |

|          |      | 5.4.1.2 Read Memory over UART $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 52$                            |

|          |      |                                                                                                                |

| 6 | Verification | and | Repro | ducibility | V |

|---|--------------|-----|-------|------------|---|

|---|--------------|-----|-------|------------|---|

$\mathbf{53}$

|   | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ |         |            | cation                                       |       |   |   |    |

|---|-------------------------------------------|---------|------------|----------------------------------------------|-------|---|---|----|

|   | 6.3                                       | •       |            |                                              |       |   |   |    |

| 7 | $\operatorname{Res}$                      | ults    |            |                                              |       |   |   | 59 |

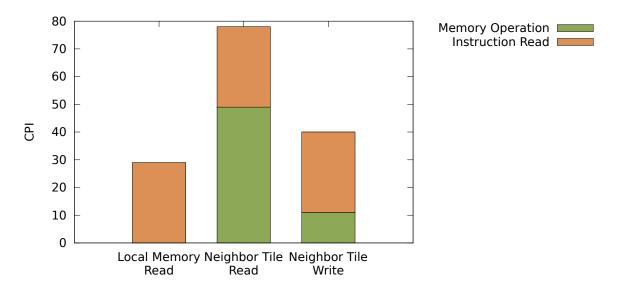

|   | 7.1                                       | Micro   | Benchman   | rks                                          |       |   |   | 59 |

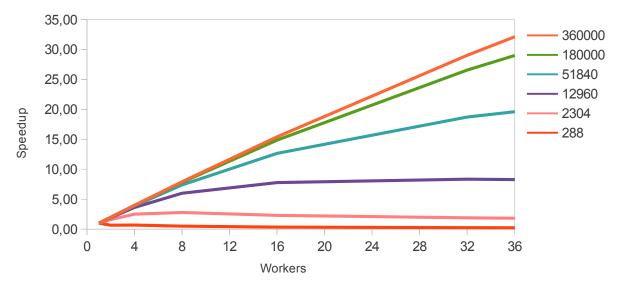

|   | 7.2                                       | Paralle | el Sum     |                                              |       |   |   | 60 |

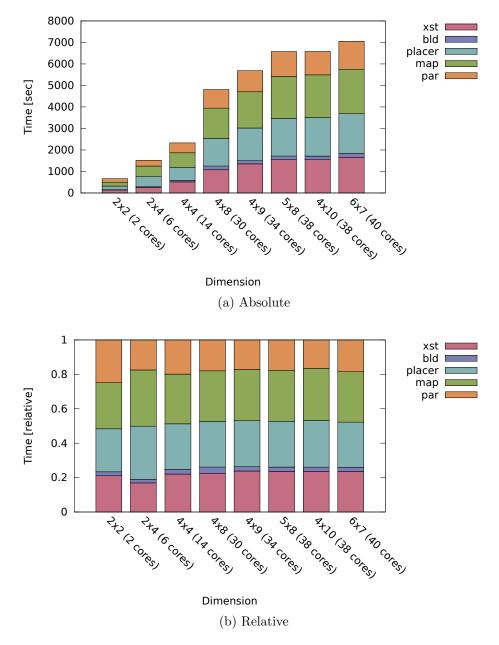

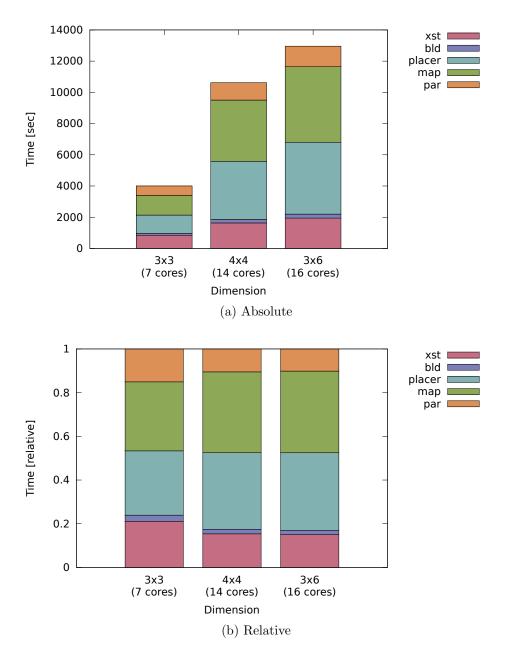

|   | 7.3                                       | Time I  | Required f | for building Prototypes                      |       |   |   | 60 |

|   |                                           | 7.3.1   |            | s Time                                       |       |   |   | 61 |

| 8 | Dis                                       | cussion | ı          |                                              |       |   |   | 65 |

|   | 8.1                                       | Proces  | sor Perfor | mance                                        |       |   |   | 65 |

|   | 8.2                                       | Synthe  | esis Time  | and Rapid Prototyping                        |       |   |   | 65 |

|   | 8.3                                       | Design  | n Vulnerak | pilities                                     |       | • |   | 66 |

|   | 8.4                                       | Run-ti  | ime Syster | n                                            |       | • |   | 66 |

|   | 8.5                                       | Altern  | ative Top  | ologies and Addressing                       | <br>• | • | • | 66 |

| 9 | Cor                                       | clusio  | n          |                                              |       |   |   | 69 |

|   | 9.1                                       | Future  | Work       |                                              |       |   |   | 69 |

|   |                                           | 9.1.1   | Processo   | r Tile Improvements                          |       |   |   | 70 |

|   |                                           |         | 9.1.1.1    | Exception Handling                           |       |   |   | 70 |

|   |                                           |         | 9.1.1.2    | Caching                                      |       |   |   | 70 |

|   |                                           |         | 9.1.1.3    | Improved FPU Performance                     |       |   |   | 70 |

|   |                                           |         | 9.1.1.4    | Dual-Port RAM Slave Unit                     |       |   |   | 70 |

|   |                                           |         | 9.1.1.5    | Improved Local Memory Performance            |       |   |   | 71 |

|   |                                           | 9.1.2   | Intercom   | nect Improvements                            |       |   |   | 72 |

|   |                                           |         | 9.1.2.1    | Configurable Memory Properties               |       |   |   | 72 |

|   |                                           |         | 9.1.2.2    | Buffering at Router Ports                    |       |   |   | 72 |

|   |                                           |         | 9.1.2.3    | Flit-buffer Flow Control                     |       |   |   | 72 |

|   |                                           |         | 9.1.2.4    | Routing Resources                            |       |   |   | 72 |

|   |                                           |         | 9.1.2.5    | Routing Algorithms                           |       |   |   | 73 |

|   |                                           | 9.1.3   | SHMAC      | Enhancements                                 |       |   |   | 73 |

|   |                                           |         | 9.1.3.1    | DRAM Tile                                    |       | • |   | 73 |

|   |                                           |         | 9.1.3.2    | Random Tile                                  |       | • |   | 73 |

|   |                                           |         | 9.1.3.3    | Crypto Tile                                  |       |   |   | 73 |

|   |                                           |         | 9.1.3.4    | Collection Tile                              |       |   |   | 74 |

|   |                                           |         | 9.1.3.5    | CA Tile                                      |       | • |   | 74 |

|   |                                           | 9.1.4   | External   | Communication                                |       |   |   | 75 |

|   |                                           |         | 9.1.4.1    | UART Debug Support                           |       |   |   | 75 |

|   |                                           |         | 9.1.4.2    | Automatic Result Gathering                   |       |   |   | 75 |

|   |                                           |         | 9.1.4.3    | SHMAC to Host Communication                  |       |   |   | 75 |

|   |                                           |         | 9.1.4.4    | Robust UART Reset                            |       |   |   | 76 |

|   |                                           | 9.1.5   | Software   | Improvements                                 |       |   |   | 76 |

|   |                                           |         | 9.1.5.1    | Work Stealing Algorithm                      |       |   |   | 76 |

|   |                                           |         | 9.1.5.2    | Task Based Parallelism (TBP) Run-time Engine |       |   |   | 76 |

|   |                                           |         | 9.1.5.3    | SHMAC Layout Introspection                   |       |   |   | 77 |

|   |                                           |         | 9.1.5.4    | Per-Experiment Configurations                |       |   |   |    |

|              | 9.1.5.5  | Alternative Linker Script | . 78 |

|--------------|----------|---------------------------|------|

|              | 9.1.5.6  | Configurable Topology     | . 78 |

|              | 9.1.5.7  | Fallback Lock Library     |      |

|              | 9.1.5.8  | Interrupt Routines        | . 78 |

|              | 9.1.5.9  | Heap Support              | . 78 |

| Bibliography |          |                           | 84   |

| Appendices   |          |                           |      |

| Appendix A   | Glossar  | У                         | 85   |

| Appendix B   | Benchm   | arks                      | 87   |

| B.1 Micro    | benchmar | ks                        | . 87 |

| B.1.1        | Sustaine | d Int                     | . 87 |

| B.1.2        | Read to  | Neighbor                  | . 88 |

|              |          | Neighbor                  |      |

| B.2 Parall   | el Sum   |                           | . 89 |

| Appendix C   | Synthes  | is Reports                | 95   |

| Appendix D   | Configu  | ration                    | 99   |

| Appendix E   | Tutorial | l                         | 101  |

# List of Figures

| $1.1 \\ 1.2$ | History of Processor Performance from 1978 to 2006.      The Power Wall.                                              |            |

|--------------|-----------------------------------------------------------------------------------------------------------------------|------------|

| 1.3          | A first SHMAC overview                                                                                                |            |

| $2.1 \\ 2.2$ | Plot showing maximal speedup for an application given its parallel portion<br>Integer performance with regard to area | 10<br>11   |

| 2.2<br>2.3   |                                                                                                                       | 11<br>11   |

| $2.3 \\ 2.4$ | •                                                                                                                     | $11 \\ 12$ |

| $2.4 \\ 2.5$ | 1 1                                                                                                                   | $12 \\ 13$ |

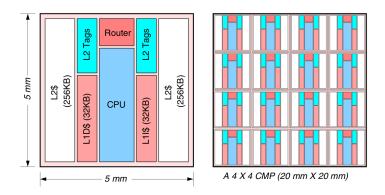

| 2.0<br>2.6   | Tile concept with CPU, cache and router.                                                                              | $15 \\ 15$ |

| 2.0<br>2.7   | Overview of the TILEPro64 <sup>TM</sup> processor                                                                     | 16         |

| 2.1<br>2.8   | Execution model using strands.                                                                                        | 17         |

| 2.0<br>2.9   |                                                                                                                       | 19         |

| 2.10         |                                                                                                                       | 20         |

| 2.10         |                                                                                                                       | 21         |

| 3.1          | Top-level overview of the SHMAC processor                                                                             | 23         |

| 3.2          | 1 1                                                                                                                   | 20<br>24   |

| 3.3          | An overview of a generic SHMAC-tile                                                                                   |            |

| 3.4          |                                                                                                                       | 26         |

| 3.5          |                                                                                                                       | 26         |

| 3.6          |                                                                                                                       | 27         |

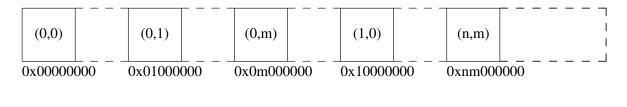

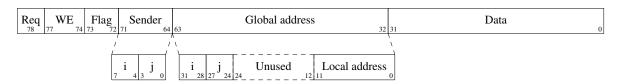

| 4.1          | Network packet layout                                                                                                 | 30         |

| 4.2          |                                                                                                                       | 32         |

| 4.3          | Processor tile                                                                                                        | 33         |

| 4.4          |                                                                                                                       | 34         |

| 4.5          |                                                                                                                       | 36         |

| 4.6          | Block diagram of FPU module                                                                                           | 37         |

| 4.7          | Complete memory layout of the LED Tile                                                                                | 39         |

| 4.8          |                                                                                                                       | 43         |

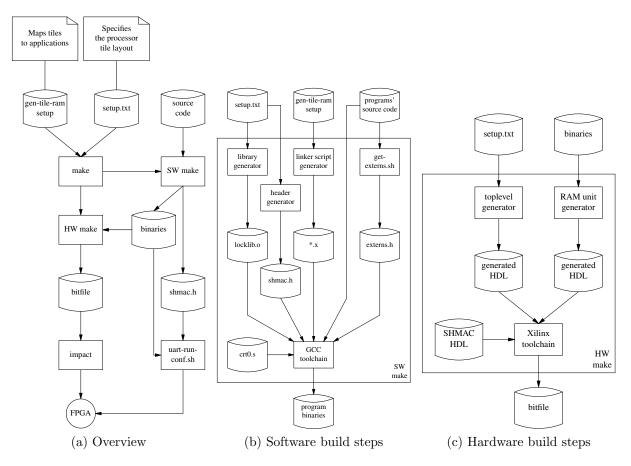

| 5.1          | Overview of the SHMAC framework.                                                                                      | 45         |

| $5.2 \\ 5.3$                              | Configuration system build steps46Example processor layout configuration file46                                                                           |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

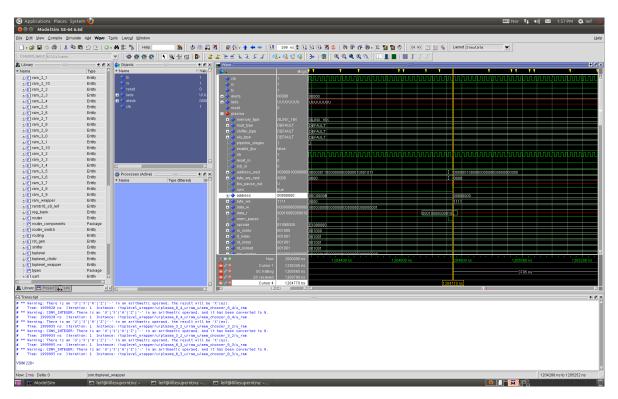

| $\begin{array}{c} 6.1 \\ 6.2 \end{array}$ | Modelsim window54Development board setup57                                                                                                                |

| $7.1 \\ 7.2 \\ 7.3 \\ 7.4$                | CPI for the implemented microbenchmarks                                                                                                                   |

| 8.1                                       | Tree Interconnect                                                                                                                                         |

| 9.1<br>9.2<br>9.3<br>9.4                  | Overview of tile with dual-port block RAM71Improved processor tile71Collection Tile with slave units74Collection Tile's internal address representation74 |

| B.1                                       | Layout for hardware in the Parallel Sum Benchmark                                                                                                         |

| D.1                                       | Example tile layout configuration file                                                                                                                    |

## List of Tables

| 1.1 | Key design decisions                                                          | 5  |

|-----|-------------------------------------------------------------------------------|----|

| 2.1 | Run time example for different processor architectures $\ldots \ldots \ldots$ | 12 |

| 4.1 | Tile Details                                                                  | 29 |

| 4.2 | Setting memory request mode                                                   | 30 |

| 4.3 | Memory layout of the clock tile                                               | 40 |

| 4.4 | Memory layout of the jump tile                                                | 41 |

| 4.5 | LL-tile's synchronization bookkeeping example                                 | 42 |

| 4.6 | UART commands                                                                 | 42 |

| 5.1 | Tile types                                                                    | 47 |

| 5.2 | uart-run-conf.sh tool-chain steps                                             | 52 |

| 6.1 | System-level Software Tests                                                   | 55 |

| 7.1 | Execution time in cycles given number of workers and problem size             | 60 |

| 7.2 | Synthesis Time for Integer Processor Tiles in second                          | 62 |

| 7.3 | Synthesis Time for Floating Point Processor Tiles in second                   | 62 |

| 7.4 | Synthesis Time for mixed Processor Tiles in second                            | 62 |

# List of Listings

| 1  | Loop-level Parallelism                                          |   |   | • |   |     | 14  |

|----|-----------------------------------------------------------------|---|---|---|---|-----|-----|

| 2  | Listing dependencies between binaries in Makefile               |   |   |   |   |     | 49  |

| 3  | Make variable accessible for other binaries                     |   |   |   |   |     | 49  |

| 5  | Retrieving Memory Addresses using shmac.h                       |   |   |   |   |     | 49  |

| 4  | Accessing a shared variable                                     |   |   |   |   |     | 50  |

| 6  | Using the locking framework                                     |   | • | • |   | •   | 50  |

| 7  | Example of UART configuration file                              |   | • | • |   | •   | 51  |

| 8  | Benchmark UART configuration file                               |   |   |   |   | •   | 88  |

| 9  | Sustained Int Benchmark                                         |   | • | • |   | •   | 88  |

| 10 | Read from Neighbor                                              |   | • | • | • | •   | 89  |

| 11 | Write to Neighbor                                               |   | • | • |   | •   | 90  |

| 12 | Parallel Sum - Master                                           |   |   | • |   | •   | 91  |

| 13 | Parallel Sum - Slave                                            |   | • | • |   | •   | 92  |

| 14 | Sequential Sum                                                  |   |   | • |   | •   | 93  |

| 15 | Halt Program                                                    |   | • | • | • | •   | 93  |

| 16 | Synthesis Report for 40 Integer Processor Tiles                 | • |   |   |   | •   | 96  |

| 17 | Synthesis Report for 16 Floating Point Processor Tiles          |   |   | • |   | •   | 97  |

| 18 | Synthesis Report for 20 integer processors and 8 FPU processors |   |   |   |   |     | 98  |

| 19 | Example of accessing a tile's memory                            |   | • | • |   | •   | 99  |

| 20 | Tutorial: shmac.h                                               |   |   |   |   | . 1 | .02 |

| 21 | Tutorial: bank_west.c                                           |   |   |   |   | . 1 | .03 |

| 22 | Tutorial: bank_east.c                                           |   |   |   |   | . 1 | .04 |

| 23 | Tutorial: externs.h                                             |   |   |   |   | . 1 | .05 |

## List of Abbreviations

- ABI Application Binary Interface. 48

ASIC Application-Specific Integrated Circuit. 72

CARD The Computer Architecture and Design Group. 2, 4, 69, 70

CMP Chip Multiprocessor. 16

CPI Cycles Per Instruction. 59

CPOP Critical-Path-on-a-Processor. 17

CPU Central Processing Unit. 14, 34

CUDA Compute Unified Device Architecture. 16

DAG Directed Acyclic Graph. 17, 18, 105

DLS Dynamic Level Scheduling. 17

FCP Fastest Critical Path. 17

FPGA Field-Programmable Gate Array. i, vii, 3–5, 43, 46, 47, 55, 56, 61, 62, 65, 69, 72, 73, 95, 105

FPU Floating-Point Unit. 24, 61, 62

GCC GNU Compiler Collection. 5–7, 24, 34, 35

- **GDB** GNU Debugger. 53, 75

- GPU Graphical Processing Unit. 15, 16

HEFT Heterogeneous Earliest-Finish-Time. 16, 17

HMP Heterogenous Multicore Processor. 8

ILP Instruction Level Parallelism. 1, 2, 5, 13, 14, 17

- **ISA** Instruction Set Architecture. 4, 6, 16, 24, 33, 34, 51, 85

- **LED** Light-Emitting Diode. 25, 29, 38, 39, 75

- LL Load-Linked. 30, 31, 34, 35, 41, 47, 49–51, 55, 56, 65, 70, 78, 85, 101

- LMT Levelized-Min Time. 17

- ${\bf LUT}$ Lookup Table. 62

- NoC Network-on-Chip. 43

- NTNU Norwegian University of Science and Technology. 2

- NUMA Non-Uniform Memory Access. 23, 26, 33

- PC Program Counter. 40

- **RAM** Random Access Memory. 25, 29, 31, 32, 38, 40, 41, 61, 65, 67, 70, 71, 73, 105

- **RISC** Reduced Instruction Set Computer. 24

- **RMW** Read-Modify-Write. 41, 51, 85

- SC Store-Conditional. 30, 31, 34, 35, 41, 47, 49–51, 55, 56, 65, 70, 78, 85, 101

- SHMAC Single-ISA Heterogeneous Multicore Architecture Computer. 3, 4, 6, 8, 23, 24, 26, 29, 31–33, 39–43, 45, 46, 48, 51, 52, 55, 56, 60, 65, 66, 69, 70, 72–76, 101, 105

- SIMD Single Instruction, Multiple Data. 16

- SoC System-on-Chip. 18

- **TBP** Task Based Parallelism. xi, 4, 17, 48, 53, 66, 76, 77

- **TLP** Task Level Parallelism. 14, 15

- WLIW Very Long Instruction Word. 14

## Introduction

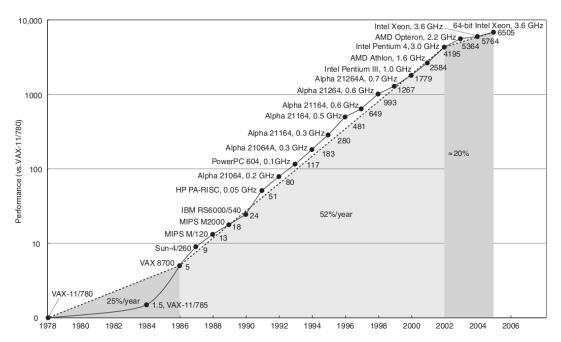

It is roughly 60 years since the first general-purpose electronic computer was created. In this period, the progress of the field of processor design has been incredible. Figure 1.1 shows that from 1986 to 2002 processors had a performance growth of about 52 % annually. The performance growth for single core processors has however declined the latest years due to the limitations of power, available Instruction Level Parallelism (ILP) and memory latency [1]. According to Horowitz and Dally [2] the power of today's chip is now limited by the cost of cooling.

As the growth in single-core processors have been high, computer software has traditionally been written for serial computation. Until recently, performance growth have focused on increasing instruction throughput through pipelining for allowing frequency scaling and exploiting all forms of ILP [3]. To enable higher frequencies and thus performance, processors became increasingly complex with deep pipelines, advanced branch

Figure 1.1: History of Processor Performance from 1978 to 2006. (Reproduced from [1, p. 3])

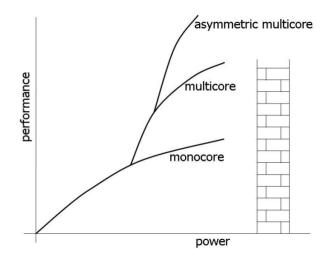

Figure 1.2: The Power Wall. (Reproduced from [4])

prediction to avoid the cost of flushing these pipelines and reordering of instructions to exploit ILP.

The increased complexity of processor designs have led to an increased power usage as frequency is increased and more transistors are utilized. Meenderinck and Juurlink [4] argues that we have reached the power wall for single-core processors (illustrated in Figure 1.2) i.e. we can no longer easily get more performance growth from adding complex hardware modules. This is due to power constraints which limit the complexity at a given clock frequency, but designs are also influenced by its economics [5]. Data centers consumed 1.5 % of all electricity in the U.S. in 2006 with an annual growth of 12 % [6]. This has created an increased focus on energy efficiency.

Borkar and Chien [7] predicts that operation frequency will increase slowly, with energy as the key limiter, during the next two decades. This forces a change in our approach to exploiting parallelism for increasing performance. One possibility is to focus on heterogeneous cores and accelerators to achieve good performance and energy efficiency. As given by Amdahl's law, total speedup for parallel execution of a program is limited by its sequential parts. Performance will therefore require research in exploiting parallelism without sacrificing single thread performance [8].

In nearly every program there will be a substantial amount of work which cannot easily be implicitly parallelized by hardware. This is due both to true dependencies within the program in addition to that there may be to expensive to exploit all available ILP within a program. In a multicore setting, the total execution time and/or power consumption would benefit from assigning unparallelizable work to a faster CPU core or accelerator. This is exactly what heterogeneous processors enables if one assigns unparallelizable or hard work to higher performance cores or accelerators, while still using simple cores for normal parallelizable work. Some early research suggests that a task-based programming model may be fitting to utilize a system using heterogeneous cores, given that the scheduler is aware of its architecture [9, 10].

Heterogeneous computing is becoming one of the main focuses of research at The Computer Architecture and Design Group (CARD) at Norwegian University of Science and Tech-

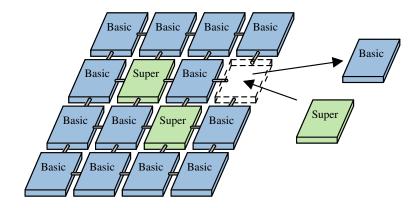

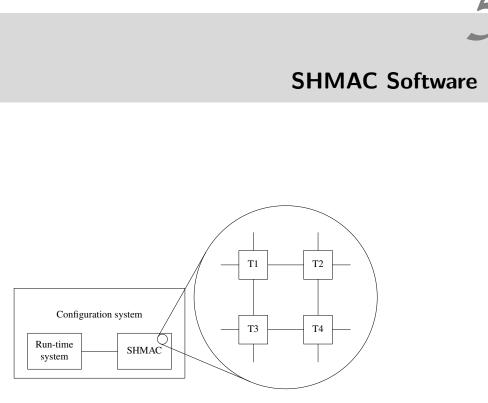

Figure 1.3: A first SHMAC overview

nology (NTNU). This computer architecture approach looks promising both for reducing energy consumption and increasing performance. To obtain as large a potential gain as possible it is necessary to understand how to utilize the heterogeneous computational units in smart ways. This requires research on the topic of heterogeneous processors, but heterogeneous processor implementations are not readily obtainable.

## 1.1 SHMAC Overview

This thesis' purpose is to implement a heterogeneous processor using an Field-Programmable Gate Andray (FPGA) in an attempt to circumvent the current lack of heterogeneous hardware available. A hardware framework is requested rather than a simulator framework because software approaches becomes limited due to simulation overhead as the core count increases. Simulators are on the other hand very flexible. Our thesis' outcome should allow for the specification of multiple different heterogeneous designs. This customization shall compensate for the lack of currently commercial solutions to build research on. The customization also tries to mitigate the loss of flexibility incurred by moving away from simulators. Based on the hardware space attainable from this customizable framework, research on characteristics software solutions need to fully exploit heterogeneous processing can be done. In case the hardware space made available in our delivery becomes to restrictive, the system is designed in a way that allows for easy modification and additions of new modules and concepts to the framework.

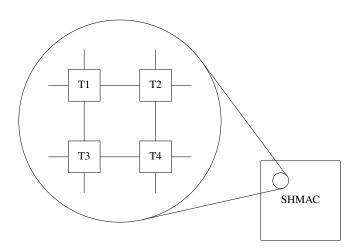

We have created a processor design called Single-ISA Heterogeneous Multicore Architecture Computer (SHMAC) which together with its associated framework promises to fulfill the previously outlined purpose. Figure 1.3 shows one possible hardware configuration of the SHMAC processor consisting of sixteen cores. The cores are encapsulated in a construct called a tile. The tile concept is known for its ease of scalability and how its reusability leverage initial design cost and subsequent maintenance efforts. Furthermore, as previous work by Zhang and Asanovic [11] shows, tile-based architectures allows for a modular approach. The details of the different interiors of tiles are kept contained within each tile. By encapsulating the different cores in uniform tiles we allow for the complete separation of the interconnection module from the core modules. This makes it easy to modify the organization of tiles and the implementations of the modules. New hardware concepts can easily be made into tiles and be integrated with the existing framework.

In addition to the processor framework we have created a small run-time support system creating the abstractions needed for communication between cores and for synchronization. If cores are to cooperate, then these building blocks are of importance since reasoning about shared memory is easily error-prone if not supported by some sort of software abstractions. The SHMAC framework is intended to be CARD's initial prototype of a heterogeneous framework. It is going to aid in the exploration of existing solutions (e.g. task-based parallelism) and discovery of novel software approaches. The delivered software abstractions is considered helpful for a swift start-up after project handover.

### **1.2** Assignment Interpretation

We have split the assignment into the following precise tasks:

- **T1** (Mandatory) Create a framework for heterogeneous multi-core processors in an FPGA. Different processor cores must be included in the delivered framework.

- T2 (Mandatory) Include a scalable interconnect for processors and memory.

- T3 (Mandatory) Add a memory interface for external access.

- **T4** (Optional) Implement a Task Based Parallelism (TBP) run-time engine on top of the hardware.

T3 has been made more precise than what the assignment text specifies as merely requiring any memory interface is trivially fulfilled in any processor design. Making precise the notion of external memory accesses as for e.g. examining memory from a lab setup, introduces functionality and possibilities not already inherent. This is assumed to be the true intent of this part of the assignment.

#### **1.2.1** Requirements

A set of developer requirements were determined based on a combination of the tasks found, input from CARD and our own self-interests in such a framework.

#### **Functional Requirements**

- 1. The framework must ship with a basic integer based core

- 2. The framework must ship with a floating-point accelerated core

- 3. The framework shall utilize the modular tile architecture

- 4. The framework shall utilize a mesh interconnect

- 5. The framework must have an external memory interface

- 6. The framework need only support a single Instruction Set Architecture (ISA)

| Design question     | Choices considered ( <b>bold</b> marks decision) | Remarks                                                                                                                                                                                                          |

|---------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architectural class | Classic, <b>Tile</b>                             | By Classic we mean the de facto indus-<br>try standard with cores connected in a<br>multi-level cache hierarchy.                                                                                                 |

| Interconnect type   | Mesh, Tree,                                      | v                                                                                                                                                                                                                |

|                     | All-to-all, Bus                                  | All-to-all and bus interconnects were<br>only briefly considered as these were<br>considered to not meet the scalability<br>requirement of T2.                                                                   |

| Core diversity by   | Accelerators, ILP                                | Starting from a simple core it seemed<br>less time-consuming to integrate an ac-<br>celerator then to add ILP techniques.                                                                                        |

| Multi-ISA           | Yes, <b>No</b>                                   | Single-ISA suffice when researching the<br>impact of software techniques on dif-<br>ferent heterogeneous processor layouts,<br>while simplifying aspects of both pro-<br>cessor tile design and run-time system. |

Table 1.1: Key design decisions

#### **Non-Functional Requirements**

- 1. A FPGA must be utilized

- 2. The GNU Compiler Collection (GCC) tool-chain should be supported

These requirements fixes the more loosely defined tasks. As the tasks left us with a great deal of freedom of choice, some overall factors were decided upon to guide in the decision making. Table 1.1 succinctly summarize the key decisions made.

From the outset we decided to opt for choices which were time-saving to implement, but still generic enough to be considered a suitable first architecture for design space explorations in both hardware and software. Also, to enable easy future extensions of the framework, modularity were considered a crucial factor when finalizing the requirements. For the same reasons the novelty of our architecture has been given a low priority so novel ideas were only brought to completion whenever it was considered the more time-efficient alternative. E.g. when implementing atomic hardware operations, in the choice between adding cache-coherence (the conventional way) and creating our own solution, the former option was discarded as it was considered too time-consuming.

Task T1 asks for multiple processor cores. We choose to fulfill this aspect by using a simple core as one of the two core designs required and then modifying this with new features to provide the second design. Modifying the core to exploit more ILP was considered to daunting for our given time budget. For instance, adding support for speculative execution would require substantial redesign of an already functioning processor pipeline, incurring regression test costs in addition to the already high costs associated with complex logic. Instead we choose to add a floating point accelerator to the design whose complexity is contained within itself.

Seeing as how the assignment tasks us to make a framework and not a complete processor design from scratch, we opted for the simple core design to be a third-party component. This was in part a consequence of our wish for supporting the GCC toolchain for easy software development. Since supporting GCC meant we had to implement a GCC supported ISA fully we would rather use a third-party design and use the time saved to focus on the overall framework.

Additionally, the core design should allow for modifications so adding an accelerator is possible. This meant we would not be using Xilinx IP from our development environment. MIPS Technologies provides complete cores, but since these are not free this was not considered an option. Instead we focused on finding suitable designs on OpenCores[12].

To evaluate third-party modules we assume that we can find suitable and working designs without too much effort wasted. Also, while using freely available modules for the more complex parts such as the cores and accelerator should allow us to focus on the integration and the overall architecture, there is a trade-off. Time and effort have to be redirected to learning these modules, possibly extending them to meet our requirements and tailor them to fit in the design. Even so this was considered a less time-consuming approach than to write and test similar modules from scratch ourselves.

An added benefit from using open sourced third-party modules is that its maintenance becomes a collective endeavor of the original authors and its users. A drawback from this is that any modifications done on the module by our part which are for internal use only and not patched upstream must be regression maintained when updating from the third-party. This effort is considered small in comparison to full maintenance, so all in all this should free resources for the users and maintainers of our framework.

When considering the requirement for a scalable interconnect, two designs were found suitable. One is a mesh based approach where each tile is connected to a neighbor on each side of itself. This is a very conventional and tried-and-true approach. The second approach is tree-based and works by dividing memory space according to the relative height of leaf nodes (i.e. tiles) in the tree. The tree-based approach, albeit interesting, was discarded in favor of a known to be reliable and seemingly simpler mesh-based design. An especially compelling reason for settling on the mesh approach is that it is deadlock free if using well-known routing strategies.

Even though the possibility for a multitude of different designs is available with a modular tile approach, for this thesis some constraints were enforced to aid and simplify the total system. The most considerable is the decision to focus on a single ISA. Even though the SHMAC architecture does not restrict the addition of cores using different ISAs, it would require inter-ISA adaptations not currently implemented. For instance, mechanisms to keep the memory space consistent with regards to endianness would be needed. The complexity introduced with these adaptions, combined with the run-time system challenges, were considered too large a work burden. Support for such a system were not needed by the research group and by constraining on the number of ISAs supported, requirements such as supporting the GCC tool-chain also becomes more feasible.

### **1.3** Main Contributions

This thesis gives a flexible and highly modular framework for heterogeneous multi-core processors, focused on being easy to expand and improve so it can be used for rapid prototyping. The resulting framework consists of the following contributions.

#### Hardware

- C1 A mesh interconnect with a uniform router interface both internal and external to tiles. Enables encapsulation and modularity

- C2 An integer tile as a basic core

- C3 A floating-point accelerated tile as a advanced core

- C4 An implementation of atomic locking in processor hardware without the use of a cache subsystem

- C5 An atomic lock tile to support C4

- C6 A technique called the jump tile to correctly bootstrap the different tiles in different parts of the memory space

#### Configuration/debug system

- C7 A configuration system to setup different processor layouts and coordinate the hardware and software components accordingly

- C8 Support for GCC using C7 with custom linker script and mechanisms to support shared symbols between cores

- C9 A communication tile for external memory access and to control execution

- C10 Support tiles such as clock tile for timing, led tile for debugging and ram tile for extending memory is also provided

#### **Run-time system**

C11 A mutex library utilizing the atomic locking enabled by C4 and C5

C1 answers task T2 as both processors and memory is contained within tiles and C1 constitutes an interconnect between tiles. Contributions C2 and C3 fulfills the requirement for multiple cores as required by task T1. Task T3 is handled by contribution C9. The rest of the listed contributions are functionality and aspects of the framework considered by us to have significant worth for users.

Throughout the thesis, multiple design opportunities and improvements outside our scope have been located and since documented in this thesis. We mention this briefly here even though it should not be considered a main contribution. On the other hand, as heterogeneous processing is an ongoing research topic, these remarks and observations are of interest, especially when considering that the delivered framework will be put to use in active research.

In addition we have created microbenchmarks which tests the memory access performance. Benchmark showing parallel performance and relative speedup is also included.

## 1.4 Report Outline

The rest of the report is organized as follows:

Chapter 2, Background, introduces the theoretical basis for the implemented architecture, in addition to a broader basis needed for understanding the different challenges arising when designing an Heterogenous Multicore Processor (HMP). This chapter will also include theory about programming models useful for these architectures. Chapter 3, The SHMAC, gives an overview of the implemented architecture. Here we present a top-down view of the system, the tile concept, its interconnect and memory system. Finally the programming model, configuration and run-time system is also described.

Implementation details for hardware is given in Chapter 4, Detailed Design. This presents the different tiles and their inner workings, including the different cores' implementations and basic units such as the interconnect switch and routing. Software implementation is given in Chapter 5, SHMAC Software. Chapter 6, Verification, gives methodology and test strategy for verification of the design.

Chapter 7, Results, lists the results from this work. This includes microbenchmarks showing memory access performance, parallel performance for the processor and synthesis time for the design. Chapter 8, Discussion, compares the obtained results with the requirements of this thesis with regard to programmability, scalability and performance and examines the merit of our contributions, as well as pinpointing possible improvements to shortcomings identified during our implementation and discusses alternative designs. Concluding remarks and outlined future work is given in Chapter 9, Conclusion.

## Background

This chapter gives the theoretical background needed for this thesis. This includes a brief introduction to analytical models, design of multi-core processors, scheduling algorithms and routing algorithms. Our main focus is on heterogeneous multi-core processors, but as a natural part of this discourse we will also consider homogeneous multi-cores.

## 2.1 Analytical Models of Computer Systems

#### 2.1.1 Amdahl's law

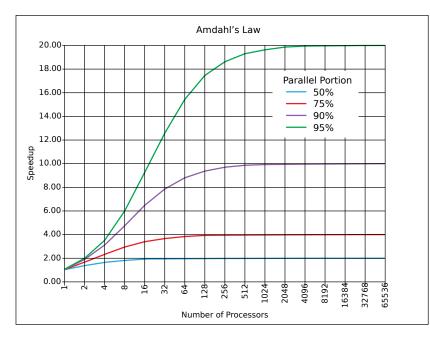

Amdahl's law states that the upper bound on the parallel speedup for any application is given by 1/(1-p), where p is the fraction of the program that can be run in parallel [13].

This assumes that the fraction is independent of the size of the problem that is solved, while this is not necessarily so. By relaxing the assumption, Gustafson comes up with a more optimistic result regarding maximal speedup. The two can be combined as equation 2.1 [4], when assuming homogeneous cores:

$$S = \frac{N}{\frac{s(N-1)}{s + \sqrt[n]{N(1-s)} + 1}}$$

(2.1)

This equation gives speedup, S, with regard to serial fraction, s. n = 1 is equal to Gustafson's law, while  $n = \infty$  is equal to Amdahl's law. A plot showing this is given in Figure 2.1.

In reality, maximum speedup for a program will be somewhere in between Amdahl's and Gustafson's law and the value of n will be application specific. Both Amdahl and Gustafson tries to express how the critical path of a program limits maximal potential speedup.

Figure 2.1: Plot showing maximal speedup for an application given its parallel portion. (Reproduced from [14])

Hill and Marty [8] describes maximal parallel speedup with respect to the software fraction that is parallelizable (f), number of cores (n) and the performance of it's cores. The equation assumes that one core is used to execute the sequential part with a performance perf(r).

$$Speedup_{symmetric}(f, n, r) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f \times r}{perf(r) \times n}}$$

(2.2)

$$Speedup_{asymmetric}(f, n, r) = \frac{1}{\frac{1-f}{perf(r)} + \frac{f}{perf(r) + n - r}}$$

(2.3)

With heterogeneous processors it may be possible to use high performance cores to increase efficiency on sequential tasks while still being able to exploit parallelism. This can be done by reducing execution time of the critical path of the program. Optimal execution of a program therefore utilize all processors in such a way that all resources are dispatched in the order to make the program's critical path as short as possible. If all cores are equal (homogeneous cores), a work intensive task will not be given more resources than any other task. If the other cores must idle during such work intensive tasks then the resources could have been spent more efficiently.

#### 2.1.2 Pollack's Rule

Pollack's Rule states that microprocessor performance increases due to micro-architecture advances is roughly proportional to the square root of the increase in complexity [15].

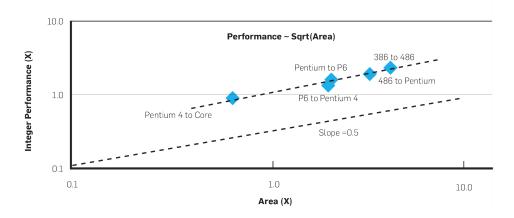

Figure 2.2: Integer performance with regard to area. (Reproduced from [7])

Figure 2.3: Examples of architectures with different complexity, showing performance with regard to complexity.

Figure 2.2 exemplifies this with a plot of integer performance versus area for a selection of processors.

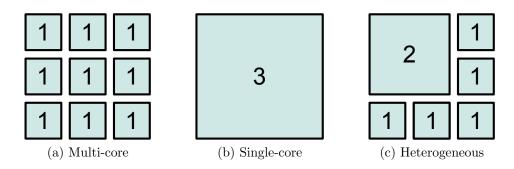

An advanced core using nine times the resources as a simple core, would according to this rule give three times the performance as illustrated by Figure 2.3. Figure 2.3a shows a multi-core processor with simple cores having a complexity and performance of 1, while Figure 2.3b shows an advanced core with a complexity of 9, which according to Pollack's rule obtains a performance of  $\sqrt{9} = 3$ . Figure 2.3c shows a heterogeneous architecture with one core with complexity of 4 and performance of 2 in addition to simple cores. The exact distribution of resources used for the advanced core versus the simple cores is set arbitrary for illustration purposes, as the optimal distribution would depend on the type of applications this processor is expected to run.

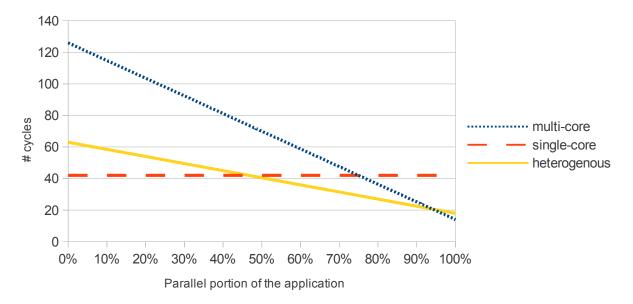

Table 2.1 shows execution time (number of cycles) for one single-threaded and one perfectly parallel program doing the same amount of work. From these extremes the generalized view is that assuming the program contains enough parallelism it will be ideal to let it run on many small cores instead of fewer advanced cores. For the sequential single-thread example, i.e. there is not enough parallelism within the program, most cores would be idle and an advanced super-core would utilize resources better. As can be seen from the table, if the program's parallel portion is e.g. 80 % then a heterogeneous approach is preferable.

Figure 2.4: Run-time example for various processor architectures showing execution time versus parallel portion of the application

Heterogeneous processors is a combination of the two extremes outlined above. It allows sequential parts such as execution start-up to be run on a super-core. Keeping Pollack's rule in mind, the parallel parts would be run on a multitude of simpler cores. Execution time is given by sequential run-time  $\times (1 - f)$  + parallel run-time  $\times f$ . These calculations are only a rough estimate and omits important aspects such as memory interfaces, caching and more.

Table 2.1: Run time example for different processor architectures, where the parallel portion of the program is given as f.

| Program                         | Work              | Multi (                                 | Core                    | Single                                  | Core                 | Heterog                                 | geneous                |

|---------------------------------|-------------------|-----------------------------------------|-------------------------|-----------------------------------------|----------------------|-----------------------------------------|------------------------|

| sequential parallel $f = 80 \%$ | 126<br>126<br>126 | $\frac{\frac{126}{1}}{\frac{126}{9}} =$ | $126.0 \\ 14.0 \\ 36.4$ | $\frac{\frac{126}{3}}{\frac{126}{3}} =$ | 42.0<br>42.0<br>42.0 | $\frac{\frac{126}{2}}{\frac{126}{7}} =$ | $63.0 \\ 18.0 \\ 27.0$ |

From this simple example it can be observed that the sequential parts of a program can significantly slow down overall performance, as shown by Amdahl [8]. For our example the heterogeneous core will outperform the single core processor even if when only half the program can be parallelised. In the same example the multicore will only be faster when the program is close to absolute parallel, as shown in Figure 2.4.

Also, the optimal distribution of advanced versus simple cores and the amount of resources allocated to each advanced core will be application specific. This is dependent on the amount of sequential work in the applications [8]. It is important to keep in mind that there may be parts of the program with different degrees of parallelization such that one could benefit from having more than one super-core. For example if some parts of the program only have a few threads while the rest is embarrassing parallel.

## 2.2 Chip Multiprocessors

Figure 2.5: ILP available in a perfect processor for size of the SPEC92 benchmarks. (Reproduced from [1, p. 157])

Lately there have been a shift from focusing on increased single-thread performance, mainly driven by exploiting ILP and increasing clock frequency, to maximizing throughput by using multi-core processors.

There are three primary factors that have led to this shift:

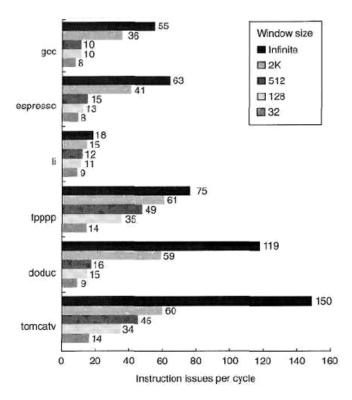

- The ILP wall To keep increasing frequency, processors needs to find enough parallelism in a instruction stream demands reordering instructions and advanced techniques to keep the processor busy. This requires speculative executions with complicated, dynamically-scheduled processors [16]. Even with these advanced techniques, finding enough parallelism to keep a high-performance processor occupied is hard. Figure 2.5 lists the available ILP for six of the SPEC92 benchmarks, where the last three benchmarks are loop-intensive floating-point programs. This figure shows that even if there is a lot of available ILP, not all of this can be exploited due to limitations in window size (as shown in the figure) for finding ILP, imperfect branch and jump predictions and finite number of virtual registers [1, p. 154].

- The power wall Power consumption is proportional with frequency, and depending on the cooling system, power can become the limiting factor for the maximum obtainable single core performance [4].

The memory wall There has been a growing disparity of the processors performance and the main memory latency [17].

One of the greatest challenges this shift have brought is increased complexity for application development as exploiting all available resources requires the software to be written with parallelism in mind.

#### 2.2.1 ILP focused CMP

ILP techniques exploit the inherent parallelism between instructions. Several instructions can be executed simultaneously (super-scalar) or multiple instructions' can be in-flight at different parts of the pipeline at once. One example of a processor utilizing these techniques is the Pentium 4, which includes massive out-of-order execution, deep pipelines and advanced branch prediction [18].

Hennessy and Patterson [1, p. 67] lists loop-level parallelism as the simplest and most common way to exploit ILP, that is to exploit parallelism among iterations of a loop. One example of code inheriting this parallelism is given in Listing 1. Each N iteration is independent, allowing them to run in parallel. This is typically exploited by either allowing the compiler to create vector instructions utilizing the Central Processing Unit (CPU)'s SIMD unit, by loop unrolling or in more advanced processors let the out-oforder unit handle loop-level parallelism automatically. Since it may be costly to flush a deep pipeline, many processors reorder instructions to avoid running instructions with dependencies at the same time.

| Listing 1 Loop-level Parallelism         |

|------------------------------------------|

| for (int i=0; i <n; ++i)<="" td=""></n;> |

| x[i] = x[i] + y[i];                      |

Very Long Instruction Word (WLIW) processors are designed to exploit ILP without adding much complexity, with the motivation that single instructions does not use all of the processors resources. In these processors, instructions are bundled. A bundle is a fixed number of instructions which can be executed simultaneously. For instance that one multiplication instruction and three addition instructions can be done in parallel and can therefore be added to the same bundle. These families of architectures is popular in embedded systems.

#### 2.2.2 TLP focused CMP

Sun Microsystem's UltraSPARC T1 (Niagara 8 Core) is an processor which focuses on maximizing Task Level Parallelism (TLP) instead of ILP. This design opts out on techniques such as multiple instruction issue, out-of-order issue and aggressive branch prediction. This allows for keeping each core simple which increases the number of cores that may fit into a chip [19].

Figure 2.6: Tile concept with CPU, cache and router. (Reproduced from [11])

It is a barrel processor support 32 threads and switches thread each clock. If a thread is waiting for memory it is simply skipped. With this architecture the processor may operate efficient even when threads are waiting for memory, reducing the need for advanced caching.

Another processor type focused on TLP is Graphical Processing Units (GPUs). This is however a separate unit giving rise to significant latency when copying data to and from the unit.

#### 2.2.2.1 Tiled Chip Multiprocessors

The term Tiled Chip multiprocessor was introduced in 2005 by Zhang and Asanovic [11]. The main idea introduced is to create a regular structure of modular processing cores named tiles. These tiles are replicated throughout the chip and connected using an interconnect. Figure 2.6 shows, that by using replicated cores, one may create a less error prone architecture, as each core may be simpler and tested independently.

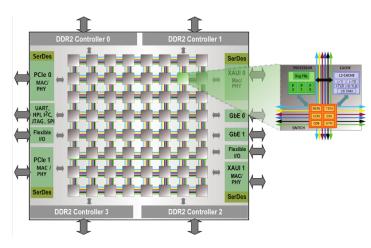

Tilera is currently shipping processors with up to 100 cores. The TILE-Gx100 processor family has an operating frequency of 1.5 GHz and typical power usage of 10 to 55W. I.e. both power and frequency lower than for typical state-of-the-art server processors. This processor includes in addition on-chip hardware accelerators for encryption and compression.

A paper by Facebook and Tilera shows that for a tuned version of Memcached "a *TILEPro64-based S2Q server with 8 processors handles at least three times as many transactions per second per Watt as the x86-based servers with the same memory foot-print*", and had a performance advantage many times higher than Intel XEON and AMD Opteron processors [20].

Figure 2.7 shows that this family of processors uses multiple copies of the same core interconnected with a mesh using packet switching. Each tile consists of a processor with L1 and L2 cache, in addition to a non-blocking switch. Each processor is connected with a two-dimensional on-chip mesh network.

To provide more deterministic throughput several parallel meshes are used with different transaction types. To keep communication latency low and scalable bandwidth, more

Figure 2.7: Overview of the TILEPro64<sup>TM</sup> processor. (Reproduced from [21])

parallel networks could be added as the number of tiles increases. In order to keep power efficiency high, idle tiles can be set to a low-power sleep mode [21].

#### 2.2.3 Heterogeneous Chip Multiprocessors

A heterogeneous multi-core architecture is a Chip Multiprocessor (CMP) composed of cores with different properties regarding size, performance and complexity and different functionality such as cryptographic accelerators or video decoding.

As the heterogeneous processor consists of both simple cores and more powerful cores, it combines the power of efficient parallel performance of multi-core processors without neglecting sequential performance.

Kumar et al. [22] shows through simulation that their heterogeneous multi-core design has the potential to increase energy efficiency by a factor of three. This work shows that most energy efficiency can be obtained even when using as few as two cores. The simulated processors are reusing four different Alpha cores, with different complexity and power usage. Minor differences between the cores are handled by using either the least common denominator of the supported ISAs or by using software traps.

## 2.3 Software for Heterogeneous CMPs

Frameworks such as Compute Unified Device Architecture (CUDA) and OpenCL are specialized for Single Instruction, Multiple Data (SIMD) operations by utilizing GPUs. These are languages which requires that the programmer reason about the architecture. They may therefore be best suited when the parallelism is regular and typically the same instruction should be executed on multiple data.

Topcuoglu et al. [23] suggests that the existing scheduling algorithms for heterogeneous architectures is not generally efficient because of their high complexity and/or insufficient results. Two new algorithms is presented: Heterogeneous Earliest-Finish-Time

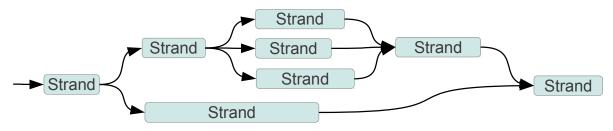

Figure 2.8: Execution model using strands. (Reproduced from [25])

(HEFT) and Critical-Path-on-a-Processor (CPOP).

Directed Acyclic Graph (DAG) scheduling is used in many applications. It uses partial ordering, which can be represented as a DAG. General DAG scheduling is NP-complete, and there have been much research in finding heuristics for this problem. Most of these are, however, targeting homogeneous processors.

The HEFT algorithm selects the task with the highest upward rank at each step and assigns this to the most suitable processor that minimizes the earliest finish time. CPOP schedules critical-path nodes onto a single processor in order to minimizes the critical path length. HEFT is claimed to outperform all other tested algorithms, but also CPOP seems to perform better or equal to existing algorithms.

HEFT has been observed to be significantly affected by how weights are assigned to the nodes and edges of the DAG [24]. This study focuses on five heuristics for heterogeneous DAG-scheduling; HEFT, CPOP, Dynamic Level Scheduling (DLS), Fastest Critical Path (FCP) and Levelized-Min Time (LMT). Sakellariou and Zhao [24] suggests using an hybrid approach for DAG scheduling by reducing the problem to smaller sub-problems for scheduling independent tasks, leading to their Balanced Minimum Completion Time heuristic.

TBP is a form of parallelization, focusing on parallelising tasks in contrast to ILP and data parallelism which is much used in most modern processors using SIMD-instructions and automatic reordering by the processor.

Using the definitions from  $Intel \odot Cilk^{TM}$  Plus, a strand is a sequence of instructions without any spawn or sync points. A spawn occurs where one strand ends and begins two new ones, and a sync ends one or more strands and starts a new strand. All new strands can be run in parallel with each other.

All strands of a programs execution can be seen as a DAG, where spawns are viewed as outgoing edges and syncs as incoming edges. This is shown in Figure 2.8.

#### 2.3.1 Work Stealing

Optimal DAG scheduling is known to be NP-hard [26]. As the execution of a program may be viewed as a DAG, finding a good online algorithm for scheduling with minimal overhead is important.

Well known implementations of TBP-libraries such as Wool [27] (C) and Intel<sup>®</sup> Cilk<sup>TM</sup>

Plus [28] (C/C++) use an algorithm called work stealing for scheduling work to each processor. This algorithm is designed to minimize the number of times work is moved between the processors [29].

The original paper on Cilk [28] proves that the upper bounds of resources used is:

- **Space** The memory used by a P-processor execution follows  $S_P \leq S_1 \times P$ , where  $S_1$  is the memory usage of a serial execution of the Cilk program.

- **Time** With P processors, the expected execution time is bounded by  $T_P = O(T1/(P + T_{\infty}))$ , where T1 is the execution time by its serial elision.

- **Communication** The expected number of bytes communicated during execution is  $O(T_{\infty} \times P \times S_{max})$ , where  $S_{max}$  is the largest size of any closure.

Even though work scheduling is known to be NP-complete, all these bounds are proved to be within a constant factor of the optimal [28].

#### 2.3.2 Architecture-aware Task-scheduling

The execution time of a program will be bound by the critical path of the application's execution DAG. Both Wool and Intel<sup>®</sup> Cilk<sup>TM</sup> Plus assumes a homogeneous architecture. An heterogeneous architecture can shorten the critical path by allocating task on this path to higher performance cores.

There has been some research on architecture-aware task-scheduling with different objectives, such as minimizing the processors temperature [30], minimize energy usage [31] and maximizing performance [23]. Task-scheduling for heterogeneous processors is a complex problem as the scheduler needs to be able to find a matching between the tasks and cores without significant cost in performance and/or power usage. This still remains an active field of research.

## 2.4 Interconnect

Interconnects is an essential part of multi-core System-on-Chips (SoCs) design since typical workloads utilize communication patterns such as map-reduce and all-to-all. Using a single communication interface between all parts of the system also allows for easy modularization and abstraction. Such networks can utilize both packet and circuit switching, but only packet switching will be covered in this report. The mesh is well-known and is thoroughly analyzed elsewhere.

A mesh arranged in *n*-dimensions with k nodes in each dimension contains a total of  $N = k^n$  nodes. The number of dimensions chosen have an impact on obtained throughput and latency, but to keep wires short and to minimize serialization latency the lowest dimension number that still allows for maximum throughput should be chosen [32]. The number of dimensions may be increased as the number of cores becomes sufficiently large, to allow the interconnect to scale well with regard to bandwidth.

#### 2.4.1 Routing Algorithms

Figure 2.9: The possible abstract cycles and turns in a 2D mesh. (Reproduced from [33])

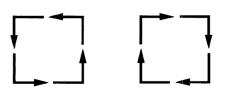

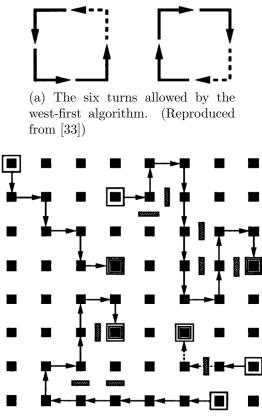

For n-dimensional mesh topologies, dimension order routing algorithms are proven to create deadlock-free routing. These algorithms are very popular, and includes the routing algorithms Turn Model and XY routing [32]. Figure 2.9 shows the eight possible turns for a two dimensional mesh. Dimensional order routing algorithms imposes restrictions on which of these turns that should be allowed to avoid possible deadlocks.

Using a torus instead of a mesh gives the network a smaller diameter, which can improve latency and efficiency in the network. Making a routing algorithm deadlock-free in a torus will however require two virtual channels, in contrast to a mesh where one channel suffices. Utilizing a torus network would require other algorithms than for a mesh and is left as future work [34].

#### 2.4.1.1 The Turn Model

The Turn Model is an deadlock and livelock free routing algorithm, which is adaptive and restricts packets to the shortest possible path [33]. The path between two nodes is determined based on the network load. By disallowing some turns, such that no cycles can be formed, the routing can be done deadlock free [32, p. 268]. Figure 2.10a shows the six turns allowed by the west-first algorithm, which is one of the possible routing algorithms within the turn model. Figure 2.10b gives an example of this algorithm for an 8x8 mesh.

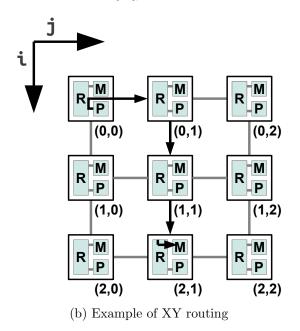

#### 2.4.1.2 XY routing

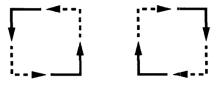

Another, more restrictive, dimensional order routing algorithm applicable for 2D meshes is the XY routing algorithm. Figure 2.11a shows the allowed turns for this algorithm, with an example given in Figure 2.11. This algorithm will route packets in the X direction until it is on the correct column before routing the packet in the Y direction.

This algorithm gives a deterministic routing, where two packets with the same source and destination will cross the same route without considering traffic. There will therefore be no reordering of memory accesses due to routing.

XY routing also guarantees that a packet will, assuming use of a mesh topology, take the shortest possible path in the network, i.e. the Manhattan distance. It does however seem like there is a tendency of accumulation of packets around the center of the network when there is significant traffic [35].

(b) Examples of the west-first algorithm. (Reproduced from [33])

Figure 2.10: The west-first algorithm.

## 2.4.2 Wormhole Flow Control

Cut-through switching is a method for packet switching networks, where the switch start forwarding a packet before the whole frame is received. Wormhole flow control is a form for flit-buffer flow control, which operates like cut-through, but the channel and buffers are allocated to flits rather than packets [32].

Each network packet is broken into a number of smaller packets named flits. When the head flit arrives at a node it acquires a virtual channel, one flit buffer and one flit of the channels bandwidth. Each following flit is routed using this virtual channel until the arrival of the tail flit. The tail flit releases the virtual channel as it passes. Using wormhole flow control the number of lines between each tiles could be decreased, but will lead to higher latency than sending full packets.

(a) The four turns allowed by the XY routing algorithm. (Reproduced from [33])

Figure 2.11: The XY routing algorithm

# The SHMAC

This chapter presents an overview of the processor architecture while the details about the implementation are deferred until Chapter 4.

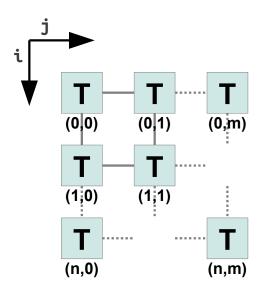

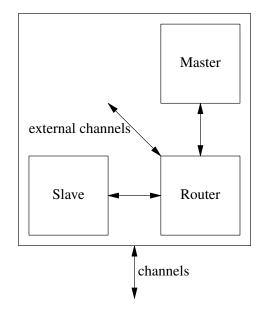

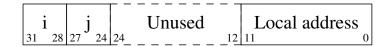

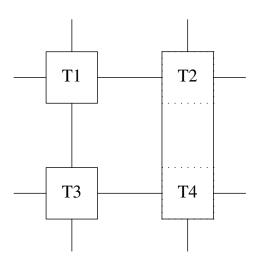

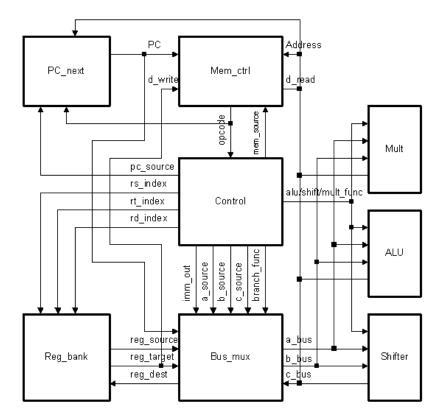

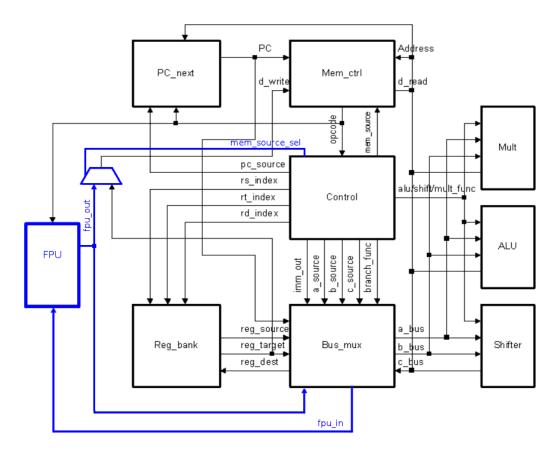

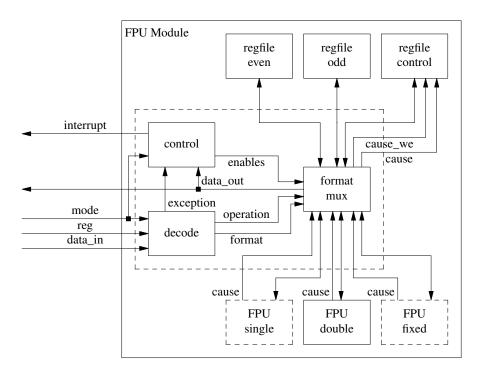

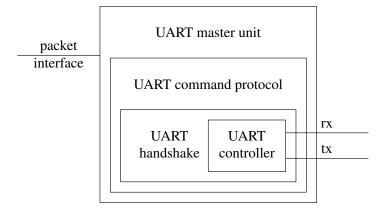

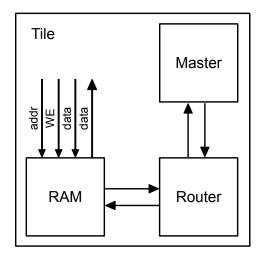

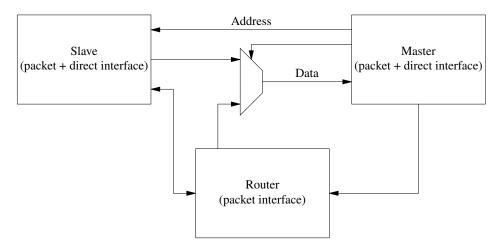

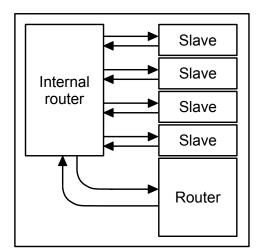

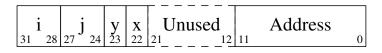

Figure 3.1 gives an overview of the implemented architecture, SHMAC, which consists of a number of independent tiles interconnected using a mesh. Each tile is allocated a subset of the global memory's address space, referred to as its local memory. This makes SHMAC a Non-Uniform Memory Access (NUMA) processor as the memory is distributed and the mesh interconnect access times are dependent on the distance between tiles.