### Databussen i en studentsatellitt

Dan Erik Holmstrøm

Master i datateknikk Innlevert: Juni 2012 Hovedveileder: Gunnar Tufte, IDI

Norges teknisk-naturvitenskapelige universitet Institutt for datateknikk og informasjonsvitenskap

# The Internal Data Bus in a Student Satellite

<sup>by</sup> Dan Erik Holmstrøm

June 2012

Master of Science in Computer Science

NTNU Norwegian University of Science and Technology

#### Abstract

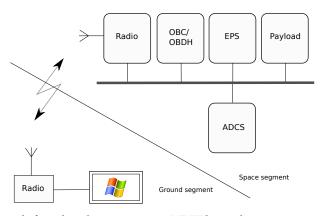

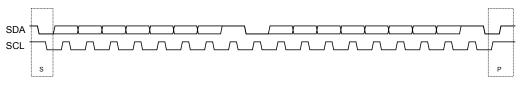

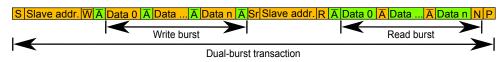

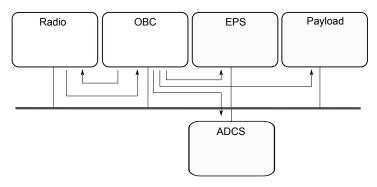

NUTS is a 2U CubeSat, scheduled for launch in 2014. NUTS is being developed at NTNU, and students take part in both the design and the construction of the satellite. Miniature satellites adhering to the Cubesat specification are often composed of separate modules. A data bus is common method for inter-module communication. But being a shared medium, traffic on data buses susceptible to disturbances from failing modules. NUTS uses  $I^2C$  as the bus type. The lack of centralised arbitration poses several challenges with respect fair use of bus time, fault resistance and error recovery.

This paper describes the process of developing a bus protocol for NUTS. The main goals of the NUTS bus protocol is to provide some extent of fairness between the modules, dictate a lower bound on data throughput given certain assumptions, as well as providing a useful abstraction to ease the implementation of higher-level logic. Several support functions are needed to make this possible. This includes defining a system architecture and develop a basic set of drivers required to communicate over an  $I^2C$  bus.

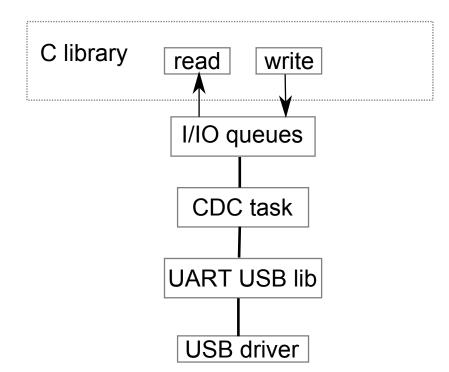

Each module participating in testing of the bus driver implementation, have USB interface connectors. This interface will be used to control the module or modules under test. If any latencies are to have guaranteed bounds, the latency in interrupt processing must be both predictable and constrained. The interrupt processing latency is measured to find out if this can be an issue.

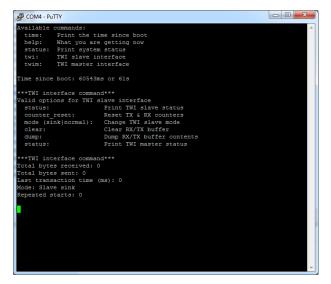

To ease both testing and debugging, a USB interface was used to control the modules under testing. The existing USB stack was extended to provide a separate communications channel, making it possible to provide terminal services and data transmission features at the same time. A design for the NUTS bus protocol is also proposed. To aid the implementation of this protocol, an  $I^2C$  master driver has been developed. A design for an  $I^2C$  slave driver has also been suggested

We find that guaranteeing fair access to a  $I^2C$  bus requires special considerations in both transmitter and the receiver. Fairness is an issue that must be respected at system-level. Variations in the interrupt processing latency when using FreeRTOS suggests that there may be room for improvement.

# Contents

| Acronyms | 5 |

|----------|---|

|----------|---|

| Ι | Ov   | erview and planning                                    | 1  |

|---|------|--------------------------------------------------------|----|

| 1 | Proj | ect overview                                           | 3  |

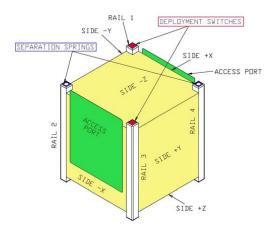

|   | 1.1  | CubeSat specification                                  | 4  |

|   | 1.2  | Project mandate                                        | 6  |

|   | 1.3  | Project background                                     | 7  |

|   | 1.4  | NTNU Test Satellite                                    | 8  |

|   | 1.5  | Problem description                                    | 8  |

|   | 1.6  | Stakeholders                                           | 9  |

|   | 1.7  | Related work                                           | 9  |

|   | 1.8  | Previous work                                          | 9  |

| 2 | Bac  | kground                                                | 11 |

|   | 2.1  | CubeSats in the ANSAT programme                        | 11 |

|   | 2.2  | HiNCube                                                | 13 |

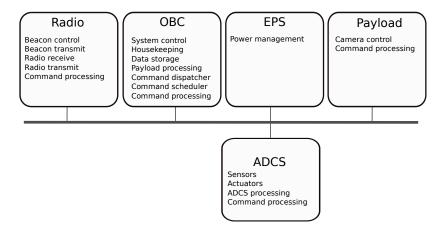

|   | 2.3  | Cubesat satellite subsystems                           | 13 |

|   | 2.4  | NUTS status and project timeline                       | 15 |

|   | 2.5  | NUTS system overview                                   | 18 |

|   | 2.6  | USB standard                                           | 27 |

|   | 2.7  | USB Communications Device Class (CDC)                  | 33 |

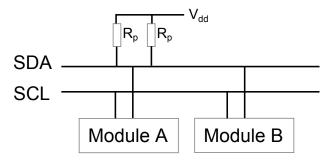

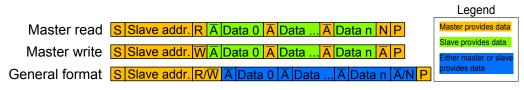

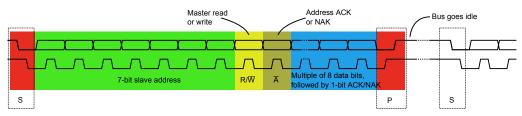

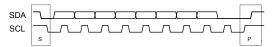

|   | 2.8  | Inter-module communication and the $I^2C$ bus standard | 34 |

|   |      |                                                        |    |

| Π | NU   | TS support functions                                   | 39 |

| 3 | USE  | 3 standard I/O                                         | 41 |

41

xi

|    | 3.1        | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42 |  |  |  |  |  |  |

|----|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|

|    | 3.2        | Current CDC-class device implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |  |  |  |  |  |  |

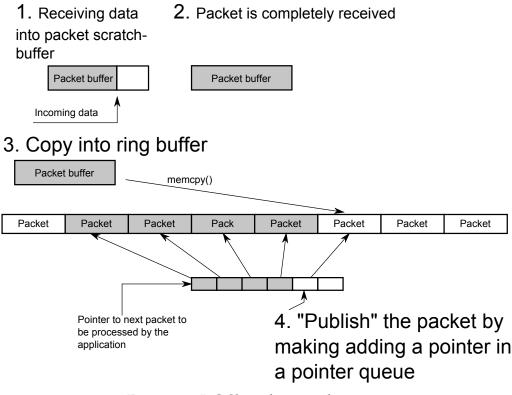

|    | 3.3        | Solution overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43 |  |  |  |  |  |  |

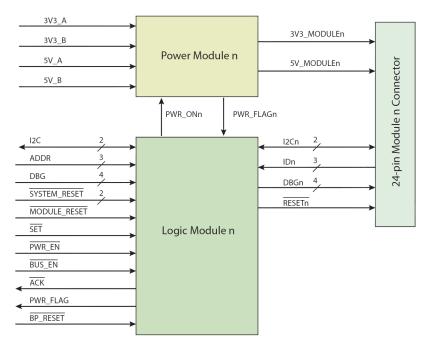

| 4  | Syst       | em architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47 |  |  |  |  |  |  |

|    | 4.1        | Architecture overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47 |  |  |  |  |  |  |

| II | INU        | TS bus protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 49 |  |  |  |  |  |  |

| 5  | NU         | ΓS bus protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51 |  |  |  |  |  |  |

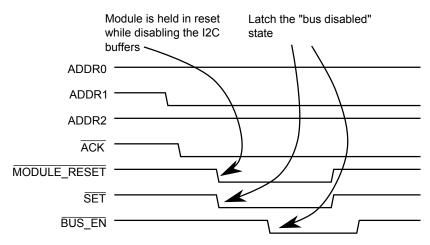

|    | 5.1        | Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 51 |  |  |  |  |  |  |

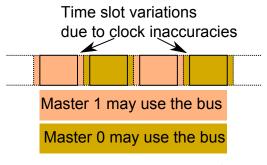

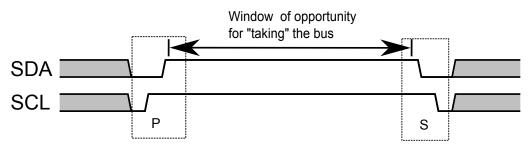

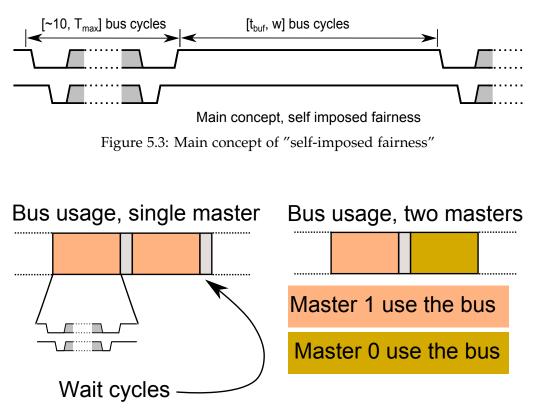

|    | 5.2        | Media access methods and fair data bus access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52 |  |  |  |  |  |  |

|    | 5.3        | NUTS bus protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55 |  |  |  |  |  |  |

|    | 5.4        | Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57 |  |  |  |  |  |  |

| 6  | Inte       | rrupt latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63 |  |  |  |  |  |  |

|    | 6.1        | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63 |  |  |  |  |  |  |

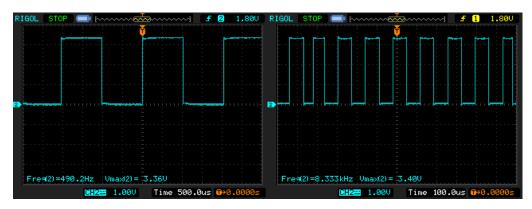

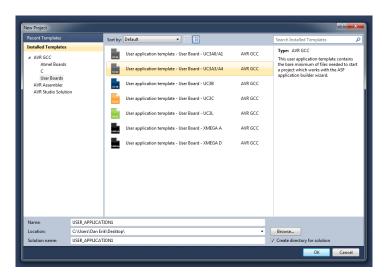

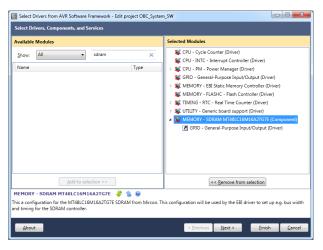

|    | 6.2        | Test environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64 |  |  |  |  |  |  |

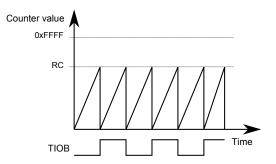

|    | 6.3        | $Experiment \ description \ \ \ldots \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ | 65 |  |  |  |  |  |  |

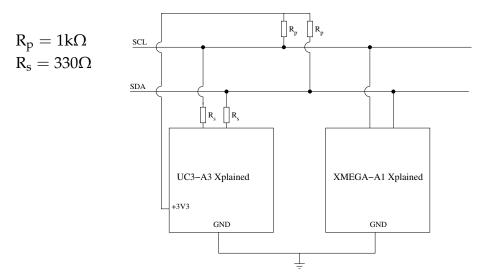

|    | 6.4        | Hardware considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 66 |  |  |  |  |  |  |

|    | 6.5        | Hardware setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67 |  |  |  |  |  |  |

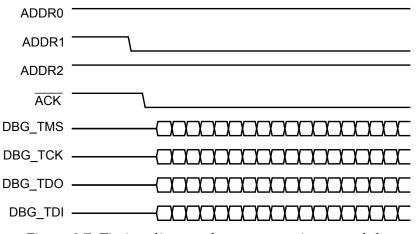

|    | 6.6        | Testing the implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 71 |  |  |  |  |  |  |

|    | 6.7        | The test cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 73 |  |  |  |  |  |  |

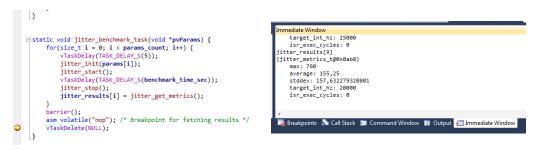

|    | 6.8        | Retrieving the results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75 |  |  |  |  |  |  |

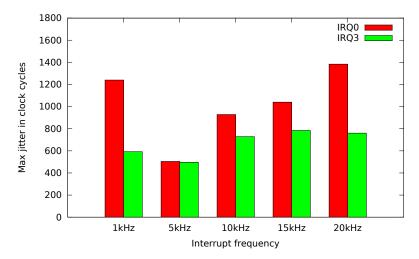

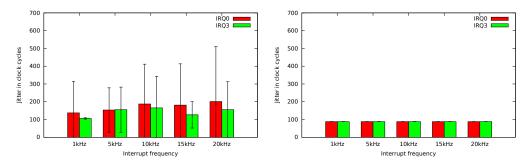

|    | 6.9        | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75 |  |  |  |  |  |  |

|    | 6.10       | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76 |  |  |  |  |  |  |

|    | 6.11       | Implementational notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77 |  |  |  |  |  |  |

|    | 6.12       | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79 |  |  |  |  |  |  |

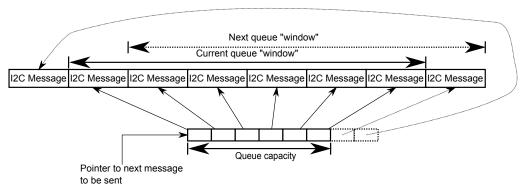

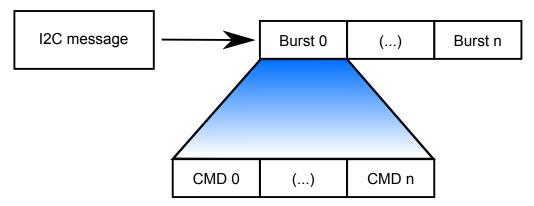

| 7  |            | driver implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 81 |  |  |  |  |  |  |

|    | 7.1        | $I^2C$ master driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81 |  |  |  |  |  |  |