# Enhancing and Porting the HPC-Lab Snow Simulator to OpenCL on Mobile Platforms

Frederik Magnus Johansen Vestre

Master of Science in Computer ScienceSubmission date:June 2012Supervisor:Anne Cathrine Elster, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

# **Problem description**

This project builds on the snow simulator developed by current and previous graduate students at the NTNU HPC-Lab. The work will include porting the code so that it works on current and future mobile platforms. Improved rendering techniques and other enhancements will also be considered.

## Abstract

### English

Porting a computationally demanding CUDA application to a GPU designed for mobile phones and tablets, which supports OpenCL, is the subject of this thesis.

Significant effort is made to prepare the snow simulator of the HPC-LAB at IDI, NTNU, for porting to an OpenCL capable GPU for mobile phones, with a reasonably limited effort, when it arrives. The snow simulator is ported to OpenCL, documented, and improved by considering multiple sorting algorithms, as well as sorting the snow particles.

A thorough study of GPUs for mobile devices and high performance computing, as well as their history is conducted to serve as a background for future porting of the simulator.

The core code resulting from the OpenCL port is documented in detail to prepare for future projects on completing the port to a mobile device.

The OpenCL port of the snow simulator is tested on a range of different OpenCL implementations. The performance of GPUs designed for different use is compared, and memory management is identified as the biggest bottleneck for performance. This bottleneck is further investigated by studying the performance of the simulator when disabling certain copy operations.

OpenCL supports more than just GPU devices. CPUs, Cell processors, and other acceleration cards are also supported. To investigate OpenCL on other devices, a part of the simulation is executed on a CPU, and compared with executing it on a GPU. The CPU version perform on par with the GPU version when using a laptop GPU.

### Norwegian

Porting av en CUDA-applikasjon som krever høy ytelse, til en GPU designet for mobiltelefoner og nettbrett er tema for denne oppgaven.

I oppgaven gjøres det en betydelig innsats for å legge til rette for at snøsimulatoren til tungregingslaboratoriet på IDI, NTNU, med forholdsvis begrenset innsats, kan portes til en GPU for mobiltelefoner og nettbrett som støtter OpenCL, når den blir tilgjengelig. Snøsimulatoren er tilpasset OpenCL, dokumentert og forbedret ved å vurdere ulike sorteringalgoritmer, samt å sortere snøpartiklene.

Som bakgrunn for fremtidige tilpasninger av simulatoren, er det gjennomført en inngående studie av GPUer for mobile enheter, og tungregning, samt deres historie.

Kjernekoden som kommer fra OpenCL-tilpasningen, er dokumentert i detalj for å legge til rette for fremtidige prosjekter, og forberede dem på å gjennomføre tilpasningen av simulatoren til en mobil enhet.

Tilpasningen av simulatoren til OpenCLer testet på en rekke forskjellige OpenCL-implementasjoner. Ytelsen til GPUer som er designet for forskjellig bruk er sammenlignet, og minnehåndtering er utpekt som den største flaskehalsen for ytelse. Denne flaskehalsen er undersøkt ytterligere ved å studere ytelsen til simulatoren, når visse kopieringsoperasjoner er deaktivert.

OpenCL støtter mer enn kun GPUenheter. CPUer, Cellprossesorer, og andre akselerasjonskort støttes også. For å undersøke OpenCL på andre enheter, ble en del av simuleringen kjørt på en CPU, og sammenlignet med å gjøre den på en GPU. CPU versjonen yter på samme nivå so GPU versjonen når den blir kjørt på en laptop GPU.

### Acknowledgements

I would like to thank Dr. Anne C. Elster for supervising this thesis. I would like to thank Jan Rovde for looking at all sorts of strange behaviour conducted by the snow simulator and giving hints of their reasons. Many thanks go to Rune Jensen for looking at my code, helping my back on the right track during debugging and suggesting ways to optimize the simulator. I would like to thank the Norwegian demo scene community at #scene.no at the EFNet Internet Relay Chat (IRC) server for many interesting discussions and viewpoints of mobile GPU computing and the history of mobile phones in general.

I would also like to thank ARM for cooperation regarding mobile GPU access, and NVIDIA for donating the GPUs in the NTNU/IDI HPC-Lab through Dr. Elster's membership in their Professor Partnership program.

# Contents

| Pı | obler                | n description                         | iii          |

|----|----------------------|---------------------------------------|--------------|

| A  | bstrac<br>Eng<br>Nor |                                       | v<br>v<br>vi |

| A  | cknov                | wledgements                           | vii          |

| C  | onten                | ts                                    | ix           |

| Li | st of ]              | Figures                               | xiii         |

| Li | st of '              | Tables                                | xv           |

| A  | crony                | ms                                    | xvii         |

| G  | lossai               | ry                                    | xix          |

| 1  | Intr                 | oduction                              | 1            |

|    | 1.1                  | Goals                                 | 1            |

|    | 1.2                  | Problem description                   | 2            |

|    | 1.3                  | Project description                   | 2            |

|    | 1.4                  | Outline                               | 3            |

| 2  | Mol                  | bile graphics computing units (GPUs)  | 5            |

|    | 2.1                  | The emergence of smartphones          | 5            |

|    | 2.2                  | Phone inspired tablets                | 6            |

|    | 2.3                  | The use cases of mobile GPUs          | 6            |

|    | 2.4                  | Mobile device manufacturing ecosystem | 7            |

|    | 2.5                  | Mobile GPU market                     | 8            |

|    | 2.6                  | State of standardisation              | 9            |

|    | 2.7                  | Open source graphics drivers          | 11           |

|    | 2.8                  | The architecture of mobile GPUs       | 12           |

|    |                      | 2.8.1 PowerVR tile rendering          | 13           |

|    |                      | 2.8.2 Mali tile rendering             | 13           |

| 3 | Gen             | eral purpose computing on graphical computing units 15                  |

|---|-----------------|-------------------------------------------------------------------------|

|   | 3.1             | High performance computing: The road to GPGPU    15                     |

|   | 3.2             | History and benefits of OpenCL                                          |

|   | 3.3             | GPGPU architecture                                                      |

|   |                 | 3.3.1 Programming model                                                 |

|   | 3.4             | Memory model                                                            |

|   |                 | 3.4.1 Synchronization                                                   |

|   | 3.5             | Terminology used in GPGPU                                               |

|   | 3.6             | Debugging                                                               |

|   | 3.7             | OpenCL                                                                  |

|   | 0.1             | 3.7.1 Devices, Context & Command-queue                                  |

|   |                 | *                                                                       |

|   |                 | 5                                                                       |

|   | 20              |                                                                         |

|   | 3.8             | OpenCL versus CUDA    21                                                |

| 4 | Des             | cription of the snow simulator 23                                       |

| Î | 4.1             | History of the simulator                                                |

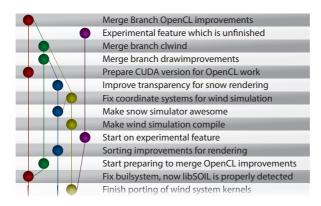

|   | 1.1             | 4.1.1         Code history         25                                   |

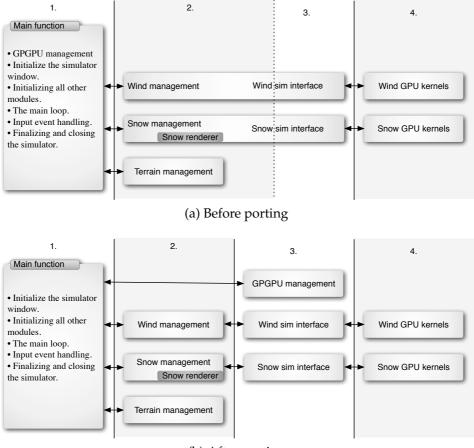

|   | 4.2             | Organisation of the simulator   26                                      |

|   | 4.3             | Simulator flow                                                          |

|   | <b>H</b> .0     | 4.3.1 Obstacles                                                         |

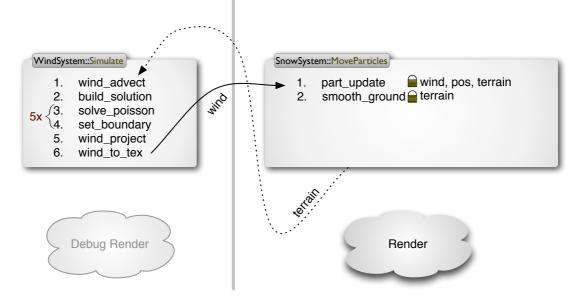

|   | 4.4             | 4.5.1         Obstacles         26           Wind simulation         28 |

|   | 4.4             |                                                                         |

|   | 4 -             |                                                                         |

|   | 4.5             | Snow simulation                                                         |

|   | 4.6             | Porting to OpenCL                                                       |

|   | 4 17            | 4.6.1 Abstracting API specific code                                     |

|   | 4.7             | Calling conventions                                                     |

|   |                 | 4.7.1 Kernel porting                                                    |

|   |                 | 4.7.2 Implementation changes                                            |

| 5 | GPI             | J sorting 39                                                            |

| U | 5.1             | Motivation                                                              |

|   | 5.2             | Traditional sequential sorting algorithms   39                          |

|   | 5.3             | Requirements for GPU algorithms   39                                    |

|   | 5.4             | GPU sorting algorithms   40                                             |

|   | 5. <del>1</del> | Bitonic sort                                                            |

|   | 5.5             | 5.5.1    Previous bitonic sort implementations    42                    |

|   |                 |                                                                         |

|   |                 | 0 1                                                                     |

|   |                 | 5.5.3 Optimizing and adapting bitonic sort for particle sorting         |

|   |                 | 5.5.4 Improving local correctness                                       |

|   | 5.6             | Integration with the snow simulator                                     |

|   | 5.7             | Future improvements to the sorting algorithm    47                      |

| 6 | Tect            | s and results 49                                                        |

| U | 6.1             | Methodology, hardware and implementations                               |

|   | 6.2             | Visualization of the results and statistical method                     |

|   | 0.4             |                                                                         |

|     | 6.3               | CPU versus GPU wind simulation         | 50                                     |

|-----|-------------------|----------------------------------------|----------------------------------------|

|     | 6.4               | Full simulation                        | 51                                     |

|     | 6.5               | Simulation on different GPUs           | 51                                     |

|     |                   | 6.5.1 The NVIDIA Tesla card            | 52                                     |

|     |                   | 6.5.2 The GPUS with display output     | 53                                     |

|     |                   | 6.5.3 Common trends                    | 53                                     |

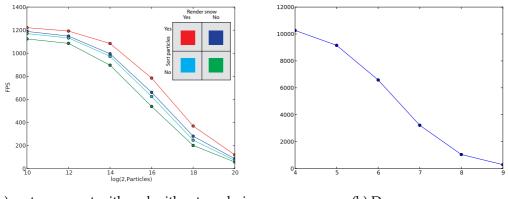

|     | 6.6               | Rendering performance                  | 55                                     |

|     |                   | 6.6.1 Terrain rendering performance    | 55                                     |

|     |                   | 6.6.2 Snow rendering performance       | 55                                     |

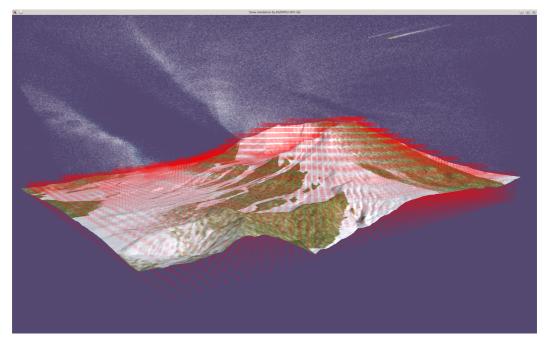

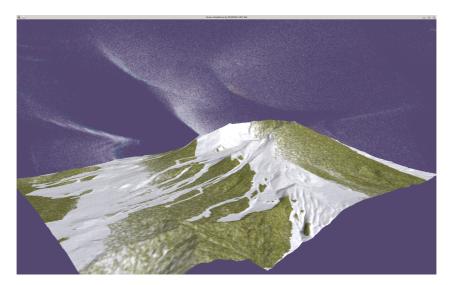

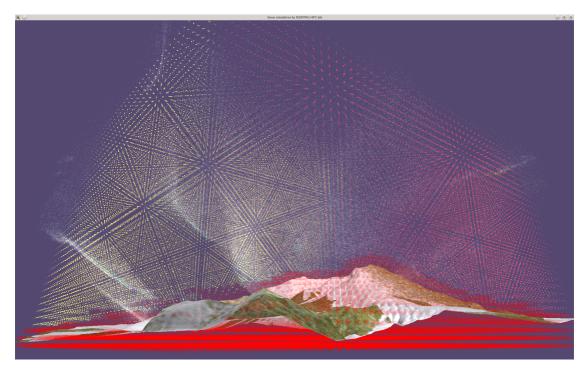

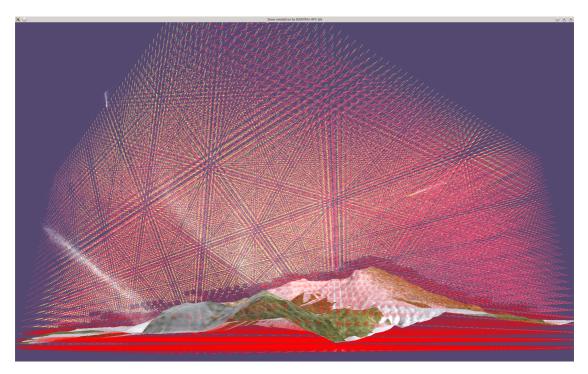

|     | 6.7               | Visual results                         | 56                                     |

|     |                   |                                        |                                        |

| 7   | Con               | clusion & Future work                  | 61                                     |

|     | 7.1               | Conclusions                            | 61                                     |

|     | 7.2               | Future work                            | 62                                     |

| Re  | ferer             | 1Ces                                   | 63                                     |

| 111 | 10101             |                                        | 00                                     |

|     |                   |                                        |                                        |

| Aŗ  | openo             | dices                                  | 67                                     |

| -   | -                 | dices<br>rce Code                      | 67<br>69                               |

| -   | Sou               |                                        |                                        |

| -   | Sou               | <b>rce Code</b><br>Simulation GPU code | 69                                     |

| -   | Sou               | <b>rce Code</b><br>Simulation GPU code | <b>69</b><br>69                        |

| -   | Sou<br>A.1        | <b>rce Code</b><br>Simulation GPU code | <b>69</b><br>69<br>69                  |

| -   | Sou<br>A.1        | rce Code<br>Simulation GPU code        | <b>69</b><br>69<br>69<br>72            |

| -   | Sou<br>A.1        | rce Code<br>Simulation GPU code        | <b>69</b><br>69<br>69<br>72<br>75      |

| -   | Sou<br>A.1<br>A.2 | rce Code<br>Simulation GPU code        | 69<br>69<br>72<br>75<br>75             |

| -   | Sou<br>A.1<br>A.2 | rce Code<br>Simulation GPU code        | 69<br>69<br>72<br>75<br>75<br>75<br>79 |

# **List of Figures**

| 1.1        | Thesis assignment                                                             | 2       |

|------------|-------------------------------------------------------------------------------|---------|

| 2.1<br>2.2 | Mobile device elements                                                        | 8<br>11 |

| 2.3        | Triangles in a tile-grid                                                      | 13      |

| 3.1        | The memory model of GPUs                                                      | 19      |

| 4.1        | Timeline of thesis related to the snow simulator                              | 24      |

| 4.2        | Git version control history DAG example                                       | 26      |

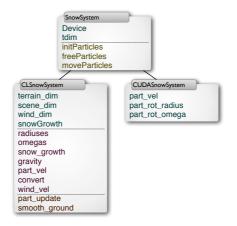

| 4.3        | Organization of the snow simulator                                            | 27      |

| 4.4        | Simulation loop sequence & interaction diagram                                | 29      |

| 4.5        | Obstacles covering the area under the terrain                                 | 29      |

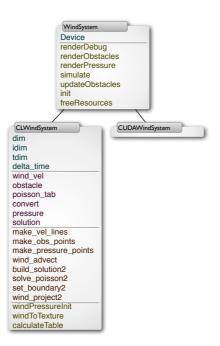

| 4.6        | Wind system classes overview                                                  | 30      |

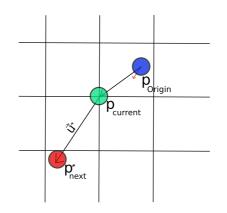

| 4.7        | Self advection                                                                | 31      |

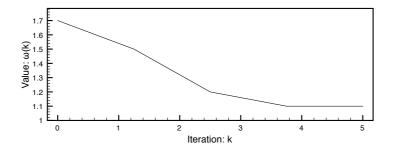

| 4.8        | Values for $\omega(k)$ used in SOR                                            | 32      |

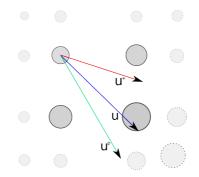

| 4.9        | Schematic overview of wind projection                                         | 33      |

| 4.10       | Snow system classes overview                                                  | 33      |

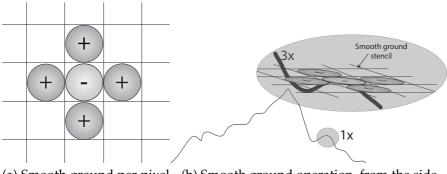

| 4.11       | Smooth ground kernel operation                                                | 34      |

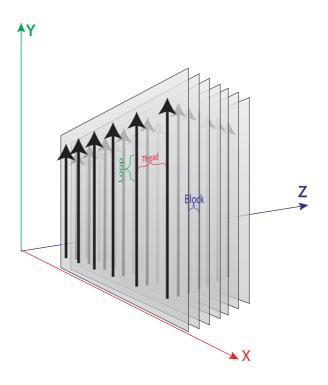

| 4.12       | Kernel memory access strategy                                                 | 36      |

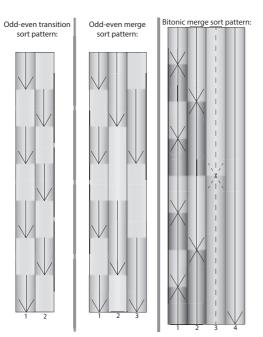

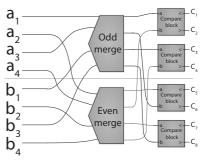

| 5.1        | GPU sorting networks                                                          | 41      |

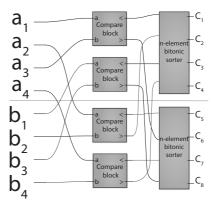

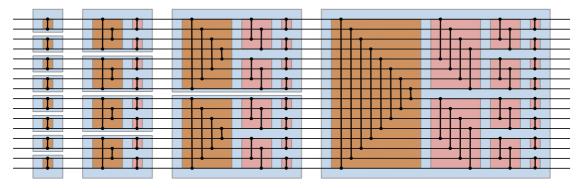

| 5.2        | Bitonic sort network for 16 elements                                          | 42      |

| 5.3        | Local correctness comparision network                                         | 44      |

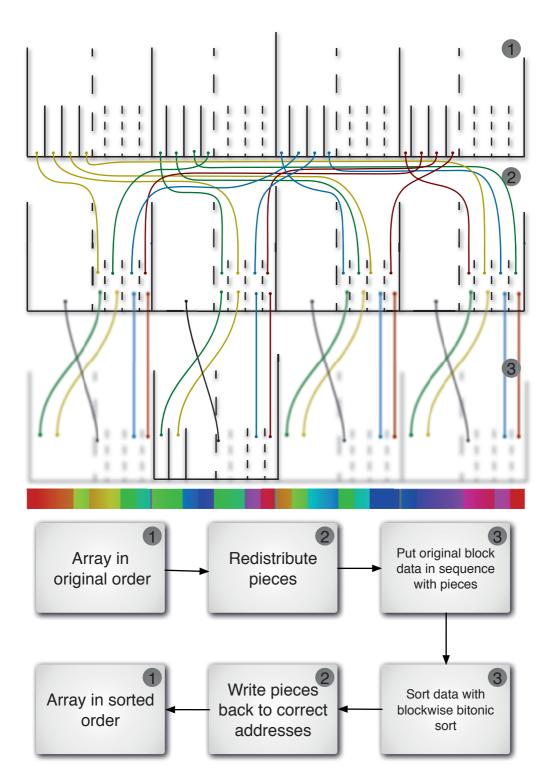

| 5.4        | Redistribution to improve local correctness                                   | 45      |

| 5.5        | Bitonic sort: alternating local sort versus alternating local and global sort | 45      |

| 5.6        | Artefacts caused by changing the index of particles during simulation         | 46      |

| 6.1        | Wind simulation only                                                          | 51      |

| 6.2        | Wind & snow simulation on GPU-CPU                                             | 52      |

| 6.3        | Simulation on different GPUs                                                  | 53      |

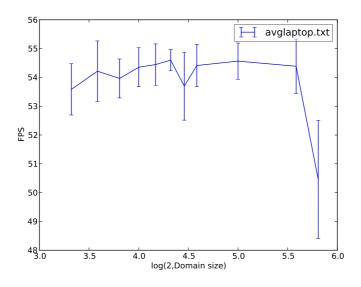

| 6.4        | Laptop wind simulation results                                                | 54      |

| 6.5        | Snow simulation with and without terrain rendering                            | 55      |

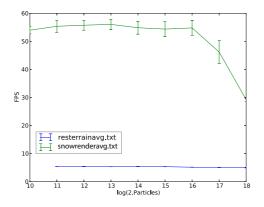

| 6.6        | snow particle rendering                                                       | 56      |

| 6.7        | Snow outside the domain                                                       | 57      |

| 6.8  | Curtain-like distribution of snow         | 57 |

|------|-------------------------------------------|----|

| 6.9  | Pressure distribution                     | 58 |

| 6.10 | Pressure distribution and wind velocities | 59 |

# **List of Tables**

| 2.1 | Leading hardware GPUs for mobiles and tablets                                                                                                        | 9  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Khronos standards applicable for mobile computing                                                                                                    | 11 |

| 3.1 | The most used terminology in OpenCL and CUDA                                                                                                         | 19 |

|     | Specifications of the hardware and software used to test the simulator on CPU Specifications of the hardware and software used to test the simulator |    |

### Acronyms

- **API** Application Programming Interface. 1, 2, 10, 12, 15, 16, 18, 20, 21, 27, 28, 35, 37, 50, 56, 62

- CAD Computer Aided Design. 53

- CPU Central Processing Unit. 1, 7, 8, 10, 16, 17, 20, 23, 49–52, 61

- CTM Close To the Metal. 16

- **CUDA** Compute Unified Device Architecture. 1–3, 15–21, 23, 25, 26, 28, 35–37, 42, 43, 51, 56, 58, 61, 62

- DAG Directed Acyclic Graph. 26

- **DMA** Direct Memory Access. 20

- ES Embedded Systems. 10, 11

- **FPS** Frames Per Second. 50, 51, 53–55

- GLSL the openGL Shading Language. 12, 15, 16, 21

- **GPGPU** General purpose graphics Processing Unit. 1–3, 7, 11, 15–18, 20, 26–28, 35, 50–55, 62

- GPU Graphics Processing Unit. 1-3, 5-13, 15-21, 23, 25-28, 31, 35, 39-42, 49-51, 53, 54, 61, 62

- **GS** Gauss-Seidel. 32

- **HPC** High Performance Computing. 1–3, 15, 23

- **IDE** Integrated Development Environment. xix

- **IDI** Department of Computer and Information Science. 2

- **IP** Intellectual Property. 7–9

- IRC Internet Relay Chat. vii

- **LBM** Lattice Boltzmann methods. 23, 25, 30

- NDA Non disclosure agreement. 12

- NTNU Norwegian University of Science and Technology. 2

- SDK Service Development Kit. 42, 50, 51

- SIMD Single Instruction Multiple Data. 17

- SM Streaming multiprocessor. 17, 35

- SoC System on a Chip. 7-9

- SOR Successive Over Relaxation. 25, 32

- SPMD Single Program Multiple Data. 17, 40

- VBO Vertex buffer object. 28, 30, 37

- VCS Version Control System. 25, 26

### Glossary

- **AMD** Advanced Micro Devices: A semiconductor company that develops computer processors and related technologies for commercial and consumer markets. In 2006 AMD bought ATI, a GPU vendor. 16, 20, 21, 42, 43, 50, 51

- **ARM** ARM: Maker of processor IP with near monopoly for processing in advanced mobile devices. 2, 3, 7, 10, 12, 13

- **Direct X** A graphics API from Microsoft which mainly is used for programming games on the Windows platform. 9

- Git A distributed version control system for code. 2

- **NVIDIA** A semiconductor company that develops GPUs and related technologies for commercial and consumer markets. Currently largest in both markets. 1, 8, 16, 21, 25, 42, 51–53

- **OpenCL** Open Computing Library is a standard specification defining a cross-platform API for functions that are specialized for running on highly paralell hardware, e.g a Graphics Card. 1–3, 8, 15–21, 25, 26, 28, 34–37, 42, 43, 49–52, 56, 58, 61, 62

- **OpenGL** Open Graphics Library is a standard specification defining a cross-language, crossplatform API for writing applications that produce 2D and 3D computer graphics. It is among other things widly used for scentific visualization. 9–12, 15, 20, 28, 30, 35, 50, 52, 53, 55, 56

- Silicon Graphics Inc. SGI was a manufacturer of high-performance computing solutions, including computer hardware and software. Its initial market was 3D graphics display terminals, but its products, strategies and market positions evolved significantly over time. 15

- XNA A quite high level coss platform architecture and Integrated Development Environment (IDE) for writing games on Microsoft platforms. Originally an acronym for Xbox New Architecture, but recently "XNA's Not Acronymed". 9

# Chapter 1

### Introduction

High Performance Computing (HPC) has traditionally been exclusive for large organization with lots of resources. However, computing performance has always been increasing. During the last decades the consumer marked for computers have exploded. Due to the economics of scale, developing hardware for consumers gives better return on investment than developing specialized hardware for demanding professionals. Consumer technology has therefore formed the basis of HPC solutions in the last decade [DSSS05].

General purpose graphics Processing Unit (GPGPU) is the means of using a Graphics Processing Unit (GPU) to perform computation in applications traditionally handled by the Central Processing Unit (CPU). The use of GPGPUs for HPC computing became feasible about 5 years ago with the introduction of a GPGPU Application Programming Interface (API) by NVIDIA called Compute Unified Device Architecture (CUDA). New forms of HPC computing became accessible for the general public as quit cheap GPUs which were originally designed to support computationally demanding graphics in computer games could now be used for demanding physical simulations and signal processing tasks.

The popularity of smartphones and tablets has created strong demand for relatively advanced graphics on those devices too. The programming interfaces of GPUs for mobile phones are inspired by the interfaces for desktop computers, and devices that supports one of interfaces for GPGPU programming on desktops, will be available for smartphones this autumn. The devices for smartphones have different underlying architecture and performance characteristics than desktop devices, even though the programming interface is the same. To gain maximum performance out of the devices, these difference have to be taken into consideration when designing or porting programs for smartphones or tablets.

### 1.1 Goals

The aim of this thesis is to port a computationally demanding program to the GPU of a tablet or mobile phone which supports OpenCL. By looking into porting a program which requires high performance to a performance constrained device insight into how the mobile platforms work, how powerful the platforms are, and what kinds of quirks the they inhibit will hopefully be gained. The HPC lab at Department of Computer and Information Science (IDI), Norwegian University of Science and Technology (NTNU) started to develop a snow simulator in 2006. The simulator as it is today, is a result of several thesis and has been used to experiment with different models for physical phenomena, and do research on how to get maximum performance from GPUs. The simulator already had been tuned for a desktop GPU. It was therefore a good candidate for porting to a mobile device, since the experiences of tuning it to the mobile device can be compared to the experiences from the desktop GPU tuning.

#### 1.2 Problem description

This project builds on the snow simulator developed by current and previous graduate students at the NTNU HPC-Lab. The work will include porting the code so that it works on current and future mobile platforms. Improved rendering techniques and other enhancements will also be considered.

#### Figure 1.1: Thesis assignment

The assignment for this master thesis is quoted in Figure 1.1. The goals for the assignment was suggested by the student, but the final text was written by the advisor. The main focus of the assignment is to port the snow simulator to mobile platforms, getting it working on the platforms, and gather experience from that.

Because mobile platforms which contained hardware necessary to run the snow simulator were not available for the market yet when this thesis was written cooperation with the vendors of the graphics solution was required. The IDI HPC lab at NTNU has contact with ARM which design a mobile GPU which are going to support OpenCL. This thesis, however, was not initiated by ARM. Therefore some uncertainty existed about the feasibility of the project.

#### 1.3 Project description

One of the API which future mobile GPUs will support is OpenCL. The snow simulator was written using another GPGPU API, named CUDA. An earlier student had ported an older version the snow simulator from CUDA to OpenCL a specialization project. The ported code had not been touched in two years, and the simulator has changed much since. Therefore the first part of the project was to get the code up running and up to date with the last changes of the simulator.

A serious effort was done in to obtaining the resulting code from the OpenCL port. However no archived code was found at the HPC lab. Contacting the student who did the port was attempted, but alas no contact could be made. Since the old code was no longer available it was decided to redo the port from scratch using the most up to date simulation code.

To make sure that future students would be able to not experience these problems a proper version control system was introduced, and a group for the whole HPC-lab, including my advisor was created at the servers of the department. The Git version control system was selected to enable students to work with their assignments easily in separate branches; using local repositories if necessary. When each branch is merged at the end of the semester this will produce a common base for future students to work from, and a history where it is possible to see which projects which are included in which version.

Porting the simulator to OpenCL was done in parallel with lobbying to get access to the mobile hardware. The first step of getting access to mobile hardware supporting OpenCL was to do a survey to discover which vendors which were designing OpenCL capable hardware. After browsing the internet for press releases and product specifications 5 vendors were discovered. An application to the ZiiLabs OpenCL Early Access Program was submitted, but did not result in any response.

My advisor did also contact the graphics division of ARM which promised to try to get a Mali sample to work on. The faculty has a good relationship with ARM, which have done several thesis together with the faculty earlier, and even did some thesis in cooperation with the faculty this term. An informal agreement was made to borrow prototype hardware from ARM, but the hardware did not arrive in time to be useful for this thesis.

Even if the hardware necessary for running the snow simulator on mobile targets did not arrive porting of the simulator to OpenCL was continued. When the port reached a runnable and physically stable state attention was divided to focus on optimizing and refining the rendering of the snow simulator.

The development of video game consoles, and personal computers have influenced how high performance computing is done. The research and development cost for new processors like the CELL processor has been divided between scientific HPC use and developing the Playstation 3 game console.

Graphic cards for gaming have surpassed the computing power of the central computing unit of personal computers several years ago. In recent years it has been a revolution in the programming flexibility of graphic cards for personal computers. When tasks are computationally intensive and possible to solve in parallel, GPGPU frameworks such as CUDA and OpenCL are capable of exploiting the performance of the graphics card.

### 1.4 Outline

This thesis falls into three parts. In the first part, Chapters 1 to 3, an outline of the field is presented. The technologies required for the simulator and their history is examined. In Chapter two the motivation for porting the snow simulator to a tablet is presented. The programming interfaces and technical architecture of mobile GPUs are also presented. In Chapter three the history and characteristics of GPGPU is presented. An overview of the differences between CUDA, which the snow simulator is ported from, and OpenCL, which it is ported to, is given to put the port in context.

In the second part, Chapters 4 and 5, the porting, and ways of optimizing rendering is described. The description of the porting is contained in Chapter 4. It description is quite detailed to form a basis for further work by later students. Chapter 5 looks at how rendering performance can be optimized by sorting snow particles on the GPU.

In the last part, Chapters 6 and 7, the simulator is tested and the thesis is wrapped up in a conclusion. Chapter 6 concerns testing to profile the performance and visual results sported by

the simulator. In this Chapter some characteristics of the simulator which could benefit from further optimization is also discovered. At last in Chapter 7 conclusions from this thesis are summarises, and ideas for future work are discussed.

# Chapter 2

### Mobile graphics computing units (GPUs)

This chapter gives an overview of how mobile phones and tablets have became an essential part of the computing experience for end users, and how this has affected the GPUs in these devices. Relevant standards and developments of mobile graphics are discussed. At the end of the chapter an introduction to the architectures of mobile GPUs are given.

#### 2.1 The emergence of smartphones

The Apple iPhone revolutionized the phone marked for end users. It was an evolution of Apples digital music players. Therefore the focus of the phone was not calling but to be a mobile entertainment and communication device. The iPhone came with unlimited Internet usage. It was integrated in to the iTunes store. Small programs called Apps can be bought from the store very easily to extend the phones functionality. However the most important feature of the iPhone was its ease of use and focus on aesthetics, even if it has quite advanced futures. Many users had old accounts for iTunes used for buying music, which lowered the bar for buying Apps to the phone. Advanced Apps which pushed the hardware of the phone to the limits appeared creating demand for phones with even more performance. A web browser capable of browsing normal desktop web pages was also included.

The ubiquity of mobile devices does also open for interaction with the environment which is difficult for a fixed computer. Augmented reality is extending the real world with synthetic elements trough the use of technology. In practise this means capturing a live image of the real world on a camera, and compositing signs, images etc. on top of the image. To do this the image has to be placed in to the model of objects to be composed. This requires substantial processing power. Currently this is only possible for recognition with low frame rates [BOM11].

Mobile gaming is another driving factor for smartphone adaption. Mobiles are good devices for casual games because people always bring their smart phone with them. Smartphone games are much simpler than games for more powerful devices. Therefore they are cheaper to create. This allows more experimentation in game play because the cost of failure is lower. Game development has always been fast to push hardware to the limit, and is a central driver for more performance in mobile phones as well.

### 2.2 Phone inspired tablets

Traditionally tablet computers have been struggling to find a need to fill for the general consumer. They have been very expensive, and the user interface of the tablets was adapted from desktop computers which use a mouse and a keyboard as input tools. User interfaces designed to be operated by a mouse have widgets which require precise placement of the mouse pointer, such as small buttons, sliders etc. To gain the accuracy of a mouse on tablets styluses are required. Styluses however are easily lost, and cumbersome to use. As a consequence tablets based on desktop technology flopped. [JS09] describes the tablet marked, form factor and design goal as it was in 2009.

April the 3rd, 2010 the tablet marked was completely changed by the announcement of the Apple iPad [App10]. It created a mass marked for tablets by expanding the iPhone ecosystem. Instead of scaling down PC user interfaces Apple scaled up the relatively simple user interface used on their smartphones. Relatively cheap components originally made for mobile phones was used to make a more affordable tablet. The tablet was marketed as a hip fashion item.

The iPad was not the first tablet to focus on a simple interface for Internet consumption. Nokia for example released a tablet with the same use case in 2005 [Sha05]. However no integration with a similar ecosystem as the one supported by the iPhone was present.

Tablets and smart phones are also gaining markets from Nintendo GameBoy and Playstation portable, positioning themselves as a replacement for mobile game consoles for casual gaming. The games used for tablets are often quite small, cheap, and fast to make. Therefore a game can be created by one, or just a few persons. This lowers the bar of entry to the marked, and makes it possible to experiment and create innovative gameplay concepts.

Tablets and mobile are also expanding in to professional use cases. Professionals are expressing interest in using these devices in settings where personal computers are viewed as cumbersome and difficult to use. Examples include supporting doctors on a sick bed visit in an hospital, and using mobile phones to collect data from inspections of roads, railways etc.

### 2.3 The use cases of mobile GPUs

The mobile GPU has evolved from displaying simple graphics to do a range of heavy processing functions of visual data on the mobile phone. In this section several use cases of the modern mobile GPU is outlined.

The screen estate of mobile phones and to some extend tablets are very small. Therefore innovative user interfaces are required to use the screen space optimally. This have prompted a redesign of the user interfaces from phones from the ground. These interfaces uses fancy animations to make them attractive for the users. In the beginning the graphics accelerators for user interfaces supported acceleration of 2D graphics; creating smooth gradient, composing transparent images etc.

Movie playback has been seen as a obvious feature for smart phones, partially because it was supported on the iPod, which the iPhone evolved from. A video accelerator was required to enable video playback on a battery constrained device. This hardware has been obsoleted by the mobile GPU.

The demand for games is creating a demand for more processing power to do be able to cope with demanding graphics and effects. Simple 3D games are already supported on modern phones. This has caused mobile GPU's to focus on 3D graphics too.

Most smart phones and tablets have cameras. In the beginning images were acquired straight from the camera and transferred to social media platforms. To differentiate the applications offering these services additional features were included. Simple image processing effects were implemented, filters simulating analogue effects making images look worn have gained popularity. GPU makers have identified this as operations which may be benefited from GPU acceleration. Therefore GPGPU processing have been added to the road maps of nearly all mobile GPU vendors.

The market for tablets and smartphones has grown substantially over the last years, and is expected to grow still. The growing marked has released lots of capital for development of new devices, making tablets and smart mobile phones more powerful than desktops were merely 15 years ago. To keep up with the graphics performance expected of the devices, specialized graphics processors are included. Many different companies compete to create the best graphics processors. The graphics processors are released at horrendous speed, supporting more and more features and programming interfaces for each release.

#### 2.4 Mobile device manufacturing ecosystem

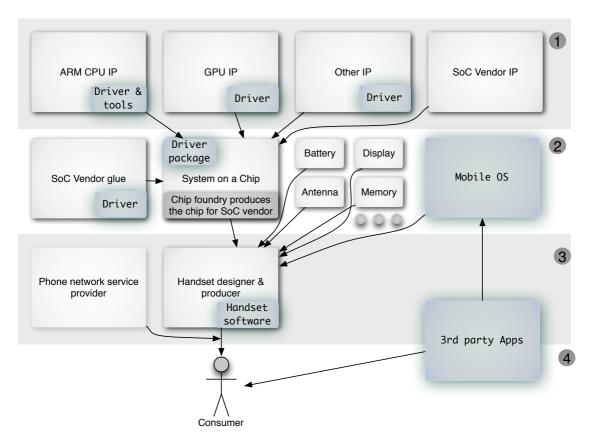

Mobile smart phones and tablets are advanced devices which contains hardware and software produced by many different vendors. The relationships between these vendors are outlined in Figure 2.1. The relationship is split in to 4 horizontal layers along interfaces which are often interfaces between components delivered by different vendors. However some vendors handle all except the topmost layer themselves.

All modern, mobile advanced electronic devices consist of so called System on a Chip (SoC). The SoC integrate the most important functions of the device in to a single chip to reduce the distance between electronic components, and hence the power required to transfer data between the parts of the system. This chip consists of several subsystems. Designing such a subsystem is a extremely complex task requiring substantial work by highly skilled engineers. In addition software, like for example compilers and debuggers, has to be written to interface with the hardware; for example compilers and debuggers. Therefore most companies buy finished designs (called Intellectual Property (IP)), from other companies. Mobile CPU is the prime example of IP being licensed from a specialized firm. ARM is the leading company for supplying IP for mobile device CPUs, having over 95% of the market [Mor11]. Similarly some mobile GPUs can be licensed as IP, while others are only supplied as part of finished SoCs.

A mobile device manufacturer may buy finished SoCs from SoC manufacturers and integrate them into their devices (as in Figure 2.1 layer 3). The mobile device manufacturer designs the complete phone and write software for the phone. The software is based on modules licensed from the SoC manufacturer. In this layer the device producer have to take care of selecting chips and components that can be integrated with the software they want to use on the device.

The operating system for Android phones and tables is provided by Google, but the device manufacturers customise it by adding their special software, and drivers for their hardware.

Figure 2.1: Stakeholders of mobile standardization & elements of a mobile device

App developers interface the operating system of the devices to create apps. The apps are then sold directly to the consumer in a store controlled by the operating system vendor. These developers are partly consumers themselves, partly selling to the consumer market. Therefore they are located between layer 3 and 4 in Figure 2.1.

### 2.5 Mobile GPU market

The mobile GPU marked is a healthy marked with four large competitors. An overview of these competitors is given in Table 2.1. A fifth competitor; Zii Labs does also produce mobile GPUs but no products for end users are available from normal outlets on the Internet. All vendors except NVIDIA have announced roadmaps which claims GPUs with OpenCL support will be released in Q4 2012 or Q1 2013. The vendors of CPUs which uses a IP based business model have finished the IP for GPU models which support OpenCL already. However no SoCs using this IP is quality assured and ready to be released in consumer products at this moment. The IP vendors will not have finished the drivers for the GPUs yet either.

<sup>&</sup>lt;sup>1</sup>Tegra4 rumored to support GPGPU [Val12]

| Vendor          | CL model             | BM  | Hardware examples                              |

|-----------------|----------------------|-----|------------------------------------------------|

| AMD Mali        | T604                 | IP  | SmartIQ, Samsung galaxy: tab 7.7, phones 2 & 3 |

| Qualcomm Adreno | 3xx                  | SoC | HP touchpad tablet, HTC EVO phone              |

| Power VR SGX    | Series 6 [Ima12]     | IP  | iPhone, iPad, Nexus S                          |

| Nvidia Tegra    | Tegra 4 <sup>1</sup> | SoC | Thinkpad tablet, EEE-Pads, Galaxy tab 10.1     |

| Ũ               | 0                    |     | · ·                                            |

Table 2.1: Leading hardware GPUs for mobiles and tablets

#### 2.6 State of standardisation

The smartphone device platform is a quite standardized platform for developers. When it comes to interfacing with the operating system of mobile phones the success of the Apple iPhone created a marked of critical size for apps. Other handset makers answered this by creating a common operating system for their phones. This lead to a big enough marked share for some apps to be released for both platforms.

Lately Microsoft have joined the marked with their Windows based phones. However the number of different platforms is still quite limited for app developers who want to reach all smartphone users. The availability of apps has a considerable influence of whether it is possible for new platforms to survive in the marked. Microsoft did actually pay several companies to create apps for their phone before it was launched, to create a critical mass of apps so that consumers would be interested in buying smartphones with their operating system.

App developers who target smartphones, encounters the same lack of formal standardization of app platforms, as developers targeting the desktop computer market. A few operating systems dominates the market and their interfaces act as de facto standards. This is a typical development of a mature marked where no standards exist. When it comes to mobile GPUs, their programming interfaces mirror the interfaces used on PC's. They are however modernized, and scaled down to fit the needs of mobile devices.

Both Google and Apple use operating systems based on OpenGL on their desktops. Therefore their phone operating systems also use OpenGL. There are several mobile GPU manufacturers, but only two big operating systems have existed on mobile phones. Therefore all GPU vendors have to implement the GPU standards required by the mobile OS manufacturers.

Microsoft however uses their own Direct X technology on the desktop. Therefore the Windows phone operating system does not use OpenGL, but a scaled down version of Direct X with the XNA framework on top to simplify the creation of games. Consequently all graphics code has to be rewritten to interface Direct X or XNA, when ported from another smartphone platform. This may stop some vendors from porting their application to Microsoft phones, if the marked for their application is not believed to be big enough. However code application can be written cross platform for all platforms controlled by Microsoft. This may provide the required marked share for porting applications by tapping into the marked share of desktop users.

Standardization is an important enabler for interoperability between different solutions, and often a sign of a mature ecosystem. Leading vendors will often try to inhibit standardisation to maintain their leading position, and to make it more difficult for competitors to compete with their products. History shows many examples of this. When graphics acceleration solutions were developed for desktop and mainframe markets several different interfaces for the systems

existed. Each vendor would deliver a vertically integrated system from the hardware, with software to the user interface. For external developers several different programming interfaces had to be interfaced. The graphics computer industry continued in this state for many years until smaller vendors started to mimic bigger vendors, and one of the leading vendors (SGI) started to standardize their interface to get a head start with the upcoming standard (OpenGL) [CvDPH98].

Apple computing is the last vendor which continues to produce vertically integrated systems for personal computers. This is possible because they have targeted a niche marked and focused on exclusivity and design instead of price and performance. Apple have gained a substantial marked share among creators of creative content like movies and graphics on desktop systems. In the recent years however they have shifted towards using standardized hardware components, and then assemble finished products. Vertical integration does however limit the number of combination of finished components which simplifies software development and testing of different hardware combinations.

Apple has transfered the recipe used on desktop system to music players, and then mobile phones with the iPhone. This proved to be very successful and positioned apple as a marked leader in mobile phones. The phone did also use standardized hardware components, but the software was tightly controlled, but quite easily extendible with applications (apps). The first major competitor to the iPhone was provided by Google with the Android operating system. The Android operating system counters the tightly controlled iPhone with openness setting an unprecedented standard of openness in the mobile handset marked. This is a classical way to counter tightly controlled marked leading solutions. Several competing manufacturers were collaborating to create a common platform which made programs interoperable between vendors. To differentiate themselves, they included their own branding, applications and hardware.

The development of mobile platforms has been driven by the vendors of the complete systems, not the makers of the underlying technology. The vendors of the complete systems want to be able to change components simply and without changing their code base. For Android support of several different underlying hardware has been essential to the philosophy of their operating systems. This has led to standardization of all hardware interfaces. Hardware component vendors, who do not implement standards, do not stand a chance in the marked. The hardware vendors are forced to compete on implementing the standards as cheap as possible with the highest possible performance, instead of locking each other out with incompatible interfaces. Most of the standards of GPUs are exposed to the programmers of apps for the phones and tablets. For the app programmers being able to use standards increase the number of potential devices can run their code, and hence the marked potential of the apps.

Currently ARM has a near monopoly on the designs of the CPU architecture used in mobile phones. Therefore their instruction set has emerged as a de facto standard for CPU programs on mobile phones.

GPUs and graphics accelerators however are provided by several different vendors who implement the graphics rendering a bit differently. Therefore a common API is presented to the programmers. The first API which was produced was the OpenGL Embedded Systems (ES) [Gro04] in 2004. This API was created by the Khronos Group, which is the proprietor of OpenGL. Soon Khronos released several other specifications for other graphics and media purposes. These standards are listed in Table 2.2.

| Standard name | Description of area                                             |

|---------------|-----------------------------------------------------------------|

| OpenGL ES     | Embedded version of OpenGL 3D graphics API                      |

| OpenVG        | For 2D Vector Graphics to accelerate Flash, SVG & 2D interfaces |

| OpenCL        | For GPGPU processing                                            |

| OpenSL ES     | For music and sound playback and recording                      |

| OpenMAX       | For audio/video-playback, 3 layers: AL, IL & DL                 |

Table 2.2: Khronos standards applicable for mobile computing

Many of these standards are implemented in the majority of GPUs in mobile phones today. OpenGL ES is supported in one version or another on nearly all phones already, OpenVG does also enjoy widespread support on mobile GPU's. OpenCL is announced in future models by several vendors, and OpenMAX is going to be integrated with future Android API's.

#### 2.7 Open source graphics drivers

Traditionally mobile phones have been rather closed devices. After the introduction of smartphones some flexibility has been introduced. However this flexibility has been confined to virtual machines with extensive sandboxing. This is very good for traditional end users which want a phone which can do some fancy stuff, but where no apps can interfere with the basic usage of the phone.

However there have always been enthusiasts who want do improve their products. Hardware vendors guard their trade secrets from competitors, and others by only shipping phones with compiled binary drivers with the phones. This stops enthusiasts from improving the lower layer of the phone operating system. Because the operating systems of smartphones are based on quite open Unix operating systems, which then are locked down some mobile devices, they have been hacked (also called rooted, or jailbraked). A hacked phone can be changed by the user. For Android devices the operating system is based on Linux, which is Open Source. The GPU drivers however are often binary modules without any source available. This hinders optimization of the drivers, and cause incompatibility with newer version of the kernel. Therefore some developers have started reverse engineering the drivers for some mobile GPUs.

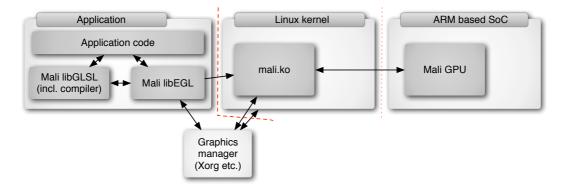

Figure 2.2: Interfaces intercepted by Lima for reverse engineering, based on info from [Ver12]

Currently two projects for reverse engineering GPUs are in development. Both projects are intercepting communication between the driver and hardware to figure out how the hardware works. The most mature project is the Lima driver for ARM Mali GPU's. The project has just demonstrated a working driver for simple OpenGL example scenes consisting of cubes. Figure 2.2 shows how a mobile GPU driver is integrated with the surrounding system on a Linux platform. The red lines symbolizes the interfaces which were monitored during the reverse engineering of the Lima driver. At the moment it looks like most of the focus of the drivers is to implement the openGL Shading Language (GLSL) support for programming the GPU.

The other project created to make open source mobile GPU drivers is named Freedreno. This driver should drive the Adreno GPUs from Qualcomm. 2D acceleration is supposed to work. The driver is created by an employee in the GPU section of Texas Instruments. The employee started his own driver because of fears concerning Non disclosure agreement (NDA)s for the Mali GPUs. Because this project still is young the success of this project is very uncertain.

Open Source Graphics driver does also benefit academic work. Details on how the GPU's work which is difficult to figure out are documented by the driver projects. Even more detail is available by reading the source code produced by the projects. This may for a basis for research in to low level graphics development outside the graphics companies.

The architecture of current open source drivers is driven by a modular approach where reuse is promoted. The common code for GPU drivers is developed as a part of the Mesa [Mes] open source OpenGL implementation by the [WMV] project. The main developers of the Gallium project is currently employed by the visualization firm VMWare which uses the drivers for their visualization solutions.

Because the development of the drivers is not done as part of the marked competition between GPU vendors, it may be possible to enhance the performance of GPUs with less efficient drivers. The reuse of modules does in effect also provide a lower level abstraction of the GPUs than the current standardized APIs. This makes it easier to experiment with other APIs and interfaces. In the Linux world several replacements for the dominating X Window System have been developed over the years. However getting good driver support has always been an issue. Binary drivers which interface with the X Window System cannot be used by replacements, and getting vendors to support experimental projects which produce no benefit for the vendors, is very difficult.

### 2.8 The architecture of mobile GPUs

The architecture of mobile GPUs are quite different from normal desktop and laptop GPUs. This is mainly because of the power envelope each GPU type is designed for. A mobile GPU is designed to run off a small battery and need to use as little power as possible. GPUs for mobiles use very low voltages internally to conserve power. These voltages are too small to be used to drive external buses. Therefore higher voltages have to be used for buses. This means that external transfers are little power efficient. This is the most important premise for the design of mobile GPUs. [AMS08]

Two of the most popular mobile GPUs (PoverVR & Mali) uses a tiling algorithm for rendering [AMS08] [SKP10]. This algorithm has also been used in gaming consoles like the Xbox 360 [SKP10].

Figure 2.3: Triangles in a tile-grid

The tiling algorithms divide the screen in to tiles (of e.g. 16x16 pixels) as in Figure 2.3, with accompanying bins. Each tile is then rendered separately. The tiling algorithm requires less memory, but accesses the memory more often. The memory used in the algorithm is moved inside the graphics chip, as cache memory. This makes it power efficient, as no external bus transfers are required for access.

When a GPU scene is prepared for rendering, all triangles are transferred to the GPU. Then all triangles are transformed to their final positions. Afterwards each triangle is considered, and a pointer is added to the bin accompanying each tile the triangle intersects. The tiles can then be rendered in parallel.

#### 2.8.1 PowerVR tile rendering

The PoverVR architecture is described in an overview [Pow09] and is used as a basis for the description of how each title is rendered.

The first step of rendering a tile is to Figure out which parts of which triangles which are visible. This is done by casting rays at each pixel, by specialized hardware. Afterwards the GPU Figures out which pixels share the same vertex to simplify shading and texturing. The shading and texturing done by PowerVR is very similar to desktop GPUs and was not described in the overview.

#### 2.8.2 Mali tile rendering

I was not able to find detailed documentation of the ARM Mali processor architecture at the ARM web page, but the general optimization guide [ARM11] hinted of a tiling architecture similar to PoverVR. However I found a marketing article [Fal06] from Falanax, the firm which designed Mali before they were acquired by ARM. This article outlines the architecture.

The Mali architecture tries to be a hybrid between (desktop) intermediate mode rendering and tile based rendering, to exploit the advantages of each algorithm. The z-termination algorithm

seems to focus more on efficiency than accuracy, and typically eliminates approximately 50% of the occluded pixels.

# Chapter 3

# General purpose computing on graphical computing units

This chapter concerns general purpose computing on graphical computing units. It is intended to give a basic understanding on how a GPU executes general programs, and how problems have to be formulated to exploit the power of GPUs.

First a short overview of the history of GPUs is given, then modern GPUs are described generally. At last the details of the CUDA and OpenCL APIs are described, and how they differ.

### 3.1 High performance computing: The road to GPGPU

For the real time graphics industry 1992 was the year of standardization. Before that each vendor had it's own proprietary interface. At the time Silicon Graphics Inc. was the leader of the computer graphics market. When the market got more competitive and other vendors started to standardize the competing programming interfaces, Silicon Graphics Inc. opened, documented and standardized it's proprietary API and renamed it OpenGL. In effect this forced all other vendors to do catch up.

Originally graphical computing units were device with a fixed hardware architecture for rendering graphics. No programming of the units where possible. In February 2001 [NVI01], graphics pipelines became much more flexible by supporting programmable shaders. Shaders were made to do advanced lightning and produce more detailed surfaces. They are executed in parallel for each pixel or vertex in the models they shade. This parallelism can be exploited for doing HPC work by rendering the objects to off screen image buffers and sending the buffers back to the CPU.

GLSL [KBR04] which was standardized in 2003 [Boa03], introduced a high level language which made it quite easy to write shaders. GLSL has a syntax inspired by C and functions for doing geometric math functions. In the early days of GPGPU computing GLSL was the language of choice for doing computations on GPUs. Writing general purpose programs using GLSL requires some effort mapping problems into a graphic domain. All information used outside the shading kernels had to be mapped in to 2- or 3-dimensional textures with one or more colour channels. GLSL shaders are split up to multiple passes of the graphics pipeline. Early

programmable GPU used different hardware for each pass. Therefore it was important to split the work between all the passes for optimal performance.

After GLSL started to be used for generic computation the vendors recognized the business potential of GPGPU. In 2006 the GPU both NVIDIA and AMD released solutions adapted for GPGPU programming. NVIDIA even released specialized graphics cards without screen connectors for GPGPU.

AMD wanted to give low level access to their GPUs and released Close To the Metal (CTM) [AMD]. CTM was an assembly-like language for AMD GPUs. Because CTM was very low level it was not used very much. This language is now defunct, and AMD has gone over to supporting OpenCL. NVIDIA released CUDA which is a more high level solution modelled. The language CUDA uses for code executed on the GPU is a combination of a generalization of GLSL and the syntax and level of hardware control characteristic of the C programming language.

### 3.2 History and benefits of OpenCL

The OpenCL standard was developed in 2008. Apple computer wanted to use GPUs in their operating system to increase performance of their systems. Apple has good experience challenging different vendors to provide the cheapest and best components for their computers. It is believed that it is the reason why CUDA was not chosen as the sole solution for GPGPU by Apple.

To standardize OpenCL Apple took the incentive [Mar08] to form a Khronos "Compute Work Group" to standardize OpenCL. AMD and NVIDIA joined the work group from the start. The standard finished very fast, in about 6 months, to be included in Apples operating system. Other implementations, and use outside Apples echo system needed, however, 2-3 years to get reasonably stable. It is still very easy to provoke the need for a reboot of a machine by passing argument which are slightly outside the specification to the drivers.

Even if OpenCL is driven by GPGPU computing and inspired by CUDA, it is designed with more than GPUs in mind. OpenCL is designed to be independent of hardware as long as it is highly parallel, and has quite low memory latency compared to for example clusters.

CPUs for desktop, laptop and mobile computers have also became parallel to increase performance, because heat has made it prohibitive to increase the clock frequencies of the processors. Both of the leading desktop CPU manufacturers provide OpenCL drivers for their CPUs. This means that in a few years, all modern computers will contain an OpenCL capable device. Computers which does not have high end GPUs, will be able to run OpenCL code, with less performance. Therefore no alternative implementations of code optimized using OpenCL is required to run the program even on low end hardware.

The OpenCL specification is also designed to work with state of the art processor architectures designed for high performance computing like the IBM Cell Blade servers. Some enthusiasts have also managed to run OpenCL programs on the Cell processors of a Playstation 3 gaming console, but that became impossible when Sony stopped supporting custom programs on the PS3. This makes OpenCL a very scalable and accessible API available on everything from mobile phones to supercomputers.

## 3.3 GPGPU architecture

In this chapter OpenCL terminology will be used. More information on the terminology and OpenCL versus CUDA terminology is detailed in Section 3.5.

GPUs are designed to do high performance computations. They are not fit do to information bookkeeping etc. Therefore device management, memory management, program allocation and invocation is done at an host processor, together with work not fit for GPGPUs.

### 3.3.1 Programming model

Modern GPUs are highly parallel computers. They can run over 128 different executions concurrently, normal state of the art desktop CPUs can run up to 8. They focus on computations and not logic.

Most programs for CPUs are serial or task parallel programs. These program split problems in to several tasks which are run concurrently, or multiple programs are ran concurrently on different cores for multitasking.

Work groups have common memory which can be accessed faster than global memory and independent of other work groups. This minimizes the speed penalty of synchronization, compared to using global memory. An iterative differential equation solver is a good example of using this organization. The matrix can be divided in to blocks, and then only the borders between blocks need global synchronization.

Graphics synthesis is generally a data parallel problem. The same operation is executed on millions of vertices and pixels. Therefore GPUs are designed to run data parallel programs. This parallelism is exposed to GPGPU programs in the form of kernels. The main idea of kernels is to expose the parallelism of for-loops. Instead of running a loop serially for each element of a problem the looping is managed by the GPU. The inner part of the loop is programmed in a kernel and executed concurrently by the GPU. If the kernel is executed more times than the GPU supports concurrently, the GPGPU framework will schedule multiple concurrent execution passes.

GPU does however need to do some different tasks concurrently. Therefore the concurrent processors are organized in three different levels of parallelism. In the upper level different type of work can be executed with out significant performance penalty.

The upper parallel processing level consists of elements named work groups. All work groups are executed on separate Streaming multiprocessor (SM) which are responsible for executing their group. No synchronization between work groups are available, except by calling a new kernel. The next level is work items. Each work item can operate on different addresses in memory, have separate registers and variables. All work items in one work group runs the same executions (called Single Program Multiple Data (SPMD) in Flynn's taxonomy). Diverging executions, for example produced by if-tests, have to be executed by all work items of a work group. If the instructions are not supposed to be executed by the work item, the result will be thrown away. The last level of parallelism is Single Instruction Multiple Data (SIMD). All GPGPU languages support vector data types, float4 is for example 4 floats in one variable. When doing arithmetic operations on vector data types, all the elements of a vector can be computed in one instruction by parallel electronics in hardware.

## 3.4 Memory model

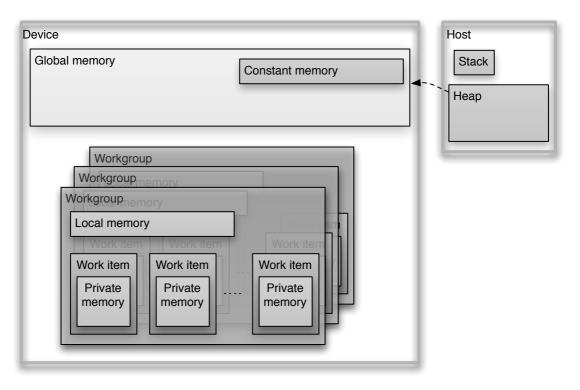

Memory is one of the largest bottlenecks in modern processors. Mass memory is often several orders of magnitudes slower than the processors. Therefore intelligent use of caching and local memory are required to keep the processor running at maximum speed. The memory model of GPUs is adapted to the programming model. It is split in to a complex hierarchy of memory, as illustrated in Figure 3.1, to try to deliver the performance required by modern graphics applications. Each type of memory has it's own characteristics strengths and weaknesses.

The largest memory is the global memory. This memory is designed to hold textures and geometry information for graphics. Therefore this memory is huge (often more than a gigabyte), but writing to this memory from the GPU is quite slow. Management and allocations in this memory has to be done by the host. The host memory is the only memory which is accessible by the host, and the only persistent memory between kernel calls.

The local memory is memory which is coupled to each work group. The size is in the magnitude of 16-64kb per work group. The memory works as scratch memory for the work groups. In OpenCL, the size of this memory has to be known before the kernel is executed. Since the memory only is writeable for the kernel, it has to be initialized from other memory. Often it works as a per work group cache for global memory.

The memory for each work item is split in to two. Each item has a number of registers (e.g. 8 or 16), which are fast, and some overflow memory which is slow. To maintain good speed it is essential to keep the number of variables in a kernel below the number of the registers.

Access to all memory shared by more than one work item is cached. To exploit the caching, programs have to be written in a manner where adjacent memory is accessed at the same time. Sometimes however this is not the case. The main memory of GPUs is divided in to multiple banks. Each banks supports only one read at a time. Therefore the most efficient way to access memory is to fill the width of the memory buses by accessing adjacent memory, but then address memory which is far away and hopefully in another bank.

## 3.4.1 Synchronization

Barriers are used inside a work group to make sure all work items inside the groups have reached the barrier before continuing. If the kernel does not execute the barrier, the result is undefined and most likely the program will not advance beyond the barrier.

If programmers want to synchronize kernels without the work group, they have to make a new kernel call. Barriers can also be used on the host with multiple work queues at the host ensuring that all work queues reach the barrier before continuing.

## 3.5 Terminology used in GPGPU

This section will describe the terminology used in the two leading programming interfaces for GPGPU; CUDA and OpenCL. Two leading programming models for GPGPU is CUDA and OpenCL. The first API to be designed was CUDA. OpenCL was created as an effort to standardize the API across multiple graphics card vendors, and to be used by other types parallel processors too. The OpenCL API is very inspired CUDA. Therefore it is quite similar organized.

Figure 3.1: The memory model of GPUs

| OpenCL          | CUDA            |

|-----------------|-----------------|

| Work-item       | Thread          |

| Work-group      | Thread block    |

| Global memory   | Global memory   |

| Constant memory | Constant memory |

| Local memory    | Shared memory   |

| Private memory  | Local memory    |

Table 3.1: The most used terminology in OpenCL and CUDA

Porting from CUDA to OpenCL is mostly syntax dependent, and very little reorganization of the program is required.

## 3.6 Debugging

Debugging code which runs on GPUs are very difficult, mostly because of the massive parallelism of the code. Some tool kits and tools for debugging do exist. But the support for OpenCL is very new, and immature in many cases. Most of the debugging tools does only debug the outside of the kernels. This can be used to profile which kernels are bottlenecks in the application, but will not give insight into how variables are changed inside the kernels and why memory accessing errors occurs. Some implementations have started to integrate debugging with their GPGPU API implementations. AMD has created a printf statement for it's OpenCL implementation, but this is not portable across implementations. Cross platform support of debuggers are another problem. For example Intel released a debugger supporting step by step debugging in Visual Studio. No Linux support for debugging was mentioned in the release notes. [Int12b]

## 3.7 OpenCL

In this section the OpenCL standard is described in more detail, outlining programming details, and how the architecture of GPUs are mapped to the OpenCL API.

## 3.7.1 Devices, Context & Command-queue

The syntax of the OpenCL API is inspired by the other standards created by the Khonos Group like OpenGL. The C version is quite verbose, but standardized wrappers for more high level languages exist. Multiple devices and device types are supported.

Some boilerplate code is necessary to use OpenCL. At the start of each program, all devices are enumerated and the program asks for a device which matches certain characteristics (type: GPU or CPU, available memory, number of compute units etc.). When the program decides which device it wants to use, it creates a context. The context is used to create command queues and manage memory objects.

The only way a host can order a device to do operations is to submit items to a work queue. To submit an item with the C-API, all parameters have to be pushed by a separate function call. This creates very verbose code compared to CUDA code.

Command queues can be ordered or out of order. If the queue is out of order, the device can reorder elements in the queue to make the execution more efficient. This means that other mechanisms must be used to enforce dependencies.

## 3.7.2 Synchronization

OpenCL features two methods for synchronizing parallel work. Events do global synchronization in a work-queue between kernel and memory-operations, while barriers manage synchronization inside a kernel.

Events are used at the host side to build a graph of dependencies between elements on a work queue. Then out of order execution may be enabled on the queue, which lets the scheduler execute elements in any order (as long as the event graph structure is fulfilled). Memory operations may for example be executed even if a kernel is running, if the Direct Memory Access (DMA) engines used for transferring memory are free.

## 3.7.3 Memory

OpenCL features explicit memory management in the same way as C. Memory may be allocated on a (limited) stack or managed explicitly by using buffers (or images).

Buffers are allocated on the host and passed as pointers in to kernels. Copying data from host memory to device memory and visa versa is done explicitly because it is relatively expensive.

The copying can be done when the buffers are allocated, or as an operation added to the work queue. After buffers are used they have to be freed to not leak memory.

Buffers can be allocated read only, write only and read write. Specifying the mode of the buffer can optimize the placement of the buffer in device memory. All modes are viewed from the device.

### 3.8 OpenCL versus CUDA

The main benefit for CUDA is that it is more mature, and supports more features because it does not depend on the bureaucracy of standardization, nor does it have to be flexible to support as many platforms as OpenCL. However OpenCL does support extensions which may be used before the features are standardized. The biggest benefit of OpenCL is that it supports more platforms and vendors, and is simpler to set up. OpenCL is supported by consumer drivers shipped by NVIDIA and AMD for Windows.

In CUDA code ran on the device, and code ran on the host can be programmed in the same file. Global variables can be defined in the host code and accessed from kernel code. The host code and the kernel code is compiled before the program is executed. All code calling GPU kernels has to be compiled together with the kernels for all targets supported by the compiler. This leads to incredibly bloated executable files. In OpenCL the code is compiled at runtime, passed as a string to the driver, like GLSL. The driver may then optimize the code for the device it is supposed to be ran for only. Debugging CUDA code is simpler than OpenCL because the code is produced by the same compiler, and because the tools are more mature.

To run multiple kernels asynchronously in CUDA, a specialized set of function calls has to be used. This is more cumbersome than the generic OpenCL APIs. The support for running kernels asynchronously has lagged behind OpenCL, but will most likely catch up pretty soon because NVIDIA uses CUDA as a basis for their OpenCL driver. This can be seen in Linux; stack traces generated when using OpenCL include calls to the CUDA library by OpenCL driver functions.

# Chapter 4

## Description of the snow simulator

This chapter is organized in two parts. First the current state of the snow simulator is outlined. The code and implementation of the mathematical algorithms is the focus of this part. For a more detailed discussion of the algorithms of the simulator see [Sal06]. Afterwards the porting process, and the changes to the simulator introduced during porting is described.

#### 4.1 History of the simulator

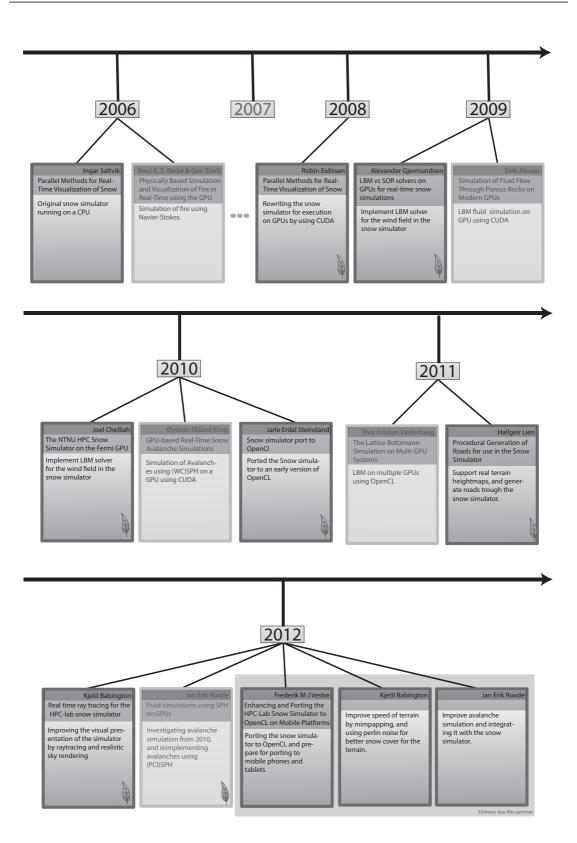

The snow simulator has been a basis for multiple thesis and autumn projects at NTNU. Most of the thesis produced are available from the web page of the lab [Els] maintained by my advisor, or from DAIM [IDI], a repository of master thesis maintained by the faculty. Figure 4.1 provides an overview of all relevant thesis and specialization projects relevant to the snow simulator produced by the HPC lab since the first thesis about the simulator. Records on the timeline marked with a leaf are specialization projects written during the autumn semester. Records which are written with grey text concerns simulation subjects relevant for the simulator, but haven't worked with the code of the simulator. In the following paragraphs a quick overview of all thesis which have worked on the actual simulator code will be given.

The first snow simulator written was written by Saltvik in 2006, as a master thesis [Sal06]. This thesis laid the foundation for the simulator. The underlying mathematical and physical models from this thesis still forms the core of the simulator today. The simulator was implemented on a CPU using multiple threads to parallelize the simulation work. Real time simulation with an acceptable frame rate was achieved. However very few particles (a few 10'th of thousands) were simulated.

Because the simulator still was quite slow no further work on the simulator was done in two years. During autumn 2008 [Eid09] ported the snow simulator to CUDA, but the report is dated 2009 because it was delivered in February. Nearly all memory used by the simulator was kept on the GPU and extensive care was shown to optimize the program for the GPU architecture. In this thesis rendering was also rewritten and improved.

The GPU snow simulator was developed further in spring 2009 in [Gje09]. In this specialization project the simulation code for simulating fluid flow trough porous rocks using Lattice Boltz-

Figure 4.1: Timeline of thesis related to the snow simulator

mann methods (LBM) [Aks09] was integrated with the snow simulator. The LBM method and the original Navier-Stokes based method was benchmarked for performance.

During autumn 2010 [Che10], the snow simulator was optimized for the NVIDIA Fermi GPU. Substantial gains were produced by optimizing memory accesses and usage to take advantage of all caches and different types of memory on the GPU. This project focused mainly on optimizing the LBM code, but the Successive Over Relaxation (SOR) code was also touched. Removal of branches and serial code was also performed to optimize the code. This resulted in a speed up of about 1.5 times the original speed for the simulator. Some of these optimizations were specific to the GPU and the compiler.