# Operating system directed power reduction on EFM32

Martin Tverdal

Master of Science in Computer Science Submission date: June 2010 Supervisor: Lasse Natvig, IDI Co-supervisor: Marius Grannæs, Energy Micro

Norwegian University of Science and Technology Department of Computer and Information Science

# **Problem Description**

Energy Micro is a Norwegian semiconductor company, located in Oslo, which focuses on 32-bit microcontrollers with ultra low energy consumption. The EFM32 microcontroller family is based on the ARM Cortex-M3. EFM is short for energy friendly microcontrollers. FreeRTOS is a small and free open source OS targeted for embedded devices. The goal of this master thesis project is to get FreeRTOS to run on an EFM32 micro controller with as low power consumption as possible. Central subtasks are:

Implementing/Exploring a tickless scheduler for FreeRTOS. Implementing/Exploring a peripheral driver structure for low-power.

Assignment given: 15. January 2010 Supervisor: Lasse Natvig, IDI

# Abstract

Power consumption has become a major concern of embedded systems. Currently FreeRTOS wastes a power waking up regularly to keep track of time. In this work FreeRTOS is modified to sleep when there is no work for the CPU to be done. Timekeeping while sleeping is done by a low frequency oscillator, consuming very little power. Drivers for peripherals have been developed, in order to optimise power consumption even more. Battery life time has been increased from 56 hours to 1867 hours for a simple self made benchmark. The goal is to get the changes into the official FreeRTOS distribution, but it has not been accepted yet. However, a customer of Energy Micro has started to develop an application based on this design.

# Acknowledgments

I want to thank my supervisor, Lasse Natvig for his guidance and encouragement throughout this spring. Marius Grannæs deserves my best, for always being sincerely helpful and supportive. Last but not least I want to thank my friends in office 443b for all the help, and for making university work fun. Especially Kjetil Wathne Oftedal for helping me in practical matters.

# Contents

| 1        | 1 Introduction |                                                                                                                                                 |  |  |

|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|          | 1.1            | Motivation                                                                                                                                      |  |  |

|          | 1.2            | Energy Micro                                                                                                                                    |  |  |

|          | 1.3            | IAR Embedded Workbench                                                                                                                          |  |  |

|          | 1.4            | Goals                                                                                                                                           |  |  |

|          | 1.5            | Contributions                                                                                                                                   |  |  |

|          | 1.6            | Structure of this report                                                                                                                        |  |  |

| _        | _              |                                                                                                                                                 |  |  |

| <b>2</b> |                | kground 5                                                                                                                                       |  |  |

|          | 2.1            | ARM Cortex M3         5                                                                                                                         |  |  |

|          | 2.2            | EFM32 5                                                                                                                                         |  |  |

|          |                | 2.2.1 Interrupts and Sleep modes                                                                                                                |  |  |

|          |                | 2.2.2 Peripherals                                                                                                                               |  |  |

|          |                | 2.2.3 Timing peripherals                                                                                                                        |  |  |

|          |                | 2.2.4 HFXO and HFRCO                                                                                                                            |  |  |

|          | 2.3            | FreeRTOS                                                                                                                                        |  |  |

|          |                | 2.3.1 Tasks                                                                                                                                     |  |  |

|          |                | 2.3.2 Co routines                                                                                                                               |  |  |

|          |                | 2.3.3 FreeRTOS and systick                                                                                                                      |  |  |

|          |                | 2.3.4 Interrupts                                                                                                                                |  |  |

|          | 2.4            | Dynamic Power Management                                                                                                                        |  |  |

|          |                | 2.4.1 Linux power management governors                                                                                                          |  |  |

|          | 2.5            | Timekeeping 16                                                                                                                                  |  |  |

| 0        | <b>D</b>       | -DTOS = EDM20 10                                                                                                                                |  |  |

| 3        |                | eRTOS on EFM32 19                                                                                                                               |  |  |

|          | 3.1            | IAR Project                                                                                                                                     |  |  |

|          | 3.2            | Demo application                                                                                                                                |  |  |

| 4        | Ticl           | kless idle 21                                                                                                                                   |  |  |

|          | 4.1            | Difference in power consumption                                                                                                                 |  |  |

|          | 4.2            | Chosen solution                                                                                                                                 |  |  |

|          | 4.3            | Interrupt handling                                                                                                                              |  |  |

|          | 4.4            | Time until next event                                                                                                                           |  |  |

|          | 4.5            | Calculating how long to sleep                                                                                                                   |  |  |

|          | 4.6            | Calculating how long was slept 27                                                                                                               |  |  |

|          |                | 4.6.1 Storing reminder                                                                                                                          |  |  |

|          |                | 4.6.2 xTickCount following RTC                                                                                                                  |  |  |

|          | 4.7            | Consequences for interrupt latency                                                                                                              |  |  |

| _        |                |                                                                                                                                                 |  |  |

| 5        |                | naging EFM32 energy modes 31                                                                                                                    |  |  |

|          | 5.1            | #1 Clocks enabled                                                                                                                               |  |  |

|          | 5.2            | $#2 \text{ Explicit control} \dots \dots$ |  |  |

|          | 5.3            | Chosen solution                                                                                                                                 |  |  |

| 6            | Met            | thodology                               | 35 |

|--------------|----------------|-----------------------------------------|----|

|              | 6.1            | Testing                                 | 35 |

|              | 6.2            | Benchmark                               | 35 |

|              |                | 6.2.1 Effect of load                    | 37 |

|              | 6.3            | Versions of FreeRTOS tested             | 37 |

|              |                | 6.3.1 Versions with DMA driver          | 37 |

|              | 6.4            | Power measurement                       | 38 |

| 7            | $\mathbf{Res}$ | ults                                    | 39 |

|              | 7.1            | Testing                                 | 39 |

|              | 7.2            | Power consumption                       | 40 |

| 8            | Con            | nclusion                                | 47 |

|              | 8.1            | Future work                             | 47 |

| Α            | Den            | no application                          | 51 |

|              |                | main.c                                  | 51 |

|              | A.2            | lcdtest.c                               | 52 |

|              | A.3            | ledtest.c                               | 53 |

|              | A.4            | ParTest.c                               | 54 |

|              | A.5            | startup_efm32.s                         | 55 |

| в            | Cod            | le                                      | 61 |

|              | B.1            | energymode.c                            | 61 |

|              | B.2            | checktiming.c                           | 65 |

|              | B.3            | Application                             | 66 |

|              |                | B.3.1 main.c                            | 66 |

|              |                | B.3.2 measurement.c                     | 69 |

|              |                | B.3.3 adc.c                             | 72 |

|              | B.4            | Diff for task.c in FreeRTOS             | 73 |

|              | B.5            | C++ program simulating GPS              | 75 |

|              | B.6            | Drivers                                 | 77 |

|              | B.7            | Serial                                  | 77 |

|              |                | B.7.1 Serial with DMA                   | 80 |

|              | B.8            | I2C                                     | 85 |

|              |                | B.8.1 Modified driver from EFMLIB       | 85 |

|              |                | B.8.2 My own I2C Driver                 | 87 |

|              |                | B.8.3 Script to process power csv files | 91 |

| $\mathbf{C}$ | Fig            | ures                                    | 92 |

# List of Figures

| 1  | Schematic of the Cortex M3 core                                                         |

|----|-----------------------------------------------------------------------------------------|

| 2  | Energy Modes on EFM32 7                                                                 |

| 3  | Peripherals on EFM32 7                                                                  |

| 4  | Peripherals used for timekeeping in EFM32 10                                            |

| 5  | Shows how a delayed list may look like                                                  |

| 6  | Interrupt priorities in FreeRTOS                                                        |

| 7  | Power state machine for StrongARM SA-1100                                               |

| 8  | Code handling overflow                                                                  |

| 9  | vTaskTickoverflow() $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 22$ |

| 10 | Sequence diagram of code 24                                                             |

| 11 | xTaskNextTick function in task.c                                                        |

| 12 | xCoRoutineNextTick function in croutine.c                                               |

| 13 | xCoRoutineNextTick in croutine.c                                                        |

| 14 | Cause of error in timekeeping 28                                                        |

| 15 | Modified idle task                                                                      |

| 16 | Benchmark application                                                                   |

| 17 | Drift on clock                                                                          |

| 18 | Drift on clock                                                                          |

| 19 | Drift on clock                                                                          |

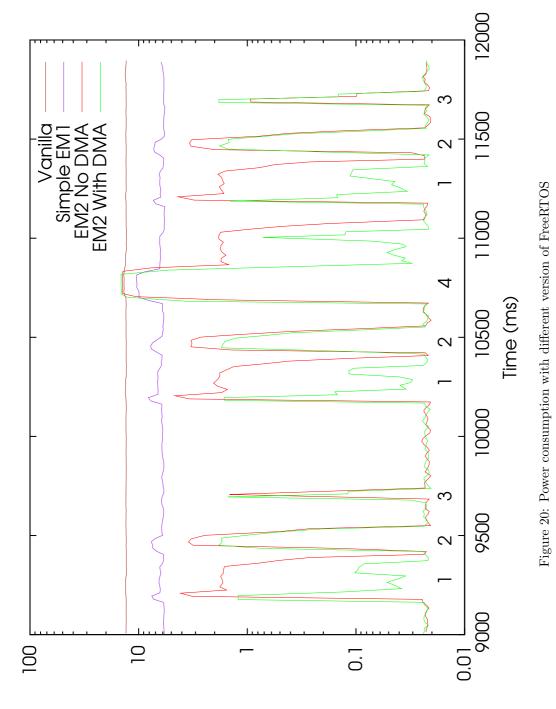

| 20 | Power consumption with different version of FreeRTOS 43                                 |

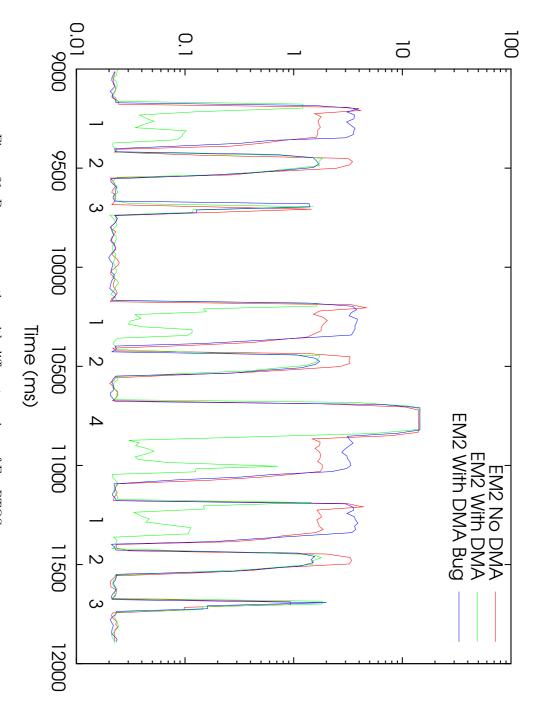

| 21 | Power consumption with different versions of FreeRTOS 44                                |

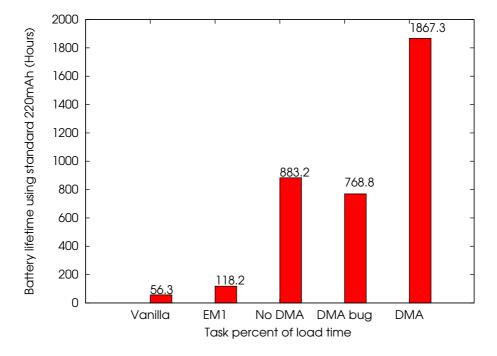

| 22 | Battery life time using 220mAh battery 45                                               |

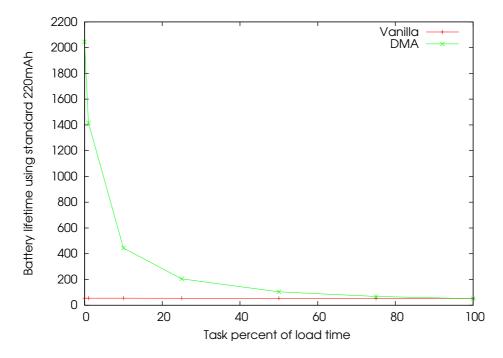

| 23 | Battery life time using 220mAh battery 46                                               |

| 24 | Bit assignments in HFPERCLKEN0                                                          |

| 25 | Bit assignments in HFCORECLKEN0                                                         |

# List of Tables

| 1 | Lists used for task management in FreeRTOS | 12 |

|---|--------------------------------------------|----|

| 2 | Sub tasks, benchmark                       | 35 |

| 3 | Parameters to load benchmark               | 37 |

# Abbreviations

- ADC Analog to Digital Converter

- **AEM** Advanced Energy Monitor

- $\ensuremath{\mathsf{CMU}}$  Clock Management Unit

- **DMA** Direct Memory Access

- **DPM** Dynamic Power Management

$\textbf{EM} \ Energy \ Mode$

GCC GNU Compiler Collection

${\ensuremath{\mathsf{GPL}}}$  GNU General Public License

**HFRCO** High Frequency Resistor Capacitor Oscillator

**HFXO** High Frequency Crystal Oscillator

IAR IAR Embedded Workbench

**ISR** Interrupt Service Routine

- **LETIMER** Low Energy Timer. Clocked by low frequency clocks. Remains active in EM2

- **NVIC** Nested Vector Interrupt Controller

$\boldsymbol{\mathsf{MPU}}$  Memory Protection Unit

LCD Liquid Crystal Display

${\it RTC}\,$  Real Time Clock

**SCB** System Control Block

**SRAM** Static Random Access Memory

$\textbf{TCB} \ {\rm Task} \ {\rm Control} \ {\rm Block}$

**UART** Universal Asynchronous Receiver/Transmitter

${\sf USART}$  Universal Synchronous Asynchronous Receiver/Transmitter

$\ensuremath{\mathsf{WFE}}$  Wait For Event

$\ensuremath{\mathsf{WFI}}$  Wait For Interrupt

**xTickCount** Variable used in FreeRTOS to count number of tick interrupts.

# 1 Introduction

## 1.1 Motivation

Reduced power consumption prolongs the battery life time of embedded systems, and other systems running on battery. This is especially important on certain embedded devices which need expensive recharging/replacement of batteries. It can be costly, or even impossible to access the device when the battery runs out. For some devices the life time is over when the battery is exhausted. Examples of this can be motion sensors embedded into the concrete of buildings, medical equipment(implants), equipment on satellites or sensors on the sea bed. Portable energy sources such as kinetic energy, or solar panels produce little power and are expensive. Low power allows the use of smaller, lower cost solar panels. Reducing the power consumption also reduces the need for cooling, which lowers the cost of electrical equipment.

Other reasons to reduce the power consumption of microprocessors is that power expensive, Rivoire et al. [Rivoire et al., 2007] reports that in data centres it can potentially exceed the cost of purchasing hardware. Using less energy reduces the emission of greenhouse gasses which, needless to say in 2010 is good for the environment. Reduced power consumption also reduces the need for cooling, which aside from reducing cost is also attractive because it makes computer systems make less noise. This can be an important selling point in home electronics. Less cooling requirement makes computer systems take less space, which is important in every segment of the computer market, from big computer centres to small embedded systems.

#### 1.2 Energy Micro

This project is done in cooperation with Energy Micro. Energy Micro is a Norwegian semiconductor company focusing on 32 bit microcontrollers with ultra low energy consumption. The founders was also the founders of Chipcon AS which was acquired by Texas Instruments for approximately 200M USD. The EFM32 Gecko (Energy Friendly Microcontroller) has a core based on the ARM Cortex-M3. It was announced on the 21. October 2009 with prototype chips available. The chips were made available for ordinary distribution in February 2010. The chip used in this work is an early engineering sample.

## 1.3 IAR Embedded Workbench

The tool chosen for this project is IAR Embedded Workbench (IAR). It is a development environment from IAR Systems, a Swedish computer technology company. It includes a C/C++ compiler, and it got support for EFM32 early in my project. The alternative was GNU Compiler Collection (GCC). Since IAR is expensive, some customers of Energy Micro demanded GCC support. However, at the start of my project there was no support for EFM32 in GCC. In order to get started on work relevant to my thesis IAR was chosen. In IAR everything worked right out of

the box, interrupt routines, single step debugging and uploading my programs to the development kit worked well. If GCC was to be used, much time would have spent too much time on tasks not relevant for my thesis.

## 1.4 Goals

# Goal 1. Introduce basic EFM32 support in FreeRTOS, without any support for energy modes.

Goal 1 is to get a basic port to the EFM32 introduced officially in FreeRTOS. Initially without any support for tickless idle or any other form of taking advantage of the different energy modes.

A basic port was made as a first step, partly to make it easier to get acceptance for a bigger change of the kernel itself at a later point if a port is already accepted in the main distribution, and partly because customers of Energy Micro were expecting RTOS support as soon as possible.

#### Goal 2. Implement FreeRTOS support for tickless idle on EFM32.

Implement a way for FreeRTOS to be totally idle while sleeping. This means that if all tasks are to sleep for 1 second, the core should also sleep for the whole second, without waking up to execute instructions. The kernel should also support keeping track of time while the EFM32 is in Energy Mode (EM)2. The complication here is that in EM2 the high frequency clock used by the core is turned off. The timekeeping has to be done with the low frequency clock.

#### Goal 3. Implement FreeRTOS management for different energy modes.

Implement support for FreeRTOS to manage the Energy Modes on EFM32. This means finding a way for FreeRTOS to determine what Energy Mode to go to when the core is idle.

#### Goal 4. Get changes into official FreeRTOS.

Get the changes developed in order to achieve goal 2 and 3 included officially in FreeRTOS. Since FreeRTOS is licensed under a Modified GNU General Public License (GPL) license, I am free to make any changes I want to the kernel as long as they are made open source. This means that Energy Micro AS is free to distribute my changes to their customers. It is however a goal to get the changes submitted to the official FreeRTOS. If the modifications gets included officially in FreeRTOS, customers of Energy Micro would be more assured that the quality is high.

## 1.5 Contributions

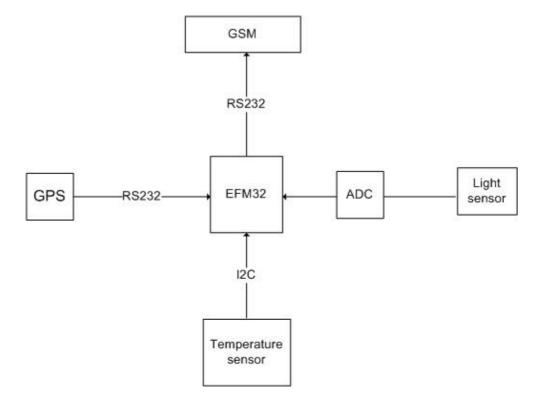

The contributions of this work is mainly a fulfilling of goals 1-3 in the previous section. In addition an application has been developed to illustrate how to use the modified FreeRTOS in order to reduce power consumption. This has involved using the I2C bus, serial bus and Analog to Digital Converter (ADC) in a way such that the EFM32 can enter the lowest possible sleep state while these modules do work.

A serial driver has been developed which enables the serial bus to stay in EM while the Direct Memory Access (DMA) copies data to to/from the transmit/receive buffer. When a transmission is complete an interrupt is issued waking up the core. When a linefeed is received or the DMA buffer is full, the core is also woken up by an interrupt. When the ADC is set up to perform a conversion, since ADC needs the high frequency oscillator, FreeRTOS is instructed not to enter any Energy Mode below EM1. The I2C is used to read the temperature. When an I2C transfer is ongoing FreeRTOS is instructed not to enter any energy mode below EM1.

A customer of Energy Micro from the US has started using my code in a project developing a new product where battery life time of multiple months is important. Because of competition the customer wants not to be mentioned by name in this thesis.

## **1.6** Structure of this report

Section 2 explains some background information which can be useful to read in order to understand the rest of the report better. Section 3 deals with the first part of my thesis, porting FreeRTOS to the EFM32 architecture. Section 4 deals with implementing tickless idle in FreeRTOS. Section 5 deals with making FreeRTOS able to go to correct energy mode. Section 6.2 explains the benchmark used, while section 6.4 explains how power consumption has been measured. Section 7 presents the results of tests of power consumption and tests for drift on the clock.

4

# 2 Background

# 2.1 ARM Cortex M3

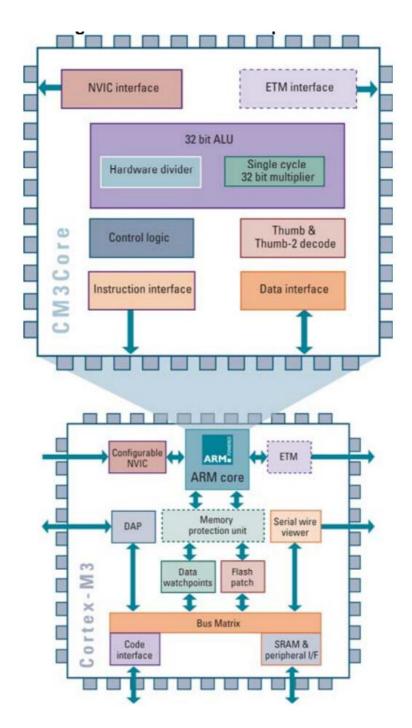

This paragraph is a small extension to the one in my project thesis [Tverdal, 2009]. Much of the information was found in Cortex-M3 Technical Reference Manual [arm, 2005]. The EFM32 has a CPU core based on the ARM Cortex-M3. This core implements the Thumb-2 instruction set, which has both 16 and 32 bit instructions. It has a 3 stage pipeline, fetch, decode and execute. It has Harvard architecture, with separate data and instruction memory. Data memory is Static Random Access Memory (SRAM), while instruction memory is flash. Figure 1 shows a block diagram of the core of the Cortex M3. The ALU supports 32 bit integer multiplication in one cycle. It also has a hardware divider which can perform integer divides in 2-12 cycles, depending on the operands. The division is completed faster if the dividend and divisor is closer in size. It also includes a *Nested Vector Interrupt Controller (NVIC)* interface (see section 2.2.1) and an optional *ETM* (Embedded Trace Macrocell) interface. The ETM is optional and provides debug and trace facilities. DAP (Debug Access Port) is implemented with Serial Wire Debug, using only 2 pins (clock and data).

## 2.2 EFM32

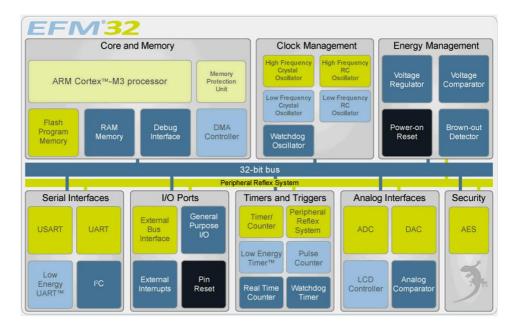

Figure 3 is a schematic overview of the peripherals on the EFM32. Figure 2 is an overview of the energy modes. There are in total 5 Energy Mode (EM)s. The most relevant ones for this thesis is EM0, EM1 and EM2. EM0 is the run mode. Everything is turned on and the core is executing instructions. In EM1 the core and the Memory Protection Unit (MPU) is shut down. Both the high frequency clock and the low frequency clock is running, meaning that the high frequency peripherals and the low frequency can be active. In EM2 the high frequency clock is turned off, but the low frequency clock is running. Which means that only the low frequency peripherals can be used. In EM3 the low frequency clock is also disabled, leaving nothing to keep track of time, the EFM32 can only be woken by the events listed in Figure 2. The flash memory code size ranges from 8KB to 128KB while SRAM data memory size ranges from 2KB to 16KB. More information can be found in Reference Manual, EFM32G Microcontroller Family [EFM32 Manual, ]

#### 2.2.1 Interrupts and Sleep modes

The NVIC on the EFM32 supports 8 priority levels for interrupts. Priorities are from 0-7, with 0 being the highest priority while 7 is the lowest. There is three exception mask registers which can affect the handling of exceptions by the processor. The technical details in this sections were found in Cortex-M3 Technical Reference Manual [arm, 2005].

**Priority Mask Register** Writing one to bit 0 prevents activation of all interrupts with configurable priority.

Figure 1: Schematic of the Cortex M3 core, taken from [Sadasivan, 2006]

| EFM32 running real application from<br>Flash memory with 3V power supply | EM0<br>Run Mode | EM1<br>Sleep Mode | EM2<br>Deep Sleep Mode | EM3<br>Stop Mode                                                   | EM4<br>Shutoff Mode |

|--------------------------------------------------------------------------|-----------------|-------------------|------------------------|--------------------------------------------------------------------|---------------------|

| Current consumption                                                      | 180 µA/MHz      | 45 µA/MHz         | 0.9 µA                 | 0.6 µA                                                             | 20 nA               |

| Wake-up time                                                             | 0               | 0                 | 2 µs                   | 2 µs                                                               | 160 µs              |

| Wake-up events                                                           | Any             | Any               | 32 kHz<br>peripherals  | Async IRQ, I2C slave,<br>Analog Comparators,<br>Voltage Comparator | Reset               |

| CPU                                                                      | On              |                   |                        |                                                                    |                     |

| High frequency peripherals                                               | On              | On                |                        |                                                                    |                     |

| Low frequency peripherals                                                | On              | On                | On                     |                                                                    |                     |

| Full CPU and SRAM retention                                              | On              | On                | On                     | On                                                                 |                     |

| Power-on Reset/Brown-out Detector                                        | On              | On                | On                     | On                                                                 | On                  |

Figure 2: Energy Modes on EFM32

Figure 3: Peripherals on EFM32

- Fault Mask Register Writing one to bit 0 prevents the activation of all exceptions except for Non-Maskable Interrupt.

- **Base Priority Mask Register** If for example a 5 is written to this register it prevents the activation of all exceptions with priority lower than or equal to 5 (5, 6 and 7).

There are two instructions used for entering sleep modes, Wait For Interrupt (WFI) and Wait For Event (WFE). If SLEEPDEEP bit in the System Control Block (SCB) is set to 0, EM1 is chosen, if it is set to 1, EM2 is chosen. EM3 is equal to EM2, except that the low frequency clocks are stopped in EM3. They have to be stopped by software explicitly. In EM3 there is no way to keep to track of time.

**WFI** When the WFI instruction is issued EFM32 enters a low energy mode. It is woken by an interrupt with high enough priority to preempt execution, disregarding the Priority Mask Register. This means that even if the Priority Mask Register is set to disable interrupts, the core will be woken up by interrupts which would have high enough priority to wake the core had it not been set to disable interrupts. This means that if the Base Priority Mask Register is set to mask out all interrupts with priority below 5 (5, 6 and 7), interrupts with these priorities will not wake up the core. An interrupt with priority of 4 and above, will wake up the core regardless of Priority Mask Register.

When the core is woken up execution proceeds at the instruction after the WFI instruction if Priority Mask Register is set. If the Priority Mask Register is not set execution proceeds in the Interrupt Service Routine (ISR).

**WFE** The other instruction that can be used to enter low energy mode is WFE. If the SEVONPEND bit in the System Control Register is set, the core is woken up by all interrupts entering the Pending state, even if they are disabled or has too low priority to cause ISR entry. When woken up, execution proceeds at the next instruction after WFE if the pending interrupt does not have high enough priority to preempt execution, or it proceeds in the ISR if it does.

#### 2.2.2 Peripherals

**ADC** Analog to Digital Converter is available in EM0 and EM1. It is used to convert an analog signal to a digital representation.

**AES** Advanced Encryption Standard is available in EM0 and EM1. It is a hard-ware accelerator for encrypting and decrypting with 128 or 256 bit keys.

**DAC** Digital to Analog Converter is available in EM0 and EM1. It is used to convert a digital value to an analog signal.

**Analog Comparator** is available in EM0,EM1,EM2 and EM3. It is used to compare two analog signals. It can monitor a signal to see if it passes a certain threshold while the EFM32 is in EM3, consuming very little power.

**Peripheral Reflex System** is available in EM0 and EM1 and allows very simple communication between peripherals.

**Timer/Counter** is available in EM0 and EM1 and keeps track of timing and counting events.

**UART** is available in EM0 and EM1 and is used for Universal Asynchronous Receiver/Transmitter (UART) communication.

**USART** is available in EM0 and EM1 and is used for Universal Synchronous Asynchronous Receiver/Transmitter (USART) communication.

**DMA Controller** Direct Memory Access is available in EM0, EM1 and EM2 and can move data while the core either sleeps, or is busy.

**External Bus Interface** is available in EM0 and EM1 and is used to access external devices. They are mapped to the memory space of the core, making them easy to use.

**General Purpose I/O** is used to communicate with external devices and can wake up the EFM32 in EM1, EM2 and EM3.

**I2C** Inter-Integrated Circuit interface supports communication on I2C buses. I2C is a common bus protocol used in embedded systems. It can be configured to wake up the EFM in EM1, EM2 and EM3.

**LCD Controller** is able to drive a Liquid Crystal Display (LCD) display with up to 4x40 segments in EM0, EM1 and EM2.

**Low Energy TIMER** can keep track of time and output waveforms in EM0, EM1, EM2 and EM3.

**Low Energy UART** is available in EM0, EM1 and EM2 and provides UART communication.

**Real Time Counter** is available in EM0, EM1 and EM2. It is a 24 bit timer used to keep track of time.

**Pulse Counter** is available in EM0, EM1, EM2 and EM3. It count pulses and can wake up the core.

Watchdog Timer is available in EM0, EM1, EM2 and EM3 and resets the EFM32 when a fault condition is reached. If the core does not reset the watchdog within the configured timeout period the watchdog resets the EFM32.

**Brown-out Detector** monitors the supply voltage in EM0, EM1, EM2 and EM3. It resets the EFM32 if it drops below a safe value.

**Power-on Reset** is available in all energy modes and monitors the supply voltage and signals when it reaches the operating value.

#### 2.2.3 Timing peripherals

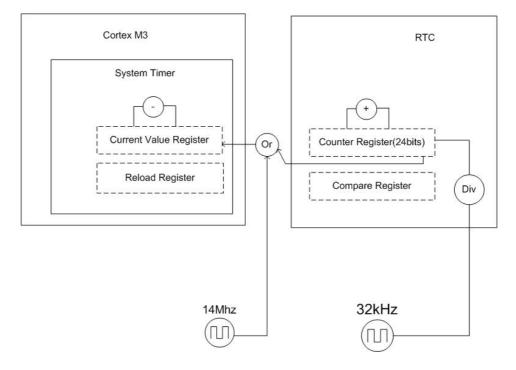

Figure 4: Peripherals used for timekeeping in EFM32

Figure 4 shows the peripherals relevant for this thesis when it comes to keeping track of time. The *Cortex M3* core has a built in *System Timer*, it works by decrementing *Current Value Register* every time the clock beats. When it reaches 0, an interrupt is issued to the core and it reloads the *Current Value Register* with the value set in the *Reload Register*. Then it continues to decrement the *Current Value Register*. This way a the System Timer can be used to generate a periodic interrupt. If for example 14'000'000 is written to the Reload Register, and the 14MHz clock is used, an interrupt occurs every second. The Current Value Register

can also be clocked by the least significant bit in the Real Time Clock (RTC), that way it can be clocked indirectly by the low frequency clock rather than the high frequency clock.

The RTC works in a similar way, it is however clocked by the low frequency 32kHz clock, which means it is available for timekeeping in EM2. The *Counter Register* (which is only 24 bits) is incremented every time the clock beats. The clock can be divided, to make it increment at a slower rate. When the value is equal to the value in the *Compare Register* an interrupt is issued to the Cortex M3 core, and starts to count up again from 0.

#### 2.2.4 HFXO and HFRCO

The core clock can be generated either by High Frequency Crystal Oscillator (HFXO) or High Frequency Resistor Capacitor Oscillator (HFRCO). HFXO is more accurate but has a considerably longer wake-up time. According to [EFM32G890F128 Datasheet, ] HFXO has a start up time of  $400\mu$ s, while HFRCO has a start up time of only  $0.6\mu$ s. When waking up from EM2 or EM3 when the high frequency oscillator is turned of, the EMF32 is always running with HFRCO. If HFXO is wanted, software has to enable it, then wait for it to start up before switching clock source. The Clock Management Unit (CMU) module of the EFM32 supports waiting for 8, 256, 1024 or 16384 cycles of the HFRCO. Since 1024 cycles of 14MHz is only  $73\mu$ s, 16384 cycles has to be used. This equals to waiting for 1.1ms.

#### 2.3 FreeRTOS

The information about FreeRTOS was found by reading the work of Sadasivan [Sadasivan, 2006], the FreeRTOS web site (http://www.freertos.org/) and the source code [FreeRTOS Code, 2010].

This paragraph is taken from my project thesis. There exists a vast amount of operating systems for microcontrollers, the decision to go with FreeRTOS came from Energy Micro. FreeRTOS is a small and free open source OS targeted for embedded devices. It contains approximately 4000 lines of code. It is a very simple OS, there is no support for complex memory management, no device drivers or any support networking. It lets the programmer create tasks with priorities and schedules them either cooperatively or preemptively. It uses a simple round robin algorithm within a priority, and does not schedule lower priorities as a long as tasks with higher priorities are ready. It provides mechanisms for tasks to communicate and share data safely (queues, semaphores and mutexes). FreeRTOS has been ported to many different architectures, including the Cortex-M3. The latest version also supports the MPU. on the Cortex-M3.

#### 2.3.1 Tasks

Table 1 shows the lists used by the scheduler to manage lists. For every priority there is one list ReadyTasksList[N] of tasks ready to run. If configured in FreeR-

TOSConfig.h there is one list *TasksWaitingTerminiation* of tasks that is waiting to be deleted, and one list *SuspendedTaskList* with suspended tasks. Suspended tasks are tasks that are delayed indefinitely, and will not be made ready by the kernel itself no matter how long time elapses. They have asked to be delayed indefinitely by calling for example by calling vTaskDelay(MAX\_DELAY).

The *PendingReadyList* list is used by the kernel for tasks that have been made ready while the scheduler has been suspended. It is needed since the scheduler can be suspended, meaning that it will not perform any tasks switches even if a task becomes ready. While the scheduler is suspended the ready list can not be modified. The task is instead added to the *PendingReadyList*, and moved to the Ready list when the scheduler is resumed.

The *DelayedTaskList* and *OverflowDelayedTaskList* is where delayed tasks are kept. They are sorted by wake up time. The reason for using two lists is that the wake up time might overflow. If at tick number 250 a task wants to sleep for 30 ticks, 250+30 will overflow and result in 25 (if a 8 bit counter is used). The task is then inserted into the overflowed list. When the Variable used in FreeRTOS to count number of tick interrupts. (xTickCount) variable overflows, the two lists are swapped. This implementation results in that the maximum time a task can sleep is 255 if a 8 bit counter is used. If a task was to sleep for 256 ticks when xTickCount was 150. 150+256 would result in 151.

| List                            | Description                                                                                     |

|---------------------------------|-------------------------------------------------------------------------------------------------|

| ReadyTaksList[N]                | Tasks ready to run, one for each priority level.                                                |

| ${\it TasksWaitingTermination}$ | Tasks that has terminated, but not yet deleted                                                  |

| SuspendedTaskList               | Suspended tasks will not get scheduled to run again by the scheduler.                           |

| PendingReadyList                | Pending tasks will be put in the ReadyTaskList once the scheduler is re-enabled.                |

| DelayedTaskList                 | Tasks that have been delayed. Sorted by wake up time.                                           |

| OverflowDelayedTaskList         | Due to arithmetic overflow, tasks delayed until after<br>the tick count overflows are put here. |

Table 1: Lists used for task management in FreeRTOS

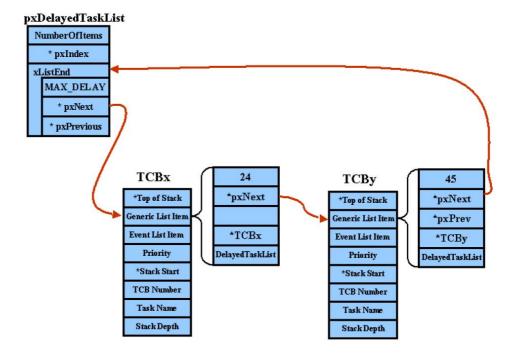

Figure 5 shows how a delayed list looks like. pxDelayedTaskList points to a struct of type xList. The first variable in a xList tells how many items is in the list. The next variable pxIndex is used when traversing the list, to keep track of the next element to be returned. The xListEnd is the end marker. In this case it contains MAX\_DELAY in xItemValue. The two other tasks in the list contain 24, and 45 in that position. Task x is delayed until xTickCount reaches 24, while task y is delayed until it reaches 45.

Figure 5: Shows how a delayed list may look like. Taken from [Sadasivan, 2006]

#### 2.3.2 Co routines

FreeRTOS also has the concept of co routines. They are intended to be used on very small processors that have very little memory. To save memory, all co routines share stack. They are handled very similar to tasks, with a ready list for each priority, a pending ready list, a delayed list and an overflowed delayed list. The difference is that they all share a stack. The consequence of sharing a stack is that the variables declared on the stack can loose the value when the co routine is blocked. The way co routines are scheduled is worth noticing. They are scheduled by repeated calls to vCoRoutineSchedule(). The normal place to call this is in the application idle hook, which is a function repeatedly called by the idle task. This has the effect that co routine has a lower priority than tasks.

#### 2.3.3 FreeRTOS and systick

FreeRTOS keeps track of time by incrementing a counter at a configurable rate, normally 1000Hz or 100Hz. The system timer of the Cortex M3 core is set up to issue an interrupt at one of these intervals. At every interrupt the xTickCount variable is incremented, and the scheduler also checks if it needs to perform any scheduler tasks.

#### 2.3.4 Interrupts

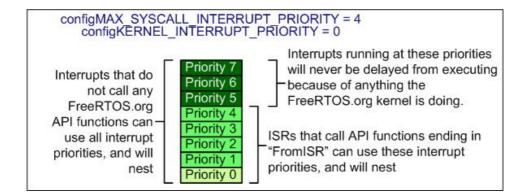

Figure 6 illustrates how interrupts are handled in FreeRTOS. The macro configK-ERNEL\_INTERRUPT\_PRIORITY defines the priority all the kernel interrupts use, SysTick and PendSV. Systick is executed periodically in order to keep track of time, while PendSV is a software interrupt used for switching tasks. configK-ERNEL\_INTERRUPT\_PRIORITY is set to the lowest possible priority, which on EFM32 is 7 (The highest priority is 0). configMAX\_SYSCALL\_INTERRUPT\_PRI-ORITY defines the highest priority an interrupt which uses the FreeRTOS API can have. An interrupt with priority below this value however only call API functions with names ending in FromISR. Interrupts with priority above configMAX\_ SYSCALL\_INTERRUPT\_PRIORITY is never delayed by anything the kernel does. They can not call any API functions in FreeRTOS.

#### 2.4 Dynamic Power Management

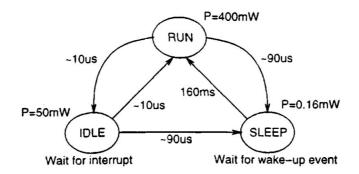

Dynamic Power Management (DPM) is different techniques for turning off, or reducing the performance of components when they are idle. There is a lot of research on this topic. Benini et al. in [Benini et al., 2000] presents a survey of different techniques where figure 7 is used as an example. It shows the states of StrongARM SA-1100 has three states, which are summarized in the figure. RUN, IDLE and SLEEP. The power consumption and transition times between states are shown. Break-even time for a state is the minimum idle required to justify entering the state. A prediction of the idle period is needed in order to determine which state to enter. Timeout is the simplest prediction, wait for a fixed amount of time and if nothing has happened enter the low power state.

Figure 6: Figure illustrating how interrupt priorities are divided in FreeRTOS. Taken from www.FreeRTOS.com

*Predictive shutdown* techniques makes a decision of which state to go to as soon as the idle period starts based on previous idle and active periods.

To reduce the delay imposed when the device has to go from an idle state back to the active state, *Predictive wake up* techniques wake up the device before anything has happened. The technique proposed by [Hwang and Wu, 2000] predicts the length of the idle period as the weighted sum of the last idle period, and the last prediction. It wakes up the device when the predicted idle period has elapsed. If the idle period is lower the the break-even time, the device stays in the active state but the calculation done over again when the break-even time has elapsed. This is to avoid staying awake when a long idle period occurs.

#### 2.4.1 Linux power management governors

The way Linux (version 2.6.34) [Lin, 2010] manages sleep states is interesting. The infrastructure used is called power management governors. There are two governors to choose from, ladder.c or menu.c. They can both found in drivers/cpuidle/governors/ in the Linux source code [Lin, 2010]. The ladder governor is the simplest one, it starts by entering the lightest sleep state. If that was successful it tries the next sleep state the next time.

The menu governor is more advanced. To estimate how long the idle period will be it uses the next scheduled event as a starting point. If timer is set to wake up the CPU in 500ms the idle period will not be longer than that. Since the idle period will rarely be that long, a correction factor which is based on previous behaviour is used. If for example all the previous idle periods was 50% of the time until the next timer event, the estimated idle period will be 50% of the time until next event. 12 independent factors used based on how long the expected idle period is, and if there is disk IO pending or not. If for example it is  $50\mu$ s until the next timer event, a different factor is used than if it is  $500\mu$ s until the next timer event. Another constraint used to limit the performance impact is a performance multiplier. It is used like this on line 237 in menu.c of the Linux kernel:

####

This means that if the exit latency of a sleep state multiplied with a multiplier is larger than the expected idle period, the state is not considered. This multiplier is based on current load of the system. The higher the load, the higher the multiplier.

Both the menu governor and the ladder governor lets device drivers register their latency constraints. For example an audio driver might know that it will get an interrupt when it has 200  $\mu$ s of samples left in the DMA buffer. Then it could set a latency constraint of 150  $\mu$ s. That way it can be sure it will have time enough to put more samples in the buffer before it runs out.

Figure 7: Power state machine for the StrongARM SA-1100 processor. Taken from [Benini et al., 2000].

#### 2.5 Timekeeping

Traditionally Linux counted the number of timer interrupts in a variable called Jiffy. A hardware device was used to generate a periodic interrupt at a specific rate. Every time the interrupt occurs, a CPU increments the jiffy variable. This scheme has a number of shortcomings. One being that the rate of the timer interrupt limits the resolution timekeeping. This was the major concern of Srinivasan et al. [Srinivasan et al., 1998]. Other issues reported by Stultz et al. concerns correctness [J Stultz, 2005]. If a buggy driver blocks interrupts for too long, timer interrupts could be lost. Stultz et al. also argues that the code introduced in the Linux kernel to increase the resolution of timekeeping could also be buggy [J Stultz, 2005]. To increase the resolution time between ticks was interpolated by a high resolution hardware timer.

Corbert [Corbet, 2005] describes how tickless idle was first implemented on Linux. Linux had support for being tickless during idle periods on some architectures (at least on S390 and OMAP ARM) already in Kernel 2.6.6. When the CPU was idle, the hardware timer was set up to give an interrupt in time for the next event. When an interrupt woke up the CPU, the jiffy variable was updated before the interrupt handler was allowed to run. The jiffy variable was updated by calling the do\_timer\_interrupt() function as many times as necessary. It is interesting to note that in kernel 2.6.13, a variable called modulo\_count was used to store the reminder when updating jiffies. For example if 300 32768Hz ticks had elapsed in the idle period, the jiffy should be updated with 300 \* 32768 / 1000 = 9.15. (With 1000Hz frequency on the timer interrupt). The jiffy variable (being an integer) can only be updated with 9. This way the reminder is always lost. In kernel 2.6.13 in arch/arm/mach-omap1/time.c [LiA, ] this is compensated for by incrementing the modulo\_count with the reminder every time, and when modulo\_count gets big enough, increase the jiffy one extra time. In kernel 2.6.14 in the same file, this modulo compensation is removed because this rounding error is compensated for by the interpolation between ticks.

[Srinivasan et al., 1998] modifies the Linux kernel to use the hardware timer to interrupt the core when the next event is scheduled to occur (Rather than interrupting it periodically). This is done to achieve higher accuracy of timekeeping. Since other subsystems in the Linux kernel uses the jiffy variable and relies on it to be updated, it is kept up to date. [Gleixner and Niehaus., 2006] started as a fork of the work presented in [Srinivasan et al., 1998]. It is the code from this project that is used in the kernel today (2.6.34). The periodic tick is not used for timekeeping at all (when configured with the option CONFIG\_NO\_HZ). Timekeeping is not done with the periodic tick at all. There is still a periodic tick when the core is active though, but it is used for other tasks than timekeeping.

# 3 FreeRTOS on EFM32

#### 3.1 IAR Project

Since FreeRTOS is already ported to Cortex-M3, getting FreeRTOS to run on EFM32 was really just a question about setting up a project in IAR Embedded Workbench, including the right files and setting up the interrupt vector table. In addition a demo application was created.

In the FreeRTOS directory there is a directory named Demo. Every vendor supported by FreeRTOS puts demo applications here. The demo includes a project that can be built without warnings or errors and run directly on the MCU from the vendor and work on a development kit. For example, STM as 4 demo applications for the STM32F103 which are in directories named: CORTEX\_STM32F103\_IAR, CORTEX\_STM32F103\_IAR, CORTEX\_STM32F103\_Primer\_GCC and CORTEX\_STM32F107\_GCC\_Rowley. This makes it easier for customers wanting to develop an application with FreeRTOS on the MCU. They can simply copy the project for the compiler they are using and have a working project they can start modifying.

A new directory called CORTEX\_EFMG890F128\_IAR was created, and inside an IAR project was configured to compile, upload, run and debug applications on the development kit from Energy Micro. In order to make it self-contained, the BSP<sup>1</sup> and CMSIS<sup>2</sup> files provided by Energy Micro was added to the directory. This makes it easier for new developers to download FreeRTOS and start developing applications on the development kit. It is however not ideal from a software development point of view since it leads to duplication of code if the CMSIS and BSP code is included inside different FreeRTOS projects. If there is a new release of either BSP or CMSIS, there would be several places to apply the updates. However, the requirement for the project in IAR to be self-contained and compilable as downloaded outweighed this consideration.

In order to set up the interrupt vector table, startup\_efm32.s was copied from the CMSIS directory and modified. The modified version can be found in Appendix A.5. The interrupts changed are vPortSVCHandler, xPortPendSVHandler and xPortSysTickHandler.

#### 3.2 Demo application

The demo application demonstrates how the LCD is used, and how the leds on the development kit can be used. This demo was added in the official FreeRTOS release 6.0.4 released March 14. 2010 [Changelog, 2010]. Richard Barry, the maintainer of FreeRTOS made some small changes to the application. The code can be found in appendix A. There is one task called LCDTask that prints out some text to the LCD display, and another that toggles leds 8-15 on the development kit. The demo application also uses a demonstration task which is included by FreeRTOS.

<sup>&</sup>lt;sup>1</sup>Board Support Package is code code provided by Energy Micro to make it easy to develop applications on the development kit.

<sup>&</sup>lt;sup>2</sup>Cortex Microcontroller Software Interface Standard contains name definitions, address definitions and helper functions to access registers and peripherals.

The task is called crflash and is common to demos from other vendors. It uses 8 co-routines to flash leds 1-7.

Every demo in FreeRTOS should implement the functions in partest.h. They are used to initialise and test the leds on the development kit. See appendix A.4 for ParTest.c. There is one function used to initialise the leds, which utilises the functions DVK\_init and DVK\_setLEDs from the BSP. There is also one function vParTestSetLED(uxLED,value) which sets led uxLed to either on or off according to value. The last function called vParTestToggleLED(uxLED) toggles led uxLED.

# 4 Tickless idle

In order for the EFM32 to take advantage of EM2 where the high frequency clock is turned off, a way to keep track of time with the low frequency clock is needed. It is also needed in order to stay in EM1 for longer periods than the period of the SysTick interrupt.

Several solutions has been tried. This subsection contains a short description of the ideas. The next subsection is a thorough description of the chosen solution. The main issue is keeping xTickCount up to date. When woken up by something, for example receiving something on the LEUART, the xTickCount has to be updated. One strategy is to modify FreeRTOS and make xTickCount point to a register which is updated when the core is sleeping. That way there is no need to update xTickCount when waking up, since the hardware has been updating it while the core was sleeping. The other conceptual idea is to update xTickCount according to the length of the period slept when the core is woken up. Care has to be taken to avoid that execution of the application is allowed to proceed before xTickCount is updated.

Idea #1: Cortex Systick count register as xTickCount The first idea tried out was to use the register used by the System Timer in the Cortex core. This register is used to count down to 0, and then give a systick interrupt. This register can be clocked by either the core clock (14MHz) or the last bit of the RTC counter value. The idea was to modify the xTickCount in FreeRTOS to point to this register. This was done with a #define, leading all references to xTickCount to dereference the memory location of the register. A prototype was implemented and seemed to work. A big problem however was that the register stopped counting when the MCU went to EM2, even though the RTC counter value continued to increment in EM2. The idea was discarded because of this.

Idea #2: RTC counter value as xTickCount The second idea tried is an adjustment of the first. The fact that the counter value register of the system timer in the Cortex core stops counting in EM2 led me to the idea to use the RTC counter value register instead. This has been implemented and seemed to work. The main reason for dropping this idea is the fact that it required bigger changes to the FreeRTOS code in order to work.

The code below shows how xTickCount was defined to be the value of the RTC count register (RTC-¿CNT).

```

#if configUSE_TICKLESSIDLE == 1

#define xTickCount (portTickType)(RTC->CNT)

#else

```

The RTC CNT value is only 24 bits, which made it more complex to get FreeRTOS to handle using it as xTickCount . Figure 8 shows how the vTaskDelay() function in task.c was modified in order to get overflowing correct. Normally xTimeToWake is calculated as a normal addition. To check for overflow vTaskDelay checks if xTimeToWake is smaller then xTickCount. If that is the case, a overflow has

happened and the task is put into the overflowed delay list. If the 24 bit CNT register was to be used as xTickCount, this overflowing had to be done manually in software by using the modulo operator.

```

#if configUSE_TICKLESSIDLE == 1

xTimeToWake = (xTickCount + xTicksToDelay)%0x1000000;

#else

xTimeToWake = xTickCount + xTicksToDelay;

#endif

```

Figure 8: The code used in vTaskDelay to get overflow correct when using 24 bit register as xTickCount

When the RTC CNT overflows, the RTC gives an interrupt. The function called by the RTC interrupt routine can be found in figure 9. This interrupt however is asynchronous to the execution of the kernel. Meaning that there is no guarantee for what the kernel is doing when the RTC CNT overflows. The RTC CNT could overflow, without giving the kernel the opportunity to swap the delayed lists right away. In turn, this could lead to unwanted behaviour. This problem was not solved completely before abandoning this Idea.

```

#if configUSE_TICKLESSIDLE == 1

void vTaskTickoverflow(void){

xList *pxTemp;

/* Tick count has overflowed so we need to swap the delay lists.

If there are any items in pxDelayedTaskList here then there is

an error! */

pxTemp = pxDelayedTaskList;

pxDelayedTaskList = pxOverflowDelayedTaskList;

pxOverflowDelayedTaskList = pxTemp;

xNumOfOverflows++;

}

#endif

```

Figure 9: The function called by the RTC interrupt routine when the RTC CNT overflows

Idea #3: Sleeping and updating xTickCount in idle loop This is the chosen idea. Namely because it requires the least amount of changes to the FreeRTOS source code. Description follows in the rest of this section.

#### 4.1 Difference in power consumption

The difference in power consumption between the ideas has not been investigated in depth, but is considered not to be significant enough to outweigh the advantages with the chosen solution. A optimisation that could be applied to idea #2 is the need to wait for HFXO (if HFXO is used as core clock, and not HFRCO) to start up before proceeding. When woken up FreeRTOS could start HFXO but continue to run with HFRCO until HFXO was ready. That way the wake up time could be reduced with idea #1 and #2, which would reduce the power consumption, since the core could stay in low energy mode for longer. The order of magnitude here is milliseconds as explained in 2.2.4. This could result in a higher power consumption with idea #3 than the first two.

A drawback to this idea is the fact that the systick interrupt would for a small period occur at a different frequency than defined by the application. This could lead to unwanted behaviour. If the systick interrupt was still used as the source for periodically running the scheduler, tasks would end up getting an uneven time slice. But if this difference could be accepted, power could be saved. Even with idea #3 this method could be used if timing while active is not very crucial. Using HFRCO for timekeeping while FreeRTOS is configured to a higher frequency because it is set up to use HFXO would lead to a drift on the clock while active. This would be corrected by the scheme presented in section 4.6.2.

#### 4.2 Chosen solution

The idle loop is scheduled to run by the scheduler every time there is no tasks with higher priority than the idle task ready to run. This makes the idle loop a good place to put the core to sleep, and wake it up again in time for the next task to run. The matter is complicated a bit by the fact that the co routines are scheduled by the idle loop making a call to vCoRoutineSchedule();

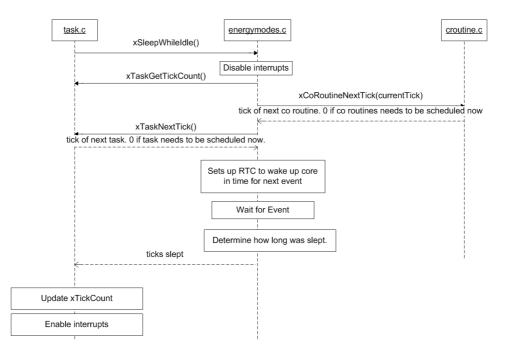

Figure 10 shows a sequence diagram for the common case when FreeRTOS puts the core to sleep. The idle task calls a function called sleepWhileIdle() which is implemented in in energymodes.c. sleepWhileIdle disables interrupts and calls xTaskGetTickCount() to get the number of ticks elapsed. Then it continues to call xCoRoutineNextTick(int) and xTaskNextTick() to determine the next event scheduled to happen. The RTC is then set up to wake up the core before the next event. When an interrupt is received, either from the RTC or something else, sleepWhileIdle() determines how long the core was sleeping by looking at the counter value in the RTC and returns the value. The idle task then updates the xTickCount value and enables interrupts. It is important that the xTickCount is updated before the interrupt is processed since the interrupt may wake up a task, and if a preemptive scheduler is used it may cause a task to run while xTickCount still has an old value for xTickCount .

## 4.3 Interrupt handling

It is considered imperative that the xTickCount variable is updated before interrupts are allowed to be processed. If an interrupt is allowed to be processed before xTickCount is updated to the correct value, a task might be woken up by the interrupt and start running while the xTickCount has an old value. This could

Figure 10: Sequence diagram showing interactions between files in my solution.

lead to unwanted behaviour, if for example the task calls vTaskDelay() while the xTickCount is old.

To make sure the xTickCount variable is updated before processing any interrupts, interrupts are disabled while sleeping. This is done by using FreeR-TOS macro called portDISABLE\_INTERRUPTS(). It disables all interrupts with priority lower than configMAX\_SYSCALL\_INTERRUPT\_PRIORITY (see Section 2.3.4). Disabling all interrupts and then going to sleep would usually make the core sleep forever. However, if the SEVONPEND bit in the System Control Register is set the core is woken up from a WFE instruction when an interrupt goes to the pending state, even if it does not have a high enough priority to wake up the core.

If an interrupt has a higher priority than configMAX\_SYSCALL\_INTERRUPT\_PRIORITY the interrupt service routine will get processed right away, without updating the xTickCount . Those interrupts are not allowed by to call any FreeRTOS API functions. This scheme ensures that those interrupts will not be delayed by code in this project. If the core is sleeping when such an interrupt occurs, the delay to start up the core (around 2  $\mu$ s) will be encountered. The interrupt will in this case be processed with HFRCO even if HFXO is used by the application.

## 4.4 Time until next event

In order to determine the time until next event two functions has been added to FreeRTOS. xTaskNextTick() in task.c and xCoRoutineNextTick(currentTick). See

Figure 11 and Figure 12 for code. They both return the next tick count on which a task or co routine is ready to run. They both return 0 if execution of a task or co routine needs to be performed, and sleeping is not possible.

```

#if configUSE_TICKLESSIDLE == 1

1

\mathbf{2}

portTickType xTaskNextTick(void){

3

if(uxTopReadyPriority>0

4

|| xPendingReadyList.uxNumberOfItems>0

5

|| pxReadyTasksLists[0].uxNumberOfItems>1){

6

return 0:

7

}

8

if(pxDelayedTaskList->uxNumberOfItems>0){

9

return (pxDelayedTaskList->xListEnd.pxNext->xItemValue);

10

}else{

11

return portMAX_DELAY;

12

7

13

}

14

#endif

```

Figure 11: xTaskNextTick function in task.c

Figure 11 shows the xTaskNextTick() function. In line 3 a check is made to see if there are any tasks ready to run right now. Since this is all done from the idle task, one should think that no tasks could be ready run when the idle task is running. However, tasks could be sharing the idle priority. That way tasks with the same priority as the idle task could be ready to run even if the idle task is running. Even if no tasks are sharing the idle priority, higher priority tasks could have been woken up by interrupts before interrupts where disabled in the idle task. This is only possible when a cooperative kernel is in use. Because if the kernel is preemptive, a task becoming ready to run would preempt the idle task and start running right away. If the kernel is cooperative the task that becomes ready would not be able to run before the idle task yields on its own. There could be a task in one of the xReadyTasksLists. If uxTopReadyPriority is set to something above 0, it means that a task is ready to run in one of the readyTask lists. If however it is 0, a task could still be ready to run at priority 0, which is why the pxReadyTaksLists[0] is checked. If any tasks are in the xPendingReadyList sleep mode can not be entered either.

If there are no tasks ready to run at this time, the next task can be found in the pxDelayedTaskList. If there are no tasks here, either no tasks have been created at all, or they are all in the pxOverflowedTaskList. Either way, *portMAX\_DELAY* is returned. Meaning the core will wake up in time to handle the *xTickCount* overflow.

Figure 13 shows xCoRoutineNextTick(portTickType currentTick), it takes in the current tick count and is called when interrupts are disabled. croutine.c maintains its one tick count variable xCoRoutineTickCount, and it is not always up to date with the "original" xTickCount in task.c. This is why xCoRoutineNextTickdiffers from xTaskNextTick in that it returns 0 if currentTick has overflowed and xCoRoutineTickCount has not overflowed yet. If that is the case sleep mode will

```

1

#if configUSE_TICKLESSIDLE == 1

\mathbf{2}

portTickType xCoRoutineNextTick(portTickType currentTick){

if(uxTopCoRoutineReadyPriority>0 ||xPendingReadyCoRoutineList

3

.uxNumberOfItems>0 || pxReadyCoRoutineLists[0].

uxNumberOfItems>0 ){

4

//there are co routines ready to run.

5

return 0;

7

6

7

if(xCoRoutineTickCount>currentTick){

8

//this means there has been an overflow on current tick,

which needs to updated.

9

return 0;

10

}

11

if(pxDelayedCoRoutineList != NULL && pxDelayedCoRoutineList ->

uxNumberOfItems >0) {

12

return (pxDelayedCoRoutineList ->xListEnd.pxNext ->

xItemValue);

13

}else{

14

return portMAX_DELAY;

7

15

16

}

17

#endif

```

Figure 12: xCoRoutineNextTick function in croutine.c

not be entered now, but rather have FreeRTOS update the xCoRoutineTickCount. The only way xCoRoutineTickCount can be bigger is if currentTick overflowed while xCoRoutineTickCount did not.

#### 4.5 Calculating how long to sleep

```

if((ticksUntillNextEvent -1) >=((0xFFFFFFF)/RTCTICKFREQ))

{

ticksUntillNextEvent=((0xFFFFFFF)/RTCTICKFREQ);

}

unsigned int rtcWakeUpVal=(((ticksUntillNextEvent -1)*RTCTICKFREQ

)/configTICK\_RATE\_HZ)+rtcCountBefore;

```

When calculating how many RTC cycles to sleep, the number of ticks until next event is multiplied with the frequency of the RTC (which is 32768 if no prescaling is used). This is divided by the frequency of the systick (configTICK\_RATE\_HZ). The current value of the RTC CNT register is added to the result.

Since ticksUntillNextEvent can be 32bits, multiplying it with 32768 might overflow. To guard against this a check is performed in advance. If the multiplication would overflow, tickUntillNextEvent is set so that it will not. This means that the maximum number of ticks that can be slept is 0xFFFFFFF/32768 = 131071. Meaning that if it is above 131071 ticks until next event, 131071 ticks will be tried to be slept. This is equal to 1310 seconds if 100Hz SysTick is used. The RTC would overflow in 512 seconds running at 32768Hz anyway, which means that this way of calculating how many RTC ticks to sleep is not the limitation in a normal

```

#if configUSE_TICKLESSIDLE == 1

portTickType xCoRoutineNextTick(portTickType currentTick){

if(uxTopCoRoutineReadyPriority>0 ||xPendingReadyCoRoutineList.

uxNumberOfItems>0 || pxReadyCoRoutineLists[0].uxNumberOfItems>0

){

return 0;

}

if(xCoRoutineTickCount>currentTick){

return 0:

}

if(pxDelayedCoRoutineList != NULL && pxDelayedCoRoutineList ->

uxNumberOfItems>0){

return (pxDelayedCoRoutineList ->xListEnd.pxNext ->xItemValue);

}else{

return portMAX_DELAY;

7

}

#endif

```

Figure 13: xCoRoutineNextTick in croutine.c

use scenario.

The alternative would be to multiply *ticksUntillNextEvent* with RTCTICK-FREQ/configTICK\_RATE\_HZ directly. This way ticksUntillNextEvent could be be bigger. However the RTC frequency would have to be evenly divisible by the tick frequency used by FreeRTOS. Essentially this would mean having the FreeRTOS systick as a power of 2. This disadvantage was to great. A very normal systick frequency are 100Hz or 1000Hz. Using this alternative they would have to be 128Hz or 1024Hz.

### 4.6 Calculating how long was slept

When the core is woken up, it is necessary to calculate how long it was sleeping. This is done by storing the RTC CNT value in a variable before going to sleep and comparing it to the RTC value when the core is woken up.

```

if(RTC->IF & RTC_IF_OF){

rtcCounterValue = RTC->CNT;

rtcTicksElapsed = (rtcCounterValue+0xFFFFFF-rtcCountBefore);

}else{

rtcTicksElapsed=(rtcCounterValue - rtcCountBefore);

}

xTickCountIncrement=rtcTicksElapsed*configTICK_RATE_HZ/

RTCTICKFREQ;

```

The code above shows how the number of RTC cycles the core was sleeping is calculated. If an overflow on the RTC CNT value has happened, 0xFFFFFF, has to be added in order to get it correct. In the next line RTC cycles is translated into xTickCount cycles. Because of the way the RTC is set up, this calculation can not overflow. Another issue is that the division when translating to xTickCount almost always result in truncation of bits, leading to a large rounding error. If for

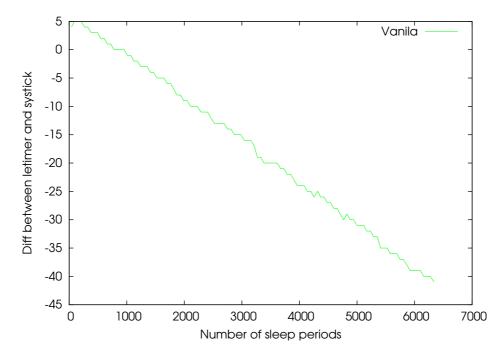

example 50'000 RTC cycles has elapsed while sleeping. This division will result in 50000 \* 1000/32768 = 1525.9. Since integer arithmetic is used, the reminder will be truncated away, with 0.9 xTickCount cycles being lost.

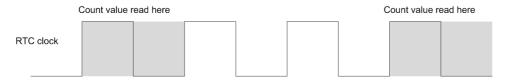

Another problem which could lead to time drifting is illustrated in figure 14. When reading the RTC CNT value there is an error margin. The value could be read anywhere in the gray area. This means that in the worst case, the error could be up to 1 period of the RTC clock. With the RTC running at 32768Hz, this is an error of around  $30\mu$ s. On average however one could suspect that the read operation is performed in the middle of the clock period, e.g. when the clock is falling. If this was true, the timing errors would even them self out. One problem however is that when the interrupts which wakes the core up is synchronous to the RTC clock, the RTC will be read at the same place every time. This could lead to errors being accumulated.

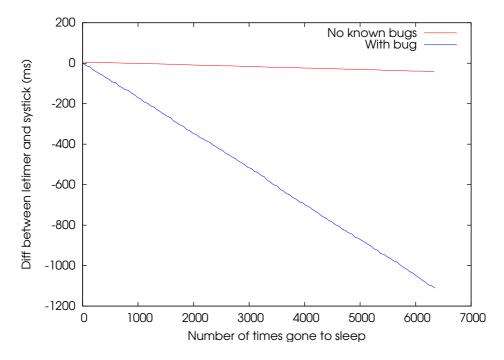

Section B.2 shows a task used when developing the tickless while idle feature. It is uses the LETIMER to keep track of time unaffected by FreeRTOS. Periodically the task examines the FreeRTOS systick, and compares it with the value from the LETIMER. The difference is sent over the LEUART.

Figure 14: The RTC CNT value could be read anywhere in the grey area, possibly resulting in error.

#### 4.6.1 Storing reminder

One way to solve the first problem in the previous subsection is to store the reminder in a variable called rounding.

```

rounding+=(rtcTicksElapsed*configTICK_RATE_HZ) % RTCTICKFREQ;

```

In the following lines of code, a check is performed to see if there is room for incrementing xTickCountIncrement by one more than the time slept this time actually dictates. It is unwanted to increase the xTickCount by any more than until one cycle before the next event is scheduled to happen. Since this might result in undefined behaviour in FreeRTOS.

```

if(rounding>=RTCTICKFREQ){

if(xTickCountIncrement+1<ticksUntillNextEvent){

xTickCountIncrement+=1;

rounding-=RTCTICKFREQ;

}

}</pre>

```

When the rounding variable is larger than the frequency of the RTC, the xTick-Count is rounded one up. This is very similar to what Linux did in 2.6.13, (see section 2.5).

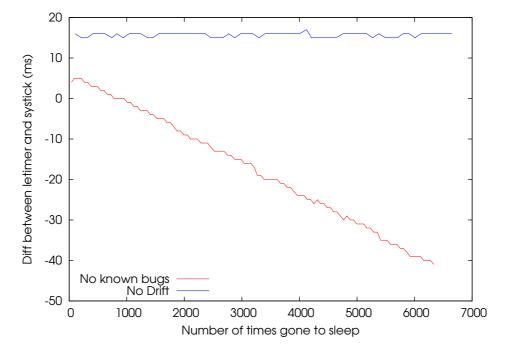

#### 4.6.2 xTickCount following RTC

To compensate for the error introduced by truncating the reminder, and the uncertainty in illustrated in 14 a different scheme was developed. The idea is to keep track of the time using the RTC, and make sure xTickCount is kept in sync with the RTC. To keep track of time with the RTC, the number of overflows is stored in a variable. When compensating for rounding errors, the time derived from the RTC is compared to the time derived from xTickCount, if they differ, xTickCount is rounded up by one.

The code below shows how this is done. First, the tick from both the RTC and from FreeRTOS (xTickCount in task.c) is calculated. Currently 64 bits is used to avoid problems with overflow. Using a 64 bit counter at 32768kHz, which is the worst case, the counter will overflow in over 17 million years. If the tick from the RTC is higher than the one in xTickCount, xTickCountIncrement is increased by one. xTickCountIncrement is the value returned to task.c, and is the value xTickCount is incremented by. There is also a check to make sure xTickCount is not incremented to past the next event scheduled to happen in FreeRTOS.

The reason this works is that in the calculation of xTickCountIncrement a truncating division is performed. This way the time slept is always rounded down, making xTickCount run slower than the RTC. When the xTickCount gets behind the tick count from the RTC, xTickCount is rounded up by one.

```

uint64_t currentTickFromRTC = ((uint64_t) rtcOverflows<<24 |

rtcCounterValue)* (uint64_t)configTICK_RATE_HZ/RTCTICKFREQ;

uint64_t currentTickInXTickCount = (uint64_t)((uint64_t)

ltaskGetNumberOfOverflows()<<32|currentTick)+

xTickCountIncrement;

if( currentTickFromRTC>currentTickInXTickCount){

if(xTickCountIncrement+1<ticksUntillNextEvent){

xTickCountIncrement+=1;

}

}else if( currentTickFromRTC<currentTickInXTickCount){

if(xTickCountIncrement>0){

xTickCountIncrement--;

}

}

```

### 4.7 Consequences for interrupt latency

The interrupt latency is impacted by my changes to the kernel. In the worst case an interrupt occurring right after interrupts are disabled, would have to wait until the entire xSleepWhileIdle() function executes. It would skip sleeping since the core would terminate the WFE instruction right away because of the pending interrupt. But still, all the instructions in the xSleepWhileIdle would have to be executed. In non optimised code (meaning compiler optimisations turned off), this was measured to around 300 CPU cycles. This corresponds to around  $10\mu$ s, and should be acceptable. If a lower latency is required by the application, an interrupt priority above configMAX\_SYSCALL\_INTERRUPT\_PRIORITY could be used. Interrupt

latency with such a priority would be unaffected by the FreeRTOS kernel. They can not call any FreeRTOS API functions.

```

static portTASK_FUNCTION( prvIdleTask, pvParameters )

{

/* Stop warnings. */

( void ) pvParameters;

for( ;; )

ł

prvCheckTasksWaitingTermination();

#if ( configUSE_PREEMPTION == 0 )

{

taskYIELD();

}

#endif

#if ( ( configUSE_PREEMPTION == 1 ) && ( configIDLE_SHOULD_YIELD

== 1 ) )

{

if( listCURRENT_LIST_LENGTH( &( pxReadyTasksLists[

tskIDLE_PRIORITY ] ) ) > ( unsigned portBASE_TYPE ) 1 )

{

taskYIELD();

}

}

#endif

#if ( configUSE_IDLE_HOOK == 1 )

ſ

extern void vApplicationIdleHook( void );

vApplicationIdleHook();

}

#endif

#if (configUSE_TICKLESSIDLE == 1)

extern portTickType sleepWhileIdle();

portTickType tickSlept=xSleepWhileIdle();

xTickCount += tickSlept;

portENABLE_INTERRUPTS();

#endif

}

}

```

Figure 15: idle task, I added the part after configUSE\_TICKLESSIDLE

# 5 Managing EFM32 energy modes

This section handles the issue of which energy mode FreeRTOS should put the EFM32 in when all the tasks are delayed. Two approaches has been implemented, and both works well. Which one is best is really more a question about which one is most convenient for the programmer of an application or device driver.

### 5.1 #1 Clocks enabled

The first solution is for the xSleepWhileIdle() function to look at which clock is enabled in the CMU register. The CMU has two registers which needs to be examined, HFCORECLKEN0 and HFPERCLKEN0. Figure 24 and 25 in appendix C shows the bit assignments of these register. The idea of this implementation is to look at these registers in order to determine which energy mode to go to. A peripheral module can not possibly be in use if it is clock is disabled in these registers. If all high frequency clocks are turned of in the CMU, then it is safe to go to EM2, where the high frequency clock is turned off. In the HFCORECLKEN0 register the only peripheral that needs to be checked is AES. The other modules need not be checked, since the DMA will keep the core awake automatically if it is in use. The PRS can only be accessed by the core or DMA. In the HFPERCLKEN0 register GPIO clock bit can be disregarded. Even if the GPIO clock is enabled energy mode 2 can still be entered.

The implementation of this becomes very simple.

```

if((CMU->HFCORECLKENO & CMU_HFCORECLKENO_AES) || (CMU->HFPERCLKENO

& ~CMU_HFPERCLKENO_GPIO)){

//Go to EM1

}else{

//Go to EM2

}

```

### 5.2 #2 Explicit control