# Parallel query evaluation on multicore architectures

Ulf Lilleengen

Master of Science in Computer Science Submission date: June 2010 Supervisor: Lasse Natvig, IDI Co-supervisor: Cyril Banino Rokkones, Yahoo! Technologies Norway A/ S

Norwegian University of Science and Technology Department of Computer and Information Science

## **Problem Description**

The introduction of multicore architectures brings the promise of great performance at low cost. However, achieving high performance on multicores requires an adequate application model, i.e. with a level of parallelism in line with the underlying hardware architecture. Tuning for multicore requires insights into complex resource sharing (e.g., caches and bandwidth) and thread interaction (e.g., synchronization, coherence and false sharing) and the application workload.

This project is an experimental redesign of a search engine threading model for multicore processors. The main goal of this project is to implement an alternative thread parallelisation based on a per-core index partitioning scheme for the search core in Vespa, and evaluate its performance compared to today's model.

The project is in cooperation with Yahoo! Technologies Norway AS (YTN), who wants to optimize performance of its search engine (Vespa) on multicore architectures.

Assignment given: 15. January 2010 Supervisor: Lasse Natvig, IDI

#### Abstract

Multicore processors are common in server systems sold today. Writing application software that takes advantage of such systems, not to mention adopting existing software to the parallel domain, is complex. Workloads such as web servers, database servers and search engines are easy to parallelize, because each incoming client may be handled in a separate thread of execution. However, as as cache coherence schemes on multicore processors do not scale with the number of cores, new ways of scaling existing applications may be needed to make better use of the cache hierarchy.

This study evalutes an alternative method of running search engine queries in a search engine core developed by Yahoo! Technologies Norway. The method seeks to lower query latencies and average memory access times of the search core by making better use of multicore processor caches. Through the study of Vespa, the search engine platform used at Yahoo!, and techniques for using processor caches as good as possible, an alternative design based on parallel query evaluation is proposed. The design is evaluated in a simulator of the search engine core and tested in different configurations. The performance of the alternative design depends highly on the workload. However, the alternative design can be configured to act as the existing design, which makes it possible to get the best of both worlds.

### Preface

This thesis was written at the Department of Computer and Information Science, Norwegian University of Science and Technology. I would like to thank my supervisors, Professor Lasse Natvig at IDI and Cyril Banino-Rokkonnes at Yahoo! Technologies Norway for their guidance and support. Thanks to Henning Baldersheim for sharing his technical expertise and experience with the Vespa search engine. I would also like to thank the employees at Yahoo! Technologies Norway and friends in the Computer Architecture group at IDI for our interesting discussions and for your support.

## Contents

| 1        | Inti | oducti |                                                                                                                                         |

|----------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  |        | $ment interpretation \dots \dots$ |

|          | 1.2  | Main   | contributions $\ldots \ldots 3$                                          |

|          | 1.3  | Repor  | t outline                                                                                                                               |

| <b>2</b> | Bac  | kgrou  | nd and state of the art 5                                                                                                               |

|          | 2.1  | Search | n engines                                                                                                                               |

|          |      | 2.1.1  | Retrieval                                                                                                                               |

|          |      | 2.1.2  | Indexing                                                                                                                                |

|          |      | 2.1.3  | Searching                                                                                                                               |

|          | 2.2  | Vespa  |                                                                                                                                         |

|          |      | 2.2.1  | Indexing                                                                                                                                |

|          |      | 2.2.2  | Disk index and attributes                                                                                                               |

|          |      | 2.2.3  | Query Result Server                                                                                                                     |

|          |      | 2.2.4  | Top Level Dispatch                                                                                                                      |

|          |      | 2.2.5  | The Vespa search node                                                                                                                   |

|          |      | 2.2.6  | Vespamalloc                                                                                                                             |

|          |      | 2.2.7  | Radix sort                                                                                                                              |

|          | 2.3  | Multic | core processors and cache coherency                                                                                                     |

|          |      | 2.3.1  | Cache coherence                                                                                                                         |

|          |      | 2.3.2  | Cache affinity                                                                                                                          |

|          |      | 2.3.3  | Software techniques for improving multicore performance 16                                                                              |

|          | 2.4  | Measu  | ring effects on the cache hierarchy                                                                                                     |

|          |      | 2.4.1  | Central Processing Unit (CPU) simulators                                                                                                |

|          |      | 2.4.2  | Performance counters                                                                                                                    |

|          |      | 2.4.3  | Comparing against the target platform                                                                                                   |

|          | 2.5  | Softwa | are profiling tools                                                                                                                     |

|          |      | 2.5.1  | Profiling tools using performance counters                                                                                              |

|          |      | 2.5.2  | Valgrind                                                                                                                                |

|          |      | 2.5.3  | What kind of profiling tool to use?                                                                                                     |

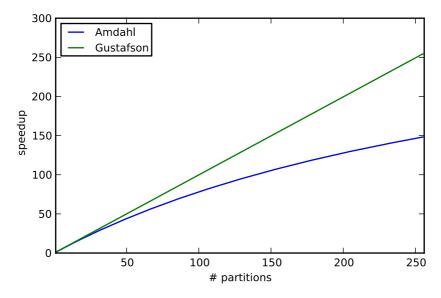

|          | 2.6  | Amda   | hl's and Gustafson's law 22                                                                                                             |

|          | 2.7  |        | are libraries                                                                                                                           |

|          |      | 2.7.1  | POSIX Threading library 24                                                                                                              |

|          |      | 2.7.2  | Affinity APIs                                                                                                                           |

| 3        | Ves | pa search core design                                           | <b>27</b> |

|----------|-----|-----------------------------------------------------------------|-----------|

|          | 3.1 | Query evaluation strategies                                     | 27        |

|          | 3.2 | Query evaluation in the Vespa search core                       | 28        |

|          | 3.3 | Parts eligible for parallelisation                              | 30        |

|          | 3.4 | Alternative query evaluation design                             | 30        |

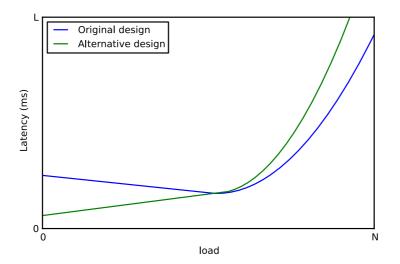

|          |     | 3.4.1 Cache effects                                             | 31        |

|          |     | 3.4.2 Latency effects                                           | 33        |

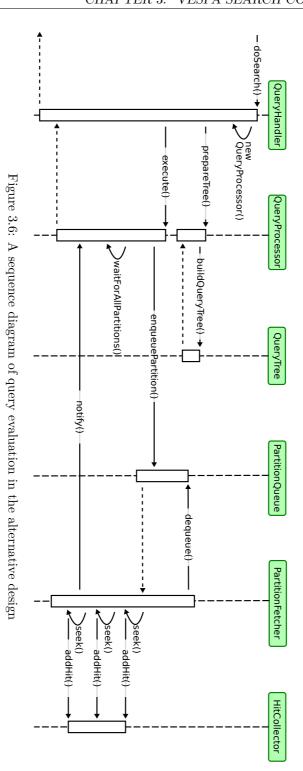

|          |     | 3.4.3 Parallel query evaluation in the Vespa search core        | 33        |

|          | 3.5 | Using Amdahl's and Gustafson's law                              | 35        |

|          | 3.6 | Implications of parallel query evaluation                       | 35        |

| 4        | Vsi | m - Vespa search core simulator                                 | 37        |

|          | 4.1 | Considerations regarding language and tools                     | 37        |

|          |     | 4.1.1 Boost                                                     | 38        |

|          | 4.2 | Simulator requirements                                          | 38        |

|          | 4.3 | Development methodology                                         | 39        |

|          | 4.4 | User interface                                                  | 40        |

|          |     | 4.4.1 Vsim output                                               | 42        |

|          | 4.5 | Software design                                                 | 43        |

|          |     | 4.5.1 Vsim overview                                             | 43        |

|          |     | 4.5.2 Partitions, slots and hit distributions                   | 44        |

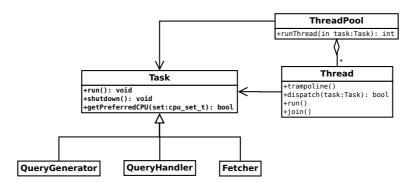

|          |     | 4.5.3 General framework code                                    | 44        |

|          |     | 4.5.4 Query generators and query data                           | 45        |

|          |     | 4.5.5 Document storage and ranking                              | 47        |

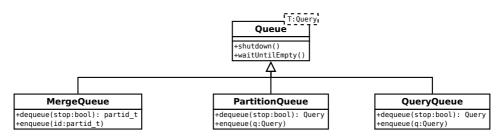

|          |     | 4.5.6 Queue generalizations                                     | 48        |

|          |     | 4.5.7 Vsim threading model                                      | 49        |

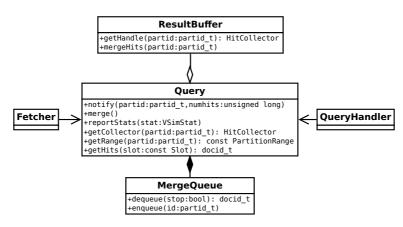

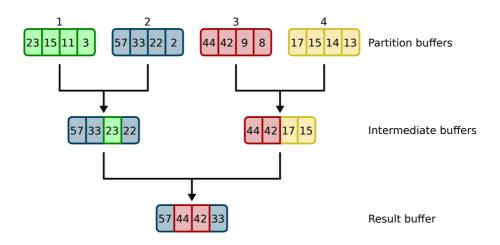

|          |     | 4.5.8 Collecting hits and storing the result                    | 50        |

|          |     | 4.5.9 Autopartitioning                                          | 52        |

|          |     | 4.5.10 Simulation setup and configuration management            | 53        |

|          |     | 4.5.11 Collecting statistics and generating a simulation report | 54        |

|          | 4.6 | Alternative designs and ideas                                   | 54        |

|          |     | 4.6.1 Parallel merge                                            | 54        |

|          |     | 4.6.2 Experimenting with alternative HitCollector implementa-   |           |

|          |     | tions                                                           | 55        |

|          | 4.7 | Initial flaws                                                   | 55        |

|          | 4.8 | Accuracy of Vsim model                                          | 55        |

| <b>5</b> | Eva | luation methodology                                             | 57        |

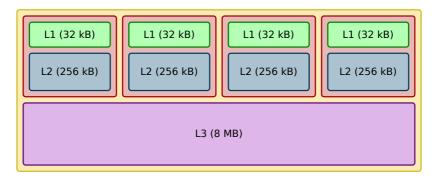

|          | 5.1 | Target platform                                                 | 57        |

|          |     | 5.1.1 Intel Xeon E5530                                          | 58        |

|          | 5.2 | Performance counters                                            | 58        |

|          | 5.3 | OProfile                                                        | 60        |

|          | 5.4 | Basic metrics used to evaluate Vsim                             | 61        |

|          |     | 5.4.1 Throughput                                                | 61        |

|          |     | 5.4.2 Latency                                                   | 61        |

|          |     | 5.4.3 Speedup and efficiency                                    | 61        |

|   |      | 5.4.4          | Average memory access time                                                                            | 62       |

|---|------|----------------|-------------------------------------------------------------------------------------------------------|----------|

| 6 | Exp  | erimei         | nts                                                                                                   | 63       |

|   | 6.1  | Vsim p         | parameters                                                                                            | 63       |

|   | 6.2  | Scalab         | bility                                                                                                | 63       |

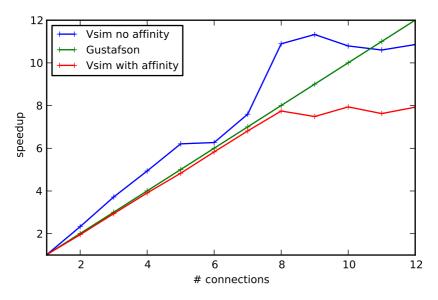

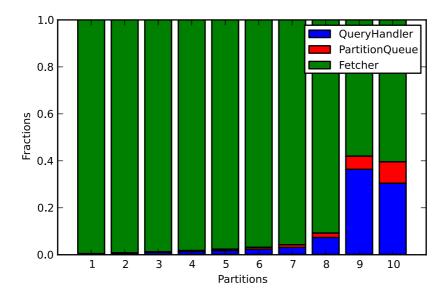

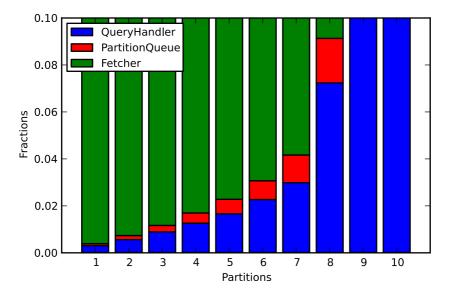

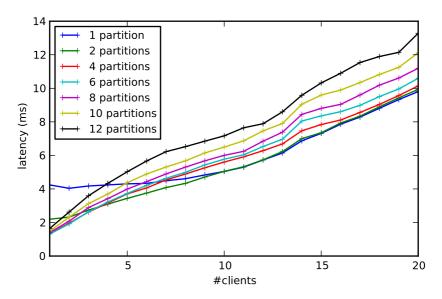

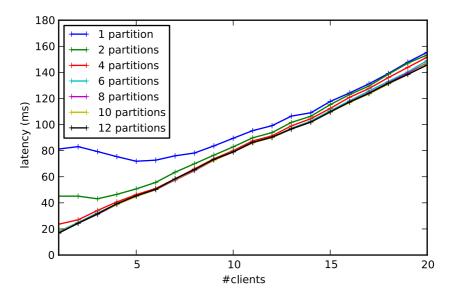

|   |      | 6.2.1          | Scalability of query handlers                                                                         | 64       |

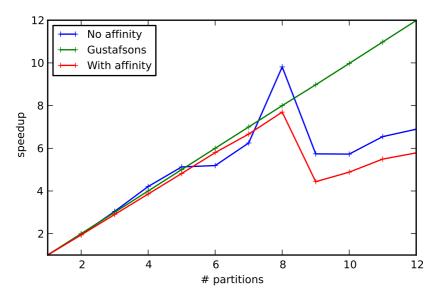

|   |      | 6.2.2          | Scalability of parallel query evaluation                                                              |          |

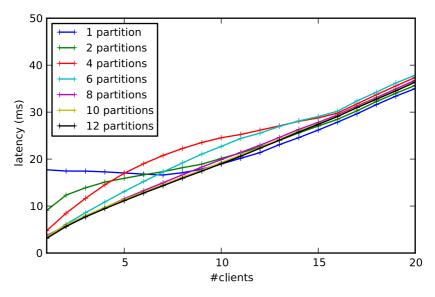

|   | 6.3  | Perfor         | mance of parallel query evaluation                                                                    |          |

|   |      | 6.3.1          | Using the same number of hits per query                                                               |          |

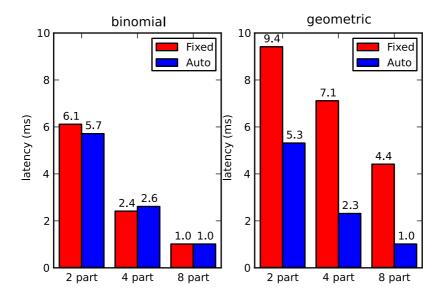

|   |      | 6.3.2          | Using Query Result Server (QRS) logs from Yahoo! News                                                 |          |

|   |      | 6.3.3          | Using QRS logs from Yahoo! Image Search                                                               |          |

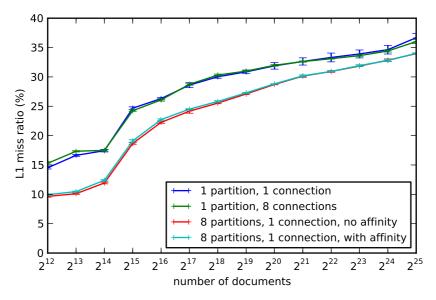

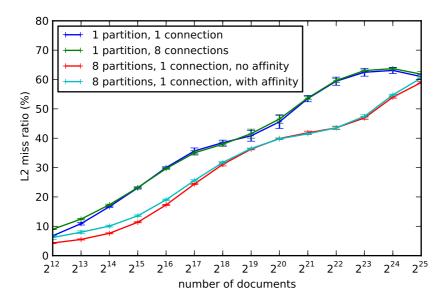

|   | 6.4  | Behav          | ior of the cache hierarchy                                                                            |          |

|   |      | 6.4.1          | L1 cache miss ratio                                                                                   |          |

|   |      | 6.4.2          | L2 cache miss ratio                                                                                   | 74       |

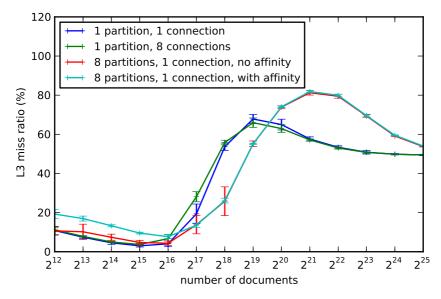

|   |      | 6.4.3          | L3 cache miss ratio                                                                                   |          |

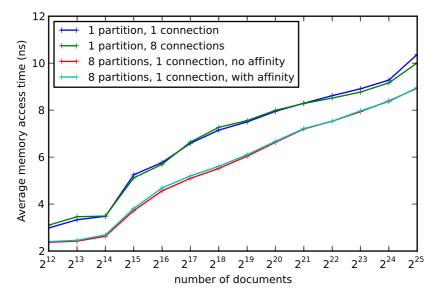

|   |      | 6.4.4          | Average memory access time                                                                            | 77       |

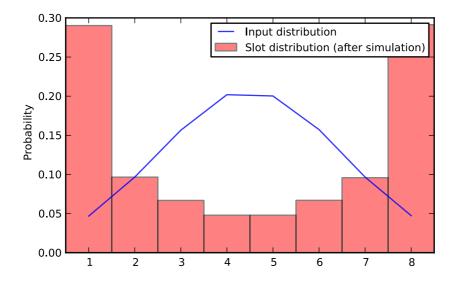

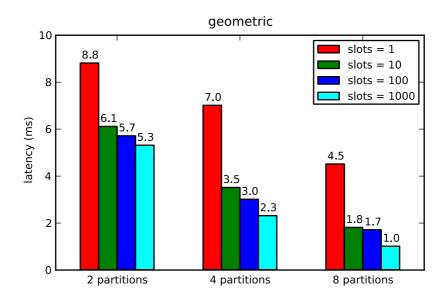

|   | 6.5  | The in         | npact of slots and autopartitioning                                                                   | 77       |

|   | 6.6  | Discus         | ssion                                                                                                 | 79       |

| 7 | Con  | clusio         | n and further work                                                                                    | 83       |

| • | 7.1  |                | usion                                                                                                 |          |

|   | 7.2  |                | er work                                                                                               |          |

|   |      |                |                                                                                                       |          |

| Α | Add  | litional       | l notes                                                                                               | 91       |

|   | A.1  |                | alternative designs and ideas                                                                         |          |

|   |      | A.1.1          | Alternative HitCollector implementations                                                              |          |

|   |      | A.1.2          | Allocating a ${\tt QueryHandler}\ {\tt and}\ {\tt Fetchers}\ {\tt for}\ {\tt each}\ {\tt Query}\ .$ . |          |

|   | A.2  |                | flaws in Vsim $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$          |          |

|   |      | A.2.1          | Performing result sorting instead of merging in the QueryHandle                                       |          |

|   |      | A.2.2          | Initial implementation of the VSimStore                                                               |          |

|   | A.3  | Techni         | iques to promote effective cache reuse                                                                | 94       |

| в | Clai | rificati       | ons                                                                                                   | 95       |

|   | B.1  | Perfor         | mance counter mappings                                                                                | 95       |

| С | Cod  |                |                                                                                                       | 97       |

| U |      |                | source code                                                                                           |          |

|   | 0.1  | C.1.1          | barrier.h.                                                                                            |          |

|   |      | C.1.2          | barrier.cpp                                                                                           | 97       |

|   |      | C.1.2          | cond.h                                                                                                | 98       |

|   |      | C.1.3<br>C.1.4 | cond.cpp                                                                                              | 98<br>98 |

|   |      | C.1.4          | fetcher.h                                                                                             | 99       |

|   |      | C.1.6          | fetcher.cpp                                                                                           |          |

|   |      | C.1.7          | hitcollector.h                                                                                        |          |

|   |      | C.1.8          | hitcollector.cpp                                                                                      |          |

|   |      | C.1.9          | hitvector.h                                                                                           |          |

|   |      |                | meteotolim to                                                     |          |

|     | C.1.10 hitvector.cpp                                                                                           |     | . 106 |

|-----|----------------------------------------------------------------------------------------------------------------|-----|-------|

|     | C.1.11 main.cpp                                                                                                | •   | . 107 |

|     | C.1.12 mergequeue.h                                                                                            | •   | . 111 |

|     | C.1.13 misc.h                                                                                                  |     | . 112 |

|     | C.1.14 misc.cpp                                                                                                |     | . 112 |

|     | C.1.15 mutex.h                                                                                                 |     | . 112 |

|     | C.1.16 mutex.cpp                                                                                               |     | . 113 |

|     | C.1.17 partitionqueue.h                                                                                        |     | . 113 |

|     | C.1.18 query.h                                                                                                 |     | . 115 |

|     | C.1.19 query.cpp                                                                                               |     | . 116 |

|     | C.1.20 querygenerator.h                                                                                        |     | . 118 |

|     | C.1.21 querygenerator.cpp                                                                                      |     | . 120 |

|     | C.1.22 queryhandler.h                                                                                          |     | . 122 |

|     | C.1.23 queryhandler.cpp                                                                                        |     |       |

|     | C.1.24 queryqueue.h                                                                                            |     |       |

|     | C.1.25 queue.h                                                                                                 |     |       |

|     | C.1.26 resultbuffer.h                                                                                          |     |       |

|     | C.1.27 resultbuffer.cpp                                                                                        |     |       |

|     | C.1.28 simendian.h                                                                                             |     |       |

|     | C.1.29 spinlock.h                                                                                              |     | . 128 |

|     | C.1.30 spinlock.cpp                                                                                            |     | . 129 |

|     | C.1.31 task.h                                                                                                  |     | . 130 |

|     | C.1.32 thread.h                                                                                                |     | . 130 |

|     | C.1.33 thread.cpp $\ldots$    |     | . 131 |

|     | C.1.34 threadpool.h                                                                                            |     | . 133 |

|     | C.1.35 threadpool.cpp                                                                                          |     | . 133 |

|     | C.1.36 types.h                                                                                                 |     | . 134 |

|     | C.1.37 vsimconfig.h.                                                                                           |     | . 135 |

|     | C.1.38 vsimconfig.cpp                                                                                          |     |       |

|     | C.1.39 vsim.h                                                                                                  |     |       |

|     | C.1.40 vsim.cpp                                                                                                |     | . 139 |

|     | C.1.41 vsimprofiler.h                                                                                          |     |       |

|     | C.1.42 vsimprofiler.cpp                                                                                        |     | . 143 |

|     | C.1.43 vsimreport.h                                                                                            |     | . 143 |

|     | C.1.44 vsimreport.cpp                                                                                          |     | . 144 |

|     | C.1.45 vsimseeder.h                                                                                            |     | . 148 |

|     | C.1.46 vsimseeder.cpp                                                                                          |     | . 149 |

|     | C.1.47 vsimstat.h                                                                                              |     |       |

|     | C.1.48 vsimstat.cpp                                                                                            | •   | . 151 |

|     | C.1.49 vsimstore.h                                                                                             | •   | . 155 |

|     | C.1.50 vsimstore.cpp $\ldots$ | • • | . 155 |

|     | C.1.51 vsimtime.h                                                                                              | •   | . 157 |

|     | C.1.52 vsimtime.cpp $\ldots$                                                                                   | • • | . 158 |

|     | C.1.53 printreport.cpp                                                                                         | • • | . 160 |

| C.2 | Scripts                                                                                                        | •   | . 160 |

| C.2.1 | Simreport Python | interface f | for sample | files |  |  |  |  |  |  |  |  |  |  | 16 | 30 |

|-------|------------------|-------------|------------|-------|--|--|--|--|--|--|--|--|--|--|----|----|

|-------|------------------|-------------|------------|-------|--|--|--|--|--|--|--|--|--|--|----|----|

## List of Figures

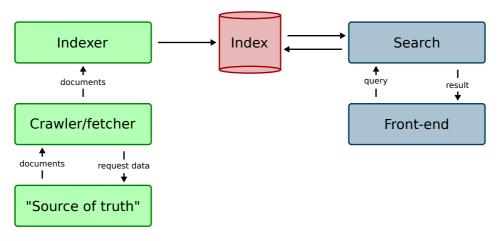

| 2.1  | A generalized search engine architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

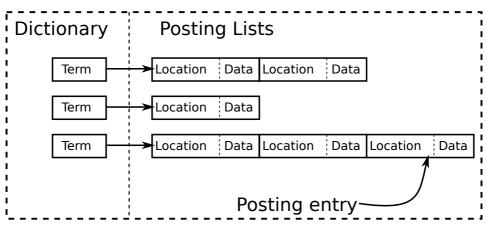

| 2.2  | An inverted index (inspired from [FLQZ06])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7  |

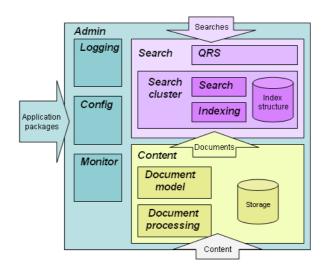

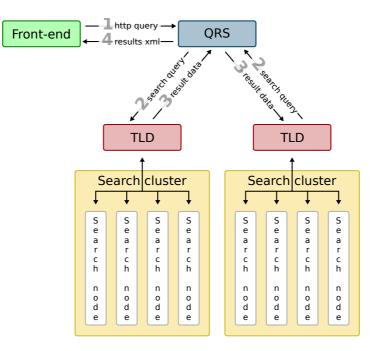

| 2.3  | An overview of Vespa [VES10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8  |

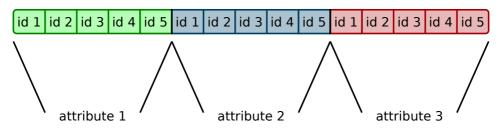

| 2.4  | Attributes stored in memory. Each attribute is represented with a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | vector with entries for all doc ids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10 |

| 2.5  | Data flow in Vespa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 |

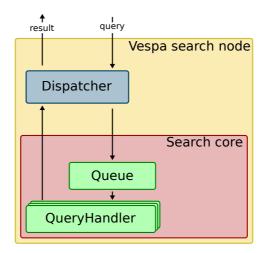

| 2.6  | An overview of a Vespa search node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 12 |

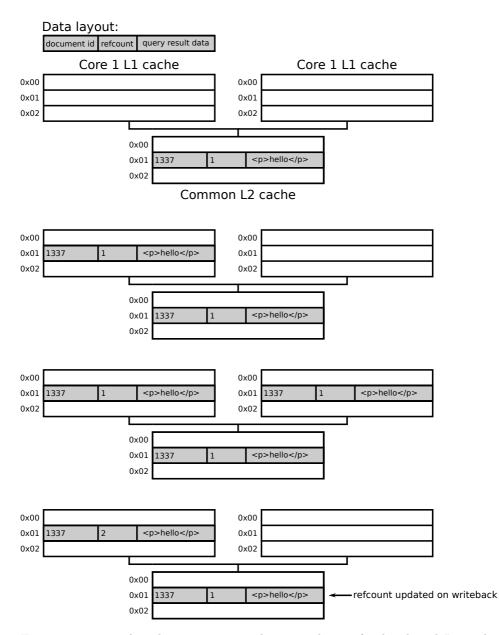

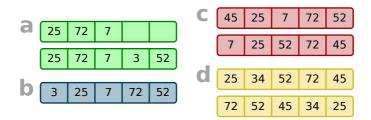

| 2.7  | Two threads try to access the same data. a) The shared L2 cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | contains result data. b) Thread running on core 1 loads data into                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | its L1 cache. c) Thread running on core 2 loads the same data into                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|      | its L1 cache. d) Thread on core 1 increases reference count and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | invalidates cache line in the L1 cache of core 2. Eventually, the second core has to reload the cache line from the level-2 cache to get                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | the correct copy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15 |

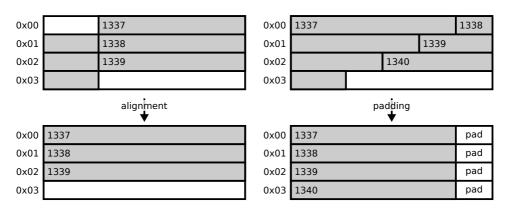

| 2.8  | Alignment (to the left) and padding (to the right) of data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

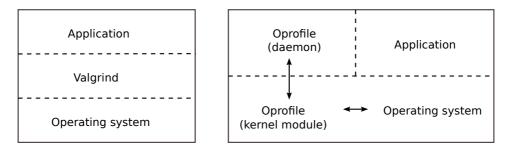

| 2.9  | Comparing OProfile and Valgrind(from [Lil09])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22 |

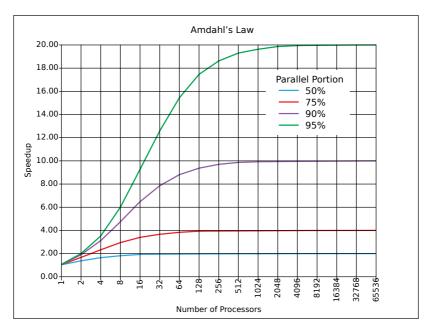

| 2.10 | The speedup of an application with different portions of parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|      | according to Amdahl's law [Dan09]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23 |

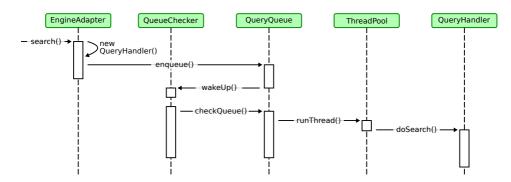

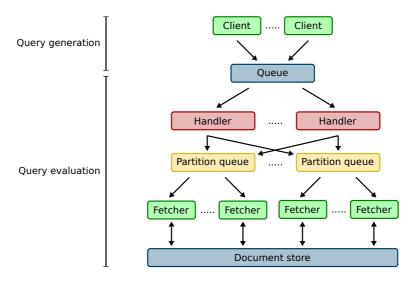

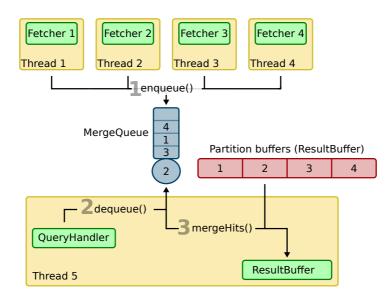

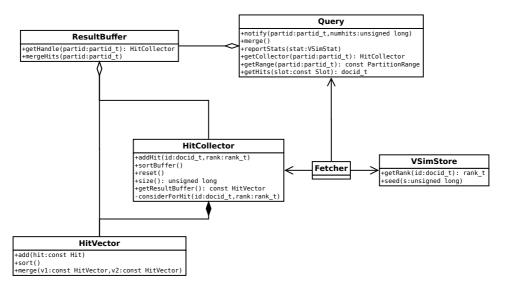

| 3.1  | A sequence diagram of query dispatching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28 |

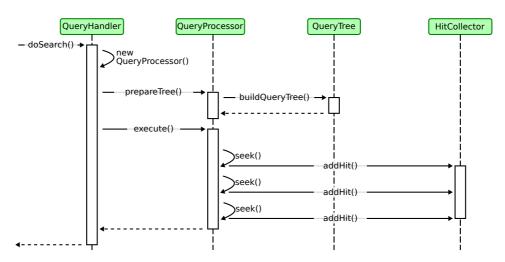

| 3.2  | A sequence diagram of query evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29 |

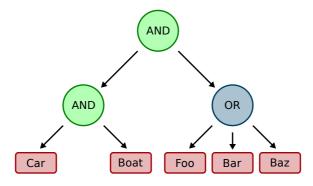

| 3.3  | An example of a query tree from the following query: ("Foo" OR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | "Bar" OR "Baz") AND ("Car" AND "Boat")                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29 |

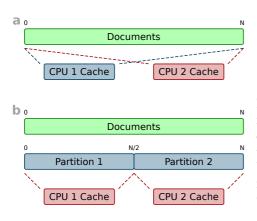

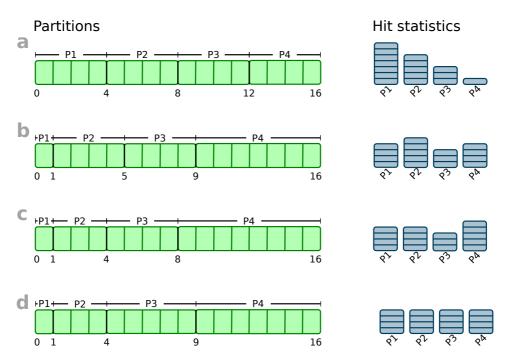

| 3.4  | The mapping of the doc id range to partitions for a) The original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|      | design, where each CPU cache will contain data from the whole                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|      | document range. b) The alternative design, where the range is split                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |