#### **Abstract**

This thesis presents the architecture and implementation of a high-performance floating-point coprocessor for Atmel's new microcontroller.

The coprocessor architecture is based on a fused multiply-add pipeline developed in the specialization project, TDT4720. This pipeline has been optimized significantly and extended to support negation of all operands and single-precision input and output. New hardware has been designed for the decode/fetch unit, the register file, the compare/convert pipeline and the approximation tables. Division and square root is performed in software using Newton-Raphson iteration.

The Verilog RTL implementation has been synthesized at 167 MHz using a 0.18  $\mu$ m standard cell library. The total area of the final implementation is 107 225 gates. The coprocessor has also been synthesized with the CPU.

Test-programs have been run to verify that the coprocessor works correctly. A complete verification of the floating-point coprocessor, however, has not been performed due to limitations in time.

### **Preface**

I would like to thank my supervisor Erik Renno and Andreas Engh-Halstvedt at Atmel Norway for giving me helpful advice and active support during the work on this thesis. I would also like to thank professor Lasse Natvig at the Department of Computer and Information Science at NTNU for providing good feedback on the thesis text.

# **Contents**

| 1 | Intr | oductio | on                                                                       | 1  |

|---|------|---------|--------------------------------------------------------------------------|----|

|   | 1.1  | Task I  | Description                                                              | 1  |

|   | 1.2  | A Sho   | ort Introduction to Floating-point Numbers and Floating-point Hardware . | 2  |

|   | 1.3  | Backg   | round for this Thesis                                                    | 4  |

|   | 1.4  | Goals   | for this Thesis                                                          | 4  |

|   | 1.5  | Outlin  | ne                                                                       | 4  |

| 2 | Bac  | kgroun  | đ                                                                        | 7  |

|   | 2.1  | IEEE S  | Standard for Binary Floating-Point Arithmetic (ANSI/IEEE 754-1985)       | 7  |

|   |      | 2.1.1   | IEEE 754 Floating-point Implementation-practice                          | 7  |

|   |      | 2.1.2   | Formats and Encoding                                                     | 8  |

|   |      | 2.1.3   | Rounding                                                                 | 10 |

|   |      | 2.1.4   | Operations                                                               | 10 |

|   |      | 2.1.5   | Exceptions                                                               | 11 |

|   |      | 2.1.6   | Traps                                                                    | 12 |

|   |      | 2.1.7   | IEEE 754 and the ISO C Standard                                          | 12 |

|   |      | 2.1.8   | Mapping Floating-point Numbers to the Real Number Line                   | 12 |

|   | 2.2  | The II  | EEE 754 Revision                                                         | 13 |

|   |      | 2.2.1   | Purpose                                                                  | 14 |

|   |      | 2.2.2   | Current Changes and Additions                                            | 15 |

|   |      | 2.2.3   | Quadruple-precision Floating-point                                       | 15 |

|   |      | 2.2.4   | Fused Multiply-Add                                                       | 15 |

|   |      | 2.2.5   | Other Proposed Additions                                                 | 16 |

|   | 2.3  | Embe    | dded FPU Implementations                                                 | 16 |

|   |      | 2.3.1   | Throughput and Latency                                                   | 16 |

## **CONTENTS**

|   |      | 2.3.2    | ARM VFP9-S                                    | 16 |

|---|------|----------|-----------------------------------------------|----|

|   |      | 2.3.3    | MIPS32 24Kf FPU                               | 18 |

|   |      | 2.3.4    | IBM PowerPC 603e FPU                          | 19 |

| 3 | Arcl | nitectui | re                                            | 23 |

|   | 3.1  | Backg    | round for the Architecture Design             | 23 |

|   | 3.2  | Requi    | rements for the Architecture                  | 23 |

|   | 3.3  | Prope    | rties of the Architecture                     | 25 |

|   | 3.4  | Target   | Processor                                     | 25 |

|   | 3.5  | Instru   | ction Set                                     | 26 |

|   |      | 3.5.1    | Arithmetic                                    | 26 |

|   |      | 3.5.2    | Compare                                       | 27 |

|   |      | 3.5.3    | Convert                                       | 28 |

|   |      | 3.5.4    | Approximation Instructions                    | 28 |

|   |      | 3.5.5    | Move and Load-Constant                        | 28 |

|   |      | 3.5.6    | Supported Formats                             | 29 |

|   |      | 3.5.7    | Implemented Instruction Set                   | 29 |

|   |      | 3.5.8    | Encoding                                      | 29 |

|   |      | 3.5.9    | Load/Store                                    | 29 |

|   | 3.6  | IEEE 7   | 754 Compliance                                | 30 |

|   | 3.7  | Datap    | ath and Main Building Blocks                  | 31 |

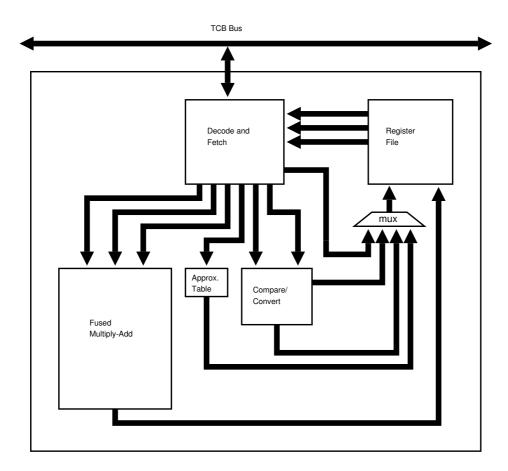

|   |      | 3.7.1    | Top Level                                     | 31 |

|   |      | 3.7.2    | Tightly Coupled Bus                           | 33 |

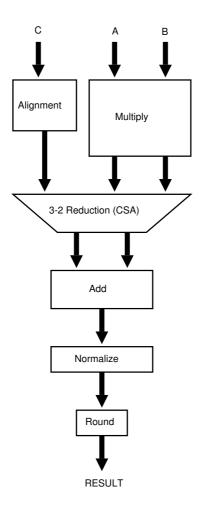

|   |      | 3.7.3    | Fused Multiply-Add (FMA)                      | 33 |

|   |      | 3.7.4    | Decode/Fetch                                  | 36 |

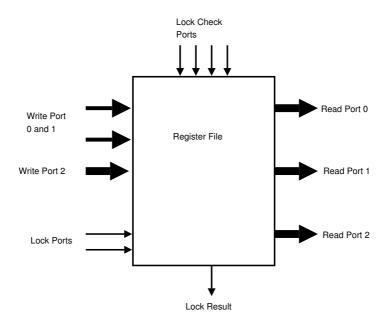

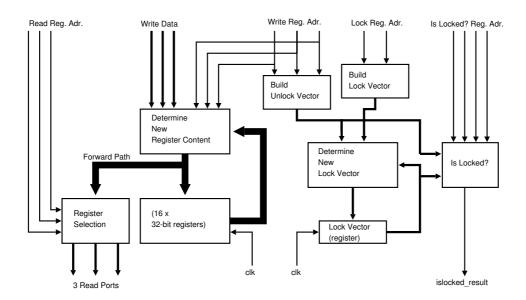

|   |      | 3.7.5    | The Register File                             | 36 |

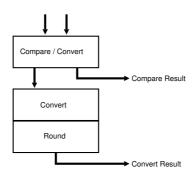

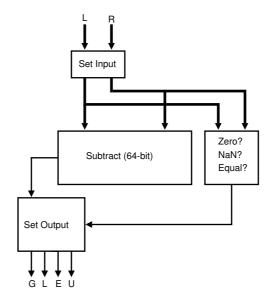

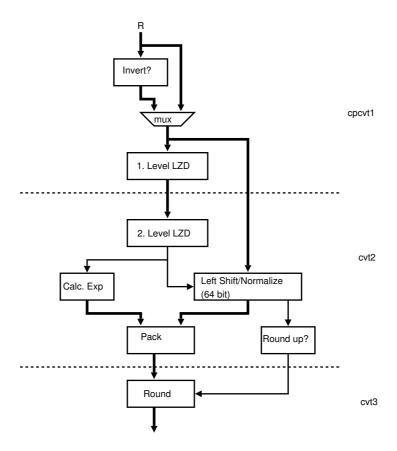

|   |      | 3.7.6    | Compare/Convert                               | 39 |

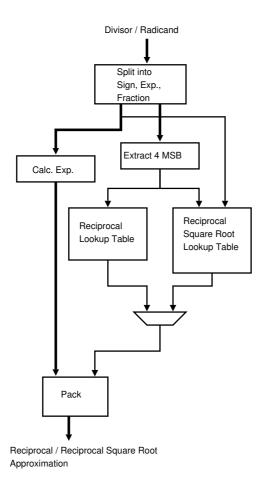

|   |      | 3.7.7    | Approximation Table                           | 40 |

|   | 3.8  | Instru   | ction Execution                               | 40 |

|   |      | 3.8.1    | Writing To a Coprocessor Register             | 40 |

|   |      | 3.8.2    | Reading From a Coprocessor Register           | 41 |

|   |      | 3.8.3    | FMA                                           | 41 |

|   |      | 3.8.4    | Compare                                       | 41 |

|   |      | 3.8.5    | Conversion Between Integer and Floating-point | 41 |

|   |      | 3.8.6    | Approximation                            | 42 |

|---|------|----------|------------------------------------------|----|

|   | 3.9  | Divisi   | on and Square Root                       | 42 |

| 4 | Imp  | lement   | ration                                   | 47 |

|   | 4.1  | Imple    | mentation Requirements                   | 47 |

|   | 4.2  | Verilo   | g Code Conventions                       | 48 |

|   | 4.3  | Design   | nWare Building Block IP                  | 48 |

|   | 4.4  | The R    | ound-, Guard- and Sticky-bit             | 49 |

|   | 4.5  | Modu     | le Descriptions                          | 49 |

|   |      | 4.5.1    | Top Level and Decode/Fetch (fpcp)        | 50 |

|   |      | 4.5.2    | The Fused Multiply-Add Pipeline (fma)    | 53 |

|   |      | 4.5.3    | Compare/Convert Pipeline (cpcvt)         | 56 |

|   |      | 4.5.4    | The Approximation Tables Module (apx)    | 57 |

|   |      | 4.5.5    | The Register File Module (fpr)           | 61 |

|   |      | 4.5.6    | Write Unit (wr)                          | 63 |

|   | 4.6  | Unim     | plemented Functionality                  | 63 |

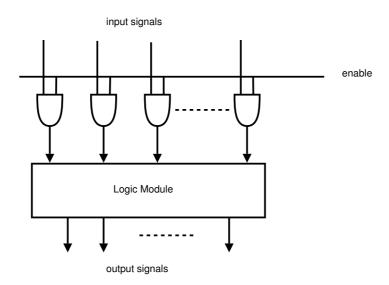

|   | 4.7  | Optim    | nizing for Low Power Consumption         | 64 |

|   |      | 4.7.1    | Power-reduction Strategies               | 64 |

|   |      | 4.7.2    | Reducing Power in the Design             | 65 |

|   |      | 4.7.3    | Potential Improvements (not Implemented) | 67 |

|   | 4.8  | Synth    | esis                                     | 67 |

| 5 | Veri | fication | 1                                        | 69 |

|   | 5.1  |          | nulation with the CPU                    | 69 |

|   | 5.2  |          | in Macros                                | 70 |

|   |      | 5.2.1    | Moving Data into Coprocessor Registers   | 71 |

|   |      | 5.2.2    | Moving Data from Coprocessor Registers   | 71 |

|   |      | 5.2.3    | Sending Commands to the Coprocessor      | 71 |

|   | 5.3  | Test P   | rograms                                  | 71 |

|   |      | 5.3.1    | asm_test                                 | 71 |

|   |      | 5.3.2    | test                                     | 72 |

|   |      | 5.3.3    | test_fused                               | 73 |

|   |      | 5.3.4    | test_approx                              | 73 |

|   |      | 5.3.5    | cpuflushed_test                          | 74 |

|   |      |          |                                          |    |

## **CONTENTS**

|   |      | 5.3.6 test_dotprod                              | 74 |

|---|------|-------------------------------------------------|----|

|   | 5.4  | FMA Pipeline Verification                       | 74 |

|   | 5.5  | Floating-point Test Software                    | 74 |

|   | 5.6  | Utility Programs                                | 75 |

|   |      | 5.6.1 fdata                                     | 75 |

|   |      | 5.6.2 fcvt                                      | 75 |

|   |      | 5.6.3 arith                                     | 75 |

|   |      | 5.6.4 approx                                    | 75 |

| 6 | Res  | ults                                            | 77 |

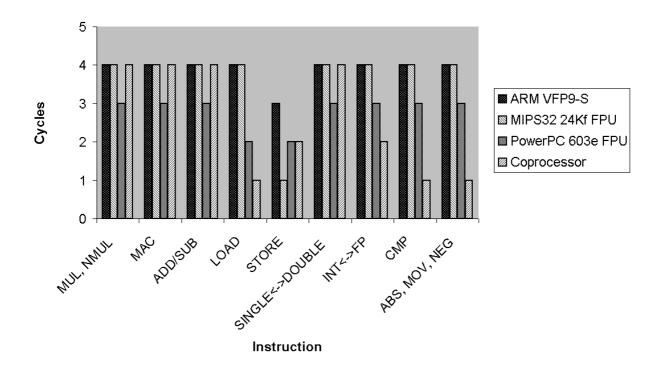

|   | 6.1  | Latency                                         | 77 |

|   | 6.2  | Throughput                                      | 81 |

|   | 6.3  | Functionality                                   | 83 |

|   | 6.4  | Performance of Typical Embedded Applications    | 83 |

|   | 6.5  | Other Criteria for a Good Implementation        | 84 |

|   | 6.6  | IEEE 754 Compliance Summary                     | 85 |

|   | 6.7  | Synthesis Results                               | 85 |

|   |      | 6.7.1 The Effect of Clock Gating                | 89 |

|   |      | 6.7.2 Synthesizing CPU and Coprocessor Together | 89 |

| 7 | Futı | ure Work                                        | 91 |

| 8 | Con  | aclusion                                        | 93 |

|   | 8.1  | Project Experiences                             | 94 |

# **List of Figures**

| 2.1  | The IEEE 754 Single Format                                                  | 8  |

|------|-----------------------------------------------------------------------------|----|

| 2.2  | The IEEE 754 Double Format                                                  | 8  |

| 2.3  | Single-precision Floating-point Exponent Ranges from $[1,2^1)$ to $+\infty$ | 13 |

| 2.4  | Single-precision Floating-point Negative Exponent Ranges                    | 13 |

| 2.5  | The Quadruple Floating-point Format                                         | 15 |

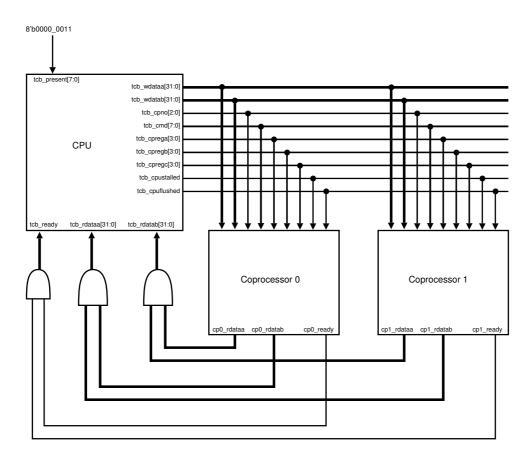

| 3.1  | Coprocessor Top Level Architecture                                          | 32 |

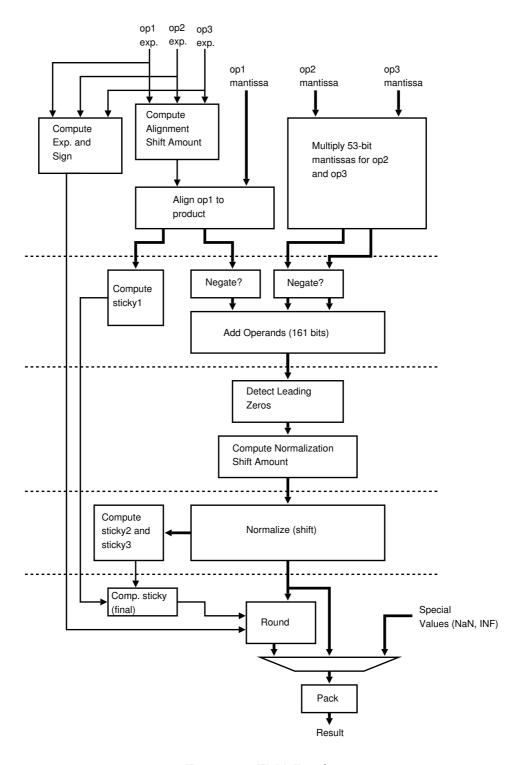

| 3.2  | Fused Multiply-Add Datapath                                                 | 34 |

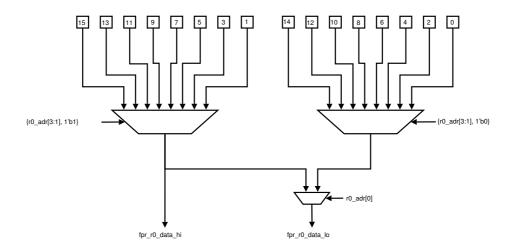

| 3.3  | Register File                                                               | 37 |

| 3.4  | Compare/Convert Unit                                                        | 39 |

| 4.1  | Floating-point Coprocessor Block Diagram                                    | 50 |

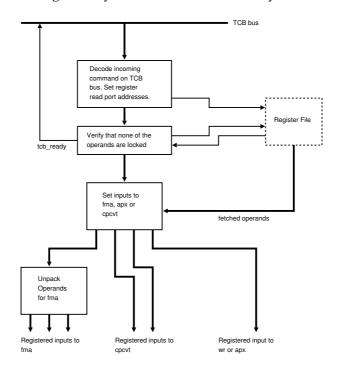

| 4.2  | Decode/Fetch Data-flow in fpcp Module                                       | 51 |

| 4.3  | Coprocessor Interfacing Using the TCB                                       | 52 |

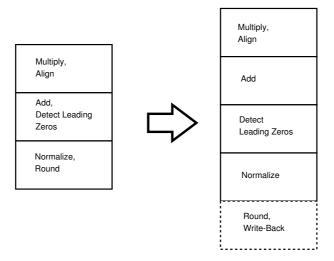

| 4.4  | Original vs. New FMA Pipeline                                               | 53 |

| 4.5  | FMA Pipeline                                                                | 55 |

| 4.6  | Compare Data-flow                                                           | 57 |

| 4.7  | Convert Data-flow                                                           | 58 |

| 4.8  | The apx Module                                                              | 60 |

| 4.9  | The fpr Module                                                              | 62 |

| 4.10 | Read Port Logic                                                             | 63 |

| 4.11 | Saving Power by Restricting Inputs to Logic Modules                         | 66 |

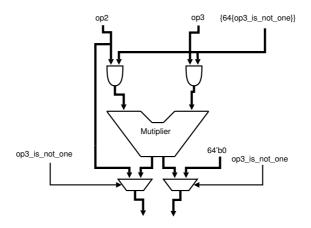

| 4.12 | Bypassing Multiplier to Save Power                                          | 67 |

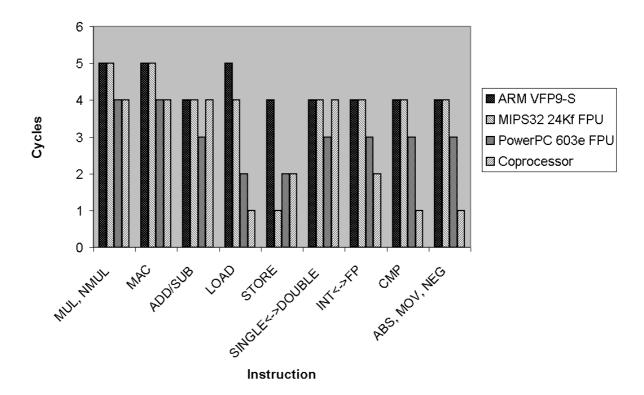

| 6.1  | Instruction Latency Comparison (single)                                     | 78 |

| 6.2  | Instruction Latency Comparison (double)                                     | 79 |

## LIST OF FIGURES

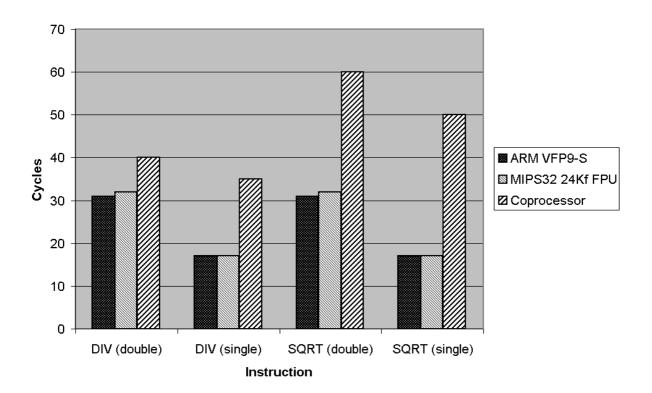

| 6.3 | Division and Square Root Latency Comparison    | 80 |

|-----|------------------------------------------------|----|

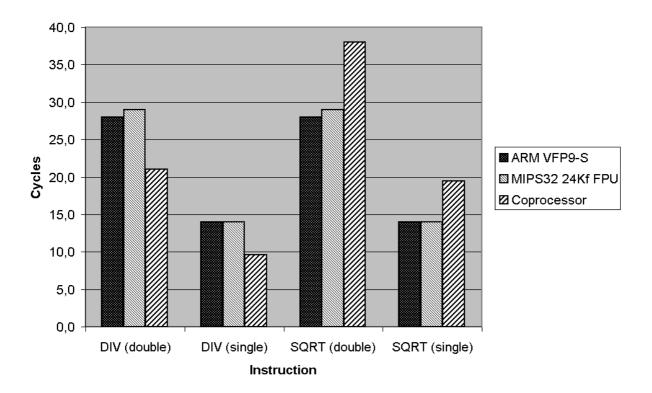

| 6.4 | Division and Square Root Throughput Comparison | 82 |

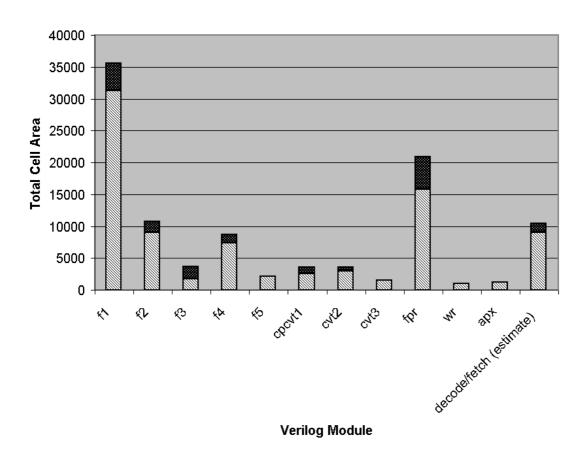

| 6.5 | Total Cell Area of Individual Modules          | 86 |

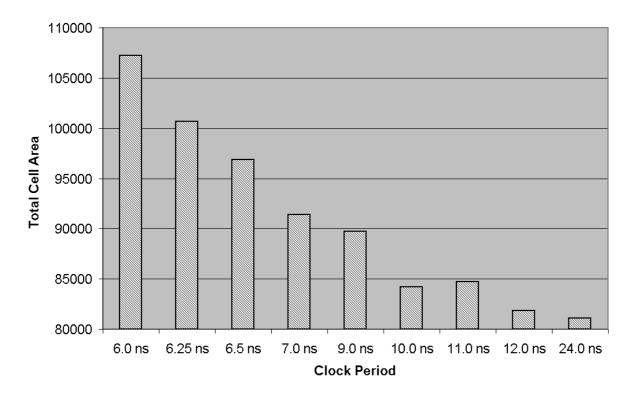

| 6.6 | Total Cell Area at Different Clock Periods     | 88 |

# **List of Tables**

| 2.1 | The Exponent Range and Bias                          | 9  |

|-----|------------------------------------------------------|----|

| 2.2 | IEEE 754 Special Values                              | 9  |

| 2.3 | Range Size and Gap Size (Single-precision)           | 13 |

| 2.4 | Quadruple Exponent Format                            | 15 |

| 2.5 | ARM VFP9-S Throughput and Latency Cycle Counts       | 18 |

| 2.6 | MIPS32 24Kf FPU Throughput and Latency Cycle Counts  | 20 |

| 2.7 | PowerPC 603e FPU Throughput and Latency Cycle Counts | 21 |

| 3.1 | Two-operand Arithmetic Instructions                  | 27 |

| 3.2 | Three-operand Fused Arithmetic Instructions          | 27 |

| 3.3 | Move-Type Instructions                               | 29 |

| 3.4 | Load Constant Instructions                           | 29 |

| 3.5 | Floating Point instruction frequency                 | 38 |

# Chapter 1

# Introduction

### 1.1 Task Description

The task was given by Atmel Norway. The full text is listed here:

"Some embedded applications are best implemented using floating-point arithmetic. Software floating-point emulation can be used in some situations but for most floating-point intensive applications this is insufficient due to strict performance requirements. Many high-end microcontrollers therefore supports floating-point instructions.

The new family of microcontrollers from Atmel supports coprocessor extensions. Atmel wants to build a *floating-point coprocessor*, based on an existing fused multiply-add unit. The coprocessor must be designed using Verilog, and synthesizable with a clock period of at most 6.0 ns (166.7 MHz) using Atmel's 0.18  $\mu$ m process technology. The implementation should, if time allows, support all operations specified in the IEEE 754 standard.

During design, trade-offs must be made between area, power consumption and performance, but the coprocessor should provide good performance. The resulting design should also be optimized for low-power and area.

The work should include:

- Defining an instruction set for the coprocessor.

- Implementing a coprocessor with a register file and data dependency detection.

- Implementing hardware for:

- Conversion between single-precision, double-precision

- Conversion between floating-point formats and integer

- Floating-point compare

- An implementation of division and square root, if time allows.

- Verification of the coprocessor implementation."

# 1.2 A Short Introduction to Floating-point Numbers and Floating-point Hardware

Real numbers are implemented as *floating-point numbers* in digital computers. In contrast to real numbers used in mathematics which represent continuous numbers with unlimited precision and range, floating-point numbers are discrete entities and have both limited precision and range. Arithmetic on floating-point numbers is usually performed by a dedicated hardware module, generally referred to as a *floating-point unit* (FPU), but can also be implemented in software utilizing a regular integer Arithmetic Logic Unit (ALU). There is however a big difference in efficiency between a hardware and a software implementation. A software implementation is much slower than a hardware counterpart. A software floating-point multiply typically takes 80 cycles and a software division takes typically about 130 cycles [5]. A typical hardware implementation, like the ARM VFP9-S [3], needs only 4-5 cycles for multiply and 17-31 cycles for division. Also, multiplications are usually pipelined. The relatively slow software implementations and the opportunity for pipelining in hardware makes floating-point arithmetic well suited for hardware implementation.

Floating-point units are now a built-in component of most modern microprocessors for desktop computers and servers. In these processors the floating-point unit is tightly integrated in the pipeline. The need for efficient floating-point calculation required in 3D graphics applications and simulation has made the floating-point unit an integral part of any competitive microprocessor. In fact, most vendors also provide multiple floating-point units that executes in parallel, in order to further increase throughput and meet the demand for higher performance.

Microcontrollers used in embedded systems have been and are still primarily designed for integer and fixed-point arithmetic. The primary reason for this is that most algorithms in embedded applications do not need floating-point calculations. Fixed-point calculation implemented using integer operations is often sufficient. Also, due to a long history with very limited support for floating-point hardware, there has been an effort throughout the industry to solve many problems which in principle requires floating-point arithmetic using integer-only instructions. The Tremor decoder library [42], for example, is an integer-only Ogg Vorbis compliant audio codec for processors without floating-point unit.

High-performance floating-point arithmetic, if needed, is usually supported by utilizing a coprocessor. A coprocessor architecture is common since very few microcontrollers have been designed with floating-point support originally. The floating-point support has been added to these processors at a later stage in response to market demands. A coprocessor does not require any change to the processor architecture. This makes it a convenient solution. Another reason for using a loosely coupled coprocessor architecture is that die area can be reduced for those parts that are manufactured without the coprocessor. This reduces the cost of these parts.

The ability to provide both large *dynamic* range and precision makes floating-point numbers attractive for many applications. Fixed-point numbers, often used to model real numbers in systems without floating-point support, have a fixed precision and range which limits their flexibility and the accuracy of the results.

Floating-point arithmetic has been standardized in the IEEE-754 Standard for Floating-point

Numbers [18] since 1985, and most implementations today follow this standard. The details of the IEEE 754 Standard are described in the next chapter.

The use of floating-point numbers in embedded applications has been limited to high-end systems for years and many battery-powered systems may not afford a floating-point unit simply due to increased power consumption. The recent announcement of Floating Point Extensions [1] from ARC International and the optional MicroBlaze v4.00 Floating Point Unit [41] from Xilinx Inc., however, clearly shows that floating-point will find its way into future embedded applications to a larger extent than before.

ARC International lists the following applications in the product brief for their new Floating Point extensions (FPX):

- Consumer Products

- 3D graphics

- Image Processing

- Imaging

- Post-script processing

- Cameras

- Communications

- GPS computations

- Impedance matching

- Automotive Control

- Powertrain control

- Antilock braking systems

- Active suspension

- Industrial Control

- Robotics and motion control

3D graphics and Automotive Control are discussed in more detail in [30, ch. 2.1]. Impedance matching is a method for maximizing the efficiency of power transfers.

Floating-point arithmetic is inherently more complex than integer arithmetic. There are several reasons for this:

The IEEE 754 Standard for Floating-point Arithmetic is quite detailed and must be studied carefully to ensure compliance.

- Several design alternatives exist. In contrast to most integer arithmetic units, floating-point units are usually pipelined. The number of pipeline stages and the level of resource sharing are only two factors that differentiates design alternatives. The design of floating-point hardware is also an active area of research both at academic institutions and in the industry and new designs are constantly being presented at conferences around the world. Most new advances in computer arithmetic are presented at the yearly IEEE Symposium on Computer Arithmetic.

- Due to the complexity of a floating-point unit, thorough verification is needed to ensure correct operation. The time spent on verification can thus contribute significantly to the total development time. A separate chapter of this thesis describes verification.

Designing floating-point hardware is therefore a complex engineering task that require much effort and includes the evaluation of many trade-offs.

## 1.3 Background for this Thesis

Fall 2004 I designed and implemented a floating-point arithmetic core for Atmel Norway as part of my 5th year specialization project (TDT 4720) [30]. The core was a double-precision Fused Multiply-Add unit. A natural continuation of this work was to integrate the Fused Multiply-Add unit in a Coprocessor. This thesis therefore builds on previous work for Atmel Norway.

#### 1.4 Goals for this Thesis

The goal for this thesis is to design an architecture for a high-performance floating-point coprocessor and implement a subset of this architecture. The implementation will show whether or not the proposed architecture also meets the timing requirements of the target processor with which the coprocessor is to be integrated. An accurate estimate of area requirements for the architecture will also be possible based on the implemented subset. The performance and area of the implemented architecture should be comparable to and possibly better than relevant implementations of the ARM, MIPS and PowerPC architectures.

#### 1.5 Outline

In chapter two the IEEE 754 standard for Binary Floating-point Numbers is described along with a description of the new revision of the IEEE 754 standard. The new revision is not yet finished, but will be completed in December 2005. In the end of the chapter the floating-point units (FPUs) for three state-of-the-art architectures are described and compared. The third chapter describes the architecture for the floating-point coprocessor. Chapter four then describes the implementation. Low-power techniques and synthesis is also discussed here. Chapter 5 is devoted to verification. This chapter describes how the implementation has been tested and a

description of the test programs used is provided. The results are presented in chapter 6. The throughput and latency for all instructions are compared against the three state-of-the-art architectures presented in chapter 2. Synthesis results are also presented in chapter 6. Possible future work is described in chapter 7. Chapter 8 concludes the thesis.

The appendix contains confidential material and is therefore not included in this document. The appendix will be opened to the public after a 5 year disclosure period. The Department of Computer and Information Science at NTNU could be consulted to get access to the appendix when the disclosure period is over.

# Chapter 2

# **Background**

This chapter first presents the IEEE Standard for Binary Floating-Point Arithmetic. Then ISO C standard floating-point to integer casting is described. The chapter then continues with a description of how floating-point numbers are mapped to the real number line. Section 2.2 presents the current status of the new revision of the IEEE 754 standard. The chapter then ends with a description and comparison of three state-of-the-art floating-point units used in microcontrollers from ARM, MIPS and IBM. A reader familiar with floating-point and the IEEE 754 standard may skip section 2.1.

# 2.1 IEEE Standard for Binary Floating-Point Arithmetic (ANSI/IEEE 754-1985)

All the following subsections, except for the first and the last two, are based on information that can be found in [18].

Floating-point arithmetic can be implemented in several ways, but having many different implementations makes software difficult to port between different architectures. Today most general purpose floating-point units are implemented according to the specifications in the IEEE 754-1985 standard.

#### 2.1.1 IEEE 754 Floating-point Implementation-practice

Even though all floating-point implementations that are said to conform to the IEEE 754 standard must implement all the obligatory features, the number of *recommended* features implemented usually differs. Consequently IEEE conformance alone provides a very limited description of what a floating-point implementation is capable of. The standard also opens up to a great extent for different implementations. One example is the encoding of so-called quiet and signaling NaNs (described below), which is up to the implementer to decide. This freedom of choice with respect to implementation manifests itself several places in the standard. Indeed one of the desiderata that guided the formulation of the standard was to "Enable rather than preclude further refinements and extensions" [18, Foreword].

The standard use the words *shall* and *should* to distinguish between elements that are obligatory and elements that are only recommendations. Trying to extract only the obligatory requirements and making an implementation based on that, is not necessarily a good strategy, even if IEEE-754 conformance is the only requirement from a marketing perspective. Leaving out support for double-precision, for example, might not be a good idea since the C programming language has support for the **double** type and many applications may need the additional precision. It is therefore very important also to consider the current practice and the user of the floating-point implementation. Implementing features that are rarely used in practice will probably not increase the value of the floating-point unit from the user's perspective.

#### 2.1.2 Formats and Encoding

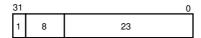

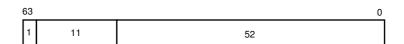

The standard specifies two *basic* formats and two *extended* formats. Single and double are the basic formats. The single and double formats are 32 and 64 bits wide respectively and both formats are encoded in the same way using a sign, exponent and fraction field. The sign bit is always in the MSB and is 0 for positive numbers and 1 for negative numbers. The exponent follows the sign bit and is 8 bits for single and 11 bits for double. The rest of the bits make up the fraction which is 23 bits for single and 52 bits for double. Figures 2.1 and 2.2 illustrates the single and double format respectively.

Figure 2.1: The IEEE 754 Single Format

Figure 2.2: The IEEE 754 Double Format

An implementation is only required to support the single format to conform to the standard.

The binary point is always located immediately to the left of the MSB of the fraction. The double and single formats need an implicit 1 or 0 bit to the left of the binary point. This implicit bit is encoded using the exponent and is often called the "hidden" bit. A nonzero exponent indicates that the hidden bit is 1. The resulting floating-point number is then said to be *normalized*. An exponent of 0 implies that the hidden bit is 0. In this case the floating-point number is said to be *denormalized* or represent zero. The hidden bit and the fraction constitutes the significand or mantissa. The term *mantissa* will be used throughout this thesis.

The extended formats are *implementation-dependent* versions of the two basic formats. In contrast to the single and double formats, the standard does not dictate the encoding for the extended formats, but states certain requirements for the significand and exponent. The requirements for a single extended number is that it must be capable of representing a positive or

negative floating-point number with a significand with a precision of at least 32 bits and a maximum exponent greater than or equal to 1023 and a minimum exponent less than or equal to -1022. For double extended the significand must be at least 64 bits wide, the maximum exponent must be greater or equal to 16383 and the minimum exponent must be less than or equal to -16382. The extended formats must also be able to represent  $+\infty$  and  $-\infty$ , +0, -0 and at least one signaling NaN and one quiet NaN. A NaN is returned from invalid operations like divide by zero and  $\infty + \infty$ . A signaling NaN raises an exception when used, a quiet does not.

Support for the extended formats are not required, but the standard recommends that implementations *should* support the extended version of the widest basic format supported. Consequently, if an implementation has support for the double format it should also have support for the double extended format, but need not have support for the single extended format. A single-only implementation similarly need no support for the extended double format.

For single and double the exponent is not stored using a 2's complement representation, as might seem natural. Instead a *biased* notation is used. The bias is a constant added to the actual exponent to make the exponent *always positive*. The smallest and largest biased exponent then becomes 0 and  $2^n-1$  respectively, where n is the number of bits used for the exponent. The smallest and largest biased exponents are reserved for encoding  $\pm 0$ ,  $\pm \infty$ , NaN and denormalized numbers. Thus, the minimum exponent is 1 and the maximum exponent is  $2^n-2$ . The maximum and minimum values for the unbiased exponents along with the biases are provided in table 2.1. No bias is specified for the extended formats since the details of how the exponent is represented is chosen by the implementer.

|                    | single | double |

|--------------------|--------|--------|

| Unbiased Max. Exp. | 127    | 1023   |

| Biased Max. Exp.   | 254    | 2046   |

| Unbiased Min. Exp. | -126   | -1022  |

| Biased Min. Exp.   | 1      | 1      |

| Bias               | 127    | 1023   |

Table 2.1: The Exponent Range and Bias

The unbiased exponent is found by subtracting the bias: *unbiased exponent = biased exp. - bias*. Table 2.2 shows how special values are encoded.

|              | Exponent | Fraction |

|--------------|----------|----------|

| ±0           | all 0's  | all 0's  |

| Denormalized | all 0's  | nonzero  |

| $\pm \infty$ | all 1's  | all 0's  |

| NaN          | all 1's  | nonzero  |

Table 2.2: IEEE 754 Special Values

The unbiased exponent is -126 and -1022 for all denormalized single and double numbers respectively. Thus, the smallest exponent (that is not reserved) is used.

Since a NaN requires a nonzero fraction there are several different NaNs. The standard requires

a conforming implementation to distinguish between two types of NaN: Quiet and signaling. At least *one* signaling NaN and at least *one* quiet NaN must be supported. The sign of a NaN is not interpreted. The standard recommends that quiet NaNs should "afford retrospective diagnostic information inherited from invalid or unavailable data and results" [18, 6.2]. How this is to be performed in practice, however, is unclear.

If one or both of the operands to an operation are of type signaling NaN, an invalid operation exception is raised and the result should be a quiet NaN. Using one or more quiet NaNs as operands, none of them signaling, does not raise an invalid operation exception. The result of the operation, if available, *should* be one of the input NaNs. Notice that a different NaN may be output as result instead.

It is common practice to use the MSB of the fraction to distinguish between quiet and signaling NaNs. A 1 in the MSB indicates a quiet NaN and 0 indicates a signaling NaN. The quiet NaN with only the MSB of the fraction set and the sign bit set to 0 is often called the *default NaN*. The Java Virtual Machine only use the default NaN and has no support for signaling NaNs. The default NaN is 0x7FC00000 and 0x7FF800000000000000 for single and double respectively.

#### 2.1.3 Rounding

A conforming implementation must support four rounding modes:

- Round to Nearest (default)

- Round toward  $+\infty$

- Round toward  $-\infty$

- Round toward 0

Round to Nearest is the default rounding mode. The three others are user-selectable *directed* rounding modes. The *Round to Nearest* mode rounds to the representable value nearest to the infinitely precise result. If the value before rounding lies exactly in the middle of the two possible rounded results, the *even* number is chosen. More details on the Round to Nearest rounding mode will be presented in chapter 4.

#### 2.1.4 Operations

The standard specifies the following operations, all of which must be supported in a conforming implementation:

- Add

- Subtract

- Multiply

- Divide

- Remainder

- Square root

- Round to integer in floating-point format

- Convert between different floating-point formats

- Convert between floating-point and integer formats

- Compare

The standard allows floating-point compare to be implemented in two ways. By using a condition code or by a true-false response to predicates. Four possible condition codes are possible: less than, equal, greater than and unordered. The unordered condition code is used when any of the operands are NaN. Notice that the sign of zero is ignored (+0 = -0). An implementation that uses predicates must provide at least the following predicates  $=, \neq, >, \geq, <, \leq$ .

It must be possible to round a floating-point number in a given format to an integer in the same format. Conversion between all supported floating-point formats must also be supported. A conforming implementation must also be able to convert between all supported floating-point formats and all supported integer formats. Rounding should be performed according to the selected rounding mode.

For details on the specific operations see [18].

#### 2.1.5 Exceptions

There are 5 types of exceptions, all of which must be supported in a conforming implementation:

- Invalid Operation

- Division by Zero

- Overflow

- Underflow

- Inexact

An implementation must provide a status flag for each exception. When an exception occurs, the default response is to set the corresponding flag. The standard also recommends that the user should be able to associate a trap handler with each exception. If traps are enabled, the response to an exception is to call the trap handler. The status flag for the exception may also be set.

It must be possible to test and alter each flag individually. When a flag is set, it can *only* be reset explicitly by the user. The standard also recommends that it should be possible to save and restore all the flags at one time.

Over- or underflow may occur simultaneously with inexact. All other exceptions can only occur individually.

Details on which conditions that can trigger the different exceptions can be found in [18].

#### 2.1.6 Traps

Traps are not required by the standard, but it is recommended that a conforming implementation has support for it. See [18] for details on traps.

#### 2.1.7 IEEE 754 and the ISO C Standard

The ISO C Standard [20] specifies that *truncation* shall be used when casting a floating-point number to an integer. This is equivalent to applying the *round toward zero* mode. For other operations the rounding mode is not defined but the default rounding mode of the IEEE 754 standard is often used in practice. This often makes it necessary to switch rounding mode before a cast and switch back again afterwards. This switching between modes can be costly on most architectures and may result in performance loss, especially in applications like 3D graphics and sound processing. 3D graphics applications must convert to integer screen coordinates and sound processing must convert to and from integer sound samples. Richard Gerber discusses ways to cope with this problem on the IA-32 architecture in [9, chap. 11].

#### 2.1.8 Mapping Floating-point Numbers to the Real Number Line

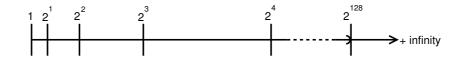

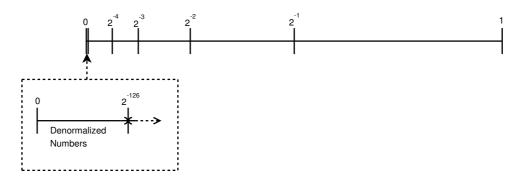

The set of floating-point numbers is finite. This finite set of floating-point numbers are not spread out evenly across the real number line. The gap or spacing between large floating-point numbers close to infinity is much greater than the gap between small floating-point numbers. In fact, the magnitude of the gap between floating-point numbers doubles each time the exponent is increased by 1. This happens because the range doubles in size while the number of discrete floating-point numbers to spread out within that range is kept constant ( $2^{23}$  for single and  $2^{52}$  for double). Notice that all floating-point numbers mapped to a given exponent range  $[2^{n-1}, 2^n)$ , are evenly spread out across this range.

Figure 2.3 shows how the ranges of single-precision floating-point numbers with increasing positive exponents grows exponentially in size. For every range,  $2^{23}$  discrete floating-point numbers are mapped to the number line.

Figure 2.4 shows ranges for positive floating-point numbers with negative exponents (numbers between 0 and 1). Denormalized floating-point numbers are mapped to the range  $(0, 2^{-126}]$ .

Table 2.3 shows range- and gap-size for some exponent ranges of single precision floating-point numbers. The gap size is calculated by dividing the range size by  $2^{23}$ . Notice how the gap size

Figure 2.3: Single-precision Floating-point Exponent Ranges from  $[1,2^1)$  to  $+\infty$

Figure 2.4: Single-precision Floating-point Negative Exponent Ranges

doubles as the exponent is increased by 1. Floating-point numbers in the range  $[2^{23}, 2^{24})$  have a gap size of 1.0.

| Range                  | Range Size                    | Gap Size                      |

|------------------------|-------------------------------|-------------------------------|

| $(2^{-126}, 2^{-125}]$ | $\approx 1.18 \cdot 10^{-38}$ | $\approx 1.40 \cdot 10^{-45}$ |

| $[2^{-2}, 2^{-1})$     | 0.25                          | $\approx 2.98 \cdot 10^{-8}$  |

| $[2^{-1}, 2^0)$        | 0.5                           | $\approx 5.96 \cdot 10^{-8}$  |

| $[2^0, 2^1)$           | 1                             | $\approx 1.19 \cdot 10^{-7}$  |

| $[2^1, 2^2)$           | 2                             | $\approx 2.38 \cdot 10^{-7}$  |

| $[2^{23}, 2^{24})$     | 8388608                       | 1.0                           |

| $[2^{127}, 2^{128})$   | $\approx 1.70 \cdot 10^{38}$  | $\approx 2.03 \cdot 10^{31}$  |

Table 2.3: Range Size and Gap Size (Single-precision)

For clarity, only positive single-precision floating-point numbers were considered here. The same type of mapping applies to negative floating-point numbers and double precision numbers as well.

#### 2.2 The IEEE 754 Revision

The information in this section is based on information found in [16], [17], [31] and [39].

The IEEE 754 standard is currently under revision. The revision work started in 2000 and is to be completed in December 2005. Each month several academic- and industry-experts in the field of floating-point arithmetic meet in the San Francisco Bay area to work on the

standardization. The meetings are open to the public and participation is free of charge. In addition to these meetings a mailing list, stds-754@ieee.org, has been created which provides crucial feedback to the revision group [17]. The current draft of the proposed standard can be found at [16].

#### 2.2.1 Purpose

The main purpose of this revision is to make the IEEE 754 standard more precise. The current standard allows too many implementation choices and makes programs less portable since the result of a computation on two implementations may differ. The standard also clarifies terminology (e.g. subnormal is used instead of denormal).

Systems that implement arithmetic according to the IEEE 754 standard can be divided into two groups, *Extended-based systems* and *Single/Double systems* [31]. Extended-based systems support an extended double-precision format that is used for all calculations. Single- and double-precision is supported through load and store operations which rounds to/from the extended double-precision format. Extended-based systems can also be configured to round results to single- or double-precision even though the result is stored in double-extended format, but this mode is not the default. Intel x86 compatible processors are extended-based systems. Single/Double systems have no support for an extended double-precision format but outputs results directly in single- or double-precision format. The ARM VFP9-S floating-point unit described later in this chapter is one example of a Single/Double system.

The problem is that the results of a computation may differ on extended-based systems and Single/Double systems. The following excerpt, taken from [31], demonstrates this.

```

int main() {

double q;

q = 3.0/7.0;

if (q == 3.0/7.0) printf("Equal\n");

else printf("Not Equal\n");

return 0;

}

```

On Single/Double systems this code will work properly and print out *Equal*, since both the stored double value q and the intermediate compare value, 3.0/7.0, are calculated using double-precision.

On Extended-based systems this code may not always work properly. The q value is stored using double-precision, but the intermediate value 3.0/7.0 in the compare will be calculated in double-extended format. Therefore, the comparison will be *not equal*.

The important thing to notice is that the extended-based systems do *conform* to the IEEE 754 standard. The standard requires that the result is rounded correctly to the precision of the destination, but does not require the precision of the destination to be determined by the user-program. Thus, intermediate results may differ on extended-based and single/double systems.

More examples of code that will execute differently on extended-based and single/double systems are provided in [31] along with a more thorough elaboration on these issues.

#### 2.2.2 Current Changes and Additions

According to the IEEE 754 revision groups webpage [17], these points have been agreed upon:

- Merging IEEE-854 into IEEE-754

- Reducing implementation choices

- Resolving ambiguities in 754

- Standardizing fused multiply-add

- Including quadruple precision

The IEEE-854 is the IEEE Standard for Radix-Independent Floating-Point Arithmetic (IEEE 854-1987). This standard only generalizes the IEEE-754 Standard for *Binary* Floating-Point Arithmetic to other radices, and provides no important additions to the standard.

#### 2.2.3 Quadruple-precision Floating-point

The quadruple-precision or "quad" format is a third basic binary floating-point format and is represented using 128 bits. The encoding follows the same pattern as single and double, but with wider fields for the exponent and fraction bits. Figure 2.5 shows how the 128 bits are arranged into sign bit, exponent bits and fraction bits.

| 1 | 15 | 112 |

|---|----|-----|

|---|----|-----|

Figure 2.5: The Quadruple Floating-point Format

Table 2.4 summarizes the exponent:

|                  | Encoding (hex) | Value  |

|------------------|----------------|--------|

| Minimum Exponent | 0x0001         | -16382 |

| Maximum Exponent | 0x7FFE         | 16383  |

| Exponent bias    | 0x3FFF         | 16383  |

Table 2.4: Quadruple Exponent Format

#### 2.2.4 Fused Multiply-Add

The Fused Multiply-Add (FMA) operation performs  $x \times y + z$  in one atomic operation without an intermediate rounding of the product. This operation is currently supported in several

floating-point architectures, so it is time for a proper standardization of this operation. The Itanium architecture [19] from Intel and PowerPC architecture [15] from IBM both have support for Fused Multiply-Add instructions. The revision also proposes other versions of the FMA operation that negates the product and subtracts the z operand.

#### 2.2.5 Other Proposed Additions

The revision proposes several other additions to the standard:

- A standard for decimal arithmetic (need in financial applications due to problems of representing decimal fractions exactly in radix 2) is proposed.

- The *round-to-nearest, ties away from zero* rounding mode for decimal arithmetic is proposed.

- Min and Max functions.

- Several classification predicates (e.g. isNaN(x)).

### 2.3 Embedded FPU Implementations

To fully understand the requirements for a competitive floating-point coprocessor, it is important to study other floating-point units on the market. These floating-point units sets the standard for what is to be expected from a new floating-point coprocessor from Atmel. The following sections list important properties of three industry-leading floating-point unit (FPU) architectures from ARM, MIPS and IBM. All implementations are implemented according to the IEEE 754 standard and supports all rounding modes. In the end of each section, latency and throughput numbers for supported instructions are presented. These numbers will also be very helpful for evaluating the coprocessor implementation. A graphical comparison will be presented in chapter 6.

#### 2.3.1 Throughput and Latency

Throughput is defined as the number of cycles after the instruction has been issued when another instruction of the same type can start. *Latency* is the number of cycles after which the result is available for another operation. These definitions for throughput and latency are used throughout the thesis.

#### 2.3.2 **ARM VFP9-S**

The following description is based on information found in [3] and [2].

The ARM VFP9-S is a synthesizable *Vector* Floating-point Coprocessor that can optionally be used by the ARM9E family of processor cores. These cores support clock frequencies of up to

200 MHz in 0.18  $\mu$ m process technology. There also exists vector floating-point coprocessors for the ARM10 and ARM11 cores, but these are designed for much higher clock frequencies and therefore does not compare very well to the 32-bit target microcontroller the coporcessor is to be designed for.

- The VFP9-S implements the ARM VFPv2 Instruction Set Architecture. The register file has 32 registers that can be used to store 32 single-precision numbers or 16 double-precision numbers. The single precision registers are named S0-S31 and the double precision registers are named D0-D15.

- Support code is needed for complete IEEE compliance (denormalized numbers and correct handling of NaNs are not supported in hardware).

- A Run-Fast mode is supported. In this mode denormalized numbers are flushed to zero, only the default NaN is used and the hardware never traps to software routines. The motivation for having a near-IEEE compliant Run-Fast mode is that it simplifies the hardware and that some users do not need complete IEEE compliance.

- The VFP9-S coprocessor can also perform operations on vectors. A vector operation is started in only a single instruction and operates on so-called *short vectors*. Single-precision short vectors can hold up to 8 single-precision values. Double-precision short vectors can hold up to 4 double-precision values. The short vectors are composed of registers in the register file.

- There are 3 separate pipelines in the VFP9-S, which operate in parallel.

- The Floating-point multiply-accumulate (FMAC) pipeline

- The Divide and square root (DS) pipeline

- The Load and Store (LS) pipeline

The FMAC pipeline performs a multiplication, rounds the result and then adds a third operand to the product. The FMAC pipeline has 5 stages (1 Decode stage followed be 4 Execute stages):

- The Decode stage decodes the operation and detects if any of the inputs are NaN, Infinity or Zero.

- The first Execute stage performs the multiplication and possibly negates the value that is to be added to the product. The multiplier generates two partial products.

- In Execute stage 2, the two partial products are added to form the product. Then the product is rounded. The operand to add is aligned to the product in parallel.

- The third Execute stage adds the aligned addend to the product and normalizes the result.

- The last stage rounds the final result and performs write-back.

All the arithmetic instructions except for division and square root are executed in the FMAC pipeline. Conversions between floating-point formats and between integer and floating-point formats are also executed in the FMAC pipeline.

The Divide and Square Root pipeline has also 5 stages (decode followed by 4 execute stages) but iterates several times between the first to execute stages. The third execute stage normalizes the results and performs rounding. The last execute stage selects between two results and writes the the selected result back to the register file.

The Load and Store pipeline performs loads and stores and has 5 stages: Fetch, Decode, Execute, Memory and Writeback.

Schematics for all the pipelines can be found in [3].

The area for the VFP9-S is estimated to 100 - 130K gates and have a worst case clock frequency of 180 - 210 MHz in 0.13um. The power consumption will typically be less than 0.4 mW/MHz for 0.13um [2].

The instruction latencies and throughputs for the VFP9-S are provided in table 2.5.

| Instructions                             | Throughput | Latency  | Throughput | Latency  |

|------------------------------------------|------------|----------|------------|----------|

|                                          | (single)   | (single) | (double)   | (double) |

| add/sub, abs, neg, move                  | 1          | 4        | 1          | 4        |

| $single \leftrightarrow double$          |            |          |            |          |

| compare                                  | 1          | 4        | 1          | 4        |

| $integer \leftrightarrow floating-point$ | 1          | 4        | 1          | 4        |

| multiply                                 | 1          | 4        | 2          | 5        |

| multiply accumulate                      | 1          | 4        | 2          | 5        |

| division, square root                    | 14         | 17       | 28         | 31       |

| load                                     | 1          | 4        | 2          | 5        |

| store                                    | 1          | 3        | 2          | 4        |

Table 2.5: ARM VFP9-S Throughput and Latency Cycle Counts

#### 2.3.3 MIPS32 24Kf FPU

This presentation is based on information that can be found in [27], [26] and [28].

The MIPS32 24Kf is a high-performance synthesizable MIPS core from MIPS Technologies that also implements a floating-point unit. The CPU has a 8-stage pipeline and the maximum clock frequency for the core is 625 MHz.

The properties for the FPU are listed below.

• The FPU implements the floating-point instructions in the MIPS64 Instruction Set Architecture (ISA). In this architecture there are 32 64-bit floating-point registers. Each floating-point register can store a single- or a double-precision number.

- In addition to the 32-bit single and 64-bit double floating-point formats, the FPU also supports a 64-bit *paired single* format. The FPU can also perform operations on fixed point numbers. There are two fixed-point types, a 32-bit and a 64-bit format.

- The FPU is optimized for execution of single-precision operations and most instructions have single cycle throughput and 4-cycle latency. Double precision operations have 2cycle throughput.

- Multiply-Add instructions are supported. The product is rounded before the addition takes place. Thus, the operation is equivalent to a multiplication followed by an addition.

- The FPU cannot run on the maximum clock frequency of the CPU. Therefore the FPU can be configured to run at half the clock frequency of the CPU. This configuration is set at build time (when the chip is sent to production) and cannot be changed later. A reduced clock frequency for the FPU can also save power for battery-powered applications.

- The FPU is a separate coprocessor and has its own pipeline that executes in parallel with the CPU and is connected to the CPU via a 64-bit coprocessor interface.

- The Pipeline has 7 stages:

- Decode, register read and unpack (FR stage)

- Multiply tree (M1)

- Multiply complete (M2)

- Addition first step (A1)

- Addition second step (A2)

- Packing to IEEE format (FP)

- Register writeback (FW)

The M1 stage is executed twice for double precision multiply. Forwarding is implemented from the A2, FP and FW stages.

• The MIPS FPU is sometimes also referred to as "Coprocessor 1".

The latency and throughput for supported instructions are given in table 2.6.

#### 2.3.4 IBM PowerPC 603e FPU

The information in this section is based on [12], [14], [13] and [22].

The PowerPC is a well-known high-performance RISC architecture with implementations that span a wide range of market segments, from small microprocessors at 100 MHz to desktop- and server-processors operating in the GHz range. PowerPC processors are also embedded into the Virtex 4 Field Programmable Gate Array (FPGA) from Xilinx [40]. The PowerPC 603e processor is a dual-issue processor designed for low-power consumption and optimized for embedded applications. The processor operates at 100-200 MHz, depending on the process technology.

| Instructions                    | Throughput | Latency  | Throughput | Latency  |

|---------------------------------|------------|----------|------------|----------|

|                                 | (single)   | (single) | (double)   | (double) |

| add/sub, abs, neg, move         | 1          | 4        | 1          | 4        |

| $single \leftrightarrow double$ |            |          |            |          |

| compare                         | 1          | 4        | 1          | 4        |

| integer ↔ floating-point        | 1          | 4        | 1          | 4        |

| multiply                        | 1          | 4        | 2          | 5        |

| multiply accumulate             | 1          | 4        | 2          | 5        |

| reciprocal                      | 10         | 13       | 21         | 26       |

| reciprocal sqrt.                | 14         | 17       | 31         | 36       |

| division, square root           | 14         | 17       | 29         | 32       |

| load                            | 1          | 4        | 1          | 4        |

| store                           | 1          | 1        | 1          | 1        |

Table 2.6: MIPS32 24Kf FPU Throughput and Latency Cycle Counts

- The architecture has 32 Floating-Point Registers (FPRs). Double precision is used as the internal format for all the registers. When a single-precision floating-point number is loaded from memory it is automatically converted to the internal double-precision format. Three types of store instructions are provided: store double, store single and store integer. The value is also here automatically converted from the internal double-precision format to the requested output format.

- The FPU is optimized for single-precision multiply-add (single-precision multiply has single-cycle throughput, while double-precision has 2-cycle throughput).

- Fused Multiply-Add instructions are supported. The product is calculated to full 106-bits precision and then the addition is performed. The result is then rounded.

- The PowerPC 603e FPU has a 3 stage multiply-add pipeline. The three stages are:

- Multiply stage

- Carry Propagate Add (CPA) stage

- Write Back (WB) stage

There is also a Bypass Unit that checks for abnormal operands and operations. This unit may send a default result to the Write Back stage.

A dual-pass multiplier is used. Double-precision operations therefore need two passes through the multiplier. This is why the throughput for single- and double-precision multiply operations differs. The PowerPC 604e has a single-pass multiplier. A comparison between the *604e* and *603e* and a discussion of the design complexities around dual-pass multiplier architectures can be found in [22].

Division is performed in a separate unit.

• Division is supported for both single- and double-precision. There is also support for a single-precision *reciprocal estimate* instruction.

- The PowerPC 603e FPU does not implement a square root instruction, but a fast *square root estimate* instruction is implemented. A software implementation of square root that uses an algorithm based on iterative approximation can use this estimate as an initial seed.

- Denormalized numbers and correct handling of NaNs are supported in hardware, thus eliminating the need for software exception routines.

Latency and throughput numbers for the PowerPC 603e are listed in table 2.7.

| Instructions                    | Throughput | Latency  | Throughput | Latency  |

|---------------------------------|------------|----------|------------|----------|

|                                 | (single)   | (single) | (double)   | (double) |

| abs, neg, move                  | 1          | 3        | 1          | 3        |

| add/sub                         | 1          | 3        | 1          | 3        |

| $single \leftrightarrow double$ |            |          |            |          |

| compare, fsel                   | 1          | 3        | 1          | 3        |

| integer ↔ floating-point        | 1          | 3        | 1          | 3        |

| multiply                        | 1          | 3        | 2          | 4        |

| multiply accumulate (fused)     | 1          | 3        | 2          | 4        |

| division                        | *          | 18       | *          | 33       |

| reciprocal estimate             | *          | 18       | **         | **       |

| reciprocal sqrt. estimate       | **         | **       | 1          | 3        |

| load                            | 1          | 2        | 1          | 2        |

| store                           | 1          | 2        | 1          | 2        |

Table 2.7: PowerPC 603e FPU Throughput and Latency Cycle Counts

A \* in table 2.7 means that the operation is not pipelined and exact throughput numbers are not available. A \*\* in table 2.7 means that the instruction is not available.

# Chapter 3

# **Architecture**

This chapter describes the architecture of the floating-point coprocessor. First a list of the requirements for the design is presented. The chapter then continues with a description of the instruction set and a discussion of IEEE 754 compliance issues. Then, the main building blocks of the datapath are described. The discussion focuses on design-issues and on describing what each module does. How different instructions are executed in the architecture is then described. The chapter ends with a description of how division and square root is performed.

### 3.1 Background for the Architecture Design

The coprocessor architecture is based on previous results presented in [30]. During that project an analysis of floating-point usage in the EEMBC Benchmarks [6] was performed. The outcome of this analysis, among other considerations, motivated the design of an arithmetic core based on a Fused Multiply-Add (FMA) structure. The focus in this thesis is to define an efficient floating-point coprocessor architecture and implementing a working, synthesizable design that meets the timing requirements. Thus, a thorough analysis of floating-point instruction frequencies in typical programs is not performed. The ARM VFP9-S, MIPS32 24Kf FPU and the PowerPC 603e FPU provides insight into what is to be expected of a competitive floating-point coprocessor and are used for evaluating the proposed architecture.

## 3.2 Requirements for the Architecture

Based on the task description and feedback from Atmel, the following list of requirements for the architecture was made:

In applications with specific floating-point needs, dedicated solutions can often be used.

In 3D graphics applications, for example, dedicated chips can be used very effectively.

The Mali(tm) Graphics Solution from Falanx [8] is a good example. The coprocessor should therefore be designed for general purposes to cover a wide range of application

areas. This means that it does not have to be optimized for specific embedded applications. The results from the floating-point usage analysis performed in the project work in [30] should be used as guidelines for the design of the architecture. A general purpose floating-point coprocessor will also be easier to program than a vector floating-point coprocessor, for example.

- High performance is important for a competitive design and the coprocessor should have performance compared to floating-point implementations from ARM, MIPS and PowerPC. This means that the latency and throughput for most instructions should be equivalent or better than for these competitors. High performance is most important for the basic arithmetic operations add, subtract and multiply. Multiply-accumulate instructions should also be executed efficiently.

- The implementation does not have to include division and square root operations, but the architecture should define how these operations can be performed. A longer latency for division may be acceptable, since division operations were not found to be be very frequent operations in [30]. Square root should also be considered as a relatively infrequent operation.

- Low power consumption is important for many battery-powered embedded applications. The architecture, however, should primarily be designed to achieve high performance. The *implementation* of the architecture, on the other hand, should try to reduce the power consumption.

- The area should not exceed the area of the VFP9-S Vector Floating-Point Coprocessor from ARM.

- The coprocessor architecture should be designed for clock frequencies in the range 150-200 MHz.

- The coprocessor interface must conform to the specification for the Tightly Coupled Bus (TCB), as specified by Atmel. The TCB bus is described in appendix C.

- The result from floating-point compare operations should be easy to process for the CPU.

This will reduce the latency for branches based on the outcome of floating-point compares.

- The design should follow the IEEE 754 Standard to a great extent. Deviation from the standard is possible, if the feature is rarely used in practice or inclusion of the feature has significant implications for performance or area when implemented.

- Practical use of floating-point in the C and Java programming languages must be kept in mind during design. It should be easy to compile C and Java code into an efficient stream of floating-point assembly instructions.

- The existing Fused Multiply-Add unit from [30] should be used as the arithmetic core for the coprocessor to simplify development. The functionality of the Fused Multiply-Add unit is currently very limited and should be further extended.

- Both single- and double-precision formats should be supported, but the architecture should be optimized for double. The motivation for optimizing for double is that the study of the EEMBC benchmarks in [30] showed that the benchmark programs uses only double-precision.

- Instructions for variants of Fused Multiply-Add operations should be implemented. The

variants negate the product or the addend, and makes it possible to reduce the number

of floating-point negate instructions.

# 3.3 Properties of the Architecture

The following is a list the most important properties of the architecture.

- Double-precision Fused multiply-add unit implements all arithmetic operations and also executes single-precision operations.

- Single-cycle throughput for both double and single precision. The architecture is designed for efficient execution of double-precision operations. Single-precision operations have the same latency as double-precision operations.

- Low latency compare. This will speed up automotive applications since these applications use compares frequently [5].

- Low latency load/store. This will make it possible to reduce the size of the register file since data can be swapped in and out more quickly.

- High precision fused multiply-add operations for future IEEE 754 revision compliance.

- Divide and square root operations are executed in software. The 4-cycle latency fused multiply-add operations allow for fast software implementations of divide and square root.

- The architecture allows hardware to be shared for compare and integer to floating-point conversion.

- Denormalized numbers are supported in hardware to avoid the need for software trap routines for IEEE compliance.

# 3.4 Target Processor

The target system for the floating-point coprocessor is a microcontroller implementation of a new 32-bit architecture from Atmel. The clock frequency of this target is in the range 150-200 MHz. Since the microcontroller is not released yet and not open to to the public, the properties of this microcontroller are not discussed here. Further details can be found in appendix E.

# 3.5 Instruction Set

The instruction set was selected based on several criteria.

- The instruction set should be as complete as possible with respect to the IEEE 754 standard. There should be instructions for performing most of the operations specified in the standard.

- ISO C style conversion (truncation) from floating-point to integer should be supported.

- Both single- and double-precision should be supported. The ARM VFP9-S, MIPS32 24Kf FPU and the PowerPC 603e FPU all support both formats. Consequently, both formats should be supported to be competitive. The floating-point coprocessor should support many applications, also those which require double precision. If the floating-point coprocessor was to be designed for specific applications, support for single precision might be sufficient.

- Multiply-accumulate (MAC) instructions should be included. These instructions should be easy to implement using the Fused Multiply Add (FMA) pipeline. They also potentially reduce the number of instructions in programs.

- Fused Multiply-add instructions should also be included. The fused multiply-add instruction differs from MAC in that the destination register need not be the same as the addend. Fused Multiply-Add instructions can also be used to implement division and square root efficiently in software.

- Instructions for supporting multiplicative division and square root should be included.

These support instructions should be provided to speed up the division and square root algorithms.

The floating-point instructions can be separated into 5 groups:

- Arithmetic

- Compare

- Convert

- Approximation

- Move and Load-Constant

# 3.5.1 Arithmetic

The instruction set defines both regular two-operand and *fused* three-operand arithmetic operations. The fused operations perform two operations using only one rounding. Table 3.1 lists the two-operand instructions and table 3.2 lists the three-operand instructions.

There are several motivations for including the three-operand instructions.

| Mnemonic | Name             |

|----------|------------------|

| fadd     | Add              |

| fsub     | Subtract         |

| fmul     | Multiply         |

| fnmul    | Negated Multiply |

Table 3.1: Two-operand Arithmetic Instructions

| Mnemonic | Name                                  |

|----------|---------------------------------------|

| fmac     | Fused Multiply and Accumulate         |

| fnmac    | Fused Negated Multiply and Accumulate |

| fmsc     | Fused Multiply and Subtract           |

| fnmsc    | Fused Negated Multiply and Subtract   |

| ffma     | Fused Multiply and Add                |

| ffnma    | Fused Negated Multiply and Add        |

Table 3.2: Three-operand Fused Arithmetic Instructions

- The dot product  $d = a_1 \cdot b_1 + ... + a_n \cdot b_n$ , is implemented effectively using multiply-accumulate. The computation is sequential as follows:  $s_1 = a_1 \cdot b_1$ ,  $s_k = s_{k-1} + a_k \cdot b_k$  for k > 1.

- Matrix multiplication, which is a sequence of dot products, is also accelerated.

- Another time-consuming computational problem where the multiply-accumulate instruction is useful, is in computing the value of a polynomial  $y = a_0 + a_1 \cdot x + ... + a_n \cdot x^n$ . By using the Horner's rule this can be rewritten to  $a_0 + x \cdot (a_1 + ... + x \cdot (a_{n-1} + a_n \cdot x)...)$ . The computation then becomes  $s_{n-1} = a_{n-1} + a_n \cdot x$ ,  $s_i = a_i + x \cdot s_{i+1}$  for i < n-1.  $s_0$  is the final result.

- Inspection of the EEMBC Benchmarks for Embedded Microprocessors in [30] revealed that multiply-accumulate instructions can improve the performance of typical embedded applications.

- The Fused Multiply-Add operation will be part of the new IEEE 754 revision.

- The Fused Multiply-Add operation can be efficiently implemented in hardware.

- The regular two-operand instructions are implemented using the Multiply-Add hardware unit.

- By replacing two instructions by one the code size can be reduced. This could be important for cost sensitive applications.

#### 3.5.2 Compare

There is only one instruction for comparing floating-point numbers. The two operands are compared and a condition code is placed in the destination register. The condition code can be

any of the four condition codes specified by the IEEE 754 standard: *greater than, less than, equal or unordered*. By putting the result into a floating-point register, a simple Move From Coprocessor Register to CPU Register instruction can be used to read the result. It is possible to perform floating-point compare using the integer instructions of the CPU. In [5] a software implementation of compare is estimated to take more than 20 cycles and a new non-IEEE floating-point format is proposed to make software compare more efficient. A hardware compare instruction is therefore the only choice for high-performance IEEE-compliant compare.

### 3.5.3 Convert

Conversion instructions exist for converting between single and double and converting between integer and the two floating-point formats. Both 32-bit integer and 64-bit integer formats are supported and the integers may be signed or unsigned. The wast number of formats are needed to support all the integer formats supported by the CPU. Both a Round-to-Nearest and a Round-to-Zero version of the convert from floating-point number to integer instruction must exist. The Round-to-Zero version is included since the ISO C standard specifies that the Round-to-Zero rounding mode shall be used when casting floating-point numbers to integers.

# 3.5.4 Approximation Instructions

Two approximation instructions are supported in the instruction set:

- Reciprocal Approximation

- Reciprocal Square Root Approximation

The Reciprocal Approximation instruction returns an approximation to  $\frac{1}{x}$  correct to 4 bits of precision. The Reciprocal Square Root Approximation instruction returns an approximation to  $\frac{1}{\sqrt{x}}$  correct to 4 bits of precision. This approximation is used as a seed for software implementations of multiplicative division and square root algorithms. Having support for these approximation instructions in hardware is essential for being able to implement efficient software routines for division and square root.

## 3.5.5 Move and Load-Constant

A few move instructions are supported in the instruction set. Table 3.3 lists the move-type instructions.

Negate and Absolute Value are also considered move-type instructions since they only alter the sign of the operand.

Three instructions for loading constants are also provided in the instruction set. These instructions are listed in table 3.4.

These instructions are included for supporting the software implementations of division and square root.

| Mnemonic | Name           |

|----------|----------------|

| fmov     | Move           |

| fneg     | Negate         |

| fabs     | Absolute Value |

Table 3.3: Move-Type Instructions

| Mnemonic | Name     |

|----------|----------|

| fldh     | Load 0.5 |

| fldtwo   | Load 2.0 |

| fldthree | Load 3.0 |

Table 3.4: Load Constant Instructions

# 3.5.6 Supported Formats

Both single and double variants exist for all the instructions. Instructions that convert between single and double need no explicit format specifier.

# 3.5.7 Implemented Instruction Set

A detailed description of the *implemented* instruction set can be found in appendix B.

## 3.5.8 Encoding

All floating-point instructions are encoded with the generic coprocessor operation instruction, cop, which is part of the CPU instruction set. The syntax is as follows:

```

cop CPn, CRd, CRx, CRy, op

```

$n \in \{0, 1, ..., 7\}$ , denotes the coprocessor number.

$d, x, y \in \{0, 1, ..., 15\}$ , denote the destination, first operand and second operand respectively.

$op \in \{0, 1, 2, ... 127\}$ , is used to encode the coprocessor operation.

### 3.5.9 Load/Store

Generic *load/store coprocessor* and *load/store coprocessor multiple* instructions are used for loading data into the coprocessor register file and storing register file content back to memory. Instructions for moving data between the register file in a coprocessor and the register file in the CPU also exist. These instructions are part of the CPU instruction set. A description of the generic load/store coprocessor instructions can be found in Appendix D.

# 3.6 IEEE 754 Compliance

The Floating-point coprocessor architecture is designed to follow the IEEE 754 standard to a great extent, but is not completely IEEE compliant due to the following:

- Division and square root operations are not always correctly rounded.

- Only the the default rounding-mode is supported.

- Signaling NaNs are not supported.

- Status flags are not included in the architecture.

- Rounding to integer in floating-point format is not supported.

- Remainder is not part of the architecture.

If correctly rounded division and square root should be supported, a combined SRT divide / square root unit should be included in the architecture. The SRT method is named after Sweeney, Robertson and Tocher. They independently proposed the algorithm [34], [29]. The SRT unit would be able to calculate an exact reminder, which could be used to obtain a correctly rounded result. A detailed discussion of SRT division is out of the scope of this thesis. An indepth description of digit-recurrence methods for division and square root can be found in [7, ch. 5,6].

There are many reasons for choosing approximate multiplicative division and square root algorithms instead of an SRT division unit.

- Higher radix SRT dividers are quite complex. Designing an efficient radix-4 or radix-8 SRT divider could easily become a masters thesis in its own right.

- Radix-2 SRT dividers are too slow.

- The throughput of SRT dividers is very low. This conflicts with the goal of building a high-performance floating-point coprocessor.

- Using a software-based multiplicative method makes it possible to pipeline division and square root operations. Up to 5 single precision divide operations or 2 double precision divide operations can be pipelined. This can improve throughput significantly compared to division/square root based on SRT.

- In many applications, especially low-cost consumer applications, a correctly rounded result is not always critical. In 3D graphics applications, for example, it should be possible to trade the reduced precision for higher throughput. Audio and video decoding will also benefit from increased throughput and the user will probably not be able to see or hear any difference in the output.