# FPGA Framework for CMP

Kenneth Østby

Master of Science in Computer Science Submission date: June 2007 Supervisor: Morten Hartmann, IDI Co-supervisor: Marius Grannæs, IDI

Norwegian University of Science and Technology Department of Computer and Information Science

#### **Problem Description**

The project's main goal is to develop a platform supporting experiments of Chip Multiprocessors on a Field Programmable Gate Array. The NCAR Group performs research on the simulation of architectural variations in Chip Multiprocessors. It's desirable to extend the experiments to run on parametrizable architectures designed for Field Programmable Gate Arrays. The solution must account for several processors and their interconnection, cache structures, and if time permits operating systems and the ability to communicate with existing simulators. Knowledge about FPGA, VHDL and the C programming language is required.

The subtasks are (to the extent time allows them to be addressed):

Background research on related projects

- Multicore solutions in FPGAs, with emphasis on cache solutions

- potential operating systems

Research on cache solutions on an FPGA

- assess the option of customizable solutions and automated synthesis of cache systems

Make several cores work on existing lab equipment in a simple testing environment

Research and identify suitable cores for the system and possibly an operating system

Cache design with emphasis on customizability and suitable cache hierarchy (L1/L2) on available FPGA cards (Nalle)

Investigate possibilities towards integration with simulation environments (M5 and/or SimpleScalar) and experiments at NCAR

Run suitable experiments and analyse results

Assignment given: 20. January 2007 Supervisor: Morten Hartmann, IDI

#### Abstract

The single core processor stagnated due to four major factors. (1) The lack of instruction level parallelism to exploit, (2) increased power consumption, (3) complexity involved in designing a modern processor, and (4) the performance gap between memory and the processor. As the gate size has decreased, a natural solution has been to introduce several cores on the same die, creating a chip multicore processor.

However, the introduction of chip multicore processors has brought a new set of new challenges such as power consumptions and cache strategies. Although throughly researched in context of super computers, the chip multiprocessor has decreased in physical size, and thus some of the old paradigms should be reevaluated, and new paradigms found.

To be able to research, simulate and experiment on new multicore architectures, simulators and methods of prototyping are needed by the community, and has traditionally been done by software simulators. To help decrease the time between results, and increase the productivity a hardware based method of prototyping is needed.

This thesis contributes by presenting a novel multicore architecture with interchangeable and easily customizable units allowing the developers to extend the architecture, rewriting only the subsystem in question. The architecture is implemented in VHDL and has been tested on a Virtex FPGA, utilizing the MicroBlaze microcontroller. Based upon FPGA technologies, the platform is close in nature to that of a chip multiprocessor. The thesis also shows that a hardware based environment will significantly decrease the time to results.

## Preface

This Master's Thesis was written as a part of the degree as "Sivilingeniør" in Computer Engineering. The Master's Thesis is founded in an earlier project in the subject TDT4720 – Computer Design and Architecture. The goal of TDT4720 was to give the student an introduction to the current state of Computer Architecture, while introducing him to the tools used in hardware construction.

The work is done for the Norwegian University of Science and Technology (NTNU) at the Faculty of Information Technology, Mathematics and Electrical Engineering, and the Department of Computer and Information Science. The group which hosted the project was the NTNU Computer Architecture and Design Group under the supervision of Associate Professor Morten Hartmann.

The advisor for this thesis was Associate Professor Morten Hartmann. Co-advisor was Research Fellow Marius Grannæs.

Kenneth Østby June 17, 2007

## Acknowledgments

I would like to thank the following persons for their support and input throughout this project. Associate Professor Morten Hartmann for being my advisor, and thus allowing me to partake in this journey through Chip Multiprocessors. Marius Grannæs for being my co-advisor, reading through my thesis several times and always available for technical discussions.

I would also like to thank the people at NTNU Computer Architecture Research Group for including me in their much interesting meetings. Also important are the people at my study room, ITV-458, May Linda Martinsen, Knut Imar Hagen, Christian Larsen, Idar Borlaug, Rolf Anders Syvertsen and Jan Peder David-Andersen.

Finally I would like to send my thanks and thoughts to all of my friends and loved ones not mentioned by name.

## Contents

| List of Tables |            | Tables     xii      | i |  |  |

|----------------|------------|---------------------|---|--|--|

| $\mathbf{Li}$  | st of      | Figures xv          | V |  |  |

| 1              | Intr       | roduction 1         |   |  |  |

|                | 1.1        | Introduction        | 1 |  |  |

|                | 1.2        | Problem Description | 4 |  |  |

|                | 1.3        | Project Motivation  | 5 |  |  |

|                | 1.4        | Contribution        | 5 |  |  |

|                | 1.5        | Scope               | 6 |  |  |

|                | 1.6        | Outline             | 6 |  |  |

|                |            | 1.6.1 Appendices    | 6 |  |  |

| 2              | Background |                     |   |  |  |

|                | 2.1        | Related Work        | 7 |  |  |

|                | 2.2        | CMP Architecture    | 8 |  |  |

|                |            | 2.2.1 Cores         | 9 |  |  |

|                |            | 2.2.2 Cache         | 2 |  |  |

|                |            | 2.2.3 Interconnect  | 4 |  |  |

|   | 2.3                                           | Introdu                                                               | action to FPGAs                             | 16                                                                                             |

|---|-----------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------|

|   | 2.4                                           | Cores                                                                 |                                             | 17                                                                                             |

|   |                                               | 2.4.1                                                                 | MicroBlaze                                  | 19                                                                                             |

|   |                                               | 2.4.2                                                                 | PowerPC                                     | 20                                                                                             |

|   | 2.5                                           | Enviror                                                               | nment                                       | 21                                                                                             |

|   |                                               | 2.5.1                                                                 | Hardware                                    | 21                                                                                             |

|   |                                               | 2.5.2                                                                 | Field Upgradable Systems Environment - FUSE | 22                                                                                             |

|   |                                               | 2.5.3                                                                 | Virtex-E                                    | 22                                                                                             |

|   | 2.6                                           | Tools .                                                               |                                             | 23                                                                                             |

|   |                                               | 2.6.1                                                                 | GCC                                         | 23                                                                                             |

|   |                                               | 2.6.2                                                                 | ISE                                         | 23                                                                                             |

|   |                                               | 2.6.3                                                                 | XPS                                         | 23                                                                                             |

|   |                                               |                                                                       |                                             |                                                                                                |

| 3 | Met                                           | hodolo                                                                | gv                                          | 25                                                                                             |

| 3 |                                               | hodolo                                                                |                                             | 25                                                                                             |

| 3 | <b>Met</b><br>3.1                             | Introdu                                                               | action                                      | 25                                                                                             |

| 3 |                                               | Introdu                                                               |                                             |                                                                                                |

| 3 | 3.1                                           | Introdu<br>OMA                                                        | action                                      | 25                                                                                             |

| 3 | 3.1<br>3.2                                    | Introdu<br>OMA                                                        | ection                                      | 25<br>26<br>27                                                                                 |

| 3 | 3.1<br>3.2                                    | Introdu<br>OMA<br>Core .                                              |                                             | 25<br>26<br>27                                                                                 |

| 3 | 3.1<br>3.2                                    | Introdu<br>OMA<br>Core .<br>3.3.1                                     | action                                      | 25<br>26<br>27<br>28                                                                           |

| 3 | 3.1<br>3.2                                    | Introdu<br>OMA<br>Core .<br>3.3.1<br>3.3.2                            | action                                      | <ol> <li>25</li> <li>26</li> <li>27</li> <li>28</li> <li>29</li> </ol>                         |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Introdu<br>OMA<br>Core .<br>3.3.1<br>3.3.2<br>3.3.3                   | action                                      | <ol> <li>25</li> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> </ol>             |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Introdu<br>OMA<br>Core .<br>3.3.1<br>3.3.2<br>3.3.3<br>Cache<br>3.4.1 | action                                      | <ol> <li>25</li> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> <li>31</li> </ol> |

|                  | 3.7                  | Benchmark                                    | 37 |  |

|------------------|----------------------|----------------------------------------------|----|--|

|                  |                      | 3.7.1 BogoMIPS kernel                        | 37 |  |

|                  |                      | 3.7.2 Load-Store kernel                      | 38 |  |

| 4                | $\operatorname{Res}$ | sults                                        | 39 |  |

|                  | 4.1                  | Introduction                                 | 39 |  |

|                  | 4.2                  | Benchmark results                            | 40 |  |

|                  |                      | 4.2.1 BogoMIPS Kernel                        | 40 |  |

|                  |                      | 4.2.2 Load/Store kernel                      | 42 |  |

| <b>5</b>         | Dis                  | cussion                                      | 45 |  |

|                  | 5.1                  | Cores                                        | 45 |  |

|                  | 5.2                  | Cache                                        | 46 |  |

|                  | 5.3                  | Time                                         | 47 |  |

|                  | 5.4                  | 3rd Party Challenges                         | 48 |  |

|                  |                      | 5.4.1 GNU Compiler Collection for MicroBlaze | 48 |  |

|                  |                      | 5.4.2 Xilinx IP Glue for OPB                 | 49 |  |

|                  | 5.5                  | Benchmarks                                   | 50 |  |

| 6                | Cor                  | nclusion                                     | 53 |  |

|                  | 6.1                  | Conclusion                                   | 53 |  |

|                  | 6.2                  | Future Work                                  | 54 |  |

| Bi               | Bibliography         |                                              |    |  |

| $\mathbf{A}_{]}$ | Appendices           |                                              |    |  |

| Α            | Ben  | nchmarks             |     |  |  |

|--------------|------|----------------------|-----|--|--|

|              | A.1  | BogoMIPS kernel      | 61  |  |  |

|              | A.2  | Sample Linker script | 62  |  |  |

|              | A.3  | Sample Makefile      | 63  |  |  |

|              | A.4  | LoadStore kernel     | 64  |  |  |

| в            | Har  | dware                | 65  |  |  |

|              | B.1  | Core OMA Interface   | 65  |  |  |

|              | B.2  | CPU Identifier       | 71  |  |  |

|              | B.3  | RAM Block            | 75  |  |  |

|              | B.4  | Cache Block          | 79  |  |  |

|              | B.5  | Arbiter              | 87  |  |  |

|              | B.6  | PCI COM              | 89  |  |  |

|              | B.7  | Toplevel - mCache    | 94  |  |  |

|              | B.8  | Toplevel - mCore     | 99  |  |  |

|              | B.9  | Toplevel - sCore     | 103 |  |  |

| $\mathbf{C}$ | Soft | ware                 | 107 |  |  |

|              | C.1  | Controller.c         | 107 |  |  |

|              | C.2  | Controller.h         | 112 |  |  |

|              | C.3  | memory.h             | 113 |  |  |

|              | C.4  | memory.c             | 114 |  |  |

|              | C.5  | cpu.c                | 118 |  |  |

|              | C.6  | cpu.h                | 122 |  |  |

| C.7 | util.h                                                                                                                                        | 3 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|---|

| C.8 | util.c $\ldots \ldots \ldots$ | 4 |

## List of Tables

| 3.1 | Signal interface         | 27 |

|-----|--------------------------|----|

| 4.1 | Processor Configurations | 40 |

# List of Figures

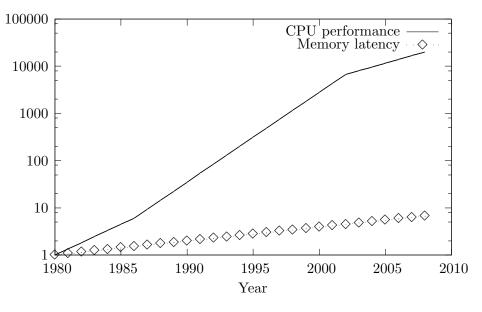

| 1.1  | CPU Memory Gap            | 2  |

|------|---------------------------|----|

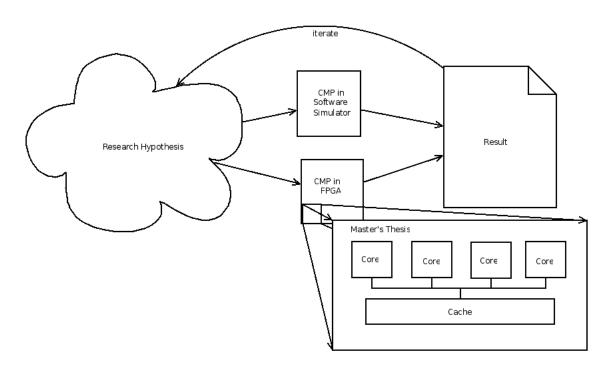

| 1.2  | Project Overview          | 5  |

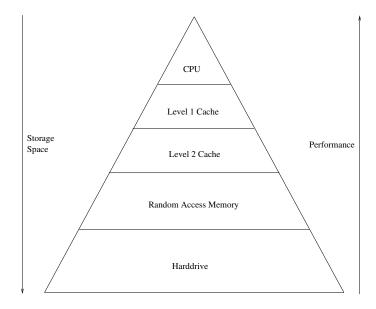

| 2.1  | Memory Hierarchy          | 9  |

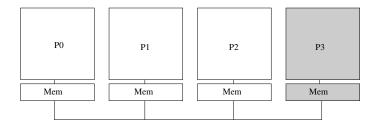

| 2.2  | Core number 3 is disabled | 10 |

| 2.3  | Fully Associative Cache   | 13 |

| 2.4  | Set Associative Cache     | 13 |

| 2.5  | Direct Associative Cache  | 13 |

| 2.6  | Shared Bus                | 15 |

| 2.7  | Crossbar interconnect     | 15 |

| 2.8  | FPGA routing              | 17 |

| 2.9  | Sample CLB                | 18 |

| 2.10 | LUTs per Core             | 19 |

| 2.11 | Cores per FPGA            | 20 |

| 2.12 | BenERA diagram            | 21 |

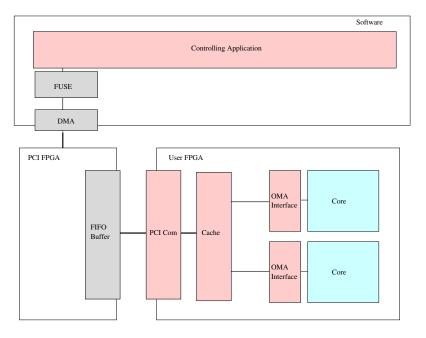

| 3.1  | Overall Architecture      | 26 |

| 3.2  | Core                      | 29 |

#### LIST OF FIGURES

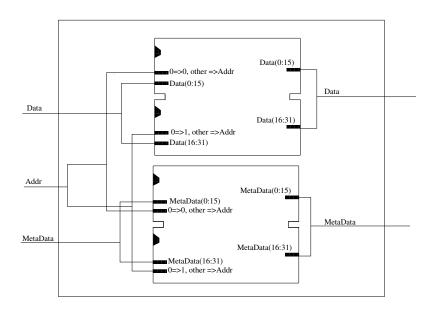

| 3.3 | Single Memory block         | 33 |

|-----|-----------------------------|----|

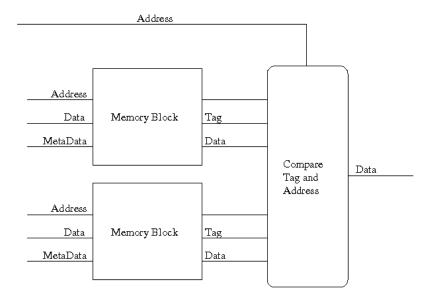

| 3.4 | 2-way set associative block | 34 |

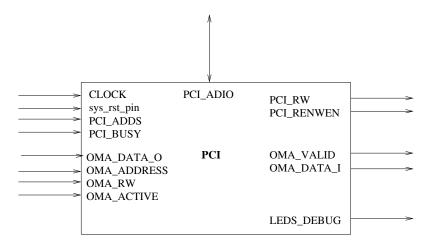

| 3.5 | PCI Unit                    | 34 |

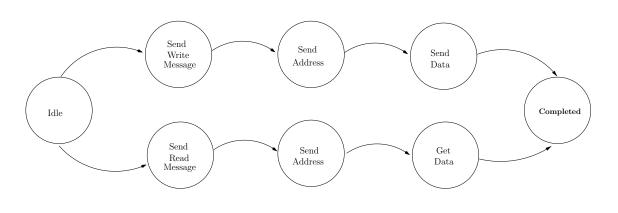

| 3.6 | Com States                  | 35 |

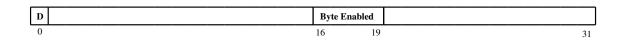

| 3.7 | Control Word                | 35 |

|     |                             |    |

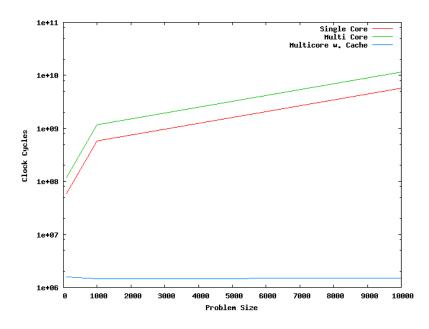

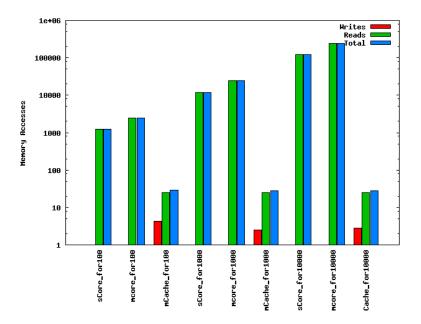

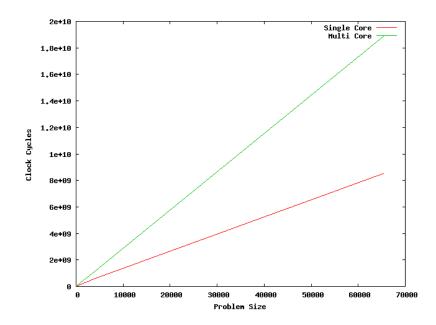

| 4.1 | BogoMIPS Performance        | 41 |

| 4.2 | BogoMIPS memory Access      | 41 |

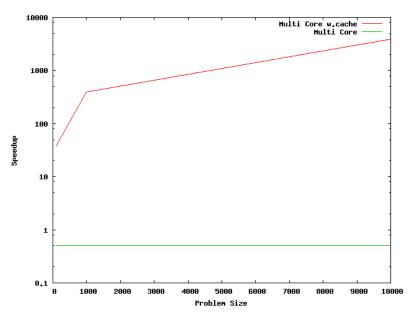

| 4.3 | BogoMIPS Speedup            | 42 |

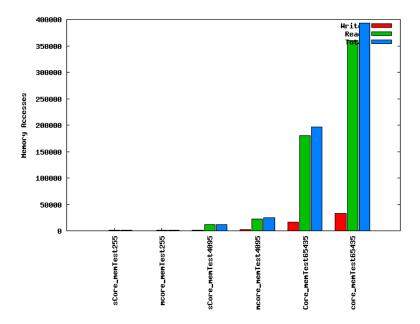

| 4.4 | MemTest Performance         | 43 |

| 4.5 | MemTest memory Access       | 43 |

|     |                             |    |

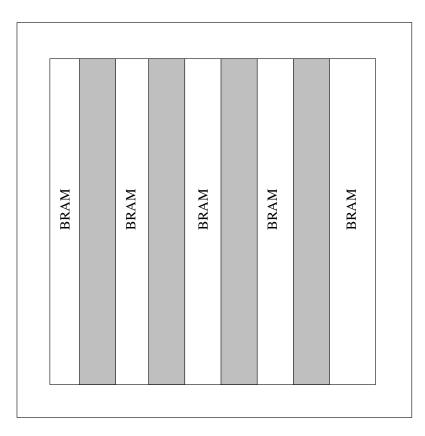

| 5.1 | BRAM Location on the FPGA   | 47 |

| 5.2 | Correct assembly code       | 49 |

| 5.3 | Output from GCC             | 49 |

## Chapter 1

## Introduction

### **1.1** Introduction

During the last couple of years, the traditional single core monolithic CPU has failed to further increase its performance proportionally to the decrease in transistor size, as the popular although not correct interpretation of Moore's Law[34] implies. This is, according to Dr. Patterson in his President's Letter[30], due to 3 main factors. (1) Power dissipation, (2) lack of Instruction Level Parallelism to exploit and (3) the long known memory gap which has steadily grown since the beginning of computer science. A fourth factor mentioned by Spracklen et al. [38] is the inherent complexity of designing a processor. A high performance single core CPU requires vast amounts of chip resources to implement the control logic, ensuring that operations don't interferes with each others. This leaves less room for implementing the computational logic, which in turn influences the overall performance of the processor. The Chip multiprocessor (CMP) tries to solve these problems by utilizing several cores inside a single processor. Having several cores on a single chip introduces several new problems, some which have been encountered before in the world of super computing and others new. This includes handling cache in an attempt to reduce the off-chip access, different topologies to allow inter-communication between on-chip processing elements and finally the power dissipation.

The memory gap, as shown in figure 1.1, has long troubled the computer engineers and has been the subject of several research projects. This is also one of the major focal points when researching CMP architectures. The reasons why the memory gap has appeared is a product of several factors. First there is the sheer distance the data signals must travel between the processor and the memory. Data on-chip have a shorter path to travel, and thus have a noticeable decrease in latency compared to off-chip access. Second, the technology and the larger size of memory that exists outside the processor adds to the latency by requiring more time to deliver the requested data onto the bus itself. All of these factors makes it important to limit redundant memory accesses, storing the frequently used

Figure 1.1: CPU/Memory performance[30]. Logarithmic plot for readability.

data in cache banks on the processor, keeping recently used data close in locality. This is done by employing different strategies which forces the processor and the cache banks to cooperate, trying not to evict the frequently used lines of data off the chip. This in an effort to reduce memory access outside the processor itself. Besides reducing the off-chip access much of the cache research studies ways of keeping data requested by the different cores near in locality close to the core which is most likely to request it. This might involve duplication and spreading cache lines around internally on the chip.

Another reason which forced the change of paradigm from single core processors to multicore processors is the increased difficulty of exploiting Instruction Level Parallelism(ILP). Exploiting ILP is to exploit the fact that certain combinations of instructions can be rearranged without changing the outcome. This is done to avoid stalls in the processor's pipeline, and hence reduce the time spent by the CPU idling. The main challenge exploiting ILP is that it gets exponentially harder per fraction of parallelism level, and thus stagnating at a certain level[15]. To achieve a perfect level of instruction parallelism, unrealisable hardware much be constructed. This to account for perfect branch prediction, unlimited access of registers and all the memory locations must be known beforehand in order to rearrange load and store operations[15]. All needed to achieve perfect ILP. Seeing how the work load on most of the commercial servers are not focused on computationally intensive tasks, but supporting several concurrent requests have forced forth a change where Thread Level Parallelism(TLP) has gained focus. By adding several cores true TLP can be achieved by running the different threads on different cores.

The power consumption of the computer processor has always been the subject of inquiries, although it has not been the major point of focus in desktop computers. Here performance has been the main focal point. However, as the frequency using traditional CMOS technology reaches its practical limit, ways of reducing the power dissipation have gained popularity. The CMP contributes mainly in two ways to help solve this problem. The first is due to the nature of cubic dependency between the operating frequency of the processor and its power dissipation as presented by Jerraya et al. [18] and Gochman et al.[13]. The practical implication of this means that by halving the frequency of a single core, the power consumption of a single core will be reduced to a mere quarter of its original use. Then by doubling the existing cores on a chip with half the frequency it is possible to retain the same performance with less dissipation of power. This is though a simplified version of the power usage. When calculating the overall consumption on a chip, the mechanisms for communication between different processing elements, cache and etcetera, must be taken into consideration. As shown by Kumar et al.[21], pending on the surrounding infrastructure, it is not only the cores themselves that dissipates power on a modern processor. Another interesting capability that comes with the inherit modularity of a CMP is the ease of resource management. If the load on a CMP is low, cores that are idling can be disabled to reduce the total power consumption. The ability to scale down the number of operational cores, and halving the total power dissipation are both important steps in battling the consumption of power in modern processors.

The final point which is mentioned by Spracklen et al.[38] and Olukotun and Hammond[27] is the inherit complexity of designing a modern processor and its cores. A high performance single core processor requires serious amount of effort into ensuring safe computations and a coherent environment. Since the cores employed by CMP's can afford a reduction in performance per each individual core and still have the same overall throughput, a single CMP core can be simplified compared to a core in a traditional single core processor. Also by allowing a scaled down version of the cores simplifies the development process, and thus reducing the time to marked and hence decreasing the production cost. Beside the purely economic reason, a simplified model decreases the chance of bugs in the core itself. Hence when gate size decreases, its performance can be improved by increasing the number of cores on-chip.

To help developers address new architectural challenges, software based simulator such as SimpleScalar[4] and M5[3] have been used. Here the developer specifies the different components on the processor and their behaviour. The problems with software based simulators are that they are not completely accurate in the sense that it has to sacrifice accuracy in some field to gain in another[16]. E.g., a simulator which perspires to be instruction set accurate will will not attempt to claim timing accuracy[16]. Another problem is that simulating an entire processor is a slow process, taking quite some time to produce results. The time it takes to produce results could be reduced by decreasing the level of details as proposed by Hines et al.[16], but this would lead to less accurate simulations. Also, by having to manually specify the different levels of detail in the model leaves room for inconsistencies between the different run levels. This might produce different results depending on the detail level when simulating.

The Field Programmable Gate Array(FPGA) is a natural evolution of the Programmable Logic Arrays which allows the developer to program the behavior of the logic hardware.

The extension which made the FPGA popular to prototyping hardware is its Field-Programmable attribute. Unlike many implementations of the Programmable Logic Array, the behaviour of the FPGA is fully reprogrammable. In modern FPGA's this is solved by connecting each programmable unit, i.e., its logic elements and routing resources, to the corresponding bit in memory. Then by changing the bit-stream the behaviour of the FPGA changes. An example would be a mathematical unit, the Arithmetic Logic Unit(ALU). Pending on its corresponding bit, the ALU might work as either an multiplier, divisor or a different mathematical operation. Then by connecting several logic elements it's possible to get the desired behaviour. The major drawback of FPGA's is that due to their flexible nature, they cannot be have the same high clock frequency as a dedicated chip, Application Specific Integrated Circuit. The advantage is that the calculations which the software based simulator must calculate serially per simulated cycle, will happen in true parallel on a FPGA. This means that the reprogrammable hardware will have an increase in performance compared to an software based simulator.

To be able to prototype new multicore architectures and architectural parameters trying to improve CMP performance, a platform which allows for rapid changes is needed. It is also important that the time to produce results is reduced to increase productivity. To help decrease the period between a new architecture or parameter is decided upon, and until the result is known, a flexible FPGA platform is used. To achieve the flexibility in hardware, an architecture must be modular to allow for interchangeable elements. This to prevent time demanding and challenging rewrites of the entire system.

### **1.2** Problem Description

One of the new trends in computer architecture to battle the performance wall by introducing several cores on the same chip. By doing so, the computer engineers were put in front of old challenges in a new setting. Techniques which were meant for large cluster suddenly had to be scaled into a single die and novel ideas was needed. Seeing how the cost in terms of money and time imprinting the first chip is to high to allow prototyping, simulators and logic analyzers have been the mainstream technology of prototyping processors. However software based simulators such as SimpleScalar[4] are notoriously slow, and in nature not able to fully accurate simulate the inner workings of a CPU[16].

The goal of the Master's Thesis is to investigate and develop a hardware based platform for testing Chip Multiprocessors using Field Programmable Gate Arrays, figure 1.2, as a alternative to the software based simulator. The platform should allow for change of architectural parameters and components.

Figure 1.2: Project Overview

## 1.3 Project Motivation

The NTNU Computer Architecture Research Group has focused their research on Chip Multiprocessor Challenges[25]. More specific, the research group have focused their attention on intercommunication, caches, pre-fetching and scheduling. At the time this thesis was written, their main method of prototyping multicore architectures was based upon software simulators such as SimpleScalar and M5.

Since the software based simulations used to much time in producing results, the NCAR group wanted an supplementary method of prototyping their proposed multicore architectures. They also wanted a platform through which they could rapidly change the architectural parameters in order to test several configurations. This without changing the underlying behavioural code.

### 1.4 Contribution

Through his work with the Master's Thesis the author has contributed with the following set of items. A throughly background search has been done in the field of Chip Multiprocessors. The author has contributed by presenting a hardware based platform for prototyping novel computer architectures. Through the hardware platform the author has contributed by allowing fellow researchers to produce results more accurate, and decreased the time waiting for results.

### 1.5 Scope

This thesis will describe a multicore architecture and the methodology used. The thesis will present relevant research and background information needed to understand chip multicore architecture. It will not describe in detail the inner workings of processor core technology beyond what's needed to implement it in a multicore environment.

### 1.6 Outline

In chapter 2, the thesis will present the relevant background information for reading this paper. It will start by an displaying the relevant work, before it will continue by introducing the central concepts in computer architecture relevant to chip multiprocessors. Chapter 2 will end with a presentation of the tools used.

Chapter 3 presents the methodology, where the hardware architecture is described. Chapter 3 will end by a presentation of the controlling software and the application used for testing the hardware design.

In chapter 4 the thesis will show the result from the benchmark suite introduced in chapter 3, before the results will be further discussed in chapter 5.

Finally the thesis will conclude with chapter 6 with the conclusion and further work.

### 1.6.1 Appendices

Appendix A contains the benchmarks created for the processor. Appendix A also contains the makefile and linker script required in order of building the binary application.

Appendix B contains the hardware developed for this project, with the toplevel configurations in B.9, B.8 and B.7. Besides the code found outside the architecture section in appendix B.1 and B.2, which is glue code code generated by the Xilinx tools, everything has been written by the author. Some bugs has also been fixed in the glue code, as discussed in section 5.4.2.

Appendix C contains the software developed by the author to control the FPGA and act as main memory as described in section 3.6.

## Chapter 2

## Background

This chapter will discuss different architectural challenges designing a CMP, and present some of the proposed solutions. It will introduce the reader to the field of processor architecture and FPGA's by first presenting the already existing work before introducing central concepts, and finally the tools used to develop the FPGA framework.

### 2.1 Related Work

One of the central problems designing new hardware architectures is to be able to test the architecture before sending it to production. Being able to both test the hardware and software before production, is of grave importance to create a stable and optimal platform. Traditionally the software developers have lagged behind the hardware manufacturers due to traditional simulators producing results to slow. This is one of the challenges that the Research Accelerator for Multiple Processors(RAMP) project is addressing[41]. The RAMP project is a collaboration between different universities and cooperations such as Berkly, Xilinx, IBM and others[2]. Having a FPGA framework allows the software developers to test different implementations in operating systems and compilers before the architecture reaches production. To serve as the developing platform, the RAMPants<sup>1</sup> have opted for the Virtex5 FPGAs to provide the hardware platform. The processor cores used are a mixture of MicroBlaze soft cores, and PowerPCs hard cores. The reference designs available from the RAMP project focuses on either transactional memory, distributed systems or distributed shared memory[41].

While the RAMP project is the first one where which a well defined interface for communication between different parts, allowing for exchangeable parts, there has been different implementations of CMP in FPGAs. Amongst these, Socrates is worth mentioning. Socrates, being one of the early adapter, has focus upon proving that a CMP can be de-

<sup>&</sup>lt;sup>1</sup>Member of the RAMP group

signed on a FPGA, and that it can be done rapidly[7]. The cores in Socrates are based upon an own implementation of ARM cores which in turn are connected to an crossbar mechanism to provide communication between the different elements. This allows the design to increase in size, leaving room for growth in FPGA transistor counts. The downside to the Socrates implementation is that the crossbar interconnect, as shown by Kumar et al.[21], wont scale as gracefully with the number of cores connected to it. This severely limits the amount of cores available to the Socrates platform, both in terms of FPGA resources, and in a real life situation where also factors like power consumption plays a major part.

Although the FPGA gains approval for prototyping hardware, there are still project prototyping using commodity hardware. The Stanford Hydra project is a research project testing out novel architectures for Chip Multiprocessors, basing their processor cores on four MIPS based processors[14]. To be able to simulate the processor design they have built a circuit board using four MIPS R3000 processors cores[28]. Each of the cores are connected to a floating point unit and a Virtex FPGA in order to form a single processor tile. By configuring the FPGAs, the Hydra project can simulate an array of different configurations.

### 2.2 CMP Architecture

Having several processor cores on a single chip brings forth new and challenging problems related to power consumption, cache strategies with multiple cores, communication between cores to ensure cache coherence and off-chip access. Although the physical scale has reached a new level, currently at a gate level of  $45 \text{nm}[10]^2$ , these problems have been addressed before by the world of supercomputers. Seeing how supercomputers traditionally have several processors, distributed/shared memory, and a network between the processing nodes, many of the concepts can be transposed down to fit the scale of a single chip. Furthermore, some of the rejected ideas have resurrected seeing how the scale have changed from several processing nodes, to a single chip, moving the limits on latency and bandwidth. This have led to interesting CMP strategies, where tried and tested supercomputer paradigms have been reused.

More specific, as shown in figure 1.1, during the last years, the core frequency have stagnated, which has left the developers looking for other ways to improve the overall performance, while improving the power consumption. Since the gate size has had a drastic drop, it has been possible to put several cores on a single processor. Then by decreasing the frequency per core, the power consumption have drastically decreased. Other interesting features of the CMP, being modular, is that it allows for easier resource management. This in turn makes it possible to turn of inactive parts, in an attempt to reduce consumption of power. Another important point of focus is that of off-chip access to remote peripherals, e.g. memory. The gap between the CPU and memory has steadily increased, and has

$<sup>^{2}</sup>$ In 2007

evolved into a complex hierarchy, known as the Memory Hierarchy, figure 2.1. This states that the further memory are from the CPU registers, the higher access cost in terms of latency, but more memory it has allocated. This challenge has introduced the notion of having banks of cache distributed around the system, allowing for temporary storage closer to the processing unit. Since the storage capabilities, in effect, dictates the latency several levels of cache can be found on the CMP. In a multicore environment the challenge lies upon having the cores cooperating on retrieving lines of external data, avoiding retrieving the same data twice. This in attempt to try reduce the amount of unnecessary duplicate off-chip communication.

Figure 2.1: Example memory hierarchy

Although if the cores weren't to cooperate on the data retrieval, they would still need a way of invalidating cache lines. Each core might have their own copy of data in cache, and if one of the cores writes to the memory, the system need some way of notifying the other cores holding a copy of the data. If not the task would lie upon the software developer to lock memory accesses, which would be a tedious and error prone job.

#### 2.2.1 Cores

The core is the main processing element on a traditional processor, performing instructions which it loads from memory. Traditionally the performance of a single core CPU has been given by the frequency of the internal clock, and the internal architecture of the core. The frequency has been dependent of the underlying feature size and has been steadily rising until year 2002, see figure 1.1. Combined with the fact that extracting performance per clock cycle gets exponentially harder<sup>3</sup>, has led for a new way of extracting performance.

<sup>&</sup>lt;sup>3</sup>e.g., achieving a perfect level of ILP is impossible due to the demands of perfect hardware[15]

Figure 2.2: Core number 3 is disabled

Besides the raw performance challenges in designing a modern CPU, lowering the power consumption has increasingly gained popularity. The power consumed by a CPU is directly influenced by the frequency on which its internal core is set as shown in formula 2.4. As the generated heat is a function of the power consumed, the manufacturers have had problems cooling the CPU with apparatuses acceptable to the general public. This, and seeing how there is a lower bound to the latency of a signal traveling across the chip has led IBM to predict that their Power6 cores will extract the last amount of clock cycles available at circa 5Ghz[9] using the current available technology.

This has led to a search of other methods for increasing performance, acknowledging that the single core technology will stagnate at a given point using current technologies. Although at the time where this report was written a company named D-Wave in cooperation with NASA presented a co-processor using quantum technologies[1], this technology is still long from perfected, and has a long way before it is common household equipment. This has led to the manufacturers decreasing the complexity of a single core and increasing the total number of cores on each chip. This allows each core to decrease it's individual throughput, but the system as a whole will retain its performance[38].

Scaling down the complexity of a single core while decreasing the core frequency influences the power dissipation of the processor as a whole. This have led to a decrease in both the Dynamical and Static power dissipation. Static power dissipation is power dissipating due to transistor leakage[5], while Dynamical power dissipation refers to the rise and fall in current when the transistors changes state. A simplified equation for the total power dissipation is shown below in equation 2.1.

$$P_{total} = P_{static} + P_{dynamic} \tag{2.1}$$

#### **Dynamic Power Dissipation**

The dynamical power dissipation is attributed the change of state in the transistor. When a transistor is set low, it has to discharge to ground, which is the main source of dissipation. The following formula (2.2) as described by Jeraya et al.[18] and Gochman et al.[13] shows the dynamical power dissipation. Here  $F_0$  is the clock frequency. The  $C_0$  is the effective capacitance of the circuit, while  $V_0$  is the voltage and  $\alpha$  is the activity factor.

$$P_{dynamic} = \alpha * C_0 * V_0^2 * F_0 \tag{2.2}$$

In the same article by Gochman et al.[13], they show that the frequency can be approximated to be proportional of the core voltage  $V_0$ , which leads forth to formulas 2.3 and 2.4

$$F_0 \approx K_f * V_0 \tag{2.3}$$

$$P_{dynamic} = \alpha * C_0 * V_0^3 * K_f \tag{2.4}$$

As shown in equation 2.4,  $P_{dynamic}$  is cubic dependant of the frequency. Thus by halving the frequency per core, the core will dissipate of one quarter of its original power. Then by doubling the number of cores on the chip, the chip will retain its performance while halving its dynamical power dissipation.

#### Static Power Dissipation

The static power dissipation, "leakage", is an effect of the current gate technology[12], mainly due to subthreshold and oxide leakage[12]. In their article, Ghiasti and Grunwald[12] presents equation 2.5. This models the static power loss as a product of the Voltage current, leakage current, the number of gates N and a scaling factor k. The scaling factor is dependent of the inherit complexity of the design itself.

$$P_{static} = V_{cc} \cdot I_{leak} \cdot N \cdot k_{design} \tag{2.5}$$

A overall measure of the effectively per power dissipated is shown in equation 2.6. This shows the static power leakage over the million instructions per second, giving a rough estimate of how resourceful the processor is.

$$Eff = \frac{P_{static}}{MIPS} \tag{2.6}$$

To reduce the static power dissipation, Muthana et al.[22] suggests that by reducing the  $I_{leak}$  factor, would have a great impact. One of the methods would find an architecture which allowed for disabling caches and cores, as shown in figure 2.2.1.

Spracklen et at.[38] also mentions that in a single core processor, much complexity and logic is used in a controlling context, not in performance issues. This leads to a high N in formula 2.5, and thus the effectively according to formula 2.6 decreases. Spracklen et al. also mentions that a high performance core is a complex design, which leads to a higher  $k_{design}$  and further decreases the efficiency.

#### 2.2.2 Cache

As the gap between the CPU performance and the memory latency have grown as shown in figure 1.1 has grown, the need for temporary storage of data has increased. This has led forth to a hierarchy of memory structures where frequently used data is located near the CPU in terms of access time, allowing faster access to more popular data. A sample structure is shown in figure 2.1, where the data with the lowest access time could be stored inside the CPU itself and its registers. Duplicates of data that is frequently used would be placed in the level 1 cache, less frequently used in the level 2 cache and so forth, whereas the data stored on the disk or other external devices would take the longest to access. This is due to external memory have a higher latency before the requested data reaches the bus, the distance the signals have to travel, and the obstacles getting there. E.g., a DDR2 has the memory clock set at 400Mhz, whilst a traditional hard drive has a seek time given in milliseconds. Both considerably higher than the internal registers to the core which operates on clock frequencies measured in gigahertz and where the registers can be accessed in a few clock cycles.

To solve this challenge, cache banks have been introduced into the computer architecture storing a subset of available memory close to the processor, and thus reducing the access time for a set of frequently used data. Which lines of data and the amount of data that the cache can store internally is given by an amount of different parameters. When the cache gets full and a new item is to be stored, the cache bank must choose which one to evict, and different strategies exists to choose the right one, such as Least-Recently-Used[35] and Random-evict[40] depending on how the cache stores its data in memory. Each cache unit can store a certain amount of datum, cache lines, in memory. What differentiate one cache organisation from another is how its chooses store its cache lines, and the different parameters controlling the behavior.

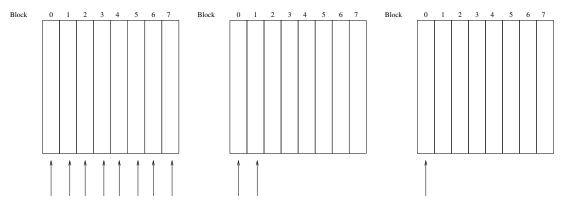

One of the easiest conceptual ways of storing cache lines would be to store the cache line at any given spot in the array of available cache lines. This strategy is known as fully associative, figure 2.3. To be able to keep track of which cache lines that is stored where in the cache, each cache lines' tag, i.e. the part of its associated meta data that describes which data that is stored in a given location, would have to be its full address. This would lead to an massive amount of overhead per cache line stored, seeing how for each line the cache must keep track of its corresponding address. Also during a lookup the cache must traverse through each line, matching its address to the requested address. This leads to a increase in latency when performing cache lookup. Another, faster way of organizing cache is directly associative cache, figure 2.5. Here a given number of the least significant bits of

Figure 2.3: Fully Associa- Figure 2.4: Strive Cache Cache

Figure 2.4: Set Associative Cache

Figure 2.5: Direct Associative Cache

the address can determinate which index that the cache line will be stored in. This would be conceptually equivalent of the mathematical modulo operation. By varying the amount of bits used to determine the index, i.e. varying the number in the modulo operation, the cache can keep a different amount of cache lines. The two obvious benefits by this method contra the fully associative is, one, the cache can reduce the number of bits in its tag. If X number of bits is used to determine the index where the data is stored, address - Xbits would be needed to provide the cache line's tag. The second advantage to directly associative cache is that a lookup requires significant less logic when determining a cache hit. A mixture between fully and directly associative cache is set associative, figure 2.4. The basic notion is that a set associative cache can keep several cache lines per index, i.e. the degrees of set associativity. A 1-set associative cache is the same as a directly associated cache, whereas a 2-set associative cache can store 2 cache lines per index.

#### Multicore Cache Architecture

Having several cores on a single chip introduces a new challenge, namely resource sharing. The basic challenge with the multicore cache architectures is the same as with a single core CPU, efficient use of off chip communication. Although the same problem, the environment has changed. Duplicate the number of cores on the chip, and the memory access will be duplicated using a naive single core cache strategy. Although the CMP is a relative new product in computer science, having several processing units in a computer isn't a new paradigm[32]. Challenges seen in CMP, e.g., communication, cache strategies, etcetera, have been addressed by earlier work. One of the more interesting effects in the CMP world is to see implementations which have been discarded in traditional supercomputing being reused in multicore CPUs. This might be strategies which have been discarded due to problems with latency, low bandwidth and so forth. Since all of the components on a CMP are placed on a single chip, old or discarded research can be re-evaluated seeing how the physical scale has changed.

To hide the gap between primary memory and the CPU, efficient off-chip communication is required. In a single core environment this can be solved using advanced prefetching, cache eviction schemes and etcetera. However, introducing multiple core on the chip have further brought new challenges. Seeing how another on-chip cache bank might hold the data requested from different core, some sort of cache cooperation is needed. Second, having several cache banks brings forth another phenomenon from the supercomputers, the Non-Uniform Memory Access(NUMA) effect, named Non-Uniform Cache Access(NUCA) [20] in CMP terminology. Although, to the core, each line of cache appears to be located in one uniform area of cache each cache bank stores a certain part of the whole. Due to the wire latency, pending on the physical location of the cache bank, accessing different parts of the memory will have different access times.

To help battling the problem several schemes have been proposed. Even though the implementations differs, they all have the same goal. Increase the off-chip communication efficiency, by making the cache banks cooperate. Chang et al. introduces an elaborate scheme based upon ideas from software[6]. Here all the cache banks are aggregated. When a cache bank evicts its data it will first try to "spill" the data over into another bank. However, if the cache is full with own data the bank will reject the "spilled" data. Another strategy is proposed by Dybdahl et al. where the instead of the LRU-scheme[35] a frequency counter is used[11]. Each cache is then allowed to grow shrink cache sets. In doing so, they allow cores with more frequently accessed data to dominate the cache.

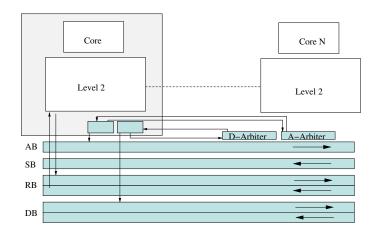

### 2.2.3 Interconnect

As soon a processor has several cores on the same chip, it starts to require an interconnect network between the cores, and other resources on the chip itself such as cache banks. Depending on a various amount of underlying architectural features, such as the number of cores available, the wanted performance in terms of latency, bandwidth and finally the power consumption, the topology of the underlying interconnect varies[21]. Thus depending on the requirements of the chip in production, different topologies will suit different needs. However, there are two main groups of interconnects which will be discussed, the crossbar interconnect and a shared bus as seen in figure 2.7 and 2.6. These two represents two completely different strategies, and thus they have two different sets of characteristics.

The shared bus, figure 2.6 is a network where all of the resources, i.e. the ones on the same network, are connected to the same set of buses. Having several resources connected to the same bus presents the problem with arbitration. If several resources tries to communicates on the same time, the signal would be ruined and the transfer would have to restart. Hence the need for a mechanism which arbitrates either the signal from the resource itself onto the bus, or a device which tells which resource that are allowed to send signals onto the bus at a given time. Kumar et al.[21] discusses a mechanism in which the cores requests access to the address and data bus by communicating with a arbitration device. However, since the medium through which the devices communicates is a shared one, only one signal can be active on the bus at one time. Even so, Kumar et al. presents methods of pipelining

Figure 2.6: Shared Bus

As described in Kumar et al.[21]

Figure 2.7: Crossbar

As described in Kumar et al.[21]

the process. One method is to include one bus for the control signals, address and data signal. Adding several buses, opens for the possibility to have one resource driving the address bus, while another one drives the data bus, fulfilling the previous request sent out on the address bus.

Unlike the shared bus, the crossbar topology, figure 2.7, relies on a direct connection between the resources on the chip. This helps reduce the time waiting for the data requested to arrive, but has a much higher cost in areal and energy consumption. An example shown in Kumar et al. shows that a crossbar mechanism introduces an area overhead of 11.4%, 22.8% and 46.8% with respectively 2-, 4-, or full sharing on a 8 core processor using a  $400mm^2$  die[21]. However, cores will have have to stall less waiting for the data to arrived using the crossbar. The same paper shows that with a 8 core, fully connected crossbar and shared cache, the power consumption will match that of 3 cores in just the interconnect alone.

## 2.3 Introduction to FPGAs

Due to their flexibility in nature, the FPGA have gained status as "reconfigurable" hardware. Having flexible hardware is a great advantage in situations where the developer don't want to be locked down by the restrictions put forth by the ASIC. Examples would be in computer architecture research and embedded devices, where reconfigurability is the key. Having a configurable hardware unit is preferred compared to performance when developing hardware.

Although traditionally, the FPGA has been viewed upon as a device for prototyping new hardware, it has recently gained approval for usage in computationally heavy areas such as DNA string matching and several cryptology algorithms[8]. The FPGA being a reconfigurable device has always lagged behind the CPU in terms of clock frequency, and thus it has been ignored when raw clock frequency is preferred. However, the ability to act as a true parallel device outperforms the serial processor in areas where parallelism is the key feature. The reconfigurability comes on cost of frequency, and when this thesis was written, Xilinx produced FPGA's which operated at about 500 megahertz[46]. This in contrast to the modern processors provided by Intel and AMD which operated in the range of 3000 megahertz.

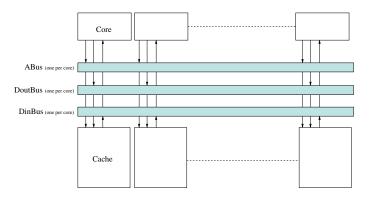

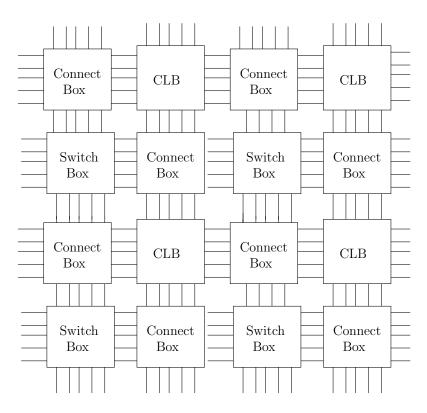

The way that FPGA's achieve such flexibility are based upon, two attributes. First the ability to configure each individual Configurable Logic Block(CLB), and second a configurable network connecting CLB's to each other. To program the FPGA, the developer loads a bitfile into the memory of the FPGA. Portions of the memory is connected to each resource in the FPGA, being either the routing switch, or the CLB. This leaves the developer able to create virtually any circuit by loading the right bitfile into memory, given that the FPGA have enough resources available.

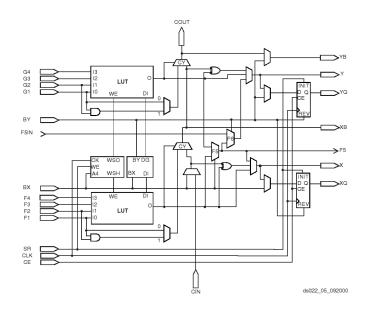

Each CLB, figure 2.9, consist of several logic elements[8]. This might range from D-Flip Flops and lookup tables to coarser units as Arithmetic Logic units. Having several logic blocks in the same block gives the developer the ability to create more advanced units without having to use an excessive amount of the available resources. However, it is important to retain the possibility to have a fine grained output. An arithmetic logic unit will outperform the lookup table at arithmetic operations, but it will not give the developer enough flexibility to design more specialized units.

The routing on a FPGA is controlled by utilizing pass-through structures[8], controlling their behaviour through the bitfile. On modern FPGA's, the CLB is connected to a nearby connect box as shown in figure 2.8, forming a Island Style network[8]. At each intersection, the control bit decides if the signal should continue in the same vertical or horizontal direction, switch direction or be routed to a neighbouring CLB. That way it is

Figure 2.8: FPGA routing

possible to route the signal between different parts of the FPGA, forming complex designs utilizing more than one CLB.

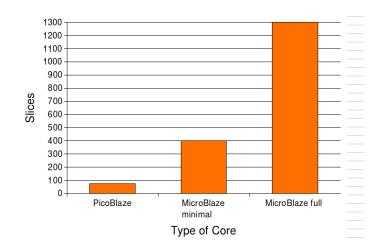

When deciding upon which FPGA to use for this project, several factors are important. A modern CMP is a complex design, and complex designs utilizes a lot of logic cells. Of the FPGA's available to the author, the VirtexE 2000 has 43,200 of logic cells, while the Virtex 1000 has a number of 27,648. Greater amount of logic cells available allows for more complex implementations, using more complex structures or having more soft cores. Figure 2.10 shows a sample of soft cores and their resource in terms of slices on the VirtexE FPGA, each slice being an aggregate of two logic blocks. Other structures that are important are the interconnect, on-chip block RAM and off-chip communication. A integral part of a multicore processor is its cache banks. Thus if the FPGA has on-chip block RAM, additional slices can be saved not having to implement storage blocks using logic units.

### 2.4 Cores

When designing a multiprocessor on a FPGA, one of its most fundamental features is its cores. Of the cores available to a designer there are two different sub-types, depending

Figure 2.9: Sample CLB[42]

on (1) the wanted qualities and (2) what the hardware supports. What differentiates the hard core from a soft core is if it is a physical implementation, e.g., core molded onto the FPGA, or if it has to be implemented together with the rest of the code.

The soft core, is a separate project delivered in a form that allows the developer to synthesize it together with the rest of the code. The core might be delivered in form of VHDL, or an already implemented netlist mapped to the underlying hardware. Having an independent core gives the developer more freedom to experiment, and decouples the core from the underlying hardware. The hard core is a new phenomenon seen where the FPGA manufactures integrates existing processor cores on the FPGA itself. The hard core allows for greater performance compared to an implementation in VHDL, being a specialized circuit. However by utilizing a hard core the design gets more bound to the underlying hardware and thus scarifies flexibility for performance.

Of the soft cores available there are mainly two groups, commercial available such as the MicroBlaze[45] and freely available microcontrollers as the NanoBlaze and other experimental cores developed by hobbyists found at sites as OpenCores. The PicoBlaze[43] core is a product of the Xilinx Cooperation, and is a small 8-bit controller. For the PicoBlaze controller, Xilinx have opted for a unit which leaves a small footprint in the design, and thus have optimized away several complex instructions which would have made the controller increase in areal. Instructions such as multiply, divide and floating point calculations are non-existing. There exists schematics which shows how to connect several PicoBlaze controllers together to gain support for such instructions. However, in doing so would render the main feature of the PicoBlaze void. Being a small microcontroller, one of stressed points about PicoBlaze is that it provide an alternative to hardware circuits without the areal overhead normally associated with introducing a microcontroller.

Figure 2.10: Number of Slices per Core.

#### 2.4.1 MicroBlaze

The MicroBlaze microcontroller is the grown up version of the PicoBlaze. Being a 32-bit processor, it matches the modern day processor both in data and address width, and thus it is more suited for modern applications than its proceeder, the PicoBlaze. MicroBlaze implements a wide array of instructions, adding support for floating point, multiplication and several others on the expense of areal and resources used. However, one of the major selling points is that the MicroBlaze controller can be customized to provided the needed functionality. Support for such instructions as floating point might be omitted if the design doesn't require it, freeing space for other components. The controller also, in attempt to match the PPC-core found on some Xilinx FPGAs, confirms to IBM's CoreConnect[17] architecture[45]. This allows the hardware developer to extend the controller with extra peripheral units. Some of the most important buses includes the Local memory bus (LMB) and On-chip peripheral bus (OPB). With these two buses the controller can attach units through which it can communicate using a memory mapped scheme. The major difference between the two buses is that the LMB is a much simpler interface, connecting units which are to guarantee a one cycle response. This bus is where the designer normally would connect on-chip memory such as Block RAM controllers. OPB is a more complex bus, allowing slower peripheral units. Typical examples would be peripherals which are not memory, including units such as media access controllers and off-chip units. The final way of attaching units to the controller is through a link called Fast Simplex Link(FSL). The MicroBlaze can have 8 FSL interfaces which provides a low latency interface through which hardware accelerators can be attached.

#### 2.4.2 PowerPC

Of the hard cores available, Xilinx have embedded IBM's PowerPC 405 on their Virtex-II Pro line of FPGAs. The 405 is an embedded core developed by IBM to suit the embedded marked. This includes a more specialized system for memory management and specialized registers for debugging etcetera. The external interface matches that of the MicroBlaze controller, so hardware developed for one would suit the other without, in theory, code rewrite. What differs the PPC405 from the MicroBlaze is that, in being a PowerPC, it must confirm to the PowerPC standard. Each PowerPC must correctly implement the User Instruction-Set Architecture(UISA). The USIA guaranties that the controller will behave exactly the same as all other PowerPC cores when in userspace. This leads forth to the PowerPC having a better support for compilers, and operating systems than the MicroBlaze core. Although a version of microcontroller-Linux has been ported to MicroBlaze, several others including NetBSD have been ported to the PowerPC platform[31, 29, 26].

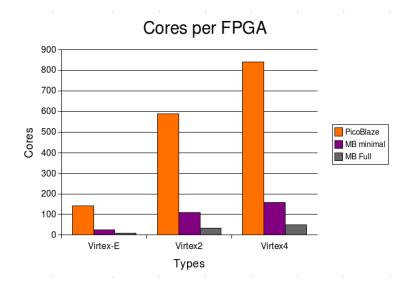

Figure 2.11: Number of Cores on a FPGA

One major implication the type of core imposes, is the number of cores available on a single FPGA. Figure 2.11 shows the amount of cores available on various types of FPGAs. However, its worth mentioning that it is an approximation. The number of cores are a function of the number of slices available on the FPGA over the number of slices occupied by a single core. In real life other resources should be taken into consideration. Even so, figure 2.11 gives an rough estimate over the number of cores available.

## 2.5 Environment

## 2.5.1 Hardware

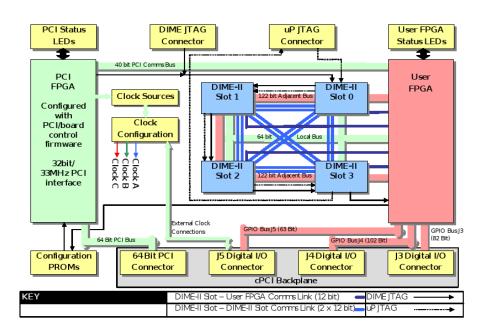

The server which hosted the project was a CompactPCI IBM Compatible server running the Debian Gnu/Linux operating system. On board the host computer were two BenERA CompactPCI DIME-II motherboards[24]. Each of the two BenERA motherboards had two Virtex-E FPGAs as shown in figure 2.12, respectively marked red and green.

Figure 2.12: BenERA functional diagram [24]

Having two FPGAs on the same motherboard, Nallatech could occupy one to perform solely administrative functions. That FPGA is marked in the functional diagram(2.12) with green and is the PCI FPGA. The PCI FPGA acts as the bridge between the User FPGA and the host computer, simplifying the communication between the software and hardware. To achieve this, Nallatech loads the PCI FPGA with firmware that communicates through the PCI bus on the host computer. To provide communication between the host computer and the User FPGA, the PCI FPGA has a FIFO buffer which can be read and written to from both User FPGA and the software through the FUSE library described in section 2.5.2.

The user programmable FPGA was a single Virtex controlled through the PCI FPGA[24] and JTAG[33]. Further, the same motherboard could be extended with four new modules confirming to the DIME-II industrial standard. Modules that fit the DIME-II standard includes memory modules such as SDRAM and DRAM or FPGAs, including the new Virtex II-Pro.

## 2.5.2 Field Upgradable Systems Environment - FUSE

To provide communication between the User FPGA and the controlling software, Nallatech ships a FUSE library with their motherboards. This creates an abstraction layer between the software developer and the design running on the User FPGA[23]. The library gives the software developer the opportunity to control the clock frequency, loading bitfiles containing the FPGA design and configuring the DMA communication channel.

## 2.5.3 Virtex-E

The programmable FPGA hosted on the BenERA motherboard is a Virtex-E. The Virtex-E is a SRAM based FPGA[42], which means that the behaviour is defined by loading the generated bit stream into SRAM memory. The bitfile loaded into memory will control the different logic elements and routing resources, behaving close to the generic FPGA described in section 2.3.

The configurable logic block is implemented as shown in figure 2.9, with four logic cells pared into two slices. Each logic cell has in turn one four bit input lookup table, which acts as the function generator. Each CLB can aggregate their Lookup Table(LUT) s, and that way it is possible to get function generators with a greater width, totalling at 5-6. However, in the modern lines of Virtex FPGAs, the native width of the LUT is 6, such as in the Virtex 5[46]. Besides the role as a function generator, and thus as a pure logical unit, it is possible to configure the logic blocks such that it will act as memory. Done correctly, the developer can use the CLB s to create memory banks. Each CLB having a four bit input is able to store either 1x16 bit RAM or connect two CLB to generate either a 2x16 or 1x32 bit RAM block. A more resourceful way of storing RAM on the Virtex-E FPGA is to use the already existing Block RAM structures. Placed evenly spread between each row of logic elements, Xilinx has placed 96 BlockRAM on the xcv1000E model. Each BlockRAM being a 4096 bit dual port RAM gives the FPGA a total amount of 393,216 bits dedicated memory. Another feature of the BlockRAM is that it might be used as a large LUT taking the memory address as input, giving the data stored as the output.

The routing network on the Virtex FPGA is close to the one described in section 2.3. However what differs is that each connect box is connected to several other lines running a various amount of distances. Each CLB is connected to, what Xilinx calls, a General Routing Matrix(GRM) which acts as both the connect and switch box. Each GRM is is connected to their direct neighbours, the neighbours with a Manhattan distance of one. To help decrease the latency, each GRM is also connected to a longer wire, which stretches over 6 GRMs. However this wire is driven from the end GRMs, but is accessible from the boxes in between. The last set of wires is those who runs from one side of the chip to the other, allowing for rapid global communication. Finally all GRMs can access global signals such as clock signals and reset.

## 2.6 Tools

The tools used can be divided into two main groups, the ones used for hardware development, and the ones used to develop software. The hardware tools for this project is mainly those delivered with the Virtex-brand of FPGA s. This includes Integrated Studio Environment(ISE) which works as a IDE providing everything from syntactical analysis of the VHDL code, down to the creation of the FPGA specific bitfile. The tool to configure the MicroBlaze core is XPS, which easily allows for configuration. The software development tools used is mainly various ports of GCC to create both the running environment on the host machine, and compiling applications to run on the FPGA implemented processor.

#### 2.6.1 GCC

GCC is the Gnu Compiler Collection, and has been ported to several platforms. One of the major advantages to the compiler, which makes it cross compatible is that they have separated the different functional layers[39]. The first layer is the language layer, converting from a programming language to an internal tree structure. Afterwards the compiler will optimize the tree, before it passes it to an machine dependant layer. By having done so, all which is needed to support a new platform is to extend the back end to support a new architecture. This has made the GCC-compiler the preferred choice for many embedded producers. Both the embedded PowerPC core and the MicroBlaze controller have a version of GCC ported by Xilinx.

#### 2.6.2 ISE

Integrated Software Environment is the development environment created by Xilinx[37]. The application is a front end to the entire chain of tools needed from synthesising the written VHDL files, to the generation of the chip specific bitfile to be loaded onto the FPGA. The general flow in creating a bitfile starts with the developer writing VHDL code which specifies the behavior of the hardware. Then XST, will generate a Xilinx spesific netlist. Afterwards the applications will perform map, translate and placement and routing(par). This will map the resources needed by the netlist to the resources found on the actual FPGA. Afterwards the bitfile used to configure the chip is generated by the bitgen command. All this is taken hand of by the ISE, and thus decreases the development cycle.

#### 2.6.3 XPS

To allow the user to make customizations to the MicroBlaze microcontroller, Xilinx packs XPS with their Embedded Development Kit[44]. Through the XPS application, the de-

veloper can extend the MicroBlaze or PowerPC core by attaching different modules to one of the many buses. Through the application the developer can tune the core to include certain features such as floating point unit, hardware support for multiply and division.

# Chapter 3

# Methodology

This chapter will describe the design of the multicore processor. It will start with a short description of the overall design notion, before it will present the most important components. After having presented the multicore processor design it will present some of the software developed to control the CPU. Finally it will present some of the developed benchmarks and test applications used to test the working CPU.

### **3.1** Introduction

The architecture is designed for extendibility, allowing the developer to test new and novel architectural changes, only rewriting or changing the parameter in question. The partitioning of the system is shown in figure 3.1<sup>1</sup>. The processor's main memory is implemented in software, while the rest of the design is implemented in hardware using VHDL. Having the memory in software allows the designer to easily calculate the number of cache misses, each software memory access not being in the on-chip cache banks. Software based memory also has the advantage that it is much cheaper in terms of areal, thus freeing resources from the FPGA which can be used for cache or other logic.

The software communicates to the hardware through the PCI FPGA, using a memory mapped scheme. On the hardware side the software communicates to the PCI FPGA, a specialized FPGA mounted to provide an interface between the programmable FPGA and the software running on the host computer. On the PCI FPGA the software accesses a FIFO buffer which is connected to the User FPGA, containing the data to be communicated to or from the processor. Being a 32 bit wide FIFO, the software will fetch 2 words, before deciding if the last transfer should be a write or read to the buffer pending on the nature of the memory access. Once transfered to the buffer, it is communicated through a bus dubiously called the Peripheral Component Interconnect which is connected to the

<sup>&</sup>lt;sup>1</sup>Red marking the systems developed, blue the 3rd party cores, and gray FPGA specific modules

Figure 3.1: Overall Architecture

User FPGA and the PCI Communication module as shown in figure 3.1. This is where the data gets handled by the implemented design, and translated into a format which suits the internal components. Limited by the width of the buffer, the communication module has to multiplex 96 bits of data<sup>2</sup> into 3 words which can be transfered between the FIFO buffer and the User FPGA.

Once the data reaches FPGA, the data is communicated between the different modules, e.g. arbiter, cores and cache through the unified signal interface described in section 3.2. Having a unified interface allows all the modules to be replaced as long as they confirm to the same interface. Having this allows for the replacements of the cores themselves, freeing the design from the restrictions put forth by the MicroBlaze core and the Xilinx team, which in turn relinquishes the complexity associated to developing with the Xilinx tool chain. This leaves an overhead in the communication latency between the cores themselves and the rest of the system, having to translate from the CoreConnect architecture to an customised interface.

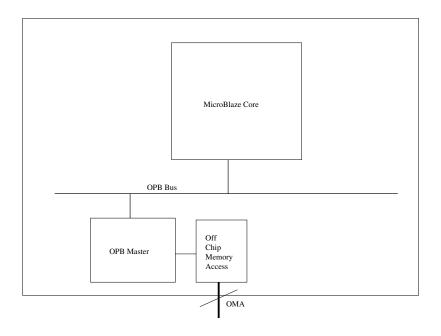

# 3.2 OMA

To uphold the demand for extendability, allowing for easily exchangeable units, a interface which all components must adhere was created. The interface itself was loosely based upon the CoreConnect architecture, although some of the fancier mechanisms removed

<sup>&</sup>lt;sup>2</sup>Address, Data and Control Word

| Name    | Description                                                  |

|---------|--------------------------------------------------------------|

| Valid   | If the data presented by the data lines are either valid, in |

|         | the case of a read or have been written to memory.           |

| Data_I  | The data to be read when the RW flag is set to high.         |

| Data_O  | The data to be written when the RW flag is set high.         |

| Address | The address to which the data either should be read or write |

| RW      | The direction of the transfer, will read on asserted.        |

| Active  | When this signal is high a transaction is ongoing.           |

Table 3.1: Signal interface

to achieve a simpler model for communication. The signal interface was based on a pure memory mapped processor architecture where all communication between the processor and the off-chip peripheral units were done through an elaborate memory scheme. The downside was the inability to communicate meta data in a separate channel, such as internal statistics, cache hit ratios and etcetera. However this could be solved using other mechanisms as JTAG interfaces and ChipScope, providing a much cleaner and more customisable mechanism to probe the hardware.

The signal interface that each component needs to confirm to is shown in table 3.1 and contains the bare minimum to provide communication. However, it is meant as interface between the different layers in the architecture, and not between specialized components, leaving room for advanced features where it is needed.

The interface defines 4 signals which are driven by the source, namely the Data Out bus, Address bus, Active flag and finally the Read not Write flag. The two foremost signals are the Data to be transfered out from the component and the address of the data that are either to be written or read. When a transaction is wanted the source will assert the active flag until the transaction is done. The direction of the transfer is signaled through the RW-flag. If the RW flag is asserted the following action is a read transfer, and the client side should drive the signal on the Data In bus, ignoring the Data Out. On the other hand, if the RW-flag is set low, the operation in question is a write transfer, and thus the source should drive the signal on the data out bus. Independent of the direction of the transfer, when the destination side is finished handling the transfer, it should assert the valid flag for one cycle and thus signal that the transfer is completed.

# 3.3 Core

The core, being the processing element of the CPU, is the main component of the processor. However to this project the core alone is just another component needed to be able to perform benchmarks on different architectures. Important criteria is the number of cores that can be made available in the design, its documentation and to some degree its feature set, i.e. a core can't have a too scarce instruction set or else it wont be able to run the most basic benchmarks and tests.

Of the different cores investigated, MicroBlaze was the one that satisfied the all the 3 different criteria. By opting for a soft core such as MicroBlaze the design has the ability to scale beyond the hard cores available on the FPGA, which in the case of a Virtex-II Pro is limited to two PowerPCs. Also by utilizing a soft core the implemented multiprocessor is not bound to the specific implementation of the FPGA itself and thus if the resources available on the FPGA can't support the design, the VHDL code can be synthesized to fit on a new type of FPGA. As to the feature set, the core has an RISC based ISA which is most able to fulfill the demands imposed by the benchmarking and test suite. One of the key features is the MicroBlaze's ability to cut down on the features, such as the floating point operation. This in turn cuts down on the resources utilized by a single core and allows for a greater amount of total cores on the chip, or more advanced features requiring more logic.

## 3.3.1 Wrapping